# SCIENTIFIC REPORTS

### OPEN

Received: 16 February 2016 Accepted: 19 April 2016 Published: 09 May 2016

## Bottom-up synthesis of ordered metal/oxide/metal nanodots on substrates for nanoscale resistive switching memory

Un-Bin Han & Jang-Sik Lee

The bottom-up approach using self-assembled materials/processes is thought to be a promising solution for next-generation device fabrication, but it is often found to be not feasible for use in real device fabrication. Here, we report a feasible and versatile way to fabricate high-density, nanoscale memory devices by direct bottom-up filling of memory elements. An ordered array of metal/oxide/ metal (copper/copper oxide/copper) nanodots was synthesized with a uniform size and thickness defined by self-organized nanotemplate mask by sequential electrochemical deposition (ECD) of each layer. The fabricated memory devices showed bipolar resistive switching behaviors confirmed by conductive atomic force microscopy. This study demonstrates that ECD with bottom-up growth has great potential to fabricate high-density nanoelectronic devices beyond the scaling limit of top-down device fabrication processes.

Resistive switching random-access memory (ReRAM) with metal-insulator-metal (MIM) structure has advantages of fast switching speed, low operation voltage, and good scalability, and has therefore been widely investigated for future memory applications<sup>1–5</sup>. Metal-oxide-based ReRAM is considered as one of the most promising candidates for next-generation high-density nonvolatile memory devices<sup>6–10</sup>. Resistive switching is a change in electrical resistance between high-resistance state (HRS) and low-resistance state (LRS), and the physical phenomenon of memory operation; therefore, stable and reliable resistance changes in metal oxide materials are very important in ReRAM device applications. Resistive switching behavior has been observed in various oxides, such as NiO<sup>11–13</sup>, CuO<sub>x</sub><sup>14–19</sup>, HfO<sub>2</sub><sup>7,20–22</sup>, and Ta<sub>2</sub>O<sub>3</sub><sup>23–25</sup>. These oxides are reported to be good candidates for use as the resistive switching layer in ReRAM devices. Among the various metal oxides, CuO<sub>x</sub> is an attractive switching material because it can be synthesized at low cost and is non-toxic. In addition, CuO<sub>x</sub>-based memory devices show good reliability. Consequently, many researchers have studied application of CuO<sub>x</sub> as a candidate for use in next-generation memory devices<sup>16,17,26</sup>.

Next-generation memory device applications demand devices with very high density that exceeds the current lithographic length scale limit. The bottom-up approach using self-assembled nanostructures is a promising solution for scaling down the memory devices.

To fabricate nanoscale ReRAM devices, self-assembled nanoporous templates have been used<sup>27-35</sup>. Among the various nanoporous templates, anodized aluminum oxide (AAO) has advantages such as thermal/mechanical stability and ease of controlling a wide range of pore diameters, inter-pore distances, and depth of pores<sup>36-40</sup>. However, it is very difficult to grow nanoscale materials/structures inside the nanoporous templates directly since the pore size is typically less than 100 nm and the aspect ratio (pore depth-to-diameter ratio) is high. To grow the nanoscale materials inside the pores electrochemical deposition (ECD) is used. ECD into AAO templates is a very versatile and facile way to deposit nanoscale nanodots with controlled diameter and thickness. The ECD enables control of the composition of deposited films by adjusting the current density (*J*), pH, and temperature of the solution ( $T_{sol}$ )<sup>16,41</sup>. Therefore, the ECD of metals, semiconductors, and insulators has been used in many industrial applications<sup>41-44</sup>.

Department of Materials Science and Engineering, Pohang University of Science and Technology (POSTECH), Pohang 790-784, Korea. Correspondence and requests for materials should be addressed to J.-S.L. (email: jangsik@postech.ac.kr)

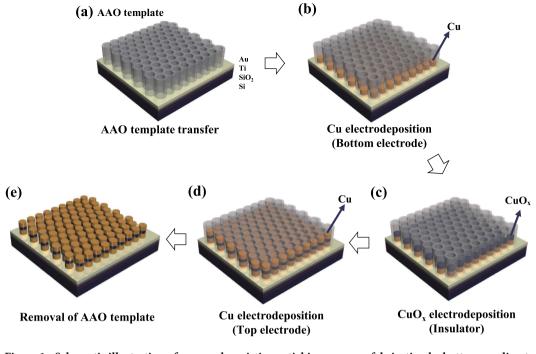

Figure 1. Schematic illustration of nanoscale resistive swtiching memory fabrication by bottom-up direct growth. (a) AAO nanotemplate transferred on conductive substrate. (b) Cu bottom electrode deposition by electrochemical deposition (ECD) through AAO nanotemplate mask. (c)  $CuO_x$  deposition by ECD. (d) Cu deposition by ECD. Cu/CuO<sub>x</sub>/Cu tri-layer was formed by bottom-up direct growth. (e) Final structure of nanoscale resistive switching memory composed of Cu/CuO<sub>x</sub>/Cu after removal of AAO template.

In this study, we used self-assembled AAO nanotemplates as masks for fabrication of uniform nanoscale Cu/ CuO<sub>x</sub>/Cu ReRAM devices. Using well-ordered AAO templates, ECD enables successful growth of Cu-based nanodots with high density on Au-coated Si substrates. The advantage of this process is growth of metal/oxide/ metal layer by sequential deposition of each layer with solution processes. In addition, there is no need to use vacuum deposition/lithography systems and etching/annealing processes for fabrication of nanoscale memory devices. The surface morphologies of AAO templates and nanoscale ReRAM devices were investigated using field-emission scanning electron microscopy (FE-SEM). The microstructure and crystal structure of the devices were analyzed using high-resolution transmission electron microscopy (HR-TEM) and x-ray diffraction (XRD). The topography of the Cu/CuO<sub>x</sub>/Cu nanodot memory devices was investigated using atomic force microscopy (AFM) and the resistive switching behavior of the CuO<sub>x</sub>-based memory devices was directly examined using conductive AFM. This work demonstrates that ECD with bottom-up growth has great potential to fabricate high-density nanoelectronic devices beyond the scaling limit of top-down device fabrication processes.

#### **Results and Discussion**

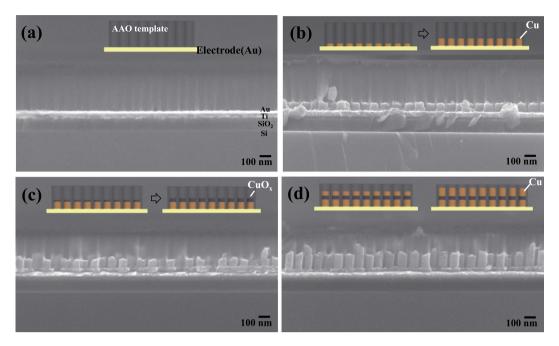

Bottom-up self-assembly approaches were used to fabricate the nanoscale resistive switching memory devices. AAO was used as the template to obtain ordered nanoscale devices by the bottom-up approach<sup>12,45,46</sup>. The AAO is a self-assembled, nano-porous structure in which pore sizes, pore densities, and thicknesses can easily be controlled by adjusting the process parameters. In addition, pore diameters ranging from several-nanometers to several hundred-nanometers can be obtained. During growth of Cu and CuO<sub>x</sub> onto the self-assembled AAO template, the metal ion reacts at surface of the electrode used for the substrate. Then the atoms are self-arranged from the bottom of the AAO template; they form a nanostructure from bottom-up self-assembly. Therefore, during the ECD of Cu, Cu nanodots can be formed by the reduction of  $Cu^{2+}$  ion in the solution starting from the bottom of AAO templates. Thicknesses can be controlled with the ECD time of Cu into the AAO template (Supporting Information, Fig. S1a-d). The thickness of Cu nanodots increased linearly with the deposition time because during ECD the amount of deposited material is proportional to the current, the deposition time, or both (Supporting Information, Fig. S1e). The Cu/CuO<sub>3</sub>/Cu nanodot arrays were fabricated as follows (Fig. 1). First, the AAO template with average pore diameter of 85 nm was transferred to the conductive substrates (Au/Ti/SiO<sub>2</sub>/Si). Cu bottom electrode/CuO<sub>x</sub> resistive switching layer/Cu top electrode were sequentially deposited by ECD using AAO nanotemplates. After ECD, the AAO templates were removed by NaOH solution and finally highly-ordered, high-density nanoscale resistive switching memory devices were fabricated by bottom-up self-assembly. The AAO template was well placed on the Au-coated substrate (Fig. 2a), and the template pores were found to be well-aligned vertically. High-density arrays (Fig. 2b-d) of Cu/CuO<sub>x</sub>/Cu nanodots were obtained by ECD with an AAO template mask ( $\sim$  300 nm-thick, average pore diameter = 85 nm). The nanodots were well formed within the pores of the AAO template. There is some fluctuation in shapes and thickness of Cu/CuO<sub>x</sub>/Cu nanodots shown

Figure 2. Bottom-up self-assembly and fabrication of nanoscale ReRAM devices by electrochemical deposition. Cross-sectional SEM images of  $Cu/CuO_x/Cu$  nanodots electrodeposited on Au-coated Si substrate (Au/SiO<sub>2</sub>/Si). (a) AAO template transferred on the substrate. (b) Electrochemical deposition of Cu bottom electrode. (c) Electrochemical deposition of  $CuO_x$  on  $Cu/Au/SiO_2/Si$ . (d) Electrochemical deposition of Cu on  $CuO_x/Cu/Au/SiO_2/Si$ .

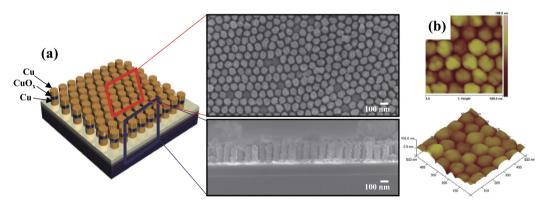

**Figure 3. High-density nanoscale resistive switching memory devices by bottom-up direct growth.** (a) Schematic illustration of the nanodot memory devices; plan and cross-sectional view SEM images of Cu/CuO<sub>x</sub>/Cu nanodots after removal of the AAO template. (b) Two and three-dimensional AFM images of Cu/CuO<sub>x</sub>/Cu nanodots.

in Fig. 2(d). This may be due to the non-uniform cutting during the preparation of samples for cross-sectional SEM images.

The final structure after removing the templates has almost uniform thickness shown in Figs 3 and 4. The total thickness of  $Cu/CuO_x/Cu$  nanodots was ~180 nm. ECD provides the bottom-up growth of  $Cu/CuO_x/Cu$  nanostructures from Au bottom electrodes to form ReRAM device structures as schematically shown in insets of Fig. 2. During ECD, the movement of the metal ions onto the AAO template was uniformly made by stirring the solution; this process increased metal ion mobility by eliminating air bubbles caused by the gas that originated from anions on the AAO template. Uniform deposition of nanodots is very important in this work, so solution was stirred at 200 rpm to prevent clogging of the AAO during metal deposition.

The formation of  $CuO_x$  and Cu nanodots in the AAO template can be explained by the charge transfer reactions and diffusion processes<sup>47–49</sup>. The formation of Cu and  $CuO_x$  is affected by pH, J, and  $T_{sol}^{49-51}$ . Temperature is one of the most important parameters to determine the overall reactions. In case of Cu, it can be deposited at high current density either at low or high temperatures. To form Cu metal as the bottom electrode, low temperature of 5 °C was selected since the deposition rate of Cu is very high at elevated temperatures. In case of CuO<sub>x</sub>, lower

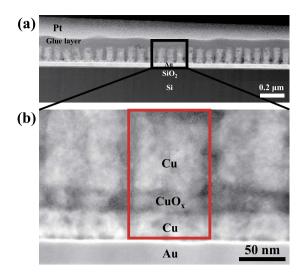

**Figure 4.** Microstructures of nanoscale ReRAM. (a) Cross-sectional high angle annular dark field (HAADF) TEM images of Cu/CuO<sub>x</sub>/Cu nanodots structure. (b) Detailed Cu/CuO<sub>x</sub>/Cu nanodots structure.

current density is required for proper synthesis of oxide layer. The deposition temperature (45 °C) is selected based on the growth rate of  $CuO_x$  layer.

In this study,  $CuO_x$  and Cu nanodots were deposited at a range of *J* at pH = 9. High *J* accelerated faster dissolution kinetics of Cu, so the concentration of  $Cu^{2+}$  ions increased and restricted the diffusion or migration of OH<sup>-</sup> in the diffusion layer. Consequently, a metallic Cu layer is easily formed on the Au substrate:

$$\mathrm{Cu}^{2+} + 2\mathrm{e}^{-} \to \mathrm{Cu},\tag{1}$$

On the other hand, at low *J*, the OH<sup>-</sup> ion shows higher diffusivity than that of Cu ions in bulk solution, resulting in easy combination of Cu<sup>+</sup> with OH<sup>-</sup> ions to form Cu<sub>2</sub>O:

$$2Cu^{2+} + 2e^{-} + 2OH^{-} \rightarrow Cu_2O + H_2O.$$

(2)

The surface morphologies of the Cu/CuO<sub>x</sub>/Cu nanodot memory devices (Fig. 3a) were investigated using FE-SEM. The SEM images of an array of Cu/CuO<sub>x</sub>/Cu nanodots were obtained after removal AAO nanotemplates. The bottom-up growth using the AAO nanotemplate mask produced uniform and well-ordered Cu/CuO<sub>x</sub>/Cu nanodots. Two- and three-dimensional AFM images (Fig. 3b) confirm that the array of Cu/CuO<sub>x</sub>/Cu nanodots was successfully synthesized with uniform dot size and thickness. Therefore, the bottom-up self-assembly processes using AAO templates successfully fabricated high-density nanoscale memory devices without using any lithography tools.

Further investigation on the morphology and crystal structure of the nanodots was conducted using cross-sectional TEM images of Cu/CuO<sub>x</sub>/Cu nanodot structure (Fig. 4a). Cu/CuO<sub>x</sub>/Cu tri-layer was confirmed from the magnified TEM image (Fig. 4b). The thickness of each layer is about 30 nm/20 nm/130 nm for Cu (bottom electrode)/CuO<sub>x</sub>/Cu (top electrode) measured using TEM image (Fig. 4b). Energy-dispersive X-ray spectroscopy (EDS) analysis was done to investigate the composition of each layer. It is clearly seen that Cu and CuO<sub>x</sub> layer are distinguishable (Supporting Information Fig. S2). XRD results also revealed that Cu and CuO<sub>x</sub> films could be well synthesized by controlling the current densities during ECD process (Supporting Information, Fig. S3). It is confirmed that Cu and CuO<sub>x</sub> films fabricated by ECD were polycrystalline with (111) and (200) orientations due to the surface energy of face-centered cubic structure<sup>19</sup>. Cu film deposited on bare wafer with Au electrode showed reddish-brown, whereas CuO<sub>x</sub> film showed dark blue (insets of Supporting Information, Fig. S3). In conjunction with TEM, XRD, and EDS analyses it is believed that Cu/CuO<sub>x</sub>/Cu structure was synthesized well by using bottom-up filling of each layer. It is very important to know the exact composition of each element in CuO<sub>x</sub> resistive switching layer. Further analysis will be done to characterize the composition of copper and oxygen in CuO<sub>x</sub> layer.

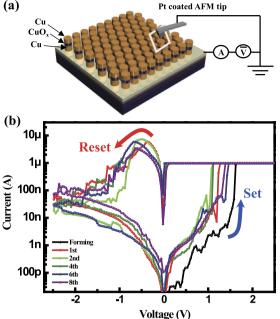

Electrical properties of nanoscale ReRAM devices were investigated by measuring current-voltage (I–V) characteristics of  $CuO_x$ -based nanodots at room temperature using conductive AFM and a Pt-coated cantilever as a probe tip (Fig. 5a). The top electrode was grounded, and the electrical bias was applied to the bottom electrode. To achieve the first filament formation (e.g. forming operation), positive bias was applied to the bottom electrode up to 2.5 V in DC sweep mode. The current was abruptly jumped to the compliance current level at 1.5 V, as shown in Fig. 5b (black line). In this transition process, the resistance state of the device is changed from high resistance state (HRS) to the low resistance state (LRS) with a conductive filament formation. By contrast, the device is changed from LRS to HRS by filament rupture when the negative bias is applied to the bottom electrode. The fabricated devices showed typical bipolar resistive switching behavior (Fig. 5b). Thus we can program and erase the device by applying positive set bias and negative reset bias, respectively. The set operations occurred at about 1.3 V, and reset operations occurred at about -0.75 V.

Figure 5. Schematic device measurement setup and programmable memory characteristics of nanoscale ReRAM. (a) Schematic measurement setup for electrical characterization of nanodot memory devices using conductive atomic force microscopy. (b) Resistive switching memory characteristics of nanoscale Cu/CuO<sub>x</sub>/Cu memory devices.

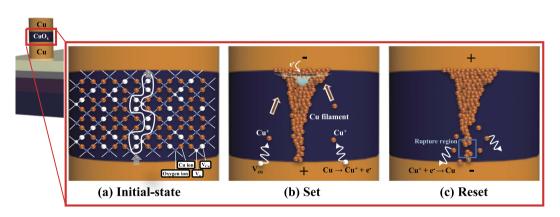

Figure 6. Resistive switching mechanism of nanoscale Cu/CuO<sub>x</sub>/Cu ReRAM. (a) Initial, (b) set, and (c) reset states.

To explain the resistive switching operations of the device (i.e. forming process, set, and reset), we considered Cu-ion migration in the device (Fig. 6a). The density and distribution of defects such as Cu<sup>+</sup> ions in the switching layer are the important parameters for resistive switching operation. In Cu/CuO<sub>x</sub>/Cu nanodot memory devices,  $CuO_x$  used as the resistive switching layer has the high binding energy between Cu and oxygen ions, while Cu used as the electrode has a low ionization energy<sup>23,52</sup>. Thus metallic Cu in the bottom electrode is more easly ionized to  $Cu^+$  ions and electrons (e<sup>-</sup>) than in the  $CuO_x$  switching layer when the positive bias is applied to the bottom electrode. Cu ions have high diffusivity and solubility in the CuO<sub>v</sub>. They are diffused from the bottom Cu electrode through the Cu vacancies of the CuO<sub>x</sub> switching layer, and they are accumulated from the top electrode to the bottom electrode with electrons injected from the top electrode. That is, the Cu ion-based filament can grow from the top to the bottom in the resistive switching layer during applying a positive bias. This soft-breakdown of the device is called forming operation which is the first set operation (Fig. 6b). The operation polarity of the device is dependent on the initial forming operation. Strong one-directional electric field is applied to a device during the forming operation. This process induces asymmetric Cu<sup>+</sup> ion distribution in the switching layer between the bottom and top electrodes because migration direction of Cu<sup>+</sup> ions is determined by the initial forming bias polarity, resulting in an asymmetric electrical property of the device. Once the filament is formed in the switching layer by forming process, the conductive filament gradually dissolves during applying the opposite bias (Fig. 6c). This filament dissolution occur at the bottom region which has a relatively weak filament than that

of the top region. Consequently, the repeated set and reset operations occur by filament formation and rupture at weak filament region. The conductive filament can be easily formed and ruptured by electrical bias due to  $Cu^+$  ion migration in the switching layer.

On/off ratio of the resistance states directly affects the sensing margin of memory devices. High on/off ratio is required for multilevel data storage and reliable reading operation. Our device shows on/off ratio of  $\sim 10^3$ . Therefore, it is thought that the memory device fabricated by bottom-up processes can be used as the nonvolatile memory element in high-density memory applications.

To check the validity of using the AFM probe as the conductive probe tip, we measured the current of samples attached directly to the bottom electrode of the AFM probe (short circuit) and of samples that did not contact the top electrode (open circuit) (Supporting Information, Fig. S4). The current increased immediately to the compliance level (1 $\mu$ A); this result confirms that the AFM probe operated well as the conductive probe. Moreover, in the open circuit the current was very low (~picoamperes). These measurements confirm that the resistive switching phenomenon originated from the fabricated nanoscale memory devices.

In this work, the individual memory device was measured by using the conductive AFM. We can program/ erase/read the individual memory elements by proper location of AFM tip since every device is separated by each other. In this study the main purpose is to demonstrate the possibility of fabrication of resistive switching memory devices *in situ* by ECD. The resistive switching properties are related to dimensions of nanodots. The layer thickness is related to set/reset voltages and the size of devices can determine the reset current. The device size is dependent on the pore diameter of templates and it is possible to change the diameter of templates by changing the AAO synthesis method. In addition, the oxide layer thickness can be controlled by deposition time. Comparative study is being done to change the dimensions of nanodevices by changing the pore diameters of AAO templates and by controlling the ECD processes.

In conclusion, we fabricated copper oxide-based ReRAM device using AAO as the template layer. Nanoscale memory devices were fabricated using bottom-up direct growth. ECD was used to synthesize  $Cu/CuO_x/Cu$  nanodots on self-assembled nanoporous AAO templates. The ordered array of MIM-structured memory devices ( $Cu/CuO_x/Cu$ ) was successfully synthesized with uniform dot size and thickness. The fabricated memory devices showed reliable and reproducible resistive switching memory characteristics with the application of electrical biases. This method overcomes the scaling limits of currently-used nano device-fabrication methods.

#### Methods

**Fabrication of self-assembled nano-templates.** To fabricate nanoporous AAO templates, aluminum (Al) foil (99.999% purity, 0.50-mm thickness, Goodfellow) was used. AAO nanotemplates were fabricated using a two-step anodization process after electro-polishing to flatten the surface as described previously<sup>40</sup>. The first and second anodizations were performed in 0.3 M oxalic acid with a carbon cathode at 7 °C and 40 V for 24 h. After the second anodization, the widening process was performed in a 0.1 M H<sub>3</sub>PO<sub>4</sub> solution at 30 °C. To remove the remaining Al layer, the AAO pores were filled with polystyrene (1.7 wt % PS/CHCl<sub>3</sub> solution), then the substrate was washed in a saturated solution of HgCl<sub>2</sub> with deionized water to separate the Al layer from AAO. The AAO/Polystyrene (PS) film was immersed in 0.1 M H<sub>3</sub>PO<sub>4</sub> solution at 30 °C for 30 min to remove the barrier layer from the oxide/metal interface, then was transferred onto the substrate. Finally, the PS film on the AAO templates was removed by immersing it in CHCl<sub>3</sub>.

**Fabrication of nano-scale resistive switching memory devices.** The Si substrate with a 100-nm SiO<sub>2</sub> layer was used as the substrate for device fabrication. A 20-nm-thick Ti adhesion layer and a 50-nm-thick Au layer were deposited on the SiO<sub>2</sub> layer by E-beam evaporation. The AAO template with 300-nm thickness was carefully transferred to the Au-coated Si substrate and dried at 80 °C for 20 min. Au is used as the seed layer for subsequent ECD. In addition, Au is used as the bottom contact for electrical measurement. Many kinds of metals can be used as the seed layer and the bottom contact, so other metals can be used for this purpose. ECD was used to deposit the Cu/CuO<sub>x</sub>/Cu nanodots sequentially on the substrate with the AAO template as the mask. The nanodots were synthesized from 0.6 M CuSO<sub>4</sub>·5H<sub>2</sub>O aqueous solution amended with 3 M lactic acid (Sigma Aldrich) to stabilize Cu (II) ions. The aqueous solution was adjusted to a pH of 9 by adding 2 M NaOH (Sigma Aldrich) then stirred overnight using a magnetic stirrer<sup>53,54</sup>. ECD of the nanodots into the AAO template was conducted in a two-electrode system using a carbon counter-electrode. ECD was performed using a DC power supply. ECD exploits electrically-driven redox reactions in the solution. On the basis of this mechanism, Cu nanodots as the bottom and top electrodes were deposited at  $J = 5 \text{ mA/cm}^2$  at 5 °C for 30 s, then CuO, nanodots as the resistive switching layer were deposited with  $J = 1 \text{ mA/cm}^2$  at 45 °C for 30 s. By this processes Cu and CuO<sub>x</sub> can be deposited by bottom-up growth on the substrates with AAO as the template. After deposition of  $Cu/CuO_x$ Cu nanodots, the substrate was immersed in 1 M NaOH solution for 30 min to remove the AAO template, then rinsed with deionized water to remove the remaining NaOH<sup>40</sup>.

**Characterization.** The morphologies of the Cu/CuO<sub>x</sub>/Cu nanodots were observed using a field emission scanning electron microscope (FE-SEM; JSM 7401F, JEOL). The microstructure and crystal structure of nanodots were investigated using a high-resolution transmission electron microscope (HR-(S)TEM-I; JEM 2100F with a Cs corrector on STEM, JEOL) and by x-ray diffraction (XRD, D/MAX-2500/PC, RIGAKU) using Cu K $\alpha$  radiation ( $\lambda = 1.54178$  Å). Before the TEM investigations, the samples were prepared using a focused ion beam (FIB; Helios, FEI). The surface morphologies of Cu/CuO<sub>x</sub>/Cu were examined using AFM (Dimension 3100 + Nanoscope V, VEECO) in non-contact mode and the electrical properties were measured using conductive AFM (XE-100, Park systems) in contact mode; the scan rate was 1 Hz, the scan configuration was 256 × 256 pixels, and the scan size was 500 nm × 500 nm. The AFM measurements were performed at room temperature

and atmospheric pressure. Micro- cantilevers (length :  $225 \mu$ m, Park Systems) with frequency of 75 kHz, a spring constant of ~2.8 N m<sup>-1</sup> and a radius of curvature of ~25 nm were used.

#### References

- Pan, F., Gao, S., Chen, C., Song, C. & Zeng, F. Recent progress in resistive random access memories: Materials, switching mechanisms, and performance. *Mater. Sci. Eng. R-Rep.* 83, 1–59 (2014).

- 2. Wang, H. et al. Resistive Switching Memory Devices Based on Proteins. Adv. Mater. 27, 7670-7676 (2015).

- 3. Onofrio, N., Guzman, D. & Strachan, A. Atomic origin of ultrafast resistance switching in nanoscale electrometallization cells. *Nat. Mater.* 14, 440–446 (2015).

- Menzel, S., Böttger, U., Wimmer, M. & Salinga, M. Physics of the Switching Kinetics in Resistive Memories. Adv. Funct. Mater. 25, 6306–6325 (2015).

- Chen, J. Y., Huang, C. W., Chiu, C. H., Huang, Y. T. & Wu, W. W. Switching Kinetic of VCM-Based Memristor: Evolution and Positioning of Nanofilament. Adv. Mater. 27, 5028–5033 (2015).

- 6. Yang, Y. et al. Oxide resistive memory with functionalized graphene as built-in selector element. Adv. Mater. 26, 3693–3699 (2014).

- 7. Wang, M. et al. Thermoelectric Seebeck effect in oxide-based resistive switching memory. Nat. Commun. 5, 4598 (2014).

- Kim, S., Choi, S. & Lu, W. Comprehensive Physical Model of Dynamic Resistive Switching in an Oxide Memristor. ACS NANO 8, 2369–2376 (2014).

- 9. Hou, J., Nonnenmann, S. S., Qin, W. & Bonnell, D. A. Size Dependence of Resistive Switching at Nanoscale Metal-Oxide Interfaces. *Adv. Funct. Mater.* 24, 4113–4118 (2014).

- 10. Wong, H. S. P. et al. Metal-Oxide RRAM. Proc. IEEE 100, 1951-1970 (2012).

- 11. Choi, D. & Kim, S. C. Coexistence of unipolar and bipolar resistive switching in Pt/NiO/Pt. Appl. Phys. Lett. 104, 193507 (2014).

- Perego, D. *et al.* Engineered fabrication of ordered arrays of Au-NiO-Au nanowires. *Nanotechnology* 24, 045302 (2013).

Goux, L. *et al.* Coexistence of the bipolar and unipolar resistive-switching modes in NiO cells made by thermal oxidation of Ni

- layers. J. Appl. Phys. 107, 024512 (2010). 14. Park, K. & Lee, J. S. Controlled synthesis of Ni/CuOx/Ni nanowires by electrochemical deposition with self-compliance bipolar

- resistive switching. *Sci. Rep.* **6**, 23069 (2016). 15. Park, K. & Lee, J. S. Flexible resistive switching memory with a Ni/CuOx/Ni structure using an electrochemical deposition process.

- Nanotechnology **27**, 125203 (2016). 16. Mignani, A., Ballarin, B., Boanini, E. & Cassani, M. C. Simple one step electrochemical preparation of copper nanostructures.

- Electrochim. Acta 115, 537–545 (2014).

17. Liang, K. D. et al. Single CuO(x) nanowire memristor: forming-free resistive switching behavior. ACS Appl. Mater. Interfaces 6, 16537–16544 (2014).

- D'Aquila, K. et al. Bipolar resistance switching in Pt/CuOx/Pt via local electrochemical reduction. Appl. Phys. Lett. 104, 242902 (2014).

- Luo, B. *et al.* Copper nanocubes and nanostructured cuprous oxide prepared by surfactant-assisted electrochemical deposition. *CrystEngComm* 15, 5654 (2013).

- Akbari, M. & Lee, J.-S. Control of resistive switching behaviors of solution-processed HfOX-based resistive switching memory devices by n-type doping. RSC Adv. 6, 21917–21921 (2016).

- Yoon, J. H. et al. Pt/Ta2O5/HfO2-x/Ti Resistive Switching Memory Competing with Multilevel NAND Flash. Adv. Mater. 27, 3811–3816 (2015).

- Kim, Y.-M. & Lee, J.-S. Reproducible resistance switching characteristics of hafnium oxide-based nonvolatile memory devices. J. Appl. Phys. 104, 114115 (2008).

- Xiao, B. & Watanabe, S. Interface Structure in Cu/Ta2O5/Pt Resistance Switch: A First-Principles Study. ACS Appl. Mater. Interfaces 7, 519–525 (2015).

- 24. Wang, M. *et al.* Conduction mechanism of a TaO(x)-based selector and its application in crossbar memory arrays. *Nanoscale* 7, 4964–4970 (2015).

- Kim, S., Choi, S., Lee, J. & Lu, W. D. Tuning Resistive Switching Characteristics of Tantalum Oxide Memristors through Si Doping. ACS NANO 8, 10262–10269 (2014).

- Kumar, M. & Som, T. Structural defect-dependent resistive switching in Cu-O/Si studied by Kelvin probe force microscopy and conductive atomic force microscopy. *Nanotechnology* 26, 345702 (2015).

- Xue, J., Xu, Y. & Jin, Z. Interfacial Interaction in Anodic Aluminum Oxide Templates Modifies Morphology, Surface Area, and Crystallization of Polyamide-6 Nanofibers. Langmuir 32, 2259–2266 (2016).

- Wu, S., Zuber, F., Brugger, J., Maniura-Weber, K. & Ren, Q. Antibacterial Au nanostructured surfaces. Nanoscale 8, 2620–2625 (2016).

- Sui, C. et al. SERS activity with tenfold detection limit optimization on a type of nanoporous AAO-based complex multilayer substrate. Nanoscale 8, 5920–5927 (2016).

- 30. Song, J. M. & Lee, J. S. Self-assembled nanostructured resistive switching memory devices fabricated by templated bottom-up growth. Sci. Rep. 6, 18967 (2016).

- Lu, X., Yan, Q., Ma, Y., Guo, X. & Xiao, S. J. Growing Embossed Nanostructures of Polymer Brushes on Wet-Etched Silicon Templated via Block Copolymers. Sci. Rep. 6, 20291 (2016).

- 32. Li, Y. et al. Preparation of Aluminum Nanomesh Thin Films from an Anodic Aluminum Oxide Template as Transparent Conductive Electrodes. Sci. Rep. 6, 20114 (2016).

- Zhao, H. et al. Self-supported metallic nanopore arrays with highly oriented nanoporous structures as ideally nanostructured electrodes for supercapacitor applications. Adv. Mater. 26, 7654–7659 (2014).

- Martin, J., Martin-Gonzalez, M., Francisco Fernandez, J. & Caballero-Calero, O. Ordered three-dimensional interconnected nanoarchitectures in anodic porous alumina. *Nat. Commun.* 5, 5130 (2014).

- 35. Duong, B. *et al.* High Throughput Printing of Nanostructured Carbon Electrodes for Supercapacitors. *Adv. Mater. Interfaces* 1, 1300014 (2014).

- Wen, L. et al. Designing Heterogeneous 1D Nanostructure Arrays Based on AAO Templates for Energy Applications. Small 11, 3408–3428 (2015).

- Lim, N. et al. A tunable sub-100 nm silicon nanopore array with an AAO membrane mask: reducing unwanted surface etching by introducing a PMMA interlayer. Nanoscale 7, 13489–13494 (2015).

- Wang, Z. L., Guo, R., Ding, L. X., Tong, Y. X. & Li, G. R. Controllable template-assisted electrodeposition of single- and multi-walled nanotube arrays for electrochemical energy storage. Sci. Rep. 3, 1204 (2013).

- Michalska-Domańska, M., Norek, M., Stępniowski, W. J. & Budner, B. Fabrication of high quality anodic aluminum oxide (AAO) on low purity aluminum—A comparative study with the AAO produced on high purity aluminum. *Electrochim. Acta* 105, 424–432 (2013).

- Lyu, S.-H. & Lee, J.-S. Highly scalable resistive switching memory cells using pore-size-controlled nanoporous alumina templates. J. Mater. Chem. 22, 1852–1861 (2012).

- Kostevšek, N., Rožman, K. Ž., Pečko, D., Pihlar, B. & Kobe, S. A comparative study of the electrochemical deposition kinetics of iron-palladium alloys on a flat electrode and in a porous alumina template. *Electrochim. Acta* 125, 320–329 (2014).

- 42. Qin, L. *et al. In Situ* Electrochemical Synthesis and Deposition of Discotic Hexa-peri-hexabenzocoronene Molecules on Electrodes: Self-Assembled Structure, Redox Properties, and Application for Supercapacitor. *Small* **11**, 3028–3034 (2015).

- Lu, Y. et al. Atmospheric-pressure microplasma as anode for rapid and simple electrochemical deposition of copper and cuprous oxide nanostructures. RSC Adv. 5, 62619–62623 (2015).

- 44. Ertekin, Z., Tamer, U. & Pekmez, K. Cathodic electrochemical deposition of Magneli phases TinO2n-1 thin films at different temperatures in acetonitrile solution. *Electrochim. Acta* 163, 77–81 (2015).

- Shimizu, T. et al. Fabrication of an Array of Ni/NiO Nanowire-ReRAM Using AAO Template on Si. e-J. Surf. Sci. Nanotech. 10, 476–479 (2012).

- Ielmini, D., Cagli, C., Nardi, F. & Zhang, Y. Nanowire-based resistive switching memories: devices, operation and scaling. J. Phys. D-Appl. Phys. 46, 074006 (2013).

- 47. Filipic, G. & Cvelbar, U. Copper oxide nanowires: a review of growth. Nanotechnology 23, 194001 (2012).

- Wang, X. et al. Selective fabrication of Cu/Cu2O nanowires using porous alumina membranes in acidic solution. Solid State Sci. 13, 280–284 (2011).

- 49. Inguanta, R., Piazza, S. & Sunseri, C. Template electrosynthesis of aligned Cu<sub>2</sub>O nanowires. *Electrochim. Acta* 53, 6504–6512 (2008).

- Nikolic, N., Pavlovic, L., Pavlovic, M. & Popov, K. Effect of temperature on the electrodeposition of disperse copper deposits. J. Serb. Chem. Soc. 72, 1369–1381 (2007).

- 51. Shin, S. *et al.* Tuning the morphology of copper nanowires by controlling the growth processes in electrodeposition. *J. Mater. Chem.* **21**, 17967–17971 (2011).

- 52. Soon, A., Wallman, J., Delley, B. & Stampfl, C. Early transition metal dopants in cuprous oxide: To spin or not to spin. *Curr. Appl. Phys.* 13, 1707–1712 (2013).

- Zheng, J. Y., Jadhav, A. P., Song, G., Kim, C. W. & Kang, Y. S. Cu and Cu<sub>2</sub>O films with semi-spherical particles grown by electrochemical deposition. *Thin Solid Films* 524, 50–56 (2012).

- Wang, L. C., de Tacconi, N. R., Chenthamarakshan, C. R., Rajeshwar, K. & Tao, M. Electrodeposited copper oxide films: Effect of bath pH on grain orientation and orientation-dependent interfacial behavior. *Thin Solid Films* 515, 3090–3095 (2007).

#### Acknowledgements

This work was supported by National Research Foundation of Korea (NRF-2015R1A2A1A15055918). This work was also supported by Future Semiconductor Device Technology Development Program (10045226) funded by the Ministry of Trade, Industry & Energy (MOTIE)/Korea Semiconductor Research Consortium (KSRC). In addition, this work was partially supported by Brain Korea 21 PLUS project (Center for Creative Industrial Materials).

#### **Author Contributions**

J.-S.L. conceived and designed the experiments. U.-B.H. performed experiments under the supervision of J.-S.L., J.-S.L. and U.-B.H. wrote the paper.

#### Additional Information

Supplementary information accompanies this paper at http://www.nature.com/srep

Competing financial interests: The authors declare no competing financial interests.

How to cite this article: Han, U.-B. and Lee, J.-S. Bottom-up synthesis of ordered metal/oxide/metal nanodots on substrates for nanoscale resistive switching memory. *Sci. Rep.* **6**, 25537; doi: 10.1038/srep25537 (2016).

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/