## Statistical variability study of random dopant fluctuation on gate-all-around inversionmode silicon nanowire field-effect transistors

Jun-Sik Yoon, Taiuk Rim, Jungsik Kim, Kihyun Kim, Chang-Ki Baek, and Yoon-Ha Jeong

Citation: Applied Physics Letters **106**, 103507 (2015); doi: 10.1063/1.4914976

View online: http://dx.doi.org/10.1063/1.4914976

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/106/10?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Random telegraph signal and spin characteristics of the gate-all-around poly-silicon nanowire J. Appl. Phys. **116**, 174508 (2014); 10.1063/1.4901196

Electronic transport mechanisms in scaled gate-all-around silicon nanowire transistor arrays Appl. Phys. Lett. **103**, 263504 (2013); 10.1063/1.4858955

Study of individual phonon scattering mechanisms and the validity of Matthiessen's rule in a gate-all-around silicon nanowire transistor

J. Appl. Phys. 113, 014501 (2013); 10.1063/1.4772720

Characteristics of gate-all-around silicon nanowire field effect transistors with asymmetric channel width and source/drain doping concentration

J. Appl. Phys. **112**, 034513 (2012); 10.1063/1.4745858

Random telegraph signal noise in gate-all-around silicon nanowire transistors featuring Coulomb-blockade characteristics

Appl. Phys. Lett. 94, 083503 (2009); 10.1063/1.3089240

## Statistical variability study of random dopant fluctuation on gate-all-around inversion-mode silicon nanowire field-effect transistors

Jun-Sik Yoon,<sup>1</sup> Taiuk Rim,<sup>1</sup> Jungsik Kim,<sup>2</sup> Kihyun Kim,<sup>1</sup> Chang-Ki Baek,<sup>1,3</sup> and Yoon-Ha Jeong<sup>3</sup>

<sup>1</sup>Department of Creative IT Engineering and Future IT Innovation Lab, Pohang University of Science and Technology, Pohang 790-784, Korea

<sup>2</sup>Division of IT Convergence Engineering, Pohang University of Science and Technology, Pohang 790-784, Korea

<sup>3</sup>Department of Electrical Engineering, Pohang University of Science and Technology, Pohang 790-784,

(Received 11 January 2015; accepted 28 February 2015; published online 13 March 2015)

Random dopant fluctuation effects of gate-all-around inversion-mode silicon nanowire field-effect transistors (FETs) with different diameters and extension lengths are investigated. The nanowire FETs with smaller diameter and longer extension length reduce average values and variations of subthreshold swing and drain-induced barrier lowering, thus improving short channel immunity. Relative variations of the drain currents increase as the diameter decreases because of decreased current drivability from narrower channel cross-sections. Absolute variations of the drain currents decrease critically as the extension length increases due to decreasing the number of arsenic dopants penetrating into the channel region. To understand variability origins of the drain currents, variations of source/drain series resistance and low-field mobility are investigated. All these two parameters affect the variations of the drain currents concurrently. The nanowire FETs having extension lengths sufficient to prevent dopant penetration into the channel regions and maintaining relatively large cross-sections are suggested to achieve suitable short channel immunity and small variations of the drain currents. © 2015 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4914976]

The device variability due to random dopant fluctuation (RDF) is one of the major problems in nanoscale devices. <sup>1–5</sup> Discretized dopants for high-doped source/drain regions permeate into both the source/drain extension regions and the channel regions of gate-all-around (GAA) inversion-mode silicon nanowire field-effect transistors (FETs), and fluctuate the device characteristics including threshold voltages ( $V_{th}$ ), source/drain series resistances ( $R_{sd}$ ), and transconductances ( $G_m$ ) related to the effective gate length ( $L_{eff}$ ) and mobility. <sup>6,7</sup>

Recently, the nanoscale devices with low-doped underlap regions are considered to meet the criteria of low-power application without reducing the drive currents critically. Respectively. However, it is important to investigate the size of diameters  $(D_{NW})$  and extension lengths  $(L_{EXT})$  to maintain proper device performance and also to reduce variations of the device characteristics. In addition, it is essential to understand the variability origins of the DC performance for reliable device design. In this work, we investigated the RDF effects, induced by the high-doped source/drain regions, on the n-type nanowire FETs with different  $D_{NW}$  and  $L_{EXT}$  in terms of short channel characteristics and drain currents. We also analyzed the variations of DC performance (drain currents and  $G_m$ ) by comparing the correlations of those with several electrical parameters.

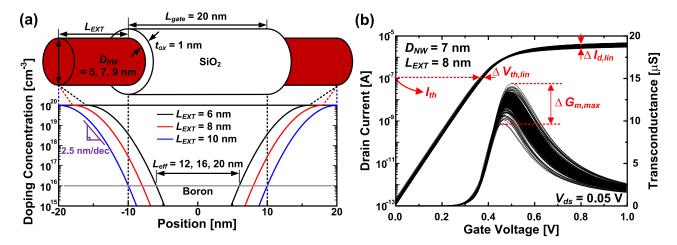

GAA inversion-mode silicon nanowire FETs were simulated using Sentaurus TCAD<sup>10</sup> by solving drift-diffusion equations coupled with Poisson equation self-consistently. For the quantum effects, density-gradient model<sup>11</sup> is considered instead of Schrodinger equation because of its shorter computation time to be effective for the variability study. In addition, three basic mobility models are considered; Philips

unified mobility model<sup>12</sup> for impurity scattering, Canali model<sup>13</sup> for velocity saturation, and Lombardi model<sup>14</sup> for surface roughness scattering at the interface between nanowire channel and oxide. All the n-type nanowire FETs had the same arsenic doping profiles with peak value of 10<sup>20</sup> cm<sup>-3</sup> at the edges of source/drain extension regions and Gaussian doping profile of about 2.5 nm/dec, which is comparable to the simulated data considering Kinetic Monte Carlo implantation.<sup>7,8</sup> Nanowire channels were doped with boron at constant value of 10<sup>16</sup> cm<sup>-3</sup> to avoid RDF effects of boron and to focus on the impact of discrete arsenic dopants on the variability. 15 The nanowire FETs had constant physical gate length ( $L_{gate}$ ) of 20 nm and SiO<sub>2</sub> thickness ( $t_{ox}$ ) of 1 nm,  $D_{NW}$  splits of 5, 7, 9 nm and  $L_{EXT}$  splits of 6, 8, 10 nm.  $L_{eff}$  was defined as the distance between two points having equal concentrations between arsenic and boron dopants. Geometrical parameters and doping profiles of the nanowire FETs were shown in Fig. 1(a).

RDF effects on the nanowire FETs were investigated using Sano model, which considers both long-range and short-range Coulomb potentials separately and places discrete dopants successfully under the drift-diffusion simulations. <sup>16</sup> Screening factor was calculated as  $2 \times N^{1/3}$ , where N is arsenic doping concentration. Since all the nanowire FETs had low boron doping concentration in the channel regions, only the arsenic dopants of the source/drain regions were randomized. The number of samples for RDF is 200 for each  $D_{NW}$  and  $L_{EXT}$ . Linear on-currents ( $I_{d,lin}$ ) were measured at the gate voltage ( $V_{gs}$ ) of 0.8 V and the drain voltage ( $V_{ds}$ ) of 0.05 V, whereas maximum transconductances ( $G_{m,max}$ ) were extracted at the maximum value of  $G_m$  at  $V_{ds}$  of 0.05 V.  $V_{th}$

FIG. 1. (a) Schematic diagram and doping profiles of the simulated nanowire FETs with three different diameters  $(D_{NW})$  of 5, 7, and 9 nm and extension lengths  $(L_{EXT})$  of 6, 8, and 10 nm. All the nanowire FETs have the equivalent arsenic doping gradients of 2.5 nm/dec. (b) One example for the fluctuations of the drain currents and the transconductances for the nanowire FETs with the  $D_{NW}$  of 7 nm and the  $L_{EXT}$  of 8 nm.

in the linear regime  $(V_{th,lin})$  were extracted using the constant current method at  $I_{th} = W_{eff}/L_{gate} \times 10^{-7}$ , where  $W_{eff}$  is defined as the perimeter of the nanowire channel  $(W_{eff} = D_{NW} \times \pi)$ . One example for the fluctuations of  $V_{th,lin}$ ,  $I_{d,lin}$ , and  $G_{m,max}$  at  $V_{ds}$  of 0.05 V is shown in Fig. 1(b).

To analyze the RDF effects, we extracted several electrical parameters such as  $R_{sd}$  and low-field mobility ( $\mu_0$ ).  $R_{sd}$  of the nanowire FETs were extracted using Y-function technique, <sup>17</sup> and  $\mu_0$  was extracted at the peak value of mobility using split C-V method. <sup>18</sup> Here, we used the oxide capacitances ( $C_{ox}$ ) extracted from the slope of the inversion charge ( $Q_{inv}$ ), integrated from the simulated C-V curves, versus  $V_{gs}$  curves in the strong inversion regime. <sup>19</sup> Y-function and mobility equations used for the extractions of  $R_{sd}$  and  $\mu_0$  in the linear regime, respectively, are given as

$$Y \equiv \frac{I_{d,lin}}{\sqrt{G_m}},\tag{1}$$

$$\mu = \frac{L_{gate}^2 \times I_d}{(V_{ds} - I_d \cdot R_{sd}) \times \int C_{gc} dV'_{gs}}.$$

(2)

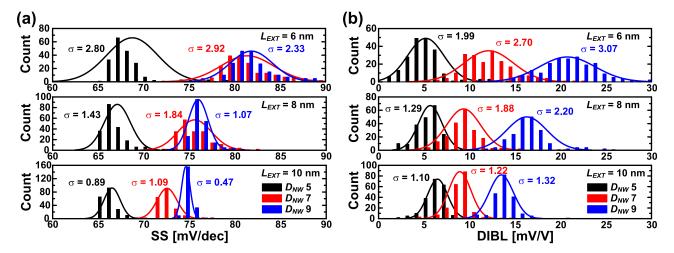

Short channel characteristics (subthreshold slope (SS), drain-induced barrier lowering (DIBL)) of the nanowire

FETs with  $D_{NW}$  and  $L_{EXT}$  splits are investigated (Figs. 2(a) and 2(b)). SS values are extracted below  $V_{th}$  in the saturation regime ( $V_{ds} = 0.8 \text{ V}$ ), whereas DIBL values are given as

$$DIBL = -\frac{V_{th,sat} - V_{th,lin}}{V_{ds,sat} - V_{ds,lin}},$$

(3)

where  $V_{th,sat}$  is the  $V_{th}$  extracted at  $V_{ds}$  of 0.8 V,  $V_{ds,sat}$  and  $V_{ds,lin}$  are the  $V_{ds}$  of 0.8 V and 0.05 V, respectively.<sup>20</sup> The nanowire FETs with longer  $L_{EXT}$  reduce the number of arsenic dopants penetrating into the channel regions, and decrease both the average and standard deviations of SS and DIBL. As  $D_{NW}$  increases, reduced gate-to-channel controllability affects DIBL and SS values to increase. But as shown in Fig. 2(a), the SS values increase critically as  $D_{NW}$  changes from 5 to 7 nm, whereas those increase slightly as  $D_{NW}$ changes from 7 to 9 nm. This non-uniform change of SS as  $D_{NW}$  increases is due to the significantly reduced quantum effects for the  $D_{NW}$  of 7 and 9 nm (Ref. 21) and is also similar to the experimental data.<sup>22</sup> The nanowire FETs with  $D_{NW}$ of 5 nm have gate-to-channel controllability enough to maintain low values and variations of SS and DIBL even under the  $L_{EXT}$  of 6 nm. Although the nanowire FETs with  $D_{NW}$  of 7 and 9 nm have large values of SS and DIBL, the standard

FIG. 2. Distribution of (a) subthreshold slope (SS) and (b) drain-induced barrier lowering (DIBL) for the nanowire FETs with all three different  $D_{NW}$  and  $L_{EXT}$ .

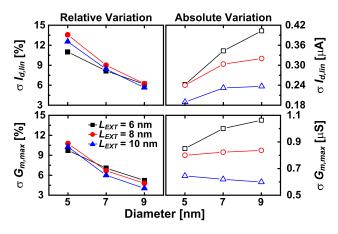

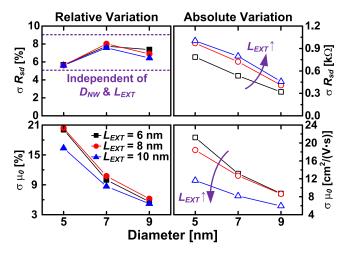

FIG. 3. Relative and absolute variations of the drain currents  $(I_{d,lin})$  and the maximum transconductance  $(G_{m,max})$  for the nanowire FETs with all three different  $D_{NW}$  and  $L_{EXT}$ .

variations of SS and DIBL are low; the maximum standard deviations of SS and DIBL are  $2.92 \,\mathrm{mV/dec}$  and  $3.07 \,\mathrm{mV/V}$ , respectively. All the variations of the  $V_{th,lin}$  induced by the RDF effects are small; the maximum standard deviation of the  $V_{th,lin}$  is  $4.7 \,\mathrm{mV}$ , which is comparable to the FinFETs with high extension doping concentrations. These results indicate that the nanowire FETs with undoped channel regions are immune to the variability from the RDF effects induced by high-doped source/drain regions.

Figure 3 shows the relative and absolute variations of  $I_{d,lin}$  and  $G_{m,max}$ . Relative variations are calculated as the standard deviations divided by the average values, whereas absolute variations are equivalent to the standard deviations. As the  $D_{NW}$  decreases, relative variations of  $I_{d,lin}$  and  $G_{m,max}$  increase but do not depend on  $L_{EXT}$ . The nanowire FETs with smaller  $D_{NW}$  have larger  $R_{sd}$  as well as smaller current drivability due to narrower source extension regions. Thus, the average values of  $I_{d,lin}$  and  $G_{m,max}$  decrease critically, causing greater relative variations and satisfying Pelgrom's law. Absolute variations of  $I_{d,lin}$  increase as the  $D_{NW}$  increases or as the  $L_{EXT}$  decreases. Absolute variations of  $G_{m,max}$  show similar aspects as the absolute variations of  $I_{d,lin}$  except for the  $L_{EXT}$  of 10 nm.

FIG. 4. Relative and absolute variations of the source/drain series resistance  $(R_{sd})$  and the low-field mobility  $(\mu_0)$  for the nanowire FETs with all three different  $D_{NW}$  and  $L_{EXT}$ .

Figure 4 shows the relative and absolute variations of the  $R_{sd}$  and  $\mu_0$ . Relative variations of  $\mu_0$  follow the same trend as those of  $I_{d,lin}$  and  $G_{m,max}$ , whereas relative variations of  $R_{sd}$  are independent of the  $D_{NW}$  and the  $L_{EXT}$ . As the  $D_{NW}$ decreases, increasing both averages and absolute variations of  $R_{sd}$  maintains certain values for the relative variations of  $R_{sd}$  between 5% and 9%. Different from the absolute variations of  $I_{d,lin}$  and  $G_{m,max}$ , the absolute variations of  $R_{sd}$  and  $\mu_0$  increase as the  $D_{NW}$  decreases. The nanowire FETs with smaller  $D_{NW}$  have higher possibility for the carriers to be affected by individual arsenic dopants because of the closer distance between the carriers and the dopants. Longer  $L_{EXT}$ affects smaller absolute variations of  $\mu_0$  because of the small number of arsenic dopants in the intrinsic channel region. Instead, the absolute variations of  $R_{sd}$  increase as the  $L_{EXT}$ increases due to the large variations of the number of arsenic dopants in the low-doped underlap regions.

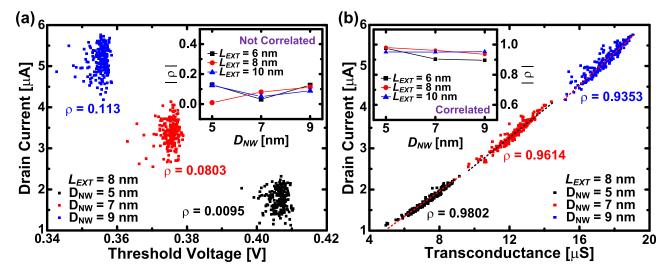

To investigate the variability origins of  $I_{d,lin}$ , correlations of  $I_{d,lin}$  with  $V_{th,lin}$  and  $G_{m,max}$  are shown in Figs. 5(a) and 5(b). Here, the correlation coefficients ( $\rho$ ) are calculated using Spearman's correlations. <sup>2,5,25</sup> All  $I_{d,lin}$  values are not

FIG. 5. One example for the scatter plots of the drain currents  $(I_{d,lin})$  versus (a) the threshold voltages  $(V_{th,lin})$  and (b) the maximum transconductance  $(G_{m,max})$  for the nanowire FETs with all three  $D_{NW}$  and the fixed  $L_{EXT}$  of 8 nm. Insets are their correlation coefficients  $(\rho)$  for all three different  $D_{NW}$  and  $L_{EXT}$ .

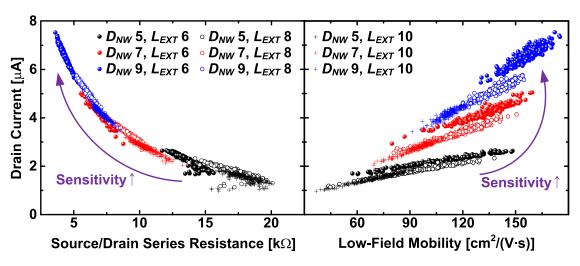

FIG. 6. Scatter plots between the drain currents  $(I_{d,lin})$  and electrical parameters  $(R_{sd}, \mu_0)$  with all three different  $D_{NW}$  and  $L_{EXT}$ .

correlated to the  $V_{th,lin}$  with maximum  $\rho$  of 0.129, whereas those are highly correlated to the  $G_{m,max}$ . As shown in Fig. 5(a), increase of  $V_{th}$  as  $D_{NW}$  decreases is due to the quantum effects from the volume inversion<sup>26</sup> as well as band-gap widening,<sup>27</sup> which reduce the inversion charge density and thus  $I_{d,lin}$  at the same  $V_{gs}$ . The components which can induce the variations of  $G_{m,max}$  are  $t_{ox}$ ,  $D_{NW}$ ,  $L_{gate}$ ,  $\mu_0$ , and  $R_{sd}$ , <sup>25</sup> but only  $\mu_0$  and  $R_{sd}$  are varied by the RDF effects.

Figure 6 shows the scatter plots of  $I_{d,lin}$  with respect to the electrical parameters ( $R_{sd}$  and  $\mu_0$ ). SS and DIBL are excluded because their absolute variations and correlations with the drain currents are negligible. Variations of  $G_{m,max}$  depend on the variations of  $R_{sd}$  and  $\mu_0$  directly, so  $G_{m,max}$  is not included here. Sensitivity is defined as the slope of the scatter plots, which is the variations of  $I_{d,lin}$  with respect to the variations of the  $R_{sd}$  or  $\mu_0$ . Sensitivity indicates how greatly the variations of the  $R_{sd}$  or  $\mu_0$  affect the variations of  $I_{d,lin}$ .

The variations of  $I_{d,lin}$  are highly correlated with the variations of all electrical parameters, meaning that the variations of  $R_{sd}$  and  $\mu_0$  affect the absolute variations of  $I_{d,lin}$  concurrently. As the  $L_{EXT}$  increases, much critically decreased variations of  $\mu_0$ , compared to the increased variations of  $R_{sd}$ , reduce the variations of  $I_{d,lin}$ . As the  $D_{NW}$  decreases, sensitivity values decrease greatly, and this results in reducing the impacts of the variations of  $R_{sd}$  and  $\mu_0$  on the variations of  $I_{d,lin}$ , even though the variations of  $R_{sd}$  and  $\mu_0$  increase, as shown in Fig. 4. Decreased current drivability for smaller  $D_{NW}$  also contributes to the smaller variations of  $I_{d,lin}$  in a relative point of view.

Absolute variations of  $G_{m,max}$  depend on the variations of  $R_{sd}$  and  $\mu_0$ . The nanowire FETs with the  $L_{EXT}$  of 6 and 8 nm have overlap regions; the number of arsenic dopants in the channel regions increases and induces the large variations of  $\mu_0$ , and thus  $G_{m,max}$ . Instead, the nanowire FETs with the  $L_{EXT}$  of 10 nm have underlap regions, causing low variations of  $\mu_0$  but increasing average values and variations of  $R_{sd}$ . Thus, the opposite relationship between the variations of  $R_{sd}$  and  $\mu_0$  affects the variations of  $G_{m,max}$  differently in terms of the  $D_{NW}$  and the  $L_{EXT}$ .

In summary, numerical 3D device simulations were performed for the nanowire FETs in order to investigate RDF

effects to the device performance according to various  $D_{NW}$ and  $L_{EXT}$ . The variations of SS and DIBL increased as  $L_{EXT}$ decreased, but the nanowire FETs with undoped channel and with small  $D_{NW}$  were enough to maintain gate-to-channel controllability. On the other hand, relative variations of  $I_{d,lin}$ and  $G_{m,max}$  increased critically as the  $D_{NW}$  decreased, satisfying the Pelgrom's law. Using the variations of  $V_{th,lin}$ ,  $R_{sd}$ , and  $\mu_0$ , the absolute variations of  $I_{d,lin}$  and  $G_{m,max}$  were explained physically for the nanowire FETs with different  $D_{NW}$  and  $L_{EXT}$ .  $R_{sd}$  and  $\mu_0$  influenced on the variations of  $I_{d,lin}$  and  $G_{m,max}$  concurrently, whereas  $V_{th,lin}$  had no influence. It is promised to minimize penetration of arsenic dopants into the channel region but to maintain large crosssections so that the nanowire FETs can achieve short channel immunity and low variations of the drain currents and the transconductances.

This research was supported by the MSIP (Ministry of Science, ICT and Future Planning), Korea, under the "IT Consilience Creative Program" (NIPA-2014-H0201-14-1001) supervised by the NIPA (National IT Industry Promotion Agency) and also supported by IDEC (IC Design Education Center).

<sup>&</sup>lt;sup>1</sup>X. Wang, A. R. Brown, B. Cheng, and A. Asenov, Tech. Dig. Int. Electron Devices Meet. **2011**, 103–106.

<sup>&</sup>lt;sup>2</sup>J. Mazurier, O. Weber, F. Andrieu, F. Allain, L. Tosti, L. Brevard, O. Rozeau, M.-A. Jaud, P. Perreau, C. Fenouillet-Beranger, F. A. Khaja, B. Colombeau, G. De Cock, G. Ghibaudo, M. Belleville, O. Faynot, and T. Poiroux, Tech. Dig. Int. Electron Devices Meet. 2011, 575–578.

<sup>&</sup>lt;sup>3</sup>G. Leung and C. O. Chui, IEEE Electron Device Lett. 33, 767–769 (2012).

<sup>4</sup>S. Markov, B. Cheng, and A. Asenov, IEEE Electron Device Lett. 33, 315–317 (2012).

<sup>&</sup>lt;sup>5</sup>A. Paul, A. Bryant, T. B. Hook, C. C. Yeh, V. Kamineni, J. B. Johnson, N. Tripathi, T. Yamashita, G. Tsutsui, V. Basker, T. E. Standaert, J. Faltermeier, B. S. Haran, S. Kanakasabapathy, H. Bu, J. Cho, J. Iacoponi, and M. Khare, Tech. Dig. Int. Electron Devices Meet. **2013**, 361–364.

<sup>&</sup>lt;sup>6</sup>J. Zhuge, R. Wang, R. Huang, J. Zou, X. Huang, D.-W. Kim, D. Park, X. Zhang, and Y. Wang, Tech. Dig. Int. Electron Devices Meet. 2009, 61–64.

<sup>7</sup>M. Uematsu, K. M. Itoh, G. Mil'nikov, H. Minari, and N. Mori, Tech. Dig. Int. Electron Devices Meet. 2012, 709–712.

<sup>&</sup>lt;sup>8</sup>P. Kerber, Q. Zhang, S. Koswatta, and A. Bryant, IEEE Electron Device Lett. 34, 6–8 (2013).

<sup>&</sup>lt;sup>9</sup>B. D. Gaynor and S. Hassoun, IEEE Trans. Electron Devices **61**, 2738–2744 (2014).

<sup>&</sup>lt;sup>10</sup>Synopsys, Sentaurus Device User Guide (Mountain View, CA, 2013).

- <sup>11</sup>M. G. Ancona and H. F. Tiersten, *Phys. Rev. B* **35**, 7959–7965 (1987).

- <sup>12</sup>D. B. M. Klaassen, Solid-State Electron. **35**, 953–959 (1992).

- <sup>13</sup>C. Canali, G. Majni, R. Minder, and G. Ottaviani, IEEE Trans. Electron Devices 22, 1045–1047 (1975).

- <sup>14</sup>C. Lombardi, S. Manzini, A. Saporito, and M. Vanzi, IEEE Trans. Comput.-Aided Des. 7, 1164–1171 (1988).

- <sup>15</sup>J.-P. Colinge, FinFETs and Other Multi-gate Transistors (Springer-Verlag, New York, NY, USA, 2008).

- <sup>16</sup>N. Sano, K. Matsuzawa, M. Mukai, and N. Nakayama, Microelectron. Reliab. 42, 189–199 (2002).

- <sup>17</sup>R.-H. Baek, C.-K. Baek, S.-W. Jung, Y. Y. Yeoh, D.-W. Kim, J.-S. Lee, D. M. Kim, and Y.-H. Jeong, IEEE Trans. Nanotechnol. 9, 212–217 (2010).

- <sup>18</sup>K. Romanjek, F. Andrieu, T. Ernst, and G. Ghibaudo, IEEE Electron Device Lett. 25, 583–585 (2004).

- <sup>19</sup>J. Franco, B. Kaczer, M. Cho, G. Eneman, G. Groeseneken, and T. Grasser, IEEE Int. Reliab. Phys. Symp. Proc. 2010, 1082–1085.

- <sup>20</sup>S. Bangsaruntip, G. M. Cohen, A. Majumdar, Y. Zhang, S. U. Engelmann, N. C. M. Fuller, L. M. Gignac, S. Mittal, J. S. Newbury, M. Guillom, T. Barwicz,

- L. Sekaric, M. M. Frank, and J. W. Sleight, Tech. Dig. Int. Electron Devices Meet. 2009, 297–300.

- <sup>21</sup>N. Neophytou, A. Paul, M. S. Lundstrom, and G. Klimeck, IEEE Trans. Electron Devices 55, 1286–1297 (2008).

- <sup>22</sup>S. Bangsaruntip, G. M. Cohen, A. Majumdar, and J. W. Sleight, IEEE Electron Device Lett. 31, 903–905 (2010).

- <sup>23</sup>Y. Wang, P. Huang, Z. Xin, L. Zeng, X. Liu, G. Du, and J. Kang, Jpn. J. Appl. Phys., Part 1 53, 04EC05 (2014).

- <sup>24</sup>M. J. M. Pelgrom, A. C. J. Duinmaijer, and A. P. G. Welbers, IEEE J. Solid-State Circuits 24, 1433–1440 (1989).

- <sup>25</sup>T. Matsukawa, Y. Liu, S. O'uchi, K. Endo, J. Tsukada, H. Yamauchi, Y. Ishikawa, H. Ota, S. Migita, Y. Morita, W. Mizubayashi, K. Sakamoto, and M. Masahara, Tech. Dig. Int. Electron Devices Meet. 2011, 517–520.

- <sup>26</sup>S.-H. Lee, C.-K. Baek, S. Park, D.-W. Kim, D. K. Sohn, J.-S. Lee, D. M. Kim, and Y.-H. Jeong, IEEE Electron Device Lett. 33, 1348–1350 (2012).

- <sup>27</sup>S. Gundapaneni, M. Bajaj, R. K. Pandey, K. V. R. M. Murali, S. Ganguly, and A. Kottantharayil, IEEE Trans. Electron Devices **59**, 1023–1029 (2012).