## Solid-phase epitaxy of amorphous Si using single-crystalline Si nanowire seed templates

Yun Sung Woo, Kibum Kang, Moon-Ho Jo, Jong-Myeoung Jeon, and Miyoung Kim

Citation: Applied Physics Letters **91**, 223107 (2007); doi: 10.1063/1.2817601 View online: http://dx.doi.org/10.1063/1.2817601 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/91/22?ver=pdfcov Published by the AIP Publishing

## Articles you may be interested in

Solid-phase epitaxy of silicon amorphized by implantation of the alkali elements rubidium and cesium AIP Conf. Proc. **1496**, 276 (2012); 10.1063/1.4766542

Solid-phase epitaxial regrowth of amorphous silicon containing helium bubbles J. Appl. Phys. **104**, 094905 (2008); 10.1063/1.3009383

Real-time optical spectroscopy study of solid-phase crystallization in hydrogenated amorphous silicon Appl. Phys. Lett. **89**, 121921 (2006); 10.1063/1.2357029

Growth mechanism for single-crystalline thin film of InGaO 3 (ZnO) 5 by reactive solid-phase epitaxy J. Appl. Phys. **95**, 5532 (2004); 10.1063/1.1712010

Nickel distribution in crystalline and amorphous silicon during solid phase epitaxy of amorphous silicon J. Appl. Phys. **84**, 6644 (1998); 10.1063/1.369039

This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP: 141.223.173.110 On: Tue, 21 Apr 2015 11:10:58

## Solid-phase epitaxy of amorphous Si using single-crystalline Si nanowire seed templates

Yun Sung Woo, Kibum Kang, and Moon-Ho Jo<sup>a)</sup> Department of Materials Science and Engineering, Pohang University of Science and Technology (POSTECH), San 31, Hyoja-Dong, Nam-Gu, Pohang, Gyungbuk 790-784, Korea

Jong-Myeoung Jeon and Miyoung Kim

Department of Materials Science and Engineering, Seoul National University, San 56-1, Sillim-Dong, Gwanak-Gu, Seoul 151-742, Korea

(Received 5 October 2007; accepted 5 November 2007; published online 27 November 2007)

We report solid-phase epitaxy of amorphous Si (*a*-Si) shells using crystalline Si (*c*-Si) nanowire cores as seed templates. The *c*-Si core/*a*-Si shell nanowire heterostructures were *in situ* synthesized via a two-step chemical vapor deposition: the Au-catalytic decomposition of SiH<sub>4</sub> for the core *c*-Si nanowires and the subsequent homogeneous decomposition of SiH<sub>4</sub> at higher temperatures for the *a*-Si shells. Upon thermal annealing above 600 °C, the *a*-Si shells crystallize into *c*-Si shells from *c*-Si core nanowires in an epitaxial fashion. We discuss the crystallization kinetics of *a*-Si shells within the frame of Gibbs-Thomson effects arising from the finite size of nanowire seeds. © 2007 *American Institute of Physics*. [DOI: 10.1063/1.2817601]

Crystallization of amorphous Si (a-Si) thin films at low temperatures has received extensive interest for their attractive applications into Si thin film transistors and Si solar cells.<sup>1-6</sup> In this regard, a number of growth processes to achieve large-grained polycrystalline Si (poly-Si) thin films have been developed including excimer laser annealing and metal-induced crystallization. Crystallization of amorphous Si using the local nucleation seeds is also an interesting scheme, because it can offer advantageous solid-phase crystallization at the controlled sites at low temperatures.<sup>7-10</sup> Relevant growth approaches, reported so far, employ various kinds of nucleation seeds followed by appropriate thermal annealing, including crystalline Si (c-Si) layers in contact to a-Si layers,<sup>7,8</sup> c-Si nanoparticles embedded in a-Si layer,<sup>9</sup> and metal nanocrystals embedded in a-Si layers.<sup>10</sup> In fact, these synthetic methods have produced large-grained poly-Si at low crystallization temperatures below 600 °C, and reported the improved mobility thin-film transistors. Nevertheless they sometimes display some drawbacks such as mechanical-stress induced damages, randomly oriented grains, and metal contaminations. Single-crystalline Si nanowires, in this respect, can serve as interesting nucleation seeds when imbedded in a-Si for its solid-phase crystallization, because their specific crystal orientations in the onedimensional structures can impose the preferred crystal orientation on the crystallizing a-Si matrices upon the subsequent solid-phase crystallization. In addition, provided that the vertical or parallel alignment of single-crystalline Si nanowires is available,<sup>11–13</sup> such ordered nanowire array can offer the promising seed templates for large-area crystallization with preferred crystal orientations. Here, we report the basic characteristics of the solid-phase crystallization of a-Si shells surrounding single-crystalline Si nanowires upon thermal annealing. Specifically, we examined the microstructural evolution and the crystallization kinetics of a-Si shells around 20 nm thick c-Si nanowire cores by extensive transmission electron microscopy study, and compared them with the cases of planar a-Si layers on Si wafers reported in literature. We found that the *a*-Si shells crystallize into *c*-Si shells in excellent epitaxial relations with single-crystalline nanowire cores upon thermal annealing. We also discuss the kinetics of crystallization of *a*-Si shells based on our observations within the frame of Gibbs-Thomson effect, arising from the finite size effects of nanowire seed templates.

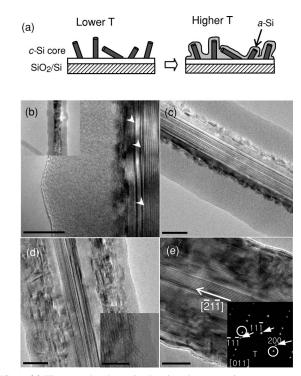

The c-Si core/a-Si shell nanowire heterostructures were in situ synthesized using a two-step chemical vapor deposition (CVD) using SiH<sub>4</sub> precursors. Figure 1(a) shows the schematics of our syntheses of the nanowire a-Si shell/c-Si core heterostuctures. First, single-crystalline Si nanowires were grown by the Au catalyst-assisted chemical vapor process.<sup>14,15</sup> Au catalysts of the nanometer scale were prepared by the dispersion of colloidal Au particles of 20 nm in diameter on SiO<sub>2</sub>/Si (100), and were subsequently loaded in a quartz tube furnace. The catalytic decomposition of SiH<sub>4</sub> onto Au catalysts occurs at 500 °C and results in the axial growth of single-crystalline Si nanowires. Subsequently, we promote the radial growth of a-Si surrounding upon the pregrown Si nanowires by the homogeneous SiH<sub>4</sub> decomposition at the elevated temperature of 550 °C. That is, the axial nanowire growth by the catalytic decomposition of  $SiH_4$  at 500 °C is kinetically facilitated over the radial growth of a-Si shell which is only activated above 550 °C. Thus, we were able to grow c-Si core/a-Si shell nanowire heterostructures by exploiting two different SiH<sub>4</sub> decomposition behaviors at each temperature regime.

We then investigated crystallization behaviors of *a*-Si shell layers by thermal annealing of the *c*-Si core/*a*-Si shell nanowire heterostructures under N<sub>2</sub> flowing at 500, 600, and 800 °C for a given period of time. High-resolution transmission electron microscopy (HRTEM) was employed to observe the epitaxial characteristics at the interfaces between *a*-Si shells and *c*-Si nanowire cores. We found that the majority of Si nanowires in this study grow in the [211] direction along the nanowire direction, and some Si nanowires also grow in the [110] direction. Figure 1(b) shows the typical TEM image of *c*-Si core/*a*-Si shell nanowire heterostructures by the two-step CVD growth, and demonstrates that the core is indeed single crystalline and the shell is amorphous.

0003-6951/2007/91(22)/223107/3/\$23.00

<sup>&</sup>lt;sup>a)</sup>Electronic mail: mhjo@postech.ac.kr.

ticle. Reuse of AIP content is subject to the terms at: http://scitatio 91, 223107-1 141.223.173.110 On: Tue, 21 Apr 2015 11:10:58

FIG. 1. (a) The growth schematic showing the successive two-step growth of *c*-Si core/*a*-Si shell nanowire heterostructures. [(b)–(e)] Representative HRTEM images of nanowire heterostructures at different annealing temperatures (the scale bar is 20 nm). (b) the as-deposited nanowires consist of amorphous Si shells surrounding crystalline Si cores. The inset shows a lower magnification image. The structural evolutions of nanowire heterostructures upon thermal annealing at (c) 500 °C for 90 min, (d) 600 °C for 30 min, and (e) 800 °C for 30 min. The scale bar of the inset of (d) is 10 nm. The diffraction pattern in the inset of (e) represents twins in the fully crystallized nanowires.

We note the presence of stacking faults parallel to the nanowire axis as marked with white arrows, and they persist after the thermal annealing, as shown in Figs. 1(c)-1(e). These stacking faults are rarely observed in catalytically grown Si nanowires,<sup>14,15</sup> and in our study, we have observed the presence of such unusual dislocations only after the a-Si shell deposition at higher temperatures. We do not understand their formation mechanism at the moment; nevertheless, we argue that the presence of these stacking faults does not affect our main conclusions on the crystallization of a-Si shells. Figures 1(c)-1(e) show the sequential crystallization behaviors of a-Si shell as the N<sub>2</sub> annealing temperature for 30 min increases from 500 to 600 and 800 °C. After annealing at 500 °C, we have not observed any noticeable structural changes, as seen in Fig. 1(c), even for the extended annealing up to 90 min. On the other hand, after annealing at 600 °C, we observed that c-Si nanowire core extended its volume outward to the surface, with the presence of only a very thin *a*-Si layer at the outermost surface, as in Fig. 1(d). Evidently, the *a*-Si shells crystallize into *c*-Si shells from the c-Si core seed templates upon annealing at above 600 °C. Upon annealing at the higher temperature of 800 °C, the crystallization of a-Si shell is completed, as shown in Fig. 1(e). Here, we emphasize that the crystallographic orientation of the crystallizing a-Si shell epitaxially templates the orientation of c-Si cores; i.e., the crystallization of a-Si shell progresses by a layer-by-layer growth fashion. Indeed, the diffraction pattern in the inset of Fig. 1(e) demonstrates that the fully crystallized nanowires at 800 °C, as a whole coreshell nanowire, are single crystalline only with few twins

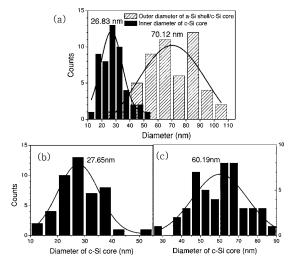

FIG. 2. Histograms of *c*-Si core diameter distributions measured from *a*-Si shell/*c*-Si core heterostructures (a) as it is deposited, (b) annealed at 500 °C for 90 min, and (c) annealed at 600 °C for 30 min. The histogram filled with declined lines in (a) shows the outer diameter distribution of *a*-Si shell/ *c*-Si core structures. The smooth curves are Gaussian fits.

present. The differences are, nevertheless, observed with HRTEM images. The crystallized shell layers contains additional structural defects such as grains, twins with {111} twin planes, and supercell structures originated from the unstable phase which are often observed in defective structures. Additional stacking faults in the shell are sometimes in the  $\langle 111 \rangle$  directions, interruption in the stacking sequence of close-packed planes, both along the growth direction and the radial direction.

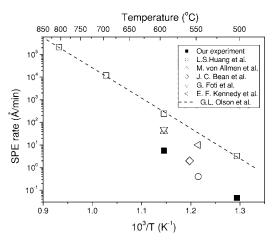

Having identified that the crystallization of a-Si shells proceeds in a layer-by-layer fashion by solid-phase epitaxy (SPE), we then investigated its kinetic characteristics by extensive TEM analyses. Due to the intrinsic diameter distribution of c-Si nanowires, we examined 50 samples at each annealing temperature by TEM and we extracted the SPE rates from the statistical distribution. Figure 2(a) is the histogram of the diameter distribution obtained from the asdeposited nanowire heterostructures, as shown in Fig. 1(b). The average diameter of c-Si nanowire core is measured to be 27 nm, which is reasonably consistent with the size of Au colloidal particles of 20 nm, and the average outer diameter of nanowire heterostructures is 70.12 nm. Figure 2(b) shows that the diameter of crystalline core remains almost the same as 27.62 nm upon annealing at 500 °C for 90 min. After annealing at 600 °C for 30 min, it increases to 60.19 nm, as shown in Fig. 1(d), followed by a complete crystallization at the 800 °C annealing. Based on the determined values above, the growth rate of a-Si layers on c-Si nanowires is calculated to be  $4.6 \times 10^{-2}$  and 5.6 Å/min at 500 and 600 °C, respectively. These values of growth rate are indicated as solid squares in an Arrhenius plot as in Fig. 3, along with the SPE rates of *a*-Si layer deposited under the various conditions on flat c-Si substrates from literature for comparison. In particular, the SPE rates of vacuum evaporated a-Si layer are indicated as dotted line in Fig. 3. We found that the value of the SPE growth rate of a-Si shells on c-Si nanowire core in our experiment is smaller by two orders of magnitudes than the case of a-Si layers on planar c-Si.

The smaller SPE growth rate of a-Si are often attributed to an effect of oxygen inevitably incorporated in a-Si. Oxygen has been known to sensitively inhibit the crystallization

FIG. 3. Temperature dependence of the SPE growth velocity in amorphous Si shell deposited on *c*-Si nanowires ( $\blacksquare$ ), compared with those of others' ( $\bigcirc$ ) evaporated amorphous Si, where the columnar epitaxial growth occurs upon annealing at 550 °C (by Huang *et al.*), ( $\triangle$ ) evaporated amorphous Si upon annealing at 600 °C (by von Allmen *et al.*), ( $\Diamond$ ) surface of amorphous Si after air exposure (by Bean and Poate), ( $\bigtriangledown$ ) amorphous Si layer containing oxygen content of  $5 \times 10^{20}$ /cm<sup>3</sup> (by Foti *et al.*), ( $\triangleleft$ ) amorphous Si layers in which oxygen with  $2.5 \times 10^{20}$ /cm<sup>3</sup> is ion implanted (by Kennedy *et al.*), and (...) amorphous Si deposited by vacuum evaporation.

of a-Si, leading to much lower SPE growth rates of a-Si layers. The presence of oxygen in high contents also causes a columnar growth if the amount of oxygen within the amorphous layer exceeds some values.<sup>1,2</sup> For instance, Huang et al. have reported that a-Si layer deposited on Si wafers which is cleaned by HF dipping followed by a H<sub>2</sub>O rinse contained about  $2 \times 10^{20}$  oxygen atoms/cm<sup>3</sup> and accordingly showed the columnar epitaxial growth.<sup>1</sup> In our two-step CVD growth, the oxygen content is presumed to be small, and its amount within a-Si shells can be estimated to be an order of  $\sim 10^{19}$ /cm<sup>3</sup> according to Ref. 16, where a similar deposition method with ours was employed.<sup>16</sup> Nevertheless, the SPE rate of nanowire heterostructures in our study displays the smallest value despite the presumed low oxygen content. Moreover, the epitaxial growth of a-Si layer surrounding Si nanowire is observed to occur in a layer-by-layer fashion but not in a columnar epitaxial growth. Thus, the lower SPE growth rate of nanowire heterostructures in our study cannot be attributed to the oxygen impurities within the a-Si shells.

The lower SPE rate in our experiments can arise from the small size of *c*-Si nanowires used as the seed templates for the crystallization of *a*-Si. According to the thermally activated growth theory,<sup>17</sup> the solid-phase growth velocity  $\nu$ is given by

$$\nu = kT/h \cdot \delta \exp(-E_a/kT) [1 - \exp(-\Delta g_{ca}/kT)],$$

$$\approx \Delta g_{ca}/h \cdot \delta \exp(-E_a/kT) \quad \text{when } \Delta g_{ca} < kT, \qquad (1)$$

where  $\delta$  is the distance across the interface of crystalline and amorphous phases,  $E_a$  is the activation energy for the crystallization, and  $\Delta g_{ca}$  is the free energy difference between crystalline and amorphous phases. Here,  $E_a$  is usually interpreted as the energy involved in bond breaking or bond arrangement responsible for SPE growth, and it can be obtained from the slope of the plot in Fig. 3. When looking into our results in Fig. 3, although the numbers of data are not sufficient to fit a linear line, the activation energy seems to be measured by Olson and Roth.<sup>6</sup> Equation (1) also indicates that the SPE growth velocity is proportional to the free energy difference between the crystalline and amorphous phase  $\Delta g_{ca}$ . According to Gibbs-Thomson effects,<sup>18</sup> the free energy of nanosized particle of phase  $\alpha$  faced with phase  $\beta$  is raised by an amount of  $2\gamma V_m/r$ , where  $\gamma$  is  $\alpha/\beta$  the interfacial energy,  $V_m$  is the molar volume of  $\beta$ , and the *r* is the radius of the nanosized particle. We argue that this size effect can be applied to our study where the *c*-Si nanowire core possesses the diameter of 20 nm, leading to a larger free energy than that of a flat Si substrate. As a result, the free energy difference between the crystalline and amorphous phase  $\Delta g_{ca}$ becomes smaller when *c*-Si nanowires are employed as the seed templates for the crystallization of *a*-Si, and the SPE growth velocity is decelerated according to Eq. (1).

In summary, we investigated the SPE growth behavior of a-Si layers when c-Si nanowires are employed as the seed templates. It was found that the a-Si shells crystallize from the interface between the a-Si shell and c-Si core in a layerby-layer epitaxy by thermal annealing at the relatively low temperatures. The measured SPE growth rate is lower compared with that of amorphous Si layers on flat Si substrates, and we attributed this to the size effects arising from the nanosized diameters of the template c-Si nanowires. Based on our observations, we suggest that the array of Si nanowires can be a promising seed template for the SPE to achieve a highly textured poly-Si thin film by imposing a preferred orientation of c-Si nanowires upon the crystallizing a-Si layers.

This work was supported by the "System IC 2010" project of the Korea Ministry of Commerce, Industry and Energy, Nano R&D program through the Korea Science and Engineering Foundation (2007-02864), the Korea Foundation for International Cooperation of Science & Technology (KICOS) through a grant provided by the Korean Ministry of Science & Technology (MOST) in 2007 (K20716000006-07A0400-00610), the Korean Research Foundation Grant MOEHRD (KRF-2005-005-J13103), and POSTECH Core Research Program.

- <sup>1</sup>L. S. Huang, S. S. Lau, M. von Allmen, J. W. Mayer, B. M. Ullrich, J. E.

- Baker, P. Williams, and W. F. Tseng, Appl. Phys. Lett. **37**, 909 (1980). <sup>2</sup>M. von Allmen, S. S. Lau, J. W. Mayer, and W. F. Tseng, Appl. Phys. Lett. **35**, 280 (1979).

- <sup>3</sup>J. C. Bean and J. M. Poate, Appl. Phys. Lett. **36**, 59 (1980).

- <sup>4</sup>G. Foti, J. C. Bean, J. M. Poate, and C. W. Magee, Appl. Phys. Lett. **36**, 840 (1980).

- <sup>5</sup>E. F. Kennedy, L. Csepregi, J. S. Mayer, and T. W. Sigmon, J. Appl. Phys. **48**, 4241 (1977).

- <sup>6</sup>G. L. Olson and J. A. Roth, Mater. Sci. Rep. 3, 1 (1988).

- <sup>7</sup>A. Doi, M. Kumikawa, J. Konishi, and Y. Nakamizo, Appl. Phys. Lett. **59**, 2518 (1991).

- <sup>8</sup>R. K. Singh, S. M. Jung, S. M. Lee, and R. E. Hummel, J. Electrochem. Soc. **145**, 3963 (1998).

- <sup>9</sup>A. T. Voutsas and M. K. Hatalis, Appl. Phys. Lett. 63, 1546 (1993).

- <sup>10</sup>B. Rau, I. Sieber, J. Schneider, M. Muske, M. S. Pollach, P. Schattschneider, S. Gall, and S. Fuchs, J. Cryst. Growth **270**, 396 (2004).

- <sup>11</sup>A. I. Hochbaum, R. Fan, R. He, and P. Yang, Nano Lett. **5**, 457 (2005).

- <sup>12</sup>Y. Huang, X. Duan, Q. Wei, and C. M. Lieber, Science **291**, 630 (2001).

- <sup>13</sup>D. Whang, S. Jin, Y. Wu, and C. M. Lieber, Nano Lett. **3**, 1255 (2003).

- <sup>14</sup>Chang-Beom Jin, Jee-Eun Yang, and Moon-Ho Jo, Appl. Phys. Lett. **88**, 193105 (2006).

- <sup>15</sup>Jee-Eun Yang, Chang-Beom Jin, Cheol-Joo Kim, and Moon-Ho Jo, Nano Lett. 6, 2679 (2006).

- <sup>16</sup>J. Nakata, J. Appl. Phys. **82**, 5446 (1997).

- <sup>17</sup>J. W. Christian, The Theory of Transformations in Metals and Alloys, Part

- 1, 3rd ed. (Elsevier Science, Oxford, 2002), Version 1, Chap. 11, p. 482

- <sup>18</sup>E. I. Givargizov, J. Cryst. Growth **31**, 20 (1975).