#### Universidad Politécnica de Madrid

Escuela Técnica Superior de Ingenieros Industriales

Departamento de Automática, Ingeniería Electrónica e Informática Industrial

#### Master on Industrial Electronics

### FPGA-Based Wireless Sensor Node Architecture for High Performance Applications

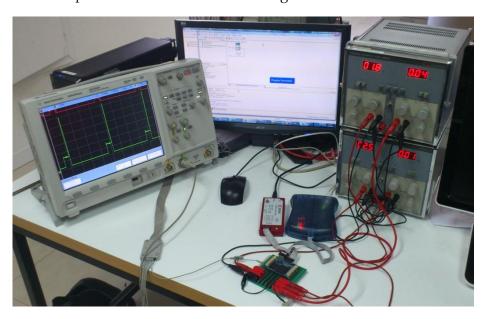

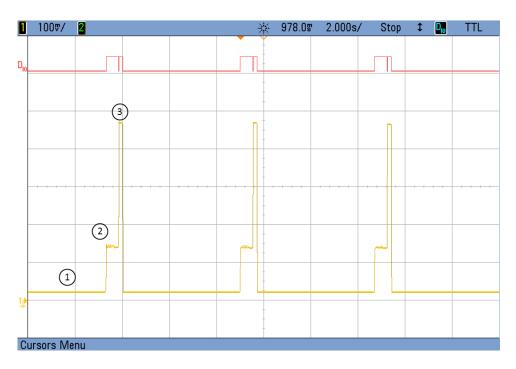

Author: Juan Valverde Alcalá

Directors: Jorge Portilla Berrueco Eduardo de la Torre Arnanz

**April 2012**

**Master Thesis**

## Index

| 1. | Int  | roduc                | etion                                                                                              | 3        |

|----|------|----------------------|----------------------------------------------------------------------------------------------------|----------|

|    | I.   | Wire                 | less Sensor Networks                                                                               | 3        |

|    | II.  |                      | oduction to Wireless Sensor Networks for High Performance                                          | <i>6</i> |

|    | III. | Moti                 | vation and Main Goals                                                                              | 7        |

|    | IV.  | Doc                  | ument Structure                                                                                    | 8        |

| 2. | Ger  | neral                | Concepts and State of Knowledge                                                                    | 13       |

|    | I.   | Cool                 | xie Platform                                                                                       | 13       |

|    | II.  | High                 | Performance Wireless Sensor Networks                                                               | 16       |

|    | III. | Harc                 | lware Reconfiguration: General Concepts                                                            | 20       |

|    | IV.  | Орр                  | ortunities of Reconfigurable Hardware in WSNs                                                      | 24       |

| 3. | Hig  | gh-Pe                | rformance Node Architecture                                                                        | 29       |

|    | I.   | Desi                 | gn Requirements                                                                                    | 29       |

|    | II.  | Syste                | em Specifications and Architecture                                                                 | 30       |

|    |      | II.1<br>II.2<br>II.3 | Node Architecture                                                                                  | 32       |

|    | III. | PCB                  | Design                                                                                             | 63       |

| 4. | Enc  | ergy S               | Saving Methodologies                                                                               | 69       |

| 5. | Pla  | tform                | Tests                                                                                              | 83       |

|    | I.   | Scen                 | arios & Applications Examples                                                                      | 83       |

|    |      | I.1<br>I.2           | Example 1: Surveillance in Restricted Military Areas<br>Example 2: Data Logging and Authentication |          |

|    | II.  | Valid                | lation Tests                                                                                       | 89       |

|    |          | Hardware ValidationApplication Tests and Power Measurements |     |

|----|----------|-------------------------------------------------------------|-----|

| 6. |          | ons & Future Work                                           |     |

| Re | ferences |                                                             | 111 |

# Chapter 1 INTRODUCTION

"Without craftsmanship, inspiration is a mere reed shaken in the wind" Johannes Brahms

#### 1. Introduction

During the last decade, Wireless Sensor Networks (WSNs) have been evolving towards more advanced applications using the latest technology breakthroughs. This evolution leads to an important increase of the resources required to cover the needs of these new scenarios. Even though the use of hardware-based solutions had been avoided by the majority of WSN designers, new approaches are being opened to this kind of devices due to their much higher powerful processing capabilities. In this Master Thesis, a novel hardware-based wireless sensor node architecture with specific energy saving methodologies is presented. This research work covers all the design steps beginning with the study of high performance WSN requirements, following with the design and development of a new node architecture and final prototype, and finishing with validation tests in order to illustrate the feasibility of the platform in terms of power consumption, size and performance.

#### I. Wireless Sensor Networks

Human endeavor for the understanding and control of the environment has led to the development of smart monitoring systems known as Wireless Sensor Networks (WSNs). These systems have been evolving during the last decade into more efficient and adaptable solutions to face a wide range of different scenarios [Buratti'09].

WSNs open a new way to understand the environment through the use of distributed intelligence. These networks consist of a group of electronic devices, called nodes or motes, deployed in different environments with the main goal of collecting information in a non-intrusive and unattended way. Depending on the tasks carried out by every one of these nodes, they must include different capabilities. Regarding their functionality, wireless sensor nodes are normally divided into three different groups:

- Sensor nodes: They must be capable of collecting information from the environment as well as processing this information to send it to other devices.

- Router nodes: They act as bridges in order to send the information through the wireless network via radio links.

- Sink nodes: They are in charge of collecting all the information from other nodes in order to share it with a computer or with another network.

These functions may change depending on each application. Besides, in some cases, a node can include some of these capabilities at the same time. For instance, a router node can work as a sensor node or, if the network is separated in different clusters, a sink node of one of these clusters can also work as a router.

Power consumption is one of the main concerns when dealing with this kind of systems since they must be both stand-alone and wireless. This fact implies a very important handicap in terms of power requirements. The use of low power processors together with power management strategies allows these systems to be powered by batteries that can last over a year depending on the applications and the platforms used. These power management strategies combined with high performance capabilities are one of the main contributions of this Master Thesis.

Even though the survey of standard WSN applications is out of the scope of this work, in order to understand their possibilities, some examples are listed. In the state of the art, it is possible to find quite a few different applications and scenarios where WSNs are being used. In [Corke'10], environmental and agricultural solutions are shown. Applications like cattle and water quality monitoring, virtual fencing, etc. take advantage of the use of these networks for continuous monitoring in a non-intrusive way. As well as in the previous case, the possibility of monitoring environmental parameters, but in food factories, is also detailed in [Valverde'11\_1].

Another important contribution of WSNs is the capability of including intelligent energy management systems, [Nguyen'10]. In a world where energy efficiency has become one of the main concerns, the possibility of being aware of the power consumption in buildings, offices or factories and therefore being capable of acting

Chapter 1 Introduction

on them, opens a wide umbrella of power management opportunities. Those are some of the most popular applications related to WSNs. Apart from them, these networks are being used for health monitoring in humans [Yung-Cheng'09], structure monitoring for buildings and bridges [Xiao'11], fire detection in forests [Shixing'10], and myriad others.

As it happens with the applications, there are quite a few different WSN platforms in the state of the art. In Table 1, some of them are listed and compared (see: [Culler'05], [Nachman'05], [Smith'07], [Libelium'09], [Benbasat'05], [Limberopoulos'07], [Yamashita'06], [Portilla'06]). The table shows which processors and communication protocols are being used on every sensor platform.

| Platform                 | Marketed | N° of<br>Layers    | Processing                                                           | Communications                |

|--------------------------|----------|--------------------|----------------------------------------------------------------------|-------------------------------|

| TelosB (Berkley)         | YES      | 2                  | MSP430F1611<br>16 bit                                                | CC2420<br>IEEE 802.15.4       |

| Intel iMote              | YES      | 2                  | XScale<br>PXA271 32 bit                                              | CC2420<br>IEEE 802.15.4       |

| Sun SPOT                 | YES      | 2                  | ARM920T<br>32 bit                                                    | CC2420<br>IEEE 802.15.4       |

| Wasp mote (Libelium)     | YES      | 3                  | ATMega1281<br>8bit                                                   | XBee module, ZigBee compliant |

| MIT Platform             | NO       | 4                  | C8051F206<br>8 bit                                                   | TDMA protocol                 |

| mPlatform<br>(Microsoft) | NO       | Not specified (>4) | 2 processors<br>in each layer<br>and 1 CPLD<br>XC2C512<br>CoolRunner | CC2420<br>IEEE 802.15.4       |

Table 1: WSN Platform Comparison.

In [Charoenpanyasak'11], a complete survey on WSNs nodes is done including both architectures for standard applications and a new generation of nodes to face more demanding tasks. In Figure 1, every one of these platforms is shown.

Figure 1: WSN Platforms. From left to right in the upper row: TelosB, Intel Mote, BTnode, mPlatform and on the lower row: Hitachi ZN1, MIT node, SunSpot, WaspMote.

In this Master Thesis, an adaptation of the *Cookie* WSN [Portilla'06] platform adding a high end FPGA to face very demanding computing requirements is presented. The main features of this architecture will be shown in chapter 2 in order to introduce the platform for future changes.

### II. Introduction to Wireless Sensor Networks for High Performance Applications

WSNs are typically conceived as all-purpose designs used to cover a wide variety of applications. However, the requirements in some of these applications in terms of security, speed or energy efficiency are being increased while new demanding scenarios have turned up. In order to cope with this situation, new approaches must be taking into consideration.

Typically, WSN nodes have had some data processing capabilities, but since power consumption is always a crucial matter, the processors used are very limited. Accordingly, the availability of processing within the node also has a big limitation in terms of amount of data and speed of processing. These low profile processors offer enough processing capabilities to face standard applications while they keep ultra-low power consumption. The MSP430 microcontroller from Texas Instruments included in the TelosB platform [Culler'05] from the University of California at

Berkeley or the ATmega1281 used by Libelium in the Waspmote [Libelium'09], are some of these examples.

Apart from standard applications, new demands have appeared recently regarding two main aspects: first, more demanding scenarios are being introduced in the WSN field, and second, the requirements for traditional applications are increasing. In this context, traditional platforms reach a limitation so new solutions must be considered keeping in mind both low power consumption and the size constraints inherent to WSNs.

Normally, standard WSN applications share some common features such as low data rates, non-restrictive latency and low number of nodes (< 100 nodes) among others. However, only by increasing the area to be covered, the requirements can change sharply. For instance, in a deployment with a huge number of nodes, the amount of raw data can be too high to be processed by a low profile controller. As an example, 200 Kbits/s is a high data rate for a wireless sensor node. At the same time, synchronization and latency can also become a big problem so much more powerful processors are required.

Apart from the increasing demands in traditional applications, new ones have shown up related to surveillance, communication security, tracking algorithms, etc. All of these applications require much more powerful processing units to deal with huge amounts of data and complex calculations. Those high performance applications are normally related to the use of video cameras, data encryption and compression, audio applications, large deployments, tracking algorithms, latency restrictions and synchronization, big memory usage, etc. That is the reason why new WSN architectures must be studied to be able to face these new complex operations.

#### III. Motivation and Main Goals

The motivation to carry out this research work is the study of high performance WSNs in order to demonstrate the convenience of using hardware-based architectures instead of the traditional microcontroller-based ones. This Master Thesis shows the design and validation of a relatively high capacity state-of-the-art

FPGA-based platform together with the implementation of energy saving methodologies.

The main goals of this Master Thesis are listed below:

- Study and understand the needs of the new high performance applications for WSNs.

- Summarize all the requirements imposed by this kind of applications and translate them into real specifications.

- Adapt the *Cookie* WSN platform to comply with these specifications developing a new processing and power supply units.

- Build a final prototype to be used by the different partners of two European projects.

- Validate the design with real tests under real scenarios.

- Guarantee enough features to:

- Carry out complex algorithms in a fast way keeping energy efficiency.

- Have enough available memory to collect and work with application data.

- o Be capable of carrying out dynamic and partial reconfiguration.

- Implement low power strategies to reduce power consumption as much as possible.

#### IV. Document Structure

This Master Thesis is organized as follows: chapter 2 is divided into three different subsections. The first one gives an overview about the Cookies Wireless Sensor Network platform. The second section describes the main requirements imposed by high performance applications, while the last one is focused on hardware reconfiguration.

Chapter 3 includes all the system requirements and specifications, details about the platform architecture and some interesting data about the real PCBs design.

In chapter 4, different methodologies to achieve the maximum energy efficiency are explained together with the different power save modes included in the design.

Chapter 5 explains two possible application scenarios where the performance of the platform proposed is shown. In addition to this, this chapter includes all the different steps needed to validate the hardware design as well as several tests to demonstrate the feasibility of the solution in terms of power of processing and energy efficiency compared to other solutions. To conclude, in chapter 6, some future lines and conclusions are discussed.

## Chapter 2

## GENERAL CONCEPTS AND STATE OF KNOWLEDGE

"Cuando creíamos que teníamos todas las respuestas, de pronto, cambiaron todas las preguntas"

Mario Benedetti

#### 2. General Concepts and State of Knowledge

General concepts about WSNs were already discussed in the Introduction chapter. This second section is focused on describing the platform developed at the Technical University of Madrid (Universidad Politécnica de Madrid) within the Center of Industrial Electronics (CEI) as well as on going a bit deeper into the needs of high performance applications for WSNs.

#### I. Cookie Platform

The first step for the correct understanding of this Master Thesis, once WSNs have been introduced, is the explanation of the basic features of the WSN platform that is going to be adapted. This is the *Cookie* WSN platform [Portilla'06].

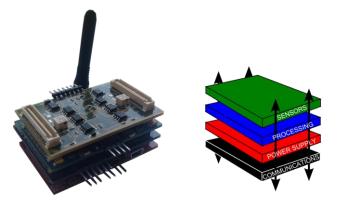

As a general matter, WSN nodes include at least four functionalities: processing, communication, sensing and/or acting and power supply. In order to have a flexible design, the *Cookie* platform is divided into four different PCB layers, each one of them covering one of these previous roles.

Every layer is connected to the following through vertical connectors. These connectors have two main goals: acting as a joint point between layers and connecting all the signals from one layer to the other. In this way, it is possible to exchange every layer separately if different sensors, communication modules, power supply sources, etc. are needed. This modularity is the main feature of this platform and it is very useful when adapting it to comply with different requirements and scenarios. The four layers mentioned are listed below:

Sensing layer: it includes conditioning circuits for both digital and analog sensors. The output signals of these conditioning circuits go through the vertical connectors to the processing layer. All the different models are detailed in the next page.

- Power supply layer: it is the power source of the node. The node can be powered from an USB cable, lithium or AA batteries or directly from the mains, if it is necessary.

- Communication layer: it includes the radio module to communicate data between nodes. It can be either a ZigBee or a Bluetooth module. In the case of the ZigBee module, different frequencies are available (2.4 GHZ and 868 MHz).

- Processing layer: it is the brain of the platform. It is the layer in charge of

processing all the information given by the sensors and the radio module. It

includes an FPGA and a microcontroller that changes depending on each

version. This Master Thesis is focused on the design of a new processing

layer.

This architecture divided in layers can be seen in Figure 2.

Figure 2: Cookies Architecture.

Even though every layer can be placed in any position, it is better for the communication one to be located in the external part of the node in order to avoid the noise from the rest of the layers. At the same time, it is important to have the sensing layer on the opposite side, since sensors and/or actuators usually need to be in contact with the environment. It is important to highlight that the position of the layers on the new adapted design will not be arbitrary but this will be explained in the following sections.

Depending on the tasks the node needs to carry out, it will include all the layers or only some of them. For instance, a node working only as a router will include the power supply layer and the communication module since only very simple processing tasks are required.

Thanks to its modularity, several versions of each layer have been already designed.

- Sensing layer:

- Water temperature and pH.

- o Gas concentration: O<sub>2</sub>, CO, NO<sub>2</sub>, SO<sub>2</sub>, CO<sub>2</sub>.

- o Air temperature, accelometer and light.

- o Strain gauge and air temperature.

- o Video camera.

- Communication layer:

- o ZigBee 2.4 GHz Telegesis module.

- o ZigBee 900 and 868 MHz Atmel module.

- o Bluetooth.

- Power supply layer:

- o USB, Lithium battery, AA batteries.

- USB, Lithium battery, TRACOPOWER. This version is capable of giving more current and it can be directly powered from de mains.

- Processing layer:

- o Spartan 3 FPGA and ADuC841.

- o Actel Igloo and MSP430 μC.

Since this Master Thesis main contribution is the design of a new processing layer, more details about the previous ones is needed. The first version of the processing layer included a low-cost and low-performance Spartan 3 FPGA together with a microprocessor (ADuC841). In this version, the FPGA was in charge of interfacing with different sensors and carrying out preprocessing tasks. In turn, the microprocessor executed the main node management functions. Despite of including an FPGA, the processing capabilities of the node were limited. In this Master Thesis its capabilities are extended while implementing more efficient energy management policies. Some reconfigurable capabilities were already included in this previous version of the processing layer, however, in the case of the Spartan 3, since the

processing board was not designed for reconfigurable purposes, reconfiguration needed to be done using the external microcontroller as a virtual JTAG port [Krasteva'11]. This feature is also enhanced in the new processing layer presented in this Master Thesis.

The *Cookie* platform has been already used in real scenarios such as tunnels, food factories, railways, food transport, mines or structure monitoring as part of other research projects. In all of those cases, the processing needs were mostly related to do some basic calculations and communication management in deployments with low number of nodes. The new design proposed in this work is not oriented to this kind of applications but for very demanding scenarios such as multimedia applications.

#### II. High Performance Wireless Sensor Networks

The evolution of WSNs towards more complex applications was already introduced in the first chapter. Standard applications are being improved in terms of latency, security or deployment size, while new application scenarios have turned up. The complexity imposed by these new requirements shows the limitation of the previous WSN platforms in terms of processing capabilities. In this context is where high performance platforms emerge as an enabling technology for WSNs.

These high performance applications are usually related to the use of complex algorithms such as video compression, data encryption, tracking algorithms, etc. The majority of them are multimedia applications that include the use of low-power video cameras and microphones. These applications are known in the state of the art as Wireless Multimedia Sensor Networks (WMSN). In [Harjito'11] and [Akyildiz'11], surveys about these applications are detailed. According to [Akyildiz'11], these applications can be classified in: surveillance, traffic monitoring and enforcement, personal and health care, gaming and environmental and industrial. Surveillance is probably the best example of the increase of complexity in traditional WSN applications. Traditionally, surveillance based on WSNs was limited to intruder detection or movement in target areas. Nevertheless, adding enhanced capabilities, like the use of cameras or node synchronization, permits the inclusion of advanced features such as location tracking or people identification, as seen in [He'06] [Tseng'06], [Wu'11] and [Kulkarni'06]. The use of these capabilities can also make a

breakthrough in terms of human health-monitoring applications. Applications related to telemedicine and complete patient monitoring can be achieved. For instance, in [Dilmaghani'11] a complete ECC monitoring scheme is shown. Regarding the same topic, the non-intrusive study of people behavior, mainly elder people suffering dementia, has been reported in the state of the art in [Avvenuti'09] and [Marzencki'09].

Applications related to environmental care and industrial monitoring can be also faced and improved by means of using these high performance networks. For instance, full manufacturing processes including quality control can be monitored relying on artificial vision techniques.

A good example of a new application field is Gaming, where 3D environmental virtualization gives the opportunity of introducing future approaches in videogames as seen in [Nedelcu'10] and [Chen'08].

Not only the inclusion of new sensors but also the toughening of traditional constraints such as maximum latency, bandwidth, the increase in the number of nodes or security requirements, causes architectural changes in WSN platforms. In [Grieco'09] and [Yong'06], a survey about this kind of applications is studied including encryption algorithms ([Stelte'06] [Portilla'10\_1]) which at the beginning where considered unfeasible to be carried out by WSNs. As an example of complex data calculations, in [Cantoni'06], the authors face data-mining for WSNs while in [Rup'09] distributed multimedia source coding is addressed.

Traditional architectures have been based on ultra-low power microcontrollers with enough but limited computing power. However, the increase of complexity requires higher resources to cope with these new applications. This extra computing power can be achieved by means of either using more powerful microcontrollers or any other solution capable of accelerating task execution. Normally the increase of the node capabilities implies an increment of the energy consumption so that new energy saving policies must be taken into consideration.

The first solution could be the inclusion of more powerful microcontrollers, [Hammel'07]. This solution can be suitable for some applications, since they offer a good trade-off between price, size and programming flexibility. However, when

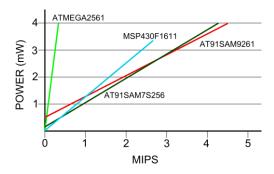

facing very intensive tasks, the computing time can be very high leading to a non-efficient solution in terms of energy consumption. A better solution can be achieved using Digital Signal Processors (DSPs), however, even though the computing time can be reduced compared to standard microcontrollers, it is still high so it is difficult to keep power consumption in acceptable levels for WSN standards. In Figure 3, a comparison between some microcontrollers in terms of power processing and power consumption is shown.

Figure 3: Power Consumption and Processing Capabilities.

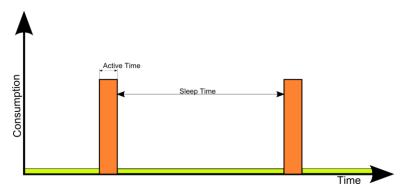

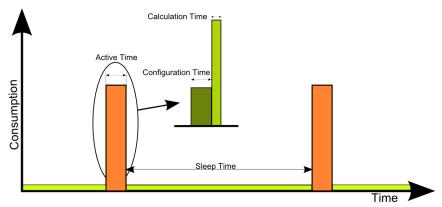

On the other hand, better solutions can be achieved taking advantage of the specific features of WSN applications. The standard working profile of a WSN has a very low duty cycle (1% - 10%). Every node is awake only during the time concerning for carrying out measurements and doing some operations ([Dutta'05] [Pinto'10]). Then, the node is taken to a power-down or sleep mode where power consumption should be close to zero. Due to this reason, very quick processing engines are very suitable for these working profiles leading to very efficient solutions in terms of energy consumption by reducing processing time.

The best way to provide high processing speed is the use of hardware based systems. FPGAs and ASICs share the capability of doing tasks in parallel. This fact can decrease the computing time sharply so the node can remain in sleep mode for longer periods of time. However, the use of ASICs in WSNs is not always suitable due to the lack of flexibility and the huge design time. Due to these reasons, FPGAs are presented as a very suitable solution for high performance WSN applications.

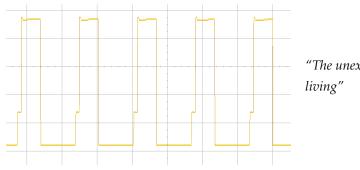

In order to illustrate the convenience of using high-speed processing engines as a suitable method to save energy while being capable of performing very complex tasks, a theoretical comparison of the working profile between an FPGA and a microcontroller in a WSN application is shown in Figure 4.

Figure 4: Consumption Profile Comparison.

While the time needed by the FPGA to carry out a certain complex task is usually very short, the time needed by a pure software-based solution is much longer. In this way, even though current consumption is much higher in the case of the FPGA, the energy is smaller due to the very short computing time. The main drawback is the fact that the FPGA configuration time is significant compared to the computing time. One of the main contributions of this work is proving that both configuration and processing times are still lower than the time the microcontroller requires to carry out the same task so very powerful energy saving methods can be implemented. It is important to highlight that this assertion is only true when dealing with complex algorithms where the computing time needed for the microcontroller is bigger than the configuration time the FPGA needs. Furthermore, the use of some FPGAs allows Partial and Dynamic Reconfiguration (DPR) which has many advantages when working with wireless sensor nodes as it will be discussed on the following section. In order to illustrate how fast hardware-based systems can be compared to software ones, in [Braun'09] a car-to-car communication system is proposed. In this kind of deployments, the reliability of communication is crucial, so both high security algorithms and low latency are required. In this work, the authors show an encryption algorithm based on elliptic curves running both in an ARM processor and a hardware-based system. Results show that for a short signature made of 160 bits, the encryption can take more than 90 ms in a 32-bit ARM processor or even more than 600 ms in a 16-bits M16C while the hardware-based solution, using 75 kgates, only takes 0.5 ms per signature verification.

It is important to highlight that it is not the aim of this work to be compared with ultra-low power WSN platforms since the application scope is completely different. This way, a trade-off between low energy consumption and high computing performance must be found.

Once the convenience of using FPGAs for high performance WSN applications has been introduced, a study of similar solutions in the state of the art is shown.

Using FPGAs in wireless sensor nodes to deal with high demanding scenarios is not a novel approach on the state of the art. In [Ji-gang'09], for instance, the authors introduce a Spartan 3E prototype board as a coprocessor attached to an external ZigBee transceiver for the implementation of a hyper-chaos encryption engine. Similar applications using off-the-shelf FPGA boards are shown in [Chalivendra'08] [Muralidhar'08] [Yan'11] and [Chao Hu'09], this last one oriented to visual sensors. These previous approaches prove that including hardware-based devices in WSNs offer certain benefits in terms of flexibility and performance. However, in spite of being valid for proof of concept, existing solutions are far from showing real WSN new architectures, leaving behind important aspects such as power consumption, power management, sensor integration, or even the inclusion of the FPGA itself on the node architecture. On the contrary, the development of a complete FPGA based node is provided in [Bellis'05], including a low-performance Spartan 2E. The complete node including the communication circuitry is integrated in a 25 mm × 25 mm board.

#### III. Hardware Reconfiguration: General Concepts

Reconfigurable hardware is presented as a feasible solution to reduce power consumption. In order to introduce the concept of reconfigurable hardware; first of all, it is sensible to make a brief review of those components that allow the implementation of this feature.

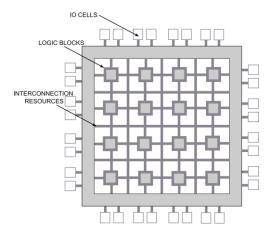

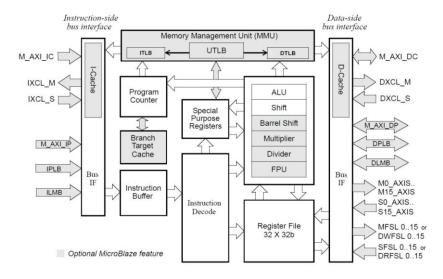

In 1984, the co-founders of Xilinx, Ross Freeman and Bernard Vonderschmitt, invented the Field Programmable Gate Array (FPGA) as an evolution of the Complex Programmable Logic Devices (CPLDs). An FPGA is an integrated circuit capable of the implementation of any logical function as a combination of several logic cells.

The most important elements in an FPGA are the Configurable Logic Blocks (CLBs), which are made of Look up Tables (LUTs) and interconnection matrixes to connect the inputs and outputs of each CLB. Apart from that, there are several Input/output elements to connect the internal logic with the external parts of the FPGA. This internal architecture can be seen in Figure 5.

Figure 5: FPGA Architecture.

These features make FPGAs to be the most efficient way for digital circuit design in terms of implementation time and price when talking about low volumes. Therefore, they have become the best alternative to Application Specific Integrated Circuits (ASICs), even though ASICs usually have lower power consumption and sometimes can implement more complex custom-made designs. In this way, due to its flexibility and low price, FPGAs are used to test prototypes for ASIC design. It is important to take into account that the new generation of FPGAs are becoming more complex and are now the most suitable elements for digital signal processing. Besides, they can have embedded microprocessors to increase, even more, flexibility, making easy-to-use designs.

In order to understand how these devices work, it is crucial to talk about the configuration memory. The configuration memory can be seen as a parallel layer to the digital circuitry of the FPGA. This layer is the one in charge of defining the logic configuration of the circuitry, so it is where the designer must define what the circuit must do.

Once the architecture and behavior of FPGAs have been briefly explained, it is possible to talk about what hardware reconfiguration is. Hardware reconfiguration is the possibility of changing the functionality of an FPGA to reach the requirements of almost any hardware application. This reconfiguration can be done in a few different ways.

As it was explained before, the reconfiguration of an FPGA means writing in the configuration memory which is in charge of changing the functionality of the logic circuit. There are three main methods to carry out this task:

#### 1) Full and Static Reconfiguration

It consists of changing the configuration of the whole area of the FPGA when the device is not working. This change is usually done by an external connection, normally the JTAG port (Join Test Action Group).

#### 2) Partial and Static Reconfiguration

In this case, only a specific region of the FPGA is configured while the device is not working. In this way the configuration time can be sharply decreased as well as the power consumption. One of the main drawbacks in this method is the necessity of having advanced knowledge about the FPGA internal architecture.

#### 3) Partial and Dynamic Reconfiguration

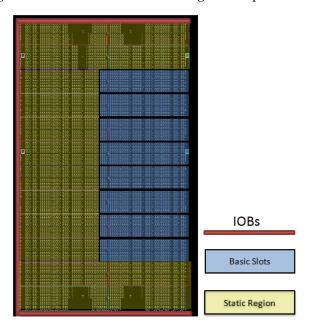

This is the most complex and the most interesting method. This option consists of changing the functionality of only certain region of the FPGA while the rest of the device is working. Normally, the internal area of the FPGA is divided into two different regions: static and reconfigurable area. The second one is in charge of allocating the changeable blocks while the first region is used for the embedded processor and peripheral controllers.

There are two main advantages when working with this reconfiguration method. The first one is the adaptation of the functionality of the FPGA in real time, and the second, is the possibility of multiplexing different tasks in time. In this way, the functionality can be changed at run time depending on different external parameters. This is translated in a huge increase of the efficiency of the system. Besides, task multiplexing allows the change of modules that have finished their tasks, replacing them for new ones with different functionalities.

On the contrary, the need of having a huge knowledge about the internal architecture of the device and the large design time, are the main drawbacks of this reconfiguration method. Besides, another aspect to take into consideration is the difficulty of porting the designs from one FPGA family to another, since everything depends on the internal architecture of the device.

Another important advantage offered by this reconfiguration method is Self-Reconfiguration. This is the possibility of changing the functionality without using any other device but the FPGA and, of course, some external memories to keep the configuration files. In this way, the system can be recovered if any problem occurs without any external help.

It is important to take into account that not all the FPGAs can be partially reconfigured. The different types of FPGAs that can be found in the market are listed below:

- RAM-based FPGAs: if the system is designed to be stand-alone, they need to have a non-volatile component to store the configuration file (bitstream hereafter), since once the FPGA is turned off, the information in the configuration memory is erased. They are quite power consuming especially considering the start-up time. Nevertheless, they are usually bigger, more evolved and they allow partial and dynamic reconfiguration.

- FLASH-based FPGAs: the power consumption in this case is lower taking into

account that they are lived-at-powered-up, so no configuration is needed when

the device is powered. The main drawback of this kind of FPGAs is that they

cannot be reconfigured either partially or dynamically.

- Hybrid technologies: they are a mixture between the previous ones.

Now that the main features of both FPGA types and reconfiguration have been explained, the opportunities of partial and dynamic reconfiguration to face high demanding WSN applications can be studied.

#### IV. Opportunities of Reconfigurable Hardware in WSNs

The capability of carrying out hardware reconfiguration, partially and at run time, opens a wide variety of new opportunities for WSNs. The possibility of loading different hardware modules depending on the changeable needs of the network is a perfect feature for the optimization of task scheduling and power saving methodologies. Carrying out tasks in parallel and having the possibility of multiplexing them allow very fast processing engines that are very powerful for certain applications such as multimedia WSNs. Moreover, partial and dynamic reconfiguration allows the implementation of energy saving policies such as fast reconfiguration to decrease the time the FPGA is working, start-up sequences [Hübner'10] to make the initial configuration using only the modules that are strictly needed, etc. It is important to notice that, in WSN scenarios, this adaptation can be done both before and after the deployment. In this way the network can be easily adapted to new standards, new environmental conditions, or to the implementation of fault tolerance algorithms.

Partial configuration implies having smaller configuration files. In this way, it is easier and less power consuming for the system to send bitstream files through the wireless network via radio, while at the same time, loading these partial files is less consuming in terms of energy and storage size.

FPGAs have the possibility of being self-configurable; this means that they may include mechanisms to read the bitstream files from external memories automatically once they are powered. This feature allows the nodes to be autonomous which is crucial when talking about WSN deployments where most of the times the devices are switched off.

Hardware reconfiguration within wireless sensor nodes has been already faced in several applications on the state of the art. In [Glesner'11], a node that includes a Flash-based FPGA is used. Even though partial and dynamic reconfiguration is not possible with these devices, the authors overcome the reconfiguration problems by creating a virtual layer on the top of the logic one to enable different hardware blocks depending on the needs of the system. Even though the hardware blocks are always

implemented, they are not working unless the virtual layer enables them. In this case, dynamic reconfiguration is emulated.

A few applications including real reconfiguration have been already proposed. In [Nahapetian'07], the MicrelEye platform is presented. This platform uses an FPSLIC, a configurable device that includes a small FPGA (40 kgates) plus an ATMEL microcontroller. This device shares hardware flexibility and speed with the advantages of a microcontroller, when at the same time power consumption is smaller than in standard FPGAs. The main drawback of this kind of systems is that due to a smaller size than standard FPGAs, it is necessary to do a very precise task scheduling. In [Garcia'09], a Virtex 4 FPGA is used to implement a dynamically reconfigurable sensor node. In this work a Kalman filter is used to remove noise during data acquisition in a moving object tracking application. However, details about the node architecture or dynamic and partial reconfiguration impact on power management or start-up time are not included in the work. In the same way, the original *Cookie* platform was featured with dynamic and partial reconfiguration, using an external processor, as shown in [Krasteva'11].

In [Leligou'10], some applications where having reconfiguration properties can be very useful, are shown. For instance, urban operations can be very challenging, covering from applications where the movement inside and between buildings need to be checked, to military applications with rapid dissemination of combatants or shooter localization. The use of cameras in museums or supermarkets can permit face recognition and intruder tracking. Besides, by reconfiguring the platform according to the needs of video quality, power consumption can be reduced. Acoustic tracking of mobile targets in real time military applications is also an extremely challenging application where reconfigurable capabilities are very useful. Requirements such as high robustness, real time decision, high frequency sampling, multi-modality of sensing, complex signal processing and data fusion, distributed coordination in a wide area coverage, etc. can take advantage of hardware reconfiguration. In order to cover all of these requirements different hardware modules can be implemented and changed in real time. These modules can be:

- Data communication modules: changing communication parameters, reconfiguration according to the RSSI value, decreasing or increasing the data transfer rate according to the battery level.

- Data encryption and authentication modules.

- Data and video compression modules.

There is another important contribution to reconfiguration in WSNs related to data encryption with the *Cookie* platform. In [Portilla'10\_2], a comparison between systems based on microcontrollers and FPGAs with embedded microcontrollers for encryption applications is done. In this case, since the Spartan 3 included in the *Cookie* platform is too small, the concept proof was done using the Spartan 3 plus a Virtex 2 plus the ADuC842 microcontroller of the *Cookies*. The idea was the adaptation of the sensor network security depending on different applications and available energy using the Elliptic curve cryptography (ECC). Apart from that, in [Otero'11] the authors have already provided a reconfiguration engine for Spartan 6, which exploits reconfiguration capabilities using the Internal Configuration Access Port (ICAP) of the FPGA. The main feature of this block is its relocation capability, which means, the possibility of changing at run time the position of the reconfigurable blocks within the device. Thanks to this block, it is possible to allocate each reconfiguration engine in any empty slot in the reconfigurable region as it will be explain in the next chapter.

## Chapter 3

## **High Performance Node Architecture**

"...just give me what I came for, then I'm out the door again..."

Perfect Circle

#### 3. High-Performance Node Architecture

#### I. Design Requirements

The requirement list must answer the following questions: what needs the system meets and what features it must include. This requirement list has been evaluated following the needs of the high performance WSNs mentioned in the Introduction chapter. It is important to notice that these are the requirements of the system. The specifications and architecture will be explained within the following section in order to explain how these requirements are solved.

The main purpose of the system is acting as a wireless sensor node compliant with the *Cookie* platform to be used in very demanding applications. The main requirements for the platform design are listed below.

- 1. The node must be self-configurable so it can return to a known state once the system is powered on and off.

- The node must be capable of including different functionalities and changing them depending on different internal or external variables, which means higher integration. All the changes must be done without stopping the rest of the system.

- 3. The configuration of the nodes must include the possibility of being done remotely and after deployment.

- 4. The platform must be capable of working with both digital and analog signals (i.e. from different sensors).

- 5. The system must be compliant with both the sensor and communication layers of the Cookie platform.

- 6. The design must be fully testable from a computer. It also has to have available check points for the initial development and validation.

- 7. The design must be compatible with future hardware upgrades.

- 8. The system must be aware of its own power consumption since it needs to implement energy saving policies.

- 9. The platform must be powerful enough to deal with multimedia applications, encryption algorithms, etc.

- 10. The physical size of the platform must be fully compatible with the Cookies architecture (60 mm x 40 mm) including the space for the vertical connectors.

- 11. The architecture of the node must include a mechanism to power different parts of the platform separately.

- 12. The design must be oriented to low power in order to be used with Lithium batteries.

- 13. The design must include hardware and software advantages to provide larger flexibility.

#### II. System Specifications and Architecture

Every one of the previous requirements must imply a specification for the node architecture. In the same way, every one of these specifications must be reflected in the node architecture. In order to make the structure of the document easier to understand, the architecture of the node is explained together with the specifications. Besides, to clarify, references to the previous requirements are done in order to explain how they are faced and solved.

This section is organized as follows: first, a top view of the system is explained in order to understand the communication between the existent layers and the new ones. Then, the new modules are explained in detail focusing on the new processing layer architecture and given some information about the new power supply layer.

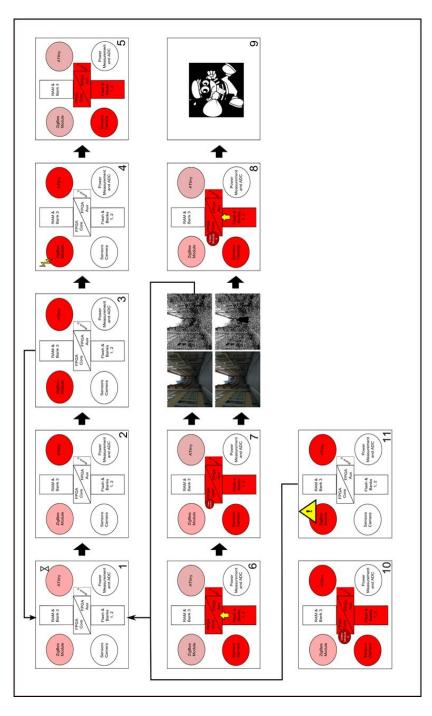

#### II.1 Node Architecture

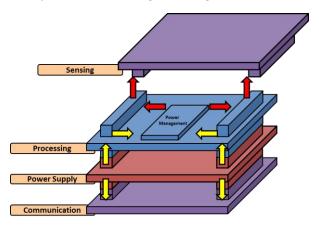

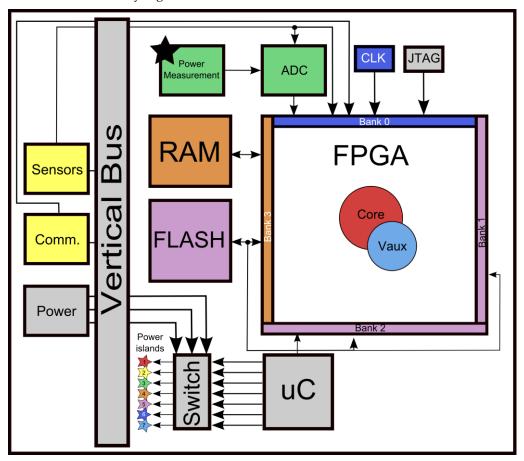

In Figure 6, the top view of the node architecture is shown. The node is divided into four different layers following the traditional design of the *Cookie* platform

(requirements 5, and 10). Both the communication and the sensor/actuator layers remain unchanged while new designs must be done for both the processing and power supply ones. The power supply layer must be redesigned in order to cover the new voltage supply values needed by the new processing layer. Besides, the power supply layer must be capable of giving much more current than the previous versions due to the current peaks required by the FPGA. Regarding the processing layer, this is the main design this Master Thesis is focused on, and it will be detailed in the following section.

As it was mentioned before, these four layers are connected through vertical buses. However, in the case of the power rails, the design has been changed in the work developed in this Master Thesis. In order to be able to power on and off the communication and sensor layers separately, the power layer must be placed under the processing one so that it is the processing layer the one in charge of controlling the voltage supply. Every module that needs to be powered permanently can be connected directly to the power supply layer in order to avoid the power rail control. Notice that in Figure 6, the communication layer is always powered while the sensor one can be powered on and off by the power management module included in the processing layer. Regarding the data transmission between layers, the signals are shared by all the layers like in the original design.

Figure 6: Power rails through the vertical buses.

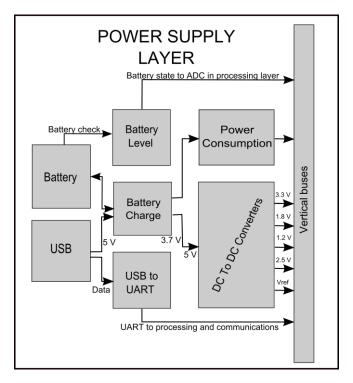

#### II.2 Power Supply layer

In this new version of the power supply layer, the node can be powered either from a battery (Lithium or AA) or from a mini-USB port. Due to maximum current peaks, it is necessary for the power source to be able to provide up to 2 A in the worst case. In the case of a computer, the USB connection provides a maximum current of 500 mA, so a USB charger needs to be used. On the other hand, the battery used is a custom made one capable of handling these current values.

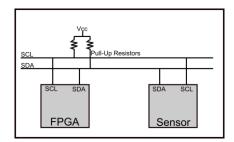

The USB connection has three main goals: powering the node, charging the battery and acting as an UART connection for debugging. The battery level and the current consumption of the whole node can be checked in order to send their values to the processing layer so that energy saving methodologies can be implemented (Requirement 8).

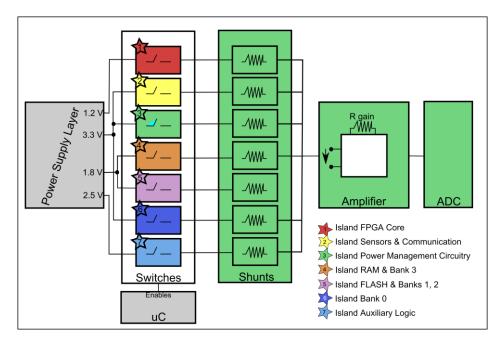

When both the battery and the USB cable are connected, the system is powered by the USB, while at the same time the battery can be charged. Both the battery and the USB outputs are connected to an integrated DC-to-DC converter with five outputs that provides the needed voltage and current values for the rest of the node. This DC-to-DC converter is an integrated circuit (IC) from Texas instruments that includes two power modes depending on the load connected to it. In this way, during the sleep periods, the load connected to the converter is low, so the power mode changes to power down mode with a power consumption of less than 1 mA. The diagram block of the power supply layer is shown in Figure 7. No further information about the development of this layer is detailed since this Master Thesis is focused on the processing layer design.

Figure 7: Power Supply Layer Diagram Block.

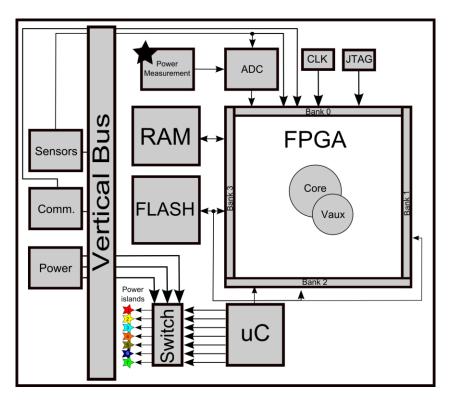

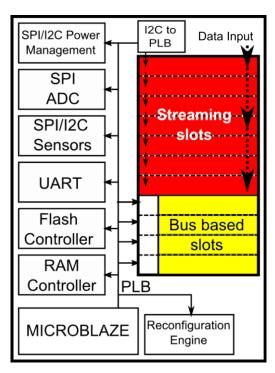

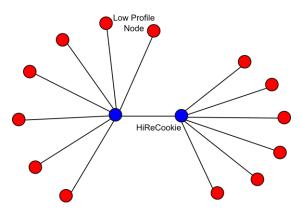

# II.3 Processing Layer: HiReCookie

This section is divided into two different subsections. First, the physical architecture of the High Performance Reconfigurable Cookie (HiReCookie) including all main components and their interconnections is detailed. Second, the internal architecture of the FPGA, called Virtual Architecture (VA), which includes both the peripheral controllers and reconfigurable areas, is explained.

When designing this kind of systems, the design of the VA is usually the first step so that the placement of all the external components can be done according to the internal architecture. However, in order to make the information clearer, the external architecture is going to be explained first.

# **II.3.1** Physical Architecture

In Figure 8, the block diagram with the main components of the processing layer is shown. The figure is divided into two different areas separated by the vertical bus. All components included on the right side belong to the processing layer while the blocks placed on the left side correspond with the rest of the layers of the *Cookies* architecture. The architecture of the processing layer is divided into seven different power islands that can be powered on and off separately (Requirement 12). Every one of these islands together with the power management methodologies will be explained in the next section and are now represented by colored stars.

The FPGA is the brain of the platform. It will be in charge of all the processing tasks and management decisions. The external microcontroller is the only device that remains always powered. It works as a sentry to wake the rest of the system up according to the orders given by the FPGA. Since the FPGA is a RAM based device, once it is switched off, all the information is lost. In order for the system to be self-configurable, an initial bitstream is stored in the Flash memory so that it is automatically loaded into the FPGA once both devices are powered. The Flash memory also works as a storage device for program data and other bitstreams.

Figure 8: HiReCookie physical architecture.

The RAM memory is mainly used as an extension program memory to provide fast access to the program data. This is very useful when using fast partial and dynamic reconfiguration.

Not all the signals handled by the node are digital. In order for the system to be able to process data from analog sensors and measuring the instant power consumption in every island, an ADC converter is required.

All the previous blocks are detailed below.

# **FPGA**

The FPGA that better matches the requirements of the system is the Spartan 6 XC6SLX150-2 from Xilinx. This is a RAM-based FPGA with a FGG484 package, large enough to allocate all the hardware blocks and peripherals needed by the high performance applications. Actually, it is the largest Spartan 6. The Spartan 6 family

has very competitive power consumption. This feature together with the power management strategies allows the system to be very suitable for WSN applications. Besides, a low-power version of the Spartan 6 with a speed grade of (-1) is already available in the market. According to the datasheet given by the manufacturer, this version can save up to 40% of energy by reducing the speed only in a 20%. The package of this low power version is compatible with the one used in the prototype presented in this work so it can be implemented in future work (Requirement 7).

This FPGA family offers a dual-register 6-input look-up table (LUT) logic and a wide selection of built-in system-level blocks including 18 Kb block RAMs, second generation DSP48A1 slices, SDRAM memory controllers, enhanced mixed-mode clock management blocks, etc. (See the component datasheet for more information). The main features of the chosen device can be seen in Figure 9.

| Device     | Logic<br>Cells <sup>(1)</sup> | Configurable Logic Blocks (CLBs) |            |                                | Block RAM Blocks                 |                      |          | Memory              | Endpoint                                     | Maximum                   | Total               | Max          |             |

|------------|-------------------------------|----------------------------------|------------|--------------------------------|----------------------------------|----------------------|----------|---------------------|----------------------------------------------|---------------------------|---------------------|--------------|-------------|

|            |                               | Slices <sup>(2)</sup>            | Flip-Flops | Max<br>Distributed<br>RAM (Kb) | DSP48A1<br>Slices <sup>(3)</sup> | 18 Kb <sup>(4)</sup> | Max (Kb) | CMTs <sup>(5)</sup> | Controller<br>Blocks<br>(Max) <sup>(6)</sup> | Blocks for<br>PCI Express | GTP<br>Transceivers | I/O<br>Banks | User<br>I/O |

| XC6SLX4    | 3,840                         | 600                              | 4,800      | 75                             | 8                                | 12                   | 216      | 2                   | 0                                            | 0                         | 0                   | 4            | 132         |

| XC6SLX9    | 9,152                         | 1,430                            | 11,440     | 90                             | 16                               | 32                   | 576      | 2                   | 2                                            | 0                         | 0                   | 4            | 200         |

| XC6SLX16   | 14,579                        | 2,278                            | 18,224     | 136                            | 32                               | 32                   | 576      | 2                   | 2                                            | 0                         | 0                   | 4            | 232         |

| XC6SLX25   | 24,051                        | 3,758                            | 30,064     | 229                            | 38                               | 52                   | 936      | 2                   | 2                                            | 0                         | 0                   | 4            | 266         |

| XC6SLX45   | 43,661                        | 6,822                            | 54,576     | 401                            | 58                               | 116                  | 2,088    | 4                   | 2                                            | 0                         | 0                   | 4            | 358         |

| XC6SLX75   | 74,637                        | 11,662                           | 93,296     | 692                            | 132                              | 172                  | 3,096    | 6                   | 4                                            | 0                         | 0                   | 6            | 408         |

| XC6SLX100  | 101,261                       | 15,822                           | 126,576    | 976                            | 180                              | 268                  | 4,824    | 6                   | 4                                            | 0                         | 0                   | 6            | 480         |

| XC6SLX150  | 147,443                       | 23,038                           | 184,304    | 1,355                          | 180                              | 268                  | 4,824    | 6                   | 4                                            | 0                         | 0                   | 6            | 576         |

| XC6SLX25T  | 24,051                        | 3,758                            | 30,064     | 229                            | 38                               | 52                   | 936      | 2                   | 2                                            | 1                         | 2                   | 4            | 250         |

| XC6SLX45T  | 43,661                        | 6,822                            | 54,576     | 401                            | 58                               | 116                  | 2,088    | 4                   | 2                                            | 1                         | 4                   | 4            | 296         |

| XC6SLX75T  | 74,637                        | 11,662                           | 93,296     | 692                            | 132                              | 172                  | 3,096    | 6                   | 4                                            | 1                         | 8                   | 6            | 348         |

| XC6SLX100T | 101,261                       | 15,822                           | 126,576    | 976                            | 180                              | 268                  | 4,824    | 6                   | 4                                            | 1                         | 8                   | 6            | 498         |

| XC6SLX150T | 147,443                       | 23,038                           | 184,304    | 1,355                          | 180                              | 268                  | 4,824    | 6                   | 4                                            | 1                         | 8                   | 6            | 540         |

Figure 9: FPGA Features. This image is taken from the Spartan 6 Datasheet.

The FPGA is the brain of the platform. It is the main component and the one in charge of taking all the decisions and implementing the energy saving methodologies.

The reasons why FPGAs are the best solution to face the requirements imposed by high performance sensor networks have been already discussed in the introduction chapter. The need of having very powerful processing capabilities working at very high speed is the perfect scenario for this kind of devices (Requirement 9). Besides, the capability of loading different hardware modules with different sizes at run time, allows the network to be configured remotely and in a very efficient way.

An overview of the FPGA architecture, as well as the most important aspects about its dedicated I/O pins, is explained below.

# 1. Power Supply Rails

The FPGA is powered by six power rails: four input/output banks, the FPGA core and the auxiliary logic. The I/O banks need to be powered according to the components connected to them. The voltage range for these I/O resources varies from 1.2 V to 3.3 V. This range, together with the possibility of powering the banks at different voltages, allows maximum flexibility for the system architecture. The FPGA core is powered at 1.2 V, except in the case of the low power version that is 1 V to reach minimum power consumption. This is the primary power supply of the FPGA so it needs to be very stable. In the case of the auxiliary logic, it includes some configuration logic and some internal and I/O resources. The voltages permitted for this rail are both 2.5 V and 3.3 V. The selection of this voltage depends on the power consumption restrictions (a voltage of 2.5 V can reduce the power consumption in this rail in up to 40%) and on the voltage standard used by the I/O banks. Then, the different power rails are set to the following voltage values:

- Vccint: FPGA core at 1.2 V.

- Vccaux: Internal logic with configuration and I/O resources at 2.5 V.

- Vcco\_0: Voltage supply for bank 0 powered at 3.3 V. As it can be seen in Figure 8, this bank is connected to the ADC, the external oscillator of 100 MHz, the communication layer (UART interface) and digital sensors.

- Vcco\_1: Voltage supply for bank 1 powered at 1.8 V. This bank is placed in the

reconfigurable side of the architecture. Some of the dedicated configuration pins

are placed in this bank. They are connected to the external Flash memory.

- Vcco\_2: Voltage supply for bank 2 powered at 1.8 V. As well as with bank 1, some of the dedicated configuration pins are placed in this bank. They are also connected to the external Flash memory. Apart from that, the external microcontroller for power management tasks is also connected to this bank.

- Vcco\_3: Voltage supply for bank 3 powered at 1.8 V. This bank is connected to the external memories.

- GND pins: All of them will be tight to the digital ground of the PCB.

- VFS: Decryptor key EFUSE power supply pin for programming. The design of the PCB allows using it or not. In this way, if the bitstream encryption is not used, this pin can be tight to GND for a lower consumption. If the encryption is to be used, then it is powered through the 3.3 V rail.

- VBATT: Decryptor key memory backup supply. The same as the previous one. It can be used or not. If it is used it may be tight to 3.3 V using a 0  $\Omega$  resistor.

#### 2. Configuration pins

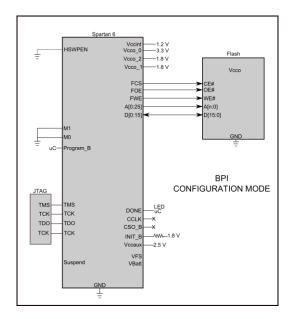

The configuration of the FPGA can be carried out through two different paths: the JTAG port and the Flash memory device.

The JTAG connection will be used for debugging and configuration issues. Thanks to the Chip Scope Tool, it will be possible to monitor all the FPGA signals in order to check the correct behavior of the modules (Requirement 6). Besides, through the JTAG port, it is possible to download total and partial bitstreams which will be a key aspect when debugging and testing the new designs in the lab.

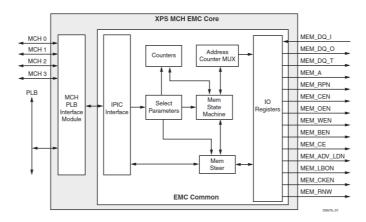

The FPGA has several initial configuration modes. The one chosen for this architecture is the Master Byte-wide Peripheral Interface (BPI) mode. This mode allows the FPGA to be configured directly and automatically from an external Flash memory device (Requirements 1 and 3). Regarding the Flash programming, the parallel interface permits a fast initial configuration. In the Master Configuration modes, it is the FPGA the one in charge of mastering the configuration clock (CCLK) while in the Slave modes the CCLK is an input. Therefore, this method follows the main concept of this platform: the FPGA is the brain of the system. The connection needed by this configuration mode is shown in Figure 10.

The pins needed for this configuration mode are mostly placed between banks 1 and 2:

• INIT\_B: Before the mode pins are sampled, INIT\_B is an input that can be connected low to delay configuration. After, INIT\_B is an output indicating

whether an error occurred during configuration. It will be connected with a pullup resistor since Program\_B (hardware reset) is the pin used to delay configuration in this design.

- CCLK: Configuration clock output. This pin is not directly connected to the flash but is used internally to generate the addresses and sample read data.

- FCS: Chip selects Output. It selects the memory device. Connected to CE#.

- FOE: Output Enable. Connected to OE#.

- FWE: Write Enable. Connected to WE#.

- Address Output: A [1:23]. The FPGA will begin automatically in 0 and will increment by 1 until the bitstream is completely downloaded. Then, the pin DONE will be asserted.

- Data Input: D [0:15] It will be sample by the rising edge of CCLK, even though is not connected to the memory.

- CSO\_B: Used for more than one memory in chain. Not connected.

- Mode pins: M [0:1]. They will be tight to GND for Master BPI configuration mode.

Figure 10: BPI Master Configuration Mode Connection.

Notice that even though the mode pins are selecting the BPI mode, the JTAG configuration can be used in any case since it is the one with the biggest priority. When the FPGA is powered, the address port starts providing addresses to the Flash memory. In this way, if the memory device is not correctly powered the configuration can be wrong. In order to ensure the correct configuration of the FPGA, it is possible to delay the addresses generation by holding the Program\_B until the Flash memory reaches the correct voltage value. This can be done by the external microcontroller in charge of the power management.

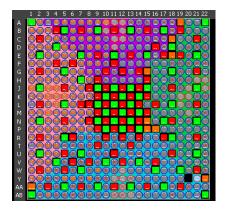

All the above design considerations, together with a pre-placement analysis to identify possible problems in critical signals due to crossover noise or to excessive toggle rate or power consumption, were done. This analysis was performed with the assistance of the pin planning tools provided by Xilinx as shown in Figure 11 for all the components connected to the FPGA.

Figure 11: FPGA Pin-Out.

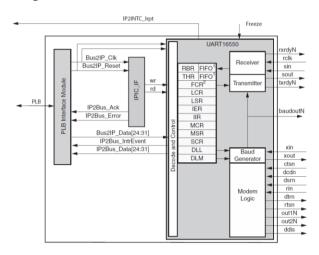

#### External Microcontroller

The external microcontroller chosen to execute the power management tasks implemented by the FPGA is the ATMEL AVR ATtiny2313V. This is a tiny microcontroller with 2k bytes programmable flash memory that can be powered at 1.8 V working in a frequency range of 0-4 MHz in a Micro-Lead-Frame (MFL) package of 4 x 4 mm. The power consumption in active mode running at 32 KHz is  $20~\mu\text{A}$  while working in power down mode it can goes below  $0.1~\mu\text{A}$ .

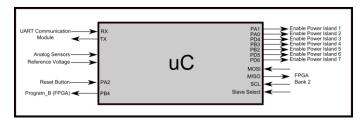

The microcontroller will be in charge enabling the seven different power islands and the interruptions caused by the external elements. The connection diagram is shown in Figure 12. The connection with the communication layer is done through an UART interface in order to be aware of the messages coming from the radio. Even though it is the microcontroller the component which actually executes the power management strategies, all the decisions of what to do and when to do it come from the FPGA. The communication between the FPGA and the microcontroller is made through the Universal Serial Interface (USI) that can be configured to work as a two-wire or three-wire connection. This is a pseudo I<sup>2</sup>C or SPI protocols that can be easily configured as hardware modules inside the FPGA. The microcontroller also includes an analog comparator very useful to create interrupts if certain threshold voltage is overtaken by an analog sensor. This module compares two signals, the sensor response and a reference voltage that can be generated either by the microcontroller itself or by the power supply layer. Besides, a reset button is also included to reboot

the system manually and the chip reset of the FPGA, the Program\_B pin, is connected to the microcontroller in case the delay of the initial configuration is necessary for any reason.

This external microcontroller will be the only component that is always powered in the platform. In this way, it can work as a sentry to wake the system up if necessary. The microcontroller works in power down mode with all the islands powered off until an external interrupt occurs. These external interrupts can be caused by: analog sensors, UART interface of the radio module, the FPGA or periodically using the internal clocks. The external microcontroller includes a JTAG connection for both programming and real time debugging (Requirement 6).

Figure 12: External Microcontroller Connection.

# Flash Memory

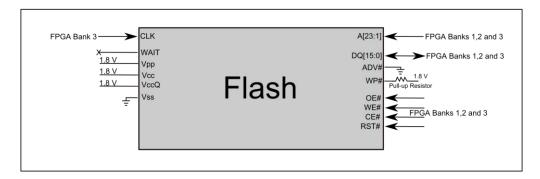

The memory device selected is a Numonyx Strata flash Embedded Memory (P30) model JS28F128P30B85 with a 56-Lead TSOP package. This is a NOR flash memory recommended by Xilinx with 128 Mbits of capacity. It can be powered at 1.8 V which matches perfectly well with the rest of the power rails. The initial access time is 85 ns working at 52 MHz (more data can be found in the manufacturer datasheet).

The inclusion of a non-volatile memory device on the platform is due to four main reasons:

- Storing sensor data to be processed and sent through the network.

- Storing program data to be used by the embedded processor including in the FPGA.

- Working as the configuration bitstream source for the FPGA, after a switch-off period. Using the BPI mode explained before.

Storing partial bitstreams of different hardware modules (Requirement 2). These

modules are configured in the device at run-time only when they are required.

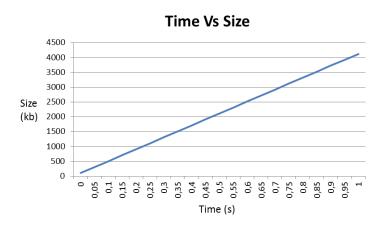

According to the proposed power management strategies that will be described in the following chapter, all the components included in the node will be switched off during sleeping periods. One of the drawbacks of using RAM based FPGAs is the fact that they do not keep their configuration when the power supply is cut off. Therefore, it is necessary to store an initial configuration file in a non-volatile device. In this way, using the automatic configuration mode (Master BPI Mode), the bitstream is automatically downloaded into the FPGA once both devices are powered on.

As it was mentioned before, in order to work as the initial bitstream source for the FPGA, the memory must be connected to the dedicated configuration pins of the FPGA. Nevertheless, the memory will also work as a storage device for other kind of information, so it needs to be accessible through another controller as well. Due to the restrictions imposed by the virtual architecture (the internal architecture within the FPGA), which will be explained in the following section, the memory controller cannot be placed close to the I/O banks 1 and 2 since they are within the reconfigurable area. Due to this reason, two different connections will be required for this memory. As it can be seen in Figure 8, the memory device is connected to the dedicated configuration pins in banks 1 and 2 and to bank 3 where the peripheral controller will be placed.

In Figure 13, the pin out of the Flash memory is shown. Notice that all pins, except the configuration clock (CCLK), are connected both to banks 1 and 2 and to bank 3. Even though the configuration mode is synchronous, the CCLK is not connected to the memory device although flash data is still sampled in every rising edge of the CCLK. The Write Protection pin (WP) is not used so it is asserted high in order to permit writing at all times.

Figure 13: Flash Memory Connection.

It is important to notice that in order for the Flash to act as the initial bitstream source of the FPGA; this initial configuration file must be previously stored in the memory. Since the Flash memory is only connected to the FPGA, this storage must be done through the JTAG port. This storage can be done using the IMPACT tool provided by Xilinx. This is an indirect programming method where a small piece of IP is needed to connect the IMPACT software to the Flash memory through the Spartan 6.

#### **RAM Memory**

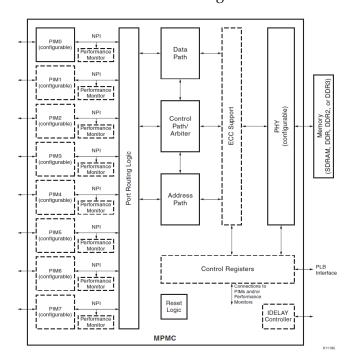

The RAM memory chosen is the Mobile Low-Power SDR SDRAM MT48H16M16LF from Micron with a 54-Ball VFBGA package. This memory is a high-speed 256 Mbits, CMOS dynamic random-access memory. The speed grade chosen is (-75) which corresponds to a 133 MHz with an access time of 5.4 ns. As well as in the case of the flash memory, it can be powered at 1.8 V. Read and write accesses to the memory are burst oriented. Accesses start at a selected location and continue for a programmed number of locations following a programmed sequence. Accesses begin with an ACTIVE command, followed by a READ or WRITE. The address bits registered in the ACTIVE command are used to select the bank and the row. The address bits registered in the READ or WRITE command are used to select the starting column location for the burst access. The device uses an internal pipelined architecture which is able to change the column address on every clock cycle in order to achieve high-speed and fully random accesses.

According to the methodology proposed in the introduction chapter, energy savings are increased by speeding up the processing. Due to this fact, a RAM memory has been also included in the node to allow fast information accesses by the embedded processor. Partial and dynamic reconfiguration speed can also have benefits by using an external RAM memory to store partial bitstreams, compared to the use of the external flash.

As it can be seen in Figure 8, the memory device is connected to the third bank of the FPGA. This is because the controller module that is normally used to master the memory, the MPMC provided by Xilinx, is a hard IP known as Memory Controller Block (MCB) which is placed both in bank 3 and bank 1. Since bank 1 is located in the side of the FPGA used for the reconfigurable blocks, the MCB used is the one in bank 3.

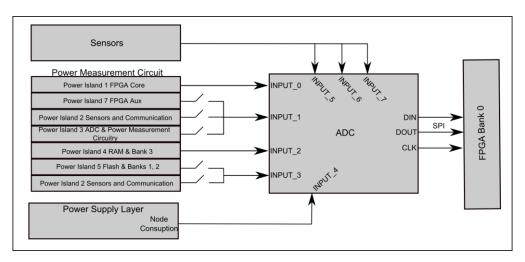

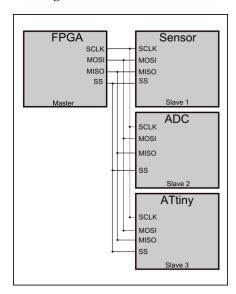

# Analog to Digital Converter

Analog to digital conversion is needed to process the signals from the sensors (Requirement 4). Besides, the system has the ability of measuring its own power consumption in every one of the power islands, so the ADC is also required to convert these consumption values. The ADC chosen is the AD7928 from Analog devices. The AD7928 is an eight-input device with a SPI interface to communicate with the FPGA. It is an 8-bit resolution converter with a throughput rate of 1 MSPS that can be powered at 3.3 V which matches the voltage range imposed by the sensors and the power measurement circuitry.

The connection diagram of the ADC is shown in Figure 14. As it can be seen, half of the ADC inputs are dedicated to convert the power consumption of the power islands (Requirement 8). The most important ones, such as the island containing the FPGA core or the one with the RAM memory, have their own input, while the less used have been combined with other important islands like the Flash memory. The selection of which islands must be monitored is done externally by placing 0  $\Omega$  resistors. The fourth input is used to monitor the global consumption of the node that is measured in the power supply board. The rest of the ADC inputs are used to convert the signals coming from the analog sensors. As it was mentioned before, the

communication between the ADC and the FPGA is made through a SPI connection that will be detailed in the VA architecture of the FPGA.

Figure 14: ADC Connection.

# Power Management and Measurement Circuit

The inclusion of high performance components in the platform leads to very high energy consumption. Even though some of the components have their own power save modes, the static consumption is still too high (in the case of the FPGA: 60-80 mA) so the components need to be powered off when they are not needed.

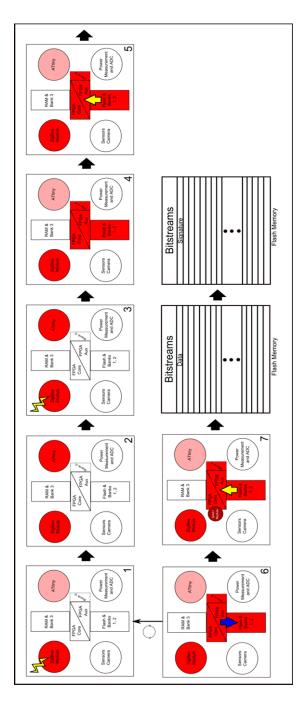

The architecture proposed in this work is divided into seven different power islands that can be switched on and off separately depending on the system needs. Therefore, all the components can be switched off during sleeping time so that global power consumption is sharply decreased. In order to control these islands, it is necessary to include the ATtiny microcontroller that was explained above.

In Figure 15, every power island is represented in a different color. The islands are listed below (Requirement 11):

- Island 1: FPGA core. Powered at 1.2 V.

- Island 2: Sensor and communication boards. Powered at 3.3 V.

- Island 3: ADC and power consumption circuitry. Powered at 3.3 V.

- Island 4: RAM memory and bank 3 of the FPGA. Powered at 1.8 V.

- Island 5: Flash memory and Banks 1, 2 of the FPGA. Powered at 1.8 V.

- Island 6: External clock and Bank 0 of the FPGA. Powered at 3.3 V.

- Island 7: Auxiliary logic of the FPGA. Powered at 2.5 V.

Figure 15: HiReCookie Architecture: Power Islands.

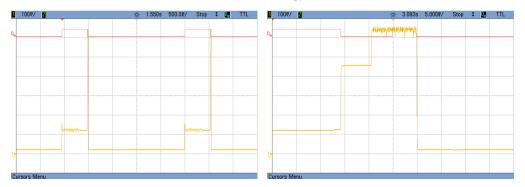

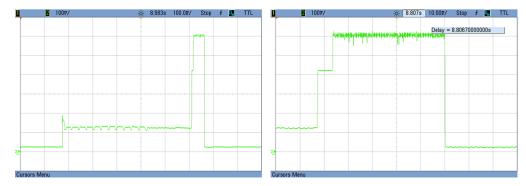

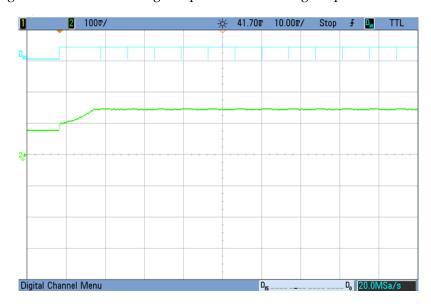

As it can be seen, four different power supply voltages are used: 1.2 V, 1.8 V, 2.5 V and 3.3 V. The FPGA core is the only one powered at 1.2 V and, therefore, it needs to be in an independent island. The 1.8 V supply is used to power banks 1, 2 and 3, the external memories and the external microcontroller. The external microcontroller is not included in the islands division since it needs to be powered at all times. During the initial configuration, the bitstream is downloaded from the flash memory