ORDENADORES. FILOSOFIAS Y DESARROLLOS

ACTUALES Y FUTUROS

Por F. Sáez Vacas Catedrático de Ordenadoes E.T.S.I.T.

Hewlett Packard 30 May 01977

# INDICE

| 0. INTRODUCCION                                      | 1   |

|------------------------------------------------------|-----|

| I. HARDWARE                                          | 1   |

| I.1. Esquema funcional                               | 1   |

| I.2. Dimensiones del espacio del ordenador           | 6   |

| I.3. Tecnología y estructura                         | 8   |

| I.4. Memorias                                        | 11  |

| I.4.1. Memorias asociativas y aplicaciones           | 17  |

| I.4.1.1. Memoria "Cache"                             | 19  |

| I.4.1.2. Memoria Virtual                             | 21  |

| I.4.2. Microprogramación                             | 26  |

| I.5. Proposiciones de Sáez (1.973) sobre condiciones |     |

| de viabilidad de innovaciones en técnica o tec-      |     |

| nología                                              | 30  |

| I.6. Arquitecturas de ordenador                      | 31  |

| I.6.1. Sistemas multiprocesadores y paralelos        | 32  |

| I.6.2. Sistemas minis y micros                       | 46  |

| I.6.2.1. Estructura-robot y aplicaciones             |     |

| de los minis                                         | 47  |

| I.7. Ordenador promedio típico del año 2.000         | 55  |

| II. SOFTWARE                                         | 56  |

| II.1. Clasificación y algunas definiciones           | 56  |

| II.2. Problemas del software                         | 60  |

| II.3. Estructura y costes del proceso de desarrollo  |     |

| y mantenimiento del software                         | 63  |

| II.4. Las técnicas de programación estructurada      | 66  |

| II.5. El futuro del software. Resumen de problemas   |     |

| y recomendaciones                                    | 70. |

| III. INFORMATICA                               | 74 |

|------------------------------------------------|----|

| III.1. ¿Cómo y en qué utilizar el ordenador?   | 74 |

| III.2. Sistemas centrados en una base de datos | 78 |

| III.3. La Informática repartida                | 81 |

| REFERENCIAS                                    | 83 |

### 0. INTRODUCCION

Esta conferencia pretende presentar una panorámica de las actuales estructuras de ordenador, de las principales corrientes tecnólogicas ya concretadas a nivel de producto tangible, de algunos aspectos y problemas de software, y de presente discusión acerca de las informáticas concentrada o repartida.

Se supone que los asistentes son de muy dispar función profesional, pero todos saben ya qué es y cómo funciona un ordenador (ver conferencia sobre Microprocesadores).

Es de observar que nuestro principal énfasis se centra en la arquitectura de los ordenadores, ya de por sí tan compleja que se suele desarrollar durante uno o varios cursos completos. Los aspectos de software se mencionan y se recorren muy su

perficialmente puesto que, en definitiva, deberían apoyarse en

una profundización de los de la arquitectura.

Por último, se destaca que estos apuntes no son más que un soporte escrito de la conferencia, que puede ser aprovechado por los asistentes más interesados para hacer sobreanotaciones.

#### I. HARDWARE

### I.1. Esquema funcional

Suele representar las principales funciones de un orde nador, que son:

Unidad de Memoria

Unidad de Control

Unidad Aritmética-Lógica

Unidad Central

Procesador Central

Unidad de Entrada/Salida.

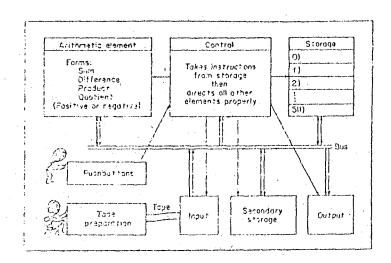

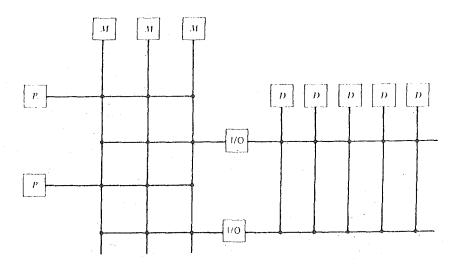

Ver esquema del ordenador Whirlwind:

Whirlwind.

Estas funciones siguen existiendo, pero se han escindido ya en numerosas unidades interrelacionadas y jerarquizadas, lo que hace que un esquema como el anterior no represente más que muy superficialmente la estructura real de un ordenador.

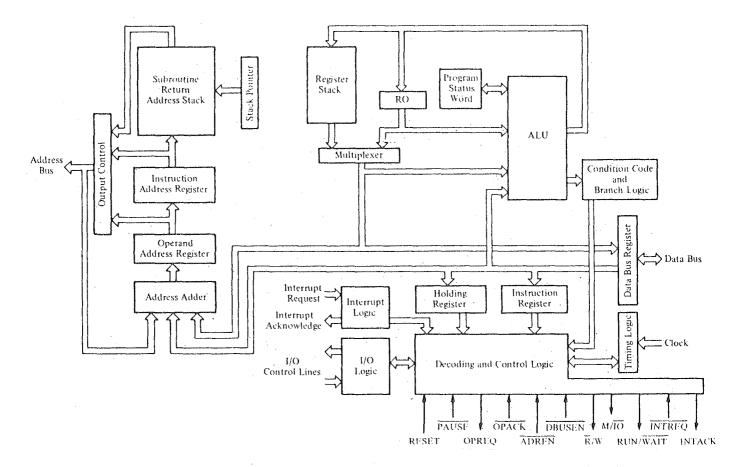

Yendo a mayor detalle hay que utilizar esquemas como - el siguiente (ver pág. 3).

El problema es ¿hasta donde puede llegarse en el detalle de representación?. Profundizando el detalle se podría ir - hasta el circuito lógico y esto, para los especialistas en estructura de ordenadores, sería demasiado. Por otro lado, la figuración mediante cajas y flechas es ambígua, depende mucho del individuo que la emplea.

Bell y Newell han atacado este problema y han elaborado unos sistemas de representación, con unos elementos primitivos perfectamente definidos y una notación simbólica a varios -

ESQUEMA DE BLOQUES DEL SIGNETICS 2650 (FUENTE: FOSTER)

niveles o capas de detalle. El libro donde han descrito esta - aproximación es hoy un clásico en el género y absolutamente in-dispensable en la biblioteca de los especialistas.

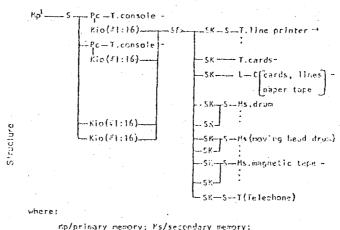

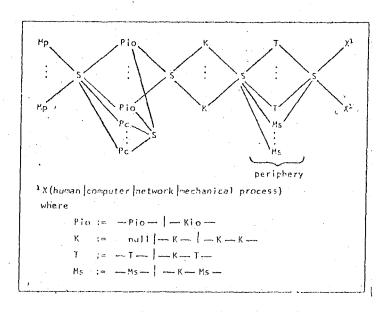

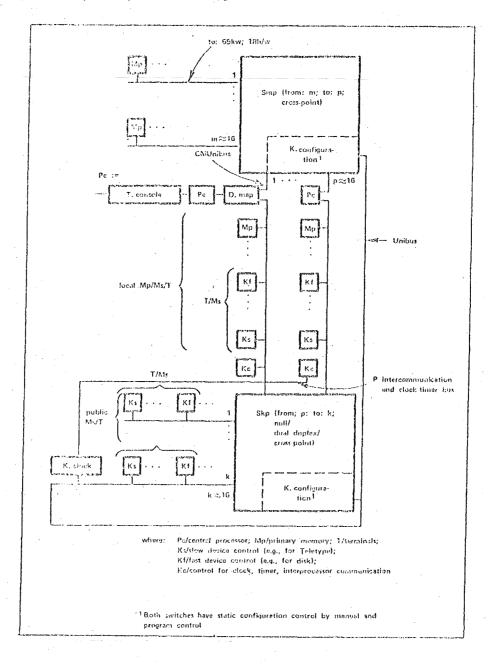

A título de ejemplo, recogemos aquí un ordenador des--crito al nivel PMS:

rp/primary memory; Ps/secondary memory;

Fc/central processor; T/terminal; and t/link

S/switch: K/control: Kic/control for To equipment;

1 Hp (#0:7: coré; 32768 word)

Estructura representada en PMS.

Otros niveles reconocidos por Bell/Newell son los siquientes:

- . Nivel Programación

- . Nivel Diseño Lógico

Subnivel RT (Register Transfer)

Subnivel circuitos conmutación:

- . secuencial

- . combinacional

. Nivel circuito

A continuación transcribimos la definición de los componentes que intervienen en el nivel PMS (Processor Memory Switch).

MEMORIA, M. Es un componente que retiene o almacena información (es decir, unidades de información, unidades i) a lo largo del tiempo. Sus operaciones son leer unidades i de la memoria y escribir unidades i en la memoria. Toda memoria que almacene más de una unidad i debe comportar, asociadamente, un sistema de direccionamiento, por medio del cual pueda seleccionar una unidad particular. Puede también considerarse a una memoria como un conmutador a un cierto número de submemorias. Las unidades i no se modifican en modo alguno al ser almacenadas en memoria.

INTERCONEXION, (Link; L). Es un componente que transfiere información (unidades i) de un lugar a otro en el sistema

ordenador. Tiene puertas fijas. Su operación consiste en transmitir una unidad i (o una secuencia de unidades) desde una puer

ta a otra del componente. Excepto el cambio de posición, no se

produce ninguna otra modificación en las unidades i.

CONTROL, K. Es un componente que activa las operaciones de otros componentes en el sistema. Todos los demás componentes son considerados como consistentes en un conjunto de operaciones discretas, cada una de las cuales, al ser activada, -

realiza alguna transformación discreta de estado. Con la excepción de un procesador, P, el resto de componentes es esencíal-mente pasivo, por lo que requiere algún agente activo (un K) para entrar en período de actividad.

CONMUTADOR, (Switch, S). Es un componente que construye un enlace entre otros componentes. A cada conmutador va asociado un conjunto de enlaces posibles y sus operaciones consisten en tender algunos de estos enlaces y cortar otros.

TRANSDUCTOR, T. Es un componente que modifica la uni-dad i utilizada para codificar un determinado significado. El cambio puede afectar al soporte (p. ej. niveles de tensión a flujo magnético, o niveles de tensión a perforaciones en una tarjeta de cartulina), o a la misma estructura de la unidad i (p. ej. bits en serie a bits en paralelo). Los componentes T preservan el significado, pero no necesariamente la información (en el sentido del número de bits).

OPERADOR DE DATOS, D. Es un componente que produce uni dades i con nuevos significados. Este tipo de componente realiza todas las operaciones con datos, p. ej. operaciones aritméticas, lógicas, de desplazamiento, etc.

PROCESADOR, P. Es un componente capaz de interpretar - un programa en orden a la ejecución de una secuencia de operaciones. Consiste en un conjunto de operaciones de los tipos ya mencionados -M, L, K, S, T y D- más el control necesario para - obtener instrucciones de una memoria e interpretarlas como operaciones a ejecutar.

#### Comentarios

- Complejidad

Dificultad de representación

Dificultad de comprensión

Más dificultad de representación, comprensión y comunicación.

- Falta de normalización

Dificultad de comparación, comunicación y de evaluación.

### I.2. Dimensiones del espacio del ordenador

El cuadro puede dar una idea de un espacio multidimensional, en cada uno de cuyos ejes se identifican distintos valo res posibles. Un ordenador concreto quedaría situado en ese espacio por la especificación de los valores que le corresponden (uno o más valores por cada dimensión-eje). Su situación en el espacio mencionado le indica al especialista cuales son sus características funcionales y operativas, tanto en valor absoluto como relativamente a la constelación de ordenadores producidos.

#### FUNCION DEL OPDENADOR

Cientifico Control Comunicaciones (condutes on spacentracion) Control de Laneros Termenal Tiempo compartido

| TECNOLOGIA DE<br>LA LOGICA                  | GENERACION | FECHA<br>HISTORICA | VELOCIDAD<br>Political | COSTE OPERACION |

|---------------------------------------------|------------|--------------------|------------------------|-----------------|

| Mecanica                                    |            |                    |                        |                 |

| Electromecan ca                             |            | 1930               | 10 3                   | 1000            |

| (Fluidica)                                  |            | (1970)             | 10 7 -                 |                 |

| Tubio de vacio                              | Primera    | 1945               | 10 3                   | 10              |

| Transistor                                  | Segunda    | -1958              | 1U °                   | 1               |

| hi brida                                    |            | 1064               | 10 6                   |                 |

| Circuito integrado/IC                       | Tercera    | 1966               | 10-7                   | 0.1             |

| Integrada de media a<br>gran escala MSI~LSI | ¿Cuarta?   | :197->             | 10 "                   | 0 01            |

| LONGITUD PALABRA | BASE           | T POS DE INFORMACION      |

|------------------|----------------|---------------------------|

| 86               | binaria        | pulabra                   |

| 124              | geomal         | e itera anección (entero) |

| 16 b             |                | Lie south de bits         |

| 24.5             |                | incting on                |

| 32 b             |                | na Hotante                |

| 48 b             |                | (*18°00] [2]              |

| 64 b             |                | coderra de caracteres     |

|                  | caracter (6 h) | enitor de palabras        |

| •                | (Bracter (Bib) | vector                    |

| •                |                | reating                   |

|                  |                | att 175 -                 |

|                  |                | listas, pilas             |

| DIRECCIONES INSTRUCCION | ESTADO DE MEMORTA DEL PROCESADOR<br>lexeluyendo contacor programa) |

|-------------------------|--------------------------------------------------------------------|

|                         | <br>                                                               |

O direcciones (ona) -1 direction 1 + x (inclise) directiones

1 in the procedures of the economics of

Jampuesta

metroprostations.

Lacamulador acumulador y registros indice

estado no explicato

| ESTRUCTURA PMS                    | CONMUTACION               | FUNCION PROCESADOR |

|-----------------------------------|---------------------------|--------------------|

| 1 F2                              | I n (duplex)              | P microprogr       |

| 1.Paliyars repayant               |                           | Pc                 |

| FPs in Pie                        | nim (multiplex de tiempo) | Pa (no ial         |

| 1 Pc - n Pio - P (display) .      |                           | Pio ·              |

| 2 C (duplex)                      | 2.n (dual duplex)         | P. display         |

| n Po in Litiprocesamiento)        | n im punto de cruce       |                    |

| n Pe P (array algoritmo especial) |                           | P array            |

| n Puliprocesamiento curaleio)     | and the second second     | P mov vectores     |

| C (r, 3)                          |                           | P Ligaritmo        |

| Red                               | n-2 n/2 (sin jerargara)   | Pienguaje          |

|                                   |                           | ***                |

| ALGORITMO ACCESO                         | CAPACIDAD<br>NP    | CAPACIDAD<br>NS                     | VELOCIDAD<br>NP (b si | VELOCIDAD<br>MS (b s) |

|------------------------------------------|--------------------|-------------------------------------|-----------------------|-----------------------|

| imeal (pita)<br>- neal (cofa)<br>trandar |                    | cinta maq. (grande)                 |                       | - 105                 |

| Cronco aleatorio                         |                    | tyranite ; futu almace              |                       |                       |

| Cielico                                  | ramber (grande)    | rambor (pequena)<br>nucleus (menor) | > 109                 |                       |

| Alestorio                                | nucleos (mecha)    |                                     | > 107                 | > 167                 |

| Por contenido                            | peticulà (pequeña) |                                     | > 10°                 |                       |

| Asociativo                               | circuito integrado |                                     | ~ 10°                 |                       |

| CONCURRENCIA Mp                         | COMUNICACION INTERFROCESOS                                                                                    |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 1 Programa                              | Subrutinuš                                                                                                    |

| 1 Principling con interropciones        | interrupt times                                                                                               |

| 1 Programa con multiples subjengamas    | interrupciones interprocesador                                                                                |

| concurrences (p. er. 1 Pc ii Pio)       | e de la companya de |

| Monitor o Pray (Ejo EM) + 1 programa    | lamarla: monitor)                                                                                             |

| m + n programas canjeubles              | •                                                                                                             |

| m + n programus (multiprogramation)     |                                                                                                               |

| No reubicación                          |                                                                                                               |

| 1 seamento,                             |                                                                                                               |

| 2 sugmentos spura, impurol 💢            |                                                                                                               |

| * 2 segmentos                           |                                                                                                               |

| Pag-nas                                 |                                                                                                               |

| m + n segmentos c un progr. compartidos | comunicación intersegmentos                                                                                   |

| segmentos paginarius, lung fija j       |                                                                                                               |

| segmentos paginados, lang, multiple     |                                                                                                               |

| segmentos torgitud variable             |                                                                                                               |

| segmentos nonunados                     |                                                                                                               |

#### CONCURRENCIA PROCESADOR

Serve bit a bit Serve bit à bit.

Paulelej por palabra.

Paulelej por palabra.

Nutripies corrientes datos currays!

Ebetler p. instrucción

in butters p. instrucción

in butters p. instrucción

inemorias anticipativas

Procesanviento pape ligis.

### I.3. Tecnología y estructura

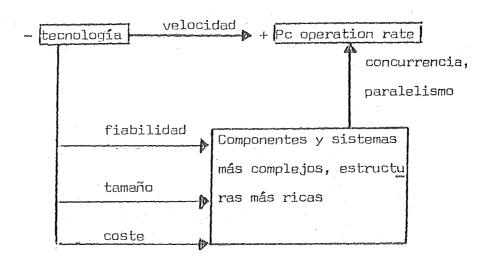

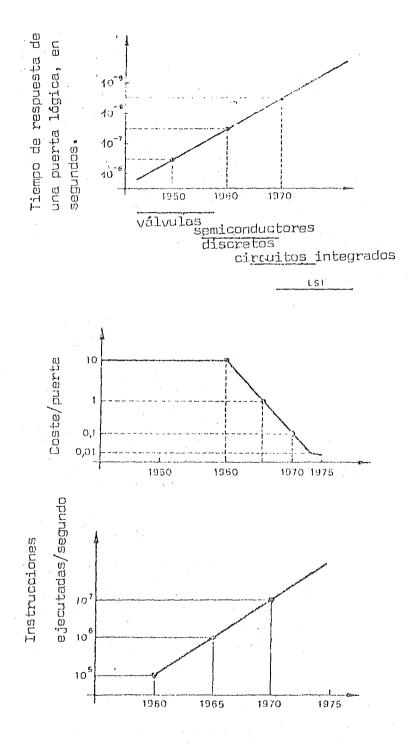

La tecnología es la dimensión más significativa o influyente de todo el espacio, ya que prácticamente condiciona - los valores de todas las demás dimensiones. Aunque existen - otros tipos de tecnología es la electrónica la que reviste más espectacularidad y trascendencia. Vemos en la figura cómo, por dos caminos diferentes, influye la tecnología en la velocidad de operación del Procesador central (Pc-operation rate).

VELOCIDAD DEL PROCESADOR CENTRAL

En particular, es muy importante el esfuerzo emprendido en una mejor estructuración y organización de los circuitos y unidades funcionales, lo que conduce a un mayor grado de concurrencia o paralelismo. Este punto ha dado lugar a unas familias de ordenadores que, por su nivel técnico, marcan el estado tecnológico actual del "arte" de la arquitectura de los ordenadores. Por esta razón y por el desconocimiento general — acerca del tema, dedicaremos un amplio apartado a estas familias.

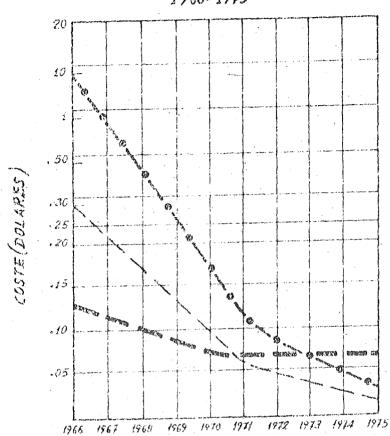

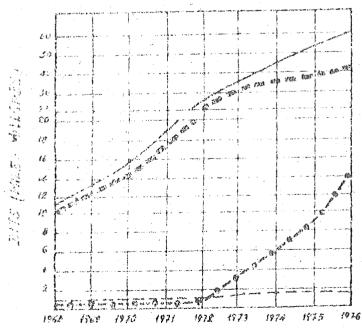

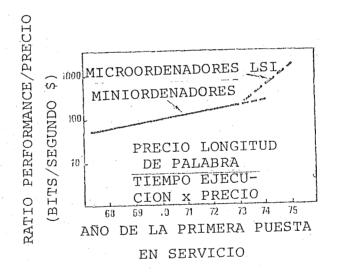

Las siguientes figuras señalan el efecto de la evolución de la tecnología en los costes y en la velocidad del procesador.

Contrastando la primera y tercera gráficas, se comprue ba cómo la velocidad del procesador (instr/seg.) ha crecido relativamente más deprisa que la velocidad de una puerta lógica, a lo largo del tiempo. Esto se debe básicamente a los avances técnicos de diseño e implementación.

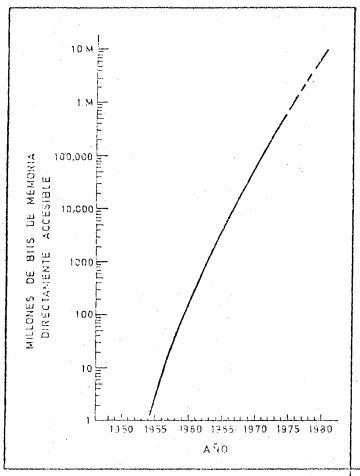

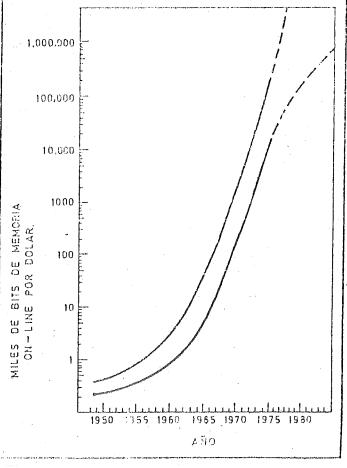

Las próximas curvas dan una idea de la misma evolución en el terreno de las memorias.

#### I.4. Memorias

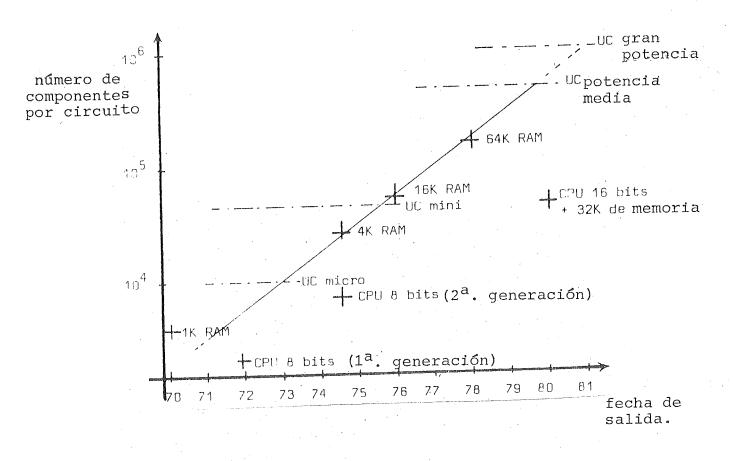

Los circuitos integrados y ultimamente los microproces sadores representan puntos culminantes en la evolución tecnológica de los ordenadores y de manera general de los sistemas digitales. Estos temas han sido exhaustivamente presentados por conferenciantes anteriores.

Interesa resaltar ahora que los circuitos a base de - semiconductores e integración a gran escala suponen que, por - primera vez, es posible construir toda la estructura de la unidad central de un ordenador a base de la misma tecnología electrónica. Esto es un hito en la historia de los computadores.

Veamos algunos elementos acerca de las memorias centrales de un ordenador. (El cuadro siguiente presenta una panorámica general de las memorias más conocidas, no solamente centrales, al año 1.971 (Bell/Newell)).

Tecnológicamente, la memoria central de un ordenador puede ser de:

- a) núcleos de ferrita

- b) película delgada magnética

- c) semiconductores.

La memoria de núcleos es demasiado conocida, precisamente fué introducida por vez primera en el computador Whirl--wind (ver I.1.), y la memoria de semiconductores se ha tratado en otra conferencia.

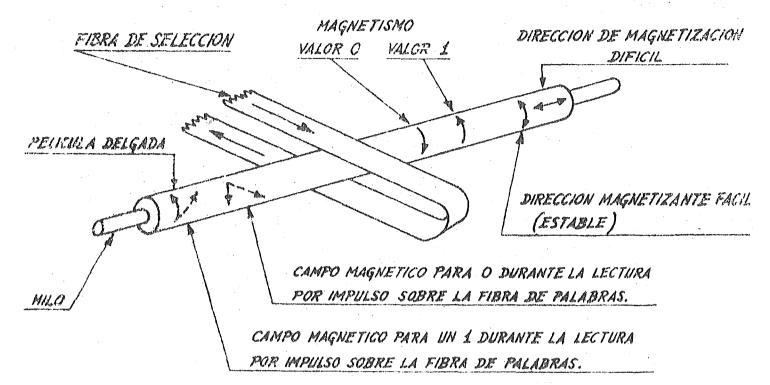

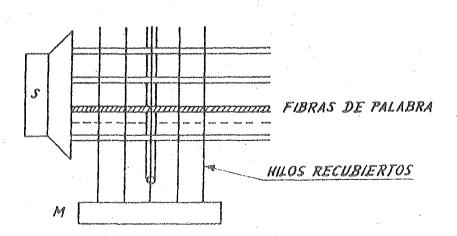

Por consiguiente, demos algunos datos de la tecnología de película delgada magnética en la técnica de hilo recubierto.

Se basa en una película muy fina de material magnético anisotrópico con el que se recubre un hilo de cobre-berilio, -

### CARACTERISTICAS DE LAS MEMORIAS

|                                                            | -                                        | ——— DIMENSION ———    |                                                  | I                      |                               |                                    |                                          |

|------------------------------------------------------------|------------------------------------------|----------------------|--------------------------------------------------|------------------------|-------------------------------|------------------------------------|------------------------------------------|

| MODULO MEMORIA FUNC                                        | FUNCION                                  | MODO DE<br>ACCESO    | CAPACIDAD<br>DEL MODU-<br>LO (bits)              | MODULOS/<br>COMPUTADOR | TIEMPO DE<br>ACCESO<br>(Seg.) | CAUDAL (bits/seg.)                 | COSTE/BIT (\$) (Soporte + transductor)   |

| Tarjeta perfor <u>a</u><br>da                              | permanente,<br>fichero                   | random + secuen cial | (500∿1000)/<br>tarjeta;∿<br>1000 tarj/<br>unidad | 1 ∿ 2                  | 10°∿10 <sup>3</sup>           | 10 <sup>4</sup>                    | 2x10 <sup>-6</sup> +2x10 <sup>-1</sup>   |

| Tarjeta magné-<br>tica                                     | secundaria,<br>fichero                   | cial +               | 3 x 10 <sup>9</sup>                              | 1 ∿ 4                  | 10 <sup>-1</sup> ∿10°         | 0,4x10 <sup>6</sup>                | 1,5x10 <sup>-8</sup> +5x10 <sup>-5</sup> |

| Cinta magnética                                            | secundaria,<br>fichero                   | secuen<br>cial       | 2 x 10 <sup>8</sup>                              | 1 ∿ 16                 | 10° ~10 <sup>2</sup>          | 0,4~4x10 <sup>6</sup>              | $2 \times 10^{-7} + 10^{-4}$             |

| Disk-pack de ca<br>bezas móviles                           | secundaria,<br>"swapping"<br>de ficheros | cial +               | 2 x 10 <sup>8</sup>                              | 1 ~ 16                 | 10 <sup>-1</sup> √10°         | 2,5x10 <sup>6</sup>                | $3\times10^{-6}+10^{-4}$                 |

| Disco cabezas<br>fijas                                     | secundaria<br>"swapping"<br>de ficheros  | cíclico              | 5 x 10 <sup>7</sup>                              | 1 ~ 40                 | ∿10 <sup>-2</sup>             | 10 <sup>6</sup> ∿10 <sup>7</sup>   | 10 <sup>-3</sup>                         |

| Tambor                                                     | secundaria<br>"swapping"                 | cíclico              | (1∿5)x10 <sup>7</sup>                            | 1 ∿ 10                 | (5√30)x10 <sup>-3</sup>       | 10 <sup>6</sup> ~10 <sup>7</sup>   | 10-3                                     |

| Memoria extendi<br>da                                      | primaria y/o secun daria, "swapping"     | random               | 107                                              |                        | (2∿10)×10 <sup>-6</sup>       |                                    | 0,02 ∿ 0,05                              |

| Núcleos alta v <u>e</u><br>locidad o pelí-<br>cula delgada | primaria                                 | random               | 10 <sup>5</sup> ~10 <sup>6</sup>                 | 1 ∿ 16                 | (0,2∿2)x10                    | 6 10 <sup>7</sup> ~10 <sup>8</sup> | 0,05 ∿ 0,25                              |

### CARACTERISTICAS DE LAS MEMORIAS

| MODO DE DEI                               |                                    | — DIMENSION— RENDIMIENTO—   |                                  |                    |                                         |                                  |                        |

|-------------------------------------------|------------------------------------|-----------------------------|----------------------------------|--------------------|-----------------------------------------|----------------------------------|------------------------|

|                                           | CAPACIDAD DEL MODU- LO (bits)      | MODULOS/<br>COMPUTADOR      | TIEMPO DE<br>ACCESO<br>(Seg.)    | CAUDAL (bits/seg.) | COSTE/BIT (\$) (Soporte + trans ductor) |                                  |                        |

|                                           |                                    |                             |                                  |                    |                                         |                                  |                        |

| Circuito inte-<br>grado (scratch-<br>pad) | primaria,<br>estado pro<br>cesador | random                      | 10 <sup>3</sup> ~10 <sup>5</sup> | 1                  | <sub>~10</sub> -7                       | 10 <sup>9</sup>                  | 0,25 ∿ 1,0             |

| Circuito inte-<br>grado (asocia-<br>tiva) | primaria<br>tampón                 | por con<br>tenido<br>random | 2 x 10 <sup>5</sup>              | 1 ∿ 2              | ~10 <sup>-7</sup>                       | 10 <sup>9</sup>                  | 1.∿ 3.                 |

| Real only (capacitor, inductor)           | procesa-<br>dor                    | random                      | (1∿5) x10 <sup>5</sup>           | 1                  | 10 <sup>-6</sup> ~10 <sup>-7</sup>      | 10 <sup>8</sup> ~10 <sup>9</sup> | $10^{-3} \sim 10^{-2}$ |

que actúa a la vez como hilo de lectura y de escritura. El hilo puede tener de 2 a 5 milésimas de pulgada de diámetro recu-

bierto por una película de unas 30 micropulgadas, compuesta en un 81,5% de niquel y en un 18,5% de hierro. (Sáez, 1.975).

La organización de la memoria es del tipo 2D como se - representa en la figura.

Para almacenar una información se aplica una corriente por la fibra selectora (fibra de palabras) y al tiempo una corriente por el hilo de bi+

Leer información se consigue enviando un impulso de - corriente por la fibra de palabra, provocando con ello un giro de la magnetización del eje fácil (circular) al difícil (longitudinal). Durante el tiempo de subida del impulso de corriente, la rotación de la magnetización induce una tensión en el hilo de bit, cuya polaridad será positiva o negativa según el bit estuviera imantado en un sentido o en otro. Al no sobrepasar el campo de palabra la región de "no conmutación", normalmente un giro de 45° del momento magnético, la imantación vuelve a su estado inicial una vez desaparecido el impulso de corriente, con lo que se consigue una lectura no destructiva.

La memoria de hilo recubierto tiene numerosas interesantes características de sencillez de operación, velocidad, - bajo consumo, densidad de información, tolerancia a los ambien tes especialmente duros. Parecía que podría haber conseguido - un puesto privilegiado en el mercado y no ha sido así, lo que puede comentarse en la conferencia, como muestran las siguientes gráficas.

Tecnologías basadas en el fenómeno de las burbujas — magnéticas o en el laser no han pasado al estado de comercial $\underline{i}$  zación y las dejaremos de momento.

Hay, sin embargo, distintas funciones o refinamientos en las memorias actuales que, más o menos extendidos, empiezan a ser corrientes y con gran probabilidad se extenderán aún más. Se trata de técnicas de organización de las unidades de memoria, como la memoria asociativa, o de técnicas de utilización de ciertas memorias, como la memoria cache, la memoria virtual y por último la microprogramación.

# COSTES POR BIT

# 1956-1975

# CONSUMO MEMORIA (BITS)

1988-1916

TOTAL

NUCLEOS

HILO RECUBIERTO

SEMICONDUCTORES

### I.4.1. Memorias asociativas y aplicaciones

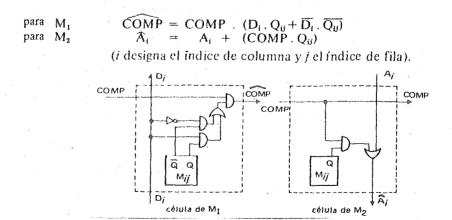

Reproducimos del libro de Meinadier la muy esquemática presentación que éste hace de la memoria asociativa, también - llamada en la literatura C.A.M. (Content Addresable Memory). Co mo podrá comprobarse, el esquema de funcionamiento corresponde a unos circuitos especializados en la operación de lectura. Sólo la lectura es asociativa. La fase de escritura se realiza de la manera corriente, R.A.M. (Random Access Memory) que no representan las próximas figuras.

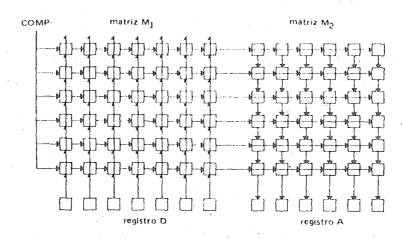

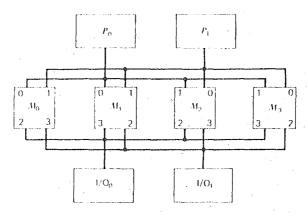

Se conciben estas memorias, también llamadas memorias direccionables por el contenido, no para buscar una informa-ción cuya dirección de almacenamiento se conoce, sino para investigar si una información, bautizada descriptor, está en la memoria y, en caso afirmativo, proporcionar una información asociada. Una memoria asociativa se divide en dos partes: una primera parte M<sub>1</sub>, en que todas las palabras son comparadas en parelelo al descriptor D, y una segunda parte M<sub>2</sub>, que entrega eventualmente a un registro la información asociada al descriptor D. La memoria asociativa se nos presenta, entonces, como la realización cableada de la estructura de informaciones llamada tabla.

A manera de ejemplo, vamos a mostrar cómo puede realizarse una memoria asociativa en lógica celular.

Las memorias  $\mathrm{M}_1$  y  $\mathrm{M}_2$  están organizadas por palabras, correspondiendo las células de una misma horizontal a los diferentes bits de una palabra y las células de una vertical a los bits de un peso determinado de las diferentes palabras. Cada célula representa un punto de memoria con un biestable y las lógicas de escritura y de comparación para la matriz  $\mathrm{M}_1$ , de escritura y de lectura para la matriz  $\mathrm{M}_2$ . Aquí nos desinteresare mos de las operaciones de escritura que permiten la carga inicial de la memoria.

La búsqueda en memoria implica la carga previa del descriptor en el registro D. A continuación, se ejecutarán todas las operaciones en paralelo con todas las palabras, bajo el efecto de un solo impulso COMP. Una célula de  $\mathrm{M}_1$  transmitirá el impulso COMP si el contenido del punto de memoria es idéntico al contenido del biestable del registro D situado en la misma vertical, y lo bloqueará en caso contrario. Si se supone que hay, como máximo, una información idéntica al descriptor en  $\mathrm{M}_1$ , se tendrá como máximo, un impulso COMP a la salida de  $\mathrm{M}_1$  que designará a la palabra de  $\mathrm{M}_2$  para enviar al registro A.

La próxima figura esquematiza una célula  $u = \frac{1}{1}$  una célula de  $M_2$ . Sus ecuaciones son las siguientes.

unos treinta dígitos) con tiempos de búsqueda del orden de 100 a 200 ns. Se utilizan las memorias asociativas para las búsque das en tabla o para ciertas transcodificaciones, en las que el factor tiempo es demasiado importante como para perderlo en - búsquedas programadas sobre tablas en memoria central.

# I.4.1.1. Memoria "Cache"

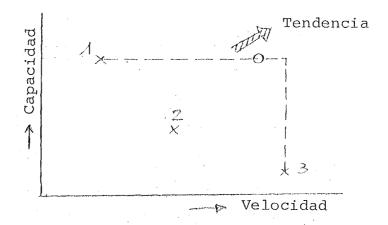

Se inscribe dentro del concepto y de las técnicas de jerarquía de memorias. Este concepto, en síntesis, viene a con siderar todas las unidades de memoria como componentes de un sistema con distintos niveles. El objetivo ideal del sistema es conseguir un conjunto que se comporte con el máximo de velo cidad y el máximo de capacidad, a un mínimo coste por bit.

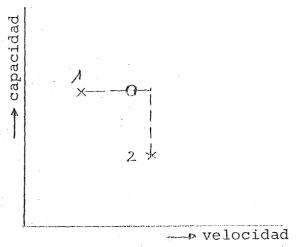

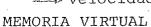

Visto en abstracto, supóngase que se cuenta con tres unidades de memoria, cuyas características de capacidad y velocidad vienen representadas por los puntos numerados 1, 2 y 3. Con ellas puede organizarse un sistema jerarquizado, cuyo comportamiento operativo en estas coordenadas equivaliera estadísticamente al circulito representado en el mismo gráfico.

La memoria Cache y la memoria Virtual son ejemplos de Jerarquía de Memorias, utilizados en principio en grandes ordenadores, transferidos cada vez más a ordenadores de tipo medio y en un plazo más o menos corto a los pequeños ordenadores. De

hecho la técnica de Memoria Cache ya ha sido utilizada en al-

La memoria cache consiste en una memoria de pequeña - capacidad de consulta asociativa y de gran velocidad (realiza-da con tecnología más rápida que la memoria principal). En esta memoria se cargan dinámicamente informaciones (instruccio-nes y datos) cuyas direcciones tienen la mayor probabilidad de ser generadas por el Procesador central. Ocurre así:

- a) El procesador central busca la dirección en la memoria asociativa. Si está allí, lee o escribe. Si no está, y se trata de una lectura, lee en memoria principal y aprovecha para cargar en memoria Cache un entor no de la información leida. Este entorno se carga en aquellas posiciones de la memoria cache que hace más tiempo no han sido utilizadas. Para ello hay un cablea do, que mantiene actualizada una tabla de uso, median te un algoritmo LRU (Least Recently Used).

- b) La operación de escribir lleva aparejado siempre la operación de escribir en la memoria principal. Existe comunicación entre Memoria cache y Memoria principal.

c) Para que el sistema sea eficiente debe haber alguna - forma de que la memoria principal pueda transferir  $v\underline{a}$  rias unidades de información de golpe.

La probabilidad de que la información necesaria esté disponible en la memoria cache depende de:

- 1°. la capacidad de la memoria cache

- 2°. la adecuación del algoritmo de sustitución de informaciones.

- 3°. la dinámica del programa en ejecución.

Un sistema cache típico consigue del 64 al 96% del - rendimiento teórico que tendría una memoria con la velocidad - de la cache y con la capacidad de la principal. Por fijar ideas, una memoria cache, la más conocida de todas, implementada en - el ordenador IBM 360/85, tenía 80 ns frente a aproximadamente 1 µs la memoria central.

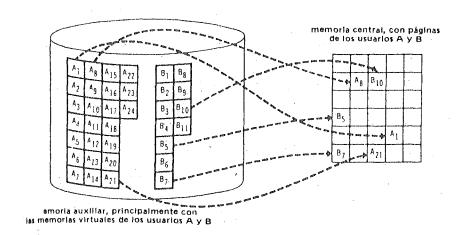

### I.4.1.2. Memoria Virtual

La memoria virtual es un compendio bastante complejo - de técnicas de hardware y software que pretenden desembarazar al programador de las limitaciones asociadas a la capacidad física de la memoria central. Para ello, sustituye el espacio - real por un espacio lógico, llamado espacio de direccionamiento, que es considerablemente mayor que el espacio real. El trabajo del sistema virtual se reduce a transformar continuamente el espacio de direccionamiento (virtual) en el espacio real de la memoria central, y viceversa.

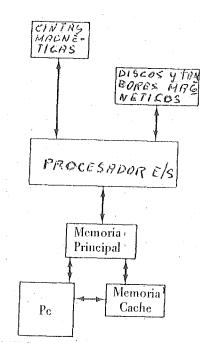

Desde el punto de vista de hardware se cuenta con dos unidades de memoria, un disco y la memoria central. A esto hay que añadir los circuitos adecuados para menejar la transformación antes citada.

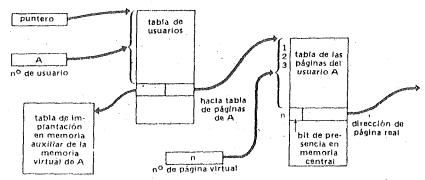

Dinámicamente, la situación que se produce es la que se representa en la figura (Meinadier).

Las memorias virtuales de los distintos usuarios, las memorias auxiliares y la memoria central son divididas en páginas de idéntica longitud (en general de 128, 256, 512 ó 1.024 palabras). Se escribe cada programa en relación con su propia memoria virtual, es decir, que todas las direcciones que contiene son relativas a su primera instrucción. Las llamaremos direcciones virtuales y, en principio, se componen de: un número de página dentro de la memoria virtual y una dirección de palabra dentro de la página. Los programas susceptibles de ser activados son implantados en la memoria auxiliar. En un determinado instante, sólo un reducido número de páginas de cada programa está presente en la memoria central.

El sistema operativo se ocupa de mantener actualizada, mediante una tabla, la correspondencia entre las páginas en me moria auxiliar y las páginas en memoria central. Dedica a cada usuario una tabla de páginas virtuales, indicando si la página ha sido cargada en memoria real y, si así es, especificando la dirección de la primera palabra de la correspondiente página - real. En el curso de la ejecución de un programa, la transformación de la dirección virtual en dirección real implicaría -

una búsqueda dentro de estas tablas, por cada acceso a memoria. Se evita tal búsqueda en virtud del dispositivo de topografía de memoria.

Tablas del sistema de explotación de un sistema paginado

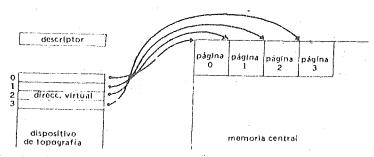

El dispositivo de topografía de la memoria central. - Es un conjunto de registros montados como memoria asociativa. En nuestro modelo, cada registro está vinculado a una página - de la memoria central y contiene dos informaciones que definen perfectamente su afectación: el número de programa dado por el sistema operativo, o, si se prefiere, el número de memoria virtual, y el número de página virtual en esta memoria.

Dispositivos de topografía de memoria

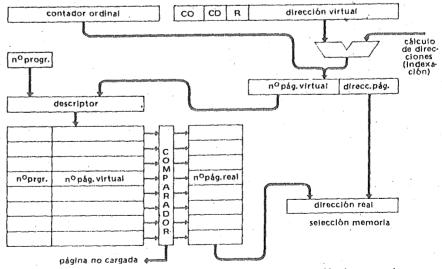

El dispositivo de topografía de memoria permite el di reccionamiento en la memoria real, sabiendo que las direcciones contenidas en las instrucciones se refieren a la memoria vir-tual del programa en curso. Las informaciones básicas para obtener la dirección son:

1) el número de programa, contenido en un registro de

la unidad central, cargado por el sistema operativo antes de ceder el control al programa.

2) la dirección virtual, conocida del programador. La dividimos lógicamente en dos partes: la dirección dentro de la página (pesos inferiores) y el número de página virtual (pesos superiores).

La yuxtaposición del número de programa y del número - de página virtual proporciona un descriptor, que es comparado - en paralelo con los contenidos de los registros asociativos.

Si se produce una coincidencia es que la página vir-tual referenciada está presente en memoria central y el número de registro asociativo da el número de la página real correspondiente. Si, por el contrario, no hubiera coincidencia entre el descriptor y el contenido de uno de los registros asociativos, es que la página de referencia no ha sido cargada en la memoria central. En este último caso, se producirá una desviación hacia el sistema operativo, que cargará la página y actualizará el registro asociativo pertinente.

Princípio de utilización de un dispositivo de topografía de memoria para el direccionamiento en un contexto paginado

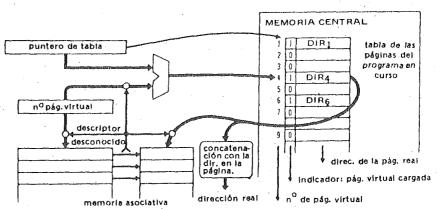

En la práctica no es posible normalmente contar con - una memoria asociativa que recoja la topografía completa de la memoria central. Se dispone entonces de un sistema incompleto que, lógicamente, es menos rápido.

Búsqueda automática de la dirección en memoria cuando la dirección de página virtual no se halla en memoria topográfica

De manera similar a la memoria cache, se emplean ciertos algoritmos para decidir qué páginas de memoria van a ser - sustituidas.

Si recogemos la descripción realizada y la comparamos con la memoria cache, podremos establecer diferencias de objetivos que, a simple vista, no resaltan fácilmente. La organización con la memoria cache es una jerarquía de memorias cuyo objetivo particular es acelerar la velocidad de la memoria central sin modificar el trabajo del programador.

La organización con la memoria virtual es una jerarquía de memorias cuyo objetivo particular es ampliar la capacidad de la memoria central sin modificar el trabajo del programador.

- 1. Disco

- 2. M. central

- 0. Resultante

### MEMORIA CACHE

- 2. M. central

- 3. M. asociativa (cache, buffer).

- 0. Resultante.

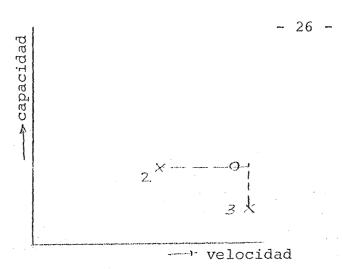

### I.4.2. Microprogramación

La microprogramación es básicamente una técnica de diseño de unidades de control, a cualquier nivel. Si se introduce en el apartado de memorias es porque su materialización práctica es sobre soporte de memoria, y en una mayoría de casos, so-bre memoria ROM.

Como el asistente a la conferencia ya conoce este tipo de memoria y su utilización en el terreno de los microprocesado res, sólo haremos aquí unas reflexiones acerca de la incidencia de la microprogramación en el diseño de las unidades secuenciadoras de microfrdenes.

Al secuenciador llegan informaciones, directamente procedentes de los campos de condiciones de direccionamiento del registro de instrucción o a través del decodificador de instrucciones, del distribuidor de fases, del reloj interno y de ciertos biestables de estado, y con ellas genera automáticamente se cuencias de señales, llamadas microórdenes, que se desparraman

y actúan sobre cada uno de los elementos de la ruta de datos.

El secuenciador, cuyas ecuaciones lógicas se calculan, es un autómata de múltiples salidas, normalmente una sola en-trada activa y un conjunto de estados representativos de la circunstancia real de la máquina. Produce un microprograma.

microprograma = secuencia de microórdenes/instrucción

microorden = f (instrucción, estado).

La microprogramación consiste en reemplazar el secuenciador cableado por un secuenciador programado, residente en una memoria especial, llamada memoria de control, que normalmente es accesible sólo en lectura (R.O.M.). Es ésta la aplicación más corriente de la técnica de microprogramación y fue propuesta por Wilkes en el año 1.951, en un modelo cuya finalidad principal era la de sistematizar y simplificar los procedimientos de diseño de la unidad central de control.

El código de operación de una instrucción cualquiera es interpretado como la dirección de una posición precisa de - la memoria de control, que contiene una microinstrucción. Se - llama microinstrucción porque está registrada en una memoria y porque forma parte de un conjunto asociado a la particular instrucción mencionada, conjunto denominado microprograma. Una mi

croinstrucción consta de un código, que da directamente las microfrdenes a distribuir al conjunto del ordenador, y de los ele mentos de información necesarios al desarrollo del resto de las microinstrucciones del mismo microprograma (normalmente la dirección de la próxima microinstrucción).

"La microprogramación es análoga a la programación con vencional. El programador le dice al sistema o al dispositivo - lo que tiene que hacer por medio de instrucciones en la memoria central. El microprogramador le dice cómo lo tiene que hacer, - controlando qué elementos lógicos y de memoria deben usarse y - cómo para cada operación. Así, la instrucción de máquina, que - para el programador representaba el nivel más profundo de comunicación con el sistema, puede contemplarse ahora como una subrutina cerrada desglosable en secuencia de funciones más elementa les llamadas microinstrucciones" (Husson, 1.970).

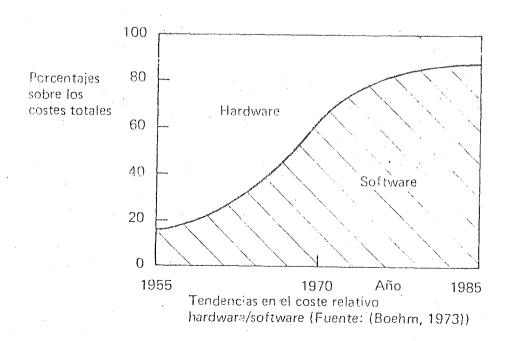

Es evidente que la microprogramación plantea de forma llamativa lo convencional de la línea divisoria entre los dominios del hardware y del software. Pero esta técnica está contri buyendo, además, a la gestación de un enfoque distinto en la concepción de los ordenadores. La concepción de los ordenadores se ha iniciado siempre de abajo arriba, o sea, el circuito se ha hecho algoritmo, por expresarlo de manera metafórica. En tér minos generales, se ha ido del hardware al software. Sin embargo, la verdadera esencia de los ordenadores es el software, nivel todavía sin formular. Por ello, es de esperar que la concep ción futura se llevará de arriba abajo, o sea, el algoritmo se hará circuito. Esta es nuestra interpretación personal de los esfuerzos emprendidos para formular lenguajes y compiladores de hardware. En este mismo sentido, la microprogramación pone de manifiesto la auténtica naturaleza algorítmica de las operaciones de control, más parecida en su estructura a la programación que al tradicional enfoque tomado en préstamo de los dos subniveles inferiores de diseño lógico.

Las aplicaciones actuales y las que se preven para un futuro inmediato son muchas y variadas. Husson las clasifica - en las siguientes categorías:

- 1. Diseño de un control eficaz para una arquitectura bien especificada de un sistema. Se basa en que ya no es cierto, que, microscópicamente, cada instrucción sea un estímulo que provoque necesariamente en el ordenador siempre la misma respuesta, ya que, de un diseño a otro -dentro de la misma arquitectura- es posible cambiar fácilmente el microprograma.

- 2. Modificación de una arquitectura existente, con o sin modificaciones del flujo de datos existente. (se refiere a los conceptos de repertorio de instrucciones a la medida o de extensibilidad del mismo a gusto del consumidor. El ordenador universal es un hecho, pero una arquitectura universal no es una arquitectura óptima para muchas clases de aplicacio-nes).

- 3. Emulación de algunas estructuras de hardware. (Se refiere a dotar a algún sistema de la capacidad de interpretar y ejecutar otras arquitecturas o lenguajes de alto nivel).

- 4. Integración del hardware y de diferentes niveles de software. (Se refiere al firmware).

- 5. Aplicaciones especializadas.

Según Dolotta y otros autores, que han hecho un estu-dio prospectivo del Procesamiento de Datos para el quinquenio - de 1.980-85, el trinomio hardware/firmware/software evolucionará así:

"Existe una tendencia clara hacia un uso progresivamente creciente del firmware (microprogramación) para instrumentar funciones que antes eran cableadas o, en ciertos casos,

realizadas por software. Así la complejidad de la lógica cableada es aún creciente, pero no tan deprisa como la del lengua

je de máquina, que es contemplado por el software; éste está haciéndose más y más sofisticado y de mayor nivel . Se

espera que cada vez más funciones implementadas por software ·

hasta ahora lo sean en adelante por microcódigo (p. ej. partes

de paginación, acceso de datos, mecanismos de interrupción, in

térpretes de lenguajes de alto nivel, etc.).

Debemos subrayar sin embargo, que no hay magia en el firmware. Participa de muchos de los problemas del hard y del soft, aunque tenga muchas y variadas ventajas propias: es más fácil de modificar (pero es más lento) que el hard, y más rápido (pero más difícil de modificar) que el soft. Añade flexibilidad a la tarea del diseño y por ello se ha convertido en -- otra herramienta para el diseñador de computadores. Programas implementados por firmware no son inherentemente más fiables - que sus contrapartidas en soft. Especialmente, el advenimiento del firmware "escribible" ha eliminado parte del incentivo de hacer programas muy bien depurados.

"Pensamos que se usará más cada vez el firmware pero que, en la mayoría de los casos, los usuarios tendrán poco -si es que tienen alguno-, acceso a él a causa de los fuertes incon venientes derivados de los problemas de fiabilidad y manteni- - miento asociados a dicho acceso".

- I.5. Proposiciones de Sáez (1.973) sobre condiciones de viabilidad de innovaciones en técnica o tecnología.

- 1ª. Toda innovación en estructura es posible gracias

a un avance <u>tecnológico</u> que, puesto al servicio de una <u>idea</u> o de una <u>necesidad</u>, se justifica técnicamente si la mejora producida en algún factor de <u>rendimiento</u> es muy superior relativa--mente al aumento de coste del sistema.

2<sup>a</sup>. Una técnica o una tecnología es, o debe ser, introducida a nivel industrial cuando viene a cubrir una necesidad o produce sustanciales mejoras de rendimiento, siempre que no atente contra las inversiones\* de la comunidad de constructores-usuarios.

Aplicar en discusión a los siguientes temas:

- Memoria Cache.

- Topografía Memoria, en Memoria Virtual

- Memoria película delgada NDRO

- Microprogramación

- Minicomputadores

- Microprocesadores y microordenadores

#### I.6. Arquitecturas de ordenador

Se experimenta hoy día una tendencia, cada vez más acu

<sup>\*</sup> Por "inversión" debe entenderse no sólo la puramente financie ra, sino la inversión en trabajo, en formación, en ideas, en mo lestias, en tiempo, en modificaciones de organización, etc. y - al decir "atentar contra" no se quiere significar inmovilismo - sino dosificación de los cambios para que éstos sean absorbidos por un sistema cuya estructura y relaciones tienden a un equilibrio dinámico, con un crecimiento sostenido.

sada, hacia una polarización hacia el uso de grandes y pequeños sistemas en el mundo de la informática. Esto es cierto por

lo que se refiere a ordenadores convencionales. Pero también lo es en lo concerniente a ordenadores no convencionales. De es

tos podemos distinguir a los que tienen características peculiares, como los sistemas multiprocesadores y paralelos, como

la gama de minis y micros que, en lo referente a su estructura

han sido tratados en conferencias anteriores, y como la clase

de sistemas especiales cuya estructura no refleja los esquemas

de Von Neumann.

Por ser menos conocidos, recogeremos con alguna mayor extensión, aunque un tanto superficialmente, las arquitecturas de los sistemas multiprocesadores y paralelos, siguiendo el libro de Enslow.

### I.6.1. Sistemas multiprocesadores y paralelos

La tabla siguiente lista una cronología resumida de - estos sistemas. (Ver pág. 33 y siguientes).

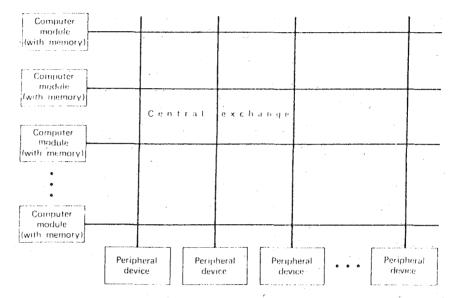

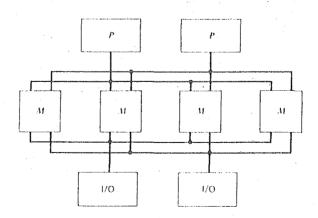

La definición que da Enslow de un sistema multiprocesador es ésta; un sistema con:

Dos o más unidades de procesamiento

Memoria compartida.

E/S compartida.

Sistema Operativo único integrado.

Interacción del hardware y del software a todos los - niveles.

Es de destacar que gran parte de estos sistemas han - sido diseñados para aplicaciones de tipo más bien poco corriente en los terrenos nuclear, meteorológico, espacial, de teleco

| Date         | System Manufacturer and Model Number                                                                                           | Remarks                                                                                                                                                                                                                                                                                              |

|--------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1958         | National Bureau of<br>Standards<br>PILOT                                                                                       | Three independently operating computer that could work in cooperation.                                                                                                                                                                                                                               |

| 1958 (circo) | IBM, AN/FSQ-31<br>and 32                                                                                                       | Solid-state SAGE computer; not mult processors; merely duplexed systems.                                                                                                                                                                                                                             |

| 1960         | Ramo Wooldridge<br>TRW-400                                                                                                     | "Polymorphic system"; for USAF comman<br>and control. Some construction done<br>not completed. Important for earl<br>concepts.                                                                                                                                                                       |

| May 1960     | UNIVAC LARC                                                                                                                    | One I/O processor and one computed tional processor capable of operating in parallel. One delivered to Livermor AEC Laboratories. Not a "true" multiprocessor.                                                                                                                                       |

| May 1961     | IBM Stretch(7030)                                                                                                              | Original design called for separate character-oriented processor and bin ary arithmetic processor. These were dropped from final design; therefore final product was not a multiprocessor It did contain look-ahead. Only sever delivered.                                                           |

| Nov. 1962    | Burroughs, D-825 (This system carried various military model designations depending on the major system of which it was part.) | memory modules, 10 I/O controllers and 64 devices. Important feature was one of the earliest examples of a modern operating system—the Automatic Operating and Scheduling Program (ASOP).                                                                                                            |

| Feb. 1963    | Burroughs B-5000                                                                                                               | One or two processors. Up to eight mem ory modules. Programs independent of addresses. Supervisor was the Master Control Program (MCP). Utilized virtual memory concepts and hardware Machine code based on Polish notation. Users programmed only in ALGC or COBOL. Became the B-5500 in Nov. 1964. |

|              |                                                                                                                                | Nov. 1964.                                                                                                                                                                                                                                                                                           |

| Date                           | System Manufacture and Model Number             |                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1963                           | IBM 704X/709X<br>(7040 or 44 and<br>7090 or 94) | "Direct Coupled System"                                                                                                                                                                                                                                                                                                                                 |

| 1963                           | Bendix G-21<br>(later CDC)                      | A multiprocessor version of the G-20 developed for Carnegie Institute of Technology. A crossbar system.                                                                                                                                                                                                                                                 |

| Sep. 1964                      | CDC 6600                                        | Contained multiple arithmetic and logic units each of which can execute only a small fraction of the total instruction repetoire. Ten peripheral processors were an integral part of the system. (Number of PPU's increased to 20 in 1969.) The PPU's do constitute a multiprocessor system. Overall system an example of an asymmetric multiprocessor. |

| Nov. 1964                      | Burroughs B-5500                                | An upgrade of the B-5000 (see Feb. 1963).                                                                                                                                                                                                                                                                                                               |

| 1964                           | GE 645 (now<br>Honeywell)                       | Ordered by Project MAC at MIT.                                                                                                                                                                                                                                                                                                                          |

| May 1965                       | GE 645 (now<br>HIS-645)                         | Delivered to Project MAC at MIT. Hard-<br>ware not a standard product; however<br>MULTICS operating system is being re-<br>leased.                                                                                                                                                                                                                      |

| Ded. 1965<br>1965              | UNIVAC 1108<br>SOLOMON 1                        | Design only. First large-scale array processor.                                                                                                                                                                                                                                                                                                         |

| Mar. 1966                      | IBM S/360 Model<br>67                           | Special dual-processor time-sharing system.                                                                                                                                                                                                                                                                                                             |

| Apr. 1966<br>Dec. 1966<br>1966 | CDC 6500<br>XDS Sigma 7<br>SOLOMON II           | Dual 6400's Design only.                                                                                                                                                                                                                                                                                                                                |

| lun. 1967<br>Aug. 1967<br>1968 | CDC 6700<br>XDS Sigma 5<br>CDC 7600             | Very similar to 6600, but higher speed and included hierarchy of main memory as standard feature.                                                                                                                                                                                                                                                       |

| Apr. 1969                      | IBM S/360 Model<br>65 MP                        | Dual-processor version of standard model 65. A true multiprocessor.                                                                                                                                                                                                                                                                                     |

| un. 1970                       | XDS Sigma 6                                     | •                                                                                                                                                                                                                                                                                                                                                       |

| Date                       | System Manufacture and Model Number                    |                                                                                                                          |  |  |

|----------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| Oct. 1970 Burroughs B-5700 |                                                        | Similar to B-5500 with capability for increased memory. Capability for four B-5700 systems to share disk storage.        |  |  |

| Feb. 1971                  | Honeywell 6050,<br>6060, 6080                          | 2 10 27 20 20 20 20 20 20 20 20 20 20 20 20 20                                                                           |  |  |

| Jun. 1971                  | Burroughs B-6700                                       |                                                                                                                          |  |  |

| Sep. 1971                  | Digital Equipment<br>System 10/1055,<br>10/1077        |                                                                                                                          |  |  |

| Sep. 1971                  | XDS Sigma 8, 9                                         |                                                                                                                          |  |  |

| Nov. 1971                  | UNIVAC 1110                                            |                                                                                                                          |  |  |

| 1971                       | SDC, PEPE (Parallel<br>Element Processing<br>Ensemble) | Prototype for processing of radar data for ballistic missile defense system.                                             |  |  |

| Jan. 1972                  | Honeywell 2088                                         |                                                                                                                          |  |  |

| Sep. 1972                  | ILLIAĆ IV                                              | Array processor. 64 processor elements.  Driven, by a conventional multiprocessor used as a front-end control processor. |  |  |

| Feb. 1972                  | Burroughs B-7700                                       |                                                                                                                          |  |  |

| 1972                       | CDC, Cyber 72, 73,<br>74, 76                           |                                                                                                                          |  |  |

| 1972                       | Goodyear STARAN                                        | Parallel associative system.                                                                                             |  |  |

| 1972                       | Texas Instruments ASC (Advanced Scientific Computer)   | Embodies both multiprocessing and pipe-<br>lining.                                                                       |  |  |

| 1973                       | CDC STAR-100                                           | Pipeline system.                                                                                                         |  |  |

| 1974                       | IBM S/370, Models<br>158 MP & 168<br>MP                | Shared real and virtual storage                                                                                          |  |  |

# municación, etc.

Se clasifican en siete clases:

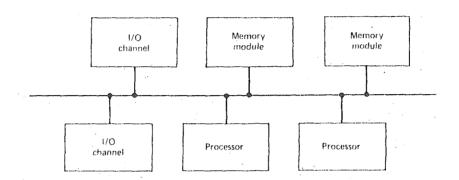

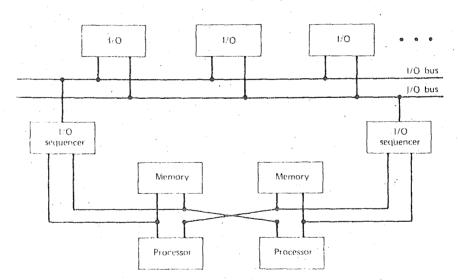

- . De bus común o en tiempo compartido.

- . Crossbar.

- . De bus múltiple/multipuerta

- . Asimétricos o no-homogéneos

- . Procesador de vectores u ordenaciones

- . Procesador pipe-line

#### . Sistemas antifallo.

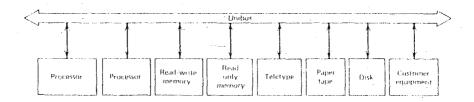

La próxima figura presenta un esquema funcional de la primera clase, en donde todos los módulos se conectan en paralelo al bus. El bus puede ser bidireccional o estar dividido - en dos buses unidireccionales con un modificador de bits. Es -

posible contar con más de un bus bidireccional, como muestra - la siguiente figura.

La vencuja de estes sistemas es la simplicidad de su control, que se paga con su bajo grado de paralelismo (práctica mente sólo una transferencia a la vez), sus posiblemente largos tiempos de respuesta, la pequeña fiabilidad en función de un fallo en el bus.

Un ejemplo clásico y bien conocido es el PDP-11 con su

sistema Unibus.

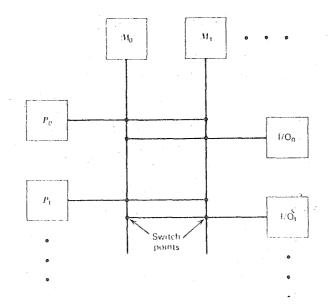

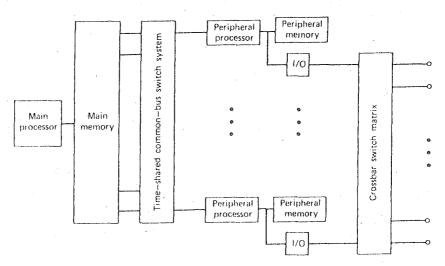

En las estructuras tipo conmutación crossbar cualquier módulo de memoria puede conectarse a cualquier procesador o unidad de E/S. Se establece una conexión real permanente entre dos unidades por toda la duración de la transferencia, de manera que se sigue el método de división en el espacio.

La matriz crossbar o matriz de conmutación puede lle-gar a ser muy complicada. El H4400 (ocho procesadores centrales o de E/S y 16 módulos de memoria) contiene circuitos y componentes equivalentes a 2,5 procesadores.

Es posible utilizar una matriz de conmutación separada para controlar la conexión de las unidades periféricas con las

unidades de E/S.

Crossbar switch system organization with separate I/O crossbar switch matrix.

Según la nomenclatura de Bell/Newell ésta es una estru $\underline{c}$ tura en celosía, representada así en su ya citado libro

Uno de los primeros multiprocesadores, importante por - los conceptos estructurales que incorporó, fué el TRW-400 o com putador polimórfico, que posee una sola matriz de conmutación a

los cuales se conectan computadores completos y dispositivos periféricos.

Ramo-Wooldridge, RW-400 system—the "Polymorphic Computer."

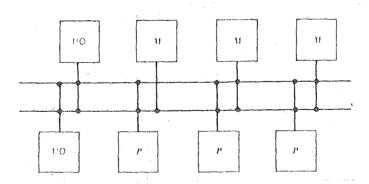

Los <u>sistemas multibus/multipuerta</u> proporcionan también más de una vía de transferencia simultánea, aunque, para ello - es esencial que los módulos de memoria tengan más de una puerta de acceso y los circuitos adecuados para resolver los conflictos que ocurren si dos o más procesadores o unidades de E/S solicitasen acceso.

Multiport-memory/multibus system organization, basic form.

Lo que suele hacerse es asociar una prioridad a cada puerta y punto de conexión, así en caso de conflicto se da preferencia de acceso, por ejemplo, al procesador asociado a su módulo primario de memoria.

ssignment of memory access priorities-multiport system organization.

Ejemplos de estructuras de esta naturaleza los tenemos en las series Univac 1100 y Honeywell 600 6 6000, en el CDC - - 3600, XDS- Sigma 7 e IBM 360 modelo 67.

La figura siguiente, que esquematiza al CDC 6600 es un ejemplo de sistema asimétrico, que es aquel que tiene componentes de un mismo tipo muy diferenciados: procesadores, módulos de memoria, etc.

Example of asymmetrical/nonhomogeneous system organization—CDC 6600.

Este sistema concreto cuenta con procesadores periféricos (PP) cuya memoria llega hasta 4 K con palabras de 12 bits. Se ocupan de las tareas de contabilidad, control de jobs y operaciones de E/S. Uno de los PP's se ocupa de la consola principal del sistema y otro actúa de monitor de todo el conjunto asignando tareas, tanto al procesador principal como a los demás PP's.

La técnica de los <u>ordenadores pipe-line</u> se basa en la repetición de la misma operación sobre varios items de una sola corriente de datos. El ejemplo típico es el de la suma de dos números representados en coma flotante. Esta es una operación que puede realizarse en cinco etapas:

- 1. Normalización de los números y ajuste de sus exponentes.

- 2. Comparación de exponentes.

- 3. Desplazamiento de la característica del número de menor exponente para alinearlo con el de mayor exponente.

- 4. Suma de las características

- 5. Normalización de resultados.

Supongamos que los tiempos para realizar cada una de estas etapas son:

En una máquina pipe-line cada paso será ejecutado por unos circuitos propios y el resultado transferido a los siguien tes circuitos, insertándose nuevos números en los circuitos que

han culminado su trabajo

| Tiempo |                               |                               |                               |                               |                               |                                   |

|--------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------------------|

| Paso 1 | a <sub>1</sub> b <sub>1</sub> | a <sub>2</sub> b <sub>2</sub> | a <sub>3</sub> b <sub>3</sub> | a <sub>4</sub> b <sub>4</sub> | a <sub>5</sub> b <sub>5</sub> | a <sub>i+4</sub> b <sub>i+4</sub> |

| Paso 2 |                               | a <sub>1</sub> b <sub>1</sub> | a <sub>2</sub> b <sub>2</sub> | <sup>a</sup> 3 <sup>b</sup> 3 | a <sub>4</sub> b <sub>4</sub> | a <sub>i+3</sub> b <sub>i+3</sub> |

| Paso 3 |                               |                               | a <sub>1</sub> b <sub>1</sub> | a <sub>2</sub> b <sub>2</sub> | a <sub>3</sub> b <sub>3</sub> | a <sub>i+2</sub> b <sub>i+2</sub> |

| Paso 4 |                               |                               | •                             | c <sub>1</sub>                | c <sub>2</sub>                | c <sub>i+1</sub>                  |

| Paso 5 | 1er.                          | resulta                       | do                            |                               | → <sup>C</sup> 1              | c                                 |

Supongamos que se ajusta el reloj para sincronizar los pasos a 120 ns para dar tiempo al paso 4. Entonces, el primer - resultado se tiene a los 5 x 120 = 600 ns, en lugar de a los - 480 ns. Pero cada nuevo resultado se tiene a los 120 ns del anterior.

Máquinas que encajen dentro de esta categoría pueden - citarse a IBM 360/91, CDC 7600, CDC STAR-100 y Texas Instruments Advanced Scientific Computer (ASC).

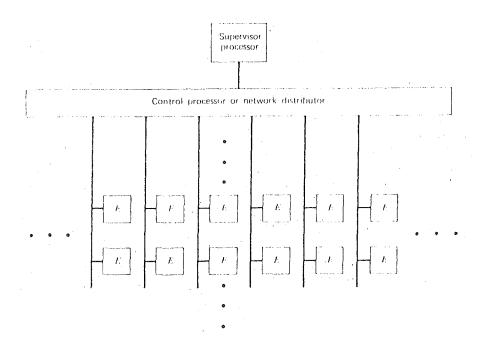

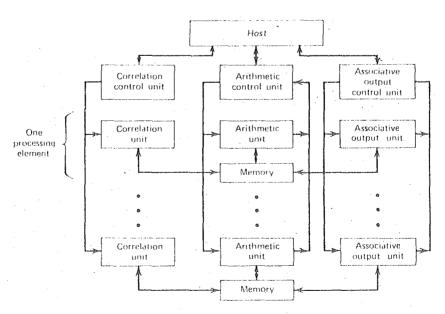

La característica más notable de los <u>ordenadores de</u> <u>procesamiento de vectores</u> es que la misma operación ha de ser - ejecutada sobre una amplia colección de elementos relacionados de alguna manera y que a menudo es posible que esta operación - sea ejecutada sobre todos los elementos a la vez. Vease la configuración básica de uno de estos sistemas. (Páq. 43).

Una configuración así corresponde a un sistema paralelo no multiprocesador, ya que los elementos de procesamiento E no son capaces de operar independientemente.

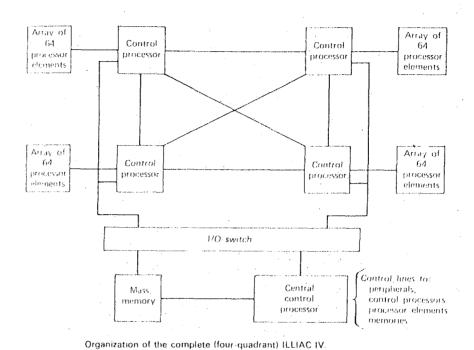

El ejemplar más conocido de esta categoría es el ILLIAC IV sucesor de los sistemas SOLOMON. Consta de 256 elementos de procesamiento (PE) organizados en cuatro cuadrantes de 64 (orde

Array processor—basic configuration, Note: Each E is an execution or processing element which has most of the capabilities of a stand-alone CPU plus its own private memory

nación 8 x8) con una unidad de control para cada cuadrante. Cada PE tiene una importante memoria propia, acceso directo a un conmutador de E/S y comunicación por cuatro vías con sus PE vecinos. El ordenador de control es un Burroughs B6700, que ejecuta programas ejecutivos y compilación.

El ILLIAC IV puede invertir una matriz de 700 x 700, - adecuadamente preparada, en 1 segundo.

El mayor problema con este tipo de máquina es la preparación de programas que puedan explotar sus capacidades y el desarrollo de traductores que puedan analizar automáticamente programas y producir código para su ejecución en paralelo.

Para terminar con esta categoría citemos el sistema PE PE, (Parallel Ensemble of Processing Elements) desarrollado por entidades tan importantes como los Bell Telephone Laboratories,

la System Development Corporation y Honeywell, y destinado al procesamiento de informaciones radar en un sistema de defensa con misiles de la U.S.Army.

PEPE system organization.

Puede uno hacerse idea del orden de magnitud del sistema cuando se sabe que el control del mismo recae sobre un ordenador (host) CDC 7600.

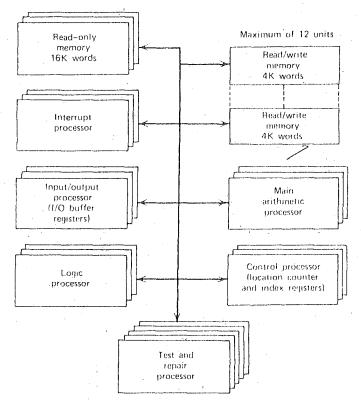

Los sistemas antifallo se llaman así porque están especialmente diseñados y organizados como sistemas para detectar, localizar y minimizar los fallos y sus efectos. Por ejemplo, en el sistema MIT/IL SIRU sus dos procesadores trabajan sobre el mismo problema, ejecutando la misma corriente de instrucciones y la misma corriente de datos síncronamente. Sólo un procesador está "activo" en el sentido de generar órdenes de "escritura". Ambas memorias poseen idéntico contenido, ya que responden a las órdenes de escritura; pero solamente una responde a las peticiones de lectura. El sistema de interconexión está diseñado para permitir un chequeo continuo de la certeza de los distin-

Fault tolerant design -- MIT/IL SIRU computer

tos módulos e inmediata reconfiguración. El sistema JPL STAR - (Self-Testing and Repair) conmuta un módulo en fallo por otro, pero no es un multiprocesador. Su finalidad es lógica y redundante.

JPL STAR system organization [Weitzman].

#### I.6.2. Sistemas minis y micros

Los miniordenadores surgen como consecuencia de varios factores que coinciden en un momento dado. En primer lugar, el impulso arrebatador de la tecnología electrónica. Se juntan a - esto la necesidad de atacar aplicaciones especializadas, para - las que los sistemas que pudieramos llamar convencionales eran demasiado caros o sobreabundantes, y la inercia natural de lo que hemos llamado comunidad de constructores-usuarios.

Todo esto explica que los grandes constructores de ordenadores ha sido pionero en la rama de los minis. Estos han sido, además un campo de experimentación de tecnología (R.O.M., - memoria central con Circuitos Integrados, circuitos LSI en el -

procesador, etc...) y la puerta de entrada de muchas industrias de electrónica en el mercado de ordenadores.

# I.6.2.1. Estructura-robot y aplicaciones de los - minis.

Hay como un retrato-robot de miniordenador (nos referimos sólo a los minis científicos o industriales), que es el siguiente:

16 bits, longitud de información palabra-dato en coma fija aritmética paralela

datos negativos en complemento a dos

direccionamiento por paginación (página cero y corriente), indexación e indirección

instrucciones de referencia a memoria de una sola di-rección

repertorio de 70 o más instrucciones memoria máxima entre 32 y 64 k palabras ciclo base, alrededor de 1 microsegundo

tecnología en parte o totalmente MSI, incluyendo a veces a la memoria.

interrupción de programa a varios niveles (muchas veces, hasta 64), reloj de tiempo real y acceso directo a memoria; macroensamblador, compilador Fortran, frecuentemente Intérprete de Basic

sistema operativo elemental

bajo precio < 20.000 \$

pequeño tamaño, normalmente de sobremesa

desnudez en cuanto a periféricos propios

El miniordenador es, pues, el resultante de un proceso de diferenciación de los ordenadores que ha producido no pocas variantes, estabilizándose hacia 1.970 mas o menos en torno a una estructura y características, como las listadas en el retrato robot. La estabilización se produce como consecuencia de un proceso de integración.

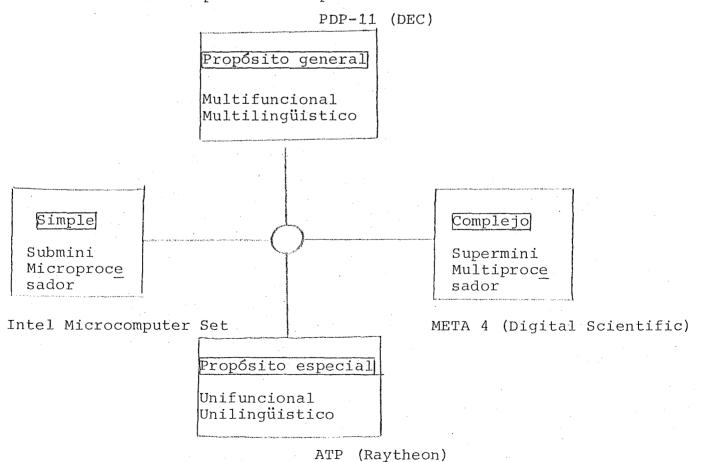

Mas a un proceso de integración sigue uno de diferenciación, y así sucesivamente. Partiendo del miniordenador tipo se ha producido, según Koudela 1.973, una diferenciación de los minis en cuatro direcciones principales, que representa el esquema siguiente.

Los que llamaríamos de "propósito general" y "complejo" llegan a no distinguirse de los ordenadores del tronco básico más que en su pequeña longitud de información y en la esca sa dotación de periferia específica.

Koudela clasifica las aplicaciones de los minis en cua tro amplias categorías de

- a) sólo procesamiento

- b) adquisición y procesamiento

- c) adquisición, procesamiento y control

- d) multiprocesamiento

La 2<sup>a</sup>. y 3<sup>a</sup>. categoría implican la existencia de fuentes exteriores de medida o señalización de las que el ordenador adquiere automáticamente datos. En la 3<sup>a</sup>. se realiza también el control de dichas fuentes en base al procesamiento de los datos de ella adquiridos.

En cuanto a la 1 $^a$ . categoría, en ella entran básicamen te las aplicaciones científicas.

En la 2<sup>a</sup>. incluimos todas aquellas relacionadas con - las comunicaciones:

- realizar interfaces entre entradas diferentes y una sola instalación de comunicaciones.

- empaquetar o desempaquetar caracteres

- localizar errores en los datos

- sincronizar datos asíncronos

- formatar

- transcodificar

- multiplicar muchos terminales de baja velocidad so-bre una línea de alta

- coordinar las entradas de comunicaciones en los grandes ordenadores.

En la última categoría debemos mencionar el proyecto - de la Universidad Carnegie Mellon llamado Ordenador Multimini--

procesador que, basado en el PDP-11, se propone estudiar los s $\underline{i}$  guientes tipos de problemas:

Procesamiento paralelo.

Procesamiento pipe-line

Procesamiento en red

Procesamiento especializados

Multiprogramación convencional con multiprocesadores.

Computadorización individualizada.

La siguiente figura presenta la estructura general de este sistema (Bell, Chen, Rege, 1.972). Este sistema podíamos

haberlo encuadrado en el apartado I.6.1., pero su origen le si túa mucho mejor en relación con el movimiento de los minis.

Volviendo a la diferenciación mencionada que se produce en la rama de los minis, recordemos la que hace referencia a los micros. Aquí se produce un nuevo núcleo que puede llegar a ser centro de una nueva integración. Puede contribuir a ello, entre otros factores, un movimiento de pensamiento de aplicación de la informática que se llama micro-informática o informática repartida (o destribuida).

En conferencia anterior se ha presentado con gran minuciosidad la estructura, funcionamiento y programación de los microprocesadores. Añadamos aquí algunos datos curiosos o interesantes relativos a esa nueva tecnología, que se comentarán.

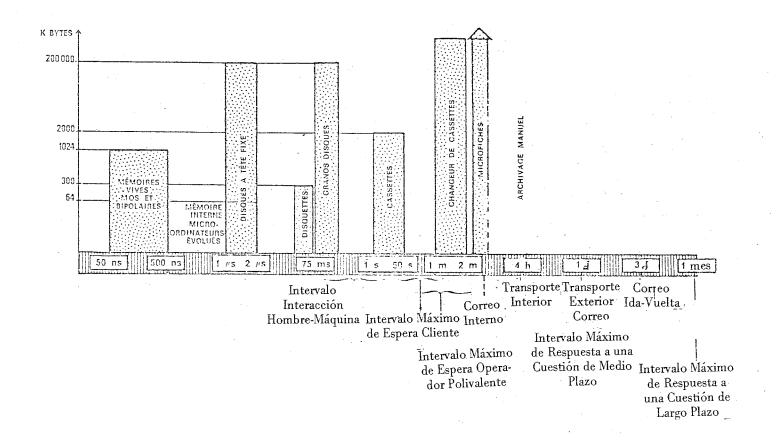

En primer lugar, una figura que representa el tiempo de respuesta y la capacidad de algunas memorias, entre las que se contabilizan algunas típicas de la informática distribuida.

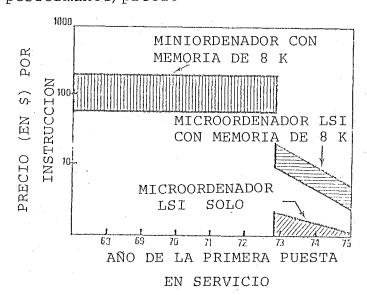

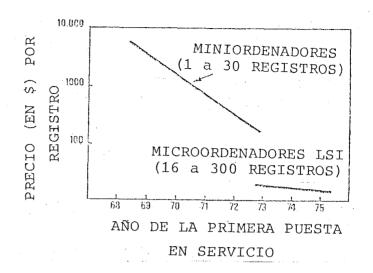

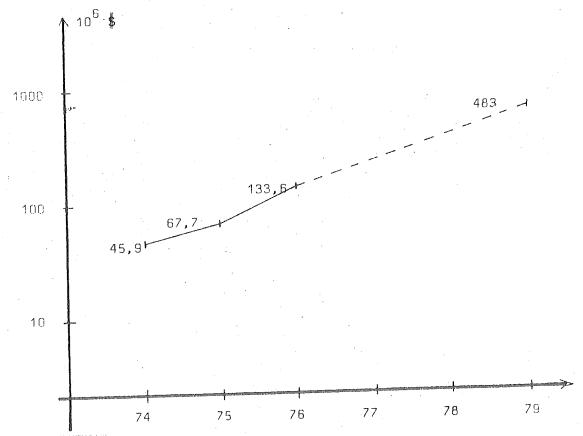

Los siguientes gráficos presentan, respectivamente, - los ratios (Lussato et al.):

- precio/instrucción

- precio/registro

- performance/precio

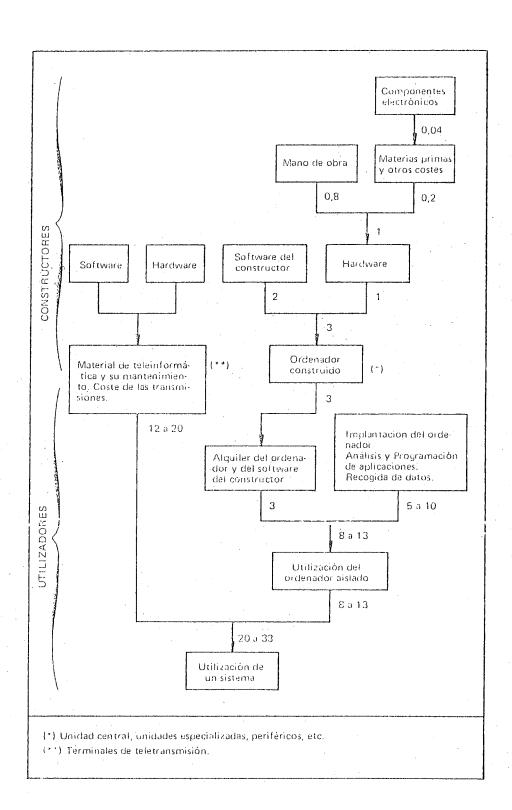

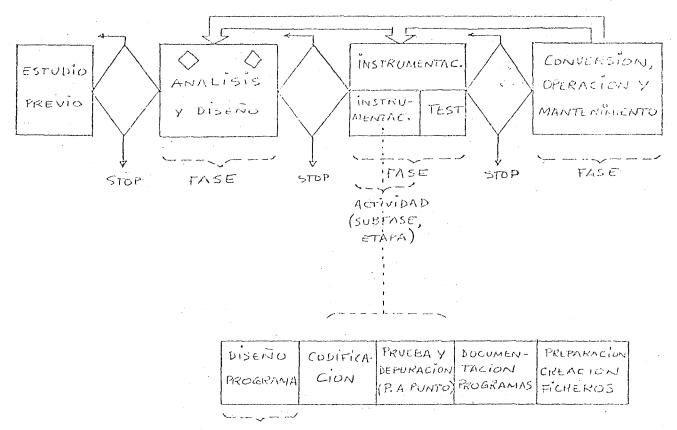

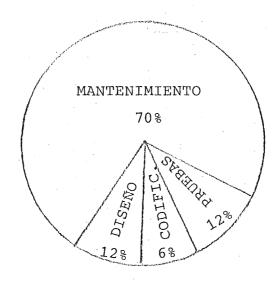

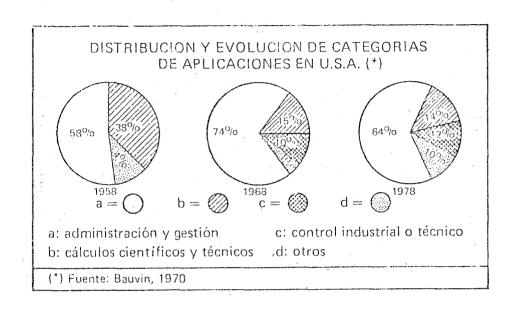

Tiempo de Respuesta Respecto a la Capacidad de la Memoria Prevista