### Máster en Ingeniería de Sistemas y Servicios para la Sociedad de la Información

| Trabajo Fin de Máster |          |      |

|-----------------------|----------|------|

| Título                |          |      |

| Autor                 |          | V°B° |

| Tutor                 |          |      |

| Ponente               |          |      |

|                       | Tribunal |      |

| Presidente            |          |      |

| Secretario            |          |      |

| Vocal                 |          |      |

|                       |          |      |

| Fecha de lectura      |          |      |

| Calificación          |          |      |

El Secretario:

## Universidad Politécnica de Madrid Escuela Universitaria de Ingeniería Técnica de Telecomunicación

#### TRABAJO FIN DE MÁSTER

Máster en Ingeniería de Sistemas y Servicios para la Sociedad de la Información

Energy/Power Consumption Model for an Embedded Processor Board

Rong Ren Julio de 2012

"世界不会在意俗的自尊,人们看的只是你的成就。 在你没有成就以前,切勿过分强调自尊。" ——此尔盖茨 The world won't care about your self-esteem.

The world will expect you to accomplish something BEFORE you feel good

about yourself.

——Bill Gates

#### Acknowledgements

I have been in this beautiful city almost two years. This is the first time I have left home such a long time; this is the first time I need to take care of everything by myself; this is the first time I have realized the world is so different. There are countless firsts; however, the most important one is, this is the first time I need to be responsible of my promise.

From the very beginning after I arrived Madrid, I was infected by the enthusiasms of Spanish people, no matter in the work or in the life. I am living here each day to the fullest. I have been enjoying the time here with sunshine, objective and progress. But everyone has roses and thorns in the life.

Last September, I started my research topic here. I feel that I am a little fish who is swimming in the boundless ocean. I often felt perplexed to the thousands paper which have the same key words; I often felt disappointed to my practice results; I often felt doubtful to my decision of continuing study. However, now, the time I am writing this thesis, one stage of my four-year is coming to be finished. Look back to the last two years, my heart is filled with joys and appreciations.

I would like to thank my family. They brought me to this world, and are supporting me on everything, in every minute. No matter how I exactly am, they always give me the confidence. My father is a serious guy. Before, I really disliked that his "heavy" topics such as what I had learned from the activities I participated, I should not only have a long-term goal but also several simple short-term goals, and his experience during his forty-year engineer career. But as I grew up, I have realized that his "lessons" are his expectations on me. He has never directly required me to do what he arranged for me, but he gives me the chance to try, to fight and to decide by myself. His words imperceptibly impact on me during my growth. I am quite lucky to have a sweet home. My mother, my grand-parents, I am so appreciate what you have done for me!

I would like to thank my supervisor, Eduardo Juárez Martínez. His suggestions and advices helped me a lot to overcome the difficulties. I cannot forget his word-by-word corrections on my paper; I cannot forget the nights he stayed with me to improve the paper; I cannot forget the time he celebrated Jianguo's and my first papers. His sincerity, meticulousness and diligence have influenced me a lot.

I would like to thank all the professors in the research group: César Sanz Álvaro, Matías Javier Garrido González, Fernando Pescador del Oso and Pedro José Lobo Perea. They are friendly and facetious, which always let me feel that the lab is a big family.

I would like to thank my lab mates: David, Gonzalo, Ernesto, Juanjo, Enrique, Miguel, Oscar and Arnaud. They are always willing to help me with the problem in work or in life. Moreover, they are the guide of this country. From them, I can often find out a charming and different Spain. Although some of them have left the lab, I hope we can keep in touch forever. I am really hoping that one day we can go to China for a travel together.

I would like to thank all my friends: 魏建国,黄姗,美娟,朱亮,王宪,杨振,土豆,温馨,钟如意, either in china or here. I like every time stay with them, no matter face-to-face or through the internet. I am really appreciating that they can bear my bad temper, my carelessness, and give me help without hesitation. A good friend is like a cup of wine which become more and more fragrant over time.

Is this true that a person who has many thank to say is a happy guy? I think so, because now I do am. Anyway, this is just a small step in my life, but the sunflower told me that as long as to endeavor forward the sunshine, every day would become pure and beautiful.

#### Content

| C  | ONTEN   | Т   |                                                    | I    |

|----|---------|-----|----------------------------------------------------|------|

| LI | ST OF F | IGI | JRES                                               | v    |

| LI | ST OF T | 'AB | LES                                                | VIII |

| SI | JMMAI   | RY. |                                                    | IX   |

| R  | FSUMF   | N   |                                                    | x    |

|    |         |     | DUCTION                                            |      |

| 1  | INII    |     |                                                    |      |

|    | 1.1     | M   | OTIVATION                                          | 2    |

|    | 1.2     | 0   | BJECTIVES                                          | 5    |

|    | 1.3     | 0   | JTLINE                                             | 6    |

| 2  | ВАС     | KG  | ROUND: ENERGY/POWER CONSUMPTION ESTIMATION METHODS | 7    |

|    | 2.1     | ln  | TRODUCTION                                         | 8    |

|    | 2.2     | Lo  | w-Level Power Estimation Models                    | 8    |

|    | 2.2.    | 1   | Circuit/Transistor-Level Estimation Models         | 8    |

|    | 2.2.    | 2   | Gate-Level Estimation Models                       | 10   |

|    | 2.2.    | 3   | RT-Level Estimation Models                         | 12   |

|    | 2.2.    | 4   | Architectural-Level Estimation Models              | 14   |

|    | 2.3     | Н   | GH-LEVEL POWER ESTIMATION MODELS                   | 16   |

|    | 2.3.    | 1   | Instruction-Level Estimation Models                | 17   |

|    | 2.3.    | 2   | Function-Level Estimation Models                   | 19   |

|    | 2.3.    | 3   | Component-Level Power Estimation Models            | 21   |

|    | 2.4     | D   | scussion                                           | 25   |

|    | 2.5     | C   | ONCLUSION                                          | 27   |

| 3  | MET     | ТНС | DOLOGY                                             | 29   |

|    | 3.1     | ln  | TRODUCTION                                         | 30   |

|    | 3.2     | G   | NERAL IDEA                                         | 30   |

|    | 3.2.    | 1   | Modeling Flow                                      | 30   |

|    | 3.2.    | 2   | Performance Monitor Counters                       | 31   |

|    | 2 2     | 2   | Components Classification                          | 22   |

| 3.2   | 2.3.1 Components Classification                                                                                                                                                                    | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2   | 2.3.2 Energy-related Events                                                                                                                                                                        | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.3   | Modeling Methodology                                                                                                                                                                               | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.3.1 | Mathematics Knowledge                                                                                                                                                                              | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.3   | 3.1.1 Spearman Rank Correlation Coefficient                                                                                                                                                        | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.3   | 3.1.2 Linear Regression Methods                                                                                                                                                                    | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.3   | 3.1.3 Principal Components Analysis                                                                                                                                                                | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.3.2 | ? Methodology                                                                                                                                                                                      | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.3   | 3.2.1 PMC-filter                                                                                                                                                                                   | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

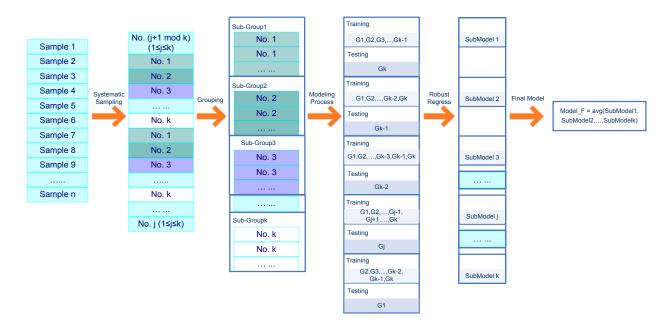

| 3.3   | 3.2.2 K-fold Cross-validation                                                                                                                                                                      | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.4   | DISCUSSION                                                                                                                                                                                         | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.5   | CONCLUSION                                                                                                                                                                                         | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| IMPLE | EMENTATION                                                                                                                                                                                         | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.1 I | Introduction                                                                                                                                                                                       | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.2 I | EXPERIMENTS ENVIRONMENT                                                                                                                                                                            | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.2.1 | ! Hardware Platform                                                                                                                                                                                | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.2   | 2.1.1 Cortex-A8 CPU                                                                                                                                                                                | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.2   | 2.1.2 Storage Hierarchy                                                                                                                                                                            | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

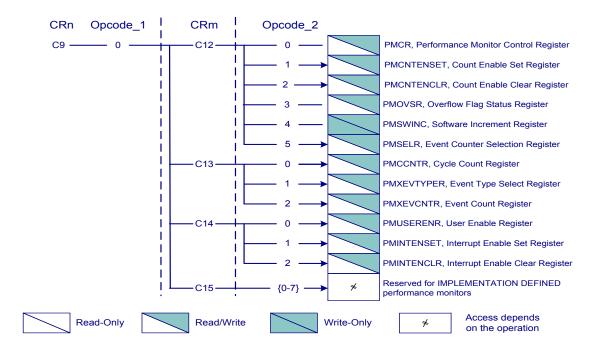

| 4.2.2 | Platform PMCs                                                                                                                                                                                      | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.2   | 2.2.1 Platform Available PMCs                                                                                                                                                                      | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

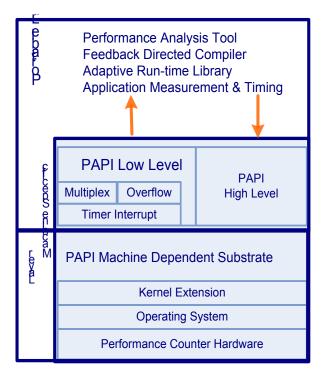

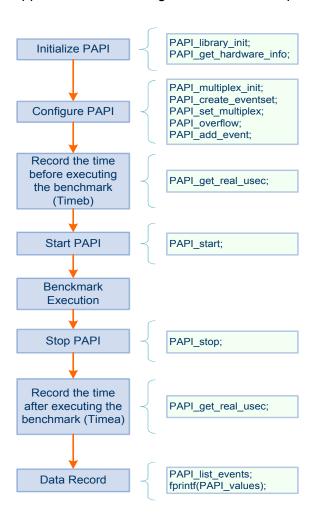

| 4.2   | 2.2.2 PMCs Interface Implementation                                                                                                                                                                | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.2.3 | 3 Components                                                                                                                                                                                       | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.3 I | Modeling                                                                                                                                                                                           | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.3.1 | Benchmarks                                                                                                                                                                                         | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

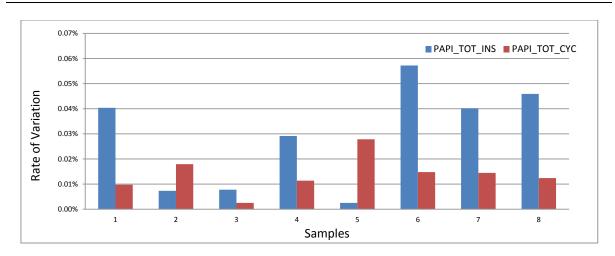

| 4.3.2 | ? Measurement                                                                                                                                                                                      | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.4   | Conclusion                                                                                                                                                                                         | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VALID | DATION AND EVALUATION                                                                                                                                                                              | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1 I | Introduction                                                                                                                                                                                       | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.2   | PROGRESS OF MODEL                                                                                                                                                                                  | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.2.1 |                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.2.2 | •                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| •     |                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0.2.0 |                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       |                                                                                                                                                                                                    | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       | 3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.4<br>3.5<br>IMPL<br>4.1<br>4.2<br>4.2.1<br>4.4<br>4.2.2<br>4.4<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2<br>4.4<br>VALII<br>5.1<br>5.2<br>5.2.2<br>5.2.3<br>5. | 3.3.1 Mathematics Knowledge 3.3.1.1 Spearman Rank Correlation Coefficient 3.3.1.2 Linear Regression Methods 3.3.1.3 Principal Components Analysis 3.3.2 Methodology 3.3.2.1 PMC-filter 3.3.2.2 K-fold Cross-validation 3.4 DISCUSSION 3.5 CONCLUSION  IMPLEMENTATION  4.1 INTRODUCTION 4.2 EXPERIMENTS ENVIRONMENT 4.2.1 Hardware Platform 4.2.1.1 Cortex-A8 CPU 4.2.1.2 Storage Hierarchy 4.2.2 Platform PMCs 4.2.2.1 Platform Available PMCs 4.2.2.2 PMCs Interface Implementation 4.2.3 Components 4.3 MODELING 4.3.1 Benchmarks 4.3.1 MODELING 4.3.2 Measurement 4.4 CONCLUSION  VALIDATION AND EVALUATION 5.1 INTRODUCTION 5.2 PROGRESS OF MODEL 5.2.1 PMC Accuracy |

| 7 | REFERE | NCE                             | 101  |

|---|--------|---------------------------------|------|

| 6 | CONCL  | USION                           | . 97 |

| 5 | 5.4 C  | ONCLUSION                       | . 95 |

|   |        | Future Work                     |      |

|   | 5.3.1  | Model Limitation                | . 93 |

| Ę | 5.3 N  | ODEL LIMITATION AND FUTURE WORK | . 93 |

|   | 5.2.6  | Final Model                     | . 91 |

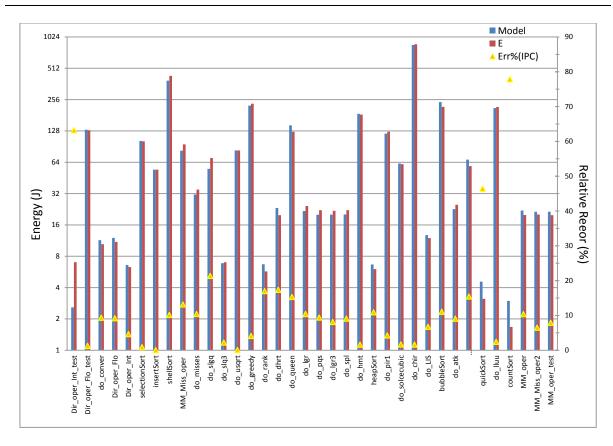

|   | 5.2.5  | Fourth Model                    | . 88 |

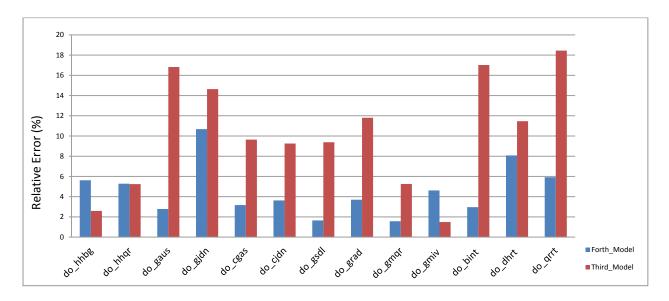

|   | 5.2.4  | Third Model                     | . 84 |

|   | 5.2.3  | 3.3 IPC Selection               | 82   |

#### List of Figures

| Figure 1-1 Energy Analysis Framework                                              | 4  |

|-----------------------------------------------------------------------------------|----|

| Figure 1-2 Simulation-based VS. Traditional Power Profiling Approach <sup>6</sup> | 4  |

| Figure 2-1 A Schemes to Measure the Average Current Drawn                         | 9  |

| Figure 2-2 A Gate-level Example <sup>15</sup>                                     | 11 |

| Figure 2-3 An Architecture Power Estimation Methodology <sup>28</sup>             | 15 |

| Figure 2-4 Principle Instruction-level Power Estimation <sup>6</sup>              | 17 |

| Figure 2-5 Processor Modeling Methodology <sup>49</sup>                           | 20 |

| Figure 2-6 Models Based on Datasheet                                              | 21 |

| Figure 2-7 General Structure of High-level Modeling Methodology                   | 22 |

| Figure 2-8 Simplest System-Level Power Model                                      | 23 |

| Figure 2-9 Power Estimation in Different Design Level                             | 25 |

| Figure 3-1 Modeling Flow                                                          | 30 |

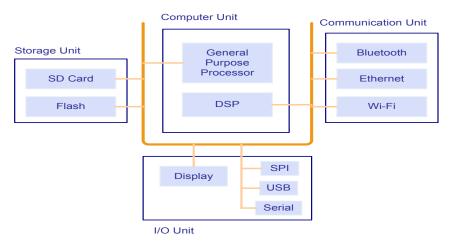

| Figure 3-2 High-Level Overview of the Embedded System Architecture                | 32 |

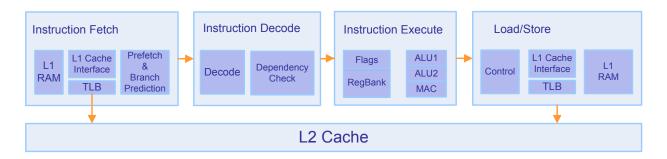

| Figure 3-3 General Core Architecture                                              | 33 |

| Figure 3-4 Shared Variance                                                        | 39 |

| Figure 3-5 Example of the K-fold Cross Validation Method                          | 41 |

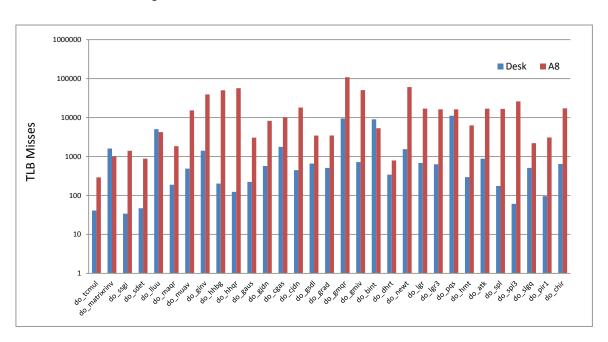

| Figure 3-6 Comparison of TLB Instruction Miss                                     | 42 |

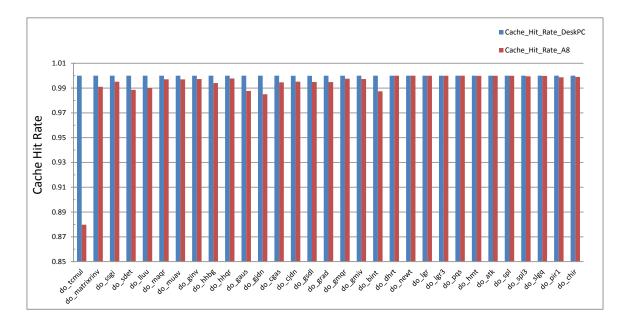

| Figure 3-7 Comparison of the Cache Hit Rate                                       | 44 |

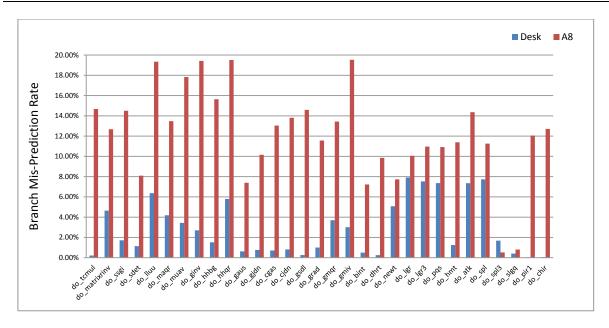

| Figure 3-8 Comparison of the Branch Miss Prediction Rate                          | 45 |

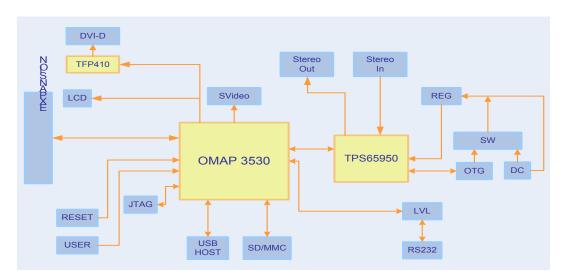

| Figure 4-1 BeagleBoard with High-Level Block Diagram                                                                                       | 50                   |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

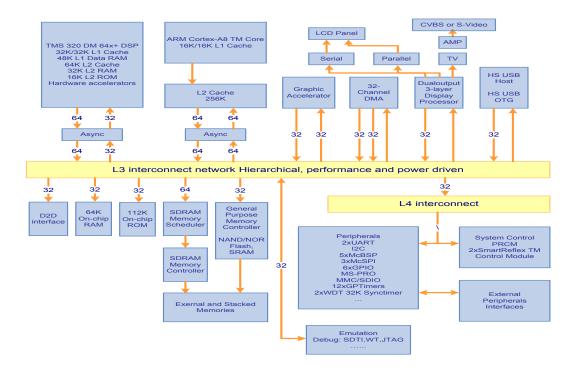

| Figure 4-2 OMAP3530 Block Diagram <sup>83</sup>                                                                                            | 52                   |

| Figure 4-3 Recommended CP15 Performance Monitors <sup>72</sup>                                                                             | 54                   |

| Figure 4-4 PAPI Architecture                                                                                                               | 57                   |

| Figure 4-5 Enable Kernel Support for PMCs                                                                                                  | 60                   |

| Figure 4-6 Enable Debugging Hardware                                                                                                       | 60                   |

| Figure 4-7 Procedure of Using PAPI                                                                                                         | 61                   |

| Figure 4-8 "Switch-case" Pattern to Execute a Benchmark                                                                                    | 64                   |

| Figure 4-9 Identify all the Object Files of Benchmarks                                                                                     | 65                   |

| Figure 4-10 Add Compile Targets                                                                                                            | 65                   |

| Figure 4-11 Indicate Source Code Path                                                                                                      | 66                   |

| Figure 4-12 Compiler Options                                                                                                               | 67                   |

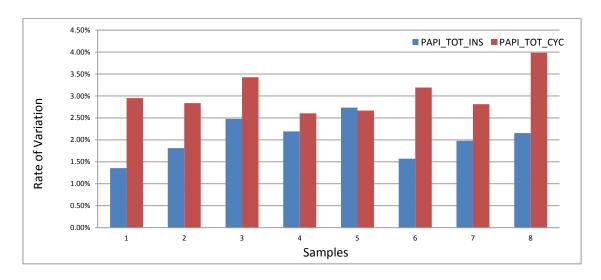

| Figure 5-1 PMCs Variation of Do_Queen                                                                                                      | 76                   |

|                                                                                                                                            |                      |

| Figure 5-2 PMCs Variation of Do_READ                                                                                                       | 76                   |

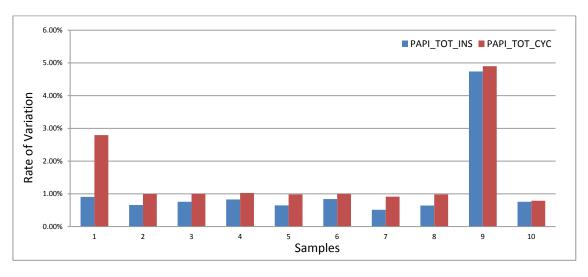

| Figure 5-2 PMCs Variation of Do_READ  Figure 5-3 PMCs Variation of MM_MISS                                                                 |                      |

|                                                                                                                                            | 76                   |

| Figure 5-3 PMCs Variation of MM_MISS                                                                                                       | 76<br>78             |

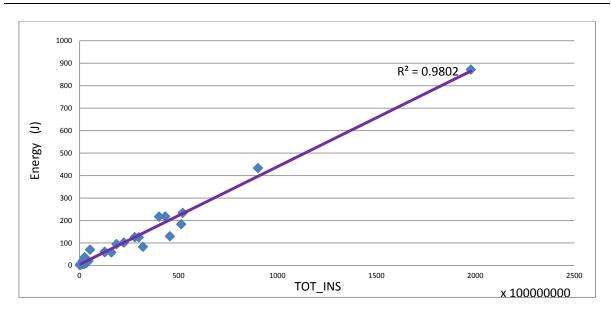

| Figure 5-3 PMCs Variation of MM_MISS  Figure 5-4 Relationship between Energy and TOT_INC                                                   | 76<br>78<br>78       |

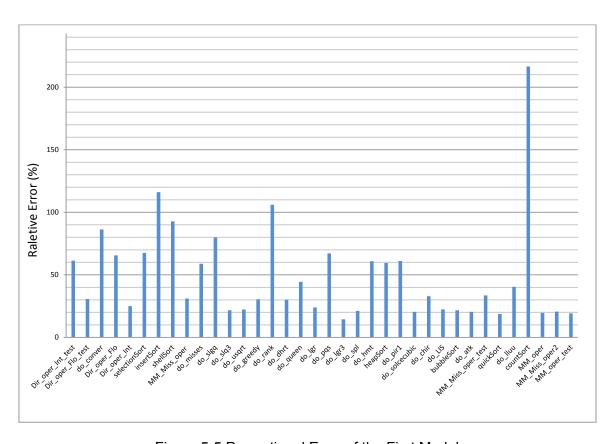

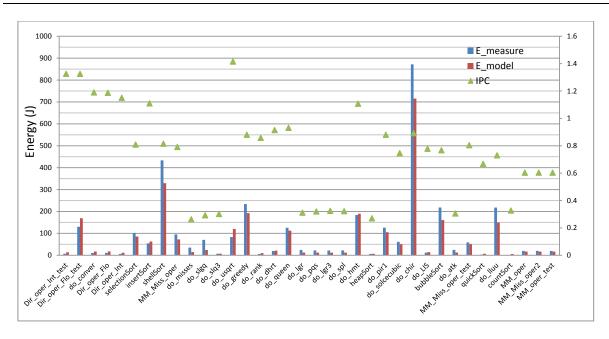

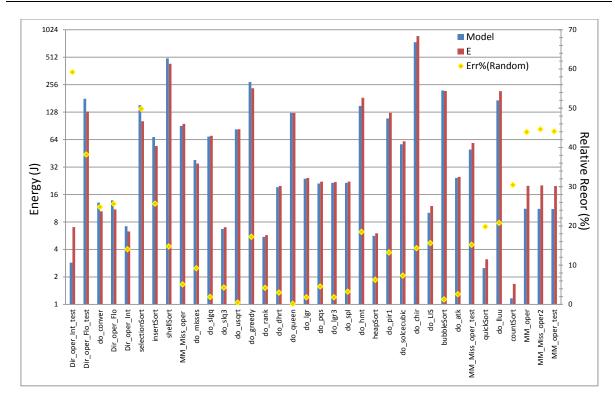

| Figure 5-3 PMCs Variation of MM_MISS  Figure 5-4 Relationship between Energy and TOT_INC  Figure 5-5 Proportional Error of the First Model | 76<br>78<br>78<br>79 |

| Figure 5-9 Real Energy Consumption VS. Second Model Estimation (c) | . 83 |

|--------------------------------------------------------------------|------|

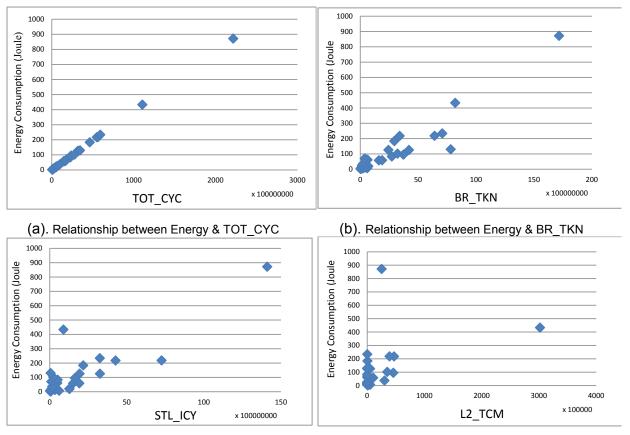

| Figure 5-10 Relationship between Energy and PMC                    | . 85 |

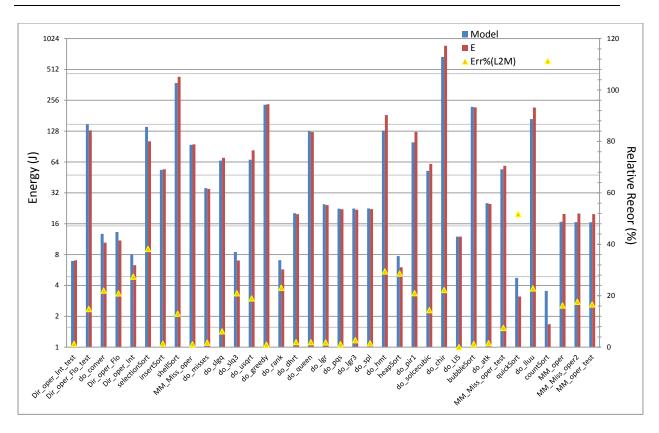

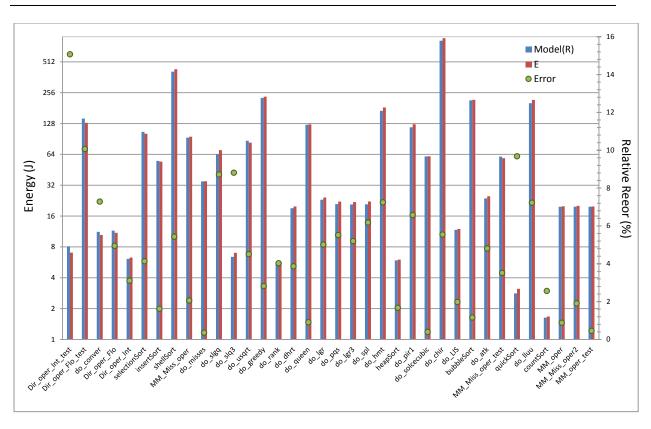

| Figure 5-11 Real Energy Consumption VS. Third Model Estimation     | . 87 |

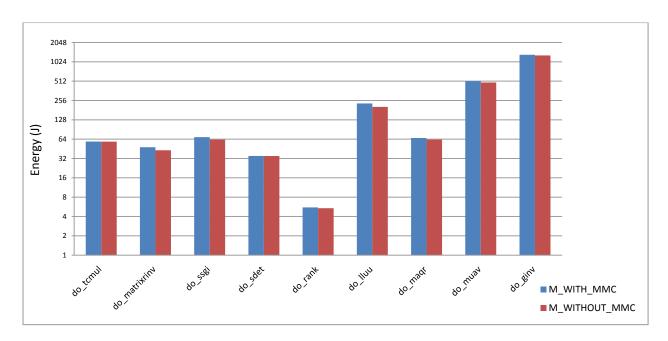

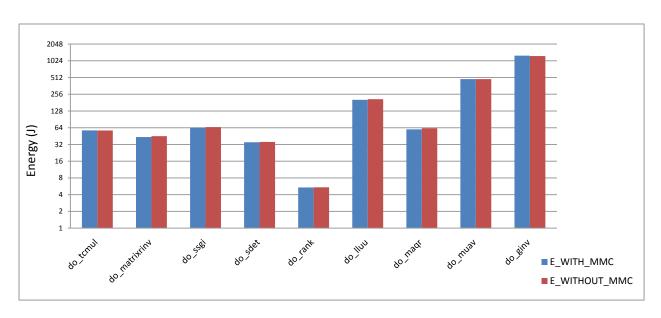

| Figure 5-12 Measurement Energy Comparison                          | . 88 |

| Figure 5-13 Estimation Energy Comparison                           | . 88 |

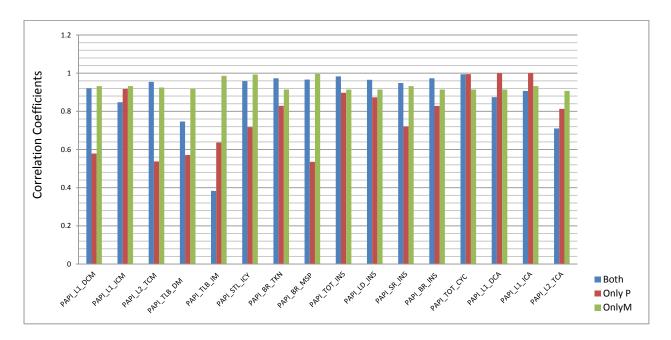

| Figure 5-14 Correlation Coefficients in Different Cases            | . 89 |

| Figure 5-15 Model Comparison                                       | . 90 |

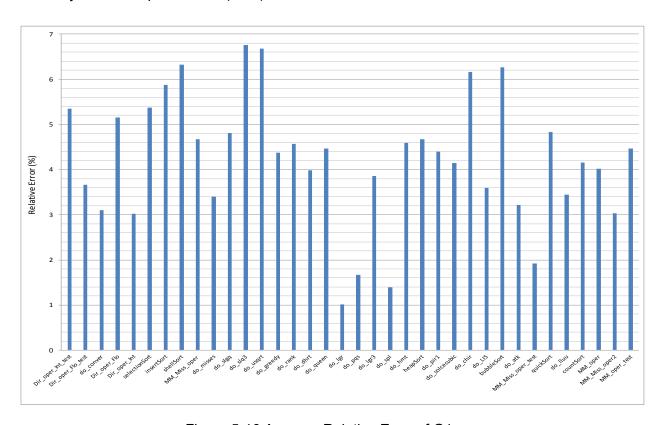

| Figure 5-16 Average Relative Error of G1                           | . 92 |

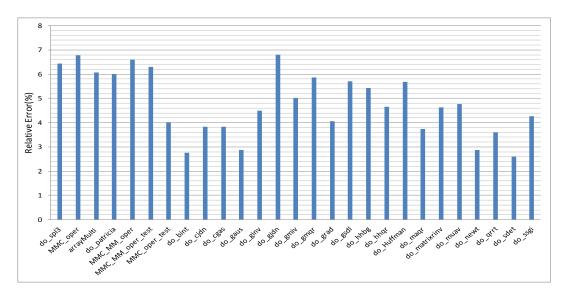

| Figure 5-17 Average Relative Error of G3                           | . 93 |

#### List of Tables

| Table 3-1 Correlation Coefficient Explanation                                      | . 38 |

|------------------------------------------------------------------------------------|------|

| Table 4-1 ARM Core Key Features                                                    | . 51 |

| Table 4-2 Supports of PMC Drivers on ARM Family (Last Update 6 <sup>th</sup> 2011) | . 59 |

| Table 4-3 Events Measured by setting the environment variable PAPI_EVENT           | . 68 |

| Table 5-1 The Correlation Coefficients between PMCs and energy                     | . 85 |

| Table 5-2 Relative Errors in Different Cases                                       | . 91 |

#### Summary

This dissertation, whose research has been conducted at the Group of Electronic and Microelectronic Design (GDEM) within the framework of the project Power Consumption Control in Multimedia Terminals (PCCMUTE), focuses on the development of an energy estimation model for the battery-powered embedded processor board.

The main objectives and contributions of the work are summarized as follows:

- ➤ A model is proposed to obtain the accurate energy estimation results based on the linear correlation between the performance monitoring counters (PMCs) and energy consumption.

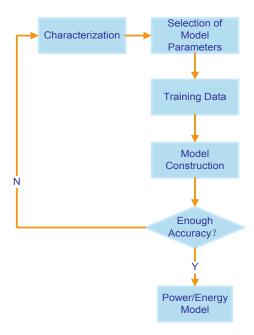

- Considering the uniqueness of the appropriate PMCs for each different system, the modeling methodology is improved to obtain stable accuracies with slight variations among multiple scenarios and to be repeatable in other systems. It includes two steps: the former, the PMC-filter, to identify the most proper set among the available PMCs of a system and the latter, the k-fold cross validation method, to avoid the bias during the model training stage.

- ➤ The methodology is implemented on a commercial embedded board running the 2.6.34 Linux kernel and the PAPI, a cross-platform interface to configure and access PMCs. The results show that the methodology is able to keep a good stability in different scenarios and provide robust estimation results with the average relative error being less than 5%.

#### Resumen

Este trabajo fin de máster, cuya investigación se ha desarrollado en el Grupo de Diseño Electrónico y Microelectrónico (GDEM) en el marco del proyecto PccMuTe, se centra en el desarrollo de un modelo de estimación de energía para un sistema empotrado alimentado por batería.

Los objetivos principales y las contribuciones de esta tesis se resumen como sigue:

- Se propone un modelo para obtener estimaciones precisas del consumo de energía de un sistema empotrado. El modelo se basa en la correlación lineal entre los valores de los contadores de prestaciones y el consumo de energía.

- Considerando la particularidad de los contadores de prestaciones en cada sistema, la metodología de modelado se ha mejorado para obtener precisiones estables, con ligeras variaciones entre escenarios múltiples y para replicar los resultados en diferentes sistemas. La metodología incluye dos etapas: la primera, filtrado-PMC, que consiste en identificar el conjunto más apropiado de contadores de prestaciones de entre los disponibles en un sistema y la segunda, el método de validación cruzada de K iteraciones, cuyo fin es evitar los sesgos durante la fase de entrenamiento.

- ➤ La metodología se implementa en un sistema empotrado que ejecuta el kernel 2.6.34 de Linux y PAPI, un interfaz multiplataforma para configurar y acceder a los contadores. Los resultados muestran que esta metodología consigue una buena estabilidad en diferentes escenarios y proporciona unos resultados robustos de estimación con un error medio relativo inferior al 5%.

## Introduction

#### 1.1 Motivation

Nowadays, battery-powered consumer electronics devices like smart phones, media players, PDAs and tablets have become more and more indispensable in people's daily life. However, the design of those devices still faces several problems: computing capability, memory constraints and, especially, the limited battery lifetime. Battery lifetime is improved very slowly comparing to the continuously increasing demands for new functionalities such as games, network services and multiplayer. These functionalities usually cause the intensive computations, heavy network transmissions and the always-on display, which are inversely proportional to the battery lifetime. Therefore, low-power design has become a hotspot. It includes several techniques such as the specialized circuit design, the architecture design, the power-aware operating system (OS) scheduler and the power management (PM) policy, all of which work at different levels to address energy/power consumption issues. Low-power design concentrates on increasing the energy efficiency, unfortunately, these techniques alone are not sufficient. High-level strategies, such as energy-aware OS schedulers and PM policies, are becoming increasingly important to maximize battery lifetime. PM policies in mainline OS assume that the energy saving can be achieved by running at the low chip speed. Therefore, one PM policy in work [1] consider the workload completion in low-power mode by scaling chip voltage and frequency. To achieve a balance between energy consumption and performance, PM policies usually, either, run the workload at the maximum performance setting within the longest time on low-power mode, or alternatively, under deadline constraints, try to save more energy by running at the lowest performance setting. However, Snowdon et al. pointed out that such a simple approach leaded to sub-optimal results on actual hardware in [2] and [3]. Furthermore, they presented that the PM policy which considered on energy characteristics of workloads was able to achieve the maximum energy efficiency. Therefore, an accurate estimation model for profiling the on-line energy consumption at a fine granularity is needed. This kind of models, as the foundation of system PM policies, can help PM policies to improve and facilitate the energy efficiency optimization on battery-powered platforms<sup>4</sup>.

Traditional energy profiling is usually based on the direct measurements. Measurement is limited to the entire chip due to chip integration and packaging. Moreover, the final entire chip is not available at early design stages. Therefore, the energy profiling cannot be obtained until the late design stage. In order to avoid this weak point, emulation-based power profiling approaches have been employed to consider energy issue at the beginning of the design stage. These approaches try to extract the physical behavior information during the application executions to make an estimation model based on the

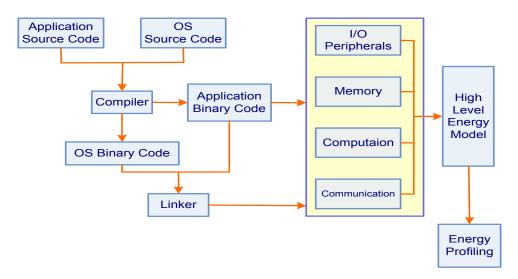

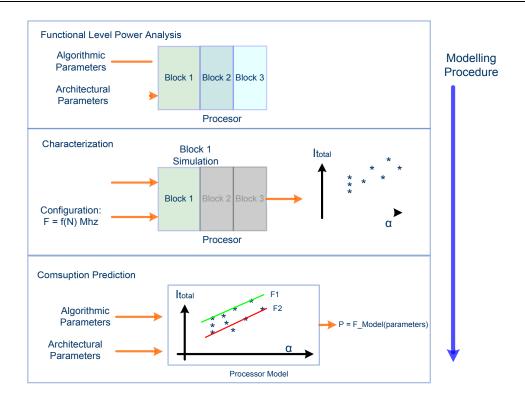

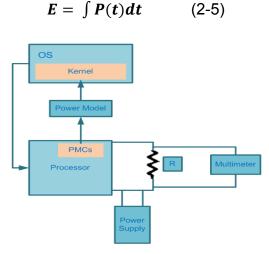

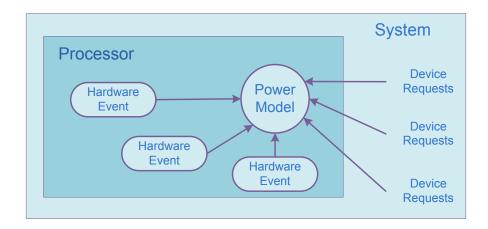

system resources' utilizations and energy consumptions. They can work at the low-level or high-level depending on how they obtain the predictions of power consumption. The lowlevel approaches exploit the main strategies to simulate the activities from the power-related hardware operation units of the microprocessor architecture. This solution suffers the lack of details on the internal structure of the system and the quite long simulation time. To overcome these problems, high-level abstract models have been proposed. These models concentrate on the events happened on the higher level of the system architecture. For example, to construct an estimation model for the processor, on one hand, they will first measure the average current drawn by the processor during the application execution; on the other hand, they monitor some key energy-related events triggered at this period. The model is constructed by relating these events with the measured energy. The energy-related events can also be divided into different levels such as instruction level, function level or system level. Usually, finding the relationship among events and energy is an off-line procedure, once a fine energy estimation model is constructed, it can be simply applied to the energy-optimizing strategies such as the PM policy and then continuously makes the online estimations. A PM unit can be considered as an energy manager. It tries to optimize the energy usage to extend the battery lifetime. Meanwhile, this energy estimation profiling will help it to make a power-aware decision. The Figure 1-1 shows a typical example to attach the software designs together with the hardware simulator platform to figure out an energy profiling. The left part in the figure is the steps involved to use the simulator. The compiler generates the objects codes from the operating system and the applications, then these object codes are linked and work as the stimuli. The right part is the simulation model, which considers the hardware of the system as several components, and then the high-level simulator models each component. Note that the modeling methodology could be various. In this work, they obtained the power models from the data-sheet except for the processor which was modeled by the instruction-level energy models. After a reasonably accurate model was done, the energy consumption profiling of the tasks ran on the system can be expressed as a sum of the energy contribution from each component.

Figure 1-1 Energy Analysis Framework<sup>5</sup>

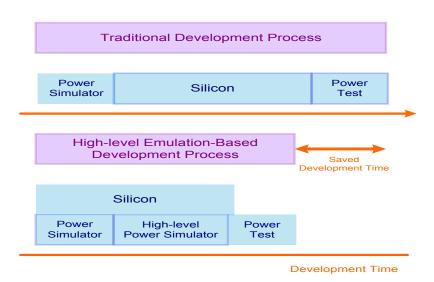

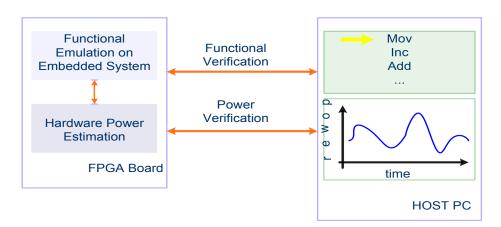

Based on the energy profiling from the software aspect, high-level energy estimation can help products to decrease their time to market<sup>6</sup>. Energy estimation is needed at different stages in the design process. Ideally, designer would like to estimate the energy of the design very early, such as when only a high-level (behavioral) description of the design is available. In this stage, when the design is still sufficiently flexible, energy information can be delivered to the designers before available silicon by utilizing an FPGA prototyping platform (Figure 1-2) to make energy tests. Therefore, designers do not need to wait until the whole design flow is finished to solve the energy problem, they can make the major changes rather cheaply.

Figure 1-2 Simulation-based VS. Traditional Power Profiling Approach<sup>6</sup>

Although there is much work that has been done to have a good energy profiling, energy estimation is still a very important topic, especially on battery-powered embedded

systems. This thesis concentrates on this topic to provide an accurate energy consumption model of the battery-powered devices. The model is based on the PMCs (Performance Monitoring Counters) which are realized as the hardware registers attached with the processor to measure various programmable events occurring in the processor. It can give a detection of those events which influence the power consumption, and supply the power-aware strategies or individual user the key issues to maximize energy efficiency. Meanwhile, this energy estimation model is able to keep the stability on various cases. For example, if an application has a low performance due to its high cache misses rate and a frequent data transfer between cache and the main memory, the model can detect their bottlenecks and identify its high energy consumption. This model is also generic and portable. It obtains its required information from a high-extracted level to mask the hardware differences. Therefore it can be attached to various platforms with few modifications.

#### 1.2 Objectives

For getting the energy/power consumption profiling, the estimation model should be able to provide a correlation between run-time resource usage and energy consumption to help the energy-related strategies to improve the energy efficiency optimization.

The main goal of this thesis is an exploration of a methodology to build a platform-independent high-level model. It estimates the energy consumption from the analysis of the on-line system energy-consuming behaviors. An ideal estimation model should be suitable for on-line using and should meet several rules described below:

- Non-intrusive and low-overhead: This model should not require too much intrusive hardware adjustments and software overhead when collect the model input parameters. It must give a quick response for real-time optimizations. A long time-taken model, in contrast, will delay the energy-optimizing strategies to make decisions of tasks arrangements or voltage/frequency scaling.

- Easy to develop and use: The model should be simple. This means a model can keep low complexity while provide enough accurate predictions, thus it can be used on different systems without too many modifications and restrict the model's own enable energy consumption in a small limitation.

- Reasonably accurate: The model must be sufficiently accurate to enable energy-efficiency optimization. A certain error range is accepted by considering the model's own overhead.

- ➤ Generic and portable: This model should have highly enough abstract level to other systems. It should work for different platforms of various combinations of processor families, memory hierarchies and components within few modifications. Generating a model for a new system, it requires neither exhaustive details nor extensive design exploration.

Considering the requirements of easy usability, good scalability and high speed, an estimation method should be a high-level abstraction to avoid many platform details. In this thesis, a PMC-based approach is focused. The PMC-based model may be built from a specific hardware platform, but the methodology can be used on any PMC available systems.

#### 1.3 Outline

This thesis continues with four chapters:

- Second chapter describes various energy/power estimation methods based on different levels. Their main methodologies are introduced and a comparison to identify the most suitable method for energy optimization strategies is given later.

- ➤ Third chapter describes the methodology introduced in this thesis in detail. It includes the basic thought of modeling associated with the PMCs, the needed mathematics knowledge and the improvement of the modeling method to give a good predictability and generalization.

- ➤ Forth chapter gives an implementation which uses the third-part existing interface to measure the according set of PMCs of a particular platform. It also introduces the usage of the according functions of the interface to configure the PMCs.

- The fifth chapter describes the progress of the modeling methodology. It begins with the simplest method which has the unacceptable estimation error, and follows with how to derive the methodology to improve the accuracy. The limitation of the methodology and the future work are also discussed in this chapter.

# **2 Background: Energy/Power Consumption Estimation Methods**

#### 2.1 Introduction

Accurate models of energy/power consumption estimation have been a crucial research field of many schemes to improve the energy efficiency. These models focus on the initial design of individual component or the whole system to provide the possibility to identify the key influences of the energy consumption. In this chapter, contributions and a discussion on previously proposed approaches of power modeling in different level are summarized.

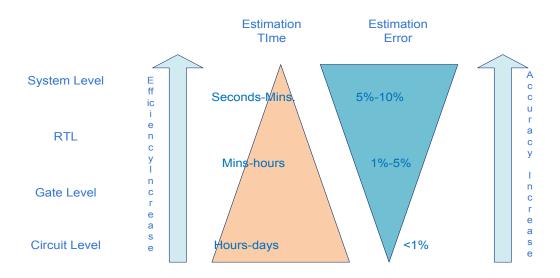

An energy profiling is the representation of the system's energy consumption. Because of the general usage, a profiling may highlight some key factors of energy consumption of the system while abstract away some others. Energy profiling can based on the real measurements or the estimation models. In this dissertation, the modeling method is focused on. Modeling methods of energy estimation involve two important issues during the model constructing: complexity and accuracy, both of which are determined by the abstraction layer on which the energy models are set up. These two issues result in two main categories of the models: low-level and high-level energy estimation models. Low-level models which estimate the energy and power from the detailed design information include circuit level, gate level, register transfer level (RT level) and architectural level. High-level models deal with the instructions, functional units or components to profile the system energy from software point in order to avoid the hardware details.

#### 2.2 Low-Level Power Estimation Models

#### 2.2.1 Circuit/Transistor-Level Estimation Models

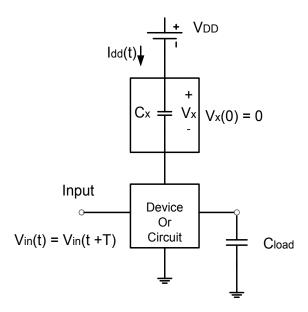

A simple and straight method of average power estimation is to simulate the circuit behaviors to obtain the power supply voltage and current waveforms, from which the average power can be computed. Several circuit simulation based approaches have been proposed in work [7] by Kang. In fact, the model in this level is most used for VLSI (Very Large Scale Integrated Circuits) design and the technology choice. The basic scheme of this approach is shown in Figure 2-1. A parallel RC sub-circuit is inserted into a VLSI circuit without any interference of the original circuit. The sub-circuit measures the current drawn from the voltage source and computes the average power as equation 2-1:

$$P(t) = u \cdot i(t) = u \cdot \frac{dq}{dt} = u \cdot C_x \frac{du}{dt} = \frac{C_x V_x(t)}{t}$$

(2-1)

Figure 2-1 A Schemes to Measure the Average Current Drawn

Yacoub et al in [8] proposed a similar circuit simulation technique as the basic one to measure the average current in complementary circuit structures. Their difference was in the complementary circuit structures, where current was not permitted to flow during a steady state of a circuit because there was no path between power and ground in this equilibrium state.

However, these early methods are not suitable to the complex circuit design with higher integration density, smaller device geometry, larger chip size and faster clock frequency caused by the rapid development of the CMOS technology. Subsequent researchers in [9],[10],[11],[12] and [13] proposed the probabilistic approach instead of directly simulating a circuit. Probabilistic approaches compute and propagate the probability for a node to change its logic state. There probability methods usually include two kinds of definition:

- > Signal Probability: The average fraction of clock cycles in which the steady state value of node x is logic high;

- Transition Probability: The average fraction of clock cycles in which the value of node x at the end of the cycle is different from its initial value.

Followed with the probabilistic logic, a novel simulator, PowerMil<sup>14</sup>, was proposed to build a transistor-level power consumption model by simulating the current and power behavior in modern deep-submicron VLSI circuits. PowerMil provides piecewise linear transistor model to capture transistor characteristics from a table to greatly shorten the

evaluation overhead. However, it is extremely complex to represent a circuit/transistor-level models due to all details of the design flow, layout, routing and parameter extraction. Probabilistic-based models can achieve very good accuracy while take unbearable long time to simulate more than one million transistors, thus, they are not suitable for the real-time demand because of both the high complexity and expense. In the other side, they also require the user to specify complete information about the input patterns.

Although the circuit details can be obtained during the logic synthesis at the early design stage, they may invalid to the transformations or design decisions made at later implementation stages, hence the model in this level is hard to be used in the early design stage. This technique is accurate and general to estimate the power of any circuit with various technology, design style, functionality and architecture. However, the estimation model is driven by the complete and specific input information which causes huge number of input pattern and heavy computation, thus it is impossible to use for the large circuits.

#### 2.2.2 Gate-Level Estimation Models

Gate-level estimation methods aim to describe the different gate circuit behaviors during the system runs. The advantage of such methods is that the simulations are driven by events and take place in the discrete time domain. This means that the model is enable to provide an estimation of the switching activities of the basic logic blocks without actually simulating the circuit with a large number of test patterns. Compared with the circuit-level models, gate-level estimation method is faster, can handle larger circuits, and, the most important difference is to be applied before all the circuits details are available. There are two major types of approaches, dynamic and static, used in gate-level power estimation. Dynamic approaches simulate the circuit based on the input sequence with the system representativeness. Their main shortcomings are their very slow estimation speed and highly dependent results on the simulated sequence. Usually, the required the required number of simulated sequence is high to produce a valid power estimate. To address this problem, Monte Carlo simulation techniques are proposed. These techniques use an input model based on a Markov process to generate the input stream for simulation. The main difficulty is that it is not clear how the input stream can be efficiently generated when the circuit inputs exhibit complex correlations. The static techniques are implemented based on the statistical information abstract from the input sequences to estimate the internal switching activity of the circuit.

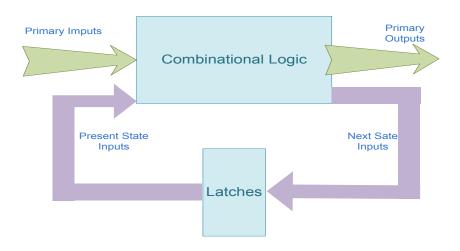

Gate-level model assumes that the circuit consists of logic gates and latches, as shown in Figure 2-2. In other words, it consists of latches driven by a common clock and

combinational logic blocks whose inputs (outputs) are latch outputs (inputs). Therefore, the average power consumption of the circuit can be divided into two parts: the power consumed by the latches and that consumed by the combinational logic blocks.

Figure 2-2 A Gate-level Example 15

Gate-level energy estimation needs the gate switching activities, thus pattern independent approaches are well-suited for this kind of power estimation. Pattern independent methods provide an estimate of the average switching activity without actually simulating the circuit with a large number of test patterns<sup>15</sup>. Gate-level energy estimation reduce the computational complexity compare with the circuit-level models, meanwhile, it does not loss too much accuracy. Several gate-level energy estimation approaches with good accuracy and high efficiency have been proposed. They are classified into dynamic and static two categories.

The dynamic approaches explicitly simulated the circuit based on the typical input sequences. Their main shortcoming was the very slow simulated speed. Moreover, their results were highly dependent on the simulated vectors. The required number of simulated vectors was usually high to produce meaningful energy estimation. Burch et al. proposed the Monte Carlo approach to solve the vector problem in work [16] by Burch et al. Their approach used the probabilities to compute the power consumption by directly monitoring the total power during the random simulation. The input vector streams for simulation were generated by Markov process. The Monte Carlo approach faced to a main difficulty of clearly showing how the input vectors could be efficiently generated when the circuit inputs exhibited complex correlations.

The static approaches in [17],[18] and [19] relied on statistical information, for instance, the mean activities of the input signals and their correlations. The concept of

probability waveforms, transition density and the enumeration approach based on symbolic simulation were proposed. An example of a gate-level statistical power estimation approach was presented by Chou et al in work [20]. They took the spatial and temporal correlations of logic signals into consideration. Their proposed the states partitions approach to reduce the computation time. Ding et al. in work [21] proposed a similar approach based on tagged (probability) waveforms. The tagged waveforms were obtained by two issues. One is the partition of the logic waveform space of a circuit node, according to the initial and final values of each waveform. The other is to compact all logic waveforms in each partition by a single tagged waveform. Then, the tagged waveform can be used to calculate the switching activity of the circuit node. Note that only tagged waveforms at the circuit inputs were exactly computed, the remaining nodes were computed using a compositional scheme that propagated the tagged waveforms from circuit inputs to circuit outputs.

In practice, the model required input probabilities could be directly provided to eliminate the need for a large set of specific input patterns. The results of the model analysis will depend on the supplied probabilities. Thus, to some extent the process is still pattern-dependent and the user must supply information about the typical behavior at the circuit inputs, in terms of probabilities.

#### 2.2.3 RT-Level Estimation Models

A register transfer level data path is consist with the interconnections of the predesigned functional blocks such as adders, substractors, multiplexers, comparators and registers (the control units, buses, memories and clock trees are excluded from this data path category). A register transfer level description captures the application specific integrated circuit (ASIC) behaviors at the physical levels. The simulation approach in RTlevel is try to functionally estimate and collect the input sequence including blocks or network on interconnections such as adders, registers, multiplexers and the netlists. The power properties of a block could be traced by the application under the controlled operating conditions of an individual block through its input statistics.

Most RT-level power estimation approaches use the capacitance models with activity profiles of data or control signals, which are signal probability or switching activity. For a node to switch state and consume dynamic power, its current state must differ from its previous one, which meant that if the previous state was zero and the node was now directly set to one. Thus, signal probability (SP) is the fraction of time a signal is logic high. This probability of this occurring was referred to the switching activity (SA), thus a simple dynamic power dissipation model of a gate could be calculated by multiplying the SA, the capacitive

load (C), the clock frequency (f) and the square of the supply voltage for each node as the formula 2-2:

$$P_{dynamic} = \alpha \cdot C_L \cdot V_{dd}^2 \cdot f_{clk} = \alpha \cdot C_L \cdot \Delta V \cdot V_{dd} \cdot f_{clk}$$

(2-2)

Here,  $C_L$  is the load capacitance,  $f_{clk}$  is the clock frequency,  $V_{dd}$  is the supply voltage,  $\Delta V$  is the swing voltage of the node, and  $\alpha$  is the node '0  $\rightarrow$ 1' transition activity factor which is defined between 0 and 1.

The switched capacitance and switching probability of each functional module are modeled by formulas that are a function of the module's inputs probabilities. These formulas are computed beforehand for each model using the polynomial simulation scheme, and stored in the model library. The switched capacitance for each isdtance of a module in the circuit can hen be efficiently evaluated for its specific input probabilities. The switching ptobabilities at the outputs of each model can be computed in a similar maner, thus ptoviding a means of propageting the switching probabilities through the circuit described at the RT level.

Najm gave a good list of several RTL power estimation approachs in work [18]. The main idea is based on the probabilisite and statistical techniques. These techniques are applicable only to combinational circuits. They require the user to specify information on the activity at the latch outputs. Some estimation tools, such as Primepower<sup>22</sup> performed power estimation both at the structural RTL and gate levels. Others like HSPICE<sup>22</sup> and SPICE<sup>23</sup> can also be used to do the low-level simulate. These tools give very closed result caompare to the actual power comsumptions. However, research studies and these tools show the limitations of RT-level power estimation: long-lasted time and required RTL design details, which are extremely difficult to get. Another tool Hotspot<sup>24</sup> although considered the power estiamiton together with the thermal, it still based the design data from a gate-level netlist and the activity factors from a structural RTL model, thus it cannot avoid those disadvantages mentioned before. Those disadvantages make them not proper for early-stage design explrations. Besides, they cannot be easily updated for the future technology.

RT-level estimation methods cannot totally avoid the pattern-dependence problem in circuit-level or gate-level since some of the inputs provided by the users are typical behaviors. These inputs are usually based on the probability, which is defined as the average fraction of time that a signal stay in high status and the density, the average number of transitions during each second. Comparatively speaking, this information is much more easily obtained by the desigers than specific input patterns are. For example, designers can

estimate the average input switching frequencies through the test streams or assume the frequency by the known clock frequency. For the real implementation, the statistial approach can ne construct by the existed simulation tools and libraries, which mainly differs with the dynamic one. In the other word, dynamic modeling approach, which based on the probabilistic technique, requires the specifc simulation models.

#### 2.2.4 Architectural-Level Estimation Models

Architects typically make decisions in the planning phase before the design has begun; therefore, those tools such as PowerMill<sup>25</sup> and QuickPower<sup>25</sup> which operate on the circuit level and need complete HDL design are not helpful for making architectural decisions. Considering with the insufficient usage of the previous estimation methods on energy efficiency optimizing, architectural and software estimation methods, as the addition to the low-level circuit estimation approaches, have become more important. However, this method still suffers from the lack of the efficient simulator tool that analyzes and quantifies the power ramification of various architectures. Such a tool requires to trade-off the low-level details and accuracy against the simulation speed and portability<sup>26</sup>.

There are three components that define the important contributions to power consumption in CMOS<sup>27</sup> technology as formula 2-3:

$$P = ACV^2 f + \tau AVI_{short} + VI_{leak}$$

(2-3)

The first component is the dynamic power consumption which depends on the capacitive load charging and discharging of each gate, in which factor "A" means the activity of the gates, factor "C" means the total capacitance seen by the gate outputs, factors "V" and "f" are the supply voltage and the system frequency, respectively. The second term stands for the power dissipated on the short-circuit. The factor " $I_{short}$ " means the short-circuit current that flows between the supply voltage and ground when the output of a CMOS logic gate switches in the  $\tau$  period. The third part is the power consumed by the leakage current depends on the number of gates and threshold voltages. Therefore, to estimate by a cycle-accurate simulator is necessary to focus on the activities on the gate level (the first two terms) and the number of the gate of each micro-architecture (the third term). Based on this reason, various architectural power simulators combine with the lower level power consumption models to get the circuit activities and capacitive models of activated components during each cycle<sup>28</sup>.

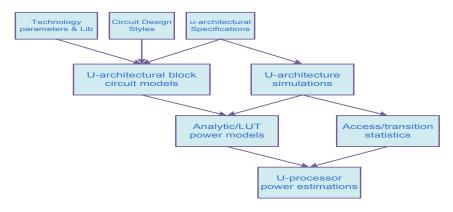

Figure 2-3 shows an architecture-level estimation model for power by extending a cycle simulator. Before model constructing, primary technology parameters, such as supply

voltage, threshold voltage, capacitance per area and the sheet resistances of the interconnectors, are needed to well prepare. Furthermore, the micro-architecture specification should also be determined. Usually, the micro-architecture functional blocks are designed as full-custom, thus the design styles influence the power consumption and require the different power models. Therefore, architectural-level model usually divides the chip into several regular functional blocks such as memory, datapath, interconnectors and clock distribution tree, thus the number of the activity patterns is reduced. The model of each block is constructed with the consideration of its specific determination and features only once and kept in the look-up table. Finally, the estimation model profile the energy of each micro-architectural block by combining the power model and the execution statistics from the cycle simulator.

Figure 2-3 An Architecture Power Estimation Methodology<sup>28</sup>