CORF

# Wireless Sensor Networks Node with Remote HW/SW Reconfiguration Capabilities

J. Portilla, Y. E. Krasteva, J. M. Carnicer, T. Riesgo Centro de Electrónica Industrial, Universidad Politécnica de Madrid {jorge.portilla, yana.ekrasteva, teresa.riesgo}@upm.es

Abstract- The inclusion of reconfigurable HW in nodes for Wireless Sensor Networks (WSNs) is not a common issue in the framework of the design of state of the art HW platforms for WSNs, mainly due to its high power consumption. But, on the other hand, reconfigurable logic as FPGAs can contribute to improve the system performance by providing not only HW acceleration as it has already been demonstrated by several research groups, but also the possibility of node HW updates after WSN deployment. This paper presents an entire working flow to generate, remotely configure and reconfigure the HW and SW in a reconfigurable node platform for WSNs. The presented reconfiguration working flow targets the custom HW platform designed at CEI (Centro de Electronica Industrial), where the processing is carried out by both a microcontroller and a partially reconfigurable Xilinx FPGA. The presented reconfiguration process is based on the JTAG protocol and thus permits to port the system to new, less power consuming FPGAs that are appearing in the market to solve problems related to energy lifetime.

#### I. INTRODUCTION

Wireless Sensor Networks (WSNs) represents one of the most outstanding and ambitious challenges in electronic design and telecommunications nowadays. These special networks are intended to be autonomous, low power consuming, context aware and reconfigurable.

The particular features related to WSNs force the designer to think in a new way. In this context, the hardware of the node becomes critical, in order to overcome the hard requirements imposed by these type of systems.

The applications in which WSNs may be involved can include hundred or thousand of nodes. In such situations, it is very important to be able to debug the network on-line and reprogramming the nodes to solve problems of working or performance. These tasks are related to the concept of commissioning [1].

Usually, WSNs HW designers include a microcontroller (uC) as the smart element, which carries out all the tasks related to communication control, sensors processing and global node management [2][3]. A modular HW reconfigurable platform has been developed during the last years at CEI, called Cookies. This platform includes a uC and an FPGA as processing elements. The idea is to have a processing support for the uC, to carry out specific tasks which could overload the uC (special processing as video and audio or sensor processing for particular digital interfaces among others). Other groups face this topic as [4][5], but their approach include the development of specific integrated circuits where the reconfigurable logic is included. The

platform developed at CEI includes a commercial FPGA from Xilinx, which makes easier the integration in new environments for designers and engineers.

One of the problems that arise when a reconfigurable element as an FPGA is introduced in a system as a WSN node is the power consumption penalization. The architecture of the hardware platform used in the present work will be detailed in section II, but it can be said in advance that new ultra low power FPGAs are appearing in the market as Actel Igloo, and a new development is been carried out to introduce this kind of elements to overcome the power consumption problem in reconfigurable WSN nodes. The HW reconfiguration feature improves the flexibility of the node, and allows remote HW updates, which can be very useful to improve node performance in new actualizations, to debug on-line (commissioning) the WSN, and make the node smarter.

This paper details the work developed to reconfigure the FPGA HW integrated in the node, using a wireless link (ZigBee in this case) and an example of application in which this HW reconfiguration capability of the node is intended to be used.

The basic idea is to use the uC to reconfigure the FPGA. The uC will use the JTAG port of the FPGA to accomplish this task. This decision was taken due to most of the market FPGAs include a JTAG port to download its configuration file. The uC will receive the bitstream from the ZigBee module and will introduce it in the FPGA configuration memory.

The current node design includes a Xilinx FPGA (XC3S200 Spartan 3). This work has taken advantage of the partial reconfigurability capabilities of such devices (other manufactures do not offer this feature). Moreover, with this approach the size of the bitstreams are much lower, and the remote configuration process is much faster.

The idea will be tested over the reconfiguration of hardware sensor interfaces. This is other line developed at CEI and will be explained in section II. The concept is to have a library of general HW digital interfaces for sensors (as I2C, 1-Wire, SPI, etc.). These interfaces are designed in a general way in order to be able to adapt them to new sensors in a fast way. The demonstrator will start with a default configuration for the FPGA with some interfaces configured and one of these interfaces will be replaced for other interface for the same sensor or another, in a dynamic (without restarting the node) and partial way (only a part of the whole configuration will be changed).

The rest of the paper is organized as follows. Section II details the HW node architecture and the HW sensor interfaces. Section III describes the remote reconfiguration process and section IV how the partial reconfiguration is carried out. Section V details the proof of concept and section VI concludes the paper.

## II. COOKIE SENSOR NODE

The WSN node in which the reconfiguration tasks are carried out is the Cookie [6] (see "Fig. 1"). This node was designed with a main philosophy in mind: modularity.

Modularity allows dividing and encapsulating the functionalities included in the node. Therefore, future redesigns may involve only part of the platform, which is desirable considering the time to market. Moreover, researching using this platform turns open, due to the node flexibility, which makes possible the proof of several concepts minimizing the effort.

TheCookie is composed of four main layers (more layers can be added in future versions): processing, communication, power supply and sensors. Every layer carries out a specific task, and these encapsulates the functionality. In the following paragraph these layers are detailed:

- 1. Processing: This is the heart of the node. It includes a 8052 uC from Analog Devices (ADuC841) and a Xilinx XC3S200 Spartan 3 FPGA. The uC and the FPGA share 3 8-bit ports for communication. Hardware modifications had to be carried out to connect the JTAG port of the FPGA to the uC, to make possible remote reconfiguration.

- 2. Communication: The last version of this layer includes a ZigBee module (ETRX2 from Telegesis). This module is controlled by the uC through the UART port. A layer version with Bluetooth is also available.

- 3. Power supply: This layer generates all the voltages needed within the Cookie. Two versions have been developed, the latest with USB included, which allows power supply from a PC and serial programming for the uC.

- 4. Sensors: This layer includes those elements which are intended to take measures from the environment. Today, 3 different layers have been developed for theCookie. These layers include sensors of acceleration, temperature, humidity, light, infrared and deformation.

One of the features of the sensor layer is that it can include sensors with both digital and analog interfaces (sensors with digital interfaces will be called digital sensors, and those with analog interfaces will be called analog sensors in the rest of the paper). Signals form analog sensors are connected to the ADC of the uC. On the other side, signals from digital

Fig. 1 Processing layer (uC on the left, FPGA on the right) and full Cookie platform

sensors are connected to the FPGA. In principle, the FPGA carries out all the processing related to digital sensors, to release the uC, which manage the communications and processes analog sensors.

Nowadays, there are a myriad of sensors in the market with several different interfaces to communicate their measurements. Much of them are digital sensors, with different protocols as SPI, I2C, 1-Wire, etc. When this kind of signals have to be processed using a uC, problems related to timing and processor overhead can appear. In fact, some manufacturers offer HDL code to implement the sensor interfaces in a coprocessor [7].

In this context, a library of general HW interfaces has been developed at CEI [8] in order to process signals of sensors with very different digital interfaces. The interfaces included in the library until now are:

- I2C and I2C modified (Sensirion Company interface)

- PWM

- Period/Frequency

- 1-Wire

The library is divided in modules which represent sensor (or actuator) interfaces. Every module has been designed following a philosophy inspired in the IEEE 1451 family of standards, but can also be used without being compatible with them. Each transducer is "seen" as a channel (or set of channels) by the sensor or actuator (transducer) controller. Two kinds of channels are recognized: sensor channel and actuator channel. Some sensors, like the SHT11 from Sensirion, supply two or more measures (in this case, humidity and temperature). Therefore, for the same sensor two different channels are needed.

The uC sends triggers to the FPGA, specifying the sensor from which the measure has to be taken, and the FPGA activates the right sensor interface. Finally, the FPGA sends the result of the measure in two bytes. So, the FPGA acts as a reconfigurable coprocessor for the uC

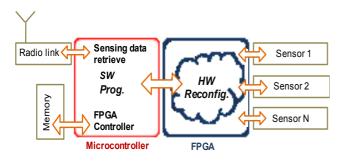

Fig. 2. HW-SW Reconfigurable Sensor Node Diagram

## III. REMOTE RECONFIGURATION

The remote reconfigurable system schematic view is shown in "Fig. 2". The problem of remote reconfiguration in the Cookie platform presents two aspects to be covered: uC reprogramming and FPGA reconfiguration.

### A. uC Reprogramming

The uC included in the Cookies (ADuC841 from Analog Devices) is programmed using its UART port. The uC includes a serial protocol in order to be able to program the uC through a host (i. e. a PC or other processor).

In the other hand, the ZigBee module is connected to the uC serial port. The uC sends commands to the ZigBee to manage the communications and sends the raw data to be delivered to the network. In order to reprogram the uC using the wireless ZigBee link a manager program (called Cookie Manager) has been developed. This manager carries out all the steps related to uC program downloading through the serial port. First of all, a ZigBee channel must be establish between the sink (network coordinator) and the remote node in which the reprogramming has to be done. Next, Cookie Manager sends all the commands needed to program the remote uC as if a real serial cable was connected between the host programmer and the remote node. Finally, the programming file is sent and is introduced in the uC flash memory. The serial downloading protocol allows starting code executing in the remote uC through a specific command.

Not only a program but other data can be loaded into the uC flash memory. So a typical file downloaded to the uC for FPGA configuration includes a program that acts as a JTAG controller and a file which includes the bitstream to be loaded into the FPGA with the instructions that the JTAG controller will follow to carry out the reconfiguration.

### B. FPGA Reconfiguration

Regarding the FPGA reconfiguration, the selected Spartan3 does not have an internal configuration port (ICAP), so the remaining configuration options are: i) Select Map and ii) JTAG. As it has been already mentioned, JTAG has been the selected reconfiguration interface. A SW implementation of the JTAG controller, provided by Xilinx, has been used [11]. Therefore no additional FPGA area is required for the reconfiguration process control, like for instance if Select Map was selected, like in [9]. On the other hand, the main

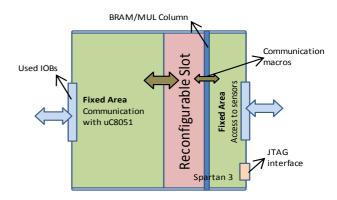

Fig. 3. HW Reconfigurable Sensor Node Spartan 3 FPGA Virtual Architecture

disadvantage of using JTAG is the reconfiguration time (JTAG is serial, while Select Map is parallel).

The JTAG configuration program running on the uC uses Xilinx specific Boundary Scan configuration files (.xsvf) where the configuration data is formatted in binary commands. In the present paper, only partial bitstreams are loaded into the FPGA, taking advantage of the partial reconfiguration capabilities of the Xilinx Spartan 3 FPGA.

To retarget the system to other FPGAs (non Xilinx) that can be programmed by JTAG, a Xilinx tool called svf2xsvf [10] can be used to transform a boundary scan standard ASCII file to a Xilinx binary file.

Once the FPGA has been configured by the uC, the final code for the application is downloaded into the uC flash memory. This step is done in the same way as it was explained before.

All these tasks can be carried out between any number of Cookies, exploiting the multihop capabilities of the ZigBee standard. This allows reconfiguring every node connected to the network with the only drawback of time delay. Tests have been done for a two hop configuration as a proof of concept. These results are shown in section V.

## IV. FPGA PARTIAL RECONFIGURATION

Partial reconfiguration in FPGAs requires defining *Virtual Architectures (VA)* on top of the selected device. For this aim, a set of steps have to be followed. Details of VAs design are outside the scope of this paper and can be found in [15]. Here, only the main aspects applied to a target Spartan 3 FPGA are included.

The first aspect to be taken into account is the VA model. VA models can be one dimensional (1D) or two dimensional (2D). According to [12], partial reconfiguration in Virtex II based architectures (this includes Spartan 3 FPGAs) is frame based, i.o.w. only reconfiguration regions that span entire FPGA columns can be defined and this permits a direct use only of 1D based VAs. A general view of the defined VA for the sensor node Spartan 3 FPGA is presented in "Fig. 3".

The structure of the Spartan 3 FPGA is quite regular in comparison with other FPGAs (Virtex II for instance). Therefore, the fixed area (the one that never changes) of the FPGA occupies only the left and right FPGA sides, because

of the regularity mentioned. The left side is in charge of the communication with the external microcontroller, while the right one is used to access the node sensors. The remaining of the FPGA, defined as reconfigurable area has a very regular structure and is divided into reconfigurable *Slots* (slots are composed only of CLB columns). In this, first approach, only one slot has been defined in the reconfigurable area because it is restricted by the needed Input Output Blocks (IOBs) for the communication with the microcontroller (left fixed area). The defined slot is 6 CLBs wide and is composed of 144 CLBs (576 Slices) in the target FPGA - XC3S200.

For slot communication with fixed areas, structures called Bus Macros are used. Two types of bus macros have been designed in this implementation. First, a vertical bidirectional macro that passes four bits of data from left to right and four bits from right to left in neighboring modules. This macro is similar to the Xilinx Bus Macros, available for Spartan 3 in [13], but the difference is that these ones are bidirectional. Our experience shows that better routing results can be achieved using bidirectional macros instead of unidirectional. The second type of macro is also a bidirectional macro, but it is used to cross the BRAM/MUL column that is allocated between the right fixed area and the reconfigurable slot. This BRAM/MUL column can be used by modules (HW Cores) loaded in the slot.

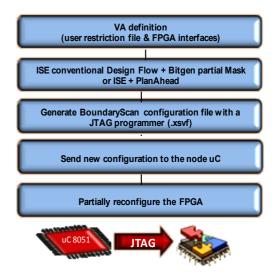

The working flow that has been developed is presented in "Fig. 4". Once the FPGA VA has been defined, that includes a user constraint file and the set of communication macros to be used, the conventional (ISE) design flow can be followed. This flow ends with the generation of a full configuration file, from which the slot configuration region is extracted using bitgen (the Xilinx tool for bitstream generation) with partial mask options. Another approach is the use of the Xilinx partial reconfiguration design flow, based on ISE and the PlanAhead tool (suitable for testing different floorplanning approaches). Differently from the first approach, the PlanAhead design flow directly results in partial configuration files and has better routing. Anyway, in the current implementation we have selected the conventional design flow because we have plenty of space in the slot and the virtual architecture floorplanning has been well defined in the first step of the working flow.

Independently from the method used to generate partial configuration files, the next step is to use the iMPACT tool to generate the needed binary formatted boundary scan configuration file to partially reconfigure the node FPGA

New FPGA partial configurations as well as new node microprocessor configurations are sent using the previously described custom software.

### V. USE CASE AND RESULTS

A use case has been setup as a proof of concept. Two different applications have been created on top of the system presented in this paper and have been alternatively loaded by remotely reconfiguring the sensor node HW and SW.

Fig. 4. Working Flow

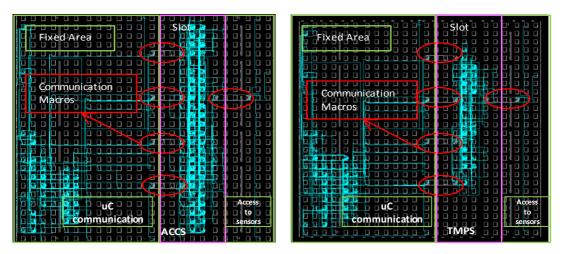

The first application uses the node accelometer and is referenced as *ACCS*, while the second one, referenced as *TMPS*, uses the node temperature sensor. The application HW part, mapped in the FPGA slot along with all the virtual architecture components can be seen in "Fig.5". Both designs HW parts include multiplier functions that can be implemented either using the embedded multipliers of the FPGA or simply using FPGA LUTs. The used area by the HW part of each application and each application version (with and without embedded multipliers) is presented in Table I. The percentage of the used slot area is also included, and it can be loaded in it without having to redefine the FPGA VA.

TABLE I FPGA USED AREA

| Design      | Used<br>MULs | Used<br>FFs | Used<br>LUTs | Used<br>Slices | % of Slot<br>Slices |

|-------------|--------------|-------------|--------------|----------------|---------------------|

| ACCS_HW_v1  | 0            | 170         | 68           | 311            | 54                  |

| TMPS_HW_v1  | 0            | 71          | 40           | 127            | 22                  |

| ACCS_HW_v2  | 2            | 127         | 68           | 232            | 40                  |

| TMPSI_HW_v2 | 2            | 63          | 40           | 111            | 19                  |

Partial configuration files have been generated from each design using the working flow presented in the previous section and the resulting file sizes in both .bit and .xsvf format are presented in Table II. Since the reconfiguration unit is a slot, the configuration files sizes are the same for both applications in "XX\_v1" (without using the embedded MULs). Differently for "XX\_v2" designs, with MULs, that use not only the slot, but also the standing next to it BRAM/MUL column, the file size increase considerably. As a reference it is important to mention that a complete XC3S200 configuration file is 131 KB and thus makes partial reconfiguration very useful for resource restricted devices.

Fig. 5. System Applications: ACCS\_HW on the left side and TMPS\_HW on the right side

TABLE II

PARTIAL CONFIGURATION FILES SIZE

Design

.bit (KB)

.xsvf (KB)

CCS\_HW\_v1

24,9

25,2

| 0           |      |      |

|-------------|------|------|

| ACCS_HW_v1  | 24,9 | 25,2 |

| TMPS_HW_v1  | 24,9 | 25,2 |

| ACCS_HW_v2  | 41,3 | 43,5 |

| TMPSI_HW_v2 | 41,3 | 43,5 |

The microcontroller program memory is 62 KB. New HW and SW configurations are loaded in this memory. The JTAG configuration program occupies 6K of the available memory, while the rest is left for the HW configuration files. A set of HW/SW configurations for each application (ACCS and TMPS) has been sent to the reconfigurable node using different type of transmission media: i) using the available communication in the sensor node (a ZigBee module) and ii) using a serial cable connection. Table III summarizes both transmission times and data rates.

| Mode       | SW (sec.) | HW(sec.) | Total (sec.) | data rate<br>(Bytes/s) |  |  |  |

|------------|-----------|----------|--------------|------------------------|--|--|--|

| Cable 8B   | 19,06     | 73,5     | 87,22        | 333,04                 |  |  |  |

| ZigBee 8B  | 49,11     | 190,22   | 219,31       | 131,95                 |  |  |  |

| Cable 16B  | 13,72     | 53,56    | 67,28        | 470,70                 |  |  |  |

| ZigBee 16B | 29,09     | 114,75   | 143,75       | 220,30                 |  |  |  |

TABLE III Configuration Times

In the table two different packetized formats can be differentiate: One of 16 Bytes and another of 8 Bytes. Both transmission packet formats have been tested in two configurations: i) a direct connection with the *Node Under Reconfiguration* (NUR) and ii) in a long distance connection with the NUR- using a node for intermediate routing (multihop). Results, included in Table III, have been measured under direct connection mode.

Reliability in WSN application is an important aspect, even more if the network is also used for transmitting device updates. Tests have shown that the 16 bytes transmission fails with a high rate in long distance connections compared with 8 bytes based transmissions that are much more reliable, but take considerably longer time. It is well known that the ZigBee standard is intended for transmitting small amount of data, also, the currently used ZigBee transmitter module does not permit low level protocol optimization and therefore, the presented results are far from being optimal. Anyway, with the expansion of the wireless sensor networks application range, new standards for nodes communication appear, like a low power WiFi version [14].

The final step, once the HW and SW configuration have been loaded into the microcontroller program memory, is to execute the JTAG programmer. The time needed for this application to partially program the FPGA is 4.2 seconds. As a comparison the time needed by the Xilinx iMPACT SW running on a PC is one second. This time can be drastically reduced if a special, FPGA specific, parallel programmer is used instead of the JTAG version.

### VI. CONCLUSIONS AND FUTURE WORK

The paper has presented a remotely reconfigurable sensor node system. The systems permits HW and/or SW updates. A simple use case, as prove of concept, has been also included in the paper. The presented approach exploits partial reconfigurable capabilities of the node state of the art Spartan 3 FPGA. As the framework is based on the JTAG standard, the solution is portable to other FPGAs. A method to use the presented framework for other, full reconfigurable, FPGAs has also been included. Results show that remote updates of WSN nodes are possible. This remote reconfiguration provides the possibility of building intelligent nodes and WSN that can be adapted dynamically to achieve a certain goal even after WSN deployment. The main drawback of the presented system is the used wireless communication module based on the ZigBee standard. High delay and fail rates during the reconfiguration process have been reported. This problem can be easily solved by simply changing the communication layer of the modular platform with a new, updated one, based on more reliable and fast communication, like WiFi. Such laver design has already been planned in the near future work. On the other hand the main drawback of currently used Xilinx FPGAs is the high power consumption, again taking advantage of the modularity of the Cookies, a new processing layer is under development that includes a very low power full reconfigurable FPGA (5 uW best case consumption) provided by Actel.

#### REFERENCES

- [1] Analysis of Deployment Methodologies for Wireless Sensor Networks, FP6-2005-IST-034642 European Project, Deliverable 8

- S. Yamshita, T. Shimura, K. Aiki, K. Ara, Y. Ogata, I. [2] Shimokawa, T. Tanaka, H. Kuriyama, K. Shimada, K. Yano, "A 15x15, 1 µA, Reliable Sensor-Net Module: Enabling Application-Specific Nodes," in Proc. of the 5th IEEE/ACM International Conference on Information Processing in Sensor Networks (IPSN'06), April 2006, pp. 383-390.

- J. Polastre, S. Szewczyk, D. Culler, "Telos: Enabling Ultra-Low Power Wireless Research", *in Proc. of the 4<sup>th</sup> IEEE/ACM* [3] International Conference on Information Processing in Sensor Networks (IPSN'05), April 2006, pp. 364-369.

- [4] H. Hinkelmann, P. Zipf, M. Glesner, "Design Concepts for a Dinamically Reconfigurable Wireless Sensor Node", in Proceedings of the 1st NASA/ESA Conference on Adaptive Hardware and Systems (AHS'06), pp. 436-441, Jun 2006.

- A. E. Susu, M. Magno, A. Acquaviva, D. Atienza, "Reconfiguration Strategies for Environmentally Powered [5] Devices: Theoretical Analysis and Experimental Validation", in Transactions on HiPEAC I, LNCS 4050, pp. 341-360, 2007.

- J. Portilla, A. de Castro, E. de la Torre, T. Riesgo, "A Modular [6] Architecture for Nodes in Wireless Sensor Networks", Journal of Universal Computer Science (JUCS), vol. 12, nº 3, March 2006, pp. 328-339.

- [7] "DS1WM, Synthesizable Verilog 1-Wire Bus Master", Dallas Semiconductor, http://www.maxim-ic.com

- J. Portilla, J.L. Buron, A. de Castro, T. Riesgo, "A Hardware [8] Library for Sensors/Actuators Interfaces in Sensor Networks", Proc. of the 13th IEEE International Conference on Circuits and Systems (ICECS'06), Nice, France, Dec. 2006.

- [9] K. Paulsson, M. Hubner, G. Auer, M. Dreschmann, L. Chen, and J. Becker. "Implementation of a Virtual Internal Configuration Access Port (JCAP) for enabling Partial Self-Reconfiguration on Xilinx Spartan-III FPGAs", in proceedings of 17th IEEE international conference on Field Programmable Logic (FPL07), Amsterdam, Netherland, August 2007.

- [10] Brendan Bridgford and Justin Cammon, "SVF and XSVF File Formats for Xilinx Devices ", XAPP 503, Xilinx, 2007.

- [11] "XAPP 058 (v. 4.0): Xilinx In System Programming Using an Embedded Microcontroller", October 2007

- [12] Davin Lim, Mike Peattie, "XAPP 290 (v1.0): Two Flows for Partial Reconfigurtion: Module Based or Small Bit Manipulation", XAPP 290, Xilinx, 2004.

- "Partial Reconfiguration Software User's Guide", Xilinx, 2006. [13]

- http://www.gainspan.com/.

- [14] <u>http://www.gainspan.com/</u>.

[15] Yana E. Krasteva, Eduardo de la Torre, Teresa Riesgo, "Virtual Architectures for Partial Runtime Reconfigurable Systems. Application to Network on Chip based SoC Emulation", to be published in Proc. of the The 34th Annual Conference of the IEEE Industrial Electronics Society (IECON 08), Nov. 2008