# Design and Validation of a model-based development process for distributed control algorithms with different target platforms

# **Master Thesis**

Enrollment number: 3292459 Master in Industrial Engineering

Institut für Steuerungstechnik der Werkzeugmaschinen und Fertigungseinrichtungen

Supervisor: M. Sc. Caren Dripke

Universität Stuttgart

Datum: 29.09.2017

# Acknowledgments

I would like to pay special thankfulness, warmth and appreciation to the persons below who made my research and personal development during this long journey successful and assisted me at every point to cherish my goal:

My Supervisor, M.Sc. Caren Dripke for giving the opportunity to join her project during this period. Her support and assistance made it possible to achieve the goal.

My Assistant Supervisor, Dipl.-Ing Florian Frick, whose help at every point during my research helped me to work in time.

To the University of Stuttgart and the people I met during this excepcoinal period, for making me feel at home and let me discover a new range of cultures, which will be really helpful in my future challenges.

My Mom, Dad and Brother, family members and friends, without whom it could not have been possible; they believed in my possibilities even when I didn't. They do not only assisted me morally and emotionally but also financially.

# Contents

| Li | st of fi   | gure             | S                                                          | V    |  |  |

|----|------------|------------------|------------------------------------------------------------|------|--|--|

| Li | st of ta   | ables            |                                                            | vii  |  |  |

| Al | obrevi     | atior            | 1S                                                         | viii |  |  |

| 1  | Int        | odu              | ction                                                      | 1    |  |  |

|    | 1.1        | Mo               | tivation/Background                                        | 1    |  |  |

|    | 1.2        | Obj              | ective                                                     | 1    |  |  |

|    | 1.3        | Sco              | pe                                                         | 2    |  |  |

| 2  | Sta        | te of            | the art                                                    | 4    |  |  |

|    | 2.1        | 2.1 Negotiation  |                                                            |      |  |  |

|    | 2.1        | .1               | Agent architectures                                        | 4    |  |  |

|    | 2.1        | .2               | System architectures                                       | 5    |  |  |

|    | 2.1        | .3               | Communication, coordination and cooperation                | 5    |  |  |

|    | 2.1        | .4               | Negotiation and conflict resolution                        | 8    |  |  |

|    | 2.2        | FPO              | GA                                                         | 8    |  |  |

|    | 2.3        | HD               | L Code                                                     | 11   |  |  |

|    | 2.4 MATLAB |                  | TLAB                                                       | 13   |  |  |

|    | 2.4        | .1               | Fixed Point vs Floating Point                              | 13   |  |  |

|    | 2.4        | .2               | MATLAB to C                                                | 14   |  |  |

|    | 2.4        | .3               | MATLAB to HDL Code                                         | 15   |  |  |

|    | 2.4        | .4               | Using HDL Coder and HDL Verifier for FPGA and ASIC Designs | 16   |  |  |

| 3  | Sys        | System modelling |                                                            |      |  |  |

|    | 3.1        | CN               | C Machine Simulation                                       | 18   |  |  |

|    | 3.2        | Neg              | gotiation protocol                                         | 24   |  |  |

|    | 3.3        | Dis              | tributed Simulation                                        | 29   |  |  |

|    | 3.3        | .1               | Explanation of the Simulation                              | 29   |  |  |

|    | 3.3        | .2               | Results                                                    | 41   |  |  |

|    | 3.3        | .3               | Improvements                                               | 43   |  |  |

| 4  | Cor        | ivers            | ion to C/HDL Code and Implementation                       | 46   |  |  |

|    | 4.1        | Cor              | oversion to C                                              | 46   |  |  |

|    | 4.2        | Cor              | version to HDL                                             | 47   |  |  |

|    | 4.2        | .1               | HDL Code verification                                      | 48   |  |  |

|    | 4.2        | .2               | Fixed-Point tool                                           | 52   |  |  |

|    | 4.3        | Imp              | plementation                                               | 56   |  |  |

|    | 4.3        | .1               | Software installation and Technical information            | 56   |  |  |

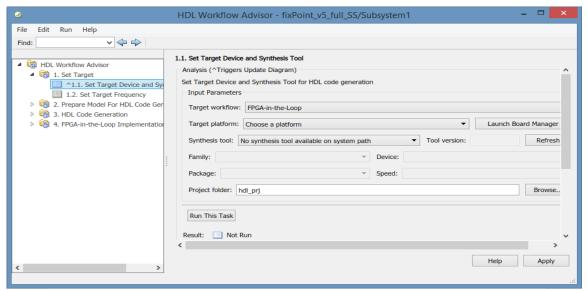

|   | 4.3.2 | 2 HDL Workflow Advisor                                | 57 |  |

|---|-------|-------------------------------------------------------|----|--|

|   | 4.3.3 | Loading programming file onto FPGA and run simulation | 59 |  |

|   | 4.4   | Inspection of the HDL Code generated                  | 60 |  |

|   | 4.4.  | Overview of the code                                  | 61 |  |

|   | 4.4.2 | FPGA Use of Material resources                        | 63 |  |

|   | 4.4.3 | Time constraints                                      | 64 |  |

| 5 | Bud   | get And Environmental Impact                          | 65 |  |

|   | 5.1   | Budget                                                | 65 |  |

|   | 5.2   | Environmental Impact                                  | 65 |  |

| 6 | Sum   | mary, Conclusions and Future goals                    | 66 |  |

|   | 6.1   | Summary and Conclusions                               | 66 |  |

|   | 6.2   | Future works                                          |    |  |

| 7 | Bibl  | ibliography68                                         |    |  |

## LIST OF FIGURES

| Figure 1: Gantt chart                                                                 | 3  |

|---------------------------------------------------------------------------------------|----|

| Figure 2: Representation of the conversation policy for a request [3]                 | 7  |

| Figure 3: Representation of Moore's Law. [10]                                         | 10 |

| Figure 4: Internal structure of an FPGA (National Instruments Tutorial – 2010)        | 11 |

| Figure 5: Example of Gate Map (Tala, D. K.URL: http://www.asic-                       |    |

| world.com/verilog/synthesis1.html)                                                    | 12 |

| Figure 6: Three-Step Workflow                                                         | 14 |

| Figure 7: Example of Polymorphism                                                     | 15 |

| Figure 8: Model-Based Design workflow                                                 | 16 |

| Figure 9: Desired trajectory                                                          | 19 |

| Figure 10: Layout of the Master System                                                | 19 |

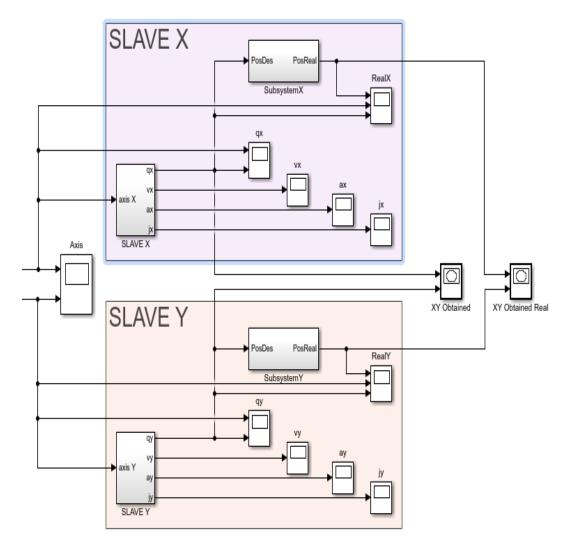

| Figure 11: Layout slaves                                                              | 20 |

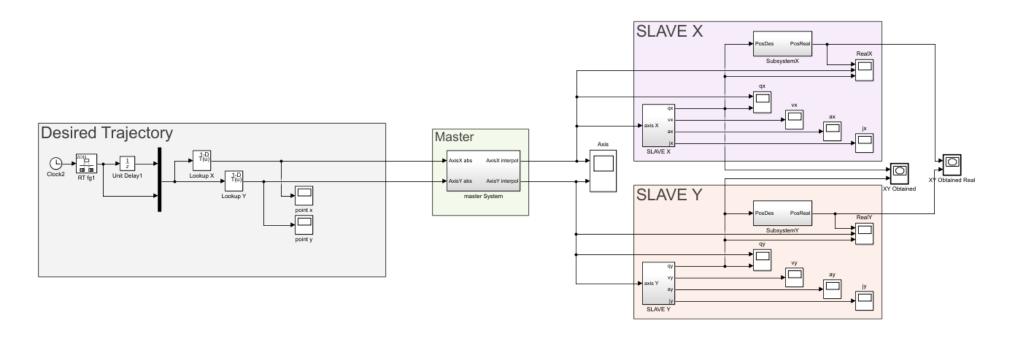

| Figure 12: Layout of CNC simulation                                                   | 21 |

| Figure 13: Layout of the Subsystem X (same as Subsystem Y)                            | 21 |

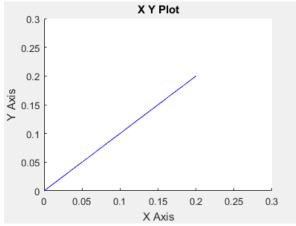

| Figure 14: Desired position                                                           | 22 |

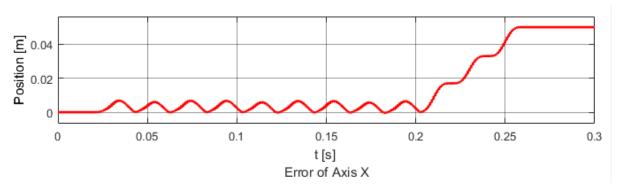

| Figure 15: Error of the Axis X                                                        | 22 |

| Figure 16: Evolution of position, velocity and acceleration                           | 23 |

| Figure 17: Message Type 1                                                             | 24 |

| Figure 18: Message Type 2                                                             | 25 |

| Figure 19: Message Type 3                                                             | 25 |

| Figure 20: Topology of the system                                                     | 25 |

| Figure 21: State diagram of com                                                       | 27 |

| Figure 22: State diagram of MOT                                                       | 27 |

| Figure 23: State diagram of GSM including the retries                                 | 28 |

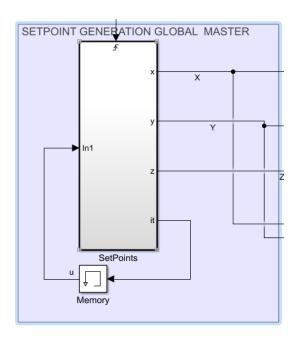

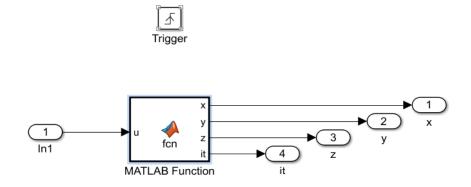

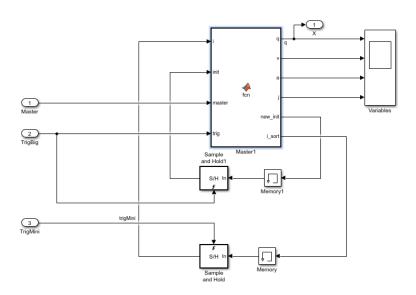

| Figure 24: Subsystem Set Point Generation                                             | 30 |

| Figure 25: View of the inside of the Subsystem                                        | 30 |

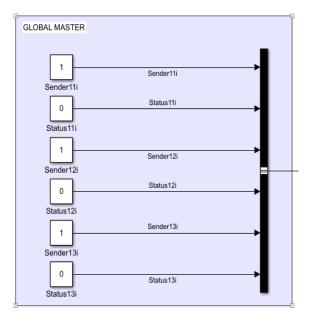

| Figure 26: Sender and Status of Global Master                                         | 31 |

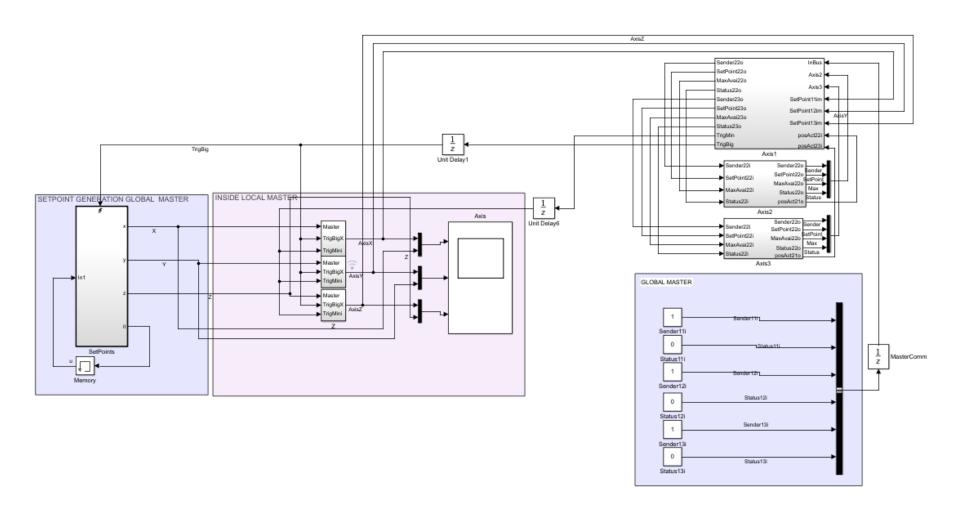

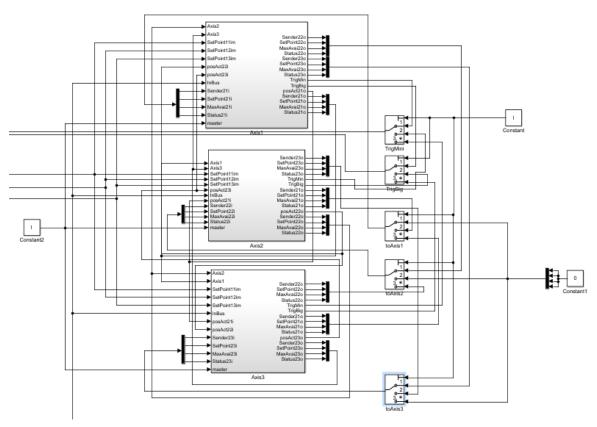

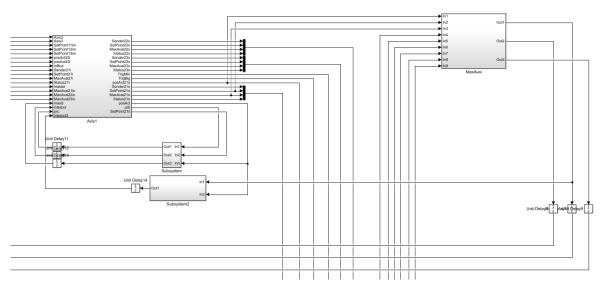

| Figure 27: Layout Distributed Simulation                                              | 32 |

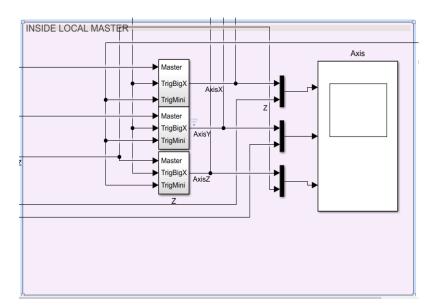

| Figure 28: Layout of the first part of the Local Master                               | 33 |

| Figure 29: Layout of the X Subsystem                                                  | 33 |

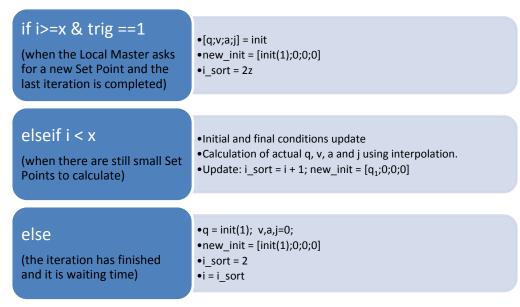

| Figure 30: Workflow of the Interpolation function                                     | 35 |

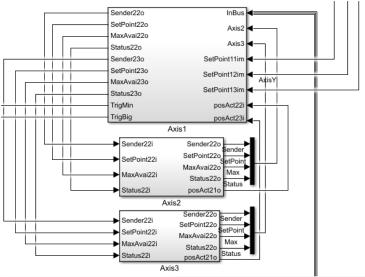

| Figure 31: Layout of the Axes                                                         | 35 |

| Figure 32: Layout of Axis 1                                                           | 36 |

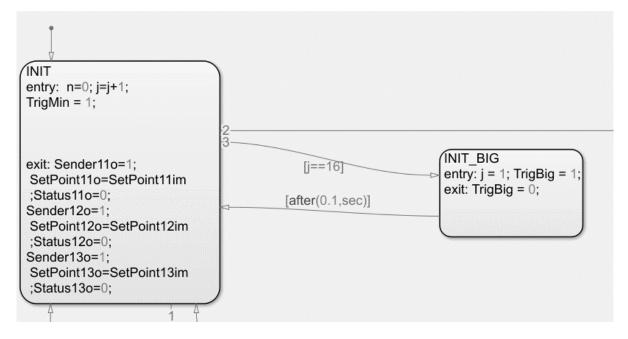

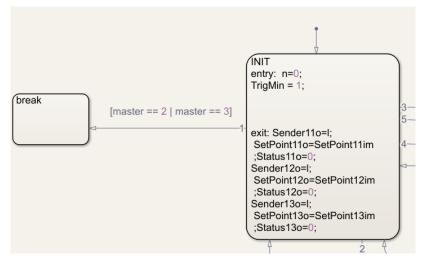

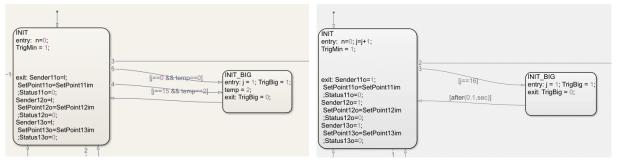

| Figure 33: Initialization of the GSM                                                  | 37 |

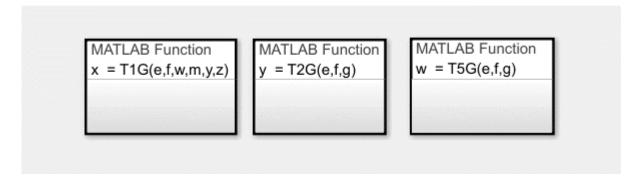

| Figure 34: The functions that govern the transitions                                  | 38 |

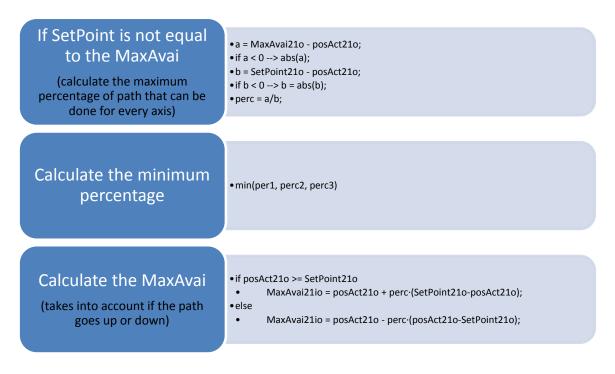

| Figure 35: Workflow of the MAXAvai Function                                           | 39 |

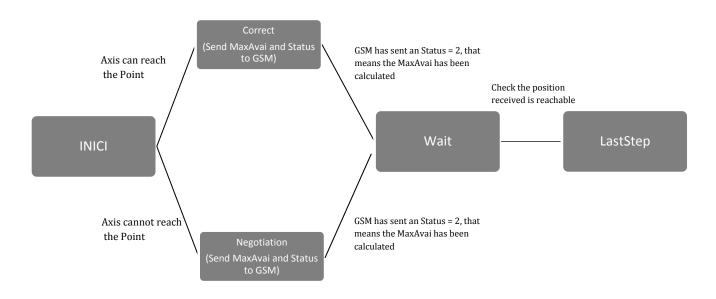

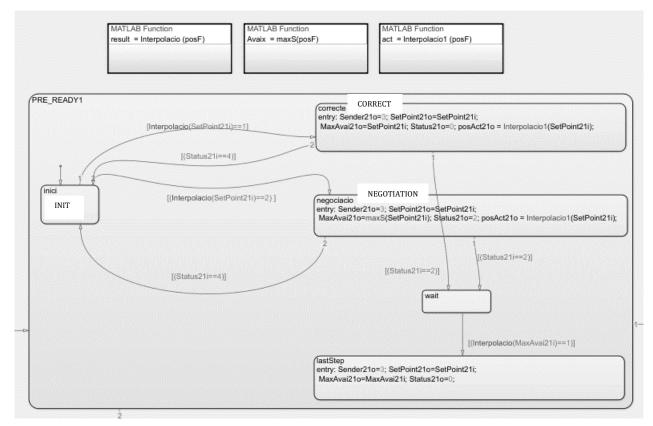

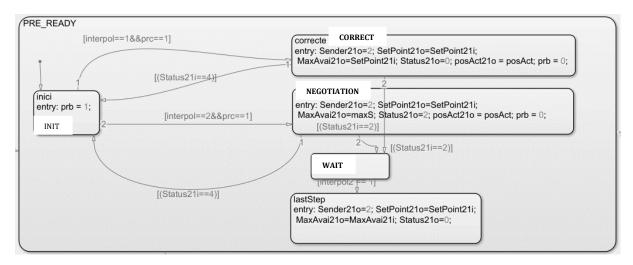

| Figure 36: Process explanation of the pre_ready state                                 | 39 |

| Figure 37:Layout of PRE_READY State of COM state machine                              |    |

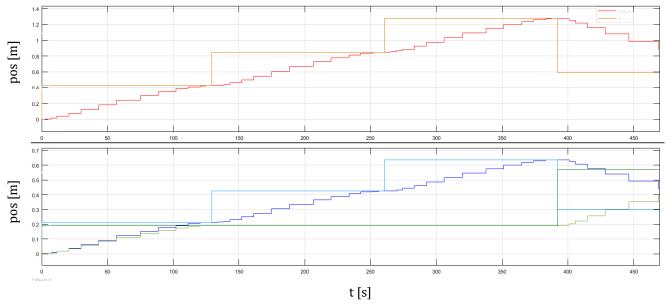

| Figure 38: Above X path and below Y and Z                                             | 41 |

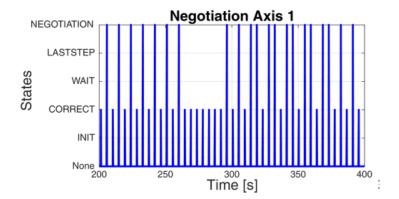

| Figure 39: Representation of the PRE_READY of the COM1 state machine                  |    |

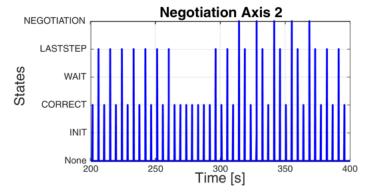

| Figure 40: Representation of the PRE_READY of the COM2 state machine                  | 42 |

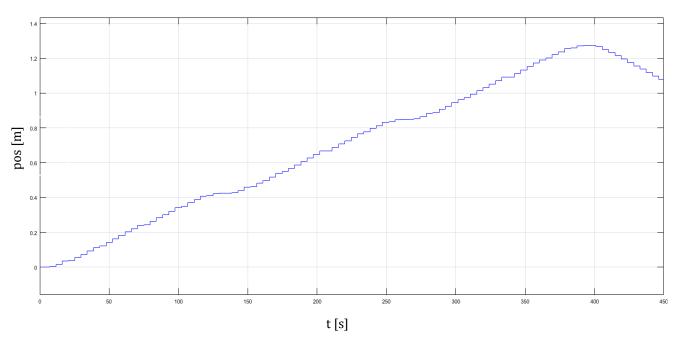

| Figure 41: Output of the position of the MOT state machine of Axis 1 – Path generated | 43 |

| Figure 42: Layout of the modified axes                                                | 44 |

| Figure 43: BREAK state inside the GSM machine of Axis 1                               | 44 |

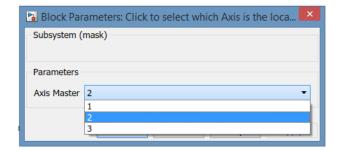

| Figure 44: Mask to select the Local Master                                    | 45 |

|-------------------------------------------------------------------------------|----|

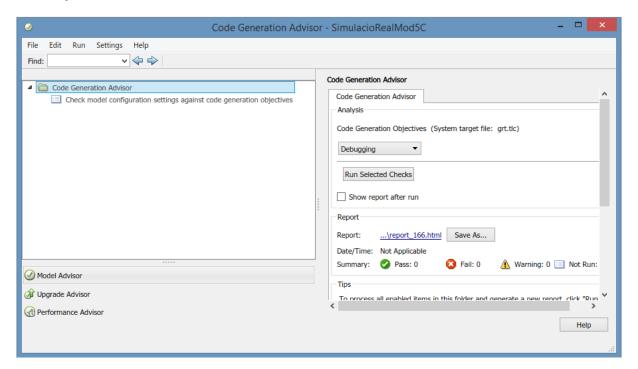

| Figure 45: Code Generation Advisor                                            | 46 |

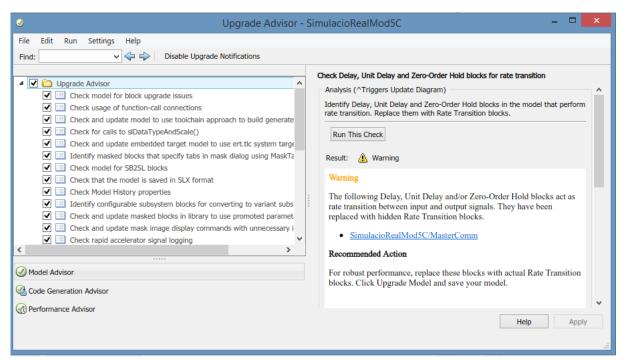

| Figure 46: Upgrate Advisor                                                    | 47 |

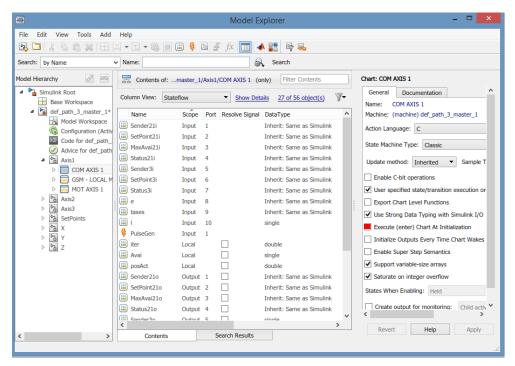

| Figure 47: Model Explorer panel                                               | 48 |

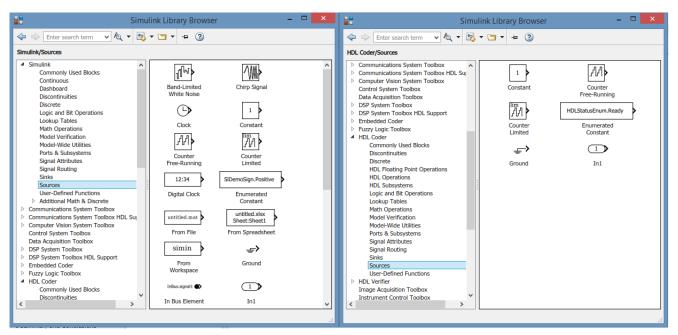

| Figure 48: Comparison of Library browser of HDL and General Simulink          | 49 |

| Figure 49: Conversion applied                                                 | 50 |

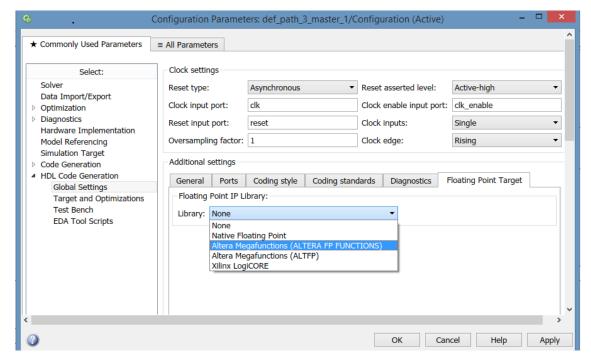

| Figure 50: FLoating Point Libraries                                           | 50 |

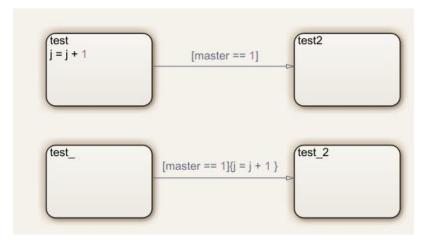

| Figure 51: Changes applied to avoid an Initial value of j                     | 51 |

| Figure 52: Code for the MATLAB function to convert into Boolean               | 52 |

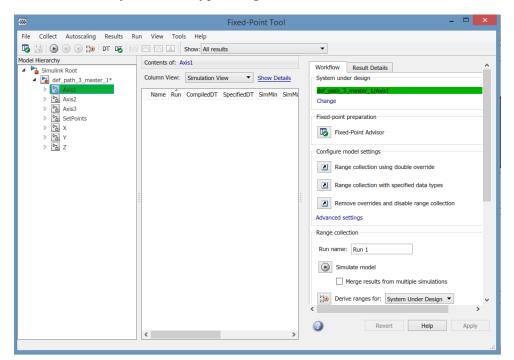

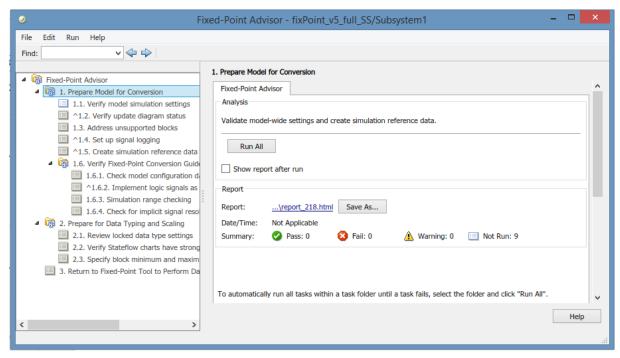

| Figure 53: Fixed-Point Tool                                                   | 52 |

| Figure 54: New Layout with the functions outside of the Axis                  | 53 |

| Figure 55: PRE_READY State after the modifications                            | 54 |

| Figure 56: Fixed-Point Advisor                                                | 55 |

| Figure 57: HDL Workflow Advisor                                               | 57 |

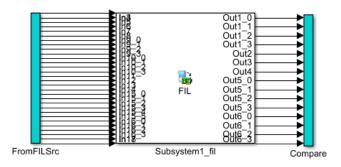

| Figure 58: Subsystem generated after the conversion                           | 59 |

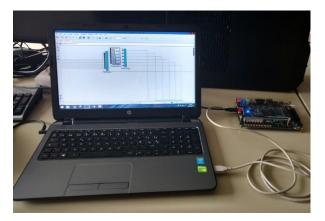

| Figure 59: Running simulation on the right and detail of the FPGA on the left | 59 |

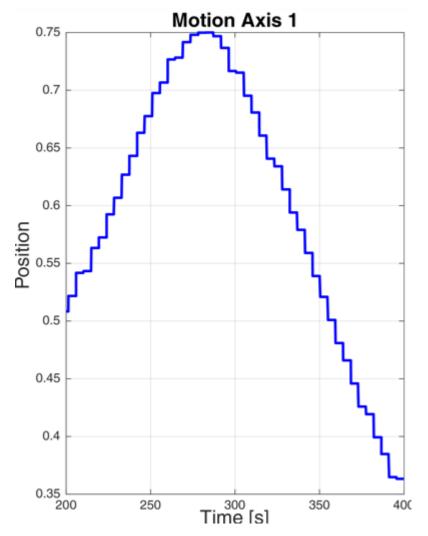

| Figure 60: Output position of axis 1                                          | 60 |

| Figure 61: First lines of .vhd Code                                           | 61 |

| Figure 62: Hierarchy definition of main subsystem                             | 61 |

| Figure 63: Subsystem after main Subsystem                                     | 61 |

| Figure 64: Rate and Clocking Details                                          | 61 |

| Figure 65: Definition of entities of COM                                      | 62 |

| Figure 66: IF statements related to the States of the MOT state machine       | 62 |

| Figure 67: Mathematical operations implemented in HDL                         | 63 |

| Figure 68: Conversion finished successfully but with warnings                 |    |

| Figure 69: High slack found in the time report                                | 64 |

### LIST OF TABLES

| Table 1: Advantages and Disadvantages of a FPGA                           | 11 |

|---------------------------------------------------------------------------|----|

| Table 2: Comparison between Fixed Point and Floating Point                | 13 |

| Table 3: Values are given to the frequency variables                      | 18 |

| Table 4: Explanation of the transitions of com machine                    | 27 |

| Table 5: Explanation of the transition of MOT machine                     | 27 |

| Table 6: Explanation of the transitions of GSM                            | 28 |

| Table 7: Technical information about the DE1-SoC Board                    | 56 |

| Table 8: Usage of the FPGA resources                                      | 59 |

| Table 9: Comparison of the FPGA usage of resources in the different tests | 63 |

| Table 10: Material and Software Cost                                      | 65 |

| Table 11: Human Resources Cost                                            | 65 |

# **ABBREVIATIONS**

| CNC     | Computer Numerical Control                                                                 |

|---------|--------------------------------------------------------------------------------------------|

| FPGA    | Field Programmable Gate Array                                                              |

| CPU     | Central Processing Unit                                                                    |

| ISW     | Institute for Control Engineering of Machine Tools and Manufacturing Units                 |

| HDL     | Hardware Description Language                                                              |

| KS      | Knowledge Source                                                                           |

| DCS     | Distributed Control System                                                                 |

| DEVEKOS | Consistent engineering for safe, distributed and communicating multi-<br>component systems |

| VHDL    | VHSIC Hardware Description Language                                                        |

| VHSIC   | Very High Speed Integrated Circuit                                                         |

| I/0     | Input / Output                                                                             |

| MATLAB  | MATrix LABoratory                                                                          |

| MOSFET  | Metal-Oxide-Semiconductor Field-Effect Transistor                                          |

| NFETS   | n-channel FET (Field-Effect Transistor)                                                    |

| PFETS   | p-channel FET (Field-Effect Transistor)                                                    |

| CMOS    | Complementary Metal-Oxide Semiconductor                                                    |

| IC      | Integrated Circuit                                                                         |

| TTL     | Transistor-Transistor Logic                                                                |

| PROM    | Programmable Read-Only Memory                                                              |

| EPROM   | Erasable Programmable Read-Only Memory                                                     |

| DST     | Depleted-Substrate Transistor                                                              |

| PLA     | Programmable Logic Array                                                                   |

| PAL     | Programmable Array Logic                                                                   |

| EEPROM  | Electrically Erasable Programmable Read-Only Memory                                        |

| GAL     | Generic Array Logic                                                                        |

| ANSI    | American National Standards Institute                                                      |

| DSP     | Digital Signal Processing                                                                  |

| ASIC    | Application Specific Integrated Circuit                                                    |

| ALM     | Adaptive Logic Module                                                                      |

| PLL     | Phase-Locked Loop                                                                          |

### 1 Introduction

#### 1.1 MOTIVATION/BACKGROUND

This master's thesis is written at the Universität Stuttgart and submitted to Universitat Politècnica de Catalunya in partial fulfillment of the requirements for Master of Science degree in Industrial Engineering. The thesis is carried out by the student Laura Villar Rio, participating in the Erasmus+ exchange program. It is supervised by M.Sc Caren Dripke, researcher of the Institute for Control Engineering of Machine Tools and Manufacturing Units (ISW).

The thesis is also framed within the DEVEKOS project, a project carried out by several organizations such as the ISW. The context of this project is the age of digitization and industry 4.0. Thanks to the miniaturization of the electronics, control, actuators and sensors now the components can be integrated into a tight space. The embedded software makes such components intelligent and they offer their own abilities in the form of manufacturer-standardized automation functions. These skills are composed in the engineering of machine integrators to higher-quality skills until a level of skill is reached that corresponds to the process of the product being produced. This results in a component-based automation with a suitable component-oriented engineering approach - both prerequisites for the implementation of the currently emerging industry 4.0 standards.

A Distributed Control System (DCS), which will be implemented in this thesis, increases reliability and reduces installation costs by localizing control functions near the process plant, but enables monitoring and supervisory control of the process remotely. The key attribute of a DCS is its reliability due to the distribution of the control processing around nodes in the system. This mitigates a single processor failure. If a processor fails, it will only affect one section of the plant process, as opposed to a failure of a central computer, which would affect the whole process, increasing also productivity. This distribution of computing power local to the field Input/Output (I/O) field connection racks also ensures fast controller processing times by removing possible network and central processing delays. Another advantage, which makes these systems appropriate for the Industry 4.0, is that the introduction of distributed control allowed easy interconnection and re-configuration of plant controls such as cascaded loops and interlocks, and easy interfacing with other production computer systems.

In line with the digitization that Industry 4.0 heralds, future control system functionality will be decided by software and firmware upgrades and be completely independent of hardware in the future. This will allow the user to purchase the control system hardware with limited functionality and as requirements increase they can continue to upgrade to add additional functionality as required — such as faster cycle times, additional communication interfaces etc. To achieve this goal this project is going to use Field Programmable Gate Arrays (FPGAs) completely reprogrammable and with high capabilities.

It also allows faster update times when new functionality is developed as this functionality can be available as soon as the firmware is upgraded, in the same way as a smartphone.

#### 1.2 OBJECTIVE

This Master Thesis should simulate a basic distributed interpolation task with Simulink, where multiple axes move in a group with distributed interpolation.

Distributed interpolation is the base of Distributed Control Systems (DCS). This is a type of automated control system that is distributed throughout a machine to provide instructions to different parts of the machine. Instead of having a centrally located device controlling all machine components, each section of a machine has its own computer that controls the operation. A DCS is commonly used in manufacturing equipment and utilizes input and output protocols to control the machine components. [1]

A concept of a control algorithm for distributed interpolation shall be developed that connects basic axis interpolation techniques with a communication concept for distributed negotiation on motion tasks. All axes should have the same set up with three basic functionalities. First, each axis issues a valid set point for each interpolation cycle. Second, the axis reacts and responds to inquiries from an external master that coordinates and negotiates a motion sequence for all axes only when all participating axes are ready for movement and can achieve the requested motion dynamics. Lastly, it communicates errors as well as a successful finish of a requested motion. Task times are crucial in this setup, as the communication/negotiation dialog needs to happen at a higher frequency as several rounds of inquiries might be needed until an agreement on the motion is ready to be executed. The result of this task should be a fully autonomously running motion execution of all axes complete with necessary negotiations and possible error states of axes, preferably paired with a behavior visualization of the separate components in order to track the internal negotiations. The modularity and extensibility of all components are presupposed.

This set up of modules should then be converted into C or VHDL Code using the Workflow described in the documentation of the MATLAB (HDL) Coder. The development process should be thoroughly documented and analyzed especially on hardships with the automated code conversion. A specific focus should be taken onto the offered top level in/outputs to the modules and how the user can configure them. The converted modules are then deployed on appropriate hardware with a sensible Input / Output visualization of the internal processes.

Algorithms for distributed interpolation need to be deployed on either Central Processing Units (CPUs) or FPGAs. As the algorithm development and validation is mostly taking place in MATLAB, it is necessary to convert the code into embedded programming languages. MATLAB offers conversion software for both cases, called MATLAB Coder and MATLAB HDL Coder, but many constraints must be considered in order to successfully convert algorithms.

#### 1.3 Scope

In terms of time scope and as this thesis is developed in the context of the European exchange program (Erasmus+) its duration it is limited until end of September 2017.

The specific time flow of this project can be checked in more detail in Fig.1 with the representation of the Gantt chart:

| Tasks                       | Duration (days) | Date of Start | Date of End | 01.April | 01.May | 01.June | 01.July | 01.August | 01.Sept. |

|-----------------------------|-----------------|---------------|-------------|----------|--------|---------|---------|-----------|----------|

| State of the Art            | 29              | 01/04/2017    | 30/04/2017  |          |        |         |         |           |          |

| CNC Simulation              | 18              | 01/05/2017    | 19/05/2017  |          |        |         |         |           |          |

| Negotiation Protocol        | 30              | 20/05/2017    | 19/06/2017  |          |        |         |         |           |          |

| Distributed Simulation      | 30              | 20/06/2017    | 20/07/2017  |          |        |         |         |           |          |

| Conversion to C & HDL Code  | 31              | 20/07/2017    | 20/08/2017  |          |        |         |         |           |          |

| Implementation              | 20              | 21/08/2017    | 10/09/2017  |          |        |         |         |           |          |

| Conclusions & Summary       | 5               | 10/09/2017    | 15/09/2017  |          |        |         |         |           |          |

| Writing Final Thesis Report | 14              | 01/09/2017    | 15/09/2017  |          |        |         |         |           |          |

| Submission Thesis Report    | 14              | 15/09/2017    | 29/09/2017  |          |        |         |         |           |          |

| Thesis Presentation         | 11              | 15/09/2017    | 26/09/2017  |          |        |         |         |           |          |

FIGURE 1: GANTT CHART

#### 2 STATE OF THE ART

This chapter is a summary of the state of the art of the different elements which will be used in this thesis.

As it has been mentioned in Chapter 1 a distributed control algorithm will be developed, validated and implemented. In order to obtain a successful algorithm, it is necessary to implement a proper negotiation technique, which fulfills the requirements of time and precision. In this context, a basic explanation of negotiation protocols can be found at the beginning of this chapter.

It has also been considered necessary to speak about the hardware, which will be used to achieve the goal, FPGAs. A brief explanation about what they are, why they have been chosen above microcontrollers and its coding language (HDL) will be introduced. The section will also refer to C language (the coding language for microcontrollers) because even though they are not going to be tested in this case, they are widely used in the field. Once the algorithm has been designed and validated with MATLAB, it will be converted into the embedded languages C/HDL through MATLAB Coder and HDL Coder, which will be also described.

#### 2.1 Negotiation

"A negotiation is a bargaining (give and take) process between two or more parties (each with its own aims, needs, and viewpoints) seeking to discover a common ground and reach an agreement to settle a matter of mutual concern or resolve a conflict. The noun form of the verb negotiate."

Business Dictionary, May 2017

In the context of this thesis, negotiation is carried out between the axes and the external master. The process consists of 3 steps: each axis receives a valid set point for each interpolation cycle. Later, axes communicate and answer to inquiries from the external master that coordinates and negotiates a motion sequence for all axes and orders them to move only when all are ready for movement. Third, each axis communicates possible errors as well as a successful finish of a requested motion. This process is crucial for the correct development of the project. For this reason, in this section, several architectures and negotiation techniques, which are considered of interest, are explained and context is also provided.

#### 2.1.1 AGENT ARCHITECTURES

An Agent is a person/object which acts on behalf of another person or group. In this case, the axes and the external master are the agents of the system.

The internal architecture of an agent is essentially the description of its modules and how the selected modules are organized in relation to each other. There are some remarkable desired characteristics that these architectures should have, such as: network-centric, communicative (axes have to communicate with each other and with the master), semi-autonomous (axes are able to know if they can achieve a determined set point and communicate its decision to the master), proactive, adaptable (axes give a set point alternative if they cannot achieve the desired one), flexible, mobile, deliberative... [3]

Agent architectures can be described using two types of classification: by behavior and by internal organization. In this case, the focus will be made in the behavior organization because it adjusts better to the project characteristics:

#### • By behavior: [4]

- Deliberative: Also called cognitive agents. They have domain knowledge and planning capability to undertake a series of actions and cooperate with other agents to achieve a task. One well-known deliberative agent architecture is the BDI (Beliefs, Desires, and Intentions). The beliefs are the expectations of the agent about a current state of the world, desire is an abstract notion which specifies preferences for future world states and intentions are what the agent is committed to doing.

- *Reactive:* Or behavior-based architectures. They respond in an event-condition-action mode. They do not have internal models of the world. They only respond to external stimulation and the information available from the sensing of the environment. The use of symbolic representation is neglected, they only share low-level data. The deliberative reasoning is replaced by emerging behavior, which adapts to changes in the real-world environment in a timely way. It has a quick response time.

- *Hybrid:* The most popular combination is to join deliberative and reactive types.

The architecture that will be implemented is hybrid, a mix between deliberative and reactive. The axes are deliberative because they have previous knowledge of their capabilities (position range, maximum velocity, acceleration, jerk...). But the local master is reactive, because it only gathers information from the axes and reacts to it, it does not know, which are their capabilities.

#### 2.1.2 System architectures

A multi-agent system architecture is a pattern of relationships among the agents (considering agents in the large). [3]

It is possible to classify agent-based system architectures into three categories:

- 1. Hierarchical: centralized behavior.

- 2. *Federated:* As it solves the problem related to the hierarchical, they are increasingly being considered as a solution. There is no explicit shared facility for storing active data. Several approaches have been considered such as the facilitator, the broker, and the mediator.

- 3. *Autonomous:* Any other software or a human being does not control it. It can communicate directly with any other agent of the system or external, has its own goals, and associated set of motivations.

The system architecture approach that will more likely be considered is the federated with the external master acting as a mediator. Axes respond to the requests of the master but they have their own capabilities.

#### 2.1.3 Communication, coordination and cooperation

Communication, coordination, and cooperation are three keys issues in terms of negotiation and in multi-agent systems:

#### Communication [3]

Communication enables agents to exchange information and to coordinate their activities. It is necessary to speak about levels of communication, modes and speech act theory.

Communication can exist in levels of sophistication as it is listed below:

- *No communication:* communication is not always necessary and it can be solved through speculation. However, if all the agents apply that method the possibilities can be infinite.

- Message and plan passing: agents communicate with each other sending messages. In the plan-passing approach agent A communicates its total plan to B and B does the same to A. Cooperation can be achieved but the computational cost is expensive, there is no guarantee that the resulting plan will be compatible with the recipient's knowledge. Total plans are difficult to derive in real world applications because of the existent uncertainty about the present state of the world.

- Information exchange through a *shared data repository*. The shared data repository is used for agents to write messages to or post partial results on, and obtain information from.

- *High-level of communication:* natural language understanding, speech act theory, conversations, and other formal theories. In this current case, this level of communication is needed. Axes should negotiate and constantly send messages to the master in order to achieve a successful movement.

Agent communication can be implemented in different ways depending on the nature of the agents, the global architecture of the system, timing or number of receivers of the message [3] [4]:

- *Direct/indirect:* direct communication is realized through message passing and indirect using a shared data repository.

- *Synchronous / asynchronous:* synchronous mode means working in the same location at the same time and asynchronous in the same location but at different times.

- *Single / multiple recipients:* the communication possibilities are point-to-point (one to one), broadcast (one to all others) and multicast (one to a selected group).

The system studied is direct, synchronous and multicast / point-to-point.

Many communication theories are based in Speech act theory and it is primarily concerned with natural language utterances. The categorization of speech acts by message types is shown below [5]:

- *Assertive:* "The production line has been improved."- Information.

- *Directive:* "Work to improve the production line." Order.

- *Commissive:* "I will work to improve the production line" Future.

- *Permissive:* "You may work to improve the production line" Permission.

- *Prohibitive:* "The production line will be stopped next month." Declaring decision/announcement.

To speak about communication, it is essential to understand what a conversation in terms of agents is:

"A conversation in this context, it is understood as a sequence of messages between two agents, taking place over a period of time, bounded by certain termination conditions for any given occurrence."

Shen, Weiming et al. Multi-agent systems for concurrent intelligent design and manufacturing. [3]

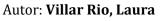

Finite State Machines, Petri Nets or Enhanced Dooley graphs, can represent a conversation as in Figure 2.

FIGURE 2: REPRESENTATION OF THE CONVERSATION POLICY FOR A REQUEST [3]

#### Coordination

The coordination is the process by which an agent reasons about its local actions and the anticipated action of others to try to ensure the community acts in a coherent manner. Therefore, coordination among agents is essential for achieving the goals and acting in a coherent manner. Coordination implies considering the actions of the other agents in the system when planning and executing one agent's actions. Coordination is also a means to achieve the coherent behaviour of the entire system. Coordination may imply *cooperation* and in this case the agent society works towards common goals to be achieved, but may also imply *competition*, with agents having divergent or even antagonistic goals. In our case, we can speak about cooperation because they try to achieve a same global goal, which can only be achieved working together (global Set Point). [3][6].

#### Cooperation

"Cooperation is the act of working together with someone or doing what they ask you."

Cambridge Dictionary, September 2017

Cooperation is necessary due to complementary abilities, to the interdependency that exists among agent actions and to the necessity to satisfy some global restrictions or criteria of success. In a cooperative model of problem solving the agents are collectively motivated or collectively interested, therefore they are working to achieve a common goal. [6]

#### 2.1.4 Negotiation and conflict resolution

The first step to resolve a conflict will be to detect it. Then, agents will use communication channels and try to eliminate them. Negotiation is done by exchanging messages among agents. Since the process involves several messages, a discussion will take place in which each agent's attitude will be an important factor. This attitude is governed by an agent's beliefs and goals and by global situation. The negotiation process follows rules, which together implement a strategy.

For instance, the master will detect that not all axes can achieve the set point given and start a negotiation with them until reaching the closest one. The axes will use their knowledge about their maximum velocity and acceleration and offer to the master a possible set point solution.

The negotiation strategies are the ones who decide the position of a particular agent in the negotiation process. In the past, agents were restricted to a fixed strategy which consisted in acting according to their beliefs and did not have a global view of the problem. The evolution moves into flexible strategies such as [3][7]:

- Contract based negotiation: each agent (manager), having some work to subcontract, broadcasts an offer and waits for the other agents (contractors) to send bids. After some delay, the best offers are retained and contracts are allocated to one or more contractors who process their subtasks.

- *Market-based approaches:* the goal is to solve a distributed resource allocation problem. Agents are classified as producers and consumers. Equilibrium is reached when the prices of goods are such that all resources are being used up.

- *Game theory based negotiation:* [8] the global outcome is given in a table showing the results of combined decisions. Each player, however, makes decisions independently. The key concepts are utility functions, a space of deals and strategies and negotiation protocols. One of the most well-known example of this theory is the prisoner's dilemma.

- *Plan based negotiation:* it is based on cooperation strategies for resolving conflicts among plans of a group of agents. Agents plan activities separately and, then, they coordinate their plans.

- *AI based negotiation:* as almost every human interaction requires negotiation, this new technique seems to suit perfectly.

Market-based approach and Game theory based negotiation seem to fit into the requirements. A deeper analysis of its implementation should be carried out.

#### 2.2 FPGA

A Field Programmable Gate Array is a prefabricated silicon device that can be customized for a specific application. Unlike traditional CPUs, FPGAs are "field-programmable," meaning they can be configured by the user after manufacturing.

A better way to understand how and why the FPGAs where developed, a brief resume of electronics field development is carried out [10]:

- <u>1960 — MOSFET:</u> Metal-Oxide-Semiconductor Field-Effect Transistor is one of the most basic elements in a FPGA. In the world of FPGAs, they are usually referred to as gates. They are used similarly to switches. Depending on what value they receive, 0 or 1, they will

either block or allow the flow of current. There are two main types of MOSFETs, PFETS and NFETS.

- <u>1961 IC:</u> An Integrated Circuit is a small chip that has a set circuit on it. ICs were an upgrade from using transistors to build circuits because they are generally printed. This way you can print an entire circuit in one shot, rather than having to assemble the circuit with possibly thousands of transistors. This saves time and space.

- <u>1962 TTL:</u> A Transistor-Transistor Logic is a family of ICs. Rather than being made of MOSFETs like the ICs, a TTL is made with BJTs (Bipolar Junction Transistors). The main advantage of the TTL over the IC is that it consumes less power and is less sensitive to damage from electrostatic discharge.

- 1963 CMOS: A Complementary Metal-Oxide Semiconductor is another improvement on

the IC technology in the construction part. They reduce waste heat as there is no standing current during the transition.

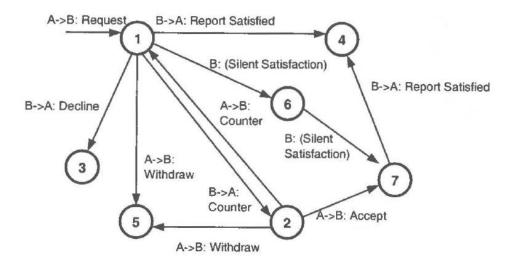

- <u>1965 — Moore's Law:</u> This law (see Fig. 3) is based on the prediction that the number of transistors in each circuit doubles every year. It is now used in industry and research to set goals. Unfortunately, soon Moore's Law may not hold, as technology is getting to the point where transistors are a number of silicon atoms wide.

#### FIGURE 3: REPRESENTATION OF MOORE'S LAW. [10]

- <u>1970 PROM:</u> Programmable Read-Only Memory was one of the first types of programmable memory. Previously there had been ROM (Read-Only Memory) where the data was set at manufacturing. Although PROM was a huge step in programmable technology, there was still improvement to be made, as it wasn't reprogrammable. Once you set the memory, it was permanent.

- <u>1971 EPROM:</u> Erasable Programmable Read-Only Memory was the second step in programmable memory, in that it could be erased. To erase an EPROM, you had to shine UV-light directly on the Eprom. However, this type of erasing was not the most practical, as it was necessary to take the EPROM out of the circuit to erase it.

- <u>1972 DST</u>: A Depleted-Substrate Transistor is similar to a MOSFET, except that it has no voltage difference from its gate to source. This provides higher gain and low noise as compared to a normal MOSFET.

- <u>1975 PLA:</u> A Programmable Logic Array is made up of programmable AND gate planes and programmable OR gate planes, connected to product a desired output. With this type of programmable logic you could most directly implement POS (Product Of Sums), OR gates then AND gates, and SOP (Sum Of Products), AND gates then OR gates, which are now only used as a formalism in design, and teaching tool. This allowed for programmable logic, but nothing near the complexity of design that FPGAs allow.

- <u>1978 PAL:</u> Programmable Array Logic is similar to PLA; however, rather than having two programmable planes, it instead has one PROM array, a fixed OR plane, and a programmable AND plane. This only allows for the sum of products logic equations with feedback from the outputs.

- <u>1983 EEPROM:</u> Electrically Erasable Programmable Read-Only Memory offered an extensive improvement from EPROM, it was erasable electrically. This allowed for data to be read, erased, and reprogrammed. However, EEPROMs only allow for a certain number of times it can be reprogrammed.

- <u>1983 GAL:</u> Generic Array Logic was a major improvement on PAL. GAL is completely erasable and re-programmable.

- <u>1984 FLASH:</u> Flash memory is a type of EEPROM, and it is the most commonly used non-volatile memory. One major improvement from the EEPROM is that FLASH memory can be erased in blocks. So, rather than having to erase all of the memory and rewrite it, you can choose what memory to erase.

- <u>1985 FPGA:</u> The first FPGA was developed.

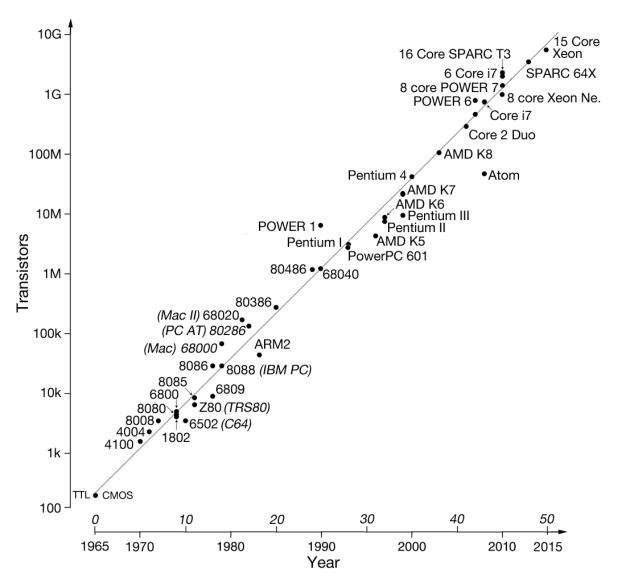

A FPGA has an internal structure which can be divided in four main components (see Fig.4) [11] [12]:

- 1) <u>Configurable Logic Blocks (CLB):</u> Hundreds or thousands of these blocks that can be interconnected between them and the I/O blocks through the Programmable Interconnects. Inside each of them basically, there is a lookup table, one or several flipflops with clock and reset function and the possibility to choose any output.

- 2) <u>Programmable Interconnects:</u> Programmable routing that connects these logic functions created with CLB.

- 3) I/O Blocks: Input / Output blocks. They are the components, which allow data transfers in and out of the FPGA. The inputs and outputs of the chip go through component groups called I/O banks, which consists of 50 individual I/O blocks. The

I/O blocks themselves are configurable in a number of ways depending on the type of data the user is either expecting to receive or transmit. These are similar to transceivers but operate at lower speeds and can maintain more functional flexibility. A simple analogy to distinguish the two would be to consider having a choice of the vehicle between a car (I/O block) and a jet (transceiver) for a commute. Even if the distance allowed to get the take off speed of the jet, it would be wildly impractical to operate.

4) <u>Flash Memory:</u> A configurable external Flash Memory is necessary because the FPGA is volatile, that means when the FPGA is disconnected it becomes blank again.

FIGURE 4: INTERNAL STRUCTURE OF AN FPGA (NATIONAL INSTRUMENTS TUTORIAL – 2010).

The advantages of a FPGA among a microcontroller are several and they are listed in the Table 1 below with the disadvantages:

| Advantages                                  | Disadvantages                                  |  |

|---------------------------------------------|------------------------------------------------|--|

| Everything can be programmed.               | High price.                                    |  |

| Extremely fast.                             | Large use of power.                            |  |

| Massive parallel calculation (with separate | Volatile.                                      |  |

| processing).                                |                                                |  |

| High I/O count.                             | High pin count.                                |  |

| Higher memory resources                     | Complicated programming language (HDL).        |  |

| Not fixed hardware structure                | Difficult of comparison because of the lack of |  |

|                                             | standardization.                               |  |

TABLE 1: ADVANTAGES AND DISADVANTAGES OF A FPGA

But despite these disadvantages, FPGAs present a compelling alternative for digital system implementation of large data due to their less time to market and low volume cost and also because of their widely ranged possibilities.

#### 2.3 HDL CODE

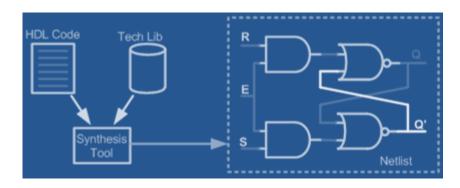

Hardware Description Language (HDL) [14] is a specialized computer language used to program electronic and digital logic circuits. The structure, operation, and design of the circuits are programmable using HDL. HDL includes a textual description consisting of operators, expressions, statements, inputs, and outputs. Instead of generating a computer executable file, the HDL

compilers provide a gate map understood as netlist describing the hardware (i.e., a list of gates and the wires connecting them).

The gate map obtained is then downloaded to the programming device to check the operations of the desired circuit. The language helps to describe any digital circuit in the form of structural, behavioral and gate level and it is found to be an excellent programming language for FPGAs and Complex Programmable Logic Devices (CPLDs), as it will be referred in this thesis.

FIGURE 5: EXAMPLE OF GATE MAP (TALA, D. K.URL: HTTP://www.ASIC-WORLD.COM/VERILOG/SYNTHESIS1.HTML)

The three most used HDL languages are Verilog, VHDL (Very High Speed Integrated Circuit Hardware Description Language), and SystemC. Of these, SystemC is the newest. HDL code appeared as a solution to Moore's law because it supplied the absence of a better programming language allowing hardware and software co-design. Complex digital circuit designs require more time for development, synthesis, simulation and debugging. The arrival of HDLs has helped to solve this problem by allowing each module to be worked by a separate team.

All the goals like power, throughput, latency (delay), test coverage, functionality and area consumption required for a design can be known by using HDL. As a result, the designer can make the necessary engineering tradeoffs and can develop the design in a better and efficient way. Simple syntax, expressions, statements, concurrent and sequential programming is also necessary while describing the electronics circuits. All these features can be obtained by using a hardware description language. Now while comparing HDL and C languages, the major difference is that HDL provides the timing information of a design.

In most of the industries, Verilog and VHDL are the most common ones. Verilog consists of modules and the language allows Behavioral, Dataflow, and Structural Description. On the other hand, VHDL's design is composed of entities consisting of multiple architectures. SystemC consist a set of C++ classes and macros.

The designing of an entire application in HDL can be very difficult and time-consuming because of the typical level of abstraction of the high-level languages. Also, a program made in HDL can be complex to modify. For these reasons, more people are using applications to convert the code to HDL as the HDL Coder that will be used in this thesis.

In this project, reference will be made only to Verilog and VHDL because the programming of HDL code it is going to be made through the conversion of MATLAB code to HDL code using the MATLAB HDL Coder which offers the possibility to choose one of these two embedded languages.

#### 2.4 MATLAB

MATLAB is a commercial software developed by the American company MathWorks to solve mathematical problems and to graphically display the results. It is also the software chosen for the implementation of that project. When the simulation is already developed in MATLAB it needs to be converted into embedded languages such as C and HDL in order to start the hardware implementation. During this conversion, it is important to check the fixed and float points that will be described in the first part of this section. Later, a brief summary is done on how to use/operate the conversion applications provided by MATLAB to pass from a Simulink model to C or HDL code.

#### 2.4.1 Fixed Point vs Floating Point

Digital signal processing can be separated into two categories: fixed point and floating point. These designations refer to the format used to store and manipulate numeric representations of data. Fixed-point DSPs are designed to represent and manipulate integers – positive and negative whole numbers – via a minimum of 16 bits. Floating-point DSPs represent and manipulate rational numbers via a minimum of 32 bits in a manner similar to scientific notation, where a number is represented with a mantissa and an exponent (e.g., A·2B, where 'An' is the mantissa and 'B' is the exponent). [15]

The exponentiation inherent in floating-point computation assures a much larger dynamic range – the largest and smallest numbers that can be represented - which is especially important when processing extremely large data sets or data sets where the range may be unpredictable. It is not the case, because the path is decided and predictable (it has to be inside the position range of the axes) and the data sets are not so big.

Floating-point processing has much greater precision than fixed-point processing, distinguishing floating-point processors as the ideal DSP when computational accuracy is a critical requirement.

Dynamic range and precision considerations typically define the criteria used by designers to determine whether fixed-point or floating-point processors are ideally suited for an application – where computational demands are high, floating point is favored. For general purpose applications with a high-volume fixed point are chosen.

However, the design will be converted to Fixed-Point because HDL Coder requires it to work but the system should not have any problem because it is not such a big application. A summary of the different characteristics explained can be seen in Table 2 [16]:

| Fixed Point                              | Floating Point                               |

|------------------------------------------|----------------------------------------------|

| 16- or 24-bit Devices                    | 32-bit Devices                               |

| Limited Dynamic Range                    | Large Dynamic Range                          |

| Overflow and quantization errors must be | Easier to program since no scale is required |

| resolved                                 |                                              |

| Long product development time            | Quick time-to-market                         |

| Faster clock rate                        | Slower clock rate                            |

| Cheaper                                  | More expensive                               |

| Lower power consumption                  | Higher power consumption                     |

TABLE 2: COMPARISON BETWEEN FIXED POINT AND FLOATING POINT

#### 2.4.2 MATLAB TO C

C, is a programming language of general purpose and high-level, originally developed by Dennis M. Ritchie to evolve the UNIX Operating system. It is a successor of B language introduced around 1970 but it was not formalized until 1988 by the American National Standard Institute (ANSI). Nowadays is the most widely System Programming Language. [17]

C was initially used for system development work, particularly the programs that make-up the operating system. It was later adopted as a system development language because it produces code that runs nearly as fast as the code written in assembly language. In our case of study, the conversion from MATLAB to C is used to implement the system into CPUs.

To accomplish this goal from a developed APP, MATLAB offers two options. The first one is to convert the entire APP directly using MATLAB compiler. In this case, a short library which will need MATLAB runtime to work is created. The second option is to convert only the code, this can be done automatically using MATLAB coder and the result will be independent of MATLAB.

A manual translation is not advisable because MATLAB and C are two completely different languages. It is not an easy process and there are high possibilities of losing valuable time. It will be hard to modify the requirements later and it will also have coding errors. Summing up, it is a time-consuming and expensive process.

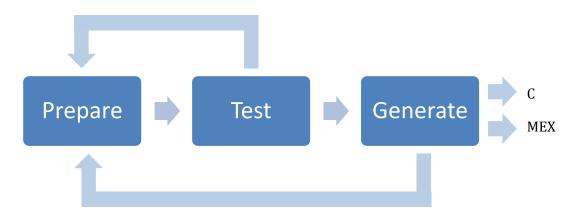

MATLAB Coder helps to do this process automatically but it is necessary to follow a specific workflow [18] and taking into account some requirements:

- 1. *Prepare:* In this step, it is necessary to prepare the MATLAB algorithm for code generation through implementation choices and the usage of supported language features.

- 2. *Test:* Verify if MATLAB code is ready for code generation. First of all, validate that MATLAB program generates code: if it is successful MATLAB will generate an .m file. Then, accelerate execution of the user-written algorithm.

- 3. *Generate:* It can generate source code or MEX for final use. Iterate your MATLAB program to optimize and implement as a source, executable or library.

FIGURE 6: THREE-STEP WORKFLOW

During this implementation, it is important to look at 4 different points that differ from MATLAB to C:

Polymorphism: the same function of MATLAB code can be used for an element by element multiplication (with logical, integer, real, complex...), matrix multiplication or dot product. However, for C code it is needed to create a specific function for each operation and to specify the entry types (see Fig. 7)[18]:

```

MATLAB

double foo (double b, double c)

function a = foo(b,c)

C element multiplication

a = b*c;

return b*c;

}

C matrix multiplication

Void foo (const double b[15], const double c[30], double a[18])

int i0, i1, i2;

for (i0=0; i0<3; i0++){

for (i1=0; i1<6; i1++){

a[i0 + 3*i1]=0.0;

for (i2=0; i2<5; i2++){

a[i0 + 3*i1] += b[i0 + 3*i2]*c[i2 + 5*i1];

}

}

}

}

```

FIGURE 7: EXAMPLE OF POLYMORPHISM

- *Memory allocation:* it is mandatory to specify if an element is statically or dynamically allocated in the memory. MATLAB is a dynamical type, which means you do never have to worry declaring memory for the data that you create. On the other hand, C is a statically type so you always have to explicitly specify the size of your data or otherwise you have to use dynamic memory allocation using specific commands.

- *Processing matrices and arrays:* In arrays/matrixes MATLAB used compact whereas C code uses for loops. Another difference is that MATLAB is 0 based indexed and C is 1 based indexed.

- *Fixed-point data types:* in C is necessary to specify the data types of your inputs and outputs as well as the internal variables.

These considerations can mean a relevant increase in the number of lines comparing C code to MATLAB Code.

#### 2.4.3 MATLAB TO HDL CODE

This conversion is made using HDL Coder but it is also necessary to follow Model-Based Design to make it work properly.

Model-Based Design is a mechanism that will show how to bridge the gap between the algorithmic description and the hardware implementation.

One easy way to verify that hardware implementation matches system specifications is using Model-Based Design and HDL Coder (MATLAB application) together. It can also be useful to iterate designs faster.

FIGURE 8: MODEL-BASED DESIGN WORKFLOW

There are few steps [19] from algorithm through Hardware implementation that will make the process successful:

- The author writes in MATLAB already thinking in the ultimate Hardware implementation. During this thesis, the author will try to clarify which are the main issues that have to be taken into account before starting to implement a simulation that will be converted to HDL Code using Matlab/Simulink.

- Leverage HDL coder workflow: launch the HDL Workflow Advisor and follow the steps:

- 1. *Definition of Input types:* it can be done by running a floating-point simulation using the Test Bench or manually defining variable by variable.

- 2. *Fixed-Point conversion:* Floating to Fix-Point validation which defines the simulation maximum and minimum values. These values and the proposed fix-point results can be easily modified and iterated again.

- 3. *HDL code generation:* it can be chosen between VHDL or Verilog language and the coding standards.

- 4. *HDL verification:* it can be done through 3 different ways:

- HDL test bench

- With Cosimulation: The signals can be checked graphically with ModelSim.

- With FPGA-in-the-loop: Using MATLAB against a real FPGA board. This option will be the one implemented in this project in 4.3 Implementation.

- 5. *Synthesis and Analysis:* to get an accurate picture of the results. The design can be integrated into a larger project using Altera. This step is not considered in the scope of this project.

- Use synthesis and implementations tools.

## 2.4.4 Using HDL Coder and HDL Verifier for FPGA and ASIC Designs

There are a few practices [20] that should be followed:

- 1. Use modeling and simulation to optimize at the system level:

- Convert floating point to optimized fixed-point model: it will be done by automatically tracking of signal range (also in intermediate quantities) and with that propose to make a recommendation on word/fraction lengths.

- Bit-true models in the same environment: as a method to be able to quantify the error occurred during the conversion.

- 2. Automatically generate readable, traceable HDL code for FPGA and ASIC designs:

- In a Simulink model, open HDL Workflow Advisor, set Target Device as Generic ASIC/FPGA and choose the synthesis tool for your specific FPGA target.

- Execute all the next steps to generate the code (Prepare Model for HDL Code Generation, HDL Code Generation and FPGA Synthesis and Analysis) where options such as the programming language, results presentation and others can be chosen.

- The report generated can be useful for analyzing the number of resources used in the implementation, for instance, the number multipliers, multiplexers, registers... that have been created and in which sections. This report will be useful in order to give a reasoned conclusion of the utility of this HDL conversion. It is important to know if the converted code employs many resources and how are they used because this project should not need a high number of them.

- Optimization adds Path Delay with should be checked in order not to affect badly to the simulation.

- Use pipeline to improve the speed and identify the true bottlenecks of the system through highlighting the critical paths.

- 3. Re-use System Level Test Bench for HDL Verification: the problem with Test Bench is the difficulty of re-using them between different levels of abstraction (Model, VHDL, FPGA). For making that possible HDL Cosimulation can be really helpful.

- Open HDL Workflow Advisor: in HDL Code Generation, use Generate Cosimulation and run the test.

- 4. Enable regression testing with FPGA-in-the-loop simulation:

- Re-use test benches for regression testing.

- Inside HDL Workflow Advisor FPGA Turnkey.

### 3 System modelling

This chapter is showing the simulations implemented with MATLAB/Simulink during the development of the thesis. These simulations represent the environment that would be used in a real project and try to be visual and easy to understand, apart from providing significant data. The system simulation has been evolved from a first centralized system where only a representation of the CNC machine workflow until getting the final system, decentralized, where the axes should accomplish 3 basic functions: each axis has a valid set point for each interpolation cycle; second, they negotiate a motion sequence with an external master; third, they communicate errors or the end of a successful movement.

#### 3.1 CNC Machine Simulation

In a CNC machine, the Master has as an input a set of points, it performs a path planning limiting the top velocities or accelerations of the axes. At that point, it sends the points of the planned path to the axes, which just make a simple linear interpolation between them before moving. This system is centralized because all the information is in possession of the master and it is also the one which gives the orders.

The layout can be seen in the Fig. 12 and it will be explained more in detail during this chapter. Some constant values, as the frequencies at which the simulation was running, needed to be defined and they were chosen to be kept as accurate as possible compared to a real CNC machine.

| Variable                | Value                        |

|-------------------------|------------------------------|

| Communication frequency | f = 1000 Hz                  |

| Interpolation frequency | $f_{int} = 16000 \text{ Hz}$ |

| Global frequency        | $f_g = f/20 \text{ Hz}$      |

| Simulation time         | simt = 12/f <sub>g</sub> Hz  |

Table 3: Values are given to the frequency variables

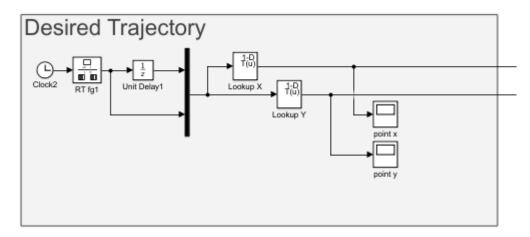

The simulation has 3 different parts: the generation of the desired trajectory, the master system, and the slaves X and Y. Only two axes have been implemented in order to make the system easier to understand but adding a third one should not be a problem, it would only be necessary to add another Lookup table.

- <u>Desired trajectory:</u> the first part of the system is the generation of the trajectory. The path is determined using two lookup tables, one for each axis. The Set Points resulted from the lookup tables are in Cartesian coordinates.

- The outputs, x and y, are the inputs of the Master system. This system gives a Set Point every  $f_g$ , which is controlled by the Rate Transition block named "RT fg1".

FIGURE 9: DESIRED TRAJECTORY

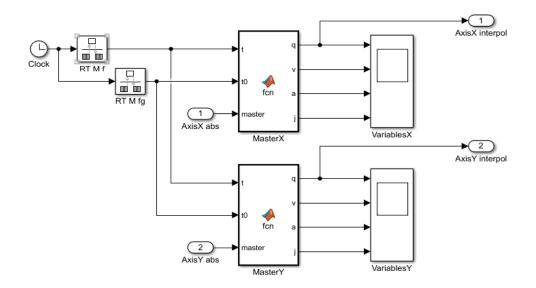

• Master subsystem: this system is in charge of the interpolation process and is the one with all the information about the axes (maximum position range, velocity, acceleration...), the intelligent part of the system. When it receives the Set Points, it applies a 7th degree polynomial interpolation to create a path and divide it into small Set Points that are going to be sent to the axes. The use of this high degree polynomial is justified by the search of a smooth trajectory, where the axes have no issues in the transition from one Set Point to the other. This polynomial secures a velocity, acceleration, and jerk equal to zero at the end of every Set Point. The Set Point given by the trajectory generator has to be divided into small ones because of the limitations, it can create a path that does not imply breaking them by imposing them as a condition. However, it was decided not to apply any limitation in this early stage of the system modelling.

This system works at two different frequencies, every Set Point is given at a  $f_g$  frequency and it generates a new small Set Point at f frequency, as it can be seen by the inputs of the both Rate Transitions blocks.

FIGURE 10: LAYOUT OF THE MASTER SYSTEM

• <u>Slave X/Y and final transformation:</u> The slaves receive the coordinates given by the master and apply a linear interpolation (Subsystem Axis X/Y) in order to calculate the velocity and acceleration that they need to accomplish the Set Point given. They would never exceed their limitations because the master has already made the calculations for them, this is the main difference from the distributed interpolation simulation that will be implemented after.

After that, the output position  $q_x$ , which is the desired position, enters in the subsystem X (layout in Fig. 11). This subsystem makes the conversion into the real position applying the saturation limits in acceleration, velocity, and position and the transfer function.

FIGURE 11: LAYOUT SLAVES

FIGURE 12: LAYOUT OF CNC SIMULATION

FIGURE 13: LAYOUT OF THE SUBSYSTEM X (SAME AS SUBSYSTEM Y).

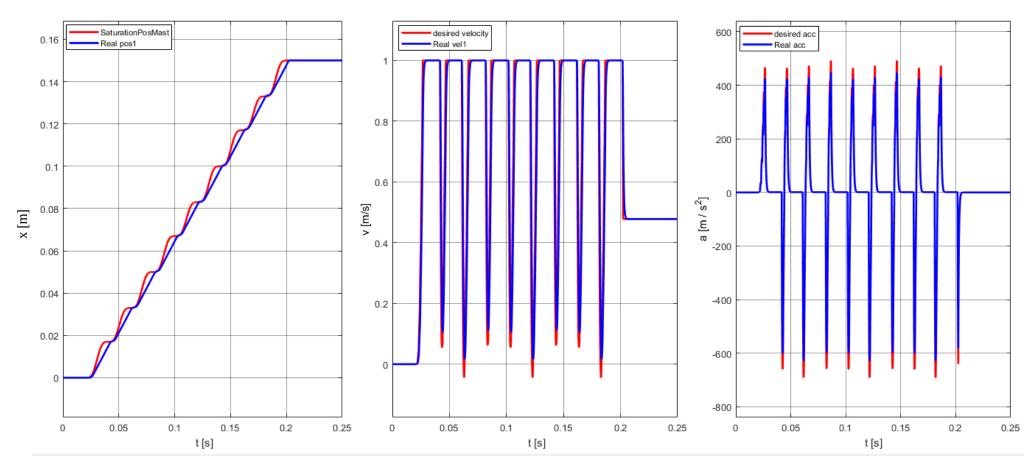

The results of the real system can be seen in the Figure 14 and 15 below. The velocity (limited at  $1\,\text{m/s}$  and position of x and y is limited to  $0.15\,\text{m}$  are affected for the saturation for this trajectory. Hence, there is no difference in the position between the path followed by the desired trajectory and the real trajectory. In the Fig. 14 we can see the desired position, which is defined until  $0.2\,\text{m}$  and in the Fig.15 the error between both of them, which is noticeable after the system goes over the  $0.15\,\text{m}$ , until  $0.05\,\text{m}$ .

FIGURE 14: DESIRED POSITION

FIGURE 15: ERROR OF THE AXIS X

More representative plots are drawn in the Fig.16, where it is possible to see more deeply the evolution of the position, velocity and acceleration and how the velocity and acceleration are reduced to zero after the maximum position (the saturation at 0.15m) is reached.

FIGURE 16: EVOLUTION OF POSITION, VELOCITY AND ACCELERATION

#### 3.2 Negotiation Protocol

For the final simulation, a negotiation protocol has been implemented which explains how/when the axes communicate with each other and with the master. The goal of this protocol was to reduce the communication at a minimum level but maintain its effectiveness. All the necessary communication until reaching an agreement should be encapsulated in the time period of a master process.

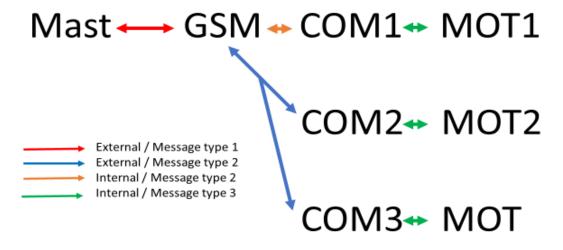

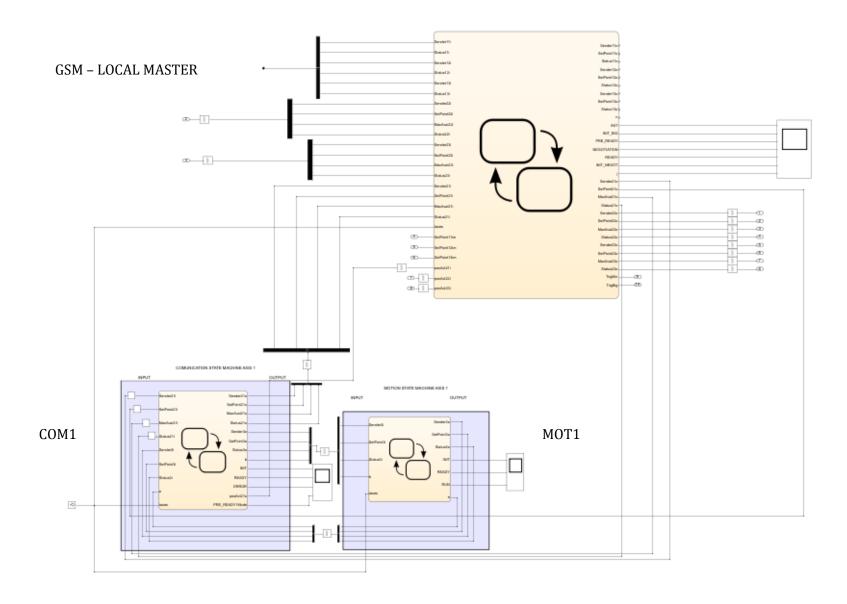

In order to develop this distributed principle, it has been considered necessary to create seven State Machines which will coordinate the actions: each axis has two State Machines, one for the communication and another one for motion. In addition, one of the axis can be randomly chosen as a Local Master. In order to perform this task, that axis will have a third State Machine to control and supervise the whole system. The functions of that machines are described below:

- Global State Machine (GSM): located in the axis chosen as the master. It communicates with the COMs and the global master. Its task consist in gathering the information given by the global master (the goal Set Points) and transmit this information to each axis. Axes will calculate if they can achieve this Set Point and send this information back to the GSM that will be in the lead of the negotiation.

- **Communication State Machine (COM):** it is located in every axis and can communicate with the Motion State Machine of the same axis and with the GSM. This machine receives the goal SetPoint and gives a positive or negative answer back to the GSM depending on whether it can or cannot reach the goal. It also transmits the OK to start the motion and the Set Point negotiated to the Motion State Machine when the GSM gives to it the validation.

- Motion State Machine (MOT): located on every axis, it has a single communication channel with the COM of its axis. Its function is to give the order of movement to the axis motor and communicate the COM machine when the movement has finished or there is any error.

The communication through these machines is made with 3 different types of messages which have an agreed format:

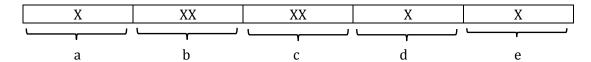

1. Message Type 1: manages the communication between the global master and the GSM.

**a:** Sender address – in order to know who sends the message, each participant is identified with a number. In this case, 0 (Global Master) and 1 (GSM).

**b:** Target / SetPoint goal – B1 refers to Axis 1, B2 to Axis 2 and B3 to Axis 3.

**c:** State status – gives necessary information about the condition of the message. 0 (all in order), 1 (Error), 3 (Confirmation of lecture).

2. **Message Type 2**: message used in the communication between GSM and COMs.

FIGURE 18: MESSAGE TYPE 2

- a: Sender address. 0 (GSM), 1 (COM axis 1), 2 (COM axis 2), 3 (COM axis 3).

- **b:** Target / SetPoint goal.

- **c:** Maximum Point that can be reached by axes.

- **d:** State status. 0 (all in order), 1 (Error), 2 (NOK axis can't reach the SetPoint goal), 5 (Communication has exit Ready State).

- e: Actual Position

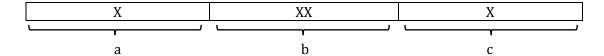

- 3. **Message Type 3**: it corresponds to the communication between COMs and MOTs.

FIGURE 19: MESSAGE TYPE 3

- a: Sender address. In this case, 0 (MOT) and 1 (COM).

- **b:** Target / SetPoint goal.

- **c**: State status. 0 (OK), 1 (Error).

In the next Figure 20, it can be observed more clearly how is the topology of the system and which communications are internal or external, which implies a different time of communication.

FIGURE 20: TOPOLOGY OF THE SYSTEM

Before explaining in more detail how this protocol works, it is necessary to enumerate the assumptions that have been considered:

- Global Master is always working properly. On this basis, there are no communication problems related to it.

- All axes will start to move synchronously because a cyclic state machine<sup>1</sup> will control their movement.

- The communication during RUN state (when the axes are moving) will be checked by the cyclic state machine mentioned above.

- A communication problem is possible between the axes.

- Internal communications are reliable.

- Communication takes 10% of the computation frequency if it is external and 5% if it is internal.

- Movement is defined as 20 times the operation time of axes

- More than one SetPoint is sent to Local Master.

- Negotiation process begins when the previous movement has started.

During the conception of this protocol, it has also been considered necessary to define the possible problems that may occur in a real system and how the system is going to confront them.

- Lack of answer: it can happen between the COMs and the GSM. The system has a lack of answer if the AnswerTime<sup>2</sup> is past and no answer is received. If this event occurs the GSM will resend the SetPoint two times, if there is still no answer, the system will understand that there is an error and all state machines will go to Error state in order to prevent the system from a higher damage.

- **Loss of communication:** Axes do not communicate to the cyclic state machine during moving phase. Axes will move to Error state.

- **Mechanical Error:** This error can happen during the moving phase and, therefore, axes will also move to Error state to stop the system.

The different states of the State Machines have been defined as well as the transitions between them through State Diagrams (default State appears in blue) as it can be seen below:

<sup>&</sup>lt;sup>1</sup> The cyclic state machine is just described in a functional way but not developed in this thesis because it corresponds to another part of the DEVEKOS project.

<sup>&</sup>lt;sup>2</sup> Answer Time: defined as the time to get an answer after having sent a SetPoint from the GSM. AT = communication time + communication time + communication time.

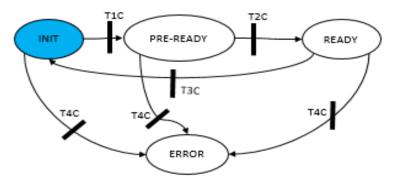

COM:

FIGURE 21: STATE DIAGRAM OF COM

| Transitions | Meaning                                                   |

|-------------|-----------------------------------------------------------|

| T1C         | SetPoint received.                                        |

| T2C         | OK received from GSM & Interp done & Movement finished.   |

| T3C         | SetPoint sent to Motion and answer from motion indicating |

|             | beginning.                                                |

| T4C         | Error message received (from Motion or Communication).*   |

Table 4: Explanation of the transitions of com machine

During the PRE-READY state the interpolation of the SetPoint will be made to check if the axis can or can't reach the goal.

\*If the Error message arrives from Motion (MOT) it has to be sent to the GSM and if it comes from GSM, COM has to inform the MOT in order to stop the axis.

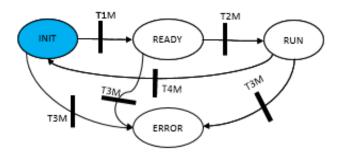

MOT:

FIGURE 22: STATE DIAGRAM OF MOT

| Transitions | Meaning                                                     |

|-------------|-------------------------------------------------------------|

| T1M         | Path received (T3C) & Axis OK.                              |

| T2M         | Axes coordinated.                                           |

| T3M         | Error message received OR error from the axis.              |

| T4M         | Movement is finished & message OK to Communication is sent. |

TABLE 5: EXPLANATION OF THE TRANSITION OF MOT MACHINE

The RUN state implies the movement of the axis. The transition T2M is managed by the cyclic state machine.

If the ERROR message is received from the COM, MOT State Machine will stop the axis. Otherwise, if it is internal it will stop and also send a message to the COM.

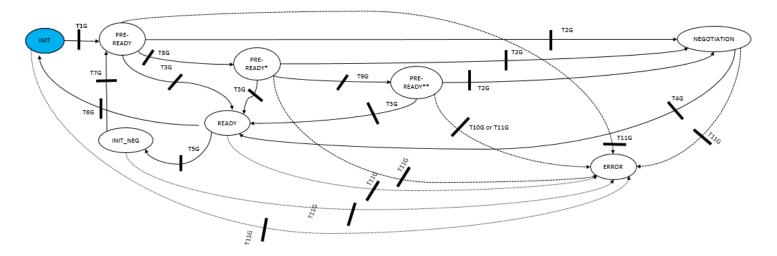

GSM:

FIGURE 23: STATE DIAGRAM OF GSM INCLUDING THE RETRIES

| Transitions | Meaning                                                              |

|-------------|----------------------------------------------------------------------|

| T1G         | SetPoint received from global Master & Confirmation of Lecture sent. |

| T2G         | If one/more axes are NOK with the SetPoint.                          |

| T3G         | All axes are OK with the new SetPoint (setpoint sent).               |

| T4G         | OK, confirmation from Axes (set n=1).                                |

| T5G         | Time for new SetPoint & n = 1.                                       |

| T6G         | Time for new SetPoint & n = 0.                                       |

| T7G         | Verify SetPoint and path are not the same.                           |

| T8G         | AnswerTime is passed and no answer (Set c = 1)                       |

| T9G         | AnswerTime is passed and no answer (Set c = 2)                       |

| T10G        | AnswerTime is passed and no answer.                                  |

| T11G        | Error message from Local Axes.                                       |

Table 6: Explanation of the transitions of GSM

It is worth to point out that every state can jump to the Error State because the GSM is managing the whole system, therefore the error can be related to any of the axis state machines and the GSM need to inform the other axes.

As this protocol contains a big amount of information, which could be difficult to process, different time diagrams considering several possibilities has been developed. Due to its large dimensions, it has not been considered appropriated to add it here but it can be found under the name 'NegotiationProtocol.xslsx' in the same folder of this document. In this file, it is possible to verify that the communication has been kept under the limits (less than the 1Khz frequency of the Global Master), concretely 0.000924 s in the longest possibility considered, which corresponds to a negotiation with 2 retries.

### 3.3 DISTRIBUTED SIMULATION

Once the negotiation protocol is defined, the simulation has been implemented using the MATLAB tool Simulink. During this section the ins and outs of this simulation will be developed in order to allow the readers understand it.

### 3.3.1 Explanation of the Simulation

First of all, it is appropriate to make a small summary of the desired behavior. In the real workflow, the Set Points (path to follow) will be generated by a Global Master, which will send them to a Local Master inside one of the Axis (chosen by the user / randomly), this Local Master will make a first and smooth interpolation and generate small Set Points which will be sent to all the axis, including itself. Then, the axes will check if they can reach the goal Set Point and answer positively. If they cannot, the negotiation will take place and finally the GSM will resend a new goal Set Point reachable by all the axes along with a motion order. After, it checks if the system has evolved correctly.