# Faculdade de Engenharia da Universidade do Porto

# Mixed-signal Test and Measurement Framework for Wearable Monitoring System

Antonio José Salazar Escobar

Dissertação realizada no âmbito do Programa Doutoral em Engenharia Electrotécnica e de Computadores

Orientador: Prof. Dr. Miguel Fernando Paiva Velhote Correia Co-orientador: Prof. Dr. José Alberto Peixoto Machado da Silva

© 2014. Antonio José Salazar Escobar. All rights reserved.

# Resumo

Circuitos de sinais analógicos e mistos proliferam em todas as áreas da eletrónica e, apesar de os sistemas digitais beneficiarem de soluções e estratégias de teste bem estabelecidas, o mesmo não pode ser dito para os sistemas analógicos, de radiofrequência e baseados em sensores. Os custos e o tempo de desenvolvimento e de realização do teste dos elementos analógicos são contribuintes maioritários para o custo total de projeto e produção, bem como o tempo de entrada no mercado, devido à sua complexidade, situação agravada quando se consideram cenários multisensor heterogéneos. Este é o caso da tecnologia de monitorização vestível, que rapidamente se está a tornar uma alternativa reconhecida na medicina, na reabilitação e no desporto. A transição da observação qualitativa para a monitorização quantitativa, que atualmente extravasa os ambientes controlados para incluir os espaços e contextos do dia-a-dia, deve ser acompanhado por estratégias contínuas in-situ de verificação do estado dos sensores, de modo a assegurar a fiabilidade dos dados. Em particular, os sensores passivos tendem a manifestar alterações de comportamento devido ao esforço induzido, forças externas, uso contínuo e desgaste geral. Estas alterações paramétricas progressivas dos sensores necessitam de ser acompanhadas por estratégias que considerem ocorrências de acessibilidade flexíveis a múltiplos níveis (i.e. considerando séries de sensores ou arranjos distribuídos de sensores), em particular para a tecnologia de monitorização vestível que apresenta condições dinâmicas em permanente modificação. O trabalho aqui apresentado propõe uma infraestrutura e uma metodologia para medição e teste que responde às necessidades atuais de sistemas baseados em sensores - um mecanismo de acesso in-situ, primordialmente direcionado para sensores passivos, gestão de recursos, sincronização de medições e controlo de estratégias de grupo, designado por SCPS - Setup, Capture, Process and Scan (Configuração, Aquisição, Processamento e Rastreio). A degradação dos sensores e o diagnóstico de falhas baseado em limiares foram considerados como cenários de teste. Uma implementação modular baseada num circuito digital reprogramável (FPGA - Field Programmable Gate Array) foi desenvolvida tendo em consideração DOIs casos de estudo: sensores resistivos de força (FSR - Force Sensing Resistors) e elétrodos de superfície descartáveis de prata e cloreto de prata, Ag-AgCl. A estratégia de medição e teste proposta foi implementada com recurso ao protocolo de barramento 12C - Inter-Integrated Circuit, enquanto um controlador I2C independente foi utilizado para execução de instruções na perspetiva de uma prova de conceito. Além disso, o acesso externo ao barramento de transporte de dados, utilizado para efeitos de depuração e teste, foi realizado por acesso direto aos registos dos módulos implementados na FPGA por uma ligação USB - Universal Serial Bus gerida por uma interface gráfica codificada em linguagem Python. A impedância dos sensores alvo foi caracterizada em vários cenários de degradação comuns por forma a estabelecer modelos base e respetivos desvios.

# Página em branco

# **Abstract**

Analogue and mixed-signal circuits are proliferating in all areas, and although digital systems benefit from well-established testing solutions and strategies, the same cannot be said for analogue, RF and sensor based systems. Testing costs for the analogue elements drive the overall design and production cost and time to market, due to their complexity, which are aggravated when considering heterogeneous multi-sensor scenarios. Such is the case for wearable monitoring technology (WMT), which is rapidly becoming a recognized alternative in medicine, rehabilitation and sports. Such transition from qualitative to quantitative based monitoring, which now transcends controlled environments to include every-day settings, must be accompanied by continuous in-situ sensor status monitoring strategies, in order to insure data reliability. In particular, passive sensors tend to undergo behavioural modifications due to induced stress, external forces, continuous usage and general wear and tear. Such progressive parametric alterations of the sensors need to be addressed through strategies which consider flexible accessibility occurrences at multiple levels (i.e., considering sensor arrays or distributed sensor arrangements), in particular for WMT which present ever-changing dynamic conditions. The work hereby presented seeks the design of a measurement and testing framework that responds to the present needs of sensor based systems --- an in-situ access mechanism, initially intended for passive sensors, resource management, measurement synchronization, an group strategies control; named SCPS (Setup, Capture, Process and Scan). Sensor degradation and fault diagnostics based on threshold were considered as testing scenarios. A field programmable gate array (FPGA) based modular implementation was developed considering two case-studies: force sensing resistors (FSR) and disposable surface Ag-AgCl electrodes. The proposed test and measurement strategy was implemented using the inter-integrated circuit (I2C) bus protocol, while an independent I2C controller for instruction handling was utilized as a proof of concept scenario. Additionally, external access to the data transport bus, utilized for debugging and testing purposes, was achieved at the present stage through direct access to the implemented FPGA modules registers through an USB connection managed by a Python based graphical user interface. The impedance of the targeted sensors was characterized in a number of common degradation scenarios in order to ascertain base models as to establish deviations.

# Página em branco

# Acknowledgements

To my wife, my never-ending guiding light...

To my daughter for the pure joy she brings

To my father, wish he could have stayed to see this

To my mother, unwavering source of support

To my siblings, nephews, and family

To God for his eternal patience and guidance

## Immortalizing then in this text:

- Mother, Eng., MSc. and pending Ph.D. Carla Mariana Borges Da Silva.

- Future everything Arianna Isabella Salazar Borges.

- Father, Ph.D., and Professor Jorge Antonio Salazar, may he rest in peace knowing his legacy is well kept.

- Mother, MSc. and Professor Yadira Escobar Toro.

- Professor Juan Gutiérrez.

- Mother, Lic., Angela Maria Salazar Escobar.

- Mother, Priest, Singer, and pending Architect Vanessa Carolina Arnaudez.

- Lic. and future MBA Andrea Carolina Arnaudez Salazar.

- Future Professional Gerardo Andres Arnaudez Salazar.

- Lic. Xiomara Escobar Toro.

- Professor Edda Rodriguez, Engineer José Antonio Veracierta and future professional Edda Valentina Veracierta.

- Rosa Veracierta, Enrique Veracierta, Olimpia Abreu and José Abreu.

- Dr. Erick Suarez Plaza.

- Army officer Luis Manuel Marcano Marcano.

Special acknowledge to my two supervisors: Prof. Miguel Velhote Correia and Prof. José Machado da Silva, who provided invaluable support during these years of work. Together we explored inter-disciplinary boundaries in an ungrateful area of knowledge ignored by most, while helping to keep the world moving ... I now entrust them to keep our work alive.

During the research and implementation process, a number of collaborating relations were established, with faculty, students and personnel, in order to gain improved insight, discuss methodologies and strategies and in occasion to obtain resources access; among such contributors

one can mention (forgive any left unmentioned, I would need another thesis to mentioned all that have had a part in this work), in no particular order:

- Prof. Artur Agostinho dos Santos Capelo Cardoso, Department of Electronics and Computer Engineering, FEUP. Bioinstrumentation and analogue circuit strategy development.

- Prof. José Carlos Magalhães Duque da Fonseca, Department of Metallurgy and Material Engineering, FEUP. Electrochemical impedance spectroscopy (EIS) equipment adaptation to for *in-vivo* electrode characterization experiments.

- The PBIO Team: Luan Costa, Miriam Machado and Gonçalo Rios. Together we explored the

vicissitudes of the electrode-skin interface, we did not know what we were getting into;

however they persevered regardless (at personal cost at time). Your contribution is noted and

not forgotten.

- Prof. José Luís Soares Esteves, Department of Mechanical Engineering, FEUP. Fundamental

in force sensing resistor (FSR) pressure characterization experiments design and

implementation.

- Prof. Manuel Rubim Silva Santos, Escola Superior de Tecnologia da Saúde do Porto.

Fundamental in physiological and medical design and experiments strategies.

- Prof. Maria do Rosário Marques Fernandes Teixeira de Pinho, Department. Electronics and Computer Engineering, FEUP. Fundamental in general strategy development and mathematical processing strategies.

- Prof. Jorge Manuel Gomes Barbosa, Department of Informatics Engineering, FEUP.

Fundamental in general strategy development.

- Eng. Cristina da Cunha Oliveira and Eng. Bruno Mendes.

- Centre for Assistive Technology, University Simón Bolívar. Eng. Carla M. Borges Da Silva and Engineer Ricardo J. Bravo. General strategy, design, development and debugging of all experiments and produced work. Resolute from beginning to end.

- The unwavering support of Rui Manuel da Silva Carvalho, Pedro Alexandre Almeida Tavares Alves, Nuno Sousa, Carlos Marques Graf, José António da Silva Nogueira, Susana María Costa Dias, Isidro Ribeiro Pereira, Isabel Maria da Silva Capitão, Maria do Rosário Fonseca Rebelo Martins Ferreira and the rest of the staff at FEUP.

- In memory of Ana Paula Silva.

## Khalil Gibran 1918:

"En los días antiguos, cuando vino a mis labios el primer temblor del discurso, ascendí a la montaña santa y hablé a Dios, diciendo: "Maestro, soy vuestro esclavo. Vuestra voluntad oculta será mi ley y os obedeceré por siempre jamás."

Pero Dios no dio ninguna respuesta, y se desvaneció como una poderosa tempestad.

Y después de mil años ascendí a la montaña santa y otra vez hablé a Dios, diciendo: "Creador, soy vuestra creación. De la arcilla me moldeasteis y a vos debo todo mi ser".

${m Y}$   ${m \mathcal D}$ ios no dio ninguna respuesta, pero como mil alas rápidas se desvaneció.

$oldsymbol{\gamma}$  después de mil años escalé de nuevo la montaña sagrada y hablé a  $oldsymbol{\mathcal{D}}$ ios de nuevo, diciendo:

"Madre, soy vuestro hijo. En la pena y el amor me disteis la vida, y por vuestro amor y compasión heredaré vuestro reino".

Y  ${\cal D}$ ios no dio respuesta, y como la niebla que vela las colinas distantes se desvaneció.

Y después de mil años escalé la montaña sagrada y de nuevo hablé a Dios, diciendo: "Mi

Señor, mi ánimo y mi satisfacción; soy vuestro ayer y vos sois mi mañana. Soy vuestra raíz en la Tierra y vos sois mi flor en el cielo, y crecemos juntos bajo la luz del Sol".

Entonces Dios se inclinó sobre mí, y susurró suaves palabras en mis oídos, y aún como la mar envuelve al arroyo que corre hacia ella, Él me envolvió.

Y cuando descendí a los valles y las llanuras. Dios estaba allí también."

Regardless of religion, spirituality or conviction, the journey of learning is the true path for self-discovery and understanding others and our surroundings, regardless of how deep they might take us it is worth the trip. There are more enigmas out there to be explored, continue the *Techer* path.

# Página em branco

# Index

| Resumo                                                                                                                                                                                        | iii      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Abstract                                                                                                                                                                                      | v        |

| Acknowledgements                                                                                                                                                                              | vii      |

| Index                                                                                                                                                                                         | xi       |

| List of Figures                                                                                                                                                                               | xiii     |

| List of Tables                                                                                                                                                                                | xix      |

| Acronyms and Abbreviations                                                                                                                                                                    | xx       |

| Chapter 1 Introduction                                                                                                                                                                        | 1        |

| 1.1 Motivation and Problem Definition                                                                                                                                                         | 1        |

| 1.2 Objectives                                                                                                                                                                                | 6        |

| 1.3 Thesis contributions                                                                                                                                                                      | 10<br>10 |

| Chapter 2 State of Art                                                                                                                                                                        | 15       |

| 2.1 Wearable Monitoring Technology                                                                                                                                                            |          |

| 2.2 Mixed-Signal, Analogue and Sensor Testing.         2.2.1 Data centric Testing Approaches         2.2.2 Design for Testability.         2.2.3 Structured Design for Testability Standards. | 28<br>31 |

| 2.3 Chapter Remarks                                                                                                                                                                           | 47       |

| Chapter 3 The SCPS Framework                                                                                                                                                                  | 49       |

| 3.1 SCPS Foundation                                                                                                                                                                           | 49       |

| 3.2 SCPS Structure                                                                                                                                                                            | 59<br>60 |

| 3.2.4 SCPS Generalized Structure                           |     |

|------------------------------------------------------------|-----|

| 3.2.5 SCPS Command Structure                               |     |

| 3.2.6 SCPS Register and Pointers                           |     |

| 3.2.8 SCPS Costs and Restrictions                          |     |

| 3.3 SCPS Procedural Flow                                   | 78  |

| 3.4 SCPS Example                                           | 86  |

| 3.5 Chapter Remarks                                        | 90  |

| Chapter 4 SCPS Framework Implementation                    | 91  |

| 4.1 SCPS Implementation Description                        |     |

| 4.1.1 SCPS Module Implementation Functional Overview       |     |

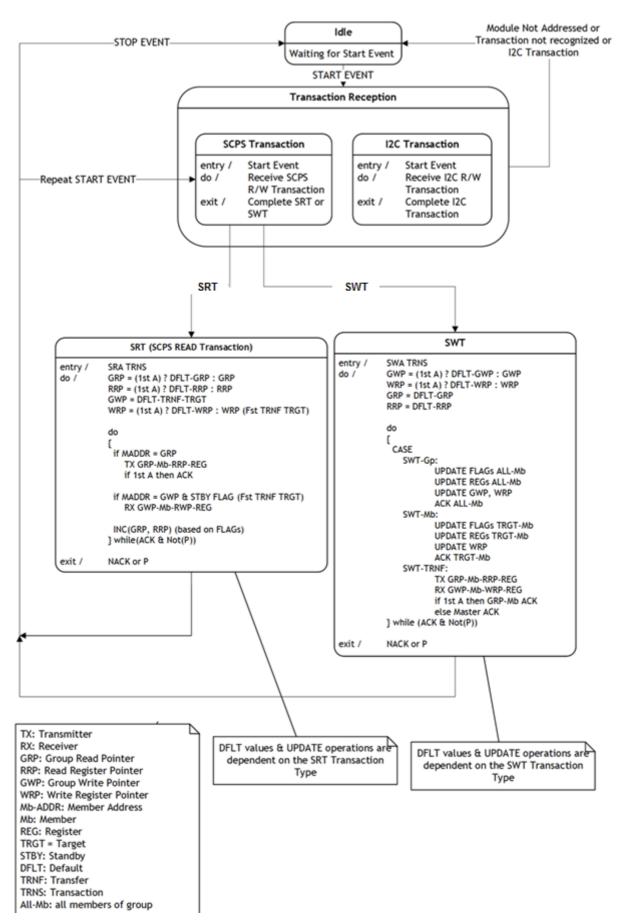

| 4.1.2 Implemented SCPS Flow                                |     |

| 4.1.4 Registers and Pointers                               |     |

| 4.1.5 SCPS Write Transactions and SCPS Instructions        |     |

| 4.1.6 SCSP Read Transactions                               |     |

| 4.1.7 RTL Representation and Simulation                    |     |

| 4.2 Switching Module                                       | 130 |

| 4.3 Impedance Analyser and Analogue Front End Modules      | 133 |

| 4.3.1 Dual-supply PXI Analogue Front End                   |     |

| 4.3.2 Single-supply PXI Analogue Front End                 |     |

| 4.3.3 LabVIEW Impedance Analyser Virtual Instrument        |     |

| 4.4 Over-Current Protection Circuit                        |     |

| 4.5 Impedance Analyser Module                              |     |

| 4.6 Line level Verification Setup                          |     |

| 4.6.1 Software Interface                                   |     |

| 4.7 Chapter Remarks                                        | 145 |

| Chapter 5 Case Studies Characterization Experiments        | 147 |

| 5.1 Case study: Disposable Electrode Ag/AgCl               | 147 |

| 5.1.1 Experimental Methodology                             |     |

| 5.1.2 Electrode-Agar Experiments                           |     |

| 5.1.3 Electrode-Skin Experiments with Gamry G-300          |     |

| 5.2 Case study: Force Sensing Resistors                    | 168 |

| 5.2.1 FSR characterization experiments with TIRA test 2705 | 1/2 |

| Chapter 6 Case Studies SCPS Methodology                    | 185 |

| 6.1 Electrode-skin Impedance SCPS Fault Detection Approach |     |

| 6.1.1 SCPS Electrode Fault Detection Methodology           | 188 |

| 6.2 FSR SCPS Fault Detection Approach                      |     |

| 6.2.1 SCPS FSR Fault Detection Methodology                 |     |

| 6.3 SCPS ProLIMB EMG Module Fault Detection Approach       |     |

| 6.3.1 Wearable Data Acquisition System for Gait Analysis   | 201 |

| Chapter 7 Conclusion and Recommendations                   | 209 |

| References                                                 | 211 |

# **List of Figures**

| Figure 2-1 — Monitoring solutions objective subdivision.                                                   | 20          |

|------------------------------------------------------------------------------------------------------------|-------------|

| Figure 2-2 — WMT architecture functional layers.                                                           | 23          |

| Figure 2-3 — High-level view of WMT architecture.                                                          | 24          |

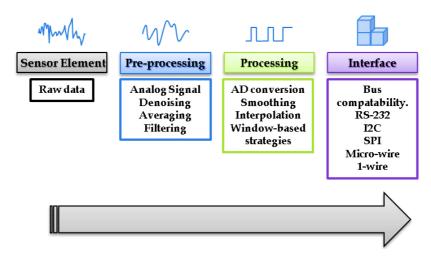

| Figure 2-4 — General sensor sections                                                                       | 25          |

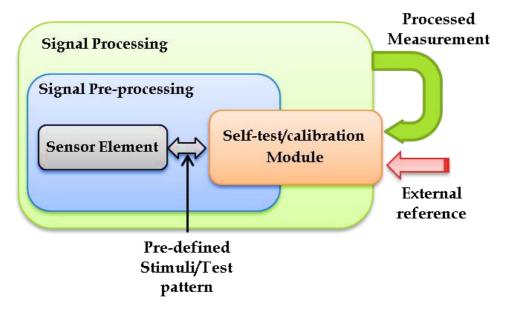

| Figure 2-5 — Self-test/calibration module, based on illustration from (Thankler & Kanoun, 2001).           | 26          |

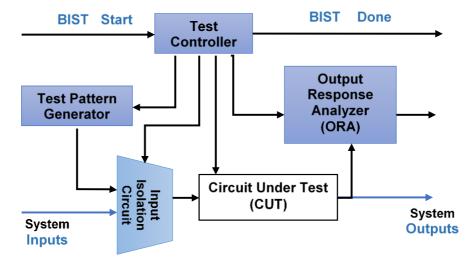

| Figure 2-6 — General BIST structure (Stroud, 2012).                                                        | 31          |

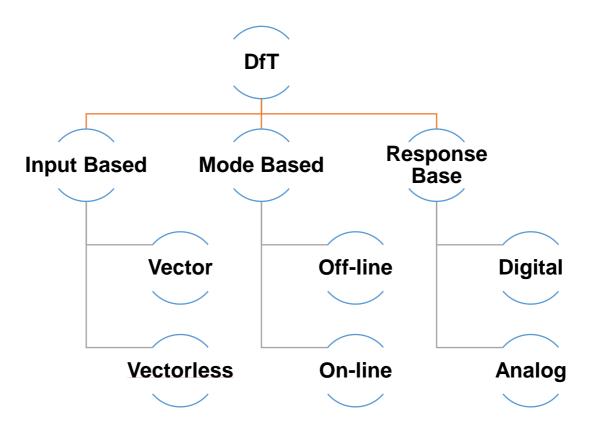

| Figure 2-7 — DfT strategies classification.                                                                | 32          |

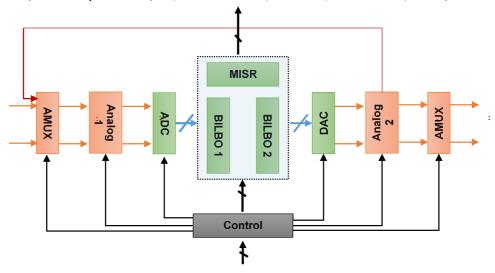

| Figure 2-8 — HBIST Structure, based on figure from (Mir, Lubaszeweki, Liberali, & Courtois, 1995), co.     | ncept from  |

| hletz, 1991)                                                                                               | 34          |

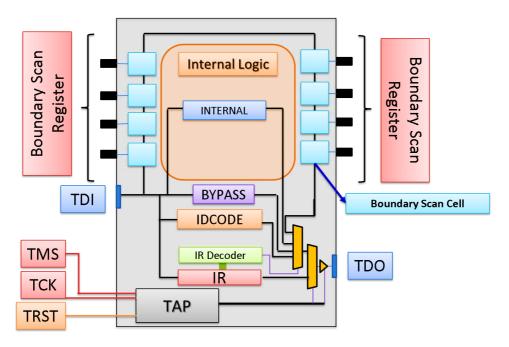

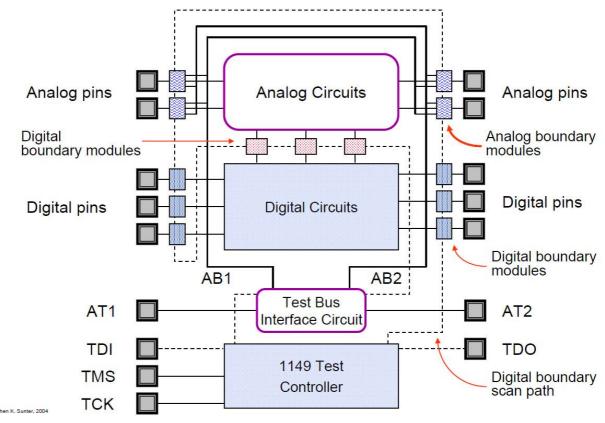

| Figure 2-9 — IEEE 1149.1 compliant architecture (IEEE Std 1149.1-2013, 2013)                               | 36          |

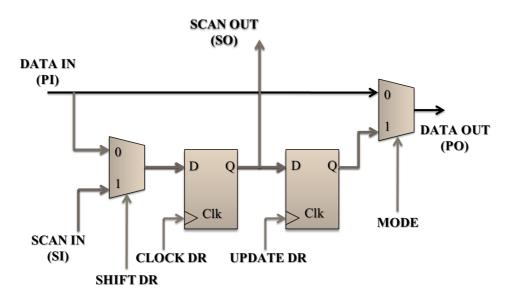

| Figure 2-10 — Generalized boundary scan cell (IEEE Std 1149.1-2013, 2013).                                 | 37          |

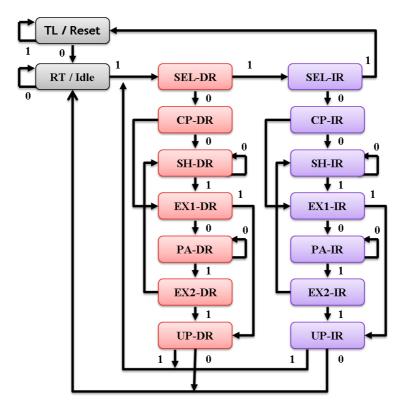

| Figure 2-11 — Test access port controller (IEEE Std 1149.1-2013, 2013).                                    |             |

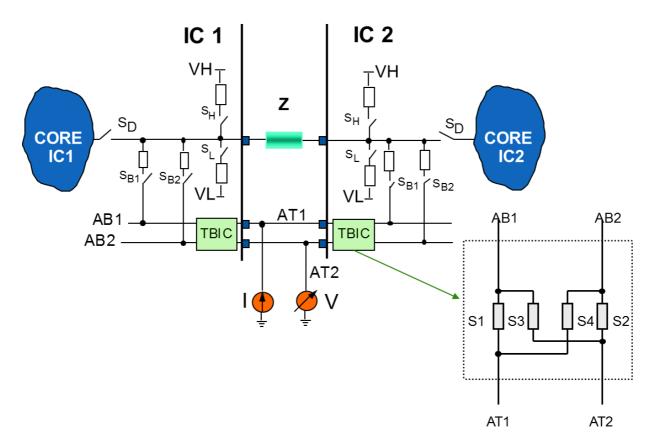

| Figure 2-12 — IEEE standard 1149.4 architecture. Extracted from (Sunter S. 2004), concept from (IEEE S     | Std 1149.4- |

| 10, 2011)                                                                                                  | 39          |

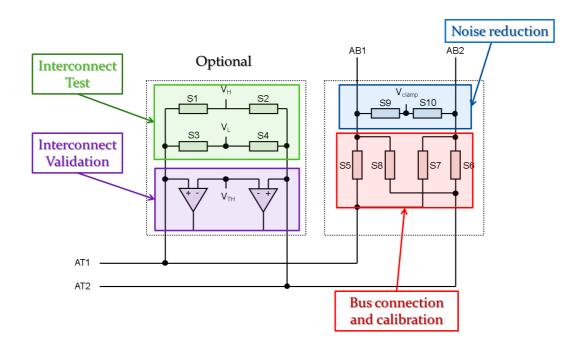

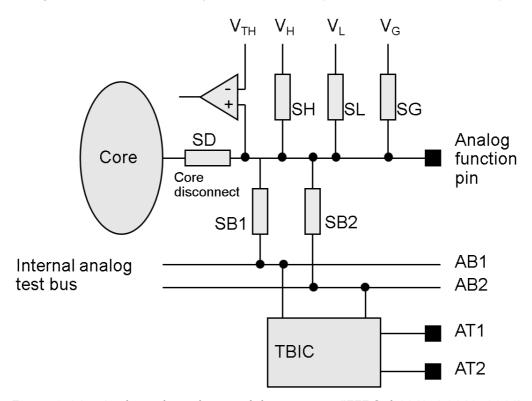

| Figure 2-13 — Test boundary interface circuit (IEEE Std 1149.4-2010, 2011)                                 | 40          |

| Figure 2-14 — Analogue boundary module structure (IEEE Std 1149.4-2010, 2011).                             | 40          |

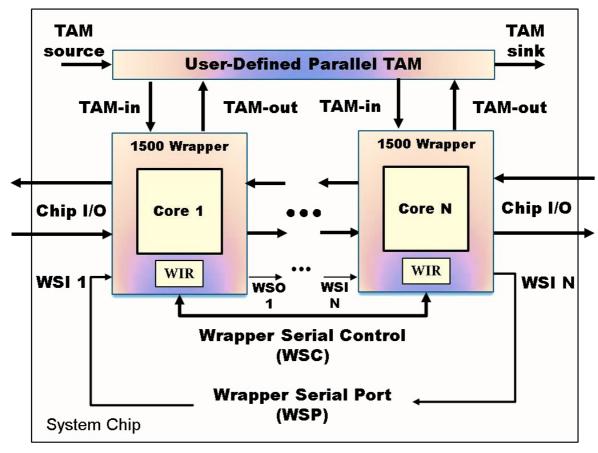

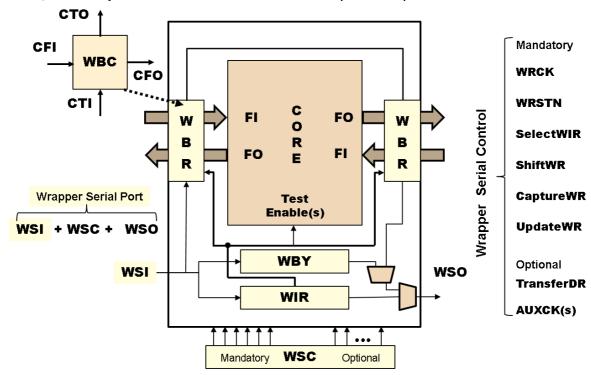

| Figure 2-15 — IEEE 1500 overview ( IEEE Std 1500-2005 IDAMS 3.5 test, 2012).                               | 41          |

| Figure 2-16 — IEEE 1500 wrapper structure overview ( IEEE Std 1500-2005 IDAMS 3.5 test, 2012).             | 42          |

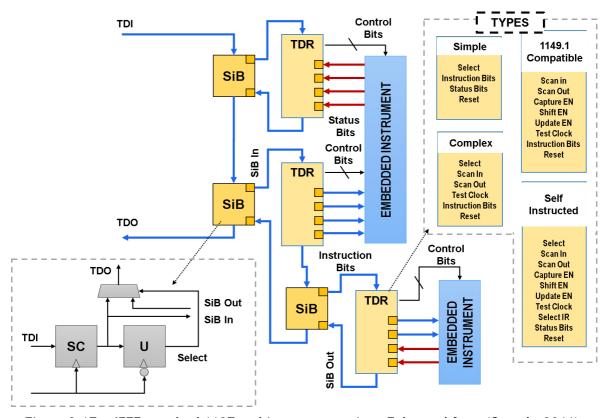

| Figure 2-17 — IEEE standard 1687 architecture overview. Enhanced from (Crouch, 2011)                       | 43          |

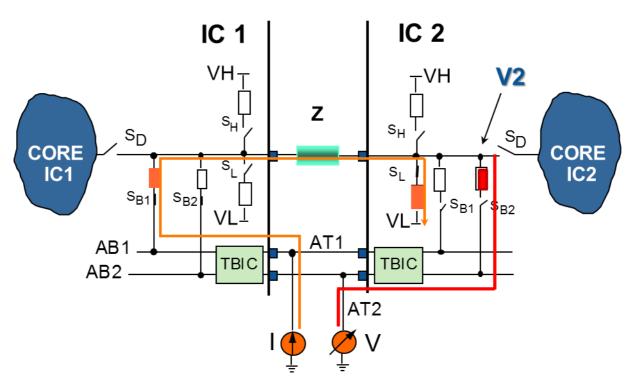

| Figure 2-18 — Parametric testing scenario for IEEE std. 1149.4 compliant cores.                            | 44          |

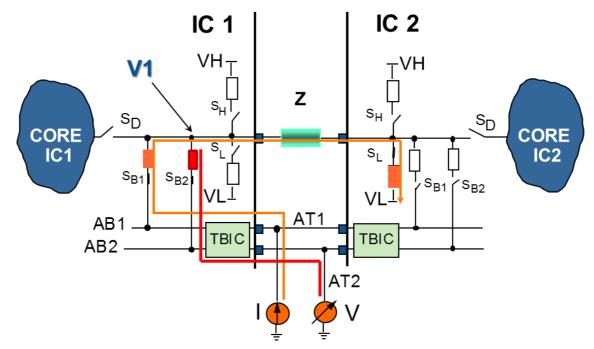

| Figure 2-19 — IC1 side voltage measurement of Z impedance voltage differential.                            | 46          |

| Figure 2-20 — IC2 side voltage measurement of Z impedance voltage differential.                            |             |

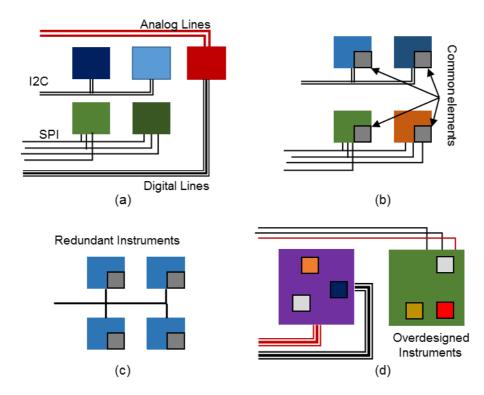

| Figure 3-1 $-$ (a) Heterogeneous communication lines. (b) Element repetition on heterogeneous instru       | ıments. (c) |

| dundant instruments with common elements. (d) Overdesigned instruments with common elements                | 50          |

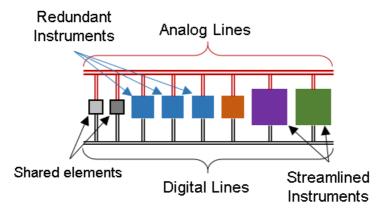

| Figure 3-2 — Idealized multiple instrument setup through standardized access and shard elements.           | 50          |

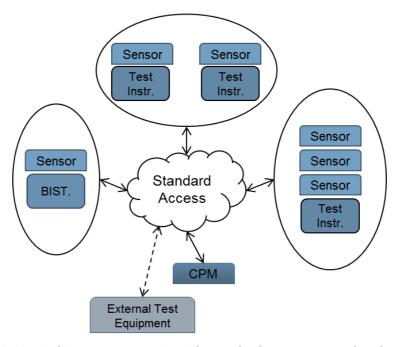

| Figure 3-3 — Multi-sensor scenario with standard access generalized concept                                | 51          |

| Figure 3-4 — Generic system overview with unifying stratagem.                                              | 52          |

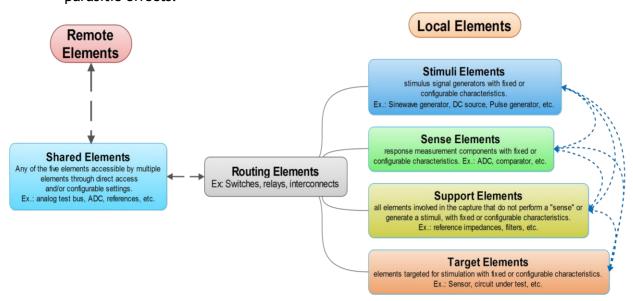

| Figure 3-5 — Characterization elements inter-relation                                                      |             |

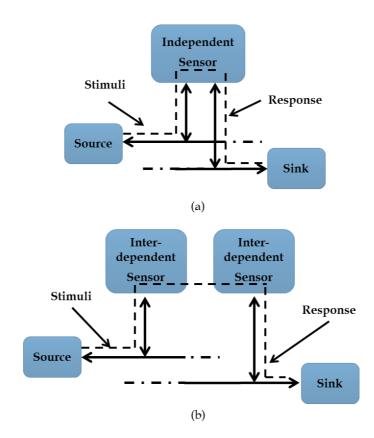

| Figure 3-6 — a) Independent sensor stimuli/capture scenario. b) Inter-dependent sensor stimuli/capture sce |             |

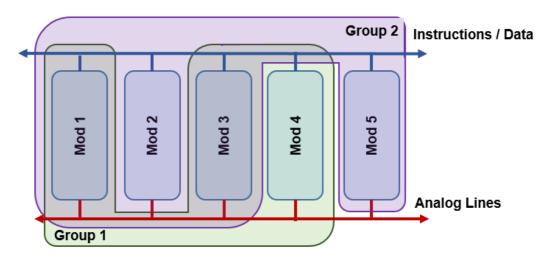

| Figure 3-7 — A multiple element grouping scenario.                                                         | 55          |

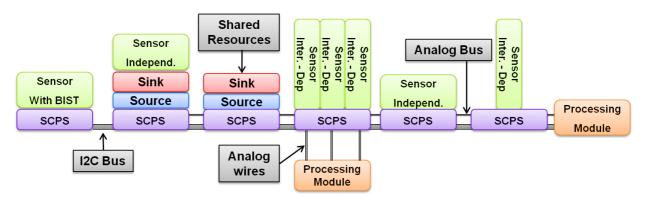

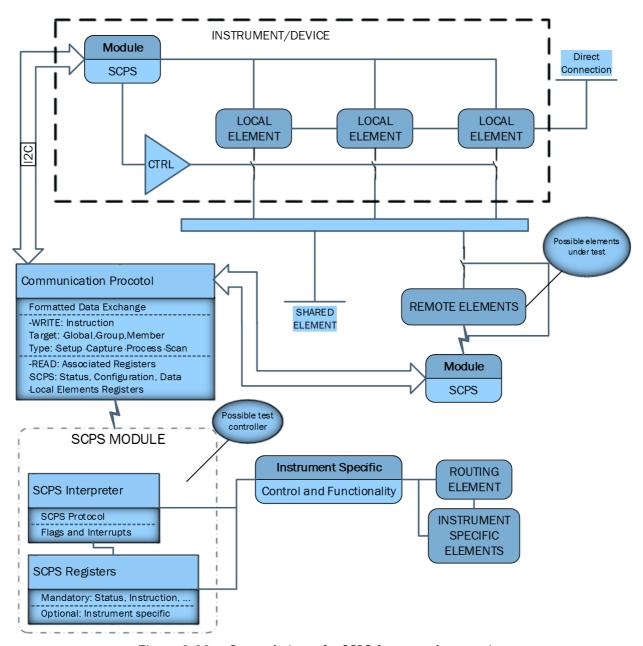

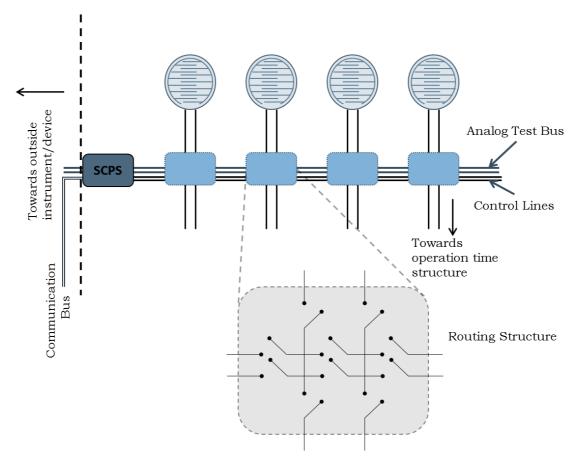

| Figure 3-8 — Multiple sensor types scenario linked through SCPS modules                                      | 57       |

|--------------------------------------------------------------------------------------------------------------|----------|

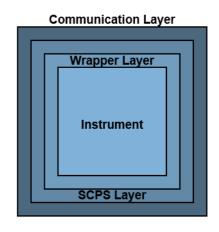

| Figure 3-9 $-$ (a) Generalized view of a SCPS compliant instrument. (b) Generalized layer view of a SCPS $c$ | ompliant |

| instrument.                                                                                                  | 58       |

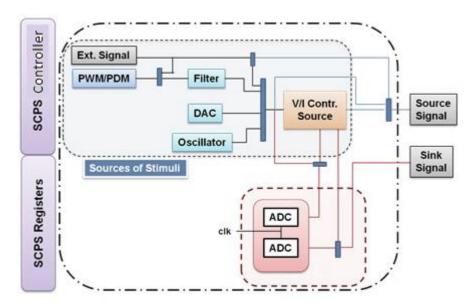

| Figure 3-10 — SCPS source/sink module general overview.                                                      | 60       |

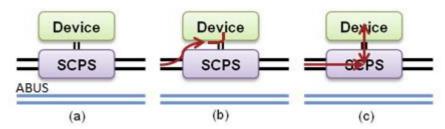

| Figure 3-11 $-$ SCPS modules configurations for analogue bus independent device. (a) General view. (b        | ) Bypass |

| configuration. (c) SCPS related configuration.                                                               | 60       |

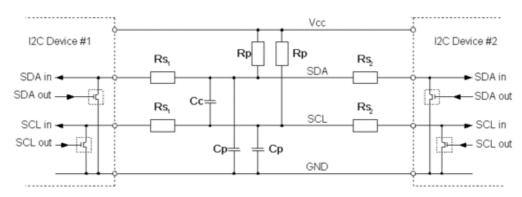

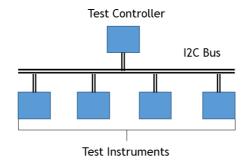

| Figure 3-12 — I2C generalized line setup. Extracted from (I2C-bus.org)                                       | 63       |

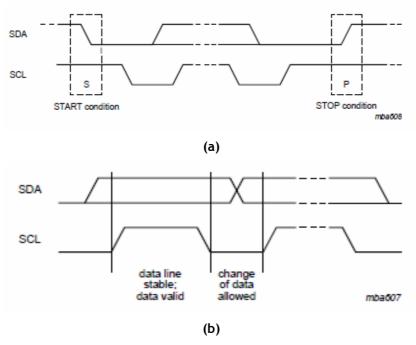

| Figure 3-13 — (a) START/STOP conditions (b) Data validity. Extracted from (NXP, 2014).                       | 63       |

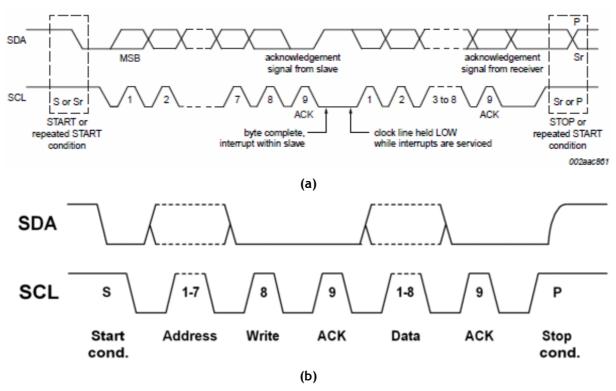

| Figure 3-14 — (a) I2C general transaction, extracted from (NXP, 2014)                                        | 64       |

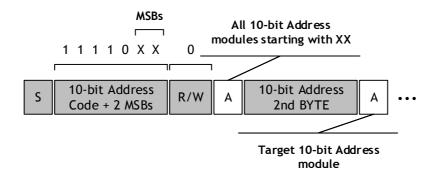

| Figure 3-15 — 10-bit Address WRITE transaction.                                                              | 65       |

| Figure 3-16 — 10-bit Address READ transaction.                                                               | 65       |

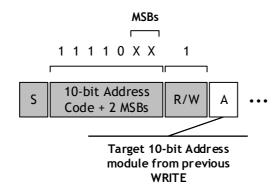

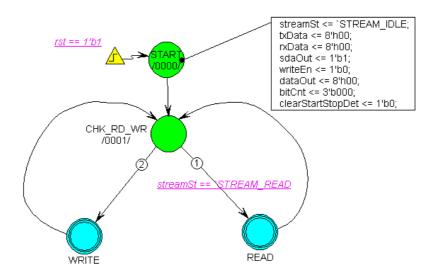

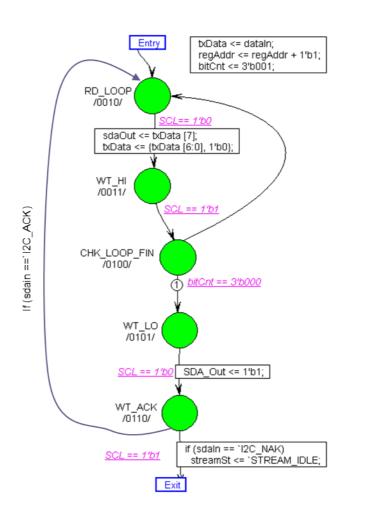

| Figure 3-17 — Top level view of I2C state machine                                                            | 66       |

| Figure 3-18 — I2C READ transaction state machine.                                                            | 66       |

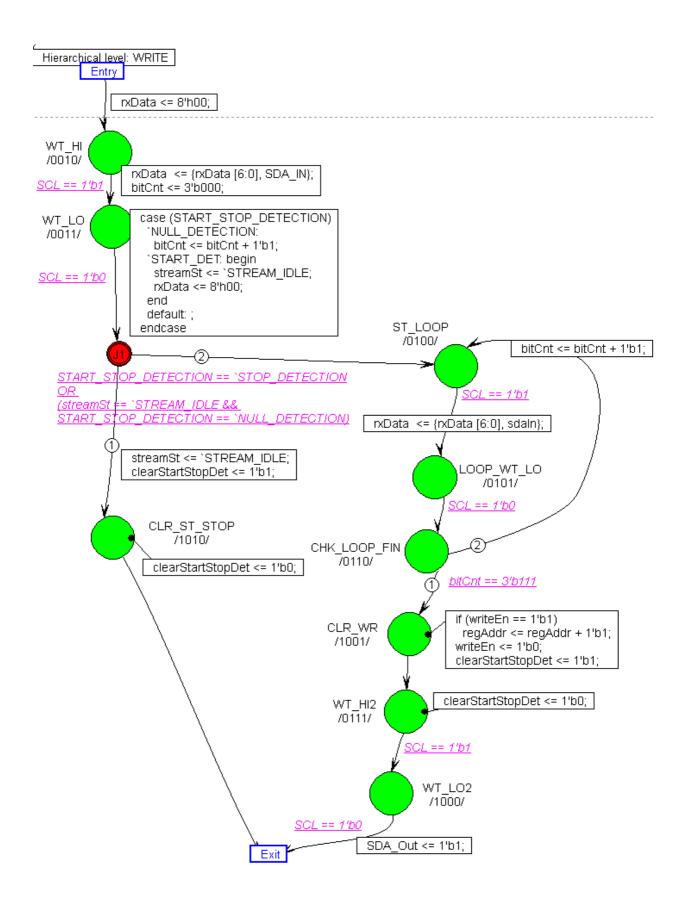

| Figure 3-19 — I2C WRITE transaction state machine                                                            | 67       |

| Figure 3-20 — General view of a SCPS framework scenario.                                                     | 68       |

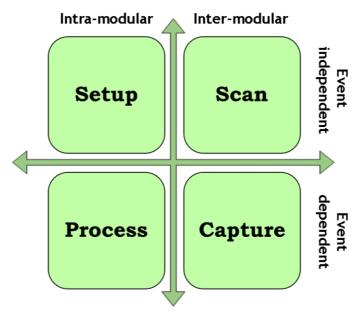

| Figure 3-21 — Command functional separation overview                                                         | 69       |

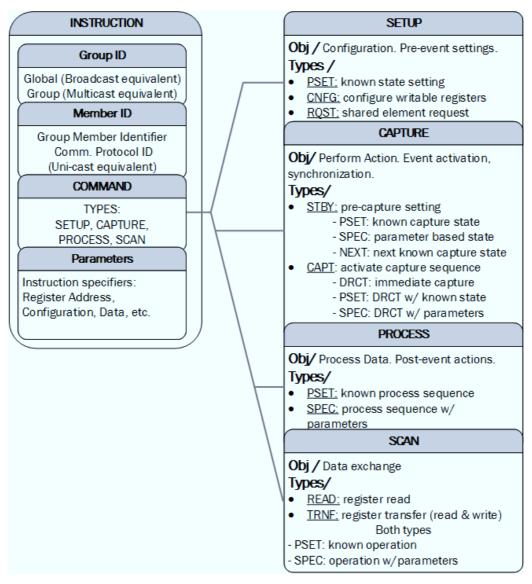

| Figure 3-22 — SCPS commands structure                                                                        | 70       |

| Figure 3-23 — Status register overview.                                                                      | 71       |

| Figure 3-24 — SCPS registers overview                                                                        | 73       |

| Figure 3-25 — SCPS pointer overview                                                                          | 73       |

| Figure 3-26 — Overview of the functional SCPS flow                                                           | 79       |

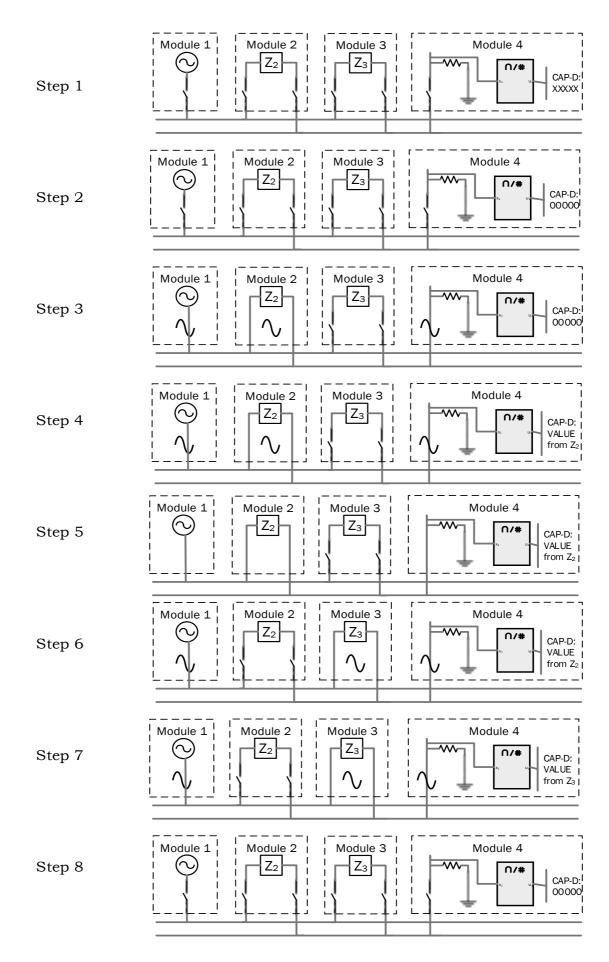

| Figure 3-27 — SCPS SETUP stage flow.                                                                         | 80       |

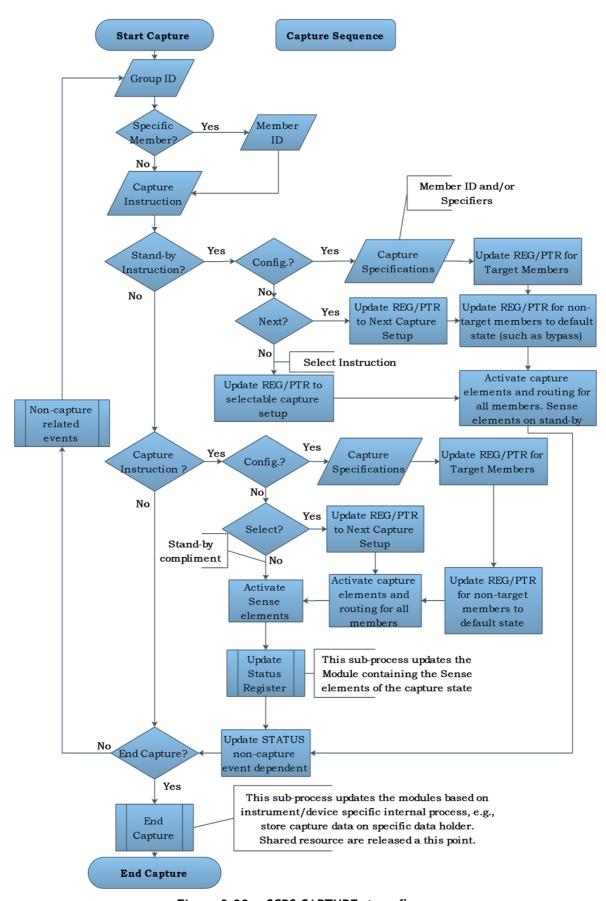

| Figure 3-28 — SCPS CAPTURE stage flow                                                                        | 82       |

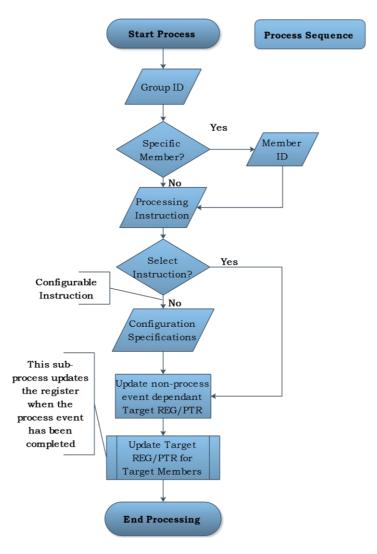

| Figure 3-29 — SCPS PROCESS stage flow.                                                                       | 83       |

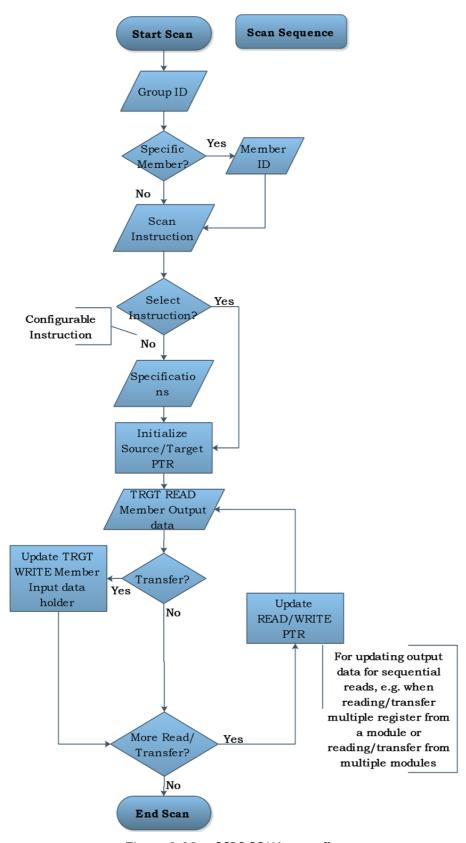

| Figure 3-30 — SCPS SCAN stage flow.                                                                          | 85       |

| Figure 3-31 — SCPS framework example.                                                                        | 88       |

| Figure 3-32 — SCPS framework sensor array scenario.                                                          | 89       |

| Figure 3-33 — SCPS framework multiple embedded test instruments example                                      | 90       |

| Figure 4-1 — Generic SCPS arrangement.                                                                       | 91       |

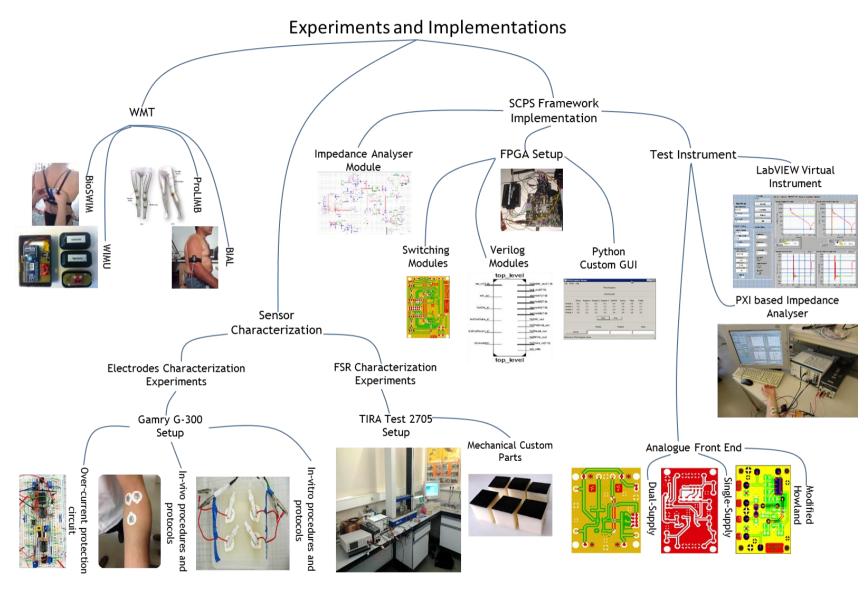

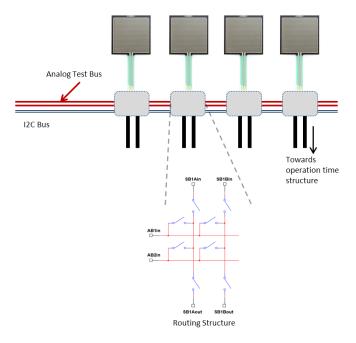

| Figure 4-2 — Overview of experiments and implementations                                                     | 92       |

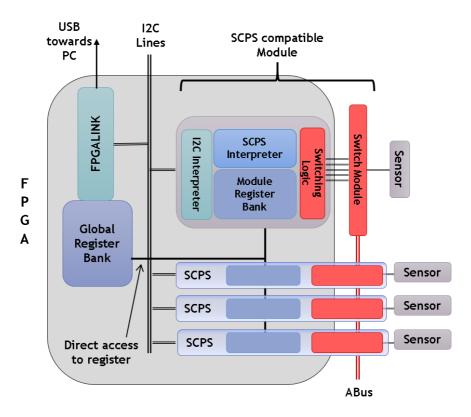

| Figure 4-3 — SCPS framework FPGA-based proof of concept overview.                                            | 94       |

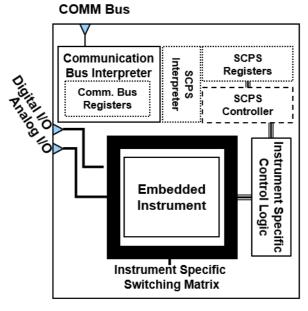

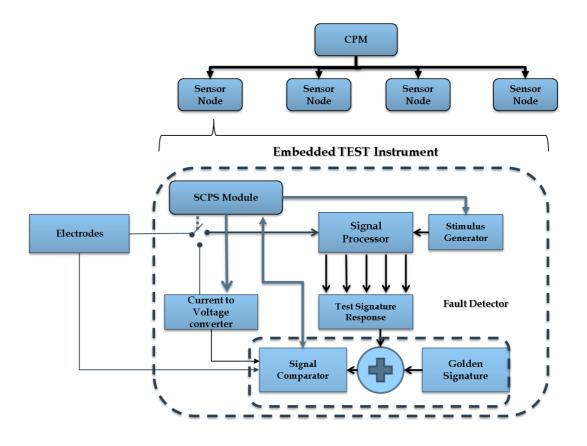

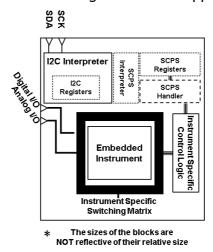

| Figure 4-4 — Embedded instrument view of associated SCPS module.                                             | 96       |

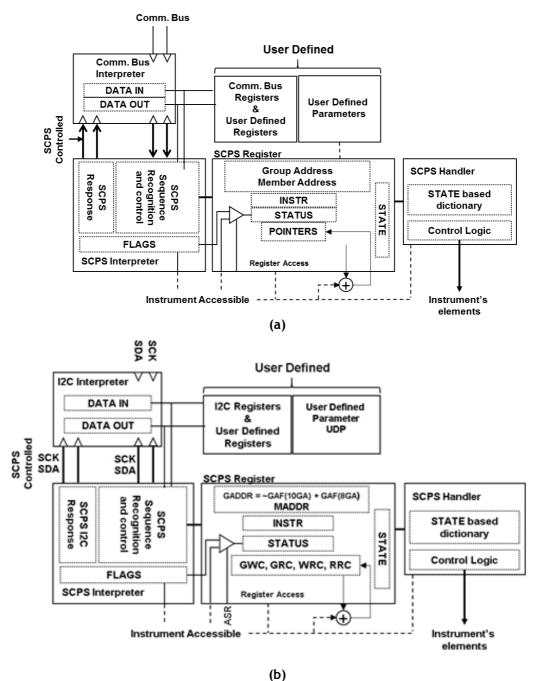

| Figure 4-5 — General view of SCPS module sections. (a) Generic communication bus. (b) I2C communication bus  | us97     |

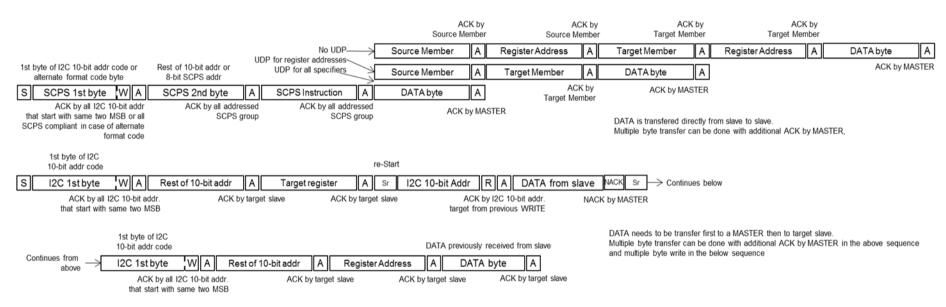

| Figure 4-6 — (a) SWT general sequence. (b) SRT general sequence.                                             | 99       |

| Figure 4-7 — SCPS transactions overview                                                                      | 101      |

| Figure 4-8 — SCPS TRANSFER operation overview                                                                | 102      |

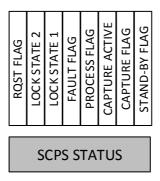

| Figure 4-9 — STATUS register.                                                                                | 103      |

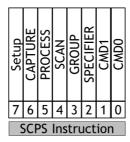

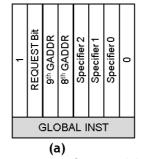

| Figure 4-10 — SCPS instruction format                                                                        | 106      |

| Figure 4-11 — Global instruction format: (a) Generic extended format. (b) Simplified implemented format      | 106      |

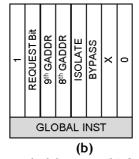

| Figure 4-12 — SRT Transaction overview.                                                                      | 115      |

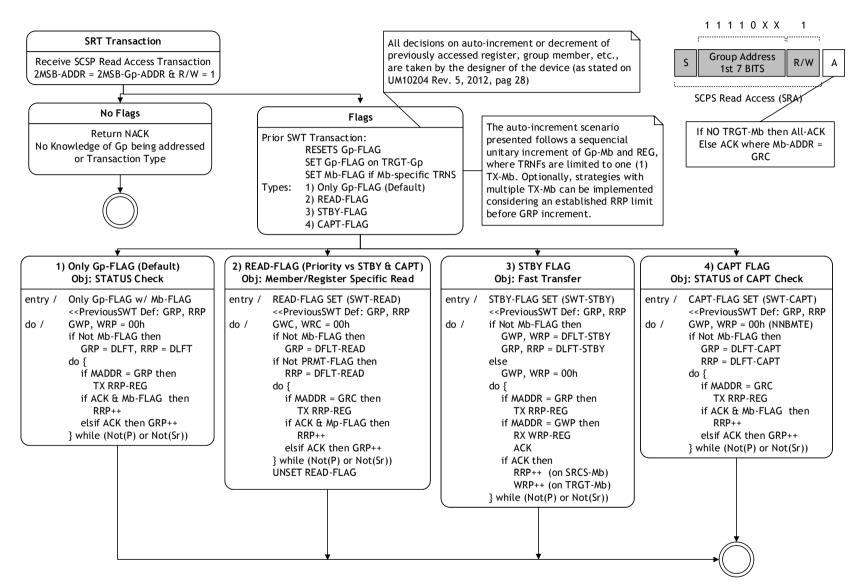

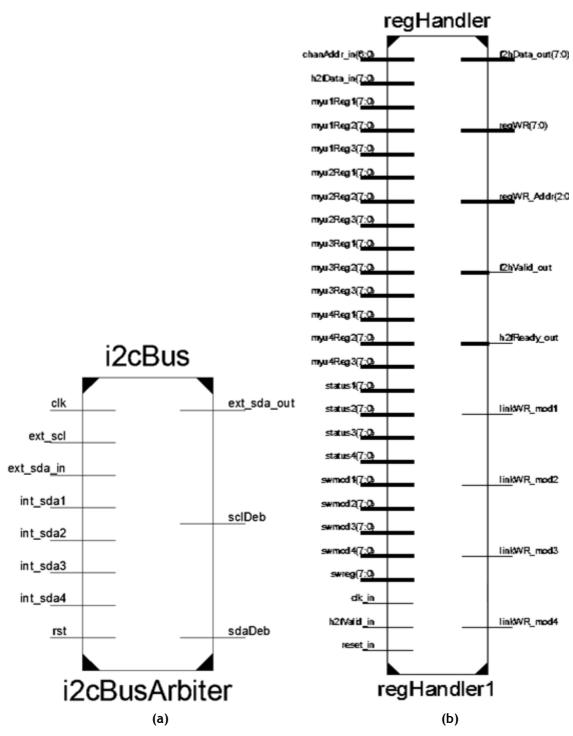

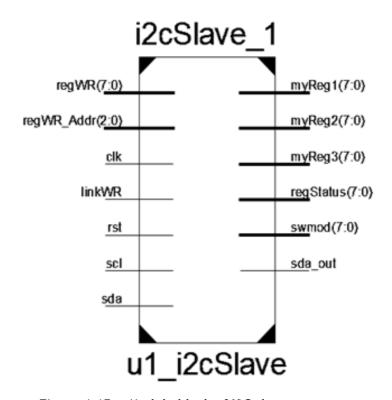

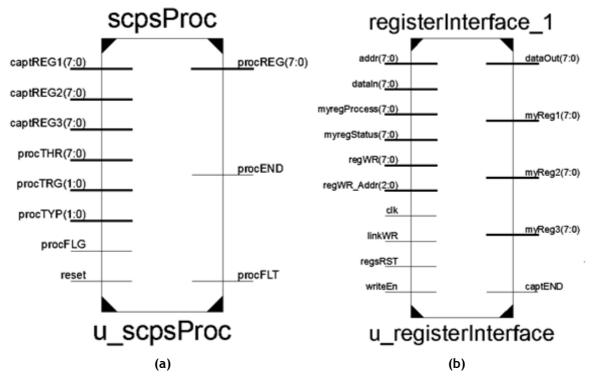

| Figure 4-13 — Module block of top level implementation                                                       | 116      |

| Figure 4-14 — (a) Module block of the I2C bus arbiter. (b) Module block of the register handler or global registe |       |

|-------------------------------------------------------------------------------------------------------------------|-------|

| Figure 4-15 — Module block of I2C slave component.                                                                |       |

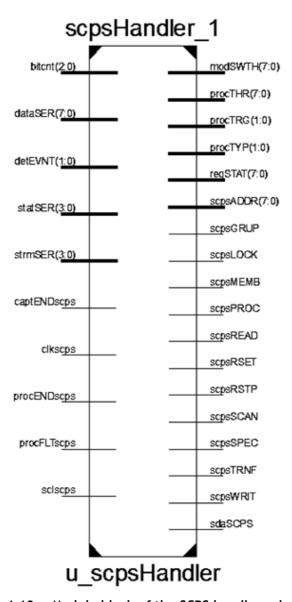

| Figure 4-16 $-$ (a) Module block of the SCPSp sub-module. (b) Module block of the register interface sub-module   | 119   |

| Figure 4-17 — Module block of the serial interface sub-module                                                     | 119   |

| Figure 4-18 — Module block of the SCPS handler sub-module                                                         | 120   |

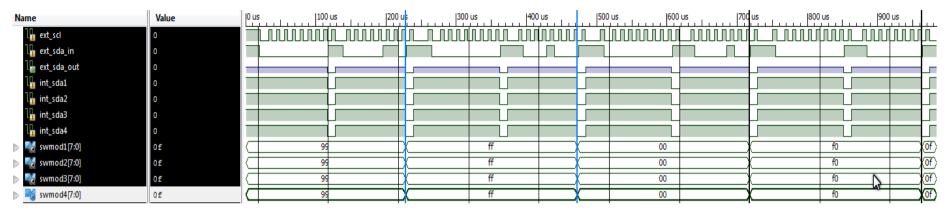

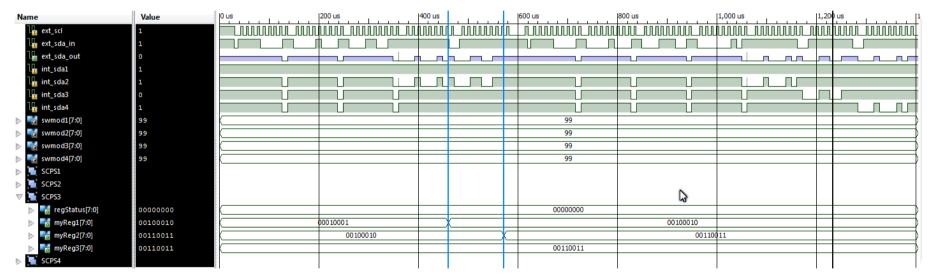

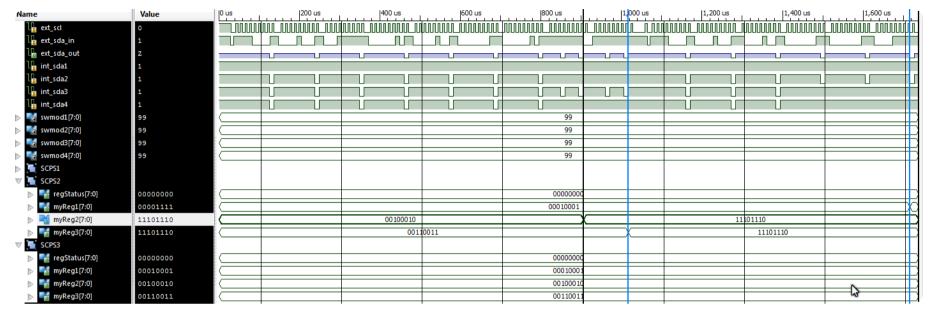

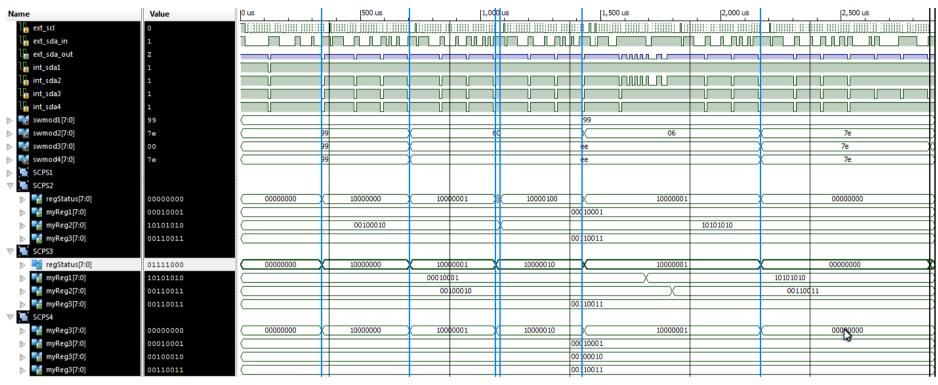

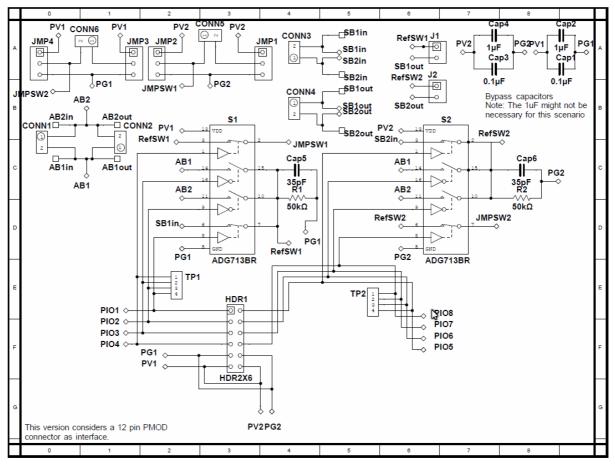

| Figure 4-19 — Functional simulation of I2C general calls followed by a SCPS general RESET, ISOLATE and E          | 3YPAS |

| command                                                                                                           | 124   |

| Figure 4-20 — Functional simulation of a SCPS transfer operation and group READ with specifier.                   | 124   |

| Figure 4-21 — Functional simulation of a SCPS transfer with specifiers and SCPS member specific WRITE.            | 125   |

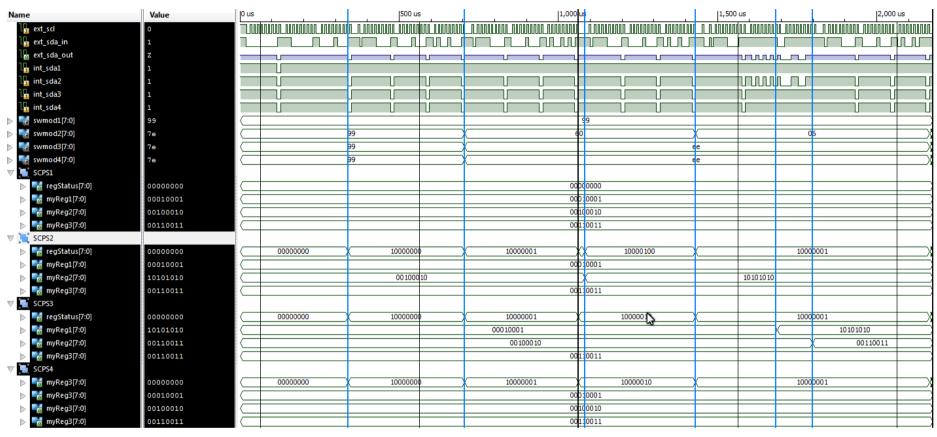

| Figure 4-22 — Functional simulation of a SCPS group CAPTURE sequence with STBY stages and data TRANSFER.          | 126   |

| Figure 4-23 — Functional simulation of a SCPS difference of read in capture and in standby                        | 127   |

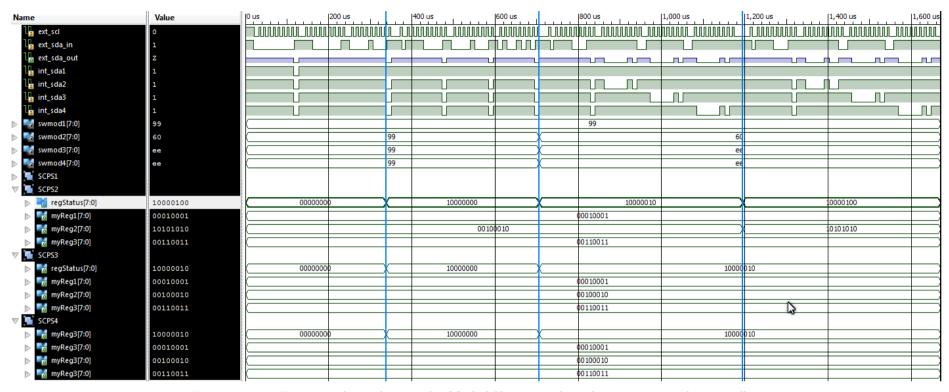

| Figure 4-24 — Functional simulation of a SCPS CAPTURE, "quick" TRANSFER and PROCESS sequence.                     | 128   |

| Figure 4-25 — Close-up of PROCESS section of the sequence of Figure 4-24.                                         | 129   |

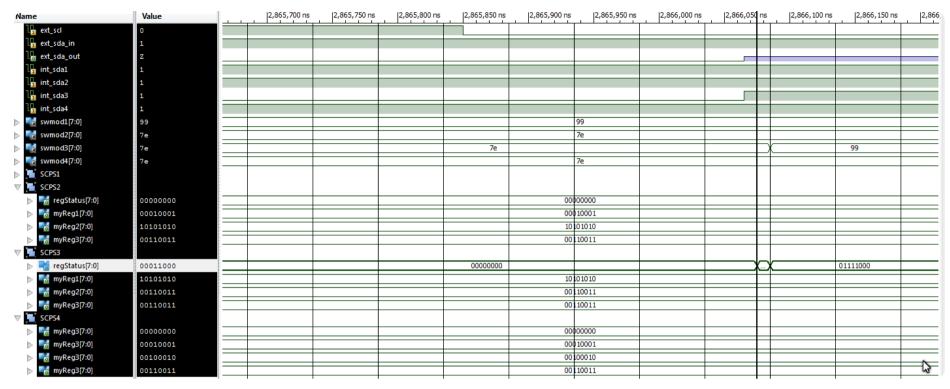

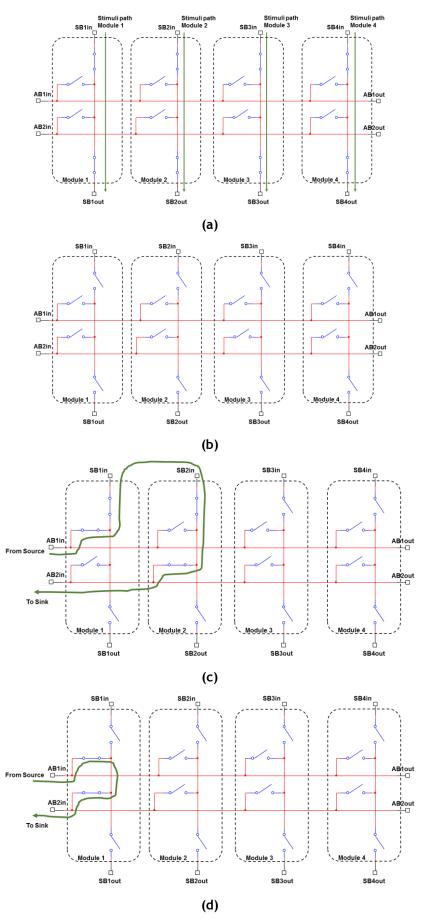

| Figure 4-26 — Universal switching structure                                                                       | 130   |

| Figure 4-27 — Schematic view of SCPS switching module                                                             | 131   |

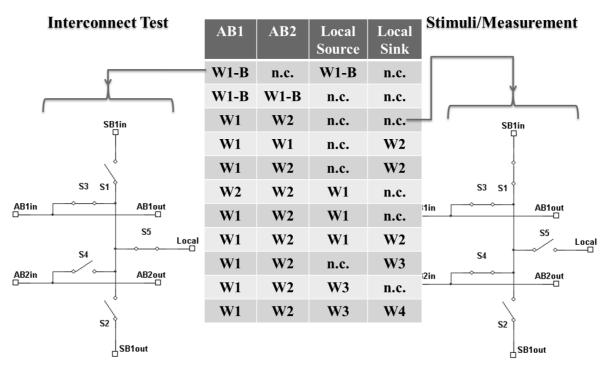

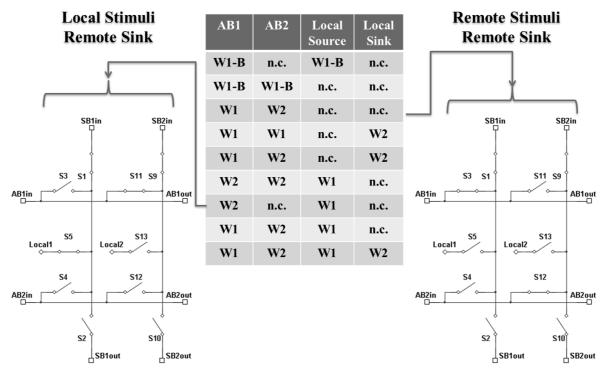

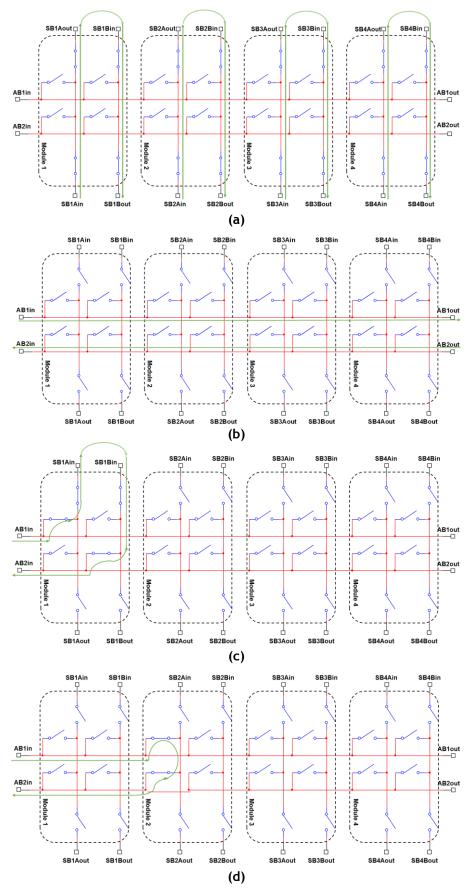

| Figure 4-28 — Single-wire switching structure various setups.                                                     | 132   |

| Figure 4-29 — Dual-wire switching structure various setups                                                        | 133   |

| Figure 4-30 — NI PXI based impedance analyser setup                                                               | 133   |

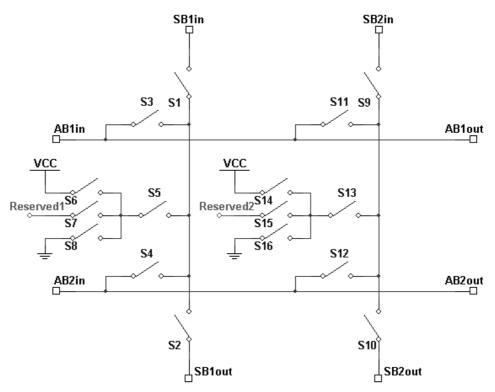

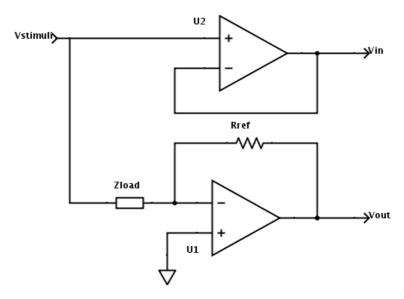

| Figure 4-31 — Dual-supply analogue front end for impedance analyser system.                                       |       |

| Figure 4-32 — Single-supply analogue front end for impedance analyser system                                      | 136   |

| Figure 4-33 — Initial impedance analyser screen-shot.                                                             | 137   |

| Figure 4-34 — Stimuli-response wave visualization screen of the impedance analyser VI                             | 138   |

| Figure 4-35 — Internal screen shot of impedance analyser VI                                                       | 138   |

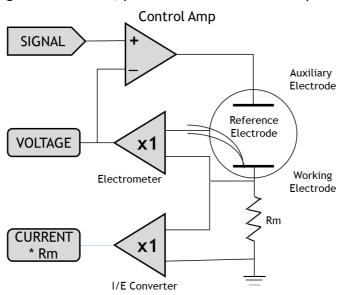

| Figure 4-36 — Diagram of Gamry series G 300 potentiostat circuit. Enhanced figure extracted from (C               | SAMR' |

| Instruments Inc., 2010)                                                                                           | 139   |

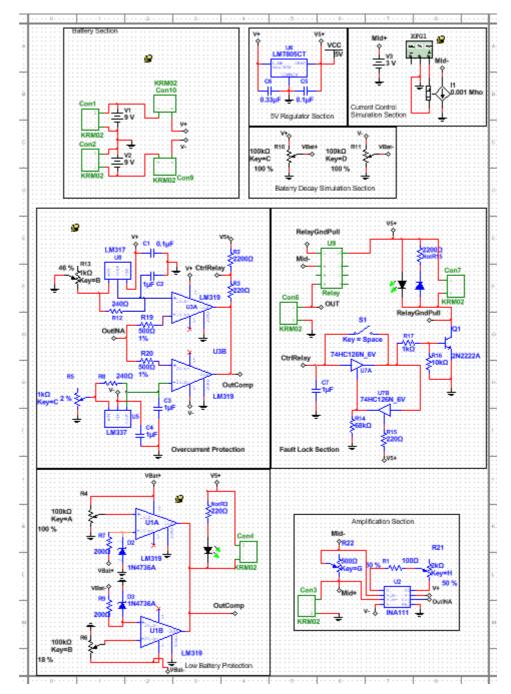

| Figure 4-37 — Overview of overcurrent-protection circuit.                                                         | 140   |

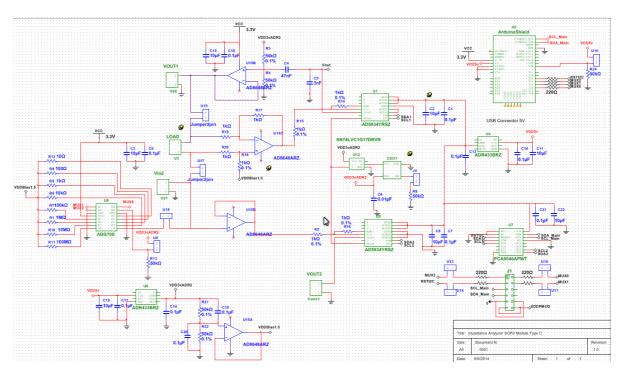

| Figure 4-38 — Overview of impedance analyser module                                                               | 141   |

| Figure 4-39 — VmodMIB VHDC module interface board                                                                 | 142   |

| Figure 4-40 — USBee ZX test pod device. Extracted from website (CWAV Inc., 2013)                                  | 143   |

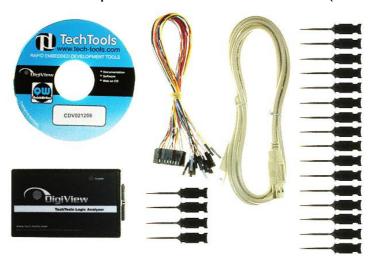

| Figure 4-41 — DV1-100 logic analyser. Extracted from website (Digikey, 2014)                                      | 143   |

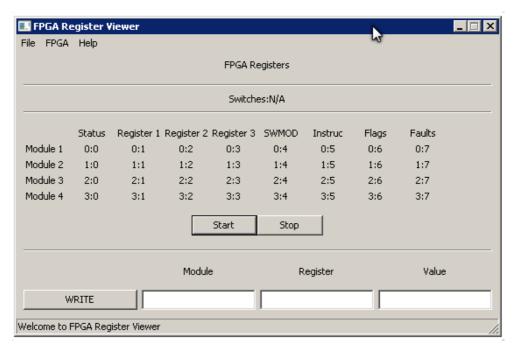

| Figure 4-42 — Snapshot of FPGA register viewer                                                                    | 144   |

| Figure 4-43 — USBee ZX I2C controller interface.                                                                  | 144   |

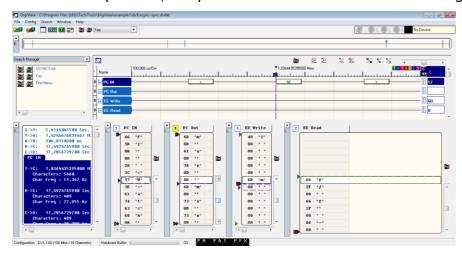

| Figure 4-44 — DigiView $^{^{	exttt{TM}}}$ portable logic analyser application                                     | 145   |

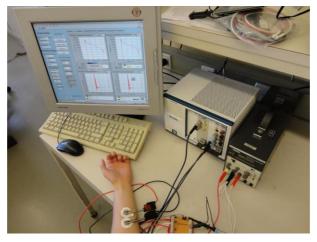

| Figure 4-45 — Hardware setup for SCPS module verification                                                         | 145   |

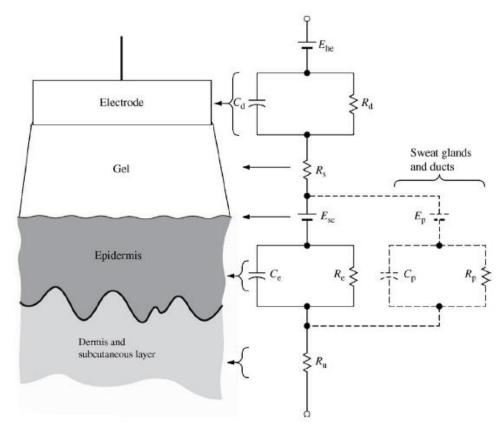

| Figure 5-1 — Electrode-skin circuit model extracted from (Webster J. , 2009).                                     | 149   |

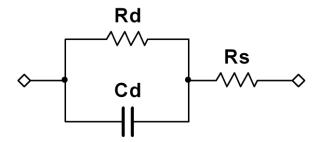

| Figure 5-2 — Simplified electrode-skin circuit model                                                              |       |

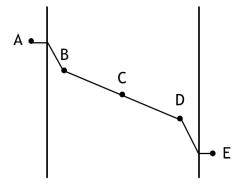

| Figure 5-3 — Potential map across a generic sample with mark reference points                                     |       |

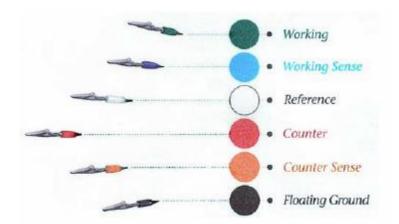

| Figure 5-4 — Gamry colour coded leads, extracted from (Gamry Instruments, Inc., 2011).                            |       |

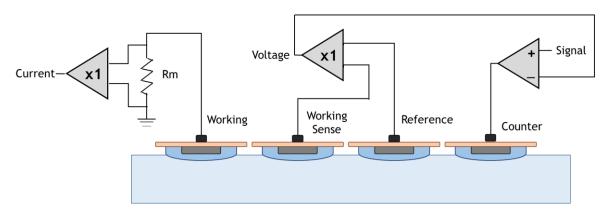

| Figure 5-5 — Four-electrode setup.                                                                                | 152   |

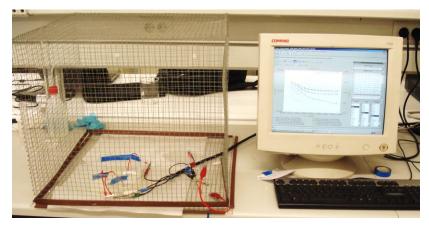

| Figure 5-6 — Electrode-Agar experimental setup. Left side: Faraday cage and agar-gel container with Gamry         | G-300   |

|-------------------------------------------------------------------------------------------------------------------|---------|

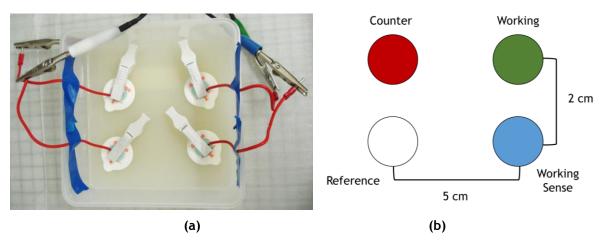

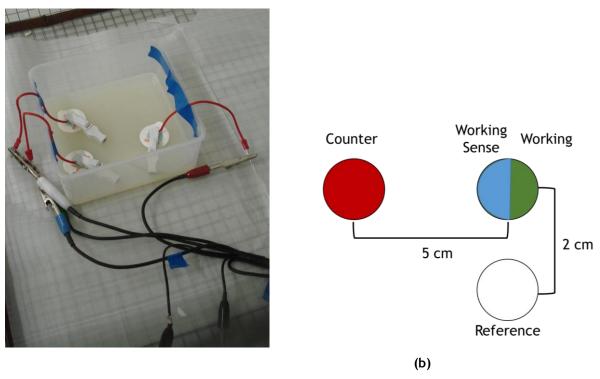

| leads. Right side: monitor with acquisition software displaying time-lapsed magnitude/phase measurements          | 153     |

| Figure 5-7 — Four-electrode arrangement for agar-gel impedance measurement. (a) Experimental setup. (b)           | Colour  |

| coded diagram.                                                                                                    | 154     |

| Figure 5-8 — Three-electrode arrangement for electrode-agar-gel impedance measurement. (a) Experimental           | setup.  |

| (b) Colour coded diagram                                                                                          | 154     |

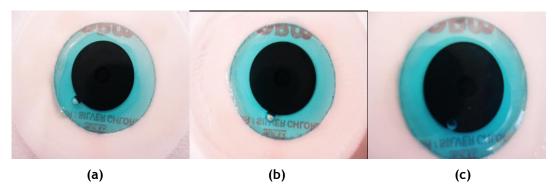

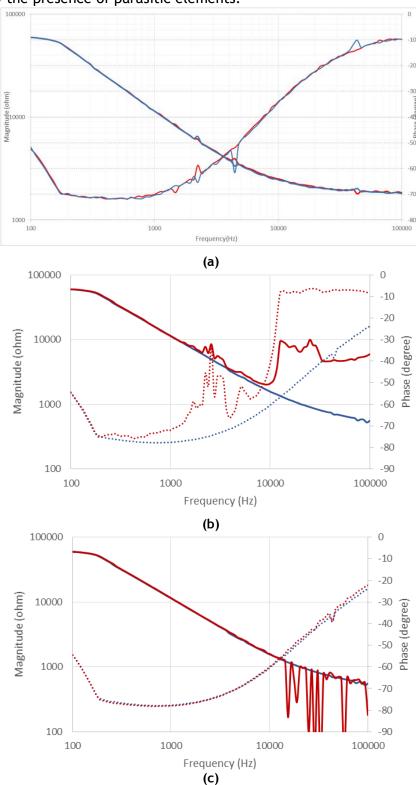

| Figure 5-9 — Three-electrode arrangement for Ag-AgCl to agar-gel measurement in normal conditions                 |         |

| Figure 5-10 $-$ (a) Electrode with small air bubble. (b) Electrode with medium air bubble. (c) Electrode with air | bubble  |

| over the metal section.                                                                                           | 156     |

| Figure 5-11 — Three-electrode arrangement for Ag-AgCl to agar-gel measurement in normal condition                 | s with  |

| electrodes that contain factory imperfections, i.e., air bubbles.                                                 | 156     |

| Figure 5-12 — Electrode-agar impedance characterization 12 hours apart.                                           | 157     |

| Figure 5-13 — Electrode-Agar impedance characterization first 6 measurements, 30 minutes apart and the 12         | ? hours |

| measurement in red.                                                                                               | 157     |

| Figure 5-14 — Electrode-agar impedance characterization showing 6 measurements 30 minutes apart starting          | at the  |

| 6th hour.                                                                                                         | 158     |

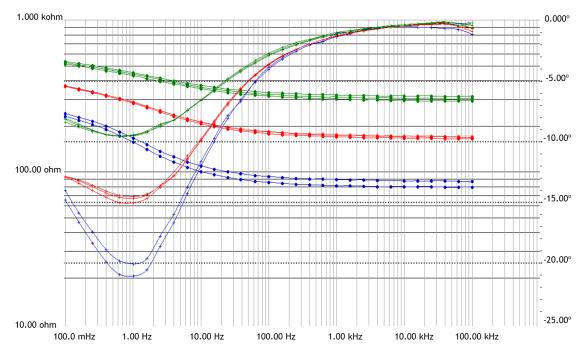

| Figure 5-15 — Electrode-Agar impedance characterization for normal scenario in blue, 50% blockage in red ar       | nd 75%  |

| blockage in green.                                                                                                | 159     |

| Figure 5-16 — Electrode-agar impedance characterization for 1 hour 70º degree exposed electrodes in red and       | 1 hour  |

| -20 degrees in blue.                                                                                              | 160     |

| Figure 5-17 — Electrode-agar impedance characterization for 5 minutes (red) and 1 hour (blue) artificial          | sweat   |

| exposed electrodes                                                                                                | 160     |

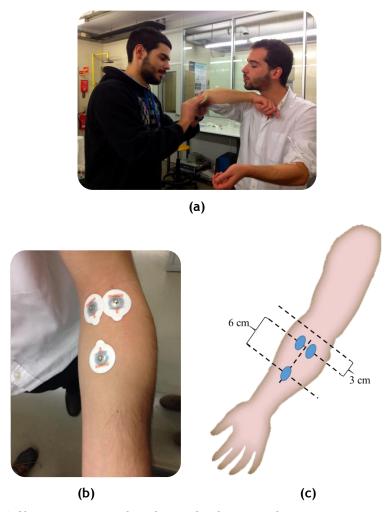

| Figure 5-18 $-$ (a) Skin preparation for electrode-skin impedance measurement. (b) Electrode placement for        | human   |

| electrode-skin impedance measurement. (c) Electrode placement diagram for electrode-skin impedance measurement    | nt. 161 |

| Figure 5-19 — Electrode characterization setup. (a) Faraday cage view, (b) Current limiter and Gamry character    | ization |

| equipment view                                                                                                    | 162     |

| Figure 5-20 $-$ (a) Close-up of volunteer within Faraday cage during electrode-skin impedance measurement. (b)    | Close-  |

| up of arm of a volunteer during an electrode-skin impedance measurement. (c) Volunteer inside Faraday cage        | during  |

| electrode-skin impedance measurement                                                                              | 162     |

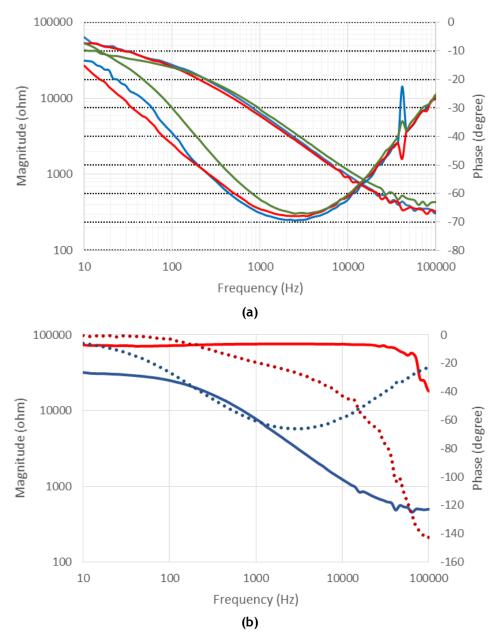

| Figure 5-21 — Electrode-skin impedance measurement for time 0 min of 4 male and 2 female student volunte          | er. (a) |

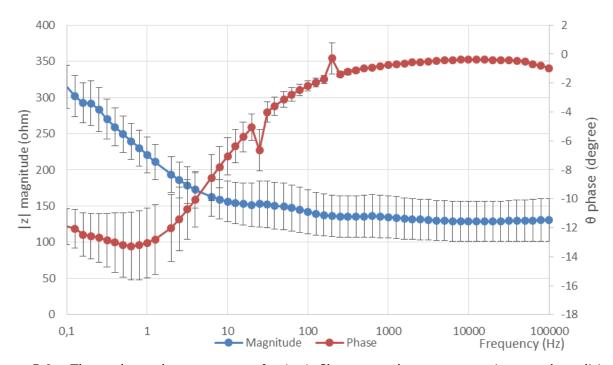

| Magnitude. (b) Phase.                                                                                             | 164     |

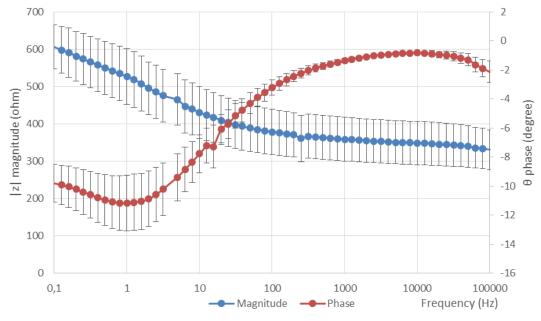

| Figure 5-22 — Electrode-skin impedance measurement average with average deviation bars (top) mag                  | nitude. |

| (Bottom) Phase                                                                                                    | 165     |

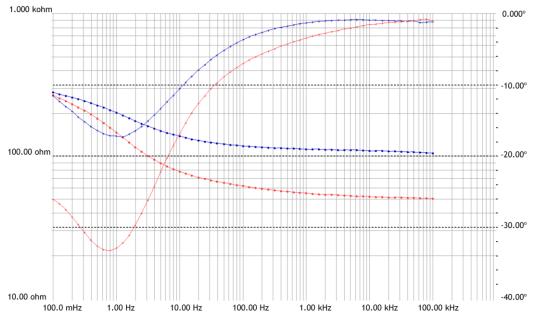

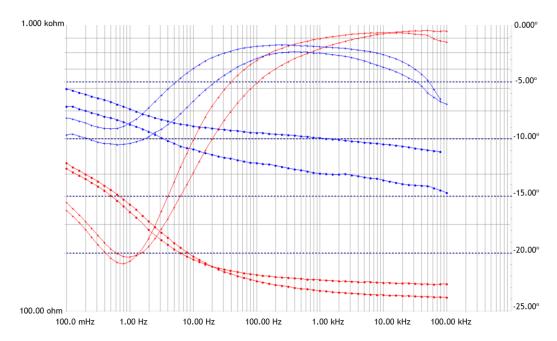

| Figure 5-23 — Time lapsed three-electrode arrangement measurements on male subject                                | 165     |

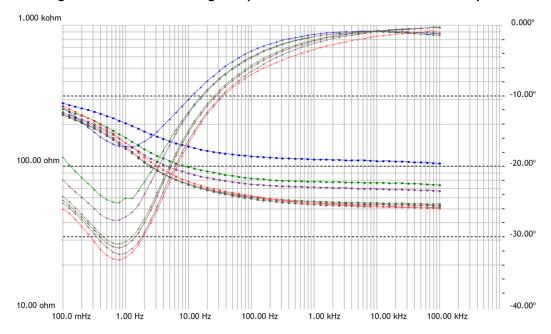

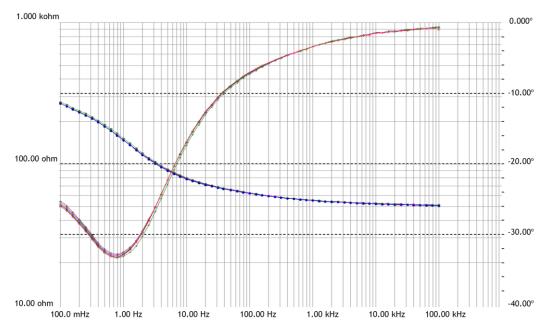

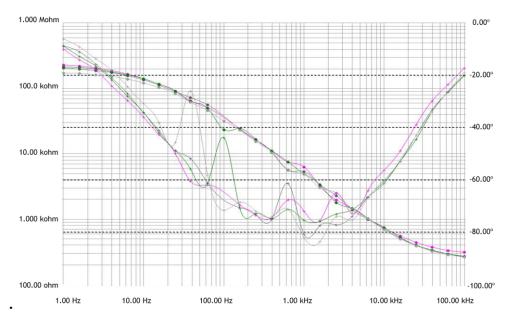

| Figure 5-24 — Electrode-skin impedance for female volunteer: 0 min. (pink), 30 min. (green), 1 hours (light grey) | , and 3 |

| hours (dark grey).                                                                                                | 166     |

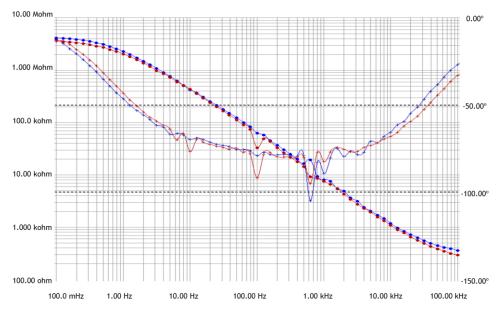

| Figure 5-25 — Electrode-skin impedance for male volunteer: 0 min (blue), 2 hours (red).                           | 166     |

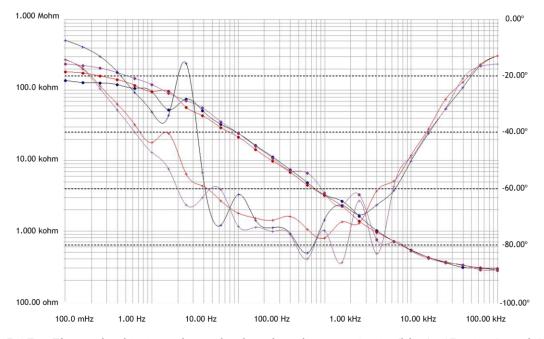

| Figure 5-26 — Electrode-skin impedance for male volunteer: 0 min (purple), 1 hour (green), and 3 hours (blue).    | 167     |

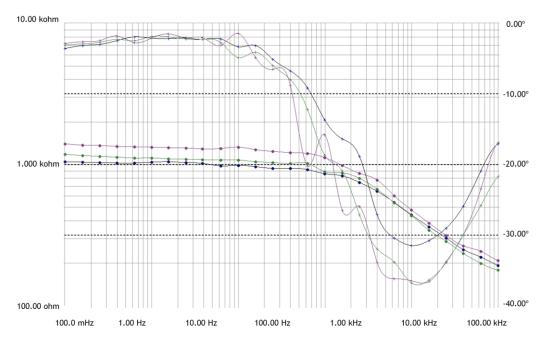

| Figure 5-27 — Electrode-skin impedance for female volunteer: 0 min (blue), 15 min. (purple), and 2 hours (red)    | 167     |

| Figure 5-28 — Electrode-skin impedance for male volunteer: 0 min (blue), 15 min. (purple), and 3 hours (red).     | 168     |

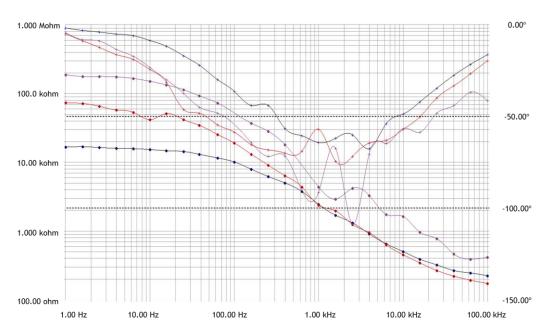

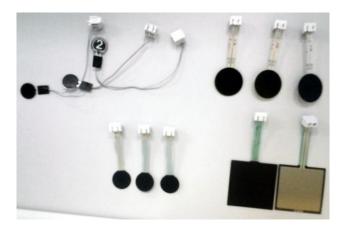

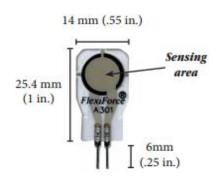

| Figure 5-29 — Variety of FSR (left). FlexiForce model A301 actual size picture extracted from (Tekscan, 201 | .(14) (right)<br>169 |

|-------------------------------------------------------------------------------------------------------------|----------------------|

| Figure 5-30 — FSR general structure, modified from (Tekscan, 2014).                                         |                      |

| Figure 5-31 — Conventional electrical setup for FSR usage.                                                  |                      |

| Figure 5-32 — Generic model for FSR, extracted from (IEE International Electronics and Engineer, 2007)      |                      |

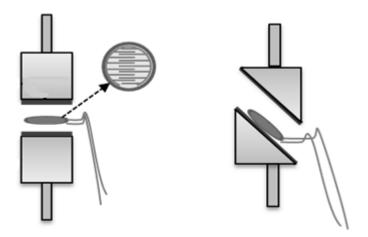

| Figure 5-33 — Pressure application setups for FSR characterization.                                         |                      |

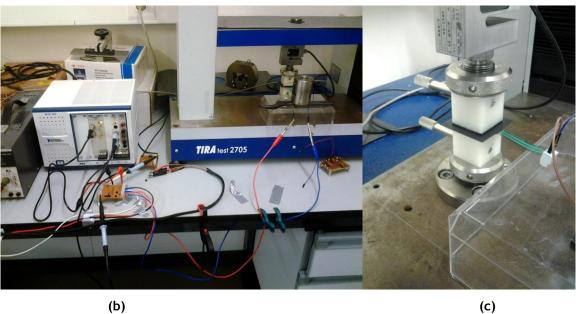

| Figure 5-34 — Tira Test 2705 FSR characterization setup. (a) View of complete experimental setup. (b) Close |                      |

| AFE arrangement and TIRA test 2705 pressure arrangement. (c) Close-up of custom made pressure element and I |                      |

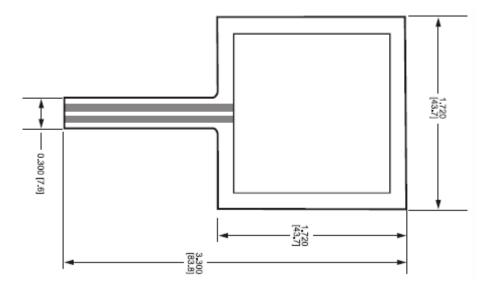

| Figure 5-35 — FSR INM-0038 dimension diagram, extracted from (Interlink Electronics, 2010)                  | _                    |

| Figure 5-36 — FSR INM-0038 (a) Front view. (b) Rear view. Extracted from (Inmotion Inc., 2010).             |                      |

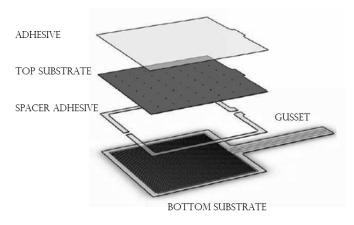

| Figure 5-37 — FSR INM-0038 layer stack-up, extracted from (Interlink Electronics, 2013).                    |                      |

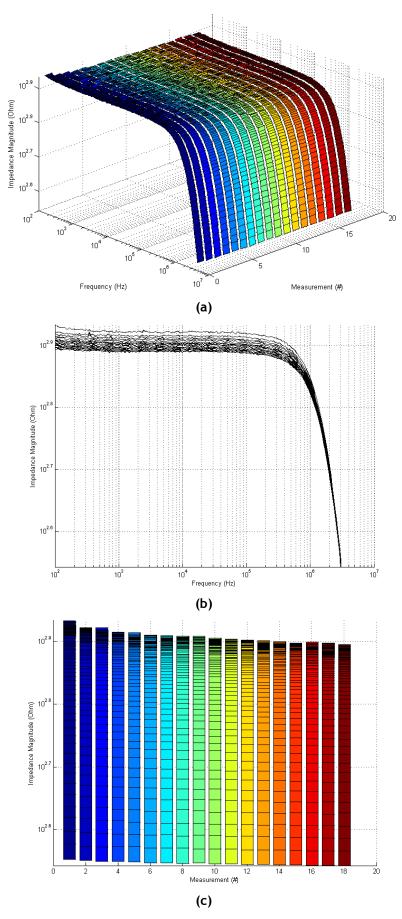

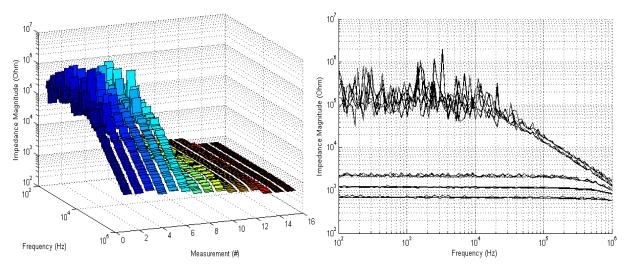

| Figure 5-38 — FSR TYPE-A measurement (a) Measurements vs frequency vs magnitude. (b) Frequency vs m         |                      |

| (c) Measurements vs magnitude.                                                                              |                      |

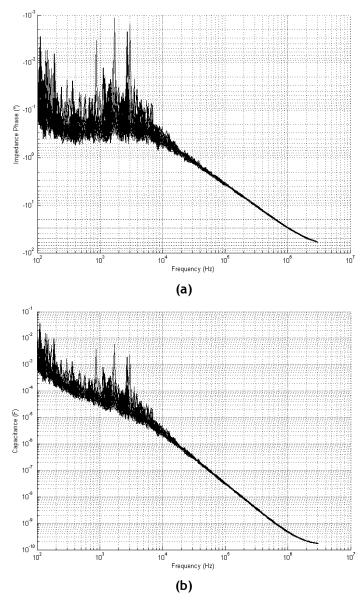

| Figure 5-39 — FSR TYPE-A measurement (a) Phase vs frequency. (b) Capacitance vs frequency.                  |                      |

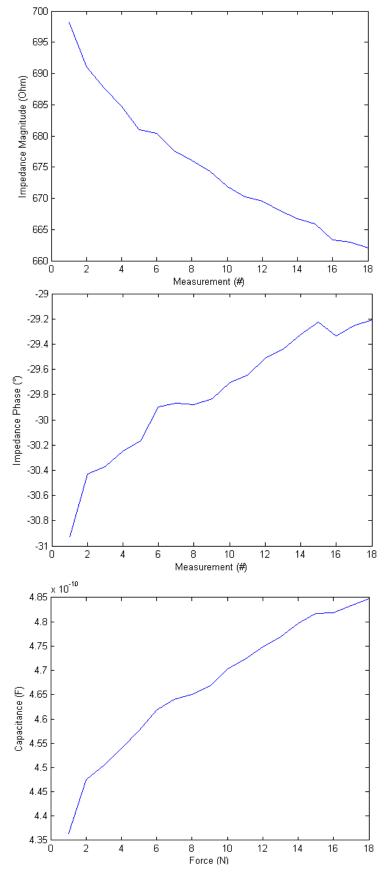

| Figure 5-40 — FSR TYPE-A measurement for 1 MHz frequency. (Top) Magnitude.                                  |                      |

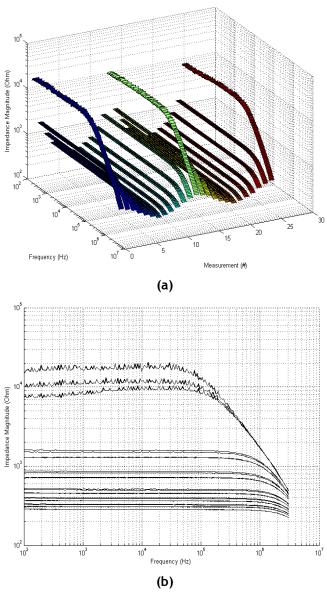

| Figure 5-41 — FSR TYPE-B measurement (a) Measurements vs frequency vs magnitude. (b) Frequency vs m         |                      |

|                                                                                                             | _                    |

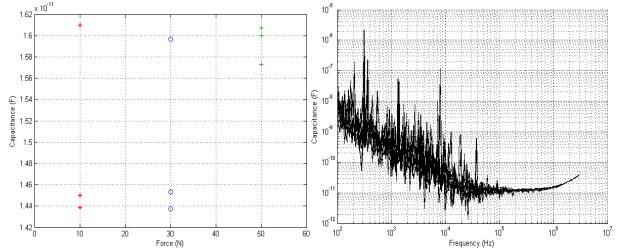

| Figure 5-42 — FSR TYPE-B measurement capacitance for 1MHz frequency.                                        |                      |

| Figure 5-43 — No-load capacitance at 1MHz measurement between degradation session (10 hours of contin       |                      |

| to 4000 N 10 second holds, with 1 mm/s speed)                                                               |                      |

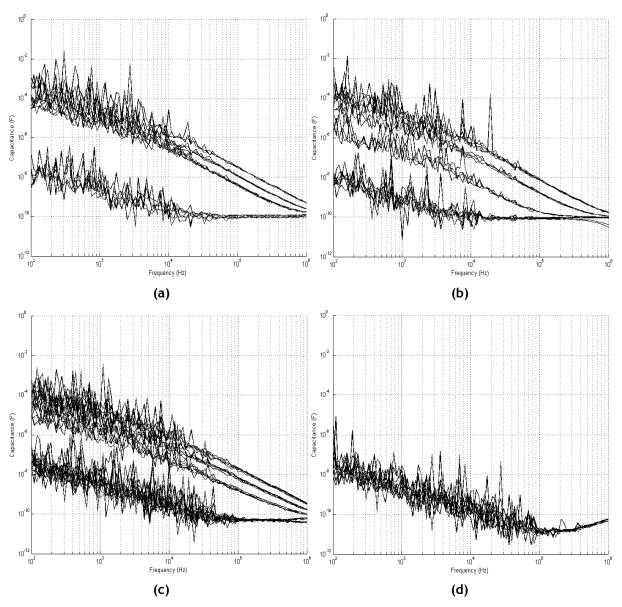

| Figure 5-44 — TYPE-B measurement after six 10 hours degradation sessions. (a) Measurements vs free          |                      |

| magnitude. (b) Frequency vs magnitude. (c) Measurements vs magnitude. (d) Force vs capacitance              | 181                  |

| Figure 5-45 — TYPE-B measurement after bending. (a) Measurements vs frequency vs magnitude. (b) Fre         | quency vs            |

| magnitude. (c) Measurements vs magnitude. (d) Force vs capacitance.                                         | 182                  |

| Figure 5-46 — Capacitance measurements after FSR breakdown for multiple forces. (Right) Capacitance vs      | frequency            |

| of all measurements. (Left) Capacitance vs force for all measurements                                       | 183                  |

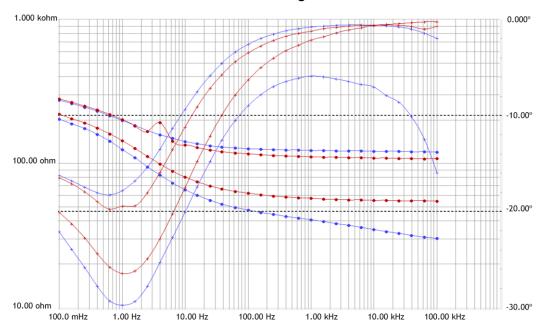

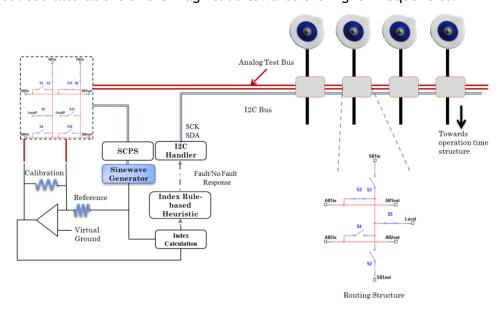

| Figure 6-1 — A SCPS based approach for electrode fault detection                                            |                      |

| Figure 6-2 — Electrode-skin impedance two-electrode arrangement for male volunteer (a) Back to back meas    | surements            |

| (b) Motion artefact (c) Loose connector. Initial measurement in blue, secondary measurement in red.         | 187                  |

| Figure 6-3 — Electrode-skin impedance two-electrode arrangement on male volunteer (a) Three back            | k to back            |

| measurements (b) Bad connection. Initial measurement in blue, secondary measurement in red. In case of      | (a) initial          |

| measurement in green                                                                                        | 188                  |

| Figure 6-4 — Pseudo-code for three electrode pair measurements.                                             |                      |

| Figure 6-5 — Switching states for a four-electrode scenario. (a) BYPASS state. (b) ISOLATE state. (c) Elec  | trode-pair           |

| connection (electrode 1 with electrode 3). (d) Line verification state.                                     | 192                  |

| Figure 6-6 — A SCPS based arrangement for FSR.                                                              | 193                  |

| Figure 6-7 — TYPE B measurement using single-supply AFE for multiple repetition of no-load, minimal         | load, 250            |

| grams, 500 grams and 1 kilogram. (Left) Measurements vs frequency vs impedance magnitude. (Right) Fred      | quency vs            |

| impedance magnitude                                                                                         | 194                  |

| Figure 6-8 — TYPE B measurement of capacitance for multiple FSR scenarios: (a) Normal. (b) Obstr            | ucted. (c)           |

| Damaged. (d) Breakdown.                                                                                     | 195                  |

| Figure 6-9 — Pseudo-code for FSR measurement.                                                           | 196                 |

|---------------------------------------------------------------------------------------------------------|---------------------|

| Figure 6-10 — Switching states for a four-FSR scenario. (a) Regular operation state. (b) BYPASS state   | e. (c) FSR module 1 |

| connection. (d) Line verification state.                                                                | 199                 |

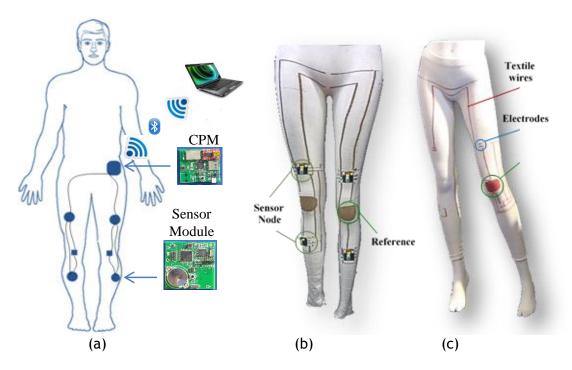

| Figure 6-11 $-$ (a) Gait analysis infrastructure (b) Early prototype of gait analysis system (c) Textil | e embedded wires    |

| and electrodes                                                                                          | 202                 |

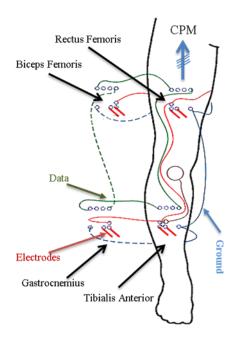

| Figure 6-12 — Gait analysis structure detailed view.                                                    | 202                 |

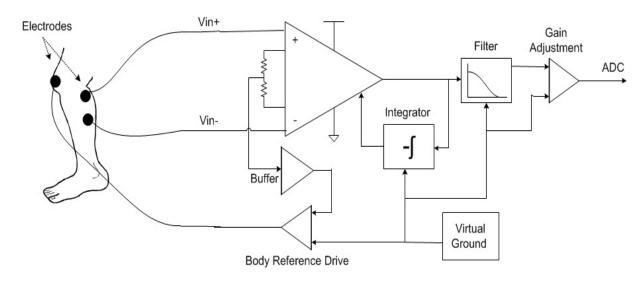

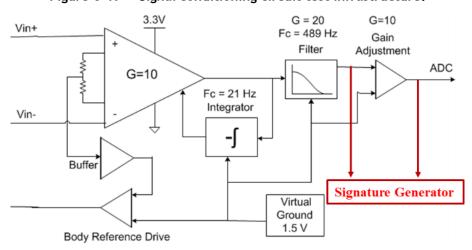

| Figure 6-13 — EMG signal conditioning module structure.                                                 | 203                 |

| Figure 6-14 — Overview of generic embedded instrument with proposed infrastructure                      | 204                 |

| Figure 6-15 — EMG module BIST structure.                                                                | 204                 |

| Figure 6-16 — Electrode-skin verification structure                                                     | 205                 |

| Figure 6-17 — Signal conditioning circuit test infrastructure.                                          | 206                 |

| Figure 6-18 — Signal conditioning circuit test nodes                                                    | 206                 |

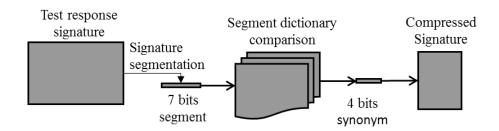

| Figure 6-19 — Compression algorithm overview.                                                           | 207                 |

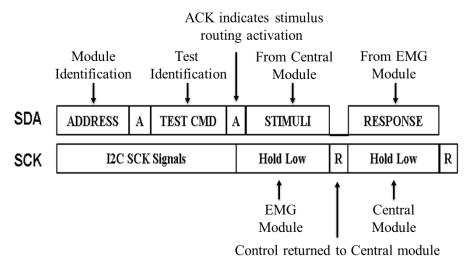

| Figure 6-20 — SCPS/I2C compatible sequence for stimulus/response transport.                             | 207                 |

# **List of Tables**

| Table 2-1. Comparison of commercially available sensor nodes                                   | 17  |

|------------------------------------------------------------------------------------------------|-----|

| Table 2-2 Wearable monitoring technology overview                                              | 21  |

| Table 3-1 SCPS Spartan 6 resource utilization                                                  | 76  |

| Table 3-2. SCPS framework example 1                                                            | 87  |

| Table 4-1. GLOBAL instructions summary                                                         | 107 |

| Table 4-2. SETUP instruction summary                                                           | 108 |

| Table 4-3. CAPTURE instruction overview                                                        | 110 |

| Table 4-4. PROCESS instruction overview                                                        | 111 |

| Table 4-5. SCAN instruction overview                                                           | 112 |

| Table 4-6. Dual-supply AFE 1 kΩ reference magnitude measurements from 100Hz to 1MHz            | 135 |

| Table 4-7. Dual-supply AFE 1 k $\Omega$ reference phase measurements from 100Hz to 1MHz        | 135 |

| Table 4-8. Single-supply AFE 1 k $\Omega$ reference magnitude measurements from 100Hz to 1MHz  | 136 |

| Table 4-9. Single-supply AFE 1 k $\Omega$ reference phase measurements from 100Hz to 1MHz      | 136 |

| Table 5-1 FlexiForce model A301 specifications                                                 | 169 |

| Table 5-2 FSR 400 series characteristics, extracted from (Interlink Electronics, 2013)         | 174 |

| Table 5-3 Summary of measurements for varying pressures for <100 kHz                           | 179 |

| Table 5-4 Summary of measurements for varying pressures for > 100 kHz after degradation        | 181 |

| Table 5-5 Summary of measurements for varying pressures for <100 kHz after FSR bending         | 182 |

| Table 6-1 SCPS instructions for electrode-pair verification flow.                              | 190 |

| Table 6-2 Continuation of SCPS instructions for electrode-pair verification flow               | 191 |

| Table 6-3 Summary of measurements for varying pressures for < 100 kHz with single-supply setup | 194 |

| Table 6-4 SCPS instructions for FSR verification flow.                                         | 197 |

| Table 6-5 Continuation of SCPS instructions for FSR verification flow                          | 198 |

| Table 6-6 SCPS instructions for FSR verification flow using "on-the-fly" instructions          | 200 |

# **Acronyms and Abbreviations**

List of acronyms, abbreviations and initialisms (ordered alphabetically)

- 10GA: 10-bit group address.

- ABM: analogue boundary module.

- ACK: acknowledge.

- ADC: analogue to digital converter.

- AFE: analogue front end.

- ATB: analogue test bus.

- BAN: body area network.

- BILBO: built-in logic block observer.

- BIST: built-in self-test.

- BISTC: built-in self-test/calibration.

- BSDL: boundary scan description language.

- BSN: body sensor network.

- CAN: controller area network.

- CAPT: capture.

- CFI: cell functional input.

- CFO: cell functional output.

- CIS: capture instruction set.

- CPM: central processing module.

- CTI: cell test input.

- CTL: cell test language.

- CTO: cell test output.

- DARPA: Defence Advanced Research Projects Agency.

- DC: direct current.

- DfT: design for testability.

- DIAMOND: Diagnosis, error-modelling and correction for reliable systems design.

- ECG: electrocardiography.

- EEG: electroencephalography.

- ELESIS: European library-based flow of embedded silicon test Instruments.

- EMBS: Engineering in Medicine and Biology Society.

- EMG: electromyography.

- EOG: electrooculography.

- ESA: embedded system access.

- ESTSP-IPP: Escolar Superior de Tecnologia do Saúde do Porto Instituto Politécnico do Porto.

- FEUP: Faculdade de Engenharia da Universidade do Porto.

- FPGA: field programmable gate array.

- FSR: force sensing resistor.

- GADDR: group address.

- GNU: GNU's Not UNIX.

- GPS: global positioning system.

- GRP: group register pointer.

- GUI: graphical user interface.

- GWP: group write pointer.

- HBIST: hybrid BIST.

- HTSG: hybrid test signal generators.

- I2C or IIC: inter-integrated circuit.

- IC: integrated circuit.

- IEEE: Institute of Electrical and Electronics Engineers

- IIC or I2C: inter-integrated circuit.

- INSTR: instruction register.

- IR: instruction register.

- LED: light emitting diode.

- LFSR: linear feedback shift register.

- LSB: least significant bit.

- MADDR: member address.

- MEMS: micro-electromechanical systems.

- MISR: multiple input shift register.

- MSB: most significant bit.

- NI: national instrument.

- OBIST: oscillation BIST.

- PCB: printed circuit board.

- PrIS: process instruction set.

- PROC: processing.

- PSET: pre-setting configuration.

- PXI: peripheral component interconnect) eXtensions for instrumentation.

- RQST: request.

- RRP: read register pointer.

- RTL: register-transfer level.

- RX: receive, receiver or reception.

- ScIS: scan instruction set.

- SCL: I2C serial clock line.

- SCPS: Setup Capture Process Scan.

- SDA: I2C serial data line.

- SGT: SCPS global transaction.

- SIB: segment insertion bit.

- SiP: system in package.

- SIS: setup instruction set.

- SMBUS: system management bus.

- SNR: signal to noise ratio.

- SoC: system on chip.

- SPI: serial peripheral interface.

- Sr: I2C re-start.

- SRT: SCPS read transaction.

- STATU: SCPS status register.

- STBY: SCPS stand-by register.

- STIL: standard test information language.

- STT: SCPS transfer transaction.

- SWT: SCPS write transaction.

- TAM: test access mechanism.

- TAP: test access port.

- TBIC: test bus interface circuit.

- TCK: test clock.

- TDO: test data out.

- TDI: test data in.

- TDR: test data register.

- TKR: SCPS token register.

- TMS: test mode select.

- TOETS: Towards One European Test Standard.

- TRST: test reset.

- TX: transmit, transmitter or transmission.

- UDP: user defined parameter.

- UDR: user defined register.

- USB: universal serial bus.

- VI: virtual instrument.

- W2M2: wireless wearable monitoring module.

- WBAN: wireless body area network.

- WBC: wrapper boundary cells.

- WBR: wrapper boundary register.

- WBSS: wearable biomedical sensors and systems.

- WBY: wrapper bypass register.

- WIMU: wearable inertial monitoring unit.

- WIR: wrapper instruction register.

- WMT: wearable monitoring technology.

- WPAN: wireless personal area network.

- WPP: wrapper parallel port.

- WRP: SCPS write register pointer.

- WSC: wrapper serial control.

- WSI: wrapper serial input.

- WSN: wireless sensor network.

- WSO: wrapper serial output.

- WSP: wrapper serial port.

- ZRA: zero resistance ammeter.

# Chapter 1

# Introduction

## 1.1 Motivation and Problem Definition

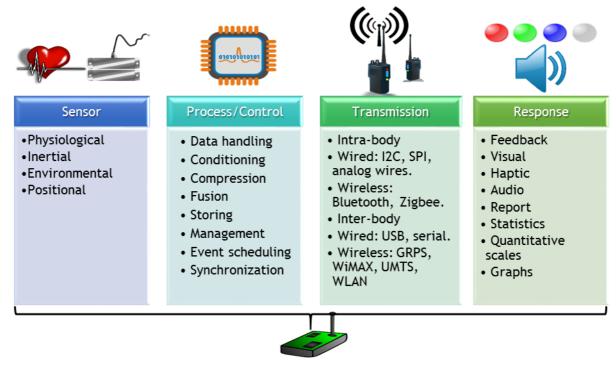

Words such as ubiquitous, pervasive, ambient, and seamless are common among most technological research areas of our day. The quest for integrating the individual within areas of technological development never has been more sought after, or among so many and varied fields. With each passing day, commercial products seem to become smaller, more complex, and more importantly, designed to be portable (dare we say wearable); the need for an individual to remain untethered seems to dominate most electronic consumer markets. Advances within technological domains such as, integrated circuits (IC), body/wireless sensor networks (BSN and WSN respectively), smart sensors, and data processing, to name a few, have contributed to the last decade's proliferation of systems designed for monitoring and responding to an individual's actions and reactions. Such human-centric approach has consequently affected the way one has come to think of personal performance and daily activities monitoring, as well as intervention assessment, progress appraisal, biosignals acquisition; and naturally a new array of associated challenges emerges.

Multiple paradigms shifts are taking place, were the snap-shot approach is replaced by continuous prolonged data gathering (e.g., instead of a doctor's consult, a patient's condition can be monitored for days or weeks); the laboratory is replaced by every day settings; and where real-time analysis is becoming a protagonist. Wearable monitoring technology (WMT) introduces a refinement to personal monitoring by allowing a long-term on-person directcontact approach; thus permitting for a new level of understanding of an individual's interaction with their surrounding environment. Multi-sensor settings, non-standard assembly, heterogeneous components, and unorthodox operating situations are a few of the conditions commonly addressed by WMT; thus a wide variety of systems can be expected. Many examples can be cited when referring to WMT: LifeGuard (Mundt, Montgomery, Udoh, & al., 2005), ClimBSN (Pansiot, ing, Mcllwraith, Lo, & Guang-Zhong, 2008), Ayushman (Venkatasubramanian & Gupta, 2008), BIOTEX (Coyle S., Lau, Moyna, & al., 2010), SwimMaster (Bächlin, Föster, & Tröster, 2009), to name a few pioneers, designed for numerous purposes, scenarios and environments (an extended examination of the WMT topic will be covered in Chapter 2), and Portugal has actively contributed in this endeavour, including projects from the Faculty of Engineering of the University of Porto (FEUP) such as: WalkinSense (Telgenkamp, 2012) a product from Tomorrow Options (now Kinematics, a startup commenced within FEUP), the BIOSWIM project which produced the WIMU - wearable inertial monitoring unit (Silva, Salazar, Borges, & Correia, 2013), W2M2 - wireless wearable monitoring module, produced for the *Escola Superior de Tecnologia de Saúde do Porto* for rehabilitation progress monitoring purposes (Salazar, et al., 2013), and the ProLIMB project (da Silva J. M., 2014).

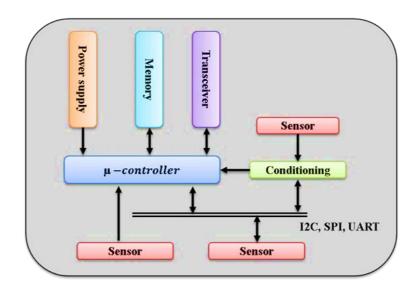

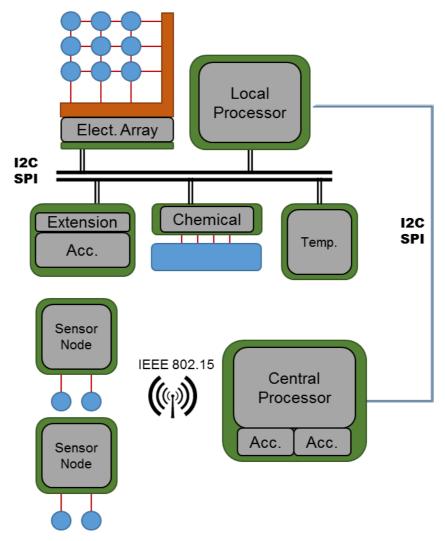

Figure 1-1 — Generalized wearable module architecture.

Wearable monitoring solutions are expected to become commonplace devices within numerous fields such as healthcare, rehabilitation, assistive technology, sports, and even entertainment, driving the need for universal options as opposed to custom designs. The before mentioned expectations require a highly flexible approach, there seems to be some concensus on the general design of a sensor node (Van Laerhoven K., et al., 2004) (Tufail & Islam, 2009) (Pantelopoulus & Bourbakis, 2010) (Rehman, Mustafa, Javaid, Qasim, & Khan, 2012) (Lara & Labrador, 2013) (Virk, 2013); following the structure presented by the BSN node project (Lo & Yang, 2007), seen in Figure 1-1.

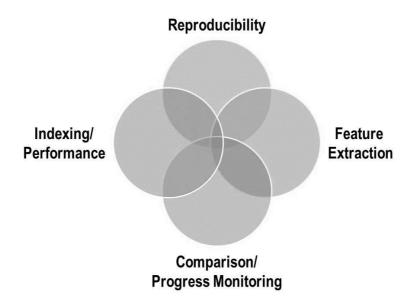

In the case of healthcare and rehabilitation facilities, monitoring systems are expected to be reused by a number of individuals and for changing life-cycles, varying from one-time use to shelve-life measured in years. In spite of the present progress, there are a number of obstacles to overcome for truly achieving seamless WMT, such as: energy availability, data compression, textile integration, feature extraction, pattern/event recognition, and biomechanical models, among many more. Nevertheless, considering that WMT's general purpose is the monitoring of an event, be it a physiological, inertial, or otherwise subject/environment influenced parameter, data reliability becomes of paramount importance; not to mention inter-session and inter-subject data comparability for systems intended for multiple uses and users. How can we insure that the equipment performs the same way between subjects and sessions? Or stated differently, how can we confidently compare the data? A number of factors come into play such as sensor quality (which can affect data resolution and error), positioning (which can vary due to physiology of the

patient, sensor shape and size, not to mention the ability of the physician/subject to place the sensor), degradation, to mention a few. All mentioned factors influence the collected data, which can have a strong effect on the final result if not compensated through calibration, filtering or associated strategies which contribute to final data comparability. Even though some compensation strategies can be applied after the fact, through data processing at software level, or through signal conditioning (e.g., filtering out noise), *in-situ* mechanism are sometimes needed, such as the classic right leg drive circuit for ECG measurements.

Wearable and portable monitoring devices are on the rise; however, modest attention has been paid to supplementary calibration/testing protocols and mechanism, in order to insure the reliability and comparability of the measurements, especially when considering long term scenarios. The concept of reliability itself needs to be adjusted from that of traditional IC and device testing, which considers field failure rate and the balance of manufacturing cost and yield (International Technology Roadmap for Semiconductor, 2011). It is no longer the case that one needs to verify the device (and its subsections) only during production or once postproduction (prior to customer shipping); product quality needs to be verified continuously during the active product life, even during usage for some instances, such as the case of WMT. The concern for some WMT is not if the system or its components will fail, instead a certainty that it will fail at different levels at some point during operation. Constantly changing conditions on the sensors could produce sporadic failures (e.g. temporary disconnects of an electrode), measurement condition degradation or even a change in the sensor's transconductance reference scale. A complex problem when considering that analogue and sensor testing are considered to be in their infancy (Azimane, 2012) when compared to the digital arena.

Traditional approaches such as parametric characterization or hardware specific testing apparatus are far from providing the cost stabilizing effects achieved by automatic testing equipment (ATE) and built-in self-testing (BIST) during the last decades of digital technology revolution. This is of particular concern when considering *in-situ* solutions which require external equipment independence; such strategies are not only limited in space, resources and accessibility (the traditional concerns of testing), they also require operation time transparency.

The world of testing seemed to favour embedded system access solutions (ESA) in the past decade (Wenzel & Ehrenberg, 2012). In fact, embedded instruments are making their mark as well, as it is evidenced by the focus of standards such as IEEE STD. 1687 and the efforts being done to develop ESA standard libraries in the "European library-based flow of embedded silicon test Instruments" (ELESIS) project (ENIAC, 2013). Although embedded test instruments can serve to increase the test quality by providing target localized resources, they are not a complete solution. Issues such as accessibility and controllability only exacerbate on WMT, due to the heterogeneous nature of their elements; and although a number of strategies can

be extrapolated from traditional testing (functional and structural alike), BIST, and design for testability (DfT), especially those aimed for system on chip (SoC) and system in package (SiP) (system in package), key differences exists that require a different approach (coverage of current testing strategies are presented of Section 2.2). The issue remains, as most testing strategies and standards were designed with the production line mind frame, as opposed to product active life time.

A number of standards and proposals are currently being used for digital and analogue testing accessibility, where the undebatable golden standard is the IEEE 1149.1. Originally meant as a set of modules and registers for facilitating board level test access through a boundary scan approach, the 1149.1 has proven extremely flexible, supporting a wide array of approaches for testing, debugging, and even in-circuit programming. Among other well-documented standards one finds the: IEEE standards 1149.4, 1149.6 and most recently 1149.7 (a discussion of such standards can be found in Section 2.2.3). The evolution of packaging strategies and increased circuit complexity has demanded the formulation of new standards that address such issues, such as the IEEE 1500 and the IEEE STD. 1687 (expected to reach standard level in short time), which are aimed for different scenarios such as core testing within SoC and for embedded instrumentation, respectively. All these standards aim to facilitate the testing of the different target elements by providing a structured access, while homogenizing the control process, but still more work is needed in order to fill the gaps left by analogue, sensor and mixed-signal testing.

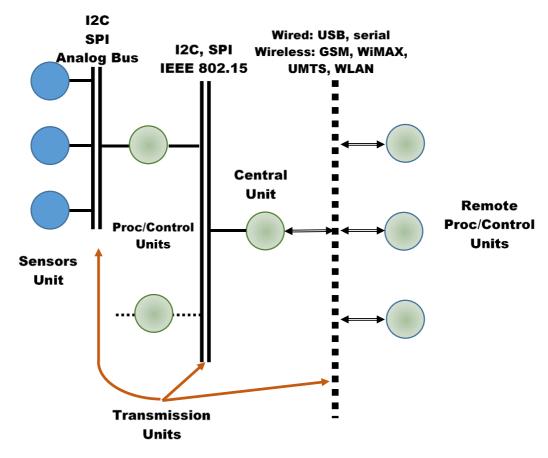

Multi-sensor centric systems present the same accessibility issues found at core or board testing levels. Likewise, they can be composed by a heterogeneous array of packages, joined by innovative non-planar ways (e.g., layered flexible PCB for instance), or include distributed interconnected modules; which only serves to exacerbate the accessibility issue. In addition, if testing (on-line or off-line) during normal operation is required, static specification or fault-models might prove insufficient, and adaptive testing strategies need to be applied while limited to *in-situ* resources. The ideal scenario is to verify functionality of a sensor under known stable conditions as to compare with a well-established reference in order to determine deviations. Nonetheless, that is not possible for operation time testing, so alternative strategies based on context-awareness, sensor redundancy, and multi-modal data fusion are sometimes necessary. Furthermore, references for some sensors are quite sensitive to drift, hysteresis, temperatures and other factors, producing a lack of well-defined fault and behavioural models as norm. The interface of sensors with the physical environment presents an unpredictable state when performing a test during operation (or during controlled conditions for that matter), making functional and structural strategies specifications a moving target. In order to better understand such scenarios let's consider two common WMT passive sensors: electrodes and force sensing resistors (FSR).

A number of biosignals (such as ECG, EMG, EEG, EOG, bioimpedance) can be captured through the use of electrodes (be it disposable, dry, textile, capacitive, etc.), which provide

a wealth of information regarding the subject — cardiac properties, muscle activity, ocular activity, nerve activity are some of the associated measures. Electrodes for biomedical applications are well understood and have been utilized for decades. The problematic influence of the electrode-skin interface in measurements has been subject of different studies. The works presented in (Spach, Barr, Havstad, & Long, 1966) (Rosell, Colominas, Riu, Pallas-Areny, & Webster, 1988) (McAdams, Jossinet, Lackermeier, & Risacher, 1996) (Huigen, Peper, & Grimbergen, 2002) (Kappenman & Luck, 2010) provide a sample of relevant related issues on the subject. The sensor in this case, while basically a piece of metal (or metal bonded material, such as the case for textile electrodes), combines with the subject to form a continuously fluctuating element, dependant on numerous ever changing parameters, such as sweat, temperature, pressure, power-line interference, and motion.

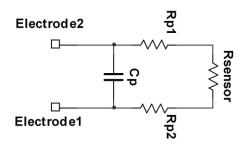

Commonly, a pairing of electrodes is necessary due to their half-cell nature, which complicates any functional or structural approach. In spite of the before mentioned complications, a number of models have been proposed to describe the electrode-skin interface. Swanson and Webster (Swanson & Webster, 1974) proposed a single time-constant linear-component equivalent model of the electrode-skin impedance which, although limited due to the non-linear nature of the interface, is widely utilized and has sprung many variations and alternative models. These models permit the formulation of specification parameters, but are quite dependant on the subject and remain time variant.

In the case of FSR sensors, different challenges are present (Buis & Convery, 1997). For these sensors the issue is not as much a problem of condition variations as FSR do not create an intrinsic relation with the object pressuring them, even though atmospheric pressure, temperature, humidity play a part on its response. FSR can be modelled as a capacitor in the absence of minimal pressure and as a variable resistor when a force is applied. In case a catastrophic failure occurs, such as a sensor connector breakage, its behaviour becomes indistinguishable from a non-pressure condition without the necessary precautions; moreover, the outer membrane's elasticity is well known to cause drift and hysteresis effects. While this might not be crucial for crude measurements or pressure switching scenarios, when utilized for sensitive measurements, wear and tear, bending, constant pressure, could introduce a significant error on the measurements. Fine tuning calibration might not be possible in a runtime scenario due to the lack of a reference pressure stimulus; however, a general idea of the health status might be, thanks to alternative approaches, as one based on the frequency response analysis.

It is not uncommon to find these two sensor cases in the form of arrays or distributed sensors, which in order to reduce wires and consolidate components, benefit of resource sharing such as an analogue bus and/or localized instruments (such as stimuli generators or signal conditioning section for acquisition). Such scenarios require synchronization strategies for routing, activation, etc., in order to avoid elements usage overlapping and even damage

to components. The associated required control and accessibility complexity could combine with design for testability (DfT) strategies to alleviate the matter.

Motivated by the complexity of the issue, consensus exists on the need to invest on testing strategies, in particular for the case of analogue, sensor and mixed-signal scenarios (the case of a significant number of WMT systems), driven by the cost that testing represents on product development and its influence in time to market. Joint industry and academia projects, funded by the international consortiums, such as TOETS - "Towards One European Test Standard" (TOETS), ELESIS (ENIAC, 2013), and DIAMOND (CORDIS, 2010) - "Diagnosis, error-modelling and correction for reliable systems design", are testament to the efforts that have been made in the area.

# 1.2 Objectives

The present doctoral work focused on the design of a measurement/testing framework that responds to the present and evolving needs of sensor based systems --- an in-situ access mechanism, which provides resource management and synchronization, while considering multi-element accessibility named SCPS (from Setup, Capture, Process and Scan). Fault diagnosis represents a driving motivation of the SCPS framework, providing flexibility for strategies that include fault detection, fault localization and/or fault prediction. That said, the main target testing scenarios considered were sensor degradation and threshold based fault detection schemes; while considering sensors inter-dependence setups. Sensors inter-dependence refers to settings where sensor characterization depends on multiple sensor instances (e.g. the case of electrode pairs for biosignals measurements) or multi-element measurement associations (e.g. context determination through multiple sensor readings combination).

Secondary objectives include a proof-of-concept implementation of the before mentioned framework and a series of experiments focused on wearable monitoring technology familiarization, sensor characterization and protocol development in order to ascertain proper methodological procedures and approaches, such as:

- Wearable monitoring technology research and familiarization, including design and implementation of prototype system for rehabilitation scenarios, patient data acquisition, and data analysis.

- In-vitro and in-vivo electrode-skin impedance characterization experiments with fault monitoring considerations, with corresponding SCPS framework setup formulation and verification.

- Force sensing resistor characterization under controlled pressure with fault monitoring considerations, with corresponding SCPS framework setup formulation and verification.

## 1.3 Thesis contributions

In reference to the previously stated, there exists a need to address the current gaps in sensor testing within wearable monitoring technology, which have led to the research and development of the present thesis. The particularity of wearable monitoring technology adds complexity to *in-situ* sensor testing, thus complicating data reliability and comparability. Two underlined issues serve as motivation: accessibility and addressability.

Accessibility is a well-known issue of testing in general. Access to specific locations within a board, IC, SoC, SiP, or in this case WMT (which can be a mix of all the previously mentioned with multiple instances), can present a challenge. When considering in-situ multi-sensor normal operation scenarios, the issue of access becomes also an issue of mode operation and local resource scheduling. Under such scenario not only mechanisms must exist for routing the corresponding modules in the proper setup (connecting a test instrument to the target), also a methodology for the participating components to synchronize their actions (using multiple operation modes). For instance, when considering an analogue bus shared by multiple sensors (an array or heterogeneous combination), it becomes necessary to schedule the operations as to avoid unwanted connections to occur (and even avoid damaging consequences). Additionally, a holistic approach to sensor testing might be required in order to address physical system state considerations as to determine expected sensor reference/response relation. Parameters such as temperature, orientation, and event detection, could proof necessary as to establish if a test or measurement should proceed a normal sensor response capture operation (e.g., the temperature might vary the transconductance of a particular sensor, then a synchronized reading from a temperature measuring sensor would provide a way to establish the proper response specifications). Consequently, addressability of the involved elements is also an issue.

Current standards address such issues by compartmentalizing the actions of the involved modules (such as IEEE STD. 1687 through communication to the test data registers, TDR or 1500 wrapper strategy) or controlling the actions of all reachable elements (such as 1149.1 and 1149.4) through boundary scan sequences. However, the message generation complexity would hard press an *in-situ* controller; as it stands, 1149.1 test sequence generation are constructed with the boundary scan description language (BSDL) support, and one would seldom expect such capability to be present on automatic local resources. Additionally, the resulting response transport of multiple elements may well be required for decision making or in order to apply adaptive testing strategies, regardless of the specific approach: functional or structural, BIST or DfT, on-line or off-line test mode. Thus, a framework that simplifies communication and considers multiple levels of addressability (unicast, multi-cast and broadcast) presents itself more pliable to WMT scenarios.

The present work aimed to develop an integrated system design for testability data transport mechanism that addresses setups with heterogeneous sensor types and varying testing approaches, while considering test instruments (ATE independent) scenarios. The

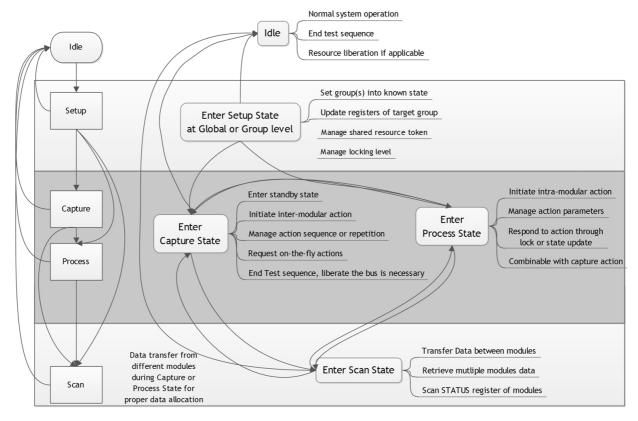

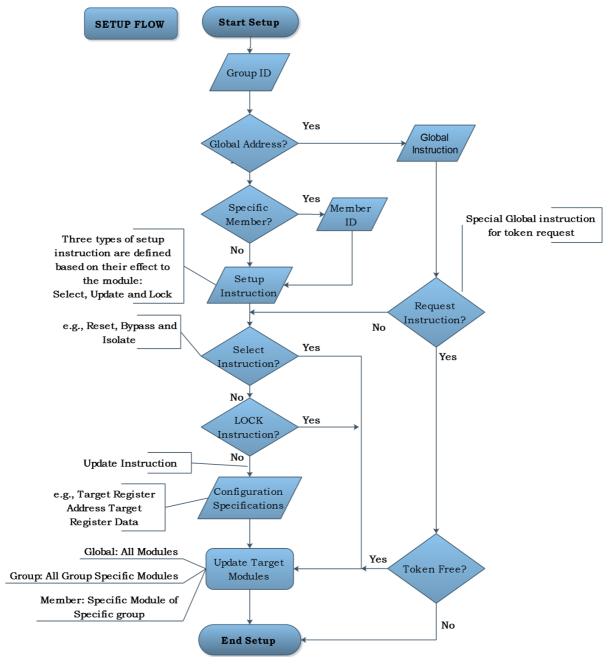

structure was organized around a four stage approach, reflective of its inspiration on proven 1149 standards. An overview of the stages follows:

- **Setup**: intended for initialization of settings for all stages prior to testing/calibration execution or for modification/adaptation to changing scenarios. Considered actions include, e.g., signal/pattern preloading, sampling settings, grouping of components, and BIST handling procedure.

- *Capture*: reminiscent of the EXTEST instruction, this stage manages the signal/pattern loading/generation, data collection and BIST activation.

- *Process:* intended for data processing and allocation on decision making registers. This stage seeks to manage the comparison of collected data through updates of registers that can be used to follow sensor history, global reference upkeep or specific reference comparison. Localized algorithm/heuristics such as least mean square strategies, Kalman filters, Markov's chains, etc., can be activated and processed at this stage.

- **Scan**: intended for data and instruction distribution. Possibilities of interfacing with external elements for setup and data gathering modes are being considered.

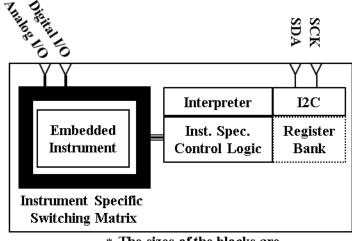

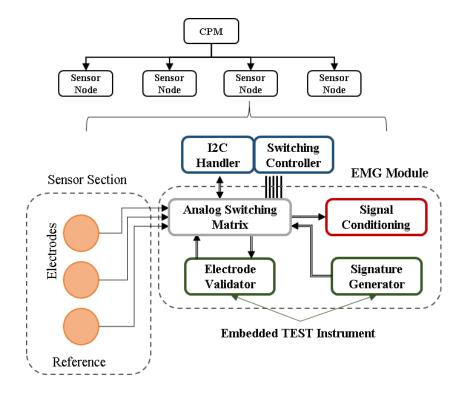

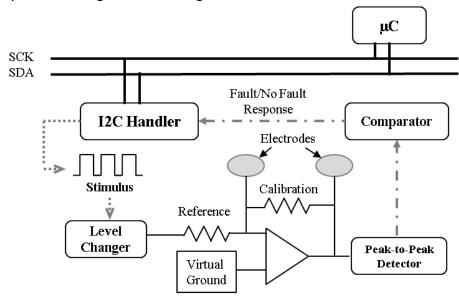

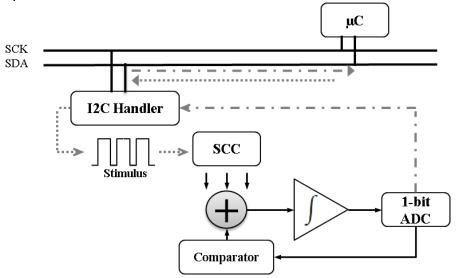

The SCPS modules (as they will be referred from now on) themselves are subdivided in four sections: I2C interpreter, SCPS interpreter, SCPS registers, and SCPS handler. The structure provides implementation flexibility, while permitting compatibility with numerous commercial sensors through the use of I2C as the communication bus. The method also permits the inclusion of these sensors together with test instruments (I2C compatible) within a testing/calibration strategies, by expanding their functionality; consequently offering a structured mixed-signal test infrastructure.

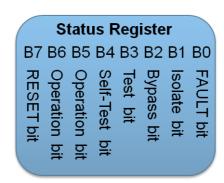

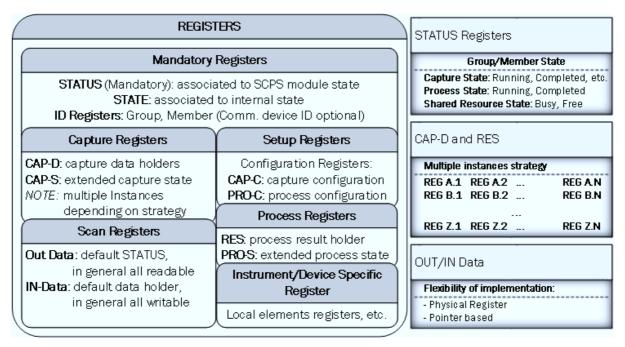

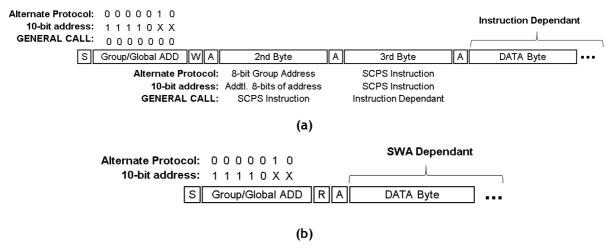

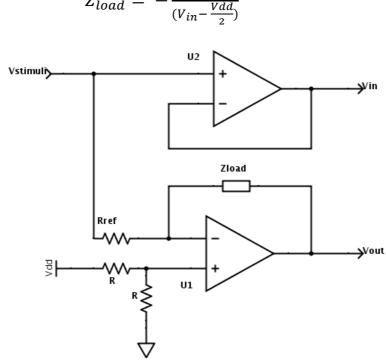

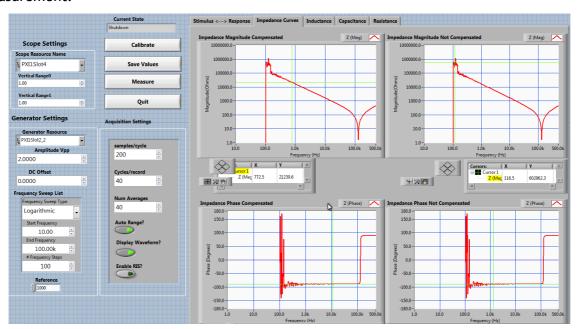

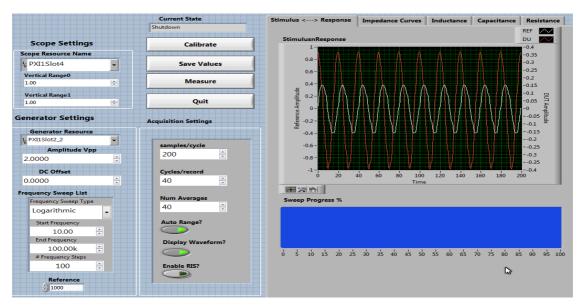

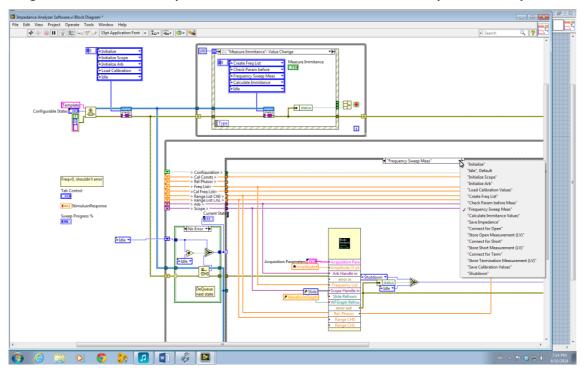

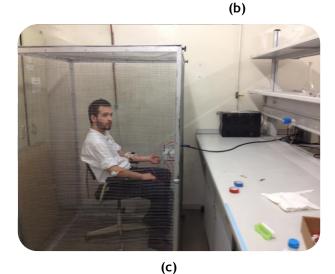

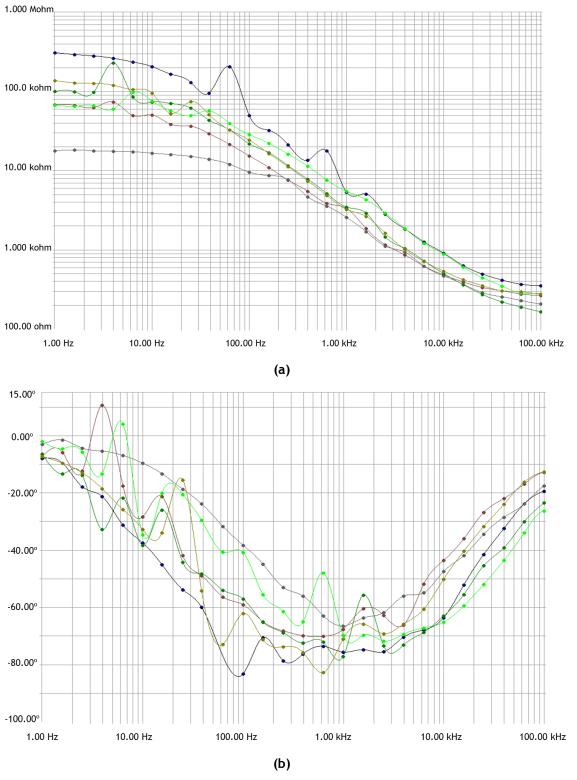

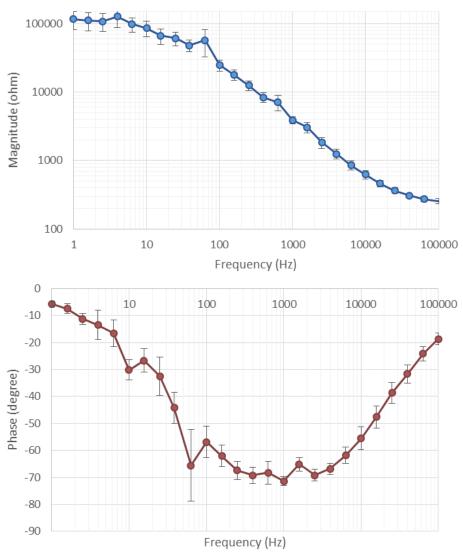

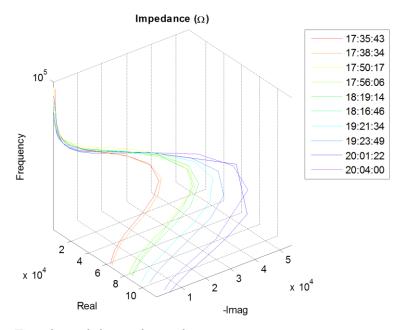

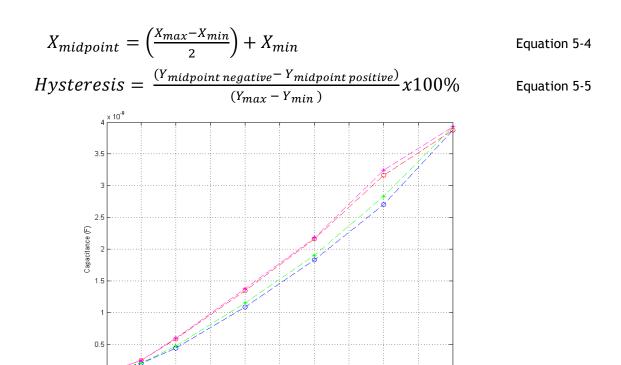

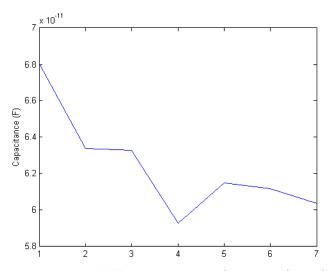

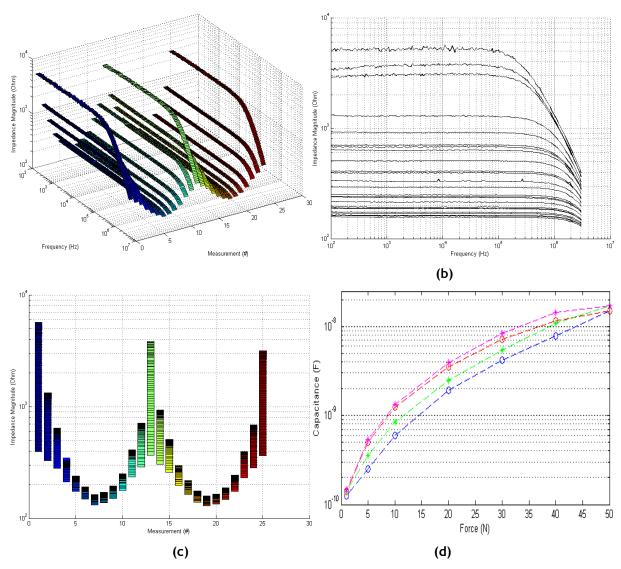

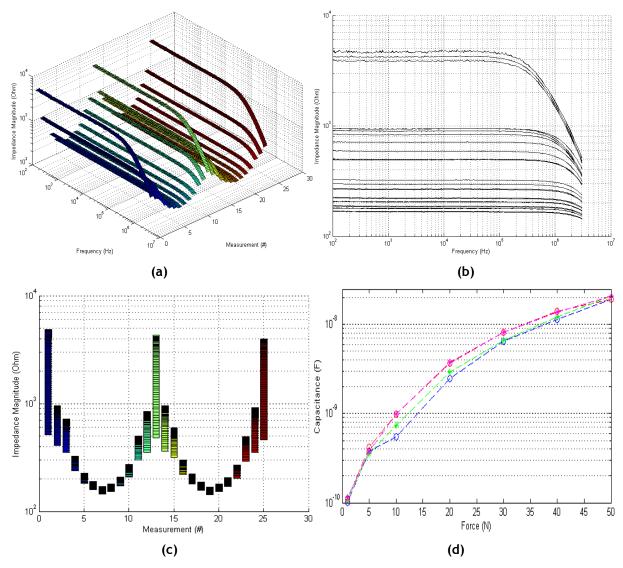

Multi-level addressability is achieved through the SCPS interpreter, considering a group approach mechanism that related multiple modules with a shared 10-bit address. An instruction set, managed internally through registers, flags and associative pointers, permits the synchronization of events, while allowing the sharing of common resources (such as an analogue bus) by token request through broadcast instructions. Although I2C is mostly a master-slave centric protocol ("general call" instructions are also part of the I2C protocol, however seldom utilized), multiple level addressability is not excluded and thus achievable with care in sequencing. Some SCPS introduced capabilities include slave-to-slave data transfer, on-the-fly action setup, and reduced instruction incremental action sequence activation, to name a few. All SCPS based I2C sequences remain transparent to non-addressed I2C elements, preserving I2C compliance. A special case usage of the I2C bus as a test stimuli/response transport was considered for digital stimuli/response utilized for testing analogue elements, such as the bioamplifier conditioning circuit and associated electrodes for the ProLIMB project system; thus, demonstrating the expandability of the SCPS module approach to particular resource re-usage strategies.