# Circuit Design, Architecture and CAD for RRAM-based FPGAs

### THÈSE N° 8084 (2017)

PRÉSENTÉE LE 24 NOVEMBRE 2017

À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS

LABORATOIRE DES SYSTÈMES INTÉGRÉS (IC/STI)

PROGRAMME DOCTORAL EN INFORMATIQUE ET COMMUNICATIONS

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

### PAR

### Xifan TANG

acceptée sur proposition du jury:

Prof. A. P. Burg, président du jury

Prof. G. De Micheli, Dr P.-E. J. M. Gaillardon, directeurs de thèse

Prof. M. Huebner, rapporteur

Dr J. Ryckaert, rapporteur

Prof. P. Ienne, rapporteur

We're paratroopers, Lieutenant.

We're supposed to be surrounded.

— Richard Winters

To my parents and grandparents...

### **Acknowledgements**

It is an amazing experience to spend six years in EPFL pursuing my master and PhD degrees. It is my great honor to have Prof. Giovanni De Micheli and Prof. Pierre-Emmanuel Gaillardon supervising my doctoral researches. Without their insights and tremendous support on both technical works and scientific writings, this work may not be possible. Their serious attitudes on scientific researches drive me to improve my works to the most. In addition, their sincere advices on personal development also inspire me greatly.

I am also grateful to my scientific collaborators: Prof. Paolo Ienne, Dr. Mathias Soeken, Prof. Zhufei Chu, Prof. Vasilis F. Pavlidis, Dr. Jian Zhang, Dr. Hu Xu, Edouard Giacomin, Kim Gain, Dr. Grace Zgheib, Dr. Ana Petkovska and Maxime Thammasack for their advices and important contributions to technical work. In particular, I really appreciate the technical contributions from Prof. Zhufei Chu, Dr. Jian Zhang and Edouard Giacomin. Their works indeed have added remarkable value to my research outcomes.

I should also express my deepest appreciation to Prof. Lingli Wang, who showed me the world of FPGA and taught me good habits at the beginning of my academic career. His encouragement solids my motivation in pursuing a PhD degree.

I would like to express my appreciation to my colleagues in Integrated Systems Laboratory, especially Mme. Christina Govoni for helping me with all the administrative work. I should also express my appreciation to IT manager, Rodolphe Buret, for his hard work in maintaining powerful computers and servers. I thank Dr. Jian Zhang, Prof. Zhufei Chu and Dr. Hu Xu for the collaboration work broadening my vision and knowledge. I am glad to have Winston Jason Haaswijk and Eleonora Testa as my office mate, for sharing happiness and sadness during work hours.

I would like to thank my family: my mother Weiqian Tang, my father Jianhua Zhang, my grandparents Yongming Tang and Jinzhu Chen for supporting me unconditionally all the time. It is their spiritually supports that give me the infinite courage and determination to crash any difficulties during my PhD.

Last but not least, I would like to thank Dr. Jian Zhang, Dr. Hao Zhuang, Dr. Tian Guo, Bin Jin, Yujie Wu, Jun Ma, Dr. Hezhi Zhang, Dechao Sun and all of my friends, who let me enjoy the life in Switzerland and the happy time we spent together.

Lausanne, August 2017

Xifan Tang

### **Abstract**

Field Programmable Gate Arrays (FPGAs) have been indispensable components of embedded systems and datacenter infrastructures. However, energy efficiency of FPGAs has become a hard barrier preventing their expansion to more application contexts, due to two physical limitations: (1) The massive usage of routing multiplexers causes delay and power overheads as compared to ASICs. To reduce their power consumption, FPGAs have to operate at low supply voltage but sacrifice performance because the transistors drive degrade when working voltage decreases. (2) Using volatile memory technology forces FPGAs to lose configurations when powered off and to be reconfigured at each power on.

Resistive Random Access Memories (RRAMs) have strong potentials in overcoming the physical limitations of conventional FPGAs. First of all, RRAMs grant FPGAs non-volatility, enabling FPGAs to be "Normally powered off, Instantly powered on". Second, by combining functionality of memory and pass-gate logic in one unique device, RRAMs can greatly reduce area and delay of routing elements. Third, when RRAMs are embedded into datpaths, the performance of circuits can be independent from their working voltage, beyond the limitations of CMOS circuits. However, researches and development of RRAM-based FPGAs are in their infancy. Most of area and performance predictions were achieved without solid circuit-level simulations and sophisticated Computer Aided Design (CAD) tools, causing the predicted improvements to be less convincing.

In this thesis, we present high-performance and low-power RRAM-based FPGAs from transistor-level circuit designs to architecture-level optimizations and CAD tools, using theoretical analysis, industrial electrical simulators and novel CAD tools. We believe that this is the first systematic study in the field, covering:

From a circuit design perspective, we propose efficient RRAM-based programming circuits and routing multiplexers through both theoretical analysis and electrical simulations. The proposed 4T(ransitor)1R(RAM) programming structure demonstrates significant improvements in programming current, when compared to most popular 2T1R programming structure. 4T1R-based routing multiplexer designs are proposed by considering various physical design parasitics, such as intrinsic capacitance of RRAMs and wells doping organization. The proposed 4T1R-based multiplexers outperform best CMOS implementations significantly in area, delay and power at both nominal and near- $V_t$  regime.

**From a CAD perspective**, we develop a generic FPGA architecture exploration tool, FPGA-SPICE, modeling a full FPGA fabric with SPICE and Verilog netlists. FPGA-SPICE provides different levels of testbenches and techniques to split large SPICE netlists, in order to obtain

#### **Abstract**

better trade-off between simulation time and accuracy. FPGA-SPICE can capture area and power characteristics of SRAM-based and RRAM-based FPGAs more accurately than the currently best analytical models.

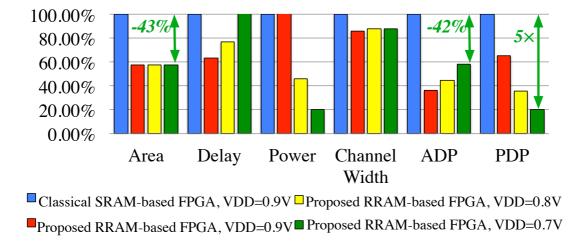

From an architecture perspective, we propose architecture-level optimizations for RRAM-based FPGAs and quantify their minimum requirements for RRAM devices. Compared to the best SRAM-based FPGAs, an optimized RRAM-based FPGA architecture brings significant reduction in area, delay and power respectively. In particular, RRAM-based FPGAs operating in the near- $V_t$  regime demonstrate a  $5\times$  power improvement without delay overhead as compared to optimized SRAM-based FPGA operating at nominal working voltage.

Key words: Resistive Memory, Field Programmable Gate Array, Circuit Design, Programming Structure, Multiplexer, Physical Design, Computer-Aided Design

### Résumé

Les Réseaux de Portes Programmables in Situ (*Field Programmable Gate Arrays* - FPGA) sont des composants indispensables aux systèmes embarqués et aux infrastructures de systèmes de données. Cependant, l'efficacité énergétique des FPGA est devenue une barrière empêchant leur expansion à de nouveaux contextes d'applications, du fait de deux limitations physiques : (1) L'utilisation massive de multiplexeurs de routage engendre une augmentation des délais et de la consommation énergétique par rapport aux ASICs. Afin de réduire leur consommation d'énergie, les FPGAs peuvent fonctionner à faible tension d'alimentation mais cela engendre une perte de performances car les transistors se dégradent lorsque la tension de fonctionnement diminue. (2) L'utilisation d'une technologie de mémoire volatile oblige les FPGA à reconfigurer leurs informations de configurations à chaque mise sous tension.

Les mémoires résistives (*Resistive Random-Access Memory* - RRAM) ont de forts potentiels pour surmonter les limitations physiques des FPGA conventionnels. Premièrement, les RRAMs permettent aux FPGA d'être non-volatiles, leur permettant ainsi de ne pas perdre leur configuration lors de la mise hors tension et d'être instantanément opérationnels lors de la mise sous tension. Deuxièmement, en combinant la fonctionnalité de la mémoire et de la logique des portes de transmission dans un seul et même composant, les RRAM peuvent considérablement réduire l'aire et le délai des éléments de routage. Troisièmement, lorsque les RRAM sont intégrées dans les chemins d'accès, les performances des circuits peuvent devenir indépendante de la tension de fonctionnement, bien au-delà des limites des circuits CMOS. Cependant, les recherches et le développement des FPGA basés sur des RRAMs en sont à leurs débuts. La plupart des prédictions en termes d'aire et de délai ont été réalisées sans simulations approfondies au niveau du circuit et sans outil de Conception *Assistée par Ordinateur* (CAO), rendant incertaines les prédictions de performances.

Dans cette thèse, nous proposons des FPGA haute performance et faible consommation, basés sur RRAMs au travers de l'étude des circuits au niveau du transistor jusqu'aux optimisations architecturales et la création d'outils CAO spécifiques, et en utilisant l'analyse théorique, les simulateurs électriques industriels et les nouveaux outils de CAO. Nous sommes convaincus que c'est la première étude du domaine couvrant :

**Du point de vue de la conception de circuits**, nous proposons des circuits de programmation efficaces basés sur des RRAMs et des multiplexeurs de routage évalués à la fois à travers des analyses théoriques et des simulations électriques. La structure de programmation 4T(ransitor) 1R(RAM) proposée démontre des améliorations significatives en termes de courant de programmation, par rapport à la structure de programmation 2T1R la plus populaire.

#### **Abstract**

Des multiplexeurs de routage basés sur les structures 4T1R sont proposés en considérant divers facteurs parasites tels que la capacité intrinsèque des RRAMs et l'arrangement des zones de dopage substrat. Les multiplexeurs basés sur les 4T1R surpassent les implémentations CMOS de manière significative en termes d'aire, délai et de consommation énergétique, en régime nominal et en régime proche de la tension de seuil.

**Du point de vue de la CAO**, nous développons un outil générique d'exploration d'architectures de FPGAs, FPGA-SPICE, capable d'exporter le modèle SPICE ou verilog d'un FPGA complet. FPGA-SPICE fournit différents niveaux de banc d'essais et des techniques pour diviser les larges représentations SPICE afin d'obtenir les meilleurs compromis en termes de temps de simulation et précision. FPGA-SPICE peut capturer les caractéristiques des FPGA basées sur SRAM et RRAM en termes d'aire et de consommation plus précisément que les meilleurs modèles analytiques actuels.

**Du point de vue de l'architecture**, nous proposons des optimisations au niveau de l'architecture pour les FPGA basés sur des RRAMs et quantifions les spécifications minimales pour les RRAMs. Par rapport aux meilleurs FPGAs basés sur des SRAM, une architecture FPGA optimisée basée sur des RRAMs apporte de grandes améliorations en termes d'aire, de délai et de consommation. En particulier, les FPGAs basées sur des RRAMs fonctionnant en régime proche de la tension de seuil démontrent une consommation énergétique 5 fois inferieur sans délais supplémentaires par rapport aux FPGAs optimisés utilisant des SRAMs et fonctionnant à la tension de travail nominale.

Mots clefs : Mémoire Résistive, Réseaux de Portes Programmables in Situ, Conception de Circuits, Structures de Programmation, Multiplexeur, Conception Physique, Conception Assistée par Ordinateur

## Contents

| A  | cknov | wledge  | ments                                                                     | j   |

|----|-------|---------|---------------------------------------------------------------------------|-----|

| Al | ostra | ct (Eng | dish/Français/Deutsch)                                                    | iii |

| Li | st of | figures |                                                                           | xi  |

| Li | st of | tables  |                                                                           | xvi |

| 1  | Intr  | oducti  | ion                                                                       | 1   |

|    | 1.1   | Overv   | riew of RRAMs                                                             | 2   |

|    | 1.2   | Advar   | ntages and Challenges for FPGAs                                           | 4   |

|    | 1.3   | Oppo    | rtunities in RRAM-based FPGAs                                             | 5   |

|    | 1.4   | Contr   | ibutions and Organization                                                 | 6   |

| 2  | Bac   | kgroui  | nd and Previous Works                                                     | 11  |

|    | 2.1   | RRAM    | 1 Technology                                                              | 11  |

|    |       | 2.1.1   | Resistive Characteristics                                                 | 13  |

|    |       | 2.1.2   | Capacitive Modeling                                                       | 15  |

|    |       | 2.1.3   | Trade-off between $R_{LRS}$ and $C_P$                                     | 16  |

|    |       | 2.1.4   | Co-Integration with CMOS Technology and Scaling Trends                    | 16  |

|    |       | 2.1.5   | Process Variations                                                        | 18  |

|    |       | 2.1.6   | Material Engineering for Application Requirements                         | 19  |

|    | 2.2   | Conve   | entional FPGA Architectures                                               | 20  |

|    |       | 2.2.1   | Classical Architectures                                                   | 20  |

|    |       | 2.2.2   | Architectural Enhancements                                                | 25  |

|    |       | 2.2.3   | Circuit Designs in FPGAs                                                  | 30  |

|    |       | 2.2.4   | Memory Technologies for FPGAs                                             | 34  |

|    | 2.3   | Previo  | ous works about RRAM-based Circuit Designs and FPGA Architectures $$ . $$ | 38  |

|    |       | 2.3.1   | Programming Structures                                                    | 38  |

|    |       | 2.3.2   | Non-Volatile Flip-Flop and SRAM                                           | 41  |

|    |       | 2.3.3   | Multiplexer and Crossbar Designs                                          | 41  |

|    |       | 2.3.4   | RRAM-based FPGA Architectures                                             | 43  |

|    | 2.4   | FPGA    | Architecture Exploration Tool and Power Modeling Technique                | 46  |

|    |       | 2.4.1   | FPGA EDA flow                                                             | 46  |

### **Contents**

|    |      | 2.4.2 | Probability-based Power Estimation Techniques        | 47         |

|----|------|-------|------------------------------------------------------|------------|

|    | 2.5  | Sumn  | nary                                                 | 52         |

| 2  | DD 4 | M baa | and Cinemit Designs                                  | <b>5</b> 2 |

|    |      |       | sed Circuit Designs<br>-based Programming Structures | 53         |

| Га |      |       |                                                      | 54         |

|    | 3.1  |       | rimental Methodology                                 | 54<br>54   |

|    | 3.2  | 3.2.1 | ations of 2T1R Programming Structure                 | 54<br>55   |

|    |      |       | I-V Characteristics of 2T1R Structure                | 56         |

|    |      |       |                                                      | 58         |

|    |      |       | Physical Design Difficulties                         | 59         |

|    |      | 3.2.4 |                                                      |            |

|    |      | 3.2.5 | Electrical Simulations                               | 60         |

|    | 2.2  | 3.2.6 | Discussion About Limitations                         | 61         |

|    | 3.3  |       | R Programming Structure                              | 62         |

|    |      | 3.3.1 | 2TG1R Circuit Structure                              | 62         |

|    |      | 3.3.2 | Area Estimation                                      | 63         |

|    |      | 3.3.3 | Electrical Simulations                               | 65         |

|    |      | 3.3.4 | Summary: Advantages and Limitations                  | 66         |

|    | 3.4  |       | Programming Structure                                | 67         |

|    |      | 3.4.1 | 4T1R Circuit Structure                               | 68         |

|    |      | 3.4.2 | Theoretical Analysis on I-V Characteristics          | 69         |

|    |      | 3.4.3 | Current Density Boosting Methodologies               | 71         |

|    |      | 3.4.4 | Area Estimation                                      | 73         |

|    |      | 3.4.5 | Benefits of 4T1R structures                          | 74         |

|    |      | 3.4.6 | Summary on the 4T1R programming structures           | 76         |

|    |      | 3.4.7 | Discussion                                           | 77         |

| Pa |      |       | -based Multiplexer Designs                           |            |

|    | 3.5  | Basic | 4T1R-based Multiplexer                               | 80         |

|    |      | 3.5.1 | Multiplexer Structure and Programming Strategy       | 80         |

|    |      | 3.5.2 | Limitations from a Physical Design Perspective       | 82         |

|    | 3.6  | Impro | oved 4T1R-based Multiplexer                          | 83         |

|    |      | 3.6.1 | One-level Multiplexer Structure                      | 83         |

|    |      | 3.6.2 | Physical Design Advantages                           | 85         |

|    |      | 3.6.3 | Two-level and Tree-like multiplexer Structure        | 86         |

|    |      | 3.6.4 | Sharing deep N-Well between multiplexers             | 88         |

|    |      | 3.6.5 | Constraints on the Programming Voltage $V_{prog}$    | 89         |

|    |      | 3.6.6 | Analytical Comparison between 4T1R multiplexers      | 92         |

|    | 3.7  | Optin | nal Physical Design Parameters                       | 93         |

|    |      | 3.7.1 | RC modeling of General 4T1R-based multiplexers       | 93         |

|    |      | 3.7.2 | Physical Position of RRAMs                           | 96         |

|    |      | 3.7.3 | Programming Transistor Sizing Technique              | 97         |

|    | 3.8  | Exper | imental Results                                      | 99         |

|   |      | 3.8.1  | Experimental Methodology                      | 99  |

|---|------|--------|-----------------------------------------------|-----|

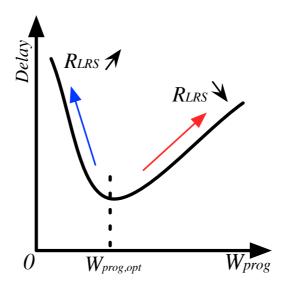

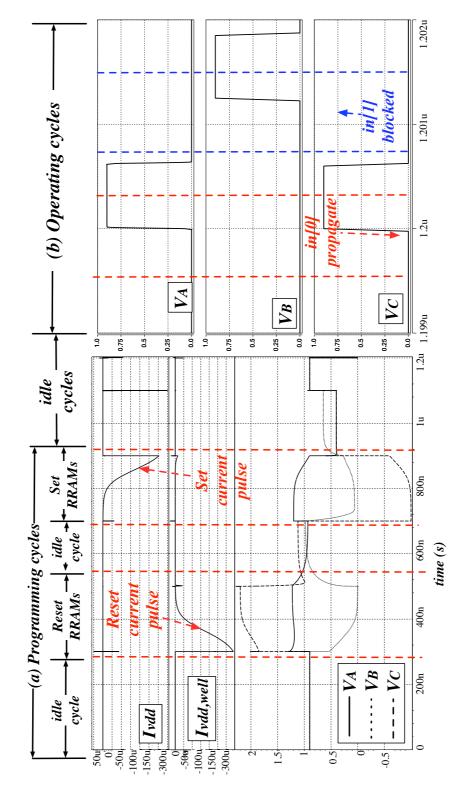

|   |      | 3.8.2  | Transient Analysis                            | 100 |

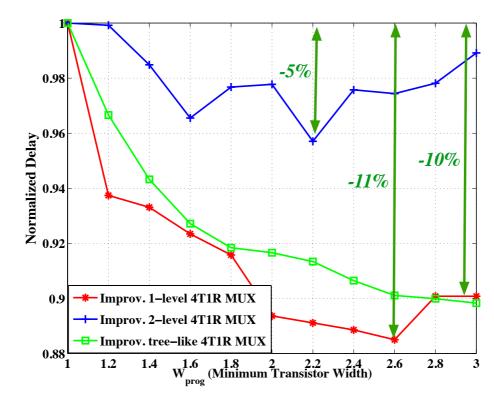

|   |      | 3.8.3  | Best $W_{prog}$ for RRAM-based Multiplexers   | 100 |

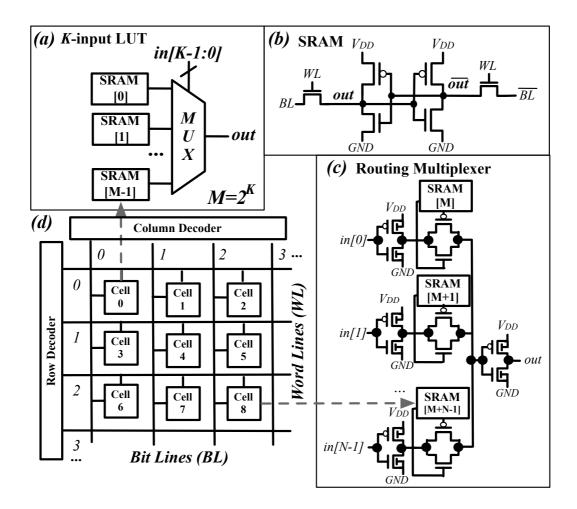

|   |      | 3.8.4  | Optimal RRAM Location                         | 104 |

|   |      | 3.8.5  | Area Comparison                               | 105 |

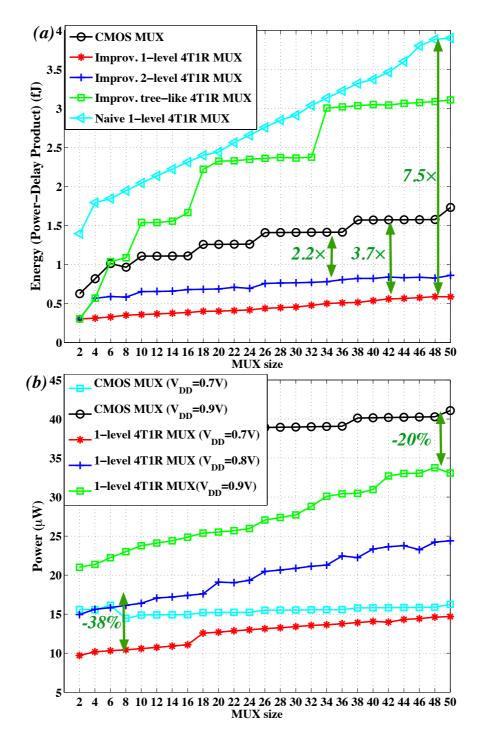

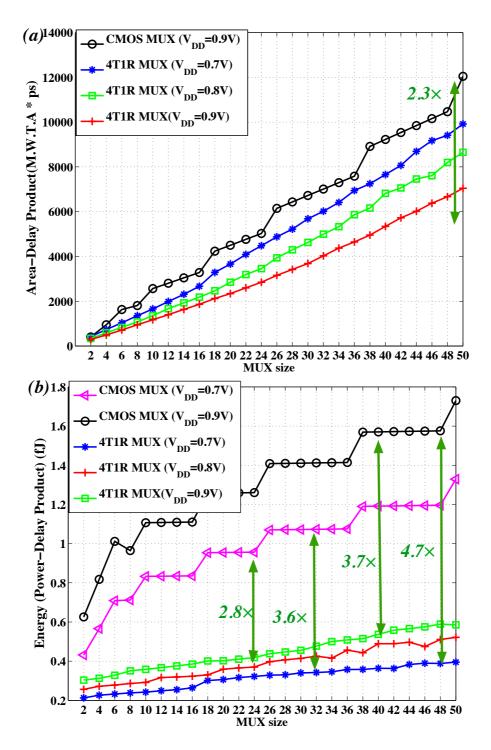

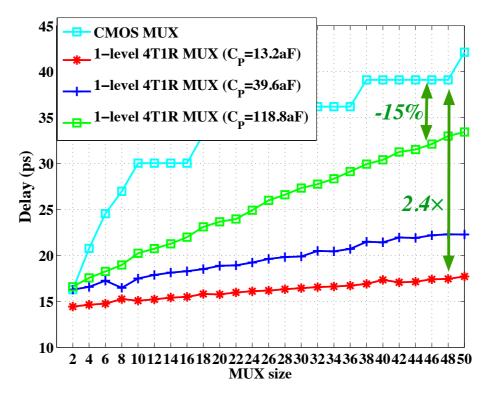

|   |      | 3.8.6  | Delay Improvements                            | 106 |

|   |      | 3.8.7  | Energy and Power Benefits                     | 110 |

|   |      | 3.8.8  | Area-Delay and Power-Delay Products Analysis  | 110 |

|   | 3.9  | Impa   | ct of Process Variations of RRAMs             |     |

|   |      | 3.9.1  | Impact of Variations on $C_P$                 | 111 |

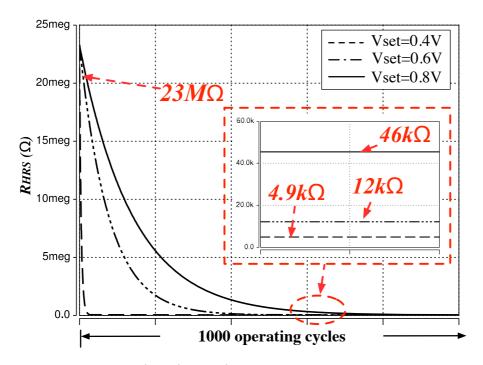

|   |      | 3.9.2  | Impact of Variations on $V_{set}$             |     |

|   |      | 3.9.3  | Impact of Variations on $V_{reset}$           |     |

|   | 3.10 | Sumn   | nary                                          |     |

|   |      |        | ,                                             |     |

| 4 | Sim  | ulatio | n-based Architecture Exploration Tool         | 117 |

|   | 4.1  | Princi | ples                                          | 118 |

|   |      | 4.1.1  | SPICE Modeling                                | 119 |

|   |      | 4.1.2  | Verilog Modeling                              | 119 |

|   | 4.2  | Exten  | ded Architecture Description Language         | 121 |

|   |      | 4.2.1  | Transistor-level Module Declaration           | 121 |

|   |      | 4.2.2  | Physical Structure Modeling                   | 124 |

|   |      | 4.2.3  | Configuration Circuitry                       | 126 |

|   | 4.3  | Transi | istor-level Circuit Netlist Generation        | 126 |

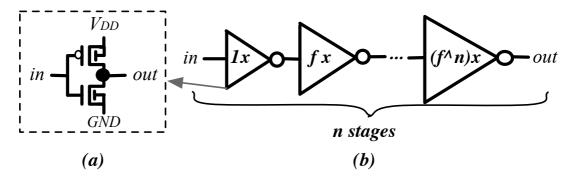

|   |      | 4.3.1  | Inverters/Buffers                             | 127 |

|   |      | 4.3.2  | Pass-gate Logic                               | 128 |

|   |      | 4.3.3  | SRAM                                          | 128 |

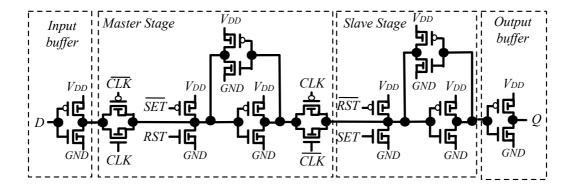

|   |      | 4.3.4  | Scan-chain Flip-Flop                          | 129 |

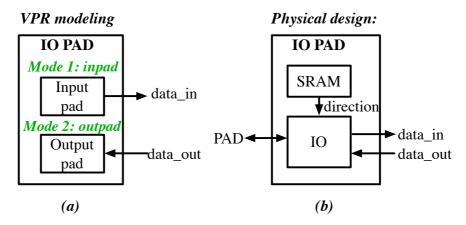

|   |      | 4.3.5  | IO Circuits                                   | 130 |

|   |      | 4.3.6  | Multiplexers                                  | 130 |

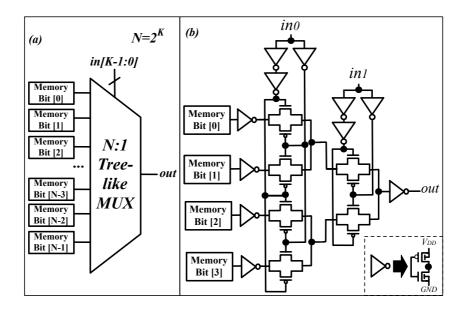

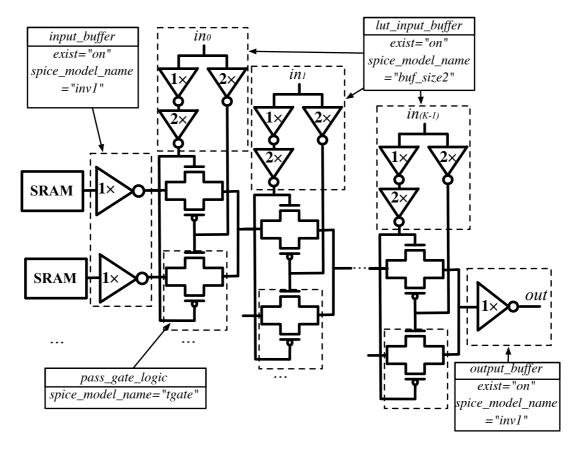

|   |      | 4.3.7  | Look-Up Tables                                |     |

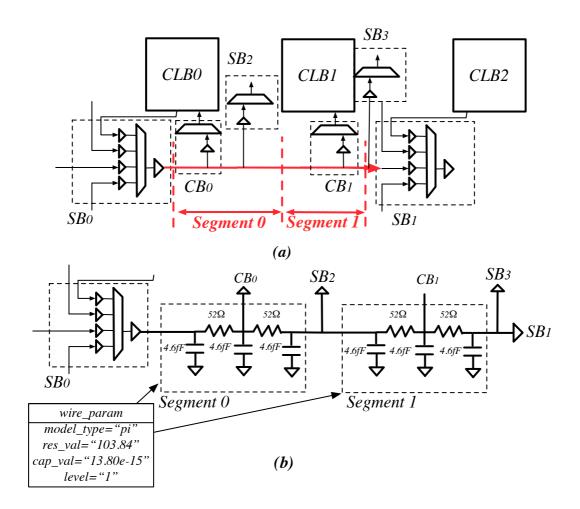

|   |      | 4.3.8  | Channel Wire                                  | 135 |

|   | 4.4  |        | t Partitioning Strategies                     |     |

|   |      | 4.4.1  | Voltage Stimuli and Loads Extraction          | 138 |

|   |      | 4.4.2  | Parasitic Activity Estimation                 |     |

|   | 4.5  | Exper  | imental Results                               |     |

|   |      | 4.5.1  | Methodology                                   |     |

|   |      | 4.5.2  | Functional Verification                       |     |

|   |      | 4.5.3  | Studies on Runtime, Memory Usage and Accuracy |     |

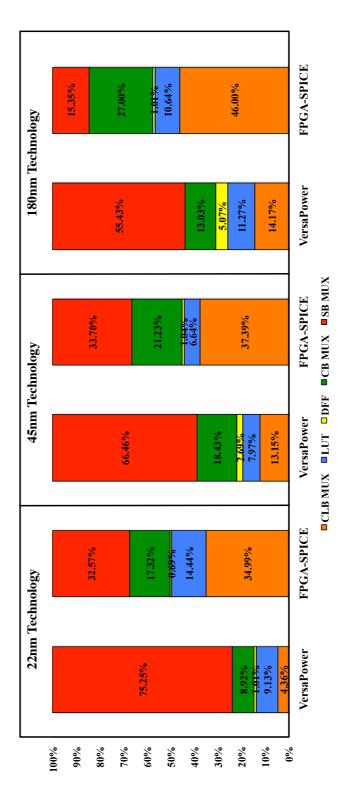

|   |      | 4.5.4  | Power Breakdowns                              |     |

|   |      | 4.5.5  | Accuracy Examination vs. VersaPower           |     |

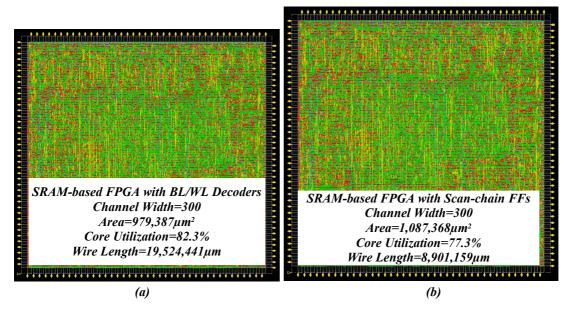

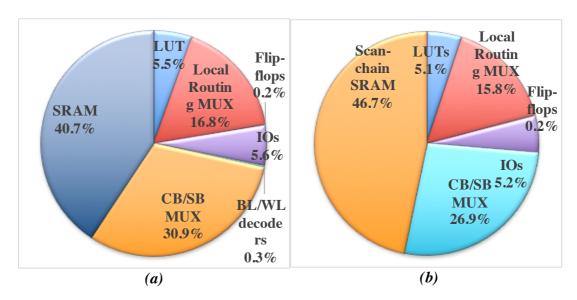

|   |      | 4.5.6  | Area Characteristics of SRAM-based FPGAs      |     |

|   | 16   | Sumn   |                                               | 147 |

### **Contents**

| 5  | RRA    | M-bas  | sed FPGA Architectures                   | 149 |

|----|--------|--------|------------------------------------------|-----|

|    | 5.1    | Gener  | ral Vision                               | 150 |

|    |        | 5.1.1  | Choice of Non-volatile Modules           | 150 |

|    |        | 5.1.2  | Configuration Circuits                   | 152 |

|    |        | 5.1.3  | Experimental Methodology                 | 153 |

|    |        | 5.1.4  | Area Characteristics                     | 154 |

|    |        | 5.1.5  | Power Characteristics                    | 157 |

|    |        | 5.1.6  | Overall Performance                      | 164 |

|    | 5.2    | Archi  | tecture-level Optimizations              | 164 |

|    |        | 5.2.1  | Experimental Methodology                 | 165 |

|    |        | 5.2.2  | Unified Connection Block                 | 166 |

|    |        | 5.2.3  | Increase Capacity of SB MUXes            | 172 |

|    |        | 5.2.4  | Smaller Best Length Wire < 4             | 174 |

|    |        | 5.2.5  | RRAM-based FPGAs vs. SRAM-based FPGAs    | 177 |

|    | 5.3    | Sumn   | nary                                     | 177 |

| 6  | Con    | clusio | n and Future Work                        | 181 |

|    | 6.1    | Sumn   | nary of Contributions                    | 181 |

|    | 6.2    | Futur  | e Work                                   | 185 |

| A  | An a   | append | lix                                      | 187 |

|    | A.1    | Exam   | ples of FPGA-SPICE Architecture Modeling | 187 |

| Bi | bliog  | graphy |                                          | 214 |

| Cı | ırricı | ulum V | Vitae                                    | 215 |

# List of Figures

| 1.1  | A RRAM Device (a) sandwiched structure and (b) I-V Characteristics: $V_{set}$ and               |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | $I_{set}$ converts part of metal oxide to low-resistance state                                  | 3  |

| 1.2  | Power consumption of (a) a SRAM-based FPGA and (b) a RRAM-based FPGA                            | 5  |

| 1.3  | Use SRAM + transistors or RRAMs to propagate and block datapath signals                         | 6  |

| 2.1  | (a) RRAM in pristine state; (b) RRAM in <i>Low Resistance State</i> (LRS); (c) RRAM in          |    |

|      | High Resistance State (HRS)                                                                     | 12 |

| 2.2  | I-V characteristic of (a) a URS RRAM; (b) a BRS RRAM                                            | 12 |

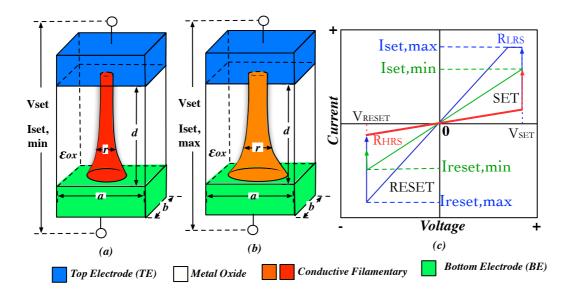

| 2.3  | (a) Size of filaments inside a RRAM achieved by $I_{set,min}$ ; (b) Size of filaments           |    |

|      | inside a RRAM achieved by $I_{set,max}$ ; (c) I-V characteristics of a RRAM with Bipolar        |    |

|      | Resistive Switching                                                                             | 14 |

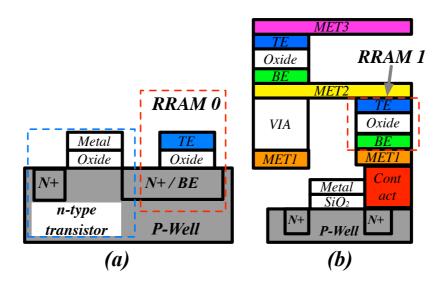

| 2.4  | Alternative integrations: (a) Natively combine with source/drain or gate of tran-               |    |

|      | sistors; (b) Locate between metal layers.                                                       | 17 |

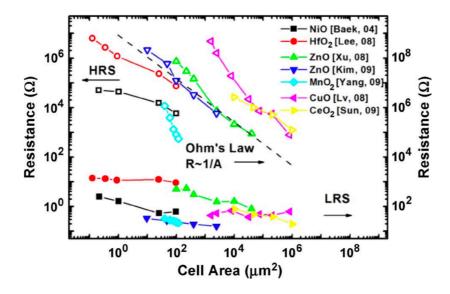

| 2.5  | Impact of cell area on $R_{HRS}$ and $R_{LRS}$ [Courtesy by [1]]                                | 18 |

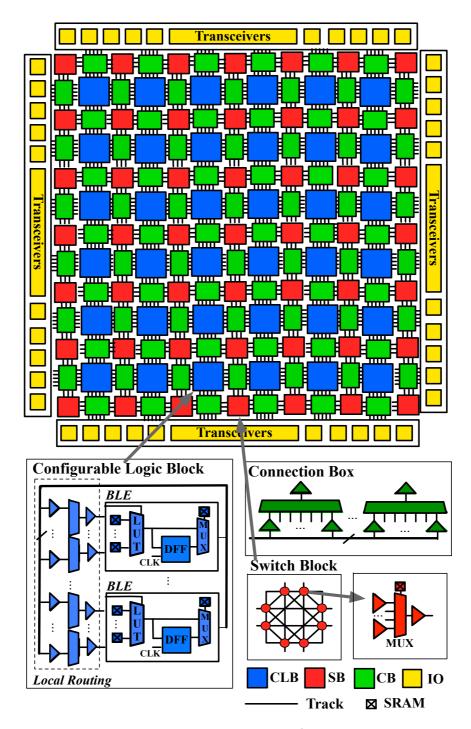

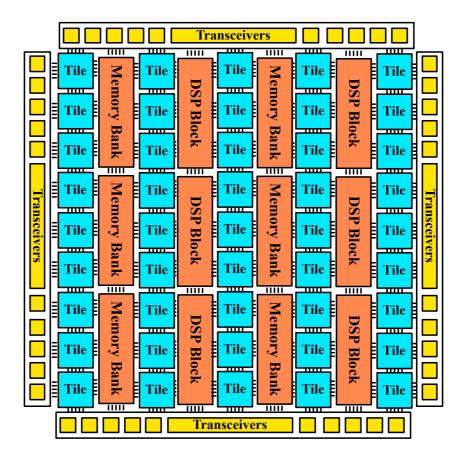

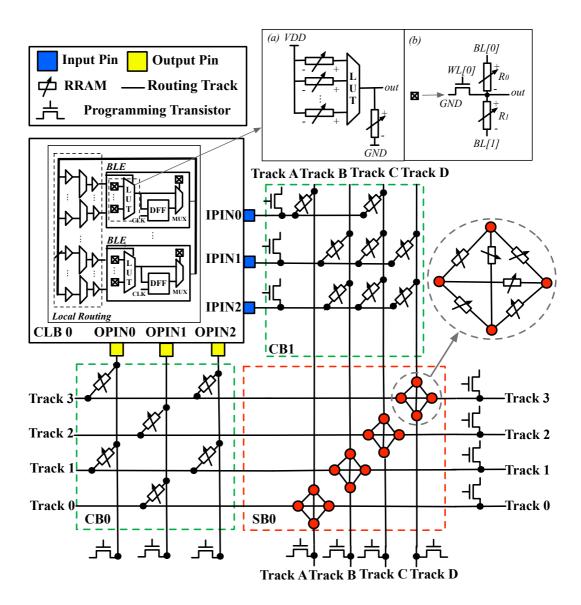

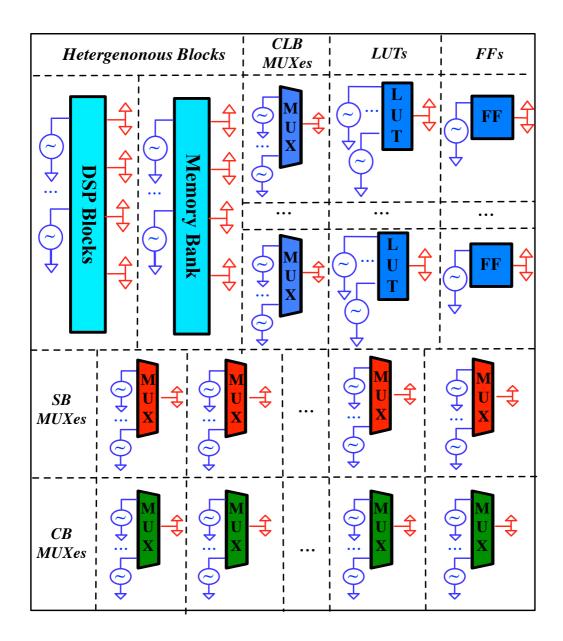

| 2.6  | Generic FPGA Architecture                                                                       | 21 |

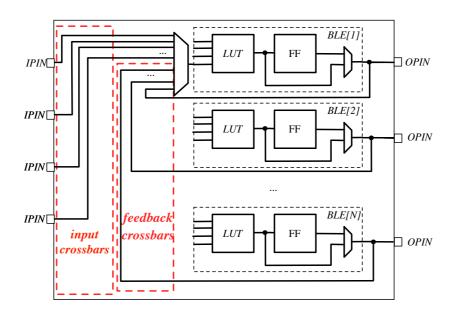

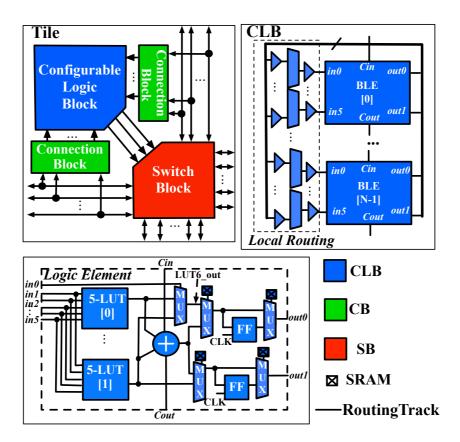

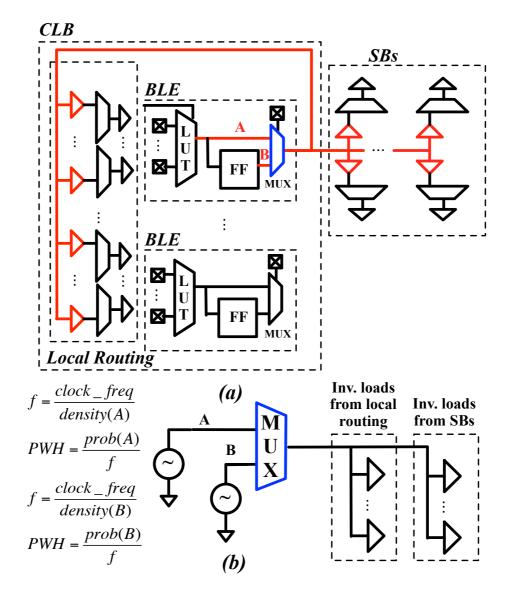

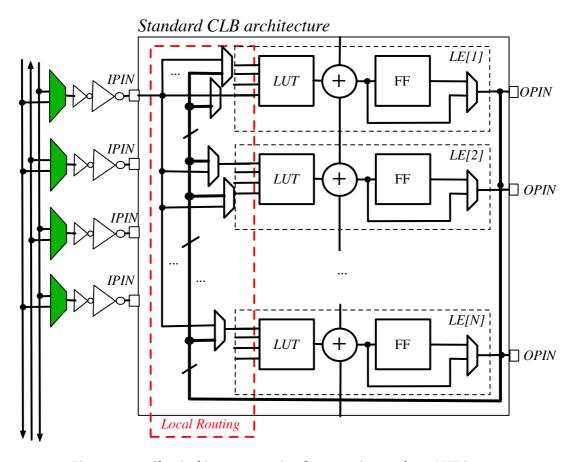

| 2.7  | Detailed CLB Architecture                                                                       | 22 |

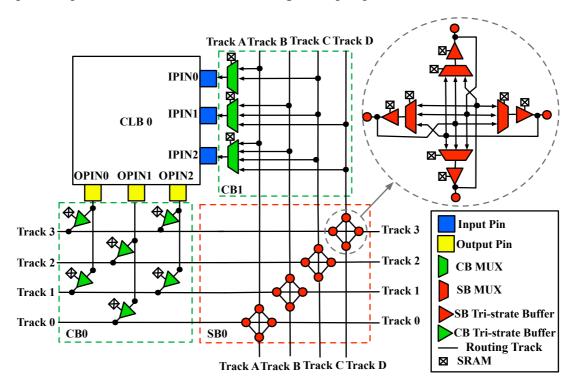

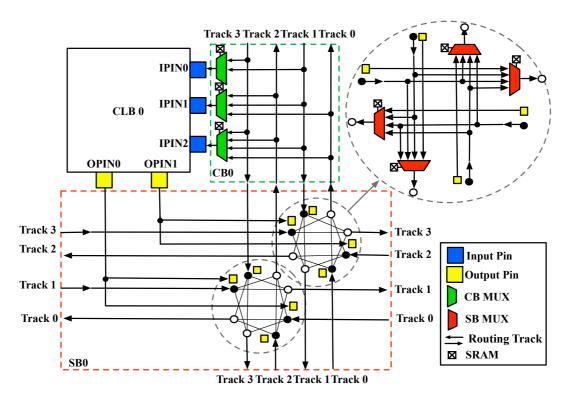

| 2.8  | Bi-directional global routing architecture                                                      | 23 |

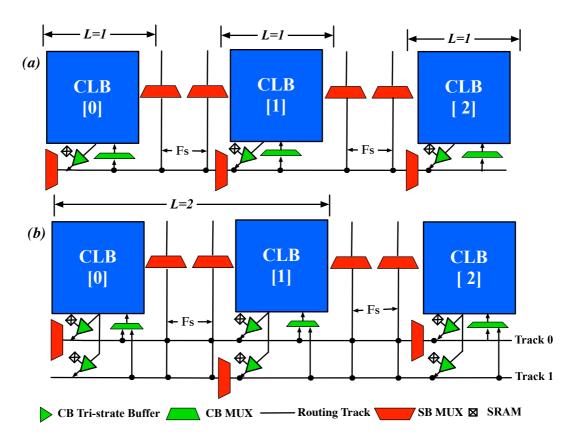

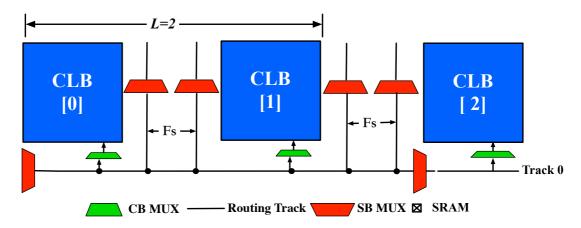

| 2.9  | Bi-directional global routing architecture featured by (a) $L=1$ ; (b) $L=2$                    | 25 |

| 2.10 | Tile-based FPGA Architecture.                                                                   | 27 |

| 2.11 | Tile and enhanced CLB architecture                                                              | 28 |

| 2.12 | Uni-directional global routing architecture                                                     | 29 |

| 2.13 | A uni-directional routing track featured by $L = 2$                                             | 29 |

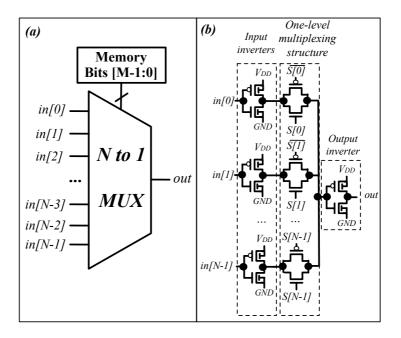

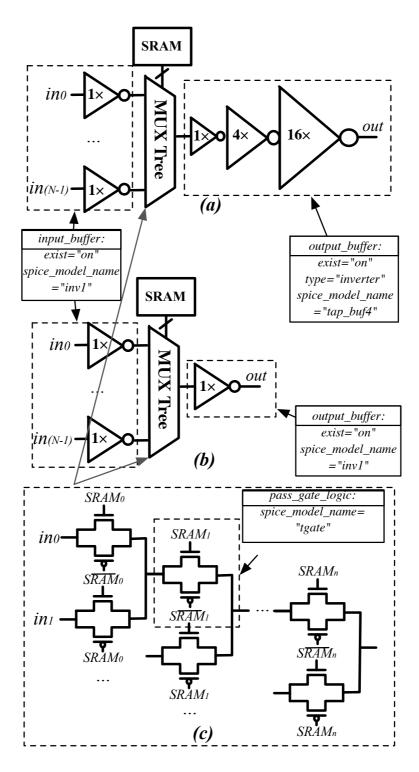

| 2.14 | (a) Symbol of a $N$ -input routing multiplexer; (b) One-level implementation [2, 3].            | 31 |

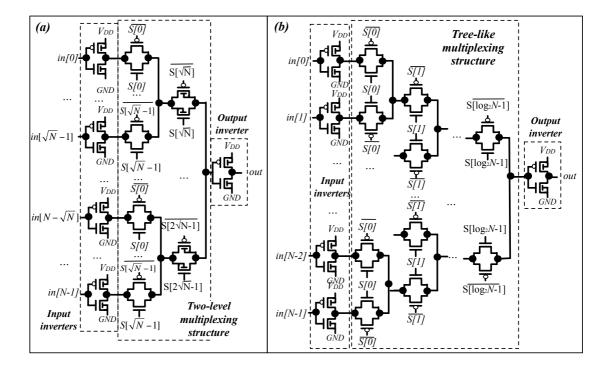

| 2.15 | Alternative routing multiplexer design topologies: (a) two-level; (b) tree-like $[2,3]$ .       | 31 |

| 2.16 | Look-Up Table (LUT): (a) principle internal structure; (b) transistor-level design              |    |

|      | of a 2-input LUT [4].                                                                           | 33 |

| 2.17 | Transistor-level design of a master-slave <i>D</i> -type <i>Flip-Flop</i> with asynchronous set |    |

|      | and reset [4]                                                                                   | 34 |

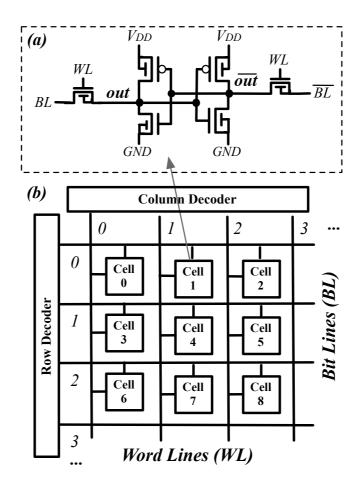

| 2.18 | (a) 6-Transistor SRAM design [4]; (b) Configuration circuits for SRAM arrays                    | 35 |

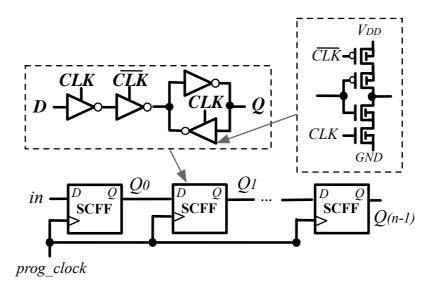

| 2.19 | Scan-Chain Flip-Flop (SCFF) design and associated configuration circuits [5, 6]                 | 36 |

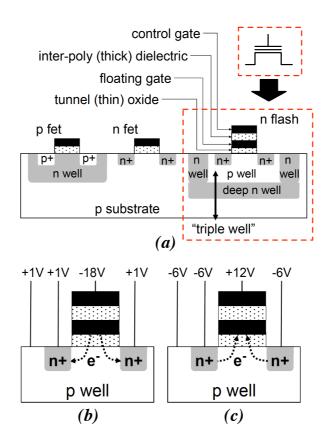

| 2.20 | (a) Embedded Flash Process (Courtesy by [7]); (b) Erasing operation of a Flash                  |    |

|      | transistor (Courtesy by [7]); (c) Programming operation of a Flash transistor                   |    |

|      | (Courtesy by [7])                                                                               | 37 |

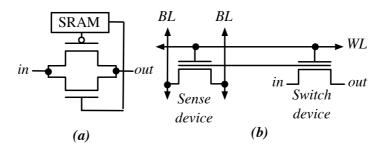

| 2.21 | (a) A transmission gate controlled by a SRAM; (b) Equivalent Flash-based pro-                                    |    |

|------|------------------------------------------------------------------------------------------------------------------|----|

|      | grammable switch. (Courtesy by [7])                                                                              | 37 |

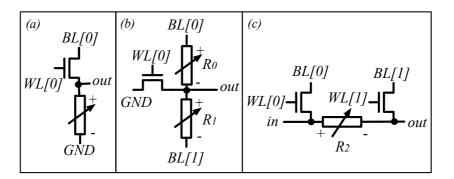

| 2.22 | Three most commonly used programming structures: (a) 1T(ransistor)1R(RAM),                                       |    |

|      | (b) 1T(ransistor)2R(RAM) and (c) 2T(ransistor)1R(RAM)                                                            | 39 |

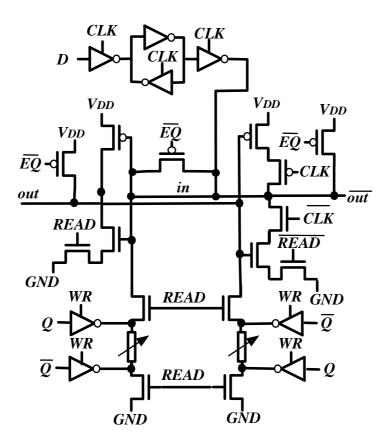

| 2.23 | A non-volatile master-slave Flip-Flop design [5, 6]                                                              | 42 |

| 2.24 | A non-volatile SRAM design [5, 6]                                                                                | 43 |

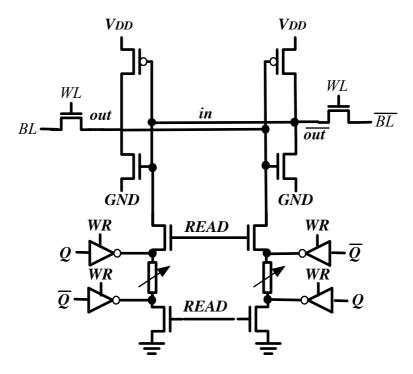

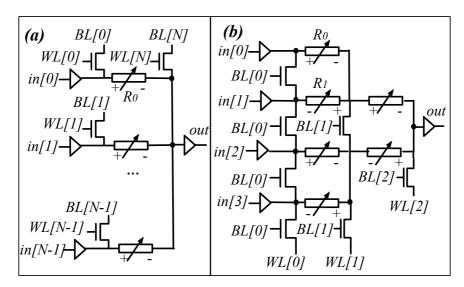

| 2.25 | Early designs of 2T1R-based multiplexers: (a) A $N$ -input one level structure [9];                              |    |

|      | (b) An illustrative example of two-level and tree-like 4:1 structure [10]. $\ldots$                              | 44 |

| 2.26 | Early RRAM-based FPGA architectures (a) LUTs embedded with 2T1R program-                                         |    |

|      | ming structures; (b) SRAMs are replaced by 2T1R programming structures                                           | 45 |

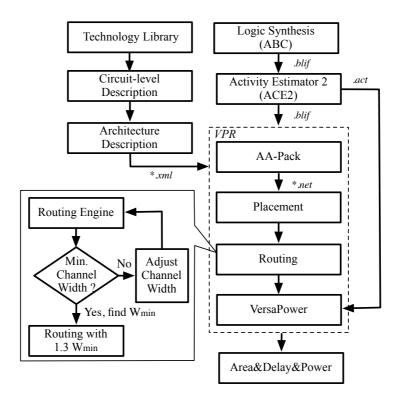

| 2.27 | Classical EDA flow for FPGA architecture exploration purpose                                                     | 47 |

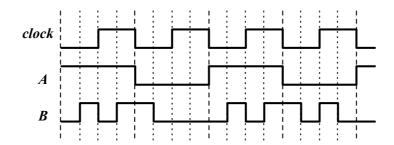

| 2.28 | Examples of signals for switching activity modeling                                                              | 48 |

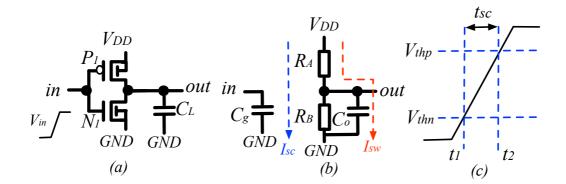

| 2.29 | Dynamic power modelling: (a) an CMOS inverter with a load capacitance $C_L$ ; (b)                                |    |

|      | Equivalent RC model; (c) Input transition from low to high voltage level. $\ \ldots \ .$                         | 50 |

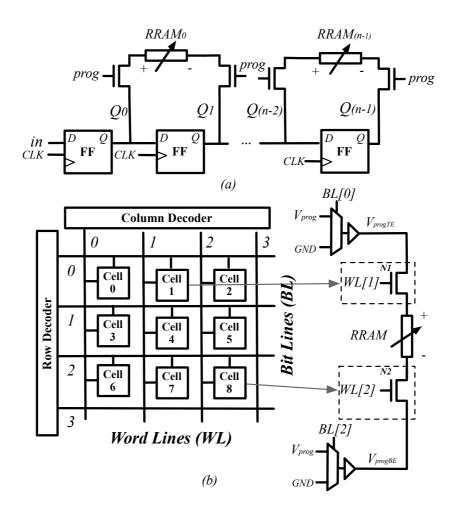

| 3.1  | System-level implementations exploiting the 2T1R programming structure: (a)                                      |    |

|      | scan chain [8]; (b) memory bank [9]                                                                              | 55 |

| 3.2  | A 2T1R programming structure extracted from system-level implementations in                                      |    |

|      | Fig. 3.1                                                                                                         | 57 |

| 3.3  | I-V characteristics of the 2T1R structure                                                                        | 58 |

| 3.4  | (a) Asymmetric bulk management of the 2T1R structure; (b) Symmetric bulk                                         |    |

|      | management of the 2T1R structure; (c) Single well application of layout; (d)                                     |    |

|      | Triple well application of layout.                                                                               | 59 |

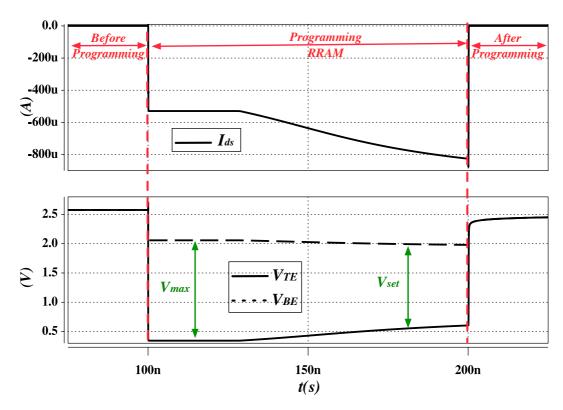

| 3.5  | Transient analysis on voltages and current in the 2T1R structure during a set                                    |    |

|      | process $(W_{prog} = 5, V_{prog} = 3.0V, W_{inv} = 20, 1 W_{prog} = 320nm)$                                      | 61 |

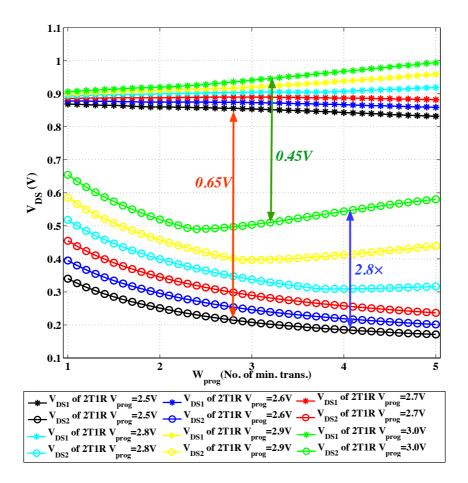

| 3.6  | $V_{DS1}$ and $V_{DS2}$ in 2T1R structure under diverse $V_{prog}$ ( $W_{inv} = 20$ )                            | 62 |

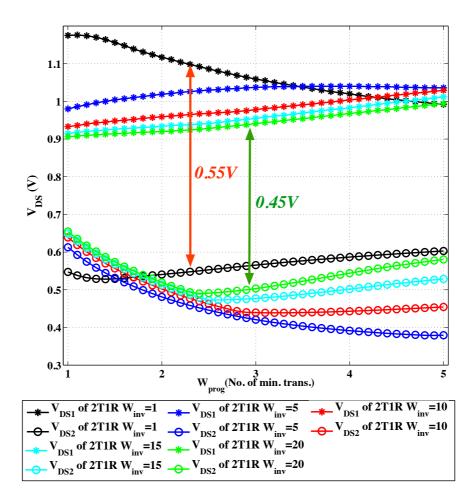

| 3.7  | $V_{DS1}$ and $V_{DS2}$ in 2T1R structure under diverse $W_{inv}$ ( $V_{prog} = 3.0V$ ). (1 $W_{prog} = 3.0V$ )  |    |

|      | 320 <i>nm</i> )                                                                                                  | 63 |

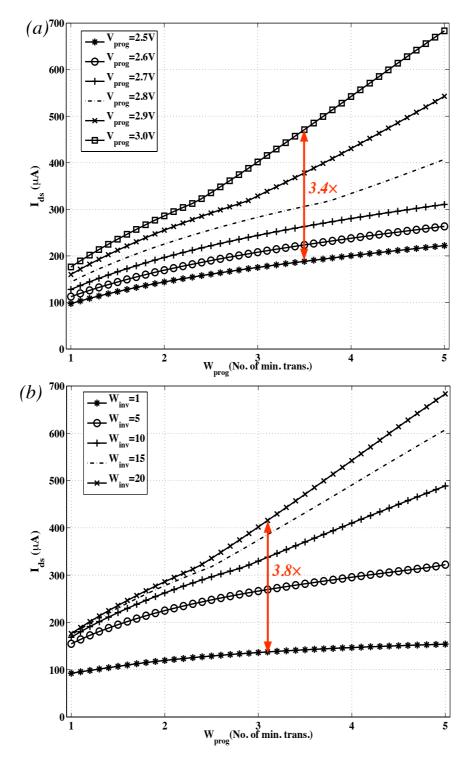

| 3.8  | (a) $I_{ds}$ in 2T1R structure under diverse $V_{prog}$ ( $W_{inv}$ = 20); (b) $I_{ds}$ in 2T1R struc-           |    |

|      | ture under diverse $W_{inv}$ ( $V_{prog} = 3.0V$ ). (1 $W_{prog} = 320nm$ )                                      | 64 |

| 3.9  | A 2TG1R programming structure extracted from system-level implementations                                        |    |

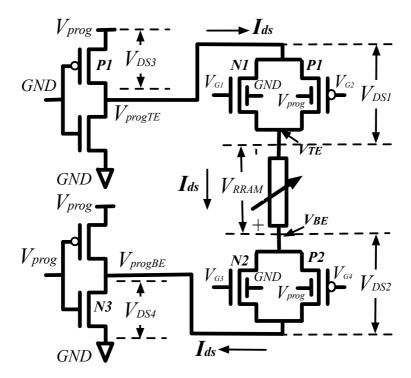

|      | in Fig. 3.1                                                                                                      | 65 |

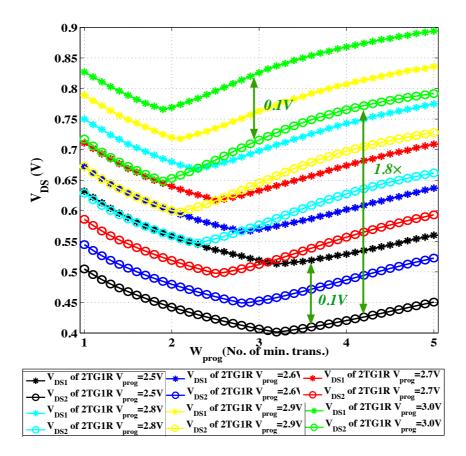

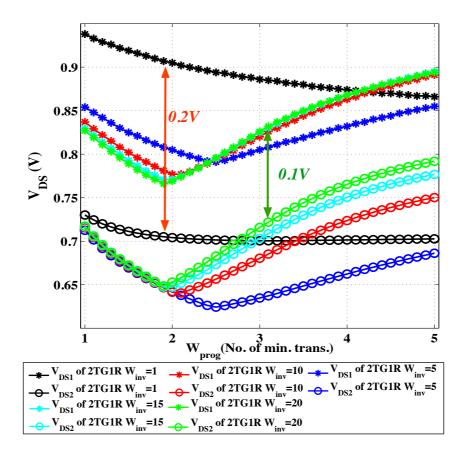

| 3.10 | $V_{DS1}$ and $V_{DS2}$ in 2TG1R structure under diverse $V_{prog}$ ( $W_{inv} = 20$ );                          | 66 |

|      | $V_{DS1}$ and $V_{DS2}$ in 2TG1R structure under diverse $W_{inv}$ ( $V_{prog} = 3.0V$ ). (1 $W_{prog} = 3.0V$ ) |    |

|      | 320 <i>nm</i> )                                                                                                  | 67 |

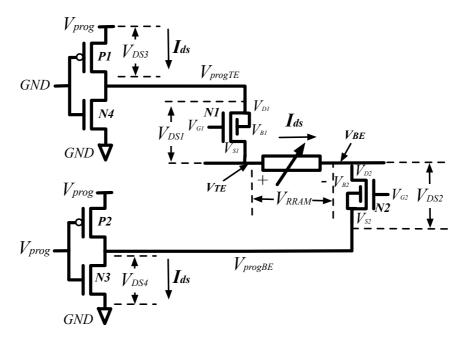

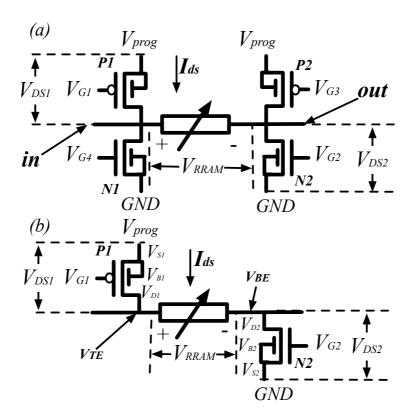

| 3.12 | (a) The proposed 4T1R structure (b) Extracted 4T1R structure in a <b>set</b> process .                           | 68 |

| 3.13 | I-V characteristics of the 4T1R structure: (a) $V_{set} = V_{reset}$ ; (b) $V_{set} < V_{reset}$ or              |    |

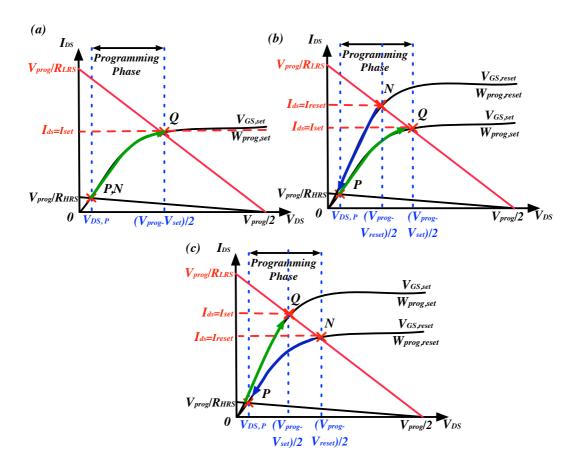

|      | $I_{set} < I_{reset}$ ; (c) $V_{set} > V_{reset}$ or $I_{set} > I_{reset}$                                       | 70 |

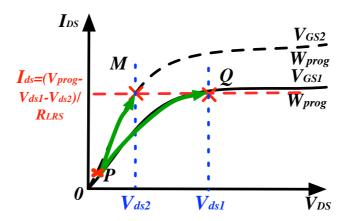

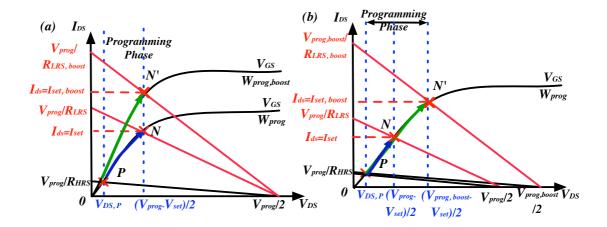

| 3.14 | I-V characteristics of the 4T1R structure during set process when: (a) Boosting                                  |    |

|      | $W_{prog}$ ; (b) Boosting $V_{prog}$                                                                             | 71 |

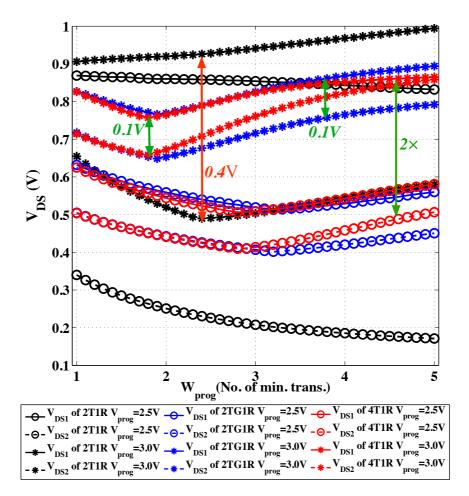

| 3.15 | Comparison on $V_{DS}$ of programming transistors under diverse $W_{prog}$ and $V_{prog}$                        |    |

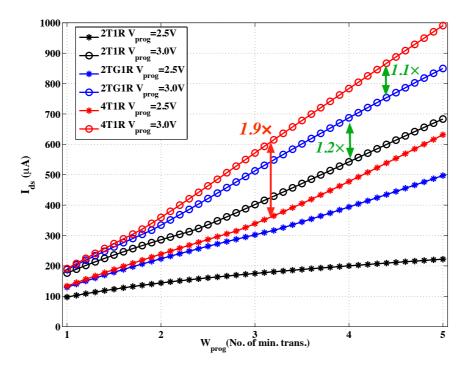

|      | in 2T1R, TG-based 2T1R and 4T1R structures ( $W_{inv} = 20$ ). (1 $W_{prog} = 320nm$ ).                          | 75 |

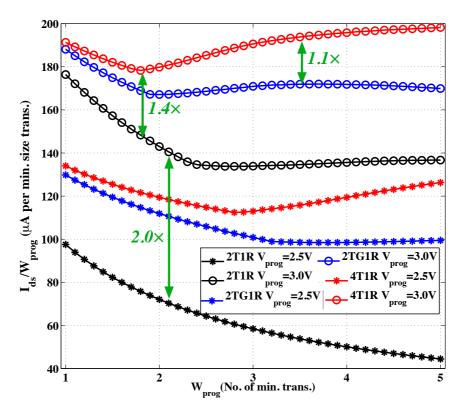

| 3.16 | Comparison on $I_{ds}$ in 2T1R, 2TG1R and 4T1R structures ( $W_{inv}$ = 20). (1 $W_{prog}$ = 320 $nm$ )                                  | 76  |

|------|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.17 | Comparison on driving current per minimum transistor width under diverse                                                                 |     |

|      | $W_{prog}$ and $V_{prog}$ between 2T1R, TG-based 2T1R and 4T1R structures ( $W_{inv} = 20$ ).                                            |     |

|      | $(1 W_{prog} = 320nm) \dots \dots$ | 77  |

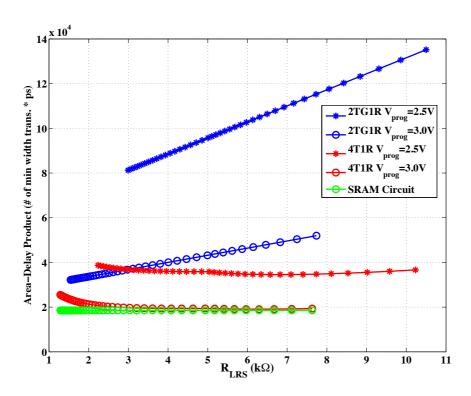

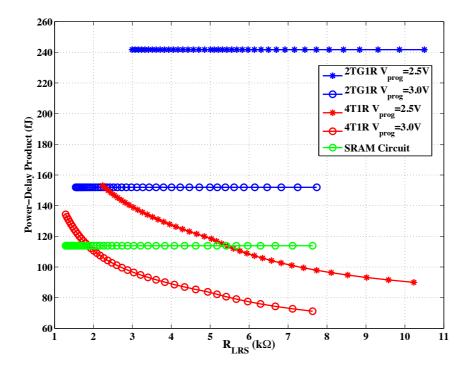

| 3.18 | Comparison on area-delay product of 2TG1R and 4T1R structures ( $W_{inv} = 20$ ).                                                        | 78  |

|      | Comparison on power-delay product of 2TG1R and 4T1R structures ( $W_{inv} = 20$ ).                                                       | 78  |

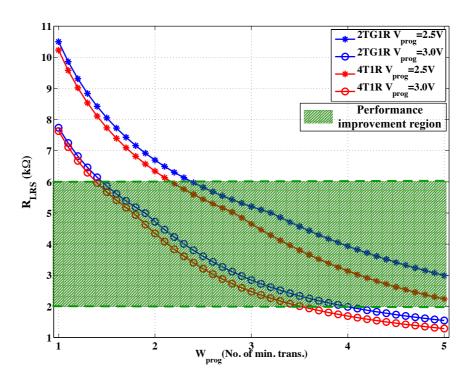

|      | Comparison on $R_{LRS}$ in 2TG1R and 4T1R structures ( $W_{inv} = 20$ ). (1 $W_{prog} =$                                                 |     |

|      | 320nm)                                                                                                                                   | 79  |

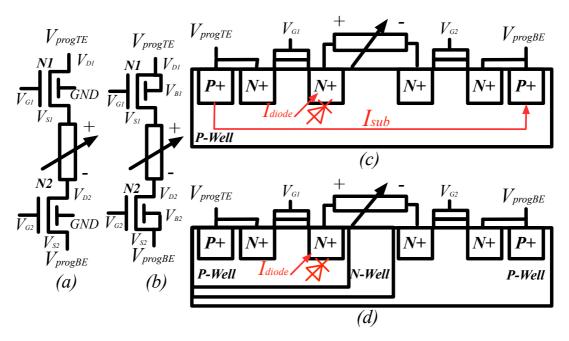

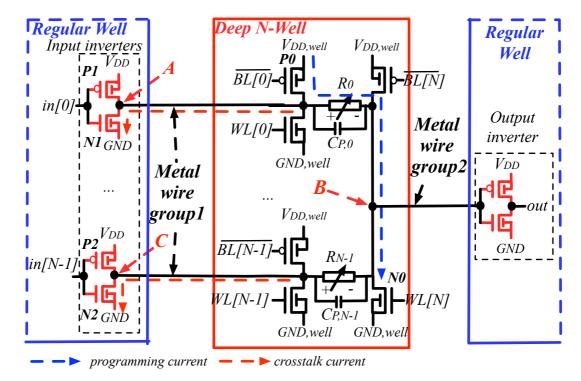

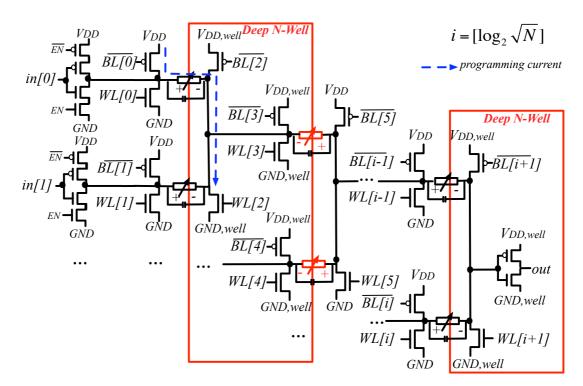

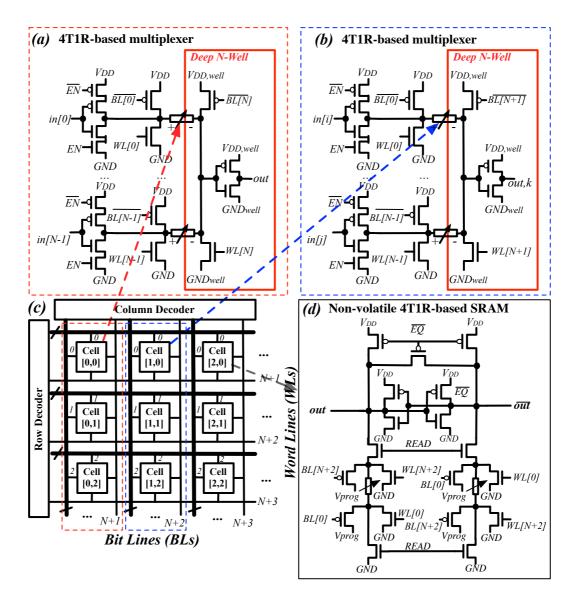

| 3.21 | Circuit design and well arrangement of a naive $N:1$ one-level 4T1R-based                                                                |     |

|      | multiplexer                                                                                                                              | 81  |

| 3.22 | Improved one-level N-input 4T1R-based multiplexer: (a) operating mode ( $V_{DD,well}$                                                    | =   |

|      | $V_{DD}$ , $GND_{well} = GND$ ); (b) set process $(V_{DD,well} = -V_{prog} + 2V_{DD}, GND_{well} =$                                      |     |

|      | $-V_{prog} + V_{DD}$ ; (c) reset process ( $V_{DD,well} = V_{prog}$ , $GND_{well} = V_{prog} - V_{DD}$ ;                                 | 84  |

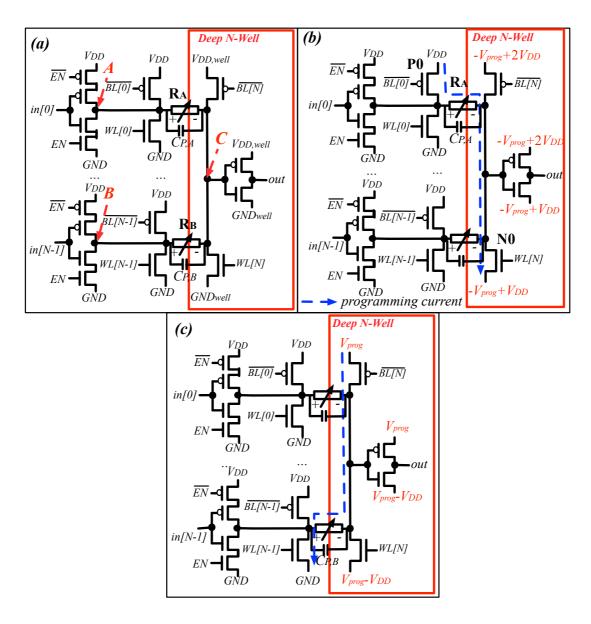

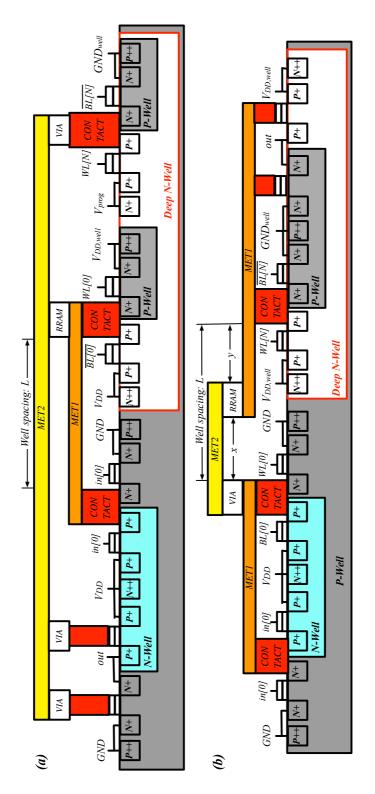

| 3.23 | Cross-section of the layout of 4T1R multiplexers: (a) naive design; (b) improved                                                         |     |

|      | design                                                                                                                                   | 87  |

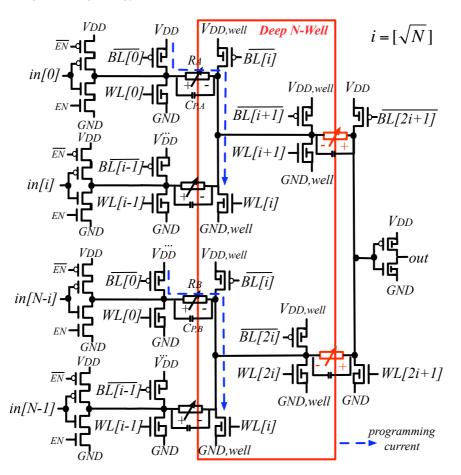

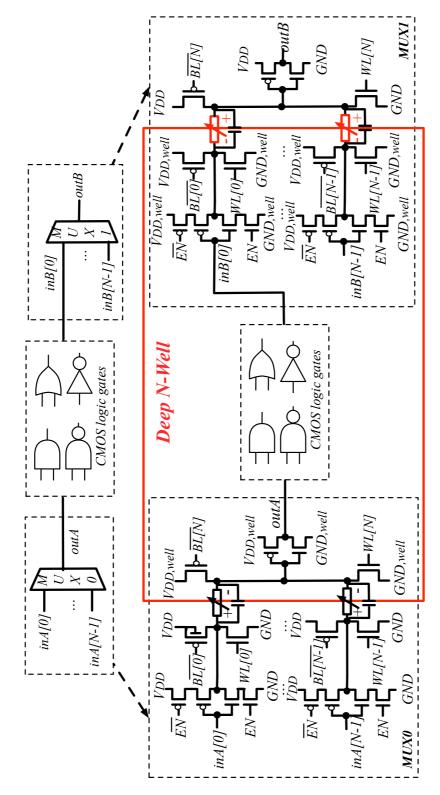

| 3.24 | Schematic of a robust two-level N-input 4T1R-based multiplexer                                                                           | 88  |

| 3.25 | Schematic of a robust tree-like <i>N</i> -input 4T1R-based multiplexer                                                                   | 89  |

| 3.26 | Cascading two <i>N</i> -input one-level 4T1R-based multiplexers: share Deep N-Wells                                                      |     |

|      | efficiently.                                                                                                                             | 90  |

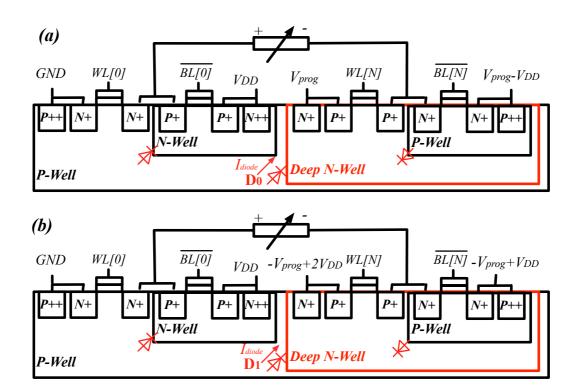

| 3.27 | Cross-section of the layout of a 4T1R programming structure: (a) during reset                                                            |     |

|      | process; (b) during set process                                                                                                          | 91  |

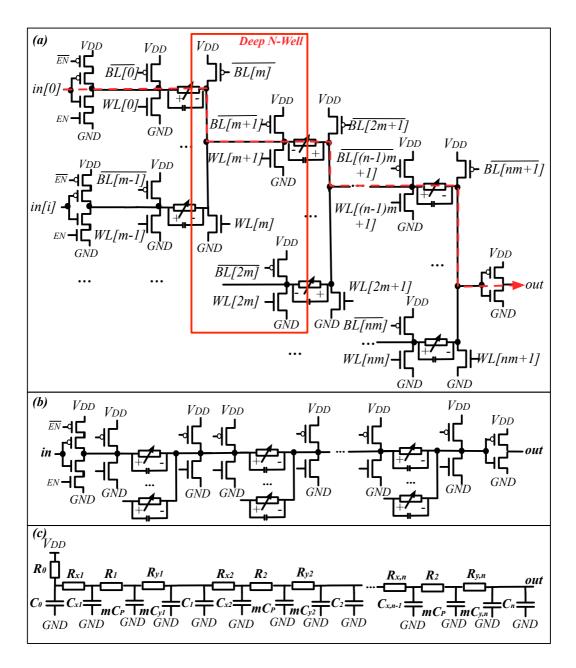

| 3.28 | (a) Critical path of a general RRAM-based multiplexer; (b) General critical path                                                         |     |

|      | of RRAM-based multiplexer; (c) Equivalent RC model                                                                                       | 94  |

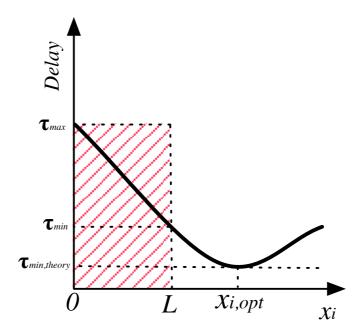

| 3.29 | Relation between $x_i$ and delay of a RRAM-based multiplexer                                                                             | 97  |

| 3.30 | Relation between $W_{prog}$ and delay of a RRAM-based multiplexer                                                                        | 98  |

| 3.31 | Transient analysis of a 2-input 4T1R-based multiplexer in Fig. 3.22(a): (a) signal                                                       |     |

|      | waveforms of programming phase; (b) signal waveforms of operation. $\dots$                                                               | 101 |

| 3.32 | Impact of $W_{prog}$ on the delay of 50-input improved 4T1R-based multiplexers                                                           |     |

|      |                                                                                                                                          | 102 |

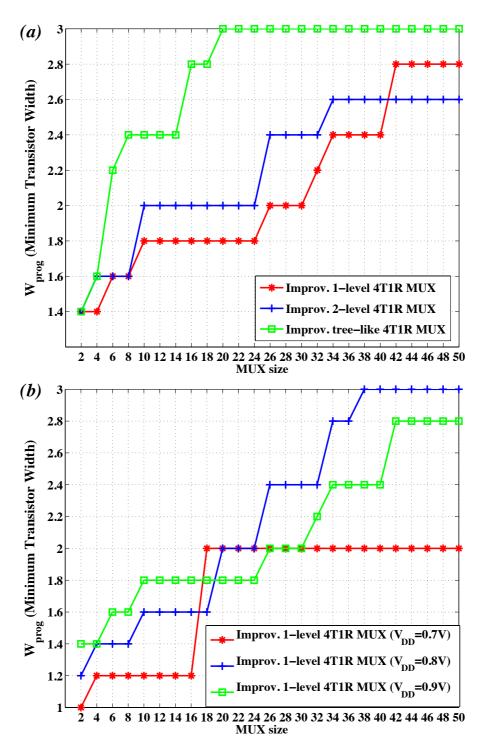

| 3.33 | Two case studies on the best $W_{prog}$ of improved 4T1R-based multiplexers ( $x = L$ ):                                                 |     |

|      | (a) impact of the multiplexing structures when $V_{DD} = 0.9V$ (b) impact of $V_{DD}$ .                                                  | 103 |

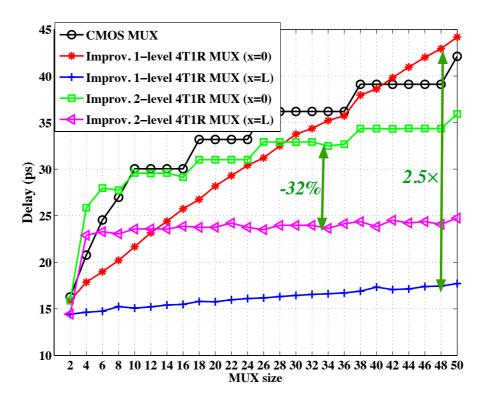

| 3.34 | Delay comparison of improved 4T1R-based multiplexers featured by $x = 0$ and                                                             |     |

|      |                                                                                                                                          | 104 |

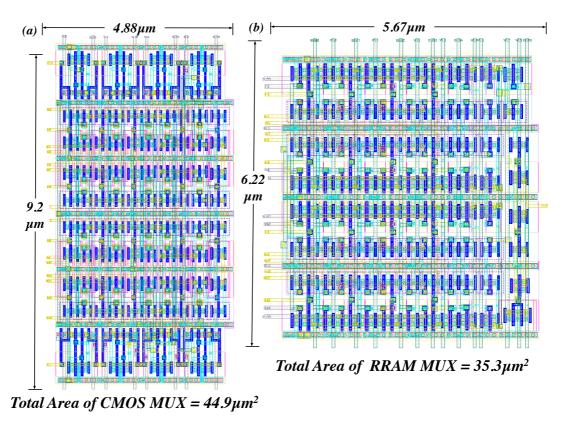

| 3.35 | Layout of 16-input multiplexers: (a) CMOS two-level structure; and (b) 4T1R-                                                             |     |

|      |                                                                                                                                          | 105 |

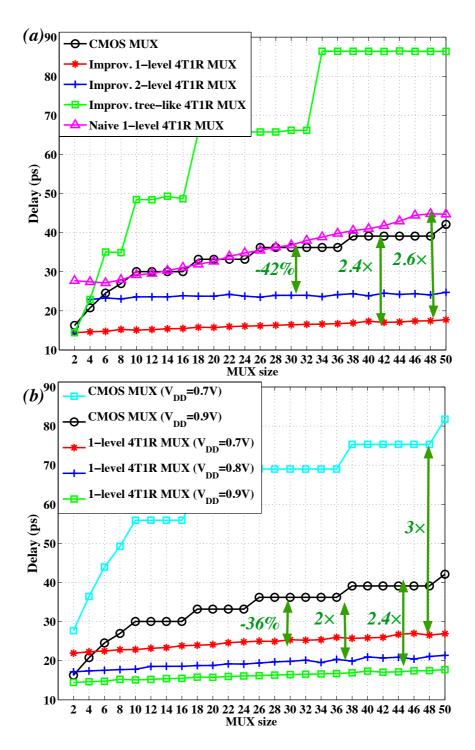

| 3.36 | Delay comparison between CMOS and 4T1R-based multiplexers: (a) delay im-                                                                 |     |

|      | provements of one-level, two-level and tree-like structures ( $V_{DD} = 0.7V$ ); (b)                                                     |     |

|      |                                                                                                                                          | 107 |

| 3.37 | Power comparison between CMOS and 4T1R-based multiplexers: (a) energy                                                                    |     |

|      | improvements of one-level, two-level and tree-like structures ( $V_{DD} = 0.7V$ ); (b)                                                   |     |

|      | power reduction of one-level structure at near $V_t$ regime                                                                              | 108 |

| 3.38 | Comparison between CMOS multiplexers and 4T1R-based multiplexers: (a) Area-Delay Product; (b) Power-Delay Product | 109 |

|------|-------------------------------------------------------------------------------------------------------------------|-----|

| 3 30 | Impact of parasitic capacitance of RRAM $C_P$ on the delay of one-level 4T1R-                                     | 100 |

| 3.33 | based multiplexers ( $V_{DD} = 0.9V$ )                                                                            | 111 |

| 3 40 | $R_{HRS}$ degradation when $V_{set} = \{0.4, 0.6V, 0.8V\} < V_{DD} = 0.9V$                                        | 111 |

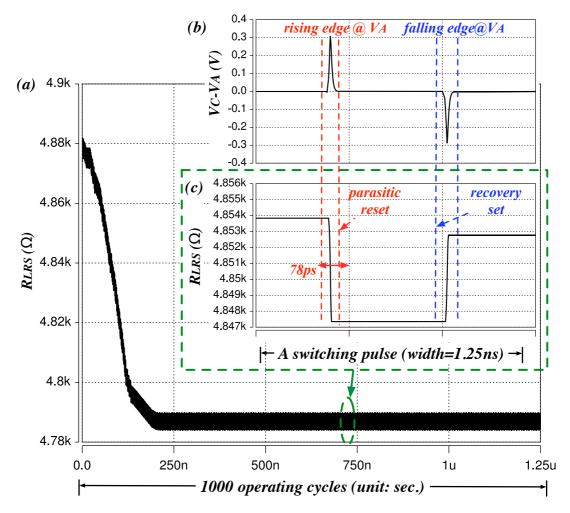

|      | (a) $R_{LRS}$ degradation when $V_{reset} = 0.3V$ over $1k$ operating cycles; (b) Voltage                         | 112 |

| 3.41 | across a RRAM in LRS ( $V_A$ and $V_C$ in Fig. 3.22(a)) during operation; and (c) $R_{LRS}$                       |     |

|      | degradation when $V_{reset} = 0.3V$ in a switching cycle                                                          | 113 |

|      | degradation when v <sub>reset</sub> = 0.5 v in a switching cycle                                                  | 110 |

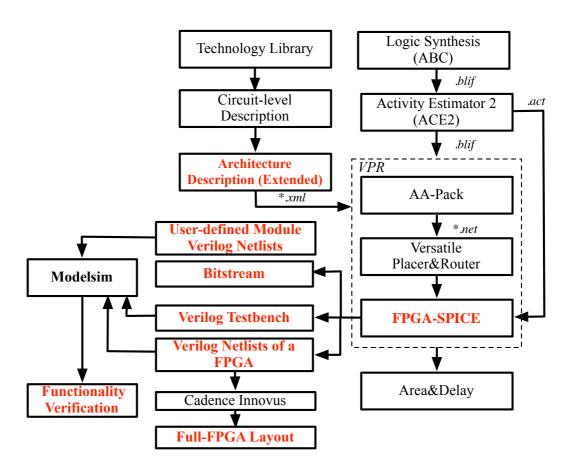

| 4.1  | FPGA-SPICE EDA flow for SPICE modeling purpose                                                                    | 118 |

| 4.2  | Ilustration of the full-chip-level testbenches                                                                    | 120 |

| 4.3  | Ilustration of the grid-level testbenches                                                                         | 121 |

| 4.4  | Ilustration of the component-level testbenches                                                                    | 122 |

| 4.5  | FPGA-SPICE EDA flow for synthesizable Verilog purpose                                                             | 123 |

| 4.6  | An I/O pad: (a) VPR abstract-level modeling, and (b) actual physical design                                       | 125 |

| 4.7  | Transistor-level circuit design of (a) an inverter and (b) a tapered buffer                                       | 127 |

| 4.8  | Transistor-level circuit design of (a) a global routing multiplexer, (b) a local                                  |     |

|      | routing multiplexer, and (c) the internal tree-like structure                                                     | 131 |

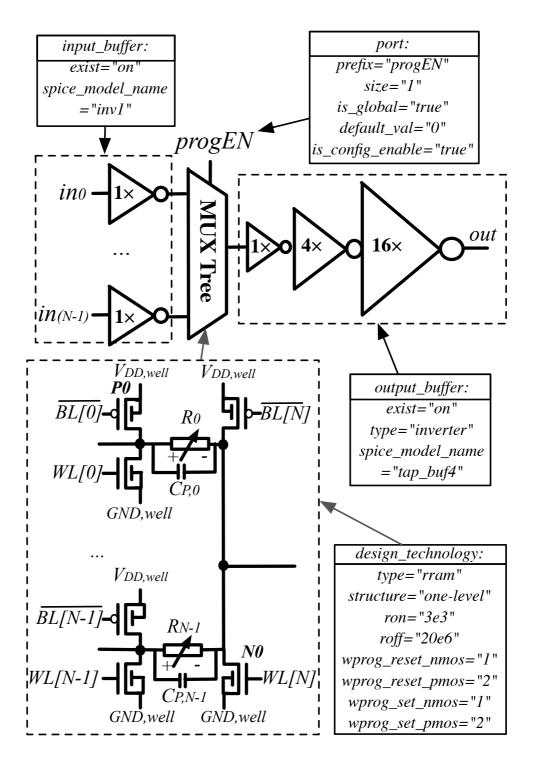

| 4.9  | Transistor-level circuit design of a 4T1R-based multiplexer                                                       | 133 |

| 4.10 | An example of the transistor-level design of a LUT                                                                | 135 |

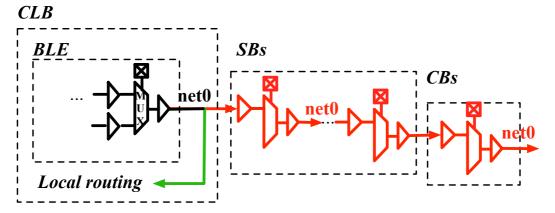

| 4.11 | (a) A length-2 unidirectional wire (highlighted in red) within FPGA routing archi-                                |     |

|      | tecture; (b) Corresponding RC modeling of segments                                                                | 136 |

| 4.12 | Ilustration of the voltage stimuli generation and load extraction techniques. (a)                                 |     |

|      | BLE multiplexer with its architectural context; (b) extracted testbench. $\ \ldots \ \ldots$                      | 137 |

| 4.13 | An example for parasitic nets estimation                                                                          | 138 |

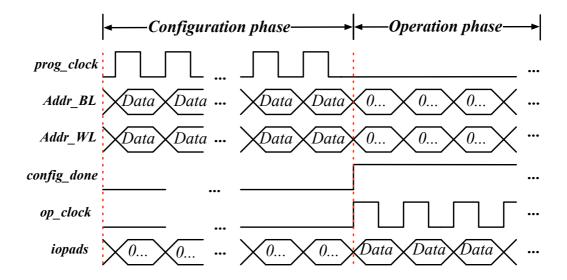

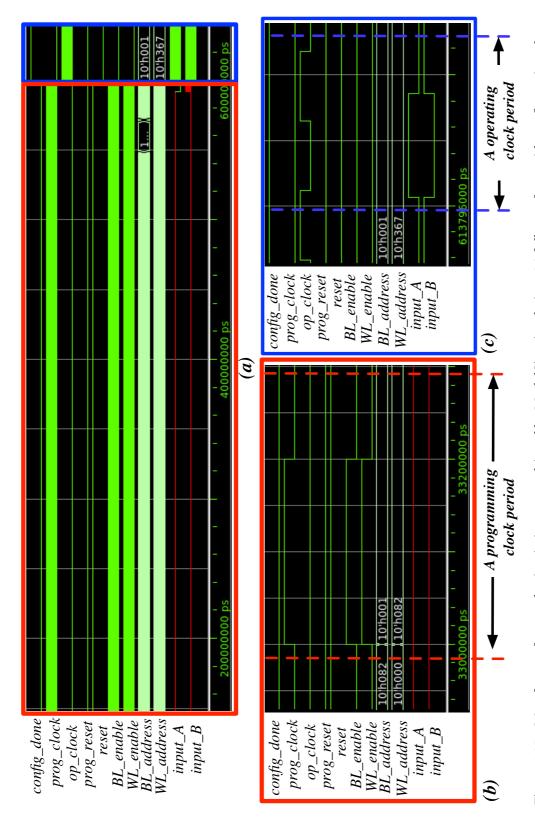

| 4.14 | An illustration of the waveforms for functional verification purpose                                              | 141 |

| 4.15 | Waveforms of a sample circuit: inverter, achieved by ModelSim simulation:                                         |     |

|      | (a) full waveform with configuration phase highlighted in red rectangle and                                       |     |

|      | operation phase highlighted in blue rectangle; (b) an example of a programming                                    |     |

|      | clock cycle; (c) an example of a operating clock cycle                                                            | 142 |

| 4.16 | Power breakdown results of the considered FPGA architecture between FPGA-                                         |     |

|      | SPICE and VersaPower averaged over the MCNC big20 benchmark suite for                                             |     |

|      | 22nm, 45nm and 180nm technology nodes                                                                             | 145 |

| 4.17 | Full-chip layouts of 40nm SRAM-based FPGAs with CLB array size $5 \times 5$ , a channel                           |     |

|      | width of 300                                                                                                      | 146 |

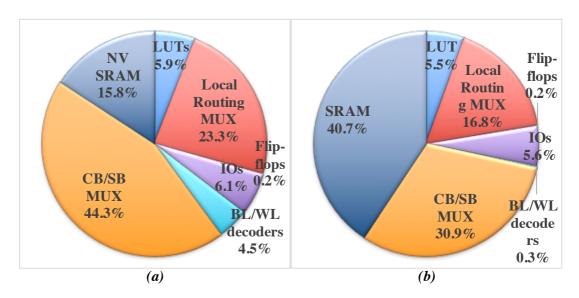

| 4.18 | Area breakdown of SRAM-based FPGAs which are configured by (a) BL/WL                                              |     |

|      | decoders, and (b) scan-chain flip-flops                                                                           | 147 |

| 5.1  | Memory access organization in SRAM-based FPGA: SRAMs are placed in an                                             |     |

| 0.1  | array and SRAMs in the same column/row share the same BL/WL                                                       | 150 |

| 5.2  | Memory access organization in RRAM-based FPGA: RRAMs belonging to the                                             |     |

| J.L  | same multiplexer/NV SRAM are placed in the same column and share BL/WL.                                           | 151 |

|      | 1 r                                                                                                               |     |

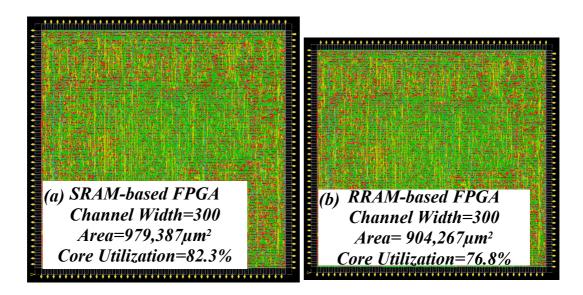

| 5.3  | Full-chip layouts of 40nm SRAM-based and RRAM-based FPGAs with CLB array                   |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | size $5 \times 5$                                                                          | 155 |

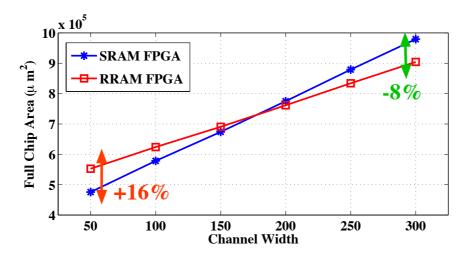

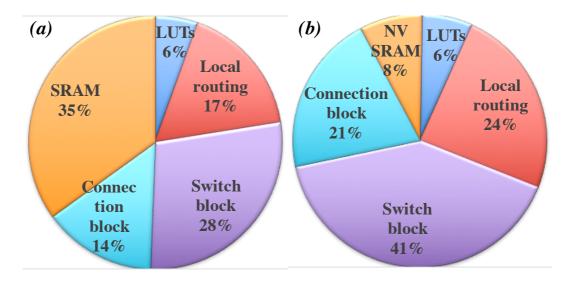

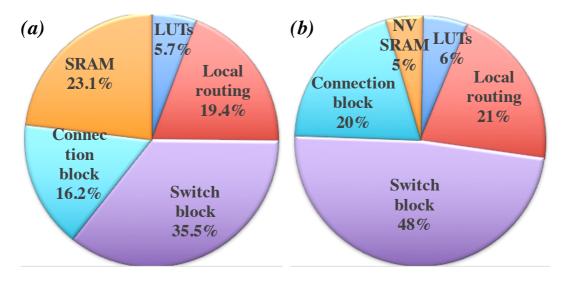

| 5.4  | Area breakdown of (a) RRAM-based FPGA and (b) SRAM-based FPGA                              | 155 |

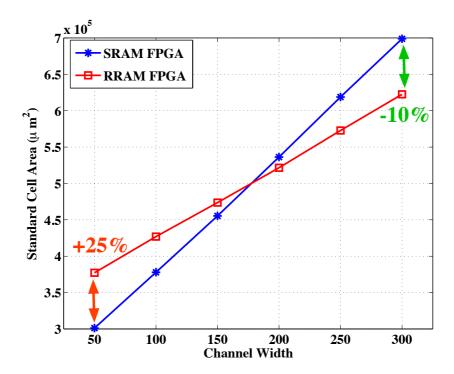

| 5.5  | Full-chip area comparison between SRAM-based and RRAM-based FPGAs by                       |     |

|      | sweeping channel widths from 50 to 300                                                     | 156 |

| 5.6  | Standard cell area comparison between SRAM-based and RRAM-based FPGAs                      |     |

|      | by sweeping channel widths from 50 to 300                                                  | 156 |

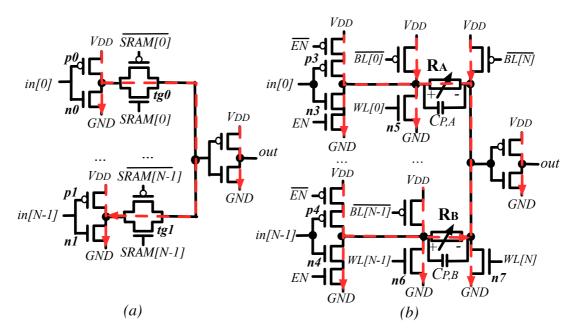

| 5.7  | Leakage paths of $N$ -input multiplexers: (a) SRAM-based (b)RRAM-based                     | 159 |

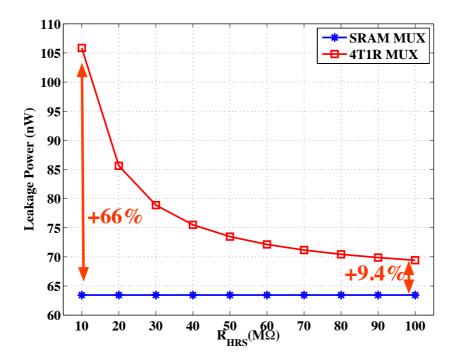

| 5.8  | Impact of $R_{HRS}$ on the average static power of a 2-input 4T1R-based multiplexer        | 160 |

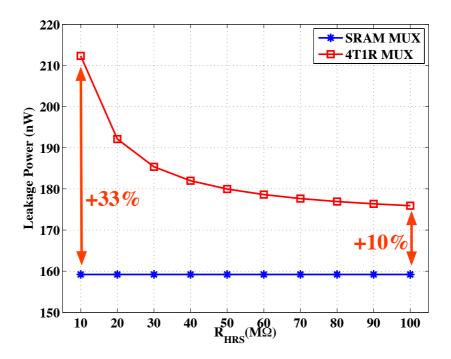

| 5.9  | Impact of $R_{HRS}$ on the average static power of a 2-input 4T1R-based multiplexer        |     |

|      | with tapered buffer at output                                                              | 161 |

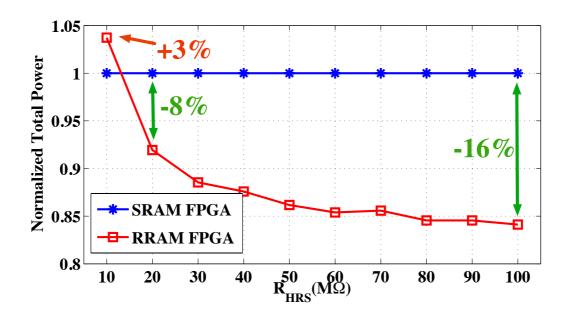

| 5.10 | Normalized power consumption of SRAM-based and RRAM-based architectures                    |     |

|      | with different $R_{HRS}$                                                                   | 162 |

| 5.11 | Static power breakdown of (a) RRAM-based FPGA and (b) SRAM-based FPGA                      | 163 |

| 5.12 | Dynamic power breakdown of (a) RRAM-based FPGA and (b) SRAM-based FPGA.                    | 163 |

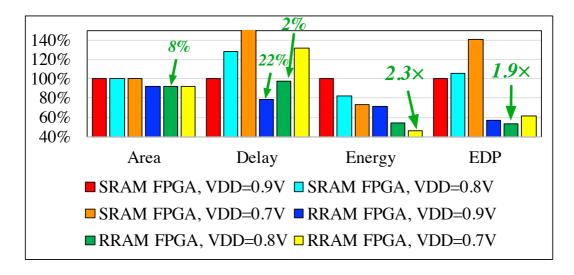

| 5.13 | Area, delay and energy comparison between SRAM-based and RRAM-based                        |     |

|      | FPGAs operating at nominal and near- $V_t$ regime                                          | 164 |

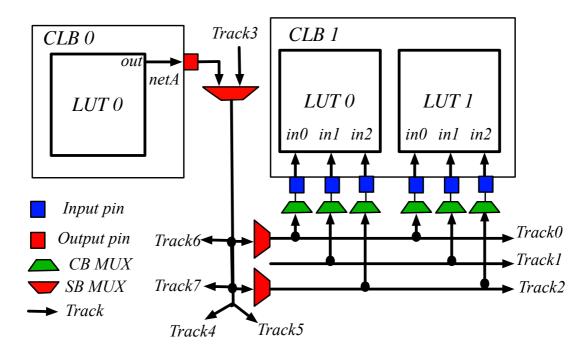

| 5.14 | Classical interconnection from routing tracks to LUT inputs                                | 167 |

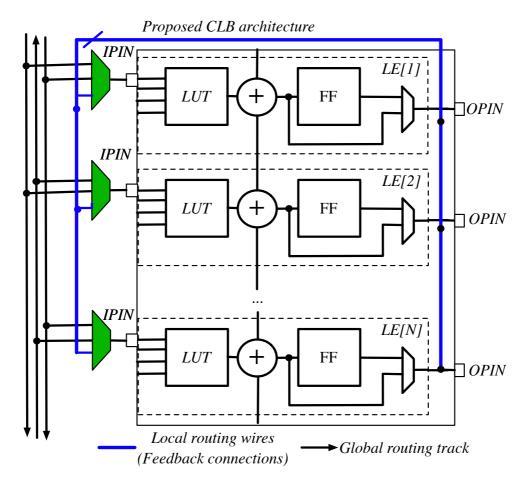

| 5.15 | Proposed interconnection from routing tracks to LUT inputs                                 | 168 |

| 5.16 | An illustrative example of the proposed routing architecture ( $K = 6$ ) with $F_{c,in} =$ |     |

|      | 0.33 and $F_s = 6$                                                                         | 169 |

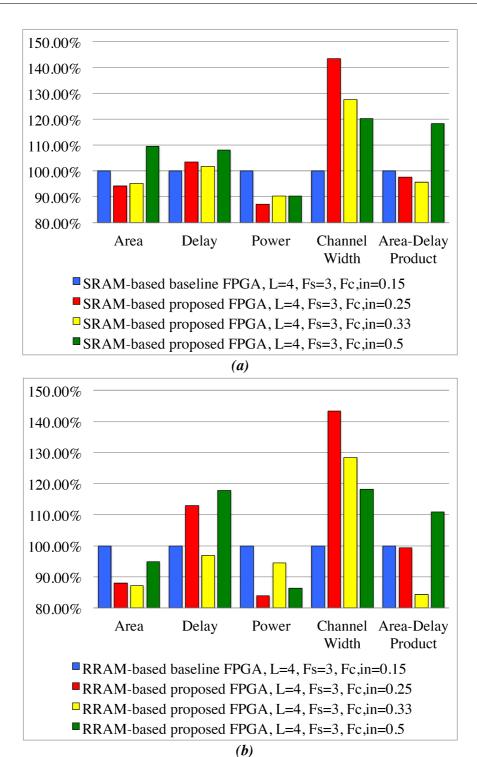

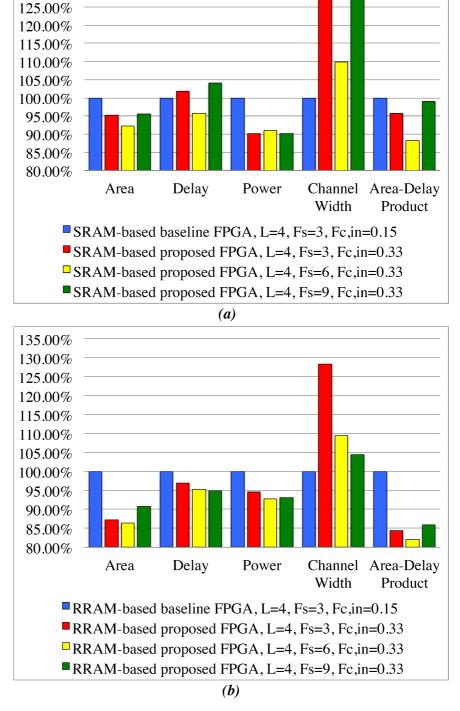

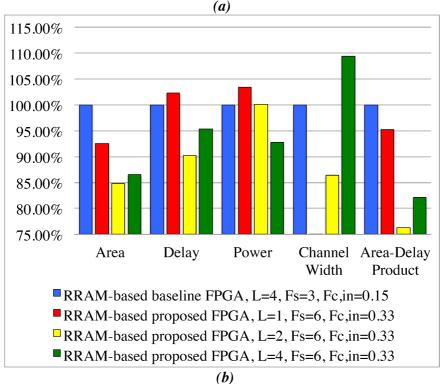

| 5.17 | Normalized average area, delay, power and channel width of baseline and pro-               |     |

|      | posed architecture by sweeping $F_{c,in}$ : (a) SRAM-based architectures; (b) RRAM-        |     |

|      | based architectures                                                                        | 170 |

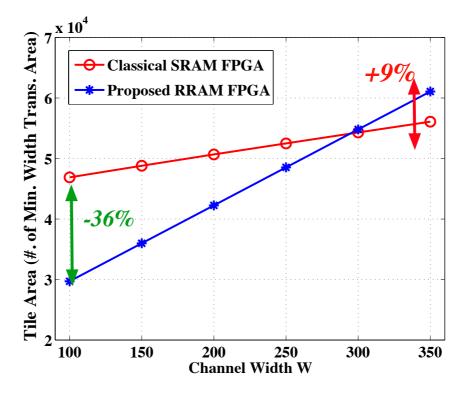

| 5.18 | Tile area comparison between a traditional FPGA architecture and the proposed              |     |

|      | RRAM FPGA architecture for different channel width $W.\ldots.$                             | 171 |

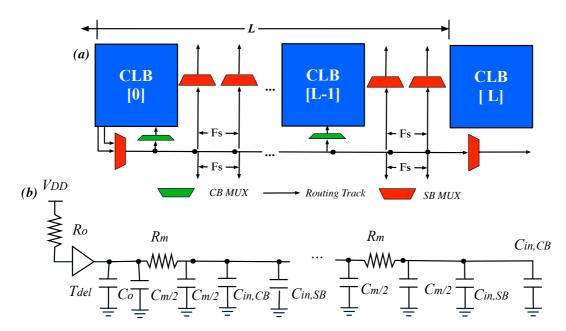

| 5.19 | (a) Driver multiplexer and fan-outs of a Length- $L$ wire; (b) Equivalent $RC$ model       |     |

|      | of a Length- $L$ wire                                                                      | 172 |

| 5.20 | Normalized average area, delay, power and channel width of baseline and pro-               |     |

|      | posed architectures by sweeping $F_s$ : (a) SRAM-based architectures; (b) RRAM-            |     |

|      | based architectures                                                                        | 173 |

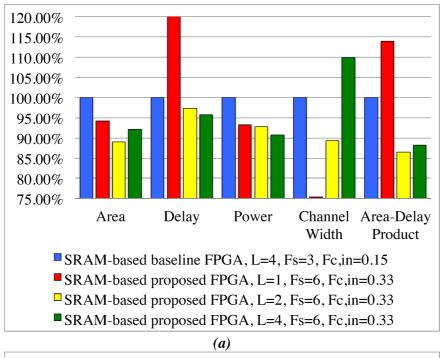

| 5.21 | Normalized average area, delay, power and channel width of baseline and pro-               |     |

|      | posed architectures by sweeping L: (a) SRAM-based architectures; (b) RRAM-                 |     |

|      | based architectures                                                                        | 176 |

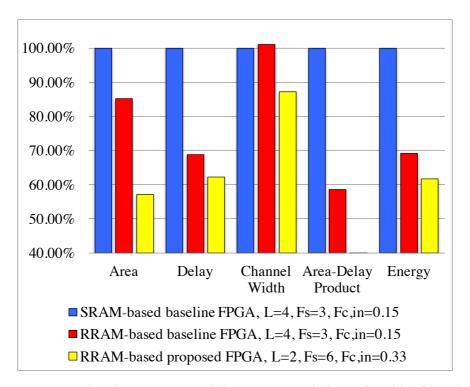

| 5.22 | Normalized average area, delay, energy and channel width of baseline and pro-              |     |

|      | posed architectures: (a) baseline SRAM-based architectures; (b) baseline RRAM-             |     |

|      | based architectures; (c) proposed RRAM-based architectures                                 | 178 |

| 5.23 | Normalized average area, delay, power, channel width, ADP and PDP of classical SRAM-       |     |

|      | based and proposed RRAM-based architectures                                                | 178 |

## List of Tables

| 2.1 | Bipolar RRAMs with different metal oxide materials                                           | 19  |

|-----|----------------------------------------------------------------------------------------------|-----|

| 2.2 | FPGA Architecture Parameters                                                                 | 24  |

| 2.3 | Analytical comparison between CMOS one-level, two-level and tree-like multi-                 |     |

|     | plexers                                                                                      | 32  |

| 2.4 | Static probability and transition density of the signals in Fig. 2.28                        | 48  |

| 3.1 | Voltages arrangements for operation, set and reset examples in Fig. 3.22(a)(b)(c)            | 85  |

| 3.2 | Analytical comparison on area, delay and switching energy of N-input 4T1R-                   |     |

|     | based multiplexers                                                                           | 92  |

|     |                                                                                              |     |

| 4.1 | Comparison of runtime, memory usage and total power of full-chip/grid/compone                | nt- |

|     | level testbenches for 22nm, 45nm and 180nm technology nodes in the case of                   |     |

|     | the MCNC big20 benchmark s298                                                                | 143 |

| 4.2 | Comparison of accuracy by modules in full-chip/grid/component-level test-                    |     |

|     | benches for 22nm, 45nm and 180nm technology nodes in the case of the MCNC                    |     |

|     | benchmark big20 s298                                                                         | 144 |

| 5.1 | Resistance of leakage paths of the 4T1R-based multiplexer in 5.7(b) whose start-             |     |

|     | ing point is <b>p3</b> and ending points are <b>n4</b> , <b>n5</b> , <b>n6</b> and <b>n7</b> | 159 |

| 5.2 | Delay comparison between SRAM-based and RRAM-based routing multiplexers.                     |     |

| 6.1 | Summary of Contributions in Differnt Research Fields                                         | 182 |

## 1 Introduction

Strong demand from the *Internet of Things* (IoT) have fueled researches on high-performance and energy-efficient computer-based systems [10, 11, 12]. We confront challenges from two-pronged ecosystems in IoT: low-power mobile devices and cloud services. The mobile devices are supposed to stay active for a long period with a limited battery life. For these devices, energy-efficiency is the most critical factor due to a tight power budget. Cloud services are actually provided by datacenters, aiming at processing huge amount of data from mobile devices or other sources. For datacenters, high-performance computing is a more important metric than energy efficiency since they are supposed to deal with abundant data while being power supplied through the grid.

Since invented in 1984, *Field Programmable Gate Arrays* (FPGAs) have demonstrated themselves not only as an alternative implementation media of *Application Specific Integrated Circuits* (ASICs) but also as an indispensable component of embedded systems and datacenter infrastructures [13, 14], growing to a \$ 4.5 billion per year industry [15, 16]. The programmability and large I/O bandwidth of FPGAs brings significant advantages in realizing energy-efficient and high-throughput applications, e.g., deep learning network [17]. Meanwhile, programmability and I/O bandwidth cost general FPGA implementations 20× bigger area, 4× longer delay and 12× higher power consumption, when compared to ASICs [18]. Such overheads prohibit FPGAs from massive deployment in ultra-low-power embedded systems.

Resistive Random Access Memories (RRAMs) [1, 19], a member of the emerging Non-Volatile Memories (NVM) family [20], have become a promising candidate in displacing conventional memory technologies of FPGAs, such as SRAM [21] and Flash [7]. Potentials of RRAMs have been investigated in many fields, i.e., memory storage [22], neuromorphic computing [23], hardware security [24] and FPGAs [25, 9, 26, 27, 28]. In particular, RRAM-based FPGAs are predicted to improve area, delay and power in addition to non-volatility, thus being an effective component for IoT applications. Still, researches and development of RRAM-based FPGAs are in their infancy. Circuit simulations focus on functional verification and employ analytical RRAM models. Area and performance predictions are achieved without fully considering physical design issues, e.g., the parasitic effects of RRAMs and their associated transistors.

### **Chapter 1. Introduction**

Additionally, the efficiency of RRAM-based circuit topologies has not been carefully examined. Lacking solid circuit-level studies, FPGA architecture explorations based on RRAMs would be less meaningful. Moreover, current FPGA architecture exploration tools provide limited supports in accurate power analysis, especially for emerging memory technologies. It is entirely possible that the predicted improvements of RRAM-based FPGAs are counteracted when the parasitic effects are considered and accurate power analysis are conducted. Therefore, it is necessary to examine the concept with realistic device modelling, circuit designs under physical design considerations and accurate architecture-level simulations.

In this thesis, we present RRAM-based FPGAs from transistor-level circuit designs to architecture-level optimizations and fast prototyping techniques. We validate their high-performance and low-power advantages over *Static Random Access Memory* (SRAM)-based FPGAs with theoretical analysis, industrial electrical simulators and novel *Electrical Design Automation* (EDA) tools. We believe that this is the first systematic study about RRAM-based essential circuit designs and FPGA architectures. To motivate our work, the rest of this chaper is organized as follows. Section 1.1 provides a brief overview about RRAM technology and explains their outstanding features to be exploited in circuit designs and FPGAs. Section 1.2 is devoted to analyzing the advantages of SRAM-based FPGAs and their bottlenecks in low-power applications. Section 1.3 introduces the opportunities of RRAM-based FPGAs in overcoming the limitations of their SRAM-based counterparts. Section 1.4 lists the major contributions of this thesis and the approaches to achieve them.

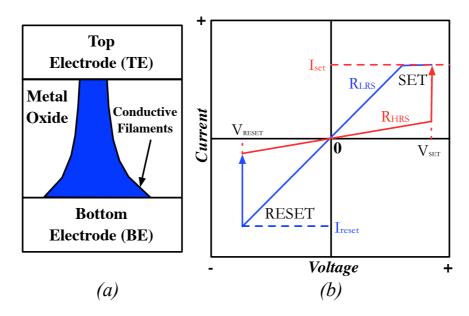

#### 1.1 Overview of RRAMs

Since their popularization in 2004 [29], *Resistive Random Access Memories* (RRAMs) are expected to trigger revolutionary changes in many applications. In terms of functionality, a RRAM can be simply regarded as a non-volatile configurable resistor, which can hold information when powered down. A RRAM device exhibits resistive switching between *High Resistance State* (HRS) and *Low Resistance State* (LRS) thanks to forming and rupturing the conductive filaments in its metal oxide, as illustrated in Fig. 1.1(a). By applying a proper combination of programming voltage and programming current between electrodes, resistance states can be switched, following the I-V curve in Fig. 1.1(b).

The non-volatile property of RRAMs have attracted interest in replacing SRAMs, *Dynamic Random-Access Memories* (DRAMs) and even Flash RAMs in computer systems. Compared to volatile memories, e.g., SRAMs and DRAMs, using RRAMs can save reconfiguration time and energy when the entire system wakes up from sleep modes, appealing to IoT and mobile applications. Different from Flash memory, RRAMs are compatible with *Back-End-of-Line* (BEoL) fabrication and hence are envisioned to be stacked on the top of the transistors, reducing fabrication cost and improving footprint of whole system. Besides, BEoL compatibility allows memories to be close to the computing logic, significantly reducing the access time to memories.

Figure 1.1 – A RRAM Device (a) sandwiched structure and (b) I-V Characteristics:  $V_{set}$  and  $I_{set}$  converts part of metal oxide to low-resistance state.

The configurable resistive property of RRAMs have been catalyst of research in In-Memory Computing [30, 31, 32], Neuromorphic Computing [33, 34] and Physical Unclonable Function (PUF) [35, 36]. The HRS and LRS can represent '0' and '1' in boolean logic, similar to the on and off states of a transistor. Hence, the two resistance states can be exploited to realize digital circuits, replacing transistors [37, 30, 38]. Interestingly, even a RRAM-based memory array is capable of implementing logic gates such as majority gate by properly connecting RRAMs [30, 31]. Such capability is called In-Memory Computing, which enables simple computing tasks to be shifted from CPUs to memories. Since long memory access time becomes a major bottleneck in accelerating modern CPU-based systems, such computing paradigm provides a promising solution. More than boolean logic, RRAMs can also realize multi-value logic thanks to its tunable resistance. By adjusting programming current, RRAMs can achieve resistance between HRS and LRS, which is a unique advantage of RRAMs over other NVM technologies, such as Magnetoresistive Random Access Memories (MRAMs) [39] and Phase-Change Random Access Memories (PCRAMs) [40]. Such resistive characteristic allow RRAMs to model the states of a neuron in human brain, which is the basis of Neuromorphic Computing. Furthermore, the stochasticity in resistive switching mechanism leads to that resistance of RRAMs is different from cycle to cycle [1]. As a result, RRAMs can be employed in PUF designs as the key to encrypt hardware designs.

In particular, the programmable resistance, non-volatility and BEoL features are attractive to FPGAs, where 90% of area is consumed by volatile memory cells and programmable routing elements. More issues about RRAM-based FPGAs will be discussed in Section 1.3.

### 1.2 Advantages and Challenges for FPGAs

Thanks to their rich programmable resources, FPGAs can implement *any* circuits by appropriately configuring memory cells and thus have two benefits over other implementations, e.g., ASICs:

- (1) Low *Non-Recurring Engineering* (NRE) costs. In addition to design efforts, fabricating an ASIC chip requires heavy NRE fees from silicon manufacturer (for example, > \$1 million for 14nm FinFET technology), covering the cost of making lithography masks, wafer-level packaging and building testing platforms. With FPGAs, not only NRE costs but also design efforts can be saved since implementing circuits only involves programming existing silicon.

- (2) Fast time-to-market. Full fabrication of an ASIC chip typically requires more than 6 weeks while a FPGA can be instantly programmed and deployed in a system. To make things worse, more iterations on designing and fabrication are needed if any problems are detected in the first manufacturing. Short production cycles is compelling nowadays as competition in consumer electronics becomes fierce.

Therefore, once introduced, FPGAs gain popularity in low volume applications where ASIC manufacturing cost is extremely high. Recent years witness FPGA's expansion in medium or even high volume applications, i.e., co-processors, thanks to their programmable and parallel nature. FPGAs can efficiently parallelize algorithms that are hard for *Central Processing Unit* (CPU) + *Graphic Processing Unit* (GPU) platforms, such as machine learning and video encoding/decoding. An representative example is Microsoft's Bing Search Engine, which employs CPU + FPGA platforms and achieves  $40 \times$  speed-up [13, 14].

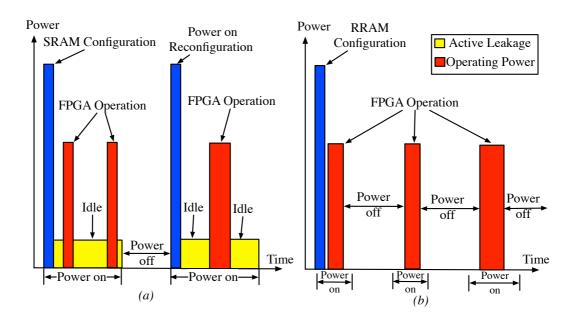

Despite their success, FPGAs are facing challenges from their physical limitations generally preventing them to embrace the IoT era. Programmable routing multiplexers in FPGAs have higher resistance and capacitance than metal wires and also drive more fanouts to guarantee routability, consuming more area and reducing circuit speed. Intensive usage of routing multiplexers introduces more signal activities, causing significant power overhead. To reduce power consumption, FPGAs have to operate at low supply voltage but sacrifice performance because speed of transistors have to degrade when working voltage decreases [41, 42, 43]. Using volatile memory technology, i.e., SRAMs, forces FPGAs to lose configurations when powered down and to be reconfigured at each power on. Such drawback leads to embarrassment in using FPGA-based embedded systems, as illustrated in Fig. 1.2(a): Power-off has to pay additional reconfiguration time and energy next time wake up. Otherwise, power-on burns more power and reduce battery cycle. To continue the success in future, it is worthwhile to advance FPGA technology by overcoming these physical limitations.

### 1.3 Opportunities in RRAM-based FPGAs

RRAM-based technology can bring three fundamental advancements to FPGA architectures, meeting the low-power demands of IoT:

(1) Non-volatility of RRAMs allows FPGAs to be frequently switched on and off without the additional reconfiguration time and energy, as depicted in Fig. 1.2(b). When powered down, RRAM-based FPGAs can hold configurations and consume zero leakage power. Such "Normally *off*, Instantly *on*" property can be achieved by simply replacing SRAMs with RRAMs [25].

Figure 1.2 - Power consumption of (a) a SRAM-based FPGA and (b) a RRAM-based FPGA.

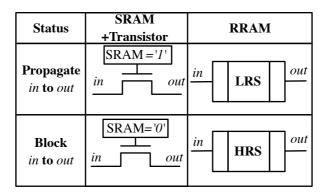

- (2) Fig. 1.3 illustrates that *Low Resistance State* (LRS) and *High Resistance State* (HRS) of RRAMs can be exploited to replace pass-gate logic in programmable routing multiplexers and propagate datapath signals [9, 26, 27, 28]. Combining functionality of memory and pass-gate logic in one unique device, RRAMs can narrow the gap between programmable routing multiplexers and long metal wires. Replacing both SRAMs and pass-gate logics, RRAMs greatly reduce area since they are fabricated on the top of transistors. Implanting RRAMs into datapaths leads to less parasitic capacitance than SRAM-based multiplexing structures, contributing to smaller delay [3]. RRAM-based implementations enable area and speed of programmable routing multiplexers to be comparable or even smaller than a long metal wire, fundamentally changing the cost functions considered in FPGA architectures [28].

- (3) RRAMs have stable resistances when exposed below programming threshold voltage. As

Figure 1.3 – Use SRAM + transistors or RRAMs to propagate and block datapath signals.

long as the working voltage is kept lower than threshold voltage of RRAMs, RRAM-based circuits and systems can exhibit resistive property independent from their work voltage, beyond the limitations on transistors [6]. Hence, using RRAMs in datapaths can have a better trade-off between power and delay than transistors. For instance, RRAM-based circuits operating in the near- $V_t$  regime keep the same performance level as if they were operated at a nominal working voltage, while their power consumption is sharply reduced. Overall, the energy efficiency of FPGAs can be profoundly improved when adapted to RRAM technology [28].

Note that ASICs cannot benefit large improvements from RRAMs as FPGAs, because they seldom use programmable routing multiplexers . Therefore, RRAM-based programmable routing multiplexers open an exclusive opportunity for FPGAs to catch up with ASICs in performance and power. Furthermore, physical features of RRAMs may also expand FPGA's application fields. For example, FPGAs would become popular in aerospace applications since RRAMs are more robust to high-energy radiations than SRAMs.

### 1.4 Contributions and Organization

This thesis provides a thorough study of the fundamentals of RRAM-based FPGAs, starting from essential circuit designs, i.e., programming structures to architecture-level optimizations and prototyping with novel *Electrical Design Automation* (EDA) tools. In order to reveal important characteristics of RRAM-based FPGAs, our researches are conducted in three aspects: circuit design, architecture exploration tool development and architecture-level optimizations.

The rest of this thesis is organized as follows.

Chapter 2 provides background knowledges covering

- (1) RRAM technology: We explain working principles, electrical characteristics and unique technology features of RRAMs, which bring both benefits and challenges to RRAM-based circuit designs.

- (2) modern FPGA architectures: We describe basic principles and important enhancements in modern FPGAs, which are the baseline FPGA architecture considered in Chapter 5.

- (3) previous works about RRAM-based circuit designs and FPGA architectures: We analysis significance and limitations of circuit topologies, including memory cells, flip-flops and routing multiplexers.

- (4) FPGA architecture exploration tools: We introduce EDA techniques of current state-of-art academic tool, i.e., VPR [44] and discuss limitations of power analysis with analytical models.

Chapter 3 aims to propose efficient RRAM-based programming circuits and routing multiplexers. The RRAM-based circuits are studied through both theoretical analysis and electrical simulations with physical design considerations. A low  $R_{LRS}$  is commonly considered as the key to guarantee high-performance for RRAM-based circuits. This chapter argues that the high-performance and energy-efficiency of RRAM-based circuits are actually impacted by many other factors, e.g., programming transistors, well organization and physical location of RRAMs. The first study is about how to program RRAMs into LRS with transistors efficiently. Most popular programming structure, i.e., 2T(ransitor)1R(RAM), cannot leverage the full driving strength of transistors, which potentially causes low circuit speed due to a higher  $R_{LRS}$  than expected. A more efficient programming structure, namely 4T(ransitor)1R(RAM), is proposed and it demonstrate significant improvements in programming current, guaranteeing a low  $R_{LRS}$ . Experimental results prove that using pairs of p-type and n-type transistors are better in driving programming current and also more flexible to diverse RRAM devices, than purely using n-type transistors. By exploiting 4T1R, high-performance and low-power RRAM-based routing multiplexer designs are proposed by considering various physical design parasitics, such as intrinsic capacitance of RRAMs and well organization. Chapter 3 draws three crucial conclusions:

- (a) despite from  $R_{LRS}$ , parasitics of programming transistors is another important factor to guarantee high-performance for RRAM-based circuits. To obtain the best trade-off between  $R_{LRS}$  and parasitics of programming transistors, programming transistor sizing technique is proposed. Experimental results validate that best performance is often achieved with a  $R_{LRS}$  larger than its lowest value.

- (b) By sharing programming transistors in multiplexing structure, performance of RRAM-based routing multiplexer is underlinear to input size, encouraging the use of large multiplexers. Actually, in large RRAM-based routing multiplexer, circuit design topology becomes the major source of high-performance, rather than a low  $R_{LRS}$ .

(c) When RRAMs are embedded in datapath, performance of RRAM-based circuits is not sensitive to working voltage. As a result, operating at near- $V_t$  regime, RRAM-based circuits can keep the same performance level as nominal working voltage, meanwhile their power consumption is sharply reduced. This implies outstanding energy-efficiency and can be generalized to any circuit with RRAMs in datapaths.

With a commercial 40nm technology, we investigate area, delay and power improvements of RRAM-based multiplexing structure by comparing to best SRAM-based implementations. To ensure the accuracy of comparisons, layouts of RRAM-based and SRAM-based routing multiplexers are generated with industrial EDA tools, i.e., Cadence Virtuoso [45] and layout-level parasitic effects are back-annotated in electrical simulations. We believe that the conclusions are generic and instructive when developing novel RRAM-based circuits.

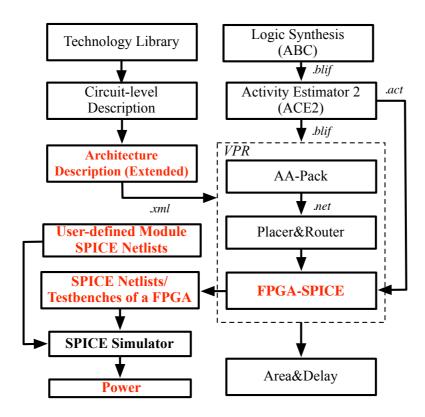

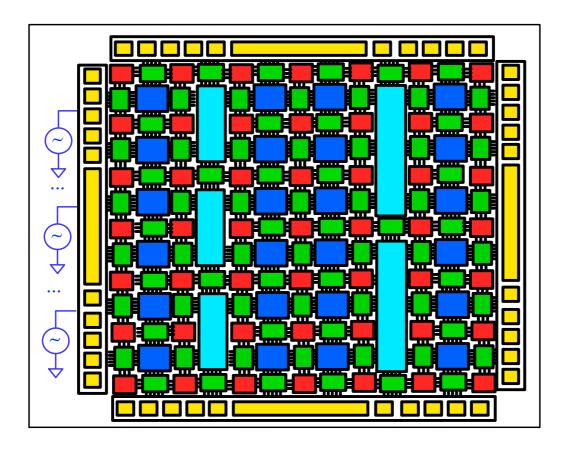

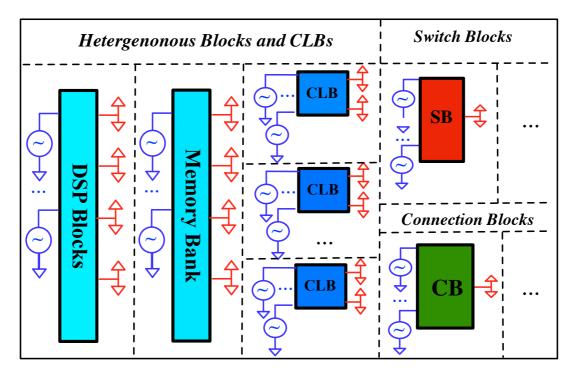

Chapter 4 introduces generic FPGA architecture exploration tool, FPGA-SPICE, for emerging technologies. Current state-of-art FPGA architecture exploration tool, i.e., VPR [44, 46], evaluates area, delay and power with analytical models, which cannot accurately capture the trends of FPGAs based on emerging technologies, such as RRAMs. In addition, VPR provides limited support in prototyping novel FPGA architecture. FPGA-SPICE is developed to enable accurate power analysis and fast prototyping for diverse FPGA architectures, including both SRAM-based and RRAM-based. FPGA-SPICE can auto-generate Simulation Program with Integrated Circuit Emphasis (SPICE) netlists, modeling a full FPGA fabric. With SPICE netlists and electrical simulator, i.e., HSPICE [47], accurate power analysis can be conducted. To accurate model physical designs in SPICE netlists, FPGA-SPICE extends the FPGA architectural description language [48] by providing rich transistor-level modeling parameters. Large SPICE netlist, e.g., the one containing a full FPGA fabric, requires a long simulation time. FPGA-SPICE provides different levels of testbenches and techniques in split large SPICE netlists, in order to obtain better trade-off between simulation time and accuracy. In addition, FPGA-SPICE is also capable of auto-generating synthesizable Verilog netlists containing a full FPGA fabric. Verilog netlists can be used to verify the functionality of FPGA designs and also allows engineers to prototype FPGA architectures through a semi-custom design flow. FPGA-SPICE can be useful in many research topics, including but not limited to the following. The power results from FPGA-SPICE can be a baseline when examining the accuracy of analytical power models for FPGA. The accurate power results are an important benchmarking metric when evaluating novel FPGA architecture. SPICE netlists help validating the functionality and performance of circuit designs based on emerging technologies. Synthesizable Verilog netlists simplify the processes in examining the feasibility of novel FPGA architectures.

**Chapter 5** focus on architecture-level optimizations in FPGA to leverage the potential of RRAM-based multiplexers proposed in Chapter 3. The architectural parameters, routing architectures and buffering strategy are modified to exploit the high-performance of large RRAM-based multiplexers. We propose that local routing architecture should be unified to connection blocks, in order to achieve high-performance when using RRAM-based multiplexers. Connectivity parameters  $F_s$  and best length of routing wire L should be tweaked because

RRAM-based multiplexers are faster in delay than long metal wires. In addition, we propose configuration circuits for the novel RRAM-based FPGA architecture and verify its efficiency with FPGA-SPICE. With cutting-edge EDA tools, VPR and FPGA-SPICE, we believe that the architectural-level results are realistic enough to validate the area, delay and power benefits of RRAM-based FPGAs. We believe that the methodology in architecture evaluation can be generalized to developing FPGA architectures based on emerging technologies.

**Chapter 6** summarizes important conclusions in circuit designs, FPGA-SPICE and RRAM-based FPGA architectures. It concludes what is the basis of high-performance and energy-efficiency of RRAM-based FPGAs, and also provides suggestions for future work.

**Appendix A** includes an example of modern FPGA architectures modelled by FPGA-SPICE architecture description language, which is also the baseline FPGA architecture considered in this thesis.

## 2 Background and Previous Works

As motivated in Chapter 1, RRAMs are promising to advance FPGA technology. The research on RRAM-based FPGA requires a wide range of background knowledge including RRAM technology, circuit designs, FPGA architecture and EDA techniques. Without any of these, evaluating RRAM-based FPGAs would not be possible with a proper level of accuracy. This chapter aims at providing the sufficient background information required for studying RRAM-based FPGAs and therefore consists of four parts. Section 2.1 introduces *Resistive Random Access Memory* (RRAM) technology, covering device structures, physical mechanism and electrical characteristics. These important features of RRAMs help us understanding their potentials in circuit designs. Section 2.2 presents detailed conventional FPGA architectures, including a few crucial architectural enhancements, circuit design topologies and memory technology. These details provide a solid foundation for developing RRAM-based FPGAs in Chapter 5. Section 2.3 reviews previous works about RRAM-based circuit designs and FPGA architectures, which stands as baseline in Chapter 3 and Chapter 5. Last but not least, we discuss current state-of-art FPGA architecture exploration tools and their limitations especially in terms of power analysis, motivating us to develop FPGA-SPICE in Chapter 4.

### 2.1 RRAM Technology

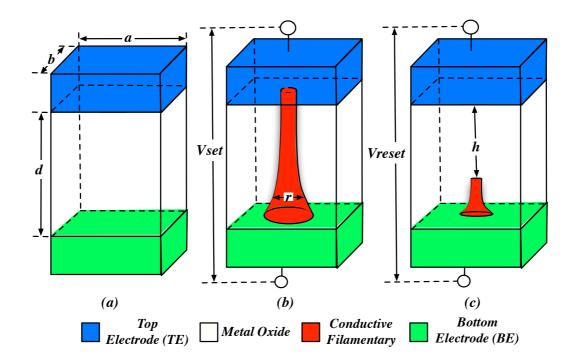

Resistive Random Access Memory (RRAM) device technology typically relies on a three-layer material stack, namely a Metal-Insulator-Metal (MIM) structure [1]. As depicted in Fig. 2.1(a), a RRAM cell is a two-terminal device, consisting of a Top Electrode (TE), a metal oxide insulator and a Bottom Electrode (BE). RRAMs can be programmed into two stable resistance states, a Low Resistance State (LRS) and a High Resistance State (HRS) respectively by modifying the conductivity of the metal oxide layer. Applying a combination of programming voltages and currents between TE and BE can trigger switching events between HRS and LRS. The switching event from HRS to LRS is called the "set" process. Conversely, the switching event from LRS to HRS is called the "reset" process. We denote the resistance of a RRAM in LRS and HRS as  $R_{LRS}$  and  $R_{HRS}$  respectively.

Figure 2.1 – (a) RRAM in pristine state; (b) RRAM in Low Resistance State (LRS); (c) RRAM in High Resistance State (HRS).

Figure 2.2 – I-V characteristic of (a) a URS RRAM; (b) a BRS RRAM.

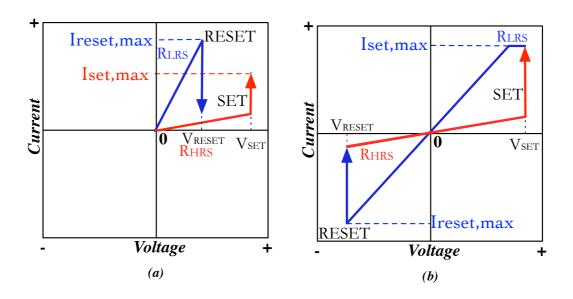

In terms of the polarity of programming voltages, RRAMs can be categorized into *Unipolar Resistive Switching* (URS) and *Bipolar Resistive Switching* (BRS) [1]. Fig. 2.2(a)(b) compare

the I-V curves of URS and BRS RRAMs. Take the example in Fig. 2.2(a), resistive switching of URS RRAMs depends on the amplitude of  $V_{set}$  and  $V_{reset}$  but not the polarity, in order to trigger **set** and **reset** processes. In contrast, BRS RRAMs account on the polarity as well as the amplitude of  $V_{set}$  and  $V_{reset}$  in programming. Take the example in Fig. 2.2(b), a set process can only be triggered by a positive programming voltage, while a subsequent reset process can only be invoked by a negative programming voltage. The minimum programming voltage inducing a positive programming current is defined as  $V_{set}$ , while the minimum programming voltage leading to a negative programming current is  $V_{reset}$ . In principle, for both types of RRAMs, a programming process can only be triggered by a proper programming voltage while the achieved  $R_{LRS}$  and  $R_{HRS}$  are determined by the provided programming current. The rest of this thesis will focus on BRS RRAMs because that they are widely adopted in RRAM-based FPGA researches.

In order to **set/reset** the RRAM into a stable resistance state, programming voltages should be applied for a given time [1]. The minimum pulse width of programming voltage determines the writing speed of the RRAM [1]. Besides, RRAMs should be able to afford a reasonably large number of writing operations, expressed by the endurance [1], and also should be able to maintain the resistance state for a long period without degradation, expressed by the retention [1].

In the following subsections, we present in-depth knowledge about the RRAM technology from five major aspects: resistive characteristics (subsection 2.1.1), capacitive properties (subsection 2.1.2), fabrication issues (subsection 2.1.4), process variations (subsection 2.1.5) and material engineering (subsection 2.1.6).

### 2.1.1 Resistive Characteristics