# **Algorithmic Verification of Component-based Systems**

# THÈSE N° 7753 (2017)

PRÉSENTÉE LE 6 JUIN 2017

À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS LABORATOIRE D'ANALYSE ET DE RAISONNEMENT AUTOMATISÉS PROGRAMME DOCTORAL EN INFORMATIQUE ET COMMUNICATIONS

# ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Qiang WANG

acceptée sur proposition du jury:

Prof. A. Lenstra, président du jury Prof. V. Kuncak, Dr S. Bliudze, directeurs de thèse Dr A. Cimatti, rapporteur Prof. S. Bensalem, rapporteur Prof. M. Odersky, rapporteur

The best way out is always through.

— Robert Frost

To my family...

# **Acknowledgements**

I would like to thank my advisor Prof. Joseph Sifakis, for giving me the opportunity to join his research group in EPFL, and also his guidances and support on my graduate study. This work would not have been possible without his technical and moral supports. He introduced me to the field of formal methods, and opened doors for me in the research community. His enthusiastic supervision will long be a source of encouragement to me. I would also like to thank Dr. Simon Bliudze, my co-advisor, for his countless explanations and everything he did to guide me through the PhD. I am also grateful to Prof. Viktor Kuncak, for hosting me in the last few months and giving me the chance to finish my PhD. Many thanks to secretary Mrs Ariane Staudenmann and Mrs Sylvie Jankow for the organizations of my study. Thanks for being patient with my stubbornness!

I want to express my deepest gratitude to Dr. Alessandro Cimatti, who offered me the opportunity to study in his group for a few months. It was a great pleasure for me to work closely with Dr.Alessandro Cimatti, Dr.Marco Roveri and Dr.Sergio Mover. I have learned a lot from them and I could not have this work done without their help. Thanks to Alessandro again for taking time to review this dissertation. I also want to thank Prof.Helmut Veith, Dr.Igor Konnov and Dr.Tomer Kotek for sharing their thoughts and insights on formal verification. It was a wonderful experience and a very productive collaboration to work with them. I am also grateful to the other jury members Prof.Martin Odersky, Prof.Arjen Lenstra, Prof.Saddek Bensalem for taking time to serve my defense and review this dissertation.

I would like to take this opportunity to thank my family for their constant moral support. I want to give my special appreciations to Dr.Tongkai Zhao for providing me the opportunity to study abroad, to Prof.Chaojing Tang, Dr.Chao Feng, Dr.Xingtong Liu for helping me with the business in China, and to Prof.Mingsheng Ying for his kind recommandations. Last but not least, many thanks to the talented students in Prof.Sifakis's group Eduard Baranov, Anastasia Mavridou, Alina Zolotukhina, Stefanos Skalistis, Wajeb Saab, and my friends Lin Yuan, Xing Bi, Fengyun Liu, Weitian Zhao, Bin Zhang, Zhicong Huang, Shiming Ou, Mengjun Li, Hua Gao, Samantha Meylan, Arthur Meylan, Marguerite Delcourt, Yanguang Yang and many others with whom I have shared the good moments over the years. Thanks to Benjamin Wesolowski for proofreading the French abstract, and Sebastian Stich, Philippe Heer for proofreading the German abstract. To whom I may have forgotten to mention here, I owe you a sincere apology and thank you!

# **Abstract**

This dissertation discusses algorithmic verification techniques for concurrent component-based systems modeled in the Behavior-Interaction-Priority (BIP) framework with both bounded and unbounded concurrency.

BIP is a component framework for mixed software/hardware system design in a rigorous and correct-by-construction manner. System design is defined as a formal, accountable and coherent process for deriving trustworthy and optimised implementations from high-level system models and the corresponding execution platform descriptions. The essential properties of a system model are guaranteed at the earliest possible design phase, and a correct implementation is then automatically generated from the validated high-level system model through a sequence of property preserving model transformations, which progressively refines the model with details specific to the target execution platform.

BIP comes with a well-defined formal modeling language and a toolchain to support the rigorous system design. The BIP modeling language offers a three-layered modeling mechanism, i.e. Behavior, Interaction, and Priority for constructing complex system behavior and architectures. Behavior is characterized by a set of components, which are formally defined as automata extended with local data variables. Interaction specifies the multiparty synchronization of components, among which data transfer may take place. Priority can be used to schedule the interactions or resolve conflicts when several interactions are enabled simultaneously. The key principle of this three-layered modeling mechanism is the separation of concerns, i.e. system behavior is captured by a set of components, and system coordination is modeled by interactions and priorities.

In BIP, algorithmic verification techniques are applied to ensure the essential safety properties of the system designs. The first major contribution of this dissertation is an efficient safety verification technique for BIP system models, where the number of participating components is fixed and the data variables can have infinite domains, but their manipulation is limited to linear arithmetic. The key insight of our technique is to take advantage of the structure features of the BIP system and handle the computation in the components and coordination between the components in the verification separately. On the computation level, we apply the state-of-the-art counterexample abstraction techniques to reason about the behavior of components and explore all the possible reachable states; while on the coordination level, we exploit both partial order techniques and symmetry reduction techniques to handle the state space explosion problem due to concurrency, and reduce the redundant interleavings of concurrent interactions. We have implemented the proposed techniques in a prototype tool

### Acknowledgements

and carried out a comprehensive performance evaluation on a set of BIP system models.

The second major contribution of this dissertation is a uniform design and verification framework for parameterized systems based on BIP. Parameterized systems are systems consisting of homogeneous processes, and the parameter indicates the number of such processes in the system. A parameterized system, therefore, describes an infinite family of systems, where instances of the family can be obtained by fixing the value of the parameter. Verification of correctness of such systems amounts to verifying the correctness of every member of the infinite family described by the system.

First of all, we propose the first order interaction logic (FOIL) as a formal language for parameterized system architectures and communication primitives. This logic is powerful enough to express architectures found in distributed systems, including the classical architectures: token-passing rings, rendezvous cliques, broadcast cliques, rendezvous stars. We also identify a fragment of FOIL that is well-suited for the specification of parameterized BIP systems and prove its decidability. Second, we provide a framework for the integration of mathematical models from the parameterized model checking literature in an automated way. With our new framework, we close the gap between the mathematical formalisms and algorithms from the parameterized verification research and the practice of parameterized verification, which is usually done by engineers who are not familiar with the details of the literature. Finally, we provide a preliminary prototype implementation of the proposed framework. Our prototype tool takes a parameterized BIP design as its input and identifies the classical model checking results which can be applies to this BIP design.

Keywords: Component-based design, Concurrent system, Model checking, Algorithmic verification, Parameterized verification, Predicate abstraction, Partial order reduction, Symmetry reduction, Well-structured transition system

# Zusammenfassung

Diese Dissertation diskutiert algorithmische Verifikationstechniken für parallel laufende komponenten basierte Systeme, die im BIP-Framework (Behavior, Interaction, Priority) mit sowohl begrenzter als auch unbegrenzter Parallelität modelliert sind.

BIP ist ein Komponenten framework für gemischte Software/Hardware Systementwicklung welches mit einer rigorosen konstruktionsbegleitenden Korrektur ausgestattet ist. Systementwicklung ist definiert als ein formaler, rechenschaftspflichtiger und kohärenter Prozess zur Ableitung vertrauenswürdiger und optimierter Implementierungen aus hochrangigen Systemmodellen und den entsprechenden Ausführungsplattformbeschreibungen. Die wesentlichen Eigenschaften eines Systemmodells werden in der frühestmöglichen Entwicklungsphase garantiert und eine korrekte Implementierung erfolgt dann automatisch aus dem zertifizierten hochrangigem Systemmodell durch eine Sequenz von zielplattformspezifischen Transformationen, welche die Modelligenschaften bewahren und das Modell schrittweise verfeinern.

BIP ist mit einer klar definierten formalen Modelliersprache und einer Werkzeugkette zur Unterstützung der rigorosen Systementwicklung ausgestattet. Die BIP-Modellierungssprache bietet einen dreischichtigen Modellierungsmechanismus, d.h. Verhalten, Interaktion und Priorität, für den Aufbau komplexer Systemverhalten und Architekturen. Das Verhalten zeichnet sich durch einen Satz von Komponenten aus, welche formal als Automaten, erweitert mit linearer Arithmetik, definiert sind. Interaktion gibt die Multi-party Synchronisation von datenübertragender Komponenten an. Priorität kann verwendet werden um die Interaktionen zu planen oder Konflikte zu lösen, wenn mehrere Interaktionen gleichzeitig aktiviert werden. Das Hauptprinzip dieses dreischichtigen Modellierungsmechanismus ist die Trennung von Aufgaben, d.h. das Systemverhalten wird durch einen Satz von Komponenten erfasst und die Systemkoordination wird durch Interaktionen und Prioritäten modelliert.

Im BIP werden algorithmische Verifikationstechniken angewendet um die wesentlichen Sicherheitseigenschaften der Systementwicklung zu gewährleisten. Der erste wesentliche Beitrag dieser Dissertation ist eine effiziente Sicherheitsüberprüfungstechnik für BIP-Systemmodelle mit einer festen Anzahl an teilnehmenden Komponenten. Die Schlüsseleigenschaft unserer Technik ist, dass sie die Struktur BIP-Systeme nutzt um die Berechnung und Koordination bei der Überprüfung separat zu behandeln. Auf der Berechnungsstufe wenden wir die State-of-the-Art-Gegenbeispiel-Abstraktionstechniken an, um das Verhalten der Komponenten zu begründen und alle möglichen erreichbaren Zustände zu untersuchen. Auf der Koordinationsebene nutzen wir Halbordnungs- und Symmetriereduktionstechniken um das Zustandsraum-Explosions-Problem aufgrund von Parallelität zu behandeln und die redun-

### Acknowledgements

danten Wechselwirkungen von gleichzeitigen Interaktionen zu reduzieren. Wir haben die vorgeschlagenen Techniken in einem Prototyp-Tool implementiert und eine umfassende Performanceevaluierung auf einem Satz von BIP-Systemmodellen vollzogen.

Der zweite Hauptbeitrag dieser Dissertation ist ein einheitliches Entwicklungs- und Verifizierungs- Tool für parametrisierte BIP-Systeme. Parametrisierte Systeme sind Systeme, die aus homogenen Prozessen bestehen, wobei der Parameter die Anzahl solcher Prozesse im System angibt. Ein parametrisiertes System beschreibt daher eine unendliche Familie von Systemen, in welcher Instanzen der Familie durch Festlegung des Parameters erhalten werden. Die Überprüfung der Fehlerfreiheit solcher Systeme beläuft sich auf das Überprüfen der Fehlerfreiheit jedes Mitglieds der unendlichen Familie, die durch das System beschrieben wird.

Zunächst schlagen wir die Interaktionslogik erster Ordnung als formale Sprache für parametrisierte Systemarchitekturen und Kommunikationsprimitive vor. Diese Logik ist leistungsfähig genug um Architekturen in verteilten Systemen auszudrücken, darunter die klassischen Architekturen wie Token-Passing Ringe, Rendezvous Cliquen, Broadcast Cliquen und Rendezvous Stars. Wir identifizieren auch ein Fragment der Interaktionslogik erster Ordnung welches gut geeignet ist für die Beschreibung von parametrisierten BIP-Modellen und beweisen seine Entscheidbarkeit. Zweitens stellen wir ein Framework für die automatische Integration von mathematischen Modelle aus der parametrisierten Modellprüfungsliteratur bereit. Mit unserem neuen Framework schliessen wir die Kluft zwischen den mathematischen Formalismen und Algorithmen aus der parametrisierten Verifikationsforschung und der Praxis der parametrisierten Verifikation, die in der Regel von Ingenieuren durchgeführt wird, die mit den Details der Literatur nicht vertraut sind. Schliesslich stellen wir eine vorläufige Prototypenimplementierung des vorgeschlagenen Frameworks zur Verfügung. Unser Prototyp-Tool nimmt ein parametrisiertes BIP-Design als Eingabe und identifiziert die klassischen Modellverifikationsresultate, welche auf dieses BIP-Design angewendet werden können.

Stichwörter: Komponentenbasiertes Design, Gleichzeitiges System, Modellprüfung, Algorithmische Verifikation, Parametrierte Verifikation, Eigenschafts Abstraktion, Partielle Auftragsreduktion, Symmetrieverkleinerung, Gut strukturiertes Übergangssystem

# Résumé

Cette dissertation traite des techniques de vérification algorithmique pour les systèmes concurrents basés sur les composants, modélisés dans le cadre BIP (Behavior, Interaction, Priority) avec des concurrences bornées et non bornées.

BIP est un framework de composants pour la conception rigoureuse et correcte par construction de systèmes de systèmes logiciels/matériels mixtes. La conception du système est définie comme un processus formel, responsable et cohérent pour obtenir des implémentations fiables et optimisées à partir de modèles de systèmes de haut niveau et des descriptions des plates-formes d'exécution correspondantes. Les propriétés essentielles d'un modèle de système sont garanties à la phase de conception la plus précoce possible et une implémentation correcte est ensuite générée automatiquement à partir du modèle de système de haut niveau certifié par une suite de transformations préservant les propriétés du modèle, qui affine progressivement le modèle avec des détails spécifiques à la plate-forme d'exécution cible.

BIP est livré avec un langage de modélisation formel bien défini et une chaîne d'outils pour soutenir la conception rigoureuse du système. Le langage de modélisation BIP offre un mécanisme de modélisation à trois couches pour construire des comportements et des architectures de systèmes complexes, c'est-à-dire Comportement, Interaction et Priorité. 'Comportement' est caractérisé par un ensemble de composants qui sont formellement définis comme des automates étendus par des variables de données locales. 'Interaction' spécifie la synchronisation multipartite des composants parmi lesquels le transfert de données peut avoir lieu. 'Priorité' peut être utilisée pour planifier les interactions ou résoudre les conflits lorsque plusieurs interactions sont activées simultanément. Le principe clé de ce mécanisme de modélisation à trois couches est la séparation des préoccupations, c'est-à-dire que le comportement du système est capté par un ensemble de composantes, et la coordination du système est modélisée par des interactions et des priorités.

Dans BIP, des techniques de vérification algorithmique sont appliquées pour assurer les propriétés de sécurité essentielles des conceptions du système. La première contribution majeure de cette dissertation est une technique efficace de vérification de la sécurité pour les modèles de systèmes BIP avec un nombre fixe de composants participants. L'idée principale de notre technique est de profiter des fonctionnalités du système BIP et gérer le calcul et la coordination dans la vérification séparément. Au niveau du calcul, nous appliquons les techniques d'abstraction de contre-exemple pour raisonner sur le comportement des composants et explorer tous les états accessibles possibles ; alors qu'au niveau de la coordination, nous exploitons des

### Acknowledgements

techniques d'ordre partiel et de réduction de symétrie pour gérer le problème de l'explosion de l'espace des états en raison de la simultanéité, et réduisons les interrelations redondantes des interactions simultanées. Nous avons implémenté les techniques proposées dans un outil prototype et évalué l'efficacité sur un ensemble de modèles de systèmes BIP.

La deuxième contribution majeure de cette dissertation est un cadre de conception et de vérification uniforme pour les systèmes paramétrés basés sur BIP. Les systèmes paramétrés sont des systèmes consistant en des processus homogènes, où le paramètre indique le nombre de tels processus dans le système. Un système paramétré décrit donc une famille infinie de systèmes où les instances de la famille peuvent être obtenues en fixant le paramètre. La vérification de l'exactitude de ces systèmes revient à vérifier l'exactitude de chaque membre de la famille infinie décrite par le système.

Tout d'abord, nous proposons la logique d'interaction du premier ordre comme langage formel pour les architectures système paramétrées et les primitives de communication. Cette logique est assez puissante pour exprimer les architectures trouvées dans les systèmes distribués, y compris les architectures classiques : anneaux de passage de jetons, cliques de rendezvous, cliques de diffusion, étoiles de rendezvous. Nous identifions un fragment de la logique d'interaction du premier ordre bien adapté à la specification des modèles BIP paramétrés et prouvons sa décidabilité. Deuxièmement, nous fournissons un framework pour l'intégration de modèles mathématiques issus de la littérature sur la vérification de modèles paramétrés de manière automatisée. Avec notre nouveau framework, nous comblons l'écart entre les formalismes mathématiques et les algorithmes de la littérature sur la vérification paramétrée et la pratique de la vérification paramétrer, ce qui est généralement fait par des ingénieurs qui ne sont pas familiers avec les détails de la littérature. Enfin, nous fournissons un prototype préliminaire d'une implémentation du framework proposé. Notre outil prototype prend une conception BIP paramétrée comme entrée et identifie les résultats classiques de vérification de modèle qui peuvent s'appliquer à cette conception BIP.

Mot Clef: Conception de composants, Système concurrent, Vérification de modèles, Vérification algorithmique, Vérification paramétrée, Abstraction de prédicat, Réduction d'ordre partiel, Réduction de symétrie, Système de transition bien structuré

# Contents

| A  | cknov | wledgements                                                        | i    |

|----|-------|--------------------------------------------------------------------|------|

| Al | ostra | ct (English/Français/Deutsch)                                      | iii  |

| Li | st of | figures                                                            | xiii |

| Li | st of | tables                                                             | xv   |

| 1  | Intr  | roduction                                                          | 1    |

|    | 1.1   | Rigorous system design                                             | 2    |

|    |       | 1.1.1 BIP component framework                                      | 3    |

|    |       | 1.1.2 The role of formal verification                              | 5    |

|    | 1.2   | Evolution of formal verification                                   | 6    |

|    | 1.3   | Challenges and contributions                                       | 9    |

|    |       | 1.3.1 Algorithmic verification of systems with bounded concurrency | 10   |

|    |       | 1.3.2 Modeling and verifying systems with unbounded concurrency    | 11   |

|    | 1.4   | Organization of this dissertation                                  | 13   |

| 2  | Pre   | liminary and system model                                          | 15   |

|    | 2.1   | Labeled transition system                                          | 15   |

|    | 2.2   | Invariant verification                                             | 16   |

|    | 2.3   | BIP modeling framework                                             | 17   |

|    |       | 2.3.1 Syntactic BIP model                                          | 18   |

|    |       | 2.3.2 BIP operational semantics                                    | 22   |

|    | 2.4   | Encoding BIP into Symbolic Transition System                       | 24   |

| 3  | Veri  | ification of concurrent systems                                    | 27   |

|    | 3.1   | Abstraction techniques                                             | 27   |

|    |       | 3.1.1 Abstract interpretation                                      | 27   |

|    |       | 3.1.2 Predicate abstraction                                        | 28   |

|    |       | 3.1.3 Counterexample guided abstraction refinement                 | 29   |

|    |       | 3.1.4 Lazy abstraction                                             | 31   |

|    | 3.2   | Partial order reduction techniques                                 | 32   |

|    |       | 3.2.1 Ample set                                                    | 34   |

|    |       | 3.2.2. Stubborn set                                                | 35   |

### **Contents**

|   |     | 3.2.3   | Persistent set                                             | 35           |

|---|-----|---------|------------------------------------------------------------|--------------|

|   |     | 3.2.4   | Partial order reduction for safety properties              | 36           |

| 4 | Von | factio  | n of DID with hounded concurrency                          | 39           |

| 4 |     |         | n of BIP with bounded concurrency abstraction of BIP       | <b>39</b> 40 |

|   | 4.1 | •       |                                                            |              |

|   |     |         | Data structures for verification                           | 40           |

|   |     |         | Main verification algorithm                                | 41           |

|   |     | 4.1.3   | Node expansion                                             | 41           |

|   |     | 4.1.4   |                                                            | 44           |

|   |     | 4.1.5   | Correctness proof                                          | 44           |

|   | 4.2 | Persis  | tent set reduction for BIP                                 | 45           |

|   |     | 4.2.1   | Combining persistent set reduction with lazy abstraction   | 48           |

|   |     | 4.2.2   | Computing persistent set                                   | 50           |

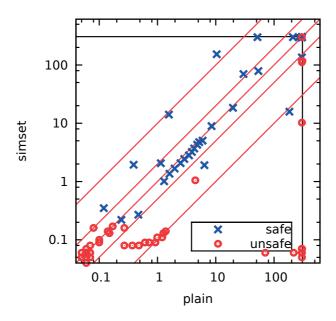

|   | 4.3 | Exper   | imental evaluation                                         | 52           |

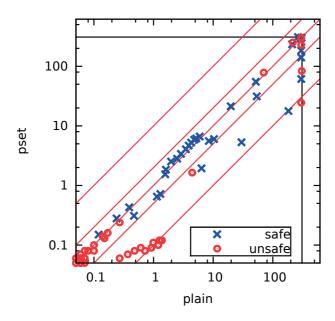

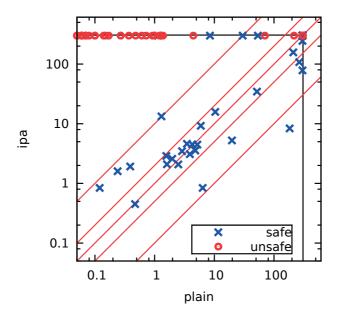

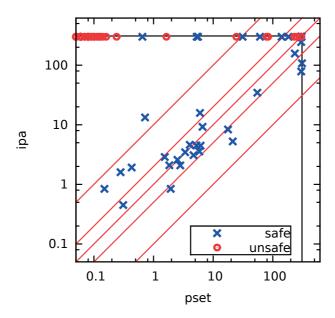

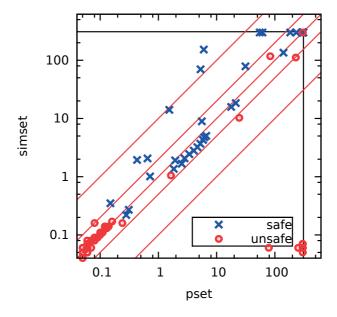

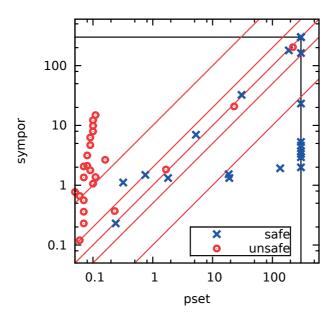

|   |     | 4.3.1   | Comparing lazy abstraction to persistent set reduction     | 53           |

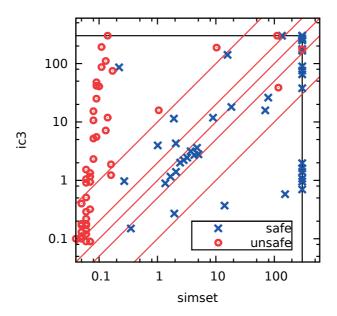

|   |     | 4.3.2   | Comparing to IC3 and IPA                                   | 57           |

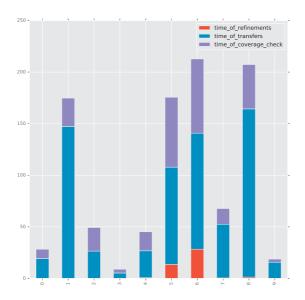

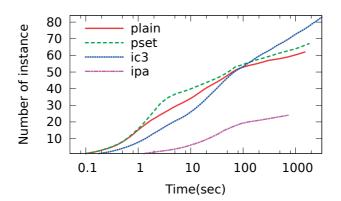

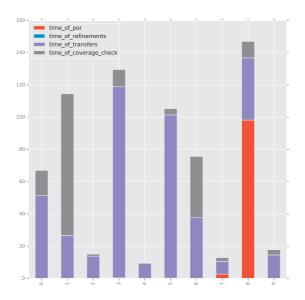

|   |     | 4.3.3   | Cumulative plots                                           | 59           |

|   | 4.4 | Relate  | ed work                                                    | 59           |

| _ | E   | 41 4 .  | -h                                                         | C.F.         |

| 5 |     |         | chniques for improving reductions                          | 65           |

|   | 5.1 |         | taneous set reduction for BIP                              | 66           |

|   |     | 5.1.1   | 0 1                                                        | 66           |

|   |     | 5.1.2   | Combining simultaneous set reduction with lazy abstraction | 67           |

|   |     | 5.1.3   | Computing simultaneous set                                 | 70           |

|   |     |         | Discussions                                                | 72           |

|   | 5.2 | -       | imental evaluation                                         | 73           |

|   |     | 5.2.1   | Comparing to lazy abstraction with reductions              | 73           |

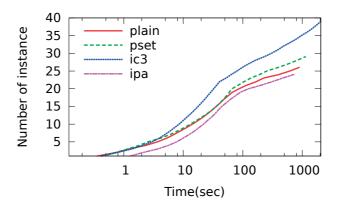

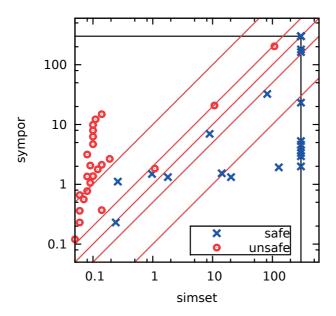

|   |     |         | Comparing to IC3 and IPA                                   | 77           |

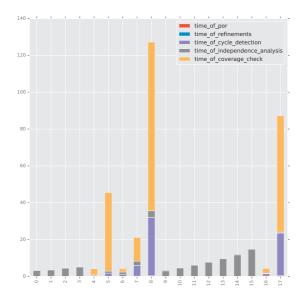

|   |     |         | Cumulative plots                                           | 78           |

|   | 5.3 | Partia  | l order reduction under symmetry                           | 80           |

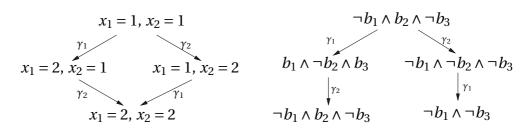

|   |     | 5.3.1   | Motivating example                                         | 81           |

|   |     | 5.3.2   | Symmetry reduction                                         | 82           |

|   |     | 5.3.3   | Persistent set under symmetry                              | 83           |

|   | 5.4 | Exper   | imental evaluation                                         | 86           |

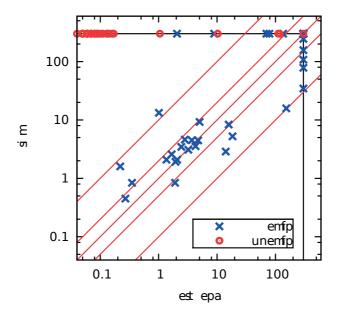

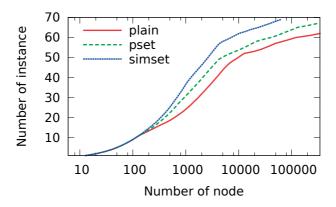

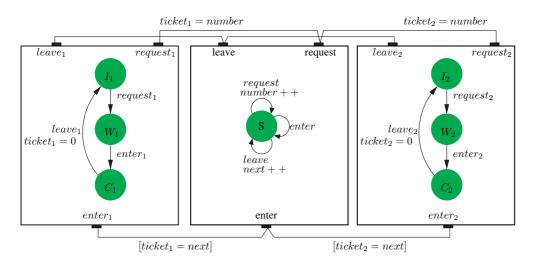

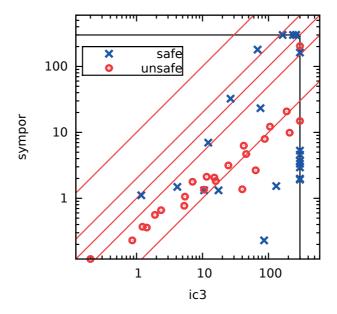

|   |     | 5.4.1   | Scatter plots                                              | 86           |

|   |     | 5.4.2   | Cumulative plots                                           | 90           |

|   | 5.5 | Relate  | ed work                                                    | 90           |

| 6 | Doc | ian ara | d verification of parameterized systems in BIP             | 95           |

| J |     | •       | neterized BIP without priorities                           | 96           |

|   | 0.1 | 6.1.1   | FOIL: First order interaction logic                        | 96           |

|   |     | 6.1.2   | Interactions as FOIL structures                            | 98           |

|   | 6.2 |         |                                                            | 101          |

|   | 0.4 | raran   | TELETIZED INOUELCHECKING                                   | 101          |

|    | 6.2                  | Desidability recults for narrow storing d DID                                | 102 |  |  |

|----|----------------------|------------------------------------------------------------------------------|-----|--|--|

|    | 6.3                  | , i                                                                          | 103 |  |  |

|    |                      | 6.3.1 Well-structured transition system                                      |     |  |  |

|    |                      | 6.3.2 Well-structured parameterized BIP                                      |     |  |  |

|    | 6.4                  | A framework of automated parameterized verification in BIP                   |     |  |  |

|    | 6.5                  | , ,                                                                          | 108 |  |  |

|    |                      | r                                                                            | 110 |  |  |

|    |                      | 6.5.2 Pairwise rendezvous in a clique                                        | 110 |  |  |

|    |                      | 6.5.3 Broadcast in a clique                                                  | 111 |  |  |

|    |                      | 6.5.4 Token rings                                                            | 113 |  |  |

|    |                      | 6.5.5 Pairwise rendezvous in a star                                          | 114 |  |  |

|    | 6.6                  | Prototype implementation and experiments                                     | 115 |  |  |

|    | 6.7                  | Related work                                                                 | 116 |  |  |

| 7  | Con                  | aclusions and perspectives                                                   | 119 |  |  |

|    | 7.1                  |                                                                              | 119 |  |  |

|    | 7.2                  | Perspectives of the future work                                              |     |  |  |

|    |                      | rerepeatives of the fattale work                                             |     |  |  |

| A  | App                  | pendix                                                                       | 123 |  |  |

|    | A.1                  | An ATM transaction protocol in BIP                                           | 124 |  |  |

|    | A.2                  | A leader election protocol in BIP                                            | 126 |  |  |

|    | A.3                  | A quorum consensus protocol in BIP                                           | 127 |  |  |

|    | A.4                  | A railway control protocol in BIP                                            | 129 |  |  |

|    | A.5                  | Statistics for lazy abstraction                                              | 130 |  |  |

|    | A.6                  | Statistics for lazy abstraction with persistent set reduction                | 133 |  |  |

|    | A.7                  | •                                                                            | 136 |  |  |

|    | A.8                  | Statistics for lazy abstraction with persistent set reduction under symmetry |     |  |  |

|    |                      |                                                                              |     |  |  |

| Bi | bliog                | graphy                                                                       | 151 |  |  |

| Cı | Curriculum Vitae 153 |                                                                              |     |  |  |

# **List of Figures**

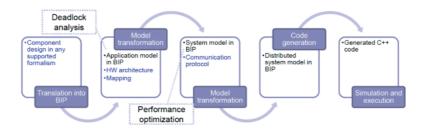

| 1.1  | The BIP instantiation of the rigorous system design flow                                           | 2  |

|------|----------------------------------------------------------------------------------------------------|----|

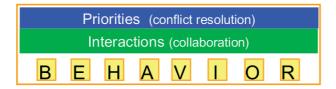

| 1.2  | BIP layered modeling framework                                                                     | 4  |

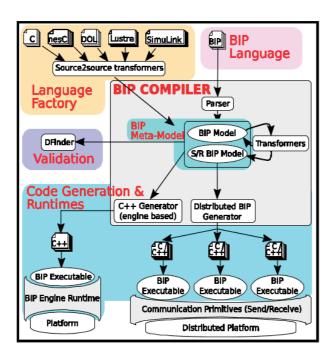

| 1.3  | BIP toolchain                                                                                      | 4  |

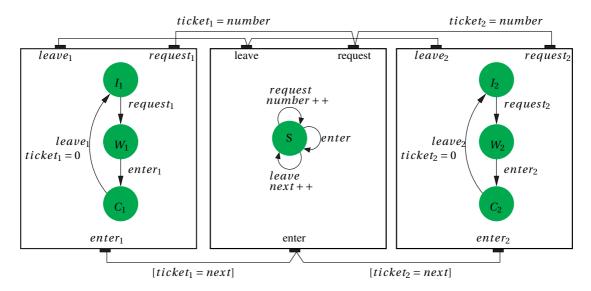

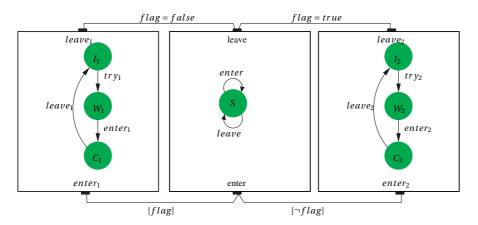

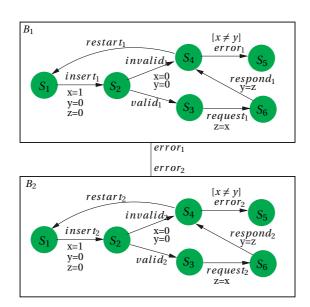

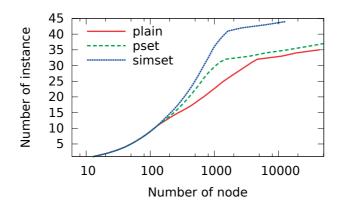

| 2.1  | Ticket mutual exclusion protocol                                                                   | 20 |

| 2.2  | Ticket mutual exclusion protocol in BIP language                                                   | 21 |

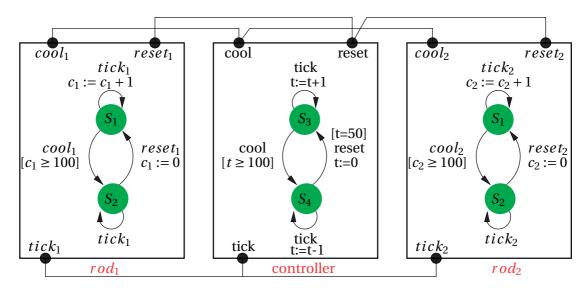

| 2.3  | Temperature Control System in BIP                                                                  | 22 |

| 2.4  | Temperature control system in BIP language                                                         | 23 |

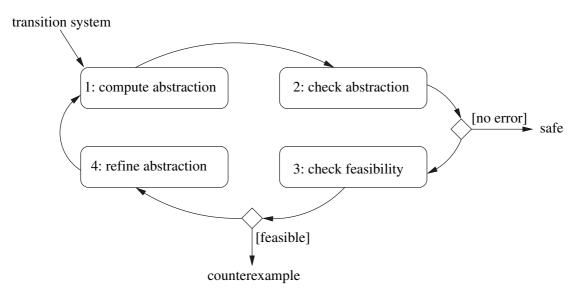

| 3.1  | Counterexample guided abstraction refinement loop                                                  | 30 |

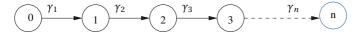

| 3.2  | A counterexample trace                                                                             | 30 |

| 3.3  | Relations between ample, stubborn and persistent sets                                              | 37 |

| 3.4  | An example for illustrating the ignoring problem                                                   | 37 |

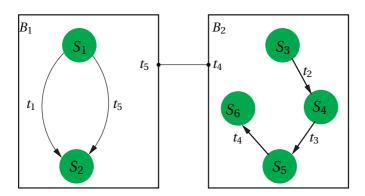

| 4.1  | Example for illustrating partial order reduction for BIP                                           | 46 |

| 4.2  | Example showing independent interactions don't commute on abstract states                          | 47 |

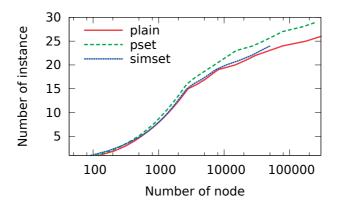

| 4.3  | Lazy abstraction vs. lazy abstraction with persistent set reduction                                | 54 |

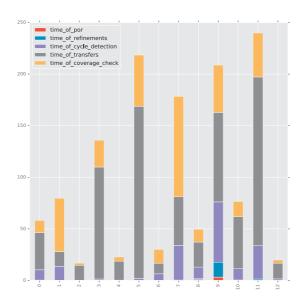

| 4.4  | Runtime of plain lazy abstraction subroutines                                                      | 55 |

| 4.5  | Runtime of lazy abstraction with persistent set reduction subroutines $\ \ldots \ \ldots \ \ldots$ | 56 |

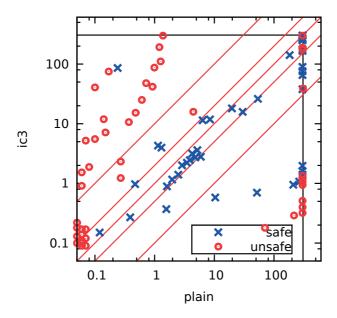

| 4.6  | Lazy abstraction vs. IC3                                                                           | 58 |

| 4.7  | Lazy abstraction with persistent set reduction vs. IC3                                             | 58 |

| 4.8  | Lazy abstraction vs. IPA                                                                           | 60 |

| 4.9  | Lazy abstraction with persistent set reduction vs. IPA                                             | 60 |

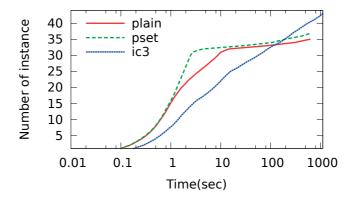

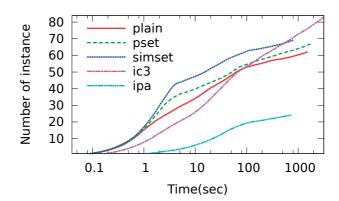

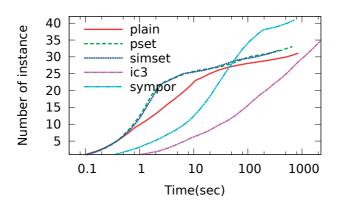

| 4.10 | Cumulative plot of time for all benchmarks                                                         | 61 |

| 4.11 | Cumulative plot of time for safe benchmarks                                                        | 61 |

| 4.12 | Cumulative plot of time for unsafe benchmarks                                                      | 61 |

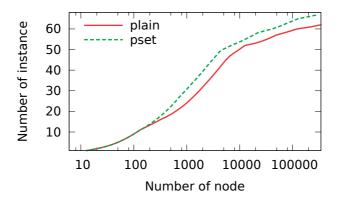

| 4.13 | Cumulative plot of ART size                                                                        | 62 |

| 4.14 | Cumulative plot of ART size for safe benchmarks                                                    | 62 |

| 4.15 | Cumulative plot of ART size for unsafe benchmarks                                                  | 62 |

| 5.1  | The first example for illustrating simultaneous set                                                | 66 |

| 5.2  | The second example for illustrating simultaneous set                                               | 72 |

| 5.3  | Examples for comparing simultaneous and persistent sets                                            | 72 |

| 5.4  | Lazy abstraction vs. lazy abstraction with simultaneous set reduction $\ \ldots \ \ldots \ \ldots$ | 74 |

# **List of Figures**

| 5.5  | Lazy abstraction with persistent set reduction vs. lazy abstraction with simultaneous set |     |

|------|-------------------------------------------------------------------------------------------|-----|

|      | reduction                                                                                 | 74  |

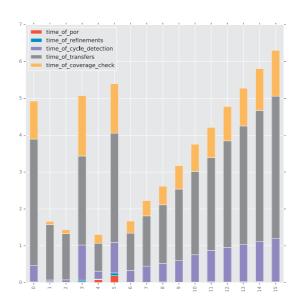

| 5.6  | Runtime of lazy abstraction with simultaneous set reduction subroutines                   | 76  |

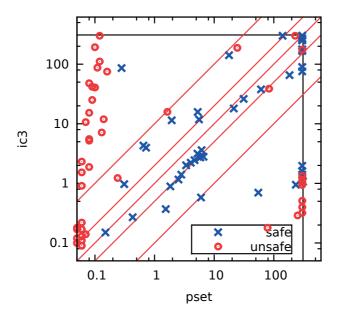

| 5.7  | Lazy abstraction with simultaneous set reduction vs. IC3                                  | 77  |

| 5.8  | Lazy abstraction with simultaneous set reduction vs. IPA                                  | 78  |

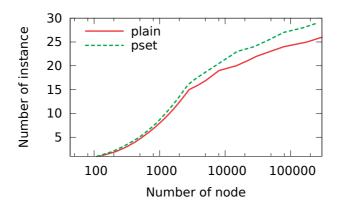

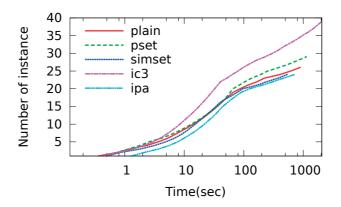

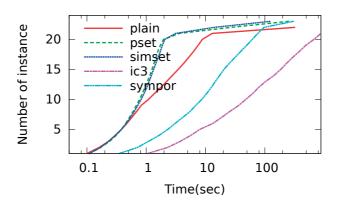

| 5.9  | Cumulative plot of time for all benchmarks                                                | 79  |

| 5.10 | Cumulative plot for safe benchmarks                                                       | 79  |

| 5.11 | Cumulative plot for unsafe benchmarks                                                     | 79  |

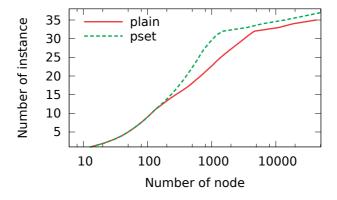

| 5.12 | Cumulative plot of ART size                                                               | 80  |

| 5.13 | Cumulative plot of ART size for safe benchmarks                                           | 80  |

| 5.14 | Cumulative plot of ART size for unsafe benchmarks                                         | 81  |

| 5.15 | Ticket mutual exclusion protocol                                                          | 82  |

| 5.16 | Lazy abstraction vs. lazy abstraction with reduction under symmetry                       | 87  |

| 5.17 | Lazy abstraction with persistent set reduction vs. lazy abstraction with reduction under  |     |

|      | symmetry                                                                                  | 88  |

| 5.18 | Lazy abstraction with simultaneous set reduction vs. lazy abstraction with reduction      |     |

|      | under symmetry                                                                            | 88  |

| 5.19 | IC3 vs. lazy abstraction with reduction under symmetry                                    | 89  |

| 5.20 | Runtime of lazy abstraction with reduction under symmetry subroutines                     | 91  |

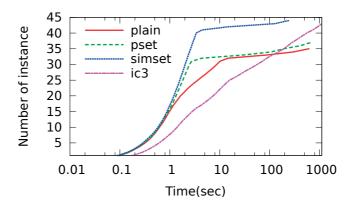

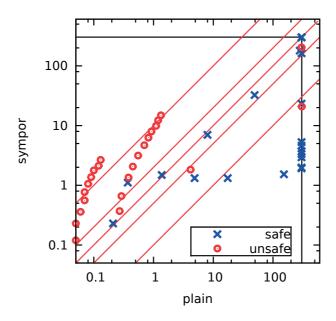

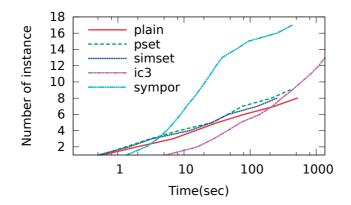

| 5.21 | Cumulative plot of time for all benchmarks                                                | 92  |

| 5.22 | Cumulative plot of time for safe benchmarks                                               | 92  |

| 5.23 | Cumulative plot of time for unsafe benchmarks                                             | 92  |

| 0.1  |                                                                                           | 00  |

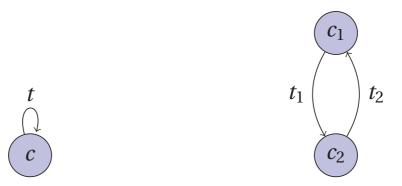

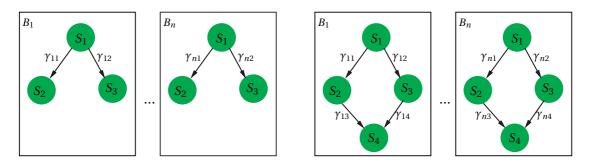

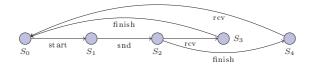

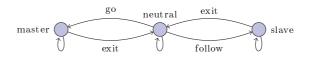

| 6.1  | Component type of Milner's scheduler                                                      | 99  |

| 6.2  |                                                                                           | 100 |

| 6.3  |                                                                                           | 100 |

| 6.4  | Framework of automated parameterized verification in BIP                                  | 109 |

# **List of Tables**

| 4.1 | Percentage of persistent set reduction                                                  | 57  |

|-----|-----------------------------------------------------------------------------------------|-----|

| 5.1 | Percentage of simultaneous set reduction                                                | 75  |

| 5.2 | Percentage of partial order reduction under symmetry                                    | 90  |

| 6.1 | Experimental results of identifying architecture models                                 | 115 |

| A.1 | Verification statistics for lazy abstraction                                            | 132 |

| A.2 | Verification statistics for lazy abstraction with persistent set reduction              | 135 |

| A.3 | Verification statistics for lazy abstraction with simultaneous set reduction $\ \ldots$ | 138 |

| A.4 | Verification statistics for lazy abstraction with persistent set reduction under        |     |

|     | symmetry                                                                                | 140 |

# 1 Introduction

Computer technology has become ubiquitous in daily life. The past few decades witnessed a widespread deployment of embedded systems on controlling communication, transportation and medical systems. The consequences of system failure can transcend mere annoyance and may have profound negative effects on our lives, due to our ever-increasing reliance on embedded systems, both at the personal and the organizational level (e.g. the explosion of the first launch of Ariane 5 <sup>1</sup>). The correctness and robustness of embedded systems are ever more important. Paradoxically, as the embedded system complexity escalates tremendously, current design techniques and tools can hardly ensure sufficiently reliable systems at affordable costs. The development of reliable and robust embedded systems remains a grand challenge in both computer science and system engineering [91, 134]. The main culprit is understood as the lack of rigorous theories and techniques for embedded system design [92].

The design of embedded systems differs radically from pure software design. Embedded system design must account not only for functional properties but also for extra-functional requirements regarding the use of execution platform resources such as time and energy. However, the systems being currently built are based on empirical approaches. Designers use different frameworks, which are only loosely coupled to build sub-systems that are sub-sequently composed into complete systems. The lack of an underlying unifying semantic framework and rigorous theoretical foundations makes it difficult to ensure that the implicit assumptions made during the design of sub-systems are satisfied after integration.

Further, the predictability of the system behaviour is impossible to guarantee at design time and therefore, a costly posteriori validation remains the only means for ensuring the correctness of the design with respect to the functional or extra-functional properties. Despite its high complexity, this posteriori validation usually goes from the implementation level back to model level, which cannot take advantage of the original design and in most cases, would be computationally infeasible for large implementations. Therefore, we need a new design methodology to develop correct implementations of systems in a predictable manner.

<sup>1.</sup> https://en.wikipedia.org/wiki/Ariane\_5

## 1.1 Rigorous system design

Rigorous system design [133, 135] has been proposed in response to the grand challenge of design, manufacture and validation of large scale reliable mixed hardware and software systems (e.g. cyber-physical systems). The main objective of the rigorous system design methodology is to develop the theories, methods and tools for building reliable systems in a predictable manner.

Rigorous system design follows the component-based approach, where complex system models are constructed by assembling simple atomic components with some composition entities. Atomic components are characterized by abstractions that ignore implementation details and only describe behavior relevant to their composition, e.g. transfer functions, interfaces. Composition entities are then used to build complex compound components from atomic ones. Component-based design allows to build large-scale systems in an incremental and predictable manner.

Rigorous system design can also be understood as a formal, accountable and coherent process for deriving trustworthy and optimised implementations from high-level system models and the corresponding execution platform descriptions. The essential properties of system models are guaranteed at the earliest possible design phase using formal verification techniques. Correct implementations are then automatically generated from validated high-level system models through a sequence of property preserving model transformations, which progressively refine the model with details specific to the target execution platform.

Figure 1.1 – The BIP instantiation of the rigorous system design flow

Figure 1.1 illustrates the rigorous system design flow, as it is instantiated in the Behaviour-Interaction-Priority (BIP) framework [19]. One starts by designing the application model, either directly in BIP or through a transformation from a domain specific language. The model consists of a set of atomic components and connectors. Atomic components model the application activities, from the control point of view, as finite state automaton. Each transition of an autamaton has an associated C function call, which realises functional computations and interaction with the environment (e.g. network communication protocols). This allows strict separation of concerns between control and functional behaviour. Connectors define all possible interactions between atomic components. Overall behaviour of the application is defined by the BIP operational semantics and enforced at run-time by the BIP Engine. This allows strict separation of concerns between stateful behaviour of individual components and

stateless coordination of their concurrent execution.

The individual components are verified to prove elementary safety properties, such as absence of local deadlock, and satisfaction of basic requirements. These elementary properties, serve as a basis for the proof of global properties, obtained by construction. Until recently, by-construction correctness provided by the BIP design flow illustrated in Figure 1.1 was limited to the fact that automatically generated executable code was guaranteed to satisfy the properties established on the corresponding BIP models. Correctness of the high-level application model was limited to deadlock freedom or had to be established by current model checking techniques.

The application model is then extended with additional components modeling the target platform to obtain the system model, which is used to perform platform specific analyses and the optimisation of performance through the exploration of the design space (memories, buses, mapping of software components to hardware elements etc.). Finally, the model is enriched with platform specific information (e.g. communication primitives) and, after removing components modelling hardware elements, executable code is automatically generated. Proving that the assumptions made at the modeling level to justify the separation of concerns hold, indeed, at the platform level, guarantees that all the properties established throughout the design process also hold for the generated code.

### 1.1.1 BIP component framework

BIP [19] is a component-based framework for rigorous system design. It addresses the following three main challenges to pursue essentials of the rigorous system design: 1) the development of a uniform modeling framework with well defined semantics for the incremental composition of heterogeneous components; 2) the development of verification methods for essential safety properties in order to guarantee the correctness of the high-level system designs, and 3) the development of automated support for component integration, validation and code generation, meeting the given requirements.

BIP comes with a well defined modeling language and an associated toolset (shown in Figure  $1.3^{\,2}$ ) to implement the rigorous design flow. BIP modeling language provides primitives for building composite components as the composition of simpler components, and it defines a common semantic model that can be used at all stages throughout the design flow. BIP also provides formal verification tools to check the deadlock-freedom of components, as well as advanced techniques to ensure by-construction correctness of the design. In BIP, the implementation (i.e. C++ code) can be automatically generated from the high-level system model using specific code generators by taking into account the specific execution platforms and environment.

<sup>2.</sup> This figure and the subsequent one are from the BIP website http://www-verimag.imag.fr/Rigorous-Design-of-Component-Based.html.

Figure 1.2 – BIP layered modeling framework

BIP language provides a three-layered modeling mechnism as shown in Figure 1.2. It allows building complex system models by coordinating three layers of modeling: 1) Behavior is descirbed by a set of components, each of which is formally specified as a finite state automaton extended with local data variables. Transition labels of the automaton are exported as ports, which are used to define the coordination between components. 2) Interaction specifies the coordination between components. An interaction is formally defined as a finite set of ports, and essentially it specifies a multiparty synchronization of the transitions, whose labels are the connected ports. 3) Priority is used to schedule the interactions or resolve conflicts when several interactions are enabled simultaneously.

BIP has clean operational semantics that describes the behavior of a composite component as the composition of the behaviors of its atomic components. A detailed introduction to BIP modeling language and its semantics is given in Chapter 2.

Figure 1.3 – BIP toolchain

BIP toolset includes the translators that translate various programming models, e.g. Simulink,

Lustre into BIP, and the source-to-source transformers that can transform one BIP model into another, e.g. a Send/Receive BIP model that is used in the distributed environment. It also includes compilers that generate executable code for various dedicated engines. The deadlock-freedom of the system model can be automatically checked, using the dedicated model checker DFinder. Currently, DFinder can only handle systems without data transfer among components. This limitation hampers the practical application of DFinder and of the BIP framework, since data transfer is necessary and common in the design of real-life systems.

#### 1.1.2 The role of formal verification

Being able to check or assert correctness of the system under design using scalable formal verification techniques is an essential requirement in rigorous system design.

As opposed to the logic circuit synthesis and certified code generators for highly critical systems, such as SCADE Suite<sup>3</sup>, most of the system and software design workflows do not combine verification of system models with guarantees that the final system satisfies the verified properties. This is due to the decoupling of modeling and verification tools. The most common workflow consists in verifying or simulating systems with dedicated modeling tools, such as MathLab/Simulink, then manually implementing the resulting solutions. As a result, the final executable code is not guaranteed to respect the verified properties, since errors may be introduced during the manual implementation phase. Another approach consists in extracting models from the implementation code for subsequent validation by existing or dedicated model checkers. This approach, on one hand, does not benefit from designtime analysis. On the other hand, the inevitable post-verification modifications of the system are costly, due to the difficulty of establishing the backward link between the automatically extracted model and the source code.

As discussed above, rigorous system design flow in BIP advocates correct-by-construction design. The system implementation, which is automatically generated executable is guaranteed to satisfy the properties established on the corresponding BIP models. While we still rely on correctness of the individual components to establish by-construction correctness of the global system model. Until recently, correctness of the high-level application model was limited to deadlock freedom. We still lack methods and tools to check general safety requirements of the high-level application model.

Differing from simulation or testing techniques, formal verification provides a rigorous way to prove or disprove that a system model meets the given requirements. The system being checked is usually modeled as a state machine and the property is specified as a formula in some temporal logic. In order to check if the system satisfies the given property, formal verification usually uses an exhaustive search procedure (either explicitly or symbolically) on the state space of the system model to check if the given property is satisfied on every reachable state. If the property is violated, a counterexample is generated as the diagnostics to

<sup>3.</sup> http://www.esterel-technologies.com/products/scade-suite/

help designers correct their designs.

Moreover, the growing power of formal verification tools makes the use of formal methods in complex embedded system design possible, as reported in [122]. Notably, formal verification has been successfully used in industry to help build reliable and secure systems. For instance, as reported in [123], formal methods have been successfully used at Amazon Web Services to solve difficult design problems and to build reliable web services. The authors reported that at Amazon seven teams have used TLA+ <sup>4</sup> to find subtle but serious bugs that they would not have found using other techniques, and also to devise optimized complex algorithms without sacrificing quality. Another example is the High-Assurance Cyber Military Systems(HACMS) program launched by Defense Advanced Research Projects Agency (DARPA) to create technologies to make networked embedded systems dramatically harder to attack <sup>5</sup>. Specifically, HACMS is pursuing a formal methods-based approach to the creation of high-assurance vehicles, where high assurance is defined to mean functionally correct and satisfying appropriate safety and security properties [67].

### 1.2 Evolution of formal verification

In this section, we give an overview of the development of formal verification. We postpone the elaboration of the relevant theories to Chapter 3.

In the early time, Floyd-Hoare logic [71, 93] and Dijkstra's predicate transformer [52] laid theoretical foundations of the modern (semi-)automated verification techniques. In [93], a formal framework for deducing the correctness of programs was introduced, also known as Floyd-Hoare logic. Given a piece of program C, and two assertions P, Q, Floyd-Hoare logic establishes the correctness proof in the form of  $\{P\}$  C  $\{Q\}$  (i.e. Hoare triple), which intuitively means if the assertion P holds, then after the execution of C, the assertion Q must hold (if the execution of C terminates). Dijkstra's predicate transformer semantics of programs can be understood as a reformulation of P Floyd-Hoare logic. It provides a way to reduce the problem of proving a Hoare triple to the problem of proving a first order formula.

In [48], a unifying framework, known as *abstract interpretation*, was proposed for automatic program analysis and verification. Since the computation of the concrete semantics of a program (i.e. the set of reachable states) is computationally infeasible in general, the idea of abstract interpretation is to map the concrete property (i.e. a set of concrete states) to an abstract property (i.e. an element in the abstract domain), and then computes the abstract semantics of the program (i.e. an over-approximation of the set of concrete reachable states). Abstract interpretation provides a disciplined way of building analysis over abstract domains.

Independently in [43] and [129], a technique, widely known as *model checking*, was proposed as an automated approach to check if a given mathematical structure satisfies a formal logic

<sup>4.</sup> http://lamport.azurewebsites.net/tla/tla.html

<sup>5.</sup> http://www.darpa.mil/program/high-assurance-cyber-military-systems

specification. In model checking, a system is formally described as a finite state machine, and the property being checked is specified as formulae in temporal logics [112]. Then model checking algorithmically enumerates all the states of the state machine to determine if it satisfies a temporal logic specification. Model checking has been successfully applied to hardware and protocol verification, which typically gives rise to relatively smaller state spaces. However, it does not apply to real programs, due to the large or even infinite-state spaces. Even for the hardware and protocol, the state space grows exponentially with the number of participating processes or components in the system, which makes automated model checking computationally infeasible. This problem is known as *state explosion problem*.

Over the last decades, a lot of effort have been made to tackle the state explosion problem, and numerous advances in model checking, abstract interpretation and constraint solving have pushed the frontiers of formal verification. We highlight the main achievements below.

Early attempts to deal with the state space explosion problem leverages on significant algorithmic advances that come in the form of symbolic techniques for succinctly representing large sets of states as formulas. In *symbolic model checking* [116], states and transition relations are symbolically represented as binary decision diagrams (BDD) that can be manipulated efficiently. While in *bounded model checking* [24], the unfolding of the transition system and the property being checked are encoded as a formula in propositional logic, whose satisfiability can be checked using SAT solvers [18]. The capability of such techniques is still limited by the underlying routines that manipulate the symbolic data structures.

One prevalent way to address the state explosion problem is to employ *abstraction* [109]. Informally speaking, abstraction aims at minimising the system model to be verified in such a way that automated verification of the abstract model becomes computationally feasible, while the desired properties are still preserved by the abstraction. Abstraction relies on the observation that in most cases the system model contains information irrelevant to the desired properties. Discarding such information reduces the verification burden dramatically. In the past decades, various abstraction techniques have been developed. In [79], *predicate abstraction* was proposed as a specific technique that over-approximates the semantics of a program and constructs a finite state abstraction of the program, where each abstract state represents possibly infinitely many concrete program states. This technique enables direct application of finite state model checking approaches to programs which have large or infinite state spaces. Since then, predicate abstraction has been widely investigated in research. In [106, 107, 138], efficient SMT based symbolic techniques for constructing predicate abstraction were studied. It has also been successfully applied in practice [50, 15, 16, 69].

Generally abstraction results in an over-approximation, which may introduce false positives. In other words, verification of the abstract system may conclude that the property is violated, which is not the case for the concrete system. The *counterexample guided abstraction refinement* (CEGAR) [39] approach offers a solution to this problem. Specifically, given a counterexample (a faulty execution) found by analyzing the finite-state abstraction, CEGAR either

confirms that the counterexample is real, i.e. it corresponds to a concrete execution, or proposes a refined abstraction in which this counterexample is eliminated. Advanced abstraction refinement techniques based on Craig interpolant have been popularized in [117, 118, 120]. Predicate abstraction and Craig interpolant abstraction refinement have been successfully applied in practice. Notably, The SLAM project [17], initiated by Microsoft Research, applied such techniques to build an industrial toolchain for verifying Windows device driver APIs, and inspired a large interests in automated software verification research.

Alternatively to the model checking and abstraction techniques, a proof rule for invariance properties of transition systems was proposed in [113], which is also known as *deductive verification* approach. In order to prove an invariance property, deductive verification approach aims at finding a stronger assertion that entails the invariance property, and then proves that the assertion is inductive, which is done by first checking that all the initial states satisfy the invariance property, and then checking that from the set of states satisfying the assertion, one cannot reach a state that violates the assertion in one step. Deductive verification provides a partial solution to the verification of invariance property, and it leaves open the questions of how to find the auxiliary predicate. More recently, a novel technique for constructing the inductive invariant incrementally, called IC3 in [32] (and also called PDR in [55]), has been proposed.

The attention of the above mentioned techniques are mainly focused on the verification problem for systems of fixed size, i.e. the number of participating processes or components is fixed. There are systems where the number of participating processes is not fixed a priori, but given as a parameter. Such systems can be widely found in the distributed context, e.g. consensus protocols, where the number of participating processes could be arbitrary large. The verification problem for such systems, known as *parameterized verification*, asks whether the desired properties hold on system of all sizes.

Though being undecidable in general [11, 136], many interesting results and decidable fragments have been obtained. One technique to prove that a fragment of the parameterized verification problem is decidable is by reduction to the *coverability problem* of *well-structured transition system*, whose decidability is known [1, 66]. Well-known well-structured transition systems include Petri net, vector addition systems. Another technique is by reduction to a finite collection of classical verification problems, known as *cutoff techniques* [60, 74, 58, 42, 10]. That is, in order to prove a property holds on system of all sizes, it is sufficient to prove the property holds for system instances up to a fixed size, i.e. cutoff. However, cutoff does not always exist. If it does exist, cutoff varies according to the property and the state machine of the process being checked.

There is also a wide range of techniques that aim at solving the parameterized verification problem automatically, instread of obtaining the decidability results. *Counter abstraction* [127, 74] is one of such widely used techniques. The idea is that, for systems consisting of an unbounded number of components, where each component is modeled as a finite state

automaton, we only keep track of the number of components in each control location, instead of tracking the exact control locations of all components. It abstracts a parameterized system into a finite state system, which can be checked by using either classical model checking techniques, or well-structured transition system based techniques [5, 6].

In [126], the authors extend the deductive verification approach to parameterized systems. The key insight is to compute a quantified inductive invariant, which can prove properties for all system sizes. The proposed way to compute such a quantified invariant is to first construct an invariant for a system of fixed size, and then generalize this invariant to the parameterized case. However, it is not guaranteed that the obtained invariant is inductive, or strong enough to prove the desired property. In [30, 3], regular model checking is proposed as general framework for algorithmic verification of infinite-state systems. In this approach, sets of system states are represented via regular languages and automata. Symbolic procedures based on automata manipulation can be applied to perform traversals of the infinite search space induced by a parameterized system. In [75, 76], the authors propose using array-based systems to model parameterized systems, and then apply a backward reachability analysis procedure, which symbolically computes pre-images of the set of unsafe states, and checks safety and fixpoint by using SMT solving. In [104], the authors propose the method of network invariant for verifying temporal properties of parameterized systems. The idea is to find a single finite state automaton (network invariant) that soundly abstracts the parallel composition of n processes. The soundness is obtained by showing a simulation relation between the network invariant and the concrete systems.

Automated verification and parameterized verification still remain very active areas of research, particularly for concurrent and distributed systems. This brief survey is biased towards the focus of this dissertation. We remark that there is a wide range of reduction techniques for algorithmic verification of concurrent systems, called *partial order reduction* [77, 124, 46, 139], that rely on the partial order semantics of concurrent systems. We postpone the elaborations to Chapter 3. For detailed explanations of each verification technique, we refer to the various books on formal verification [47, 13, 81, 28].

# 1.3 Challenges and contributions

The high-level contributions of this dissertation comprise new modeling framework and verification algorithms that push the frontiers of algorithmic verification of component-based systems modeled in BIP framework with both bounded and unbounded concurrency. By systems with bounded concurrency, we mean the systems that consist of a fixed number of components, and with unbounded concurrency, we mean the systems that consist of a parameterized number of components. These contributions have been published in the following articles:

1. Formal verification of infinite-state BIP models, Bliudze, Simon and Cimatti, Alessandro

and Jaber, Mohamad and Mover, Sergio and Roveri, Marco and Saab, Wajeb and **Wang, Qiang**, International Symposium on Automated Technology for Verification and Analysis (ATVA 2015), pages 326–343, 2015, Springer.

- 2. Verification of component-based systems via predicate abstraction and simultaneous set reduction, **Qiang, Wang** and Bliudze, Simon, International Symposium on Trustworthy Global Computing (TGC 2015), pages 147–162, 2015, Springer.

- 3. *Parameterized systems in BIP: design and model checking*, Konnov, Igor and Kotek, Tomer and **Wang, Qiang** and Veith, Helmut and Bliudze, Simon and Sifakis, Joseph, Proceedings of the 27th International Conference on Concurrency Theory (CONCUR 2016), pages 30–1, 2016, Schloss Dagstuhl–Leibniz-Zentrum fuer Informatik.

- 4. Exploiting Symmetry for Efficient Verification of Infinite-State Component-Based Systems, Wang, Qiang, International Symposium on Dependable Software Engineering: Theories, Tools, and Applications (SETTA 2016), pages 246–263, 2016, Springer.

### 1.3.1 Algorithmic verification of systems with bounded concurrency

As we discussed in the previous section, the BIP modeling language offers a three-layered modeling mechanism, i.e. Behavior, Interaction, and Priority, for constructing complex system behavior and architectures. Behavior is characterized by a set of components, which are formally defined as automata extended with linear arithmetic. Interaction specifies the multiparty synchronization of components, among which data transfer may take place. Priority can be used to schedule the interactions or resolve conflicts when several interactions are enabled simultaneously. The key insight underlying this three-layered modeling mechanism is the principle of separation of concerns, that is, system computation is captured by a set of components, and system coordination is modeled by interaction and priority.

Our approach is inspired by the *Explicit Scheduler Symbolic Thread* (ESST) approach to efficient verification of SystemC programs [130]. In brief, we aim at decomposing the verification of infinite-state component-based systems into two levels by taking advantage of the structural features of such systems, and, thus, we palliate the state space explosion by handling the computation in the components and the coordination among components separately.

On the computation level, we exploit the state-of-the-art counterexample guided abstraction refinement technique, to deal with the sequential computations and explore the reachable states of each individual component; while on the coordination level, we resolve the redundant interleavings of concurrent interactions by applying explicit state partial order reduction techniques [77, 78, 124, 125, 46, 139, 140]. Specifically, we combine the lazy abstraction with interpolant based abstraction refinement [90, 88, 119] and the persistent set partial order reduction for BIP. We have implemented the proposed verification techniques based on the Kratos model checker [36]. We also propose two further techniques to improve the reductions of redundant interleavings. The first technique aims at exploring as many independent interactions as possible simultaneously in one step, and the second technique exploits the system

symmetry to improve the persistent set reduction.

These contributions are elaborated, respectively, in Chapters 4 and 5.

We remark that in the BIP framework, DFinder [22, 21] is a dedicated tool for invariant generation and deadlock detection. DFinder computes the system invariant in a compositional manner: it first computes a component invariant over-approximating the reachable states of each component and then computes an interaction invariant over-approximating the global reachable states. The system invariant is then the conjunction of all component invariants and the interaction invariant. Though being scalable for large system models, DFinder does not handle system models with data transfer, which hampers the practical application of DFinder and of the BIP framework, since data transfer is necessary and common in the design of real-life systems (e.g. message passing). Besides, when the inferred invariant fails to prove the property, DFinder produces a single state as the counterexample other than an execution path. By the time DFinder was developed, it was not clear how to efficiently refine the abstraction automatically from the single state. In [95], the authors present an encoding of a subset of BIP models into Horn Clauses, which are solved by the model checker ELDARICA [94]. However, the encoding does not handle data transfer on interactions. As the current stage of their work, the encoding still requires massive manual work.

An efficient instantiation of the ESST framework [130] for BIP has been presented in [26]. This ESST based technique encodes the components as preemptive threads with predefined primitive functions and utilizes a dedicated stateful BIP scheduler to orchestrate the abstract reachability analysis of the components. The scheduler interacts with components via primitive functions, and also respects BIP operational semantics. Moreover, partial order reduction techniques [78] are applied in the scheduler to reduce its state space.

#### 1.3.2 Modeling and verifying systems with unbounded concurrency

Parameterized systems are systems consisting of homogeneous processes, where the parameter indicates the number of such processes in the system. A parameterized system, therefore, describes an infinite family of systems where instances of the family can be obtained by fixing the parameter value. Verification of the correctness of such systems amounts to verifying the correctness of every member of the infinite family described by the system. This problem is undecidable in general [136]. However, many efforts have been invested into extending of classic model checking to the parameterized case, leading to numerous parameterized model checking echniques (see [28] for a recent survey).

Unfortunately, often parameterized model checking techniques come with their own mathematical models, which makes their practical application difficult. To perform parameterized model checking, the user needs to apply deep knowledge from the literature. First, the user needs to manually inspect the parameterized models and match them with the mathematical formalisms from the relevant available parameterized verification techniques. Using the

match, the users would then apply the decidability results (if any) for the parameterized models, e.g. by computing a cutoff or translating the parameterized model into the language of a particular tool for the specific architecture.

Thus, there is a gap between the mathematical formalisms and algorithms from the parameterized verification research and the verification in practice, which is usually done by engineers who are not familiar with the details of the literature. We aim at closing this gap by introducing a framework for design and verification of parameterized systems in BIP. With this framework, we make the following specific contributions:

- 1. We propose the *first-order interaction logic* (FOIL) within BIP framework as a formal language for architectures of parameterized systems, i.e. system topologies and communication mechanisms. FOIL is powerful enough to express architectures found in parameterized systems, including the classical architectures: token-passing rings, rendezvous cliques, broadcast cliques, rendezvous stars. We also identify a decidable fragment of FOIL, which is important for practical applicability.

- 2. We investigate the decidability of the verification of parameterized BIP models, where components are descirbed by finite state automata, and the system architecture is specified by a FOIL formula. We prove that this problem is undecidable in general, and also identify certain decidable fragments, relying on the well-structured transition system theory [1, 66].

- 3. We provide a framework for the integration of mathematical models from the parameterized model checking literature in an automated way: given a parameterized BIP design, our framework detects parameterized model checking techniques that are applicable to this design. We present how to identify the system architecture automatically by the use of SMT solvers and standard (non-parameterized) model checkers.

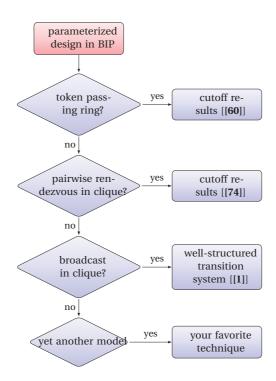

- 4. We provide a preliminary prototype implementation of the proposed framework. Our prototype tool takes a parameterized BIP design as its input and detects whether one of the following classical results applies to this BIP design: the cut-off results for token-passing rings by Emerson & Namjoshi [60], the VASS-based algorithms by German & Sistla [74], and the undecidability and decidability results for broadcast systems by Abdulla et al. [1] and Esparza et al. [64]. More importantly, our framework is not specifically tailored to the mentioned techniques.

We remark that our framework builds on the notions of BIP, which allows us to express complex notions in a terminology understood by engineers. Moreover, our framework allows an expert in parameterized model checking to capture seminal mathematical models found in the verification literature, e.g. [74, 64, 60, 42].

These contributions are elaborated in Chapter 6.

### 1.4 Organization of this dissertation

The rest of the dissertation is organized as follows:

- In Chapter 2, we present some preliminaries of safety property verification, and introduce the BIP modelling language, which we use in this dissertation as the formal system model, and its operational semantics. We also present a symbolic encoding of BIP system models as symbolic transition systems.

- In Chapter 3, we review the most relevant verification techniques for concurrent systems, in particular, abstraction and partial order reduction techniques.

- In Chapter 4, we present the main verification techniques for the class of BIP models with a fixed number of components. In particular, we present an instantiation of the lazy predicate abstraction technique and a partial order reduction for BIP, and also their combination. We also present comprehensive experimental evaluations of the proposed techniques against the state-of-the-art verification techniques in the end of this chapter.

- In Chapter 5, we present two further techniques for improving partial order reductions. First, we investigate how to explore independent interactions simultaneously, instead of postponing them as in the other classical partial order reduction approaches. Second, we study how to exploit system symmetries to improve the reductions. We also present their combinations with lazy abstraction and the experimental evaluations.

- In Chapter 6, we present the design and uniform verification framework for parameterized systems in BIP, that is the systems with unbounded number of participating components. We first present an extension of the current BIP framework to enable the modelling of a wide range of parameterized systems. Then we present an automated verification framework that can incorporate the existing parameterized verification techniques. We also present some decidability results for certain fragments of parameterized BIP models.

- In Chapter 7, we summarize this dissertation and also present some perspectives and future work.

# 2 Preliminary and system model

In this chapter, we first present some preliminaries of formal invariant verification. Then we present the BIP modeling language for systems that consist of a fixed number of components. In the end, we present an encoding of BIP system model as symbolic transition system.

## 2.1 Labeled transition system

We denote by  $\mathbb V$  a set of integer variables, and the symbol  $\mathbf V$  ranges over all possible valuations of variables. We also denote by  $\mathscr E_{\mathbb V}$  the set of expressions, and  $\mathscr F_{\mathbb V}$  the set of formulae in the theory of linear arithmetic over  $\mathbb V$ . We denote by  $\mathbf V \models \phi$  the statement that a valuation  $\mathbf V$  satisfies a formula  $\phi \in \mathscr F_{\mathbb V}$ . We denote by  $\mathbf V[x := e]$  the substitution of variable x by expression e in the valuation  $\mathbf V$ . As usual, we use primed variables to represent the state of the system after one step. The priming notation is extended to formulae and assignments in the standard way.

In this dissertation, we use labeled transition systems to define the operational semantics of computing systems.

**Definition 2.1.1 (Labeled transition system)** A labeled transition system (LTS) is defined by a tuple  $\mathcal{T} = \langle C, \Sigma, R, C_0 \rangle$ , which consists of

- 1. a set of states C;

- 2. a set of transition labels  $\Sigma$ ;

- 3. a set of transition relations  $R \subseteq C \times \Sigma \times C$ ;

- 4. a set of initial states  $C_0 \subseteq C$ .

For simplicity, we denote a transition  $\langle c, t, c' \rangle \in R$  by  $c \xrightarrow{t} c'$ . A transition t is enabled in the state c, if  $c \xrightarrow{t} c'$ , for some  $c' \in C$ . An LTS is deterministic if  $c \xrightarrow{t} c_1$  and  $c \xrightarrow{t} c_2$  implies  $c_1 = c_2$ , for any  $c \in C$  and  $t \in \Sigma$ . In this dissertation, we focus on deterministic transition systems.

A trace (or an execution) of a transition system is a sequence of transitions from a given state. We denote a trace by the sequence of transition labels. For instance, the sequence of transitions  $c \xrightarrow{t_1} c_1 \xrightarrow{t_2} \dots \xrightarrow{t_n} c'$  is represented as  $c \xrightarrow{t_1 t_2 \dots t_n} c'$ .

A state c is reachable if there is a trace  $c_0 \xrightarrow{t_1...t_n} c$ , where  $c_0 \in C_0$  and  $t_i \in \Sigma$ , for each  $i \in [1, n]$ . Given a state c, we denote by  $en(c) \subset \Sigma$  the set of transitions enabled in state c. A state c is a deadlock state if there is no such  $t \in \Sigma$ , and  $c' \in C$  that  $c \xrightarrow{t} c'$ . We denote by RS the set of all reachable states.

A set of states can also be represented by its characteristic predicate, that is, a predicate represents all the states that satisfy it. Given a predicate p, we define the post operator as follows:

$$post(p,R) = \{c' \in C \mid \exists c \in C, p(c) \land (c,t,c') \in R\}$$

In other words, post(p, R) characterises the set of states that are reachable from the states satisfying the predicate p in one step by taking a transition in R. For instance,  $post(C_0, R)$  represents the set of states that are reachable from the initial states in one step. More generally, the set of reachable states within i steps can be defined as follows using the post operator:

$$RS_i = C_0 \lor post(C_0, R) \lor \dots \lor post^i(C_0, R)$$