# Challenges and Solutions to Next-Generation Single-Photon Imagers

# THÈSE Nº 7136 (2016)

PRÉSENTÉE LE 19 AOÛT 2016

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE D'ARCHITECTURE QUANTIQUE PROGRAMME DOCTORAL EN GÉNIE ÉLECTRIQUE

# ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

# Samuel BURRI

acceptée sur proposition du jury:

Prof. J.-Ph. Thiran, président du jury Prof. E. Charbon, directeur de thèse Prof. J. Langowski, rapporteur Dr X. Michalet, rapporteur Dr R. Ischebeck, rapporteur

# Zusammenfassung

Eine immer grösser werdende Menge an Anwendungen profitiert vom Detektieren und Zählen einzelner Photonen. Die Mehrheit dieser Anwendungen benötigt dabei möglichst hohe räumliche Auflösungen, zumeist mindestens ein Megapixel. Diese Dissertation beleuchtet die Schwierigkeiten, die im Zusammenhang mit hochauflösenden Kameras zur Zählung einzelner Photonen auftreten, in umfassender Weise.

Dabei behandelt diese Dissertation eine grosse Zahl leistungsmindernder Probleme, die auftauchen wenn die Zahl der Pixel über ¼ Million steigt. Zur Diskussion dieser Probleme benutzt man den Begriff der Nicht-Uniformität (non-uniformity). Dazu werden Techniken zur Charakterisierung der Nicht-Uniformität verschiedener Parameter und mögliche Lösungen im Zusammenhang mit daraus resultierenden Problemen aufgezeigt. Diese Techniken sollen dabei helfen Nicht-Uniformität zu erkennen und damit verbundene Leistungseinbussen zu beheben.

Zur Bewertung der in dieser Arbeit vorgestellten Techniken wurden zwei Kameras hergestellt, die für die Detektion einzelner Photonen geeignet sind.

Die erste Kamera, SwissSPAD, besteht aus einem Sensor mit 512 x 128 Pixeln mit Dioden, die einzelne Photonen detektieren. Jeder Pixel hat darüber hinaus ein 1-Bit Speicherelement und einen Verschlussmechanismus der Verschlusszeiten bis hinunter zu 5 Nanosekunden erlaubt. Dabei hat der Verschluss eine hohe Uniformität für alle Pixel und kann mit einer Präzision im Bereich weniger Pikosekunden relativ zu einem Referenzsignal ausgelöst werden. Zusammen mit einer schnellen Datenübertragung mit einer Rate von über 10 Gigabit pro Sekunde ermöglicht dieser Verschluss eine Beschleunigung der Messzeiten in Anwendungen der Fluoreszenz-Lebenszeit-Mikroskopie sowie der Fluoreszenz-Korrelations-Spektroskopie um mehrere Grössenordnungen. Andere mögliche Anwendungen betreffen die räumlich hochauflösende Aufzeichnung von Flugzeiten einzelner Photonen und die Erzeugung von Zufallszahlen in hoher Frequenz. Kürzlich hat auch eine Anwendung super-auflösender Mikroskopie vom SwissSPAD-Sensor Gebrauch gemacht.

Die zweite Kamera, LinoSPAD, wendet die mit SwissSPAD gewonnenen Erkenntnisse an, wobei der Sensor auf ein Minimum an Funktionalität reduziert wird. Im Gegenzug enthält die Kamera eine leistungsfähigere Verknüpfung des Sensors mit einem FPGA, einem flexibel konfigurierbarem Schaltkreis. Dadurch wird es ermöglicht, den Sensor auf seine wichtigste Eigenschaft, die Photoneneffizienz, zu optimieren. So besteht der Sensor aus nur einer Zeile von Photonen detektierenden Dioden. Dafür ist aber jede Diode direkt mit dem FPGA verbunden, in welchem die komplexe Verarbeitung der Information über Photonen stattfinden kann. Zur Veranschaulichung der Möglichkeiten aktueller, preisgünstiger FPGAs haben wir eine Reihe hochauflösender Module (time-to-digital converters) integriert, um die Ankunftszeiten einzelner Photonen auf dem Sensor zu messen. Dieses System erlaubt die Erfassung einzelner Photonen und das Aufzeichnen ihrer Ankunftszeit in Histogrammen mit einer Rate von bis zu 8.5 Milliarden Ereignissen pro Sekunde. Unsere Kamera, in Kombination mit einer Laserdiode und einem Schaltkreis zur Erzeugung ultrakurzer

Lichtpulse im Pikosekundenbereich, ergibt eine vielfältig einsetzbare 3D Kamera basierend auf dem Prinzip der Laufzeitmessung von Photonen.

Diese Dissertation soll ein erster Schritt sein auf dem Weg zu einem Sensor mit einer Million Pixel, die auf einzelne Photonen detektierenden Dioden basieren. Wir glauben, dass ein solcher Sensor dank den in dieser Dissertation vorgestellten Möglichkeiten von Architektur und Verschaltung einer grossen Anzahl von Photonen detektierenden Dioden in naher Zukunft realisiert werden kann. Ausserdem glauben wir, dass die Anwendungen, die in dieser Dissertation präsentiert werden, Hinweise geben auf eine grosse Zahl zukünftiger Anwendungen, in welchen die hergestellten Kameras bisherige Detektionssysteme gewinnbringend ersetzen können.

#### Schlüsselwörter

Einzelphotonendiode, SPAD, CMOS, Kamera, TDC, Phänomene im Bereich der Pikosekunden, Photonen

# **Abstract**

Detecting and counting single photons is useful in an increasingly large number of applications. Most applications require large formats, approaching and even far exceeding 1 megapixel. In this thesis, we look at the challenges of massively parallel photon-counting cameras from all performance angles.

The thesis deals with a number of performance issues that emerge when the number of pixels exceeds about ¼ of megapixels, proposing characterization techniques and solutions to mitigate performance degradation and non-uniformity.

Two cameras were created to validate the proposed techniques.

The first camera, SwissSPAD, comprises an array of 512 x 128 SPAD pixels, each with a one-bit memory and a gating mechanism to achieve 5ns high precision time windows with high uniformity across the array. With a massively parallel readout of over 10 Gigabit/s and positioning of the integration time window accurate to the picosecond range, fluorescence lifetime imaging and fluorescence correlation spectroscopy imaging achieve a speedup of several orders of magnitude while ensuring high precision in the measurements. Other possible applications include wide-field time-of-flight imaging and the generation of quantum random numbers at highest bit-rates. Lately super resolution microscopy techniques have also used SwissSPAD.

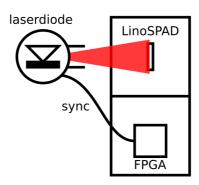

The second camera, LinoSPAD, takes the concepts of SwissSPAD one step further by moving even more 'intelligence' to the FPGA and reducing the sensor complexity to the bare minimum. This allows focusing the optimization of the sensor on the most important metrics of photon efficiency and fill factor. As such, the sensor consists of one line of SPADs that have a direct connection each to the FPGA where complex photon processing algorithms can be implemented. As a demonstration of the capabilities of current low-cost FPGAs we implemented an array of time-to-digital converters that can handle up to 8.5 billion photons per second, measuring each one of them and accounting them in high precision histograms. Using simple laser diodes and a circuit to generate light pulses in the picosecond range, we demonstrate a ubiquitous 3D time-of-flight sensor.

The thesis intends to be a first step towards achieving the world's first megapixel SPAD camera, which, we believe, is in grasp thanks to the architectural and circuital techniques proposed in this thesis. In addition, we believe that the applications proposed in this thesis offer a wide variety of uses of the sensors presented in this thesis and in future ones to come.

Keywords

CMOS, SPAD, Pixel, Camera, FPGA, TDC, picosecond phenomena, Photons

# Contents

| Zusammenfa | assung                 |                                                                  | i   |  |  |

|------------|------------------------|------------------------------------------------------------------|-----|--|--|

| Abstract   |                        |                                                                  | iii |  |  |

| Chapter 1  | Introdu                | uction                                                           | 1   |  |  |

| 1.1        | Objecti                | ives of the thesis                                               | 1   |  |  |

| 1.2        | Photon                 | Photon-counting cameras                                          |     |  |  |

|            | 1.2.1                  | Photo-multiplier tubes                                           | 2   |  |  |

|            | 1.2.2                  | Micro-channel plates                                             | 3   |  |  |

|            | 1.2.3                  | Charge-coupled devices                                           | 4   |  |  |

|            | 1.2.4                  | Active pixel sensors in complementary metal-oxide semiconductors | 6   |  |  |

| 1.3        | Single-                | photon avalanche diode and imager                                | 7   |  |  |

|            | 1.3.1                  | Operation of a SPAD                                              | 8   |  |  |

|            | 1.3.2                  | Fabrication of SPADs                                             | 9   |  |  |

|            | 1.3.3                  | Integrated quenching and recharge for CMOS SPADs                 | 10  |  |  |

|            | 1.3.4                  | SPAD metrology                                                   | 12  |  |  |

|            | 1.3.5                  | SPAD array architectures                                         | 16  |  |  |

| 1.4        | Time-co                | orrelated photon counting                                        | 17  |  |  |

| 1.5        | Applica                | ations of single-photon cameras                                  | 18  |  |  |

|            | 1.5.1                  | Fluorescence lifetime imaging                                    | 18  |  |  |

|            | 1.5.2                  | Quantum random number generation                                 | 18  |  |  |

|            | 1.5.3                  | 3D time-of-flight                                                | 19  |  |  |

|            | 1.5.4                  | Other uses of SPAD imagers                                       | 19  |  |  |

| Chapter 2  | SwissSl                | PAD: a 512x128 time-gated single-photon imager                   | 21  |  |  |

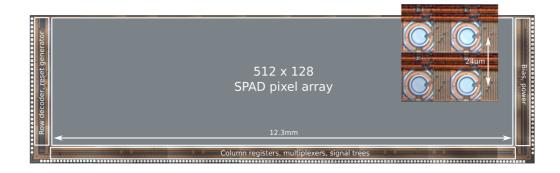

| 2.1        | Chip architecture      |                                                                  |     |  |  |

|            | 2.1.1                  | CMOS SPAD                                                        | 22  |  |  |

|            | 2.1.2                  | Pixel circuit                                                    | 22  |  |  |

|            | 2.1.3                  | Sensor architecture                                              | 24  |  |  |

| 2.2        | Chip operation         |                                                                  |     |  |  |

| 2.3        | 2.3 FGPA system design |                                                                  |     |  |  |

| 2.4        | Compu                  | ıter software                                                    | 29  |  |  |

| 2.5        | Perforr                | mance evaluation                                                 | 30  |  |  |

|            | 2.5.1                  | Breakdown voltage                                                | 31  |  |  |

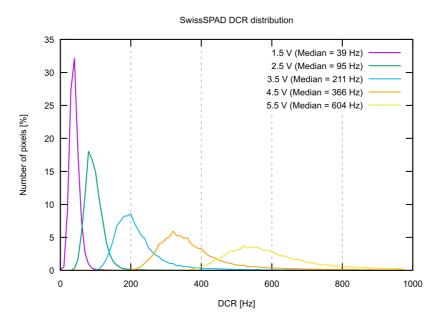

|           | 2.5.2  | DCR                                                   | 31 |

|-----------|--------|-------------------------------------------------------|----|

|           | 2.5.3  | PDP                                                   | 32 |

|           | 2.5.4  | Photo response non-uniformity (PRNU)                  | 33 |

|           | 2.5.5  | Sensitivity and noise calibration                     | 34 |

|           | 2.5.6  | Clock- and event-driven readout architectures         | 35 |

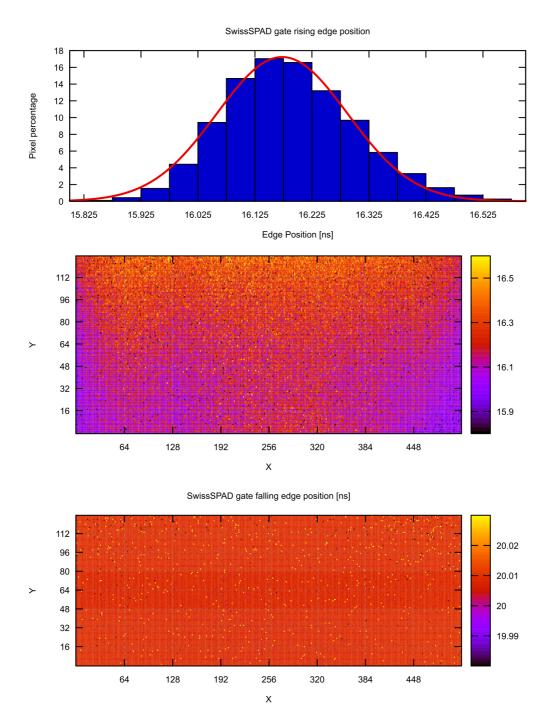

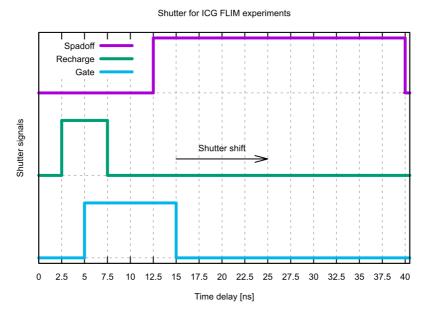

|           | 2.5.7  | Gating                                                | 36 |

|           | 2.5.8  | Readout                                               | 39 |

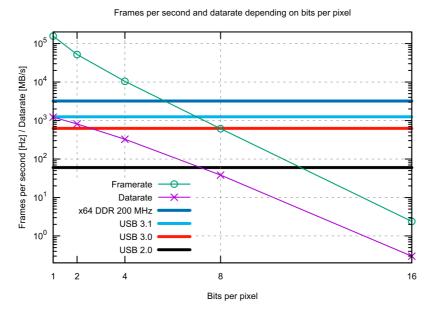

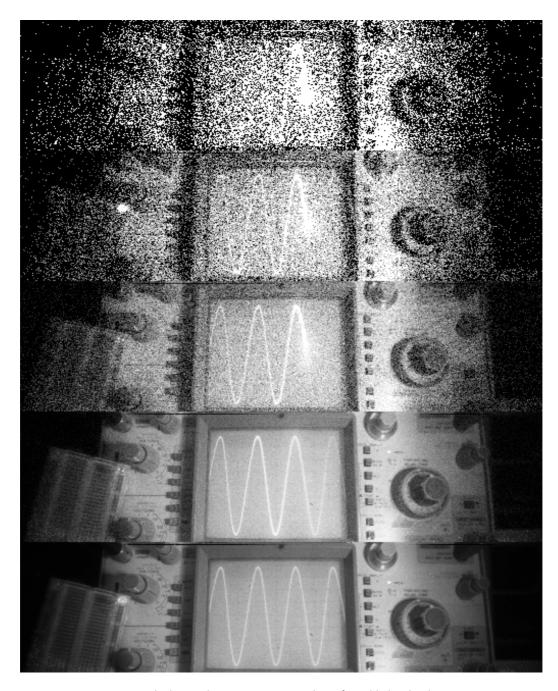

|           | 2.5.9  | High speed imaging                                    | 40 |

|           | 2.5.10 | Performance summary                                   | 42 |

| 2.6       | Transi | tion to new FPGA board                                | 42 |

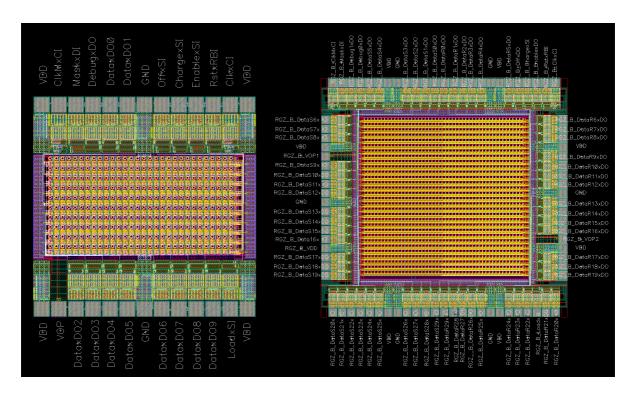

| Chapter 3 | LinoSF | PAD: a reprogrammable SPAD line sensor                | 43 |

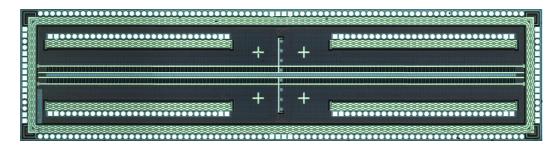

| 3.1       | Senso  | r                                                     | 43 |

|           | 3.1.1  | Chip architecture                                     | 43 |

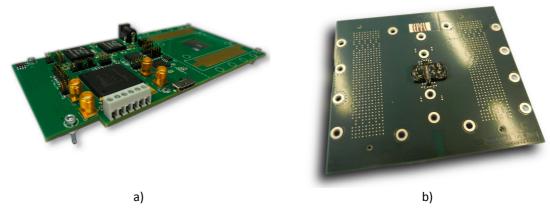

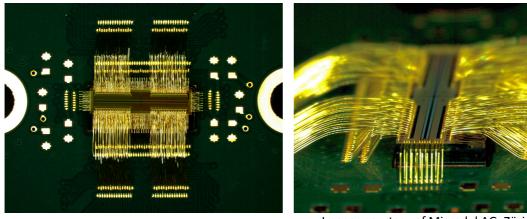

|           | 3.1.2  | FPGA interface card                                   | 44 |

| 3.2       | FPGA   | architecture                                          | 46 |

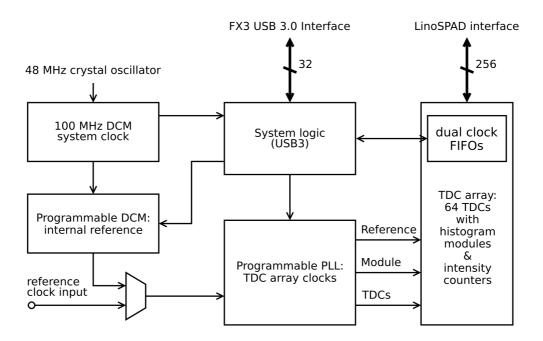

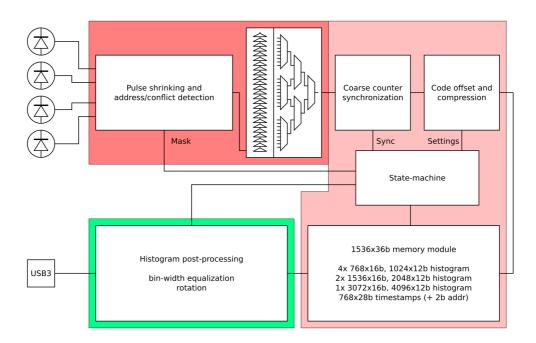

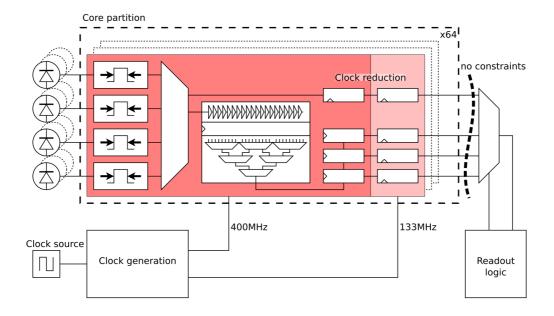

|           | 3.2.1  | Global architecture                                   | 46 |

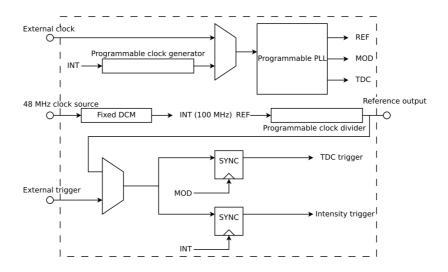

|           | 3.2.2  | Clock architecture                                    | 47 |

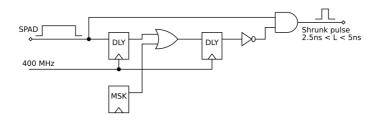

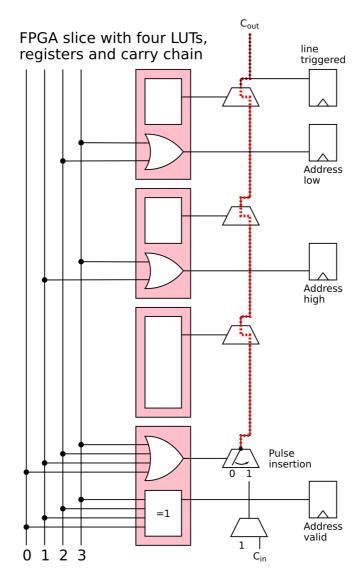

|           | 3.2.3  | TDC core                                              | 48 |

|           | 3.2.4  | Postprocessing                                        | 53 |

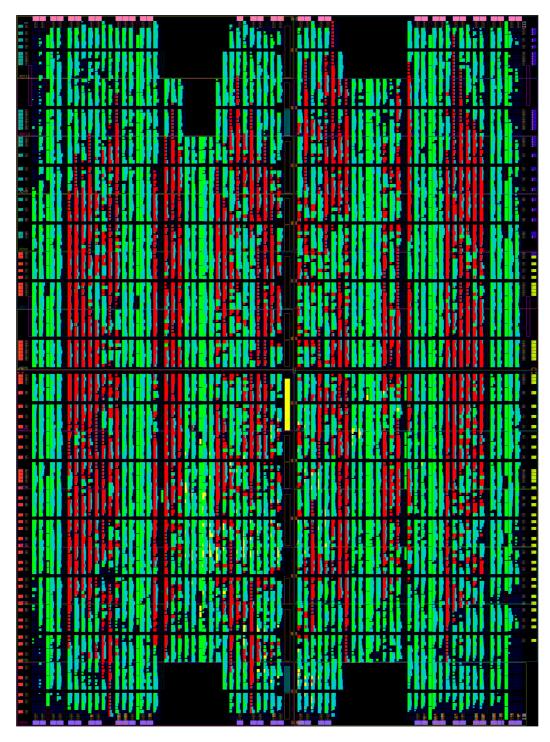

| 3.3       | FPGA   | Implementation                                        | 56 |

| 3.4       | Comp   | uter software communication                           | 60 |

| 3.5       | Result | S                                                     | 61 |

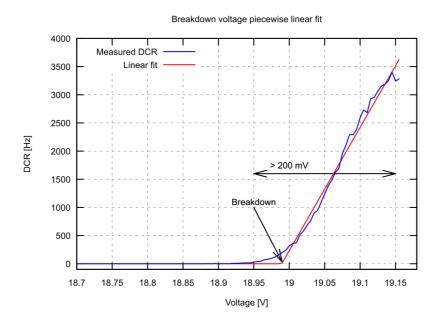

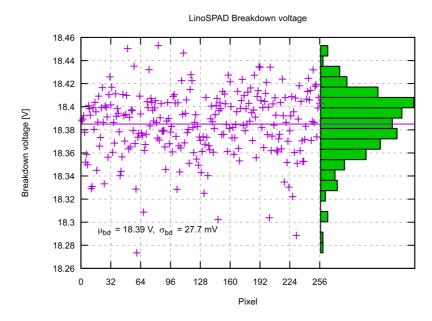

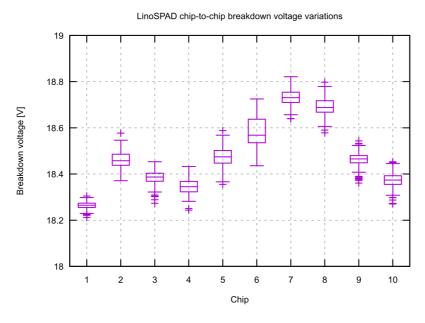

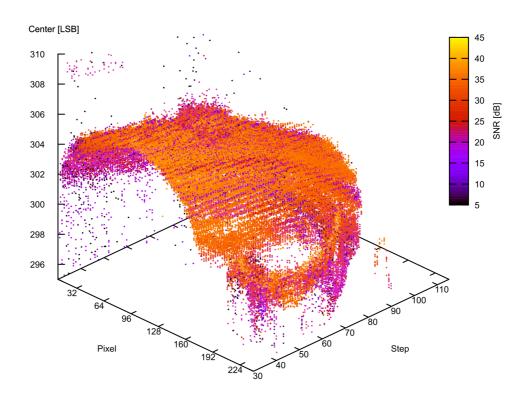

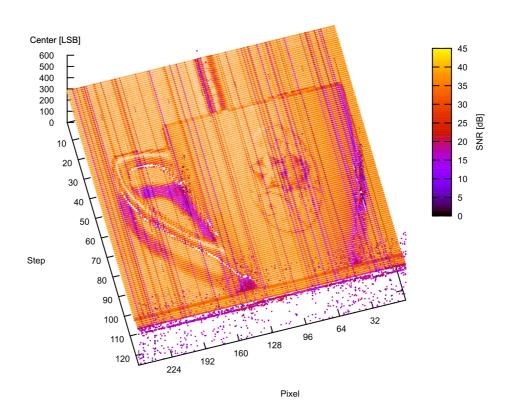

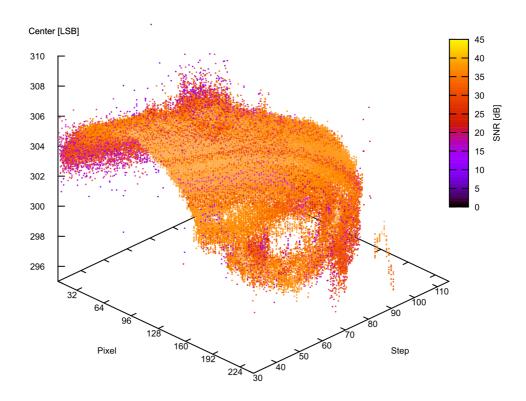

|           | 3.5.1  | Breakdown voltage                                     | 61 |

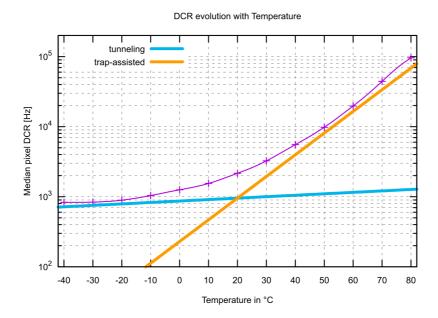

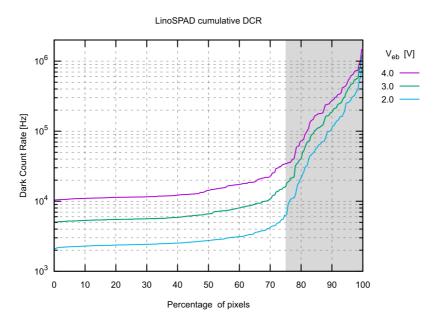

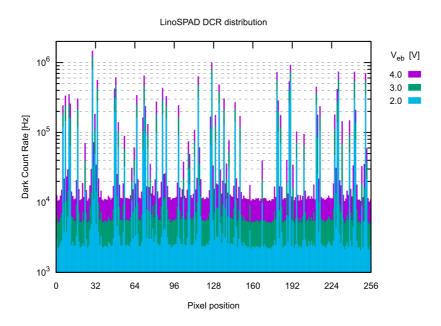

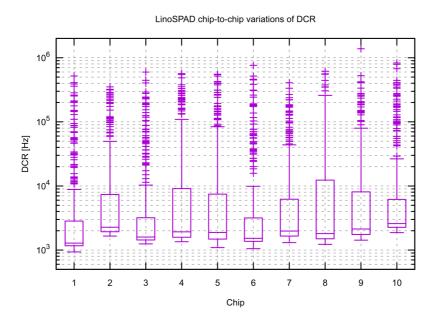

|           | 3.5.2  | DCR                                                   | 63 |

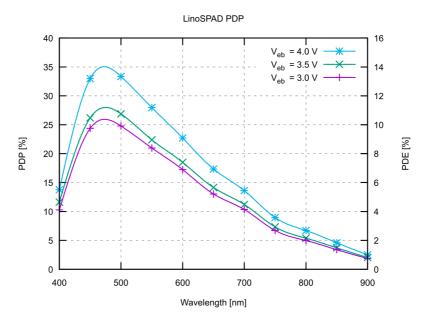

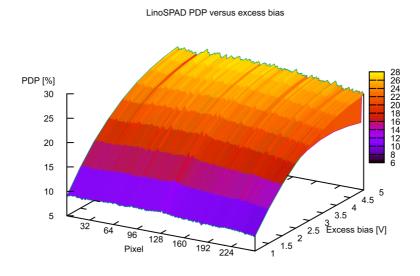

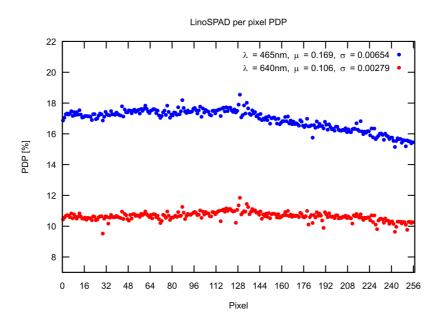

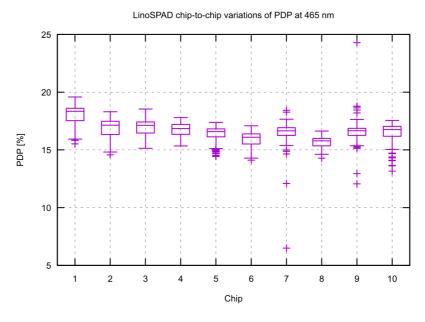

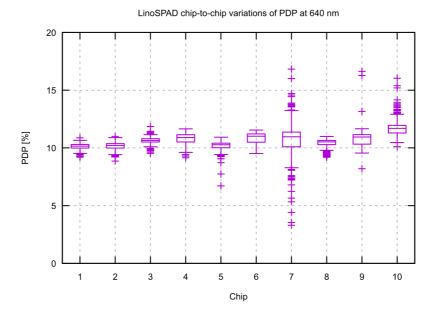

|           | 3.5.3  | PDP                                                   | 65 |

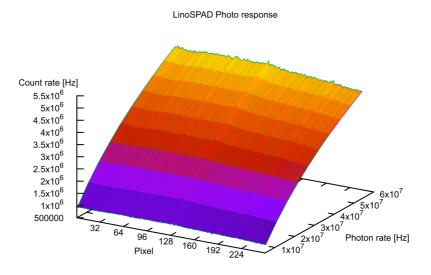

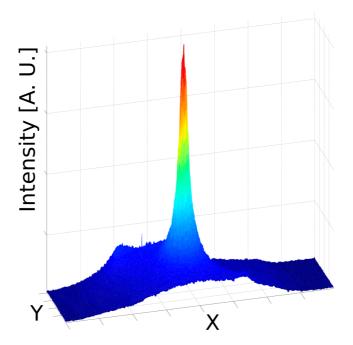

|           | 3.5.4  | Photo response                                        | 67 |

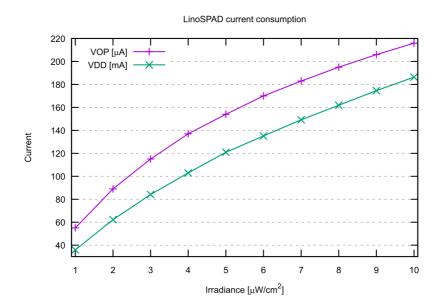

|           | 3.5.5  | Power consumption                                     | 68 |

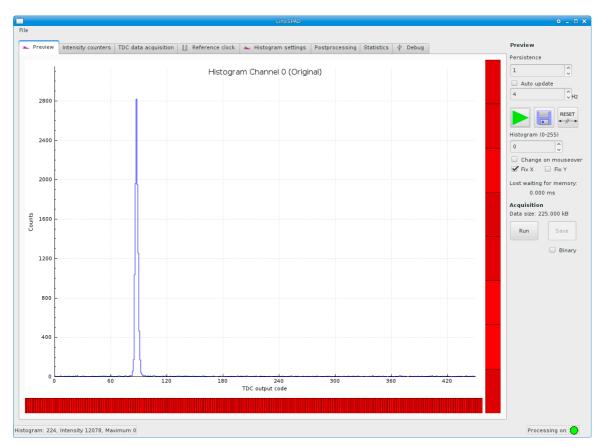

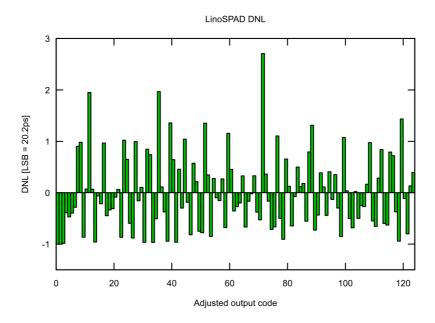

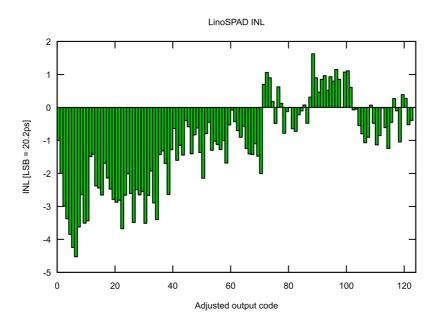

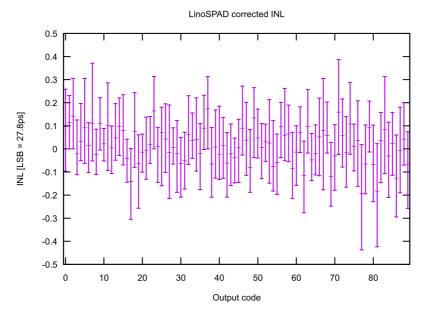

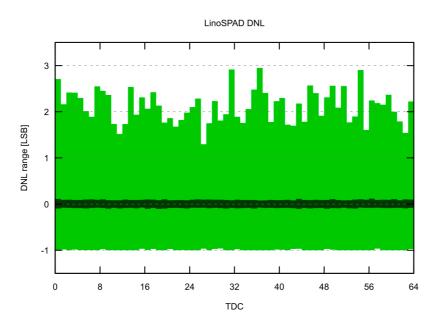

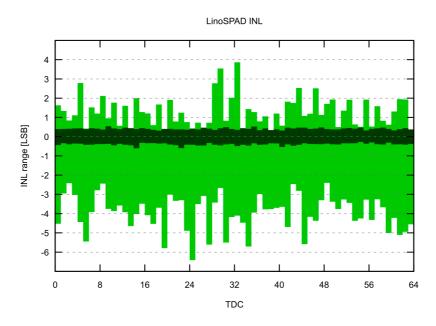

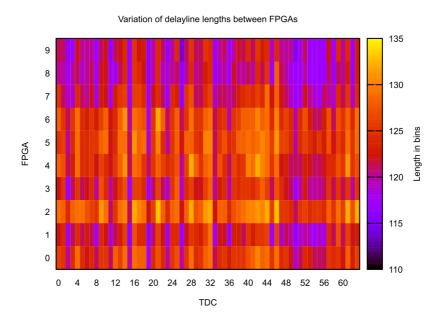

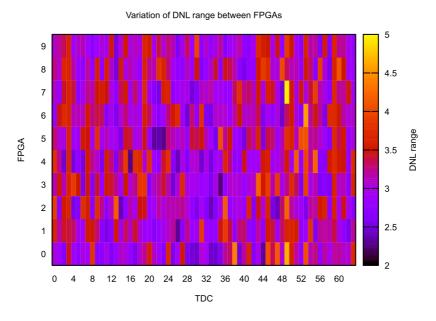

|           | 3.5.6  | TDC response                                          | 69 |

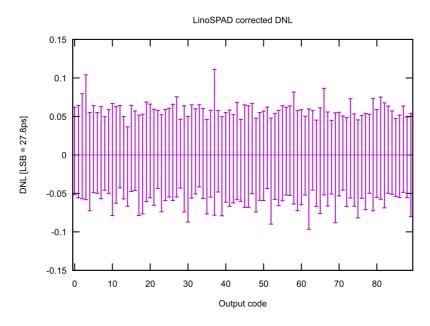

|           | 3.5.7  | Post-processing                                       | 71 |

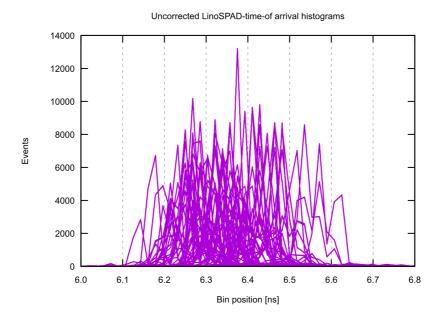

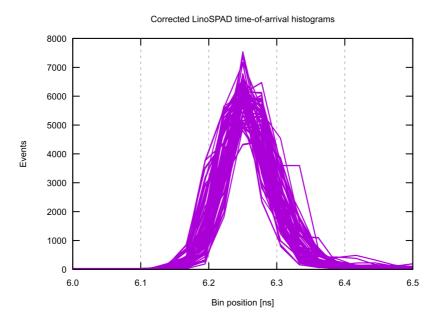

|           | 3.5.8  | Histograms                                            | 73 |

|           | 3.5.9  | Performance summary and comparison to other FPGA TDCs | 75 |

| Chapter 4 | Challe | nges of large SPAD array imagers                      | 77 |

| 4.1       | SwissS | SPAD parameter non-uniformity                         | 77 |

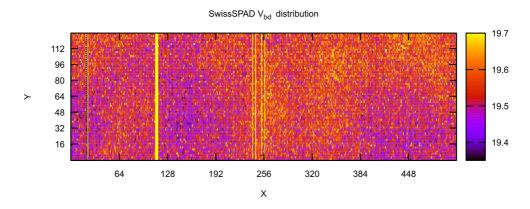

|           | 4.1.1  | Breakdown voltage                                     | 77 |

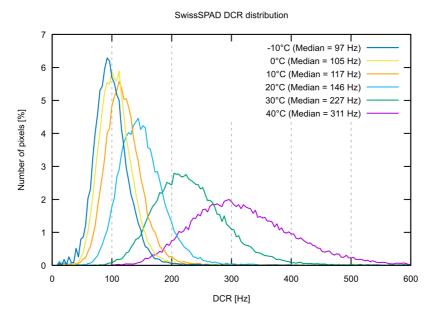

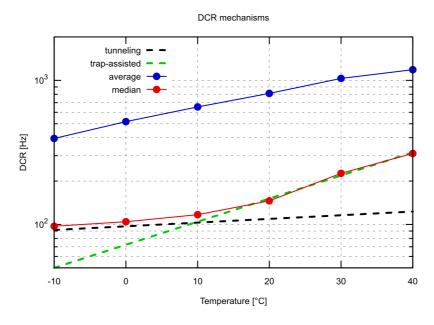

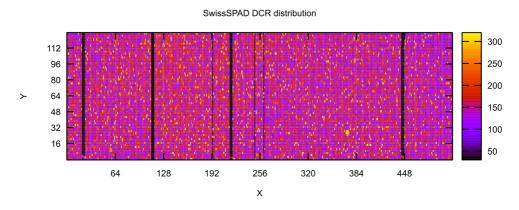

|           | 4.1.2  | Dark count rate                                       | 78 |

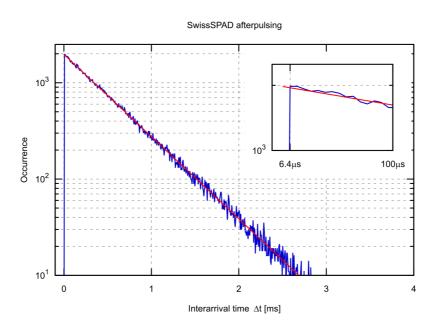

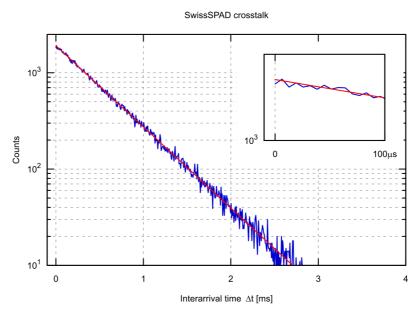

|           | 4.1.3  | Afterpulsing and crosstalk                            | 81 |

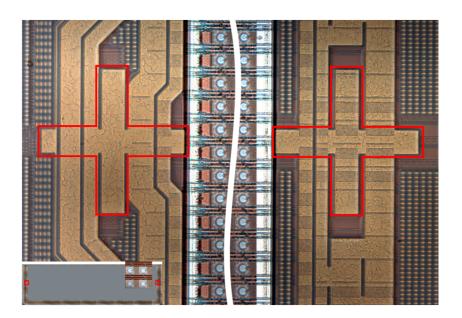

| 4.2       | Optica | al enhancement for SwissSPAD                          | 83 |

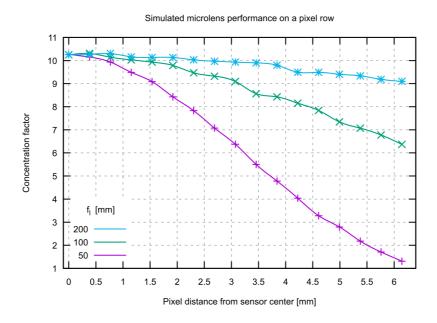

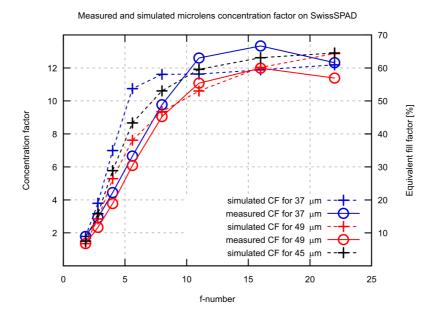

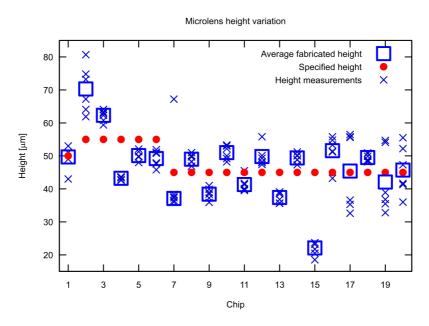

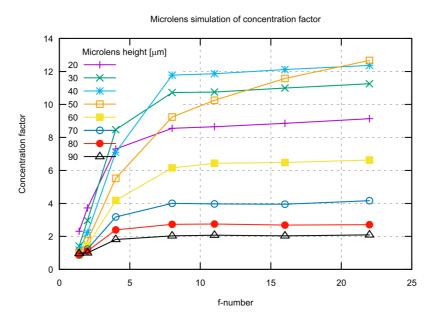

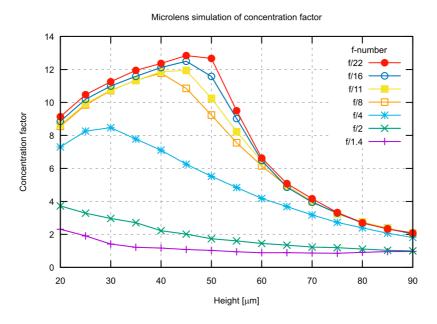

|                       |                  | 4.2.1              | Fill factor recovery using microlenses.                 | 85   |  |

|-----------------------|------------------|--------------------|---------------------------------------------------------|------|--|

|                       |                  | 4.2.2              | Non-uniformity in microlens fabrication and performance | 86   |  |

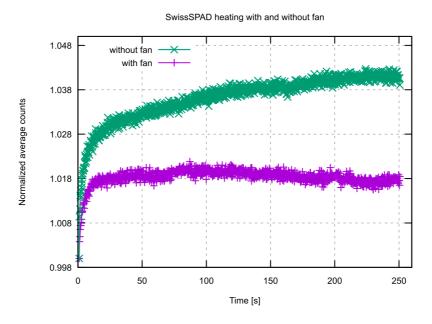

| 4                     | 4.3              | Tempe              | rature effects in SPAD sensors                          | 89   |  |

|                       |                  | 4.3.1              | SwissSPAD turn-on temperature changes                   | 89   |  |

|                       |                  | 4.3.2              | LinoSPAD TDC resolution variation with temperature      | 91   |  |

| 4                     | 4.4              | LinoSP             | AD non-uniformities                                     | 92   |  |

|                       |                  | 4.4.1              | Dead time and afterpulsing                              | 92   |  |

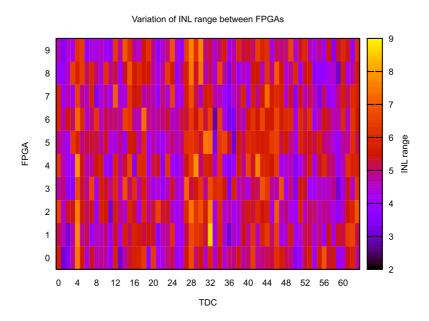

|                       |                  | 4.4.2              | TDC-to-TDC variation                                    | 95   |  |

|                       |                  | 4.4.3              | Sensor-to-Sensor variation                              | 98   |  |

|                       |                  | 4.4.4              | FPGA-to-FPGA                                            | 100  |  |

| Chapter               | · 5              | Results            | 5                                                       | 103  |  |

| !                     | 5.1              | SwissSl            | PAD                                                     | 104  |  |

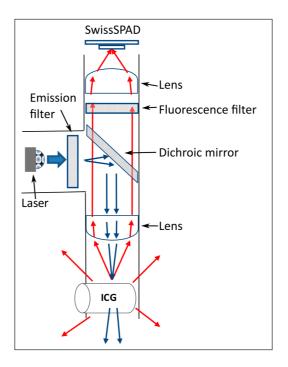

|                       |                  | 5.1.1              | FLIM experiments                                        | 104  |  |

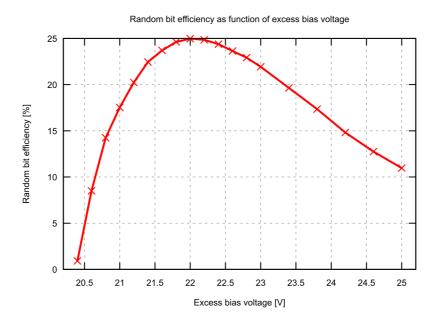

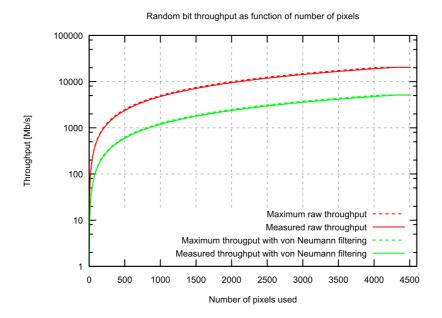

|                       |                  | 5.1.2              | Quantum random number generation                        | 115  |  |

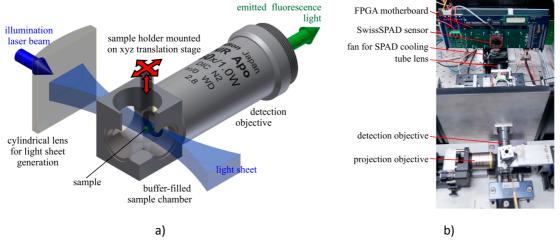

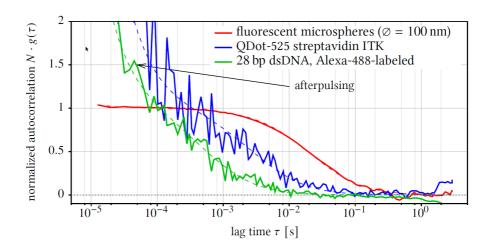

|                       |                  | 5.1.3              | Fluorescence correlation spectroscopy (FCS)             | 119  |  |

|                       |                  | 5.1.4              | Super resolution microscopy                             | 122  |  |

| !                     | 5.2              | LinoSP             | AD                                                      | 123  |  |

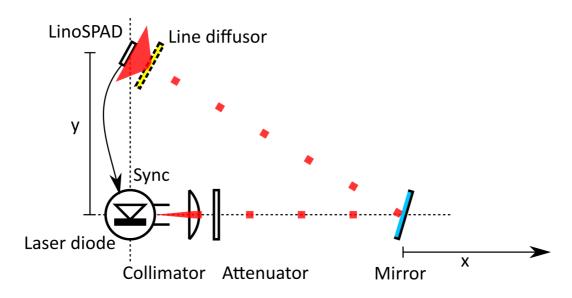

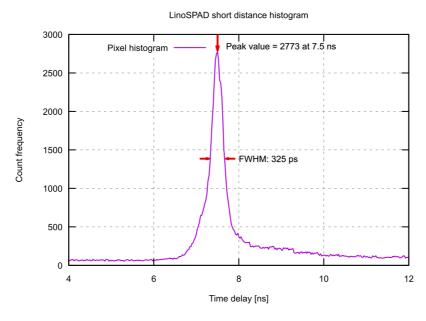

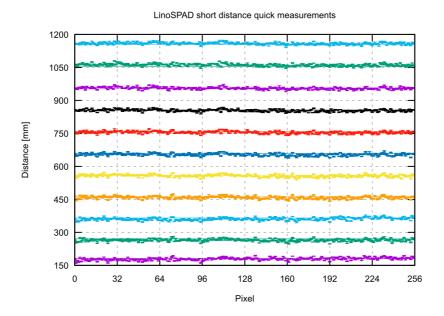

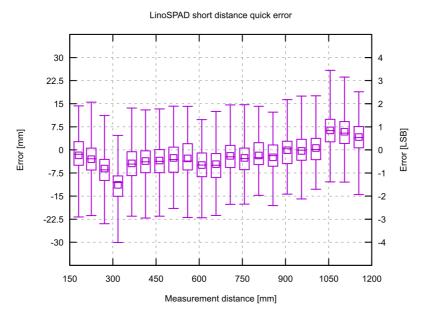

|                       |                  | 5.2.1              | Quantitative range measurements                         | 124  |  |

|                       |                  | 5.2.2              | Scanning 3D depth images                                | 134  |  |

| Chapter 6 Conclusions |                  | sions              | 141                                                     |      |  |

| (                     | 6.1              | Summary of results |                                                         | 141  |  |

| (                     | 6.2              | Current status     |                                                         | 143  |  |

| (                     | 6.3              | Future             | development                                             | 143  |  |

| Referen               | ces              |                    |                                                         | 145  |  |

| List of F             | igures .         |                    |                                                         | ix   |  |

| List of T             | ables            |                    |                                                         | xv   |  |

| List of p             | ublicat          | ions               |                                                         | xvii |  |

| Chip gal              | Chip galleryxix  |                    |                                                         |      |  |

| Acknow                | ledgen           | nents              |                                                         | xxi  |  |

| About t               | About the author |                    |                                                         |      |  |

# Chapter 1 Introduction

After a brief statement of the objectives for this work, this chapter aims to present the history and theoretical foundations behind single-photon image sensors, focusing especially on single-photon avalanche diodes (SPADs) and their applications. On the application side, the focus is on time-correlated single-photon counting (TCSPC) techniques, which make use of the excellent timing capabilities of SPADs.

# 1.1 Objectives of the thesis

The cameras ubiquitous today all around us in robotic vision, surveillance and smartphones are designed to reproduce the macroscopic observation of the environment as seen by the human eye. To achieve an authentic rendering of the environment a large amount of information related to the microscopic and quantum domain of the environment can be discarded. The most challenging aspects for this type of cameras become solely the issues of sensitivity and noise summarized in the signal-to-noise ratio SNR.

After the foundation of quantum mechanics, it became clear that the mechanisms governing our environment cannot be explained on the basis of macroscopic observation alone. The most important restriction in classical imaging approaches is the limited time discrimination, which precludes the observation of very fast phenomena that take place in the nano- and picosecond domains and below. Examples of such fast phenomena caused by the interaction of light particles, photons, and matter are various types of fluorescence where atoms or molecules are excited through the absorptions of photons and subsequent relaxation occurs usually on the time scale of hundreds of picoseconds to a few nanoseconds, a time known as lifetime.

An ideal camera would observe the full objective quantum state of the photons reaching its sensor. We know that this is not possible from Heisenberg's uncertainty principle affecting quantum observations and placing a limit on the accuracy with which the quantum state of a photon can be known. To add a small step on the path to a practical quantum camera is the main objective of this thesis.

Theoretical foundations have been researched and discussed to the point where practical, easy-to-use, and easy-to-understand cameras need to be made available to researchers and the public to give them tools to gain a better understanding of their topic of research and the world around them.

With this goal in mind, the research in this thesis started with the analysis of current single-photon sensitive imaging systems and their limitations, which led to the identification of the primary performance parameters in need of improvement. On the outset of this thesis, these were the camera resolution in both, time and space; while later data transfer speed and sensor flexibility became increasingly important.

The parameters where a SPAD based camera really differentiates itself from other camera technologies are: 1) the achievable speed or frame rate, essentially limited by the rate at which photons can be detected; 2) the time resolution, again, for single frames or single photons depending on architecture; 3) the

absence of readout noise thanks to the early digitization and fully digital architectures, and 4) the compatibility with standard CMOS fabrication processes that allow high levels of integration.

Single-photon detection is used in a wide range of areas where generally the available photon flux is low or where photon arrival timing plays an important role, or both. Examples are detectors for fiber optic communication, astrophysics, quantum computing, medical imaging, range finding, and materials science.

This chapter presents the state-of-the-art in the field of single-photon imaging and the following two chapters present the cameras developed and used for this work. Chapter 2 describes SwissSPAD, a  $512 \times 128$  pixel wide-field SPAD image sensor with global gating and fast readout, Chapter 3 presents LinoSPAD, a  $256 \times 1$  pixel SPAD line sensor with reconfigurable pixel architecture thanks to the close integration with a FPGA. 0 discusses challenges and possible solutions for non-uniformity issues encountered in higher resolution SPAD imagers, and Chapter 5 presents practical results obtained with our sensors.

# 1.2 Photon-counting cameras

Chronologically speaking, the first photon-counting cameras were based on photo-multiplier tubes (PMTs) and micro-channel plates (MCPs). In recent years, with the creation of high quality charge-coupled devices (CCDs) and complementary metal-oxide semiconductor (CMOS) sensors, photon-counting has become possible in these technologies, while speed still is a limitation due to the inherent readout architectures. SPAD imagers, on the contrary, offer single-photon sensitivity with unmatched timing resolution and readout speed.

#### 1.2.1 Photo-multiplier tubes

In the late 19<sup>th</sup> and early 20<sup>th</sup> century the photoelectric effect [1,2,3] and quantization of light in a discrete number of photons was discovered and explained. It did not take very long before the photo-multiplier tube (PMT) was invented as the first device that could be used to detect single photons. In the West, its invention is generally attributed to V. K. Zworykin et al. [4]; though, recent discussions seem to recognize that the invention was made in Russia by L. A. Kubetsky whom Zworykin visited a short time before his famous publication [5].

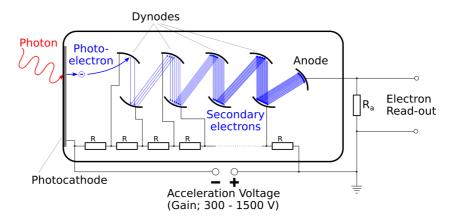

Figure 1.1 shows the schematic of a PMT with an optional scintillator to increase the detection efficiency for high-energy photons or particles. A PMT is a vacuum device multiplying the number of single electrons freed from a photo-cathode by impact ionization on a series of accelerating dynodes where multiple secondary impact ionizations take place. The total amplification factor typically between 10<sup>3</sup> and 10<sup>6</sup>, makes it possible to sense single photon events.

The quantum efficiency of the photo-cathode plays an important role as only the fraction of photons that is converted into electrons can be detected. A scintillator placed above the photo-cathode can be used to generate multiple lower energy photons from single high-energy photons or particles greatly enhancing the chance of detection in these applications.

PMTs have excellent noise and jitter performance making them useful in many applications where extremely low photon counts need to be detected, like for example in astrophysics. The largest market for PMTs with scintillators is nuclear medicine with PET and SPECT cameras. The downside of PMTs is the requirements for high voltages to drive the amplification, the bulky size, and their sensitivity to magnetic fields.

Figure 1.1: Schematic of photo-multiplier tube. A photon is converted into a primary electron on the photocathode, which then generates a larger number of secondary electrons when it impacts the dynodes after acceleration through a high electric field. At the anode, the electron current is multiplied by 10<sup>3</sup>-10<sup>6</sup> depending on the number of amplification stages and electric field strength. A scintillator in front of the photocathode can be used to detect high-energy photons or other particles by converting them into multiple visible photons. (Original image by J. Krieger; public domain.)

As PMTs have been available for many decades, they have been extensively studied. An exhaustive description of these studies is beyond the scope of this thesis. We refer instead to a recent edition of the freely available book "Photomultiplier tubes: Basics and Applications" by Hamamatsu [6].

#### 1.2.2 Micro-channel plates

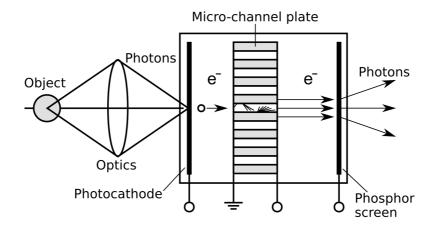

Micro-channel plates (MCPs), also known as micro-channel plates, can be seen as an extension to PMTs that allows retaining the position information of the photon impinging on the photo-cathode such that an image can be reconstructed based on the detected photons. The MCP is an extension for the first image intensifiers, the development of which began around the time when the first PMTs were developed. The image intensifier uses a phosphor screen behind a photo-cathode and a large electric field between the two accelerates electrons such that multiple photons are produced from the high energy with which they impact on the phosphor crystals. The first generation of such devices, working with active infrared illumination, where already used in World War II [7,8].

The MCP operation is perhaps best explained by M. Lampton [9]:

"It is a glass wafer, perforated by millions of electron-multiplying tubes, resembling a compound eye. It can transform a dim pattern of electromagnetic radiation into a brightened, pointillist image [...]".

Figure 1.2 shows a schematic of a MCP image intensifier. The incident photons hit the photo-cathode where they produce an electron that is accelerated and multiplied in a channel behind the cathode, before being converted back into photons on a phosphor screen. Many variations and combinations of the basic principles exist, such as multiple stages or direct position sensing of the electrons at the output using special anodes. A notable example is the H33D detector using of a stack of 3 MCPs followed by position-sensing anodes [10]. Nowadays instead of using the screen directly to display the intensified image, it is coupled to an image sensor either via optics or by using a fiber optic bundle.

Figure 1.2: Schematic of MCP image intensifier. A photon is converted into a primary electron on the photocathode that is accelerated in an electron multiplying tube. The electron shower at the output of the MCP retains the position information of the original photon. When the electrons hit the phosphor screen, they are converted back to a higher number of photons. (Image in public domain.)

Image intensifiers can be time-gated to high temporal resolution. The main advantage of MCP photodetectors is their low noise comparable to that of PMTs and their higher spatial resolution. The main drawback is again the need for high voltages for operation, which makes it difficult to integrate them with low voltage electronics.

Additional information can be found in [11]. MCPs have somewhat merged into PMTs giving rise to different combinations and often creating confusion in the terms.

## 1.2.3 Charge-coupled devices

Willard S. Boyle and George E. Smith invented the charge-coupled device (CCD) in 1969 as a nonvolatile memory [12]. The inventors were awarded the Nobel Prize in Physics in 2009 for the invention, while Michael F. Tompsett is credited for extending the use of CCDs to imaging applications. CCDs have been dominating the imaging market until recently, when they have been gradually supplanted by CMOS image sensors. So much so, that in 2015 market leader Sony announced that they would halt (conventional) CCD production by 2017 [13].

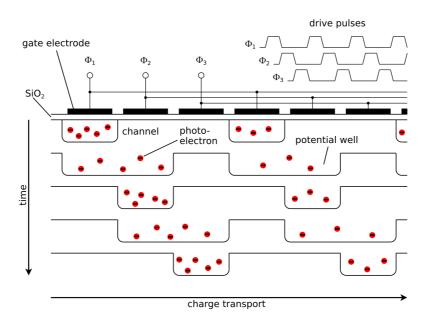

Three steps are needed to operate a CCD image sensor: 1) collect photons and convert them to electrical charge 2) transport the charge (or information) from the point of collection to the sensing elements 3) measure the transported charge, converting it into an image for display or storage.

The CCD solves these basic steps in a simple yet ingenious manner. The basic idea is to collect charge carriers generated from photon absorption in a potential well in each pixel formed by an appropriately doped and biased semiconductor area creating a MOS capacitor. After collection, the charge packets are transported from one well to the neighboring by applying a voltage sequence to shift potential wells. Once the charge reaches the end of the transport chain, it is converted in a so-called floating diffusion, and, later, into a digital signal for display or storage.

Figure 1.3: Charge transport illustration for a 3-phase CCD. The charge in the well is transported by sequencing the control voltages of adjacent gates. (Image inspired by [14].)

Figure 1.3 illustrates the charge transport mechanism in a CCD. Charge packets are moved from one place to the next by applying a sequence of gate control signals, essentially creating moving potential wells. The simplified architecture of a linear device with surface channels shown here was soon improved upon, with buried channels for increased charge transfer efficiency and better noise characteristics. Backside illumination was introduced to reach a fill factor of 100% and cooling was used from the beginning in scientific CCDs for additional noise reduction.

In 1976, image sensor development driven by the requirements of the large space telescope (LST) later named Hubble Space Telescope (HST) resulted in a  $800 \times 800$ , buried channel, backside-illuminated device with polysilicon gate [15] much like the CCDs widely used in image sensors until recently when they were replaced with additionally enhanced CCD or CMOS.

A quite natural development with the CCD was to couple it with an image intensifier employing an MCP and thereby giving birth to the intensified CCD (ICCD, [16]). The combination of a vacuum device operating at high voltages and a solid-state device was not optimal though as the image artifacts of MCPs were now imported to the CCD. The inherent possibility of gating the intensifier was on the other hand very welcome since more time can be used to read a CCD without smearing when a shutter blocks light during this time.

Smearing appears in CCDs and other image sensors when the light accumulation time on individual pixels is not the same for the whole sensor. It can be prevented easily by using a shutter to block light from reaching the sensor while it is read out. This can become impractical for larger sensors and reduces the photon efficiency by the fraction of time used for the readout process. In CCDs, the problem was addressed with interline- and frame-transfer sensors, which provide a second charge storage space for each pixel, where the image is quickly transferred to before being read out, thus preventing image smear. The price to pay for this solution is increased chip area and, in the case of the interline CCD, reduced fill factor.

Sometime later, the vacuum device in the ICCD was replaced with a solid-state solution again, like the sensor itself, when the electron-multiplying CCD (EMCCD, [17]) was invented. In an EMCCD, image amplification takes place during special multiplication stages in the charge transfer process. By using higher electrical fields, impact ionization is induced multiplying the charge collected by the CCD. EMCCD were almost immediately a viable alternative to ICCDs and replaced them quickly where no gating was needed.

#### 1.2.4 Active pixel sensors in complementary metal-oxide semiconductors

While the photon collecting pixels in CCDs are passive elements, an active pixel sensor (APS) is based on active, amplifying pixel circuits. When an APS is realized using common complementary metal-oxide semiconductor fabrication processes it is classified as CMOS APS or CMOS image sensor (CIS). Active pixel sensors were actually realized before CCD sensors, but could not be made to work well because of too large parameter variations and were quickly overtaken by CCDs. CIS eventually reappeared as low quality image sensors that could be implemented alongside other electronic and it was only from 1993 [18] onwards that large-scale image sensor development in CMOS was undertaken, leading to the image sensors now ubiquitous in everyday devices and to the announcement of Sony to stop CCD production.

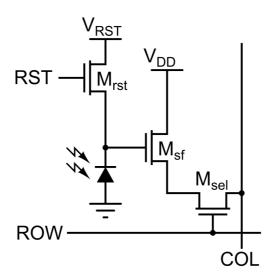

Figure 1.4 shows the CMOS active pixel in its simplest configuration using three transistors. A photodiode generates electrical charges in a capacitance formed by its own junction and the gate of  $M_{sf}$ . After an accumulation period has elapsed,  $M_{sel}$  is activated by the ROW selection signal connecting the pixel to readout line COL to sense the signal. Once the signal has been recorded, the pixel charge is emptied through  $M_{rst}$  by activating the RST signal.

Figure 1.4: Circuit schematic of a 3T CIS pixel as in [19]. A photodiode generates electrical charge collected in the capacitance of its junction and the gate of the source follower transistor  $M_{sf}$ .  $M_{sel}$  is activated by the ROW signal and used to connect  $M_{sf}$  to the readout line COL to sense the signal induced by the collected photo-charge. RST is used to switch on  $M_{rst}$  to reset the photodiode capacitor for the next charge integration period.

The most important advantage of CIS compared to CCD is their immediate compatibility with electronic circuits on the same substrate close to the sensor. Without the need to modify the fabrication process to

build the readout electronics, this causes CIS to be low-cost imagers. Additionally, CIS can directly profit from the advancements of CMOS fabrication processes with shrinking feature sizes and lower power operation.

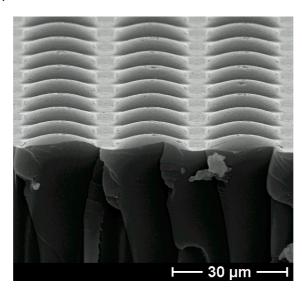

The inclusion of active devices in each pixel of an image sensor has the drawback of reducing the active area, and thus the fill factor of the sensor. A low transistor count is therefore preferred, especially for fabrication processes with larger feature sizes. The wiring needed to connect the pixels also absorbs a portion of the incident light for front-illuminated sensors. Microlenses on the pixels can be employed to reclaim insensitive area due to electronics.

Typically, the 3T pixel is read by cycling on the rows of the sensor producing an image line by line (rolling shutter mode). This process creates distortions in moving objects because the integration period is not the same, but it is shifted from one row to the next. An additional transistor can be used to solve this issue and introduce a global gating (global shutter mode).

Important progress in CMOS APS noise performance has been made with the introduction of correlated double- and multi-sampling techniques through which CMOS performance began to rival that of CCD [19]. The main technology required to perform CDS, is the pinned photodiode, invented by Nobukazu Teranishi [20,21], that enables the transfer of all charges accumulated during exposure to a temporary analog storage unit, known as floating diffusion, which transforms charges into a voltage that can be read out independently. Pinned photodiodes eliminated charge sharing during readout, while allowing low parasitic capacitance at the photodiode, thereby ensuring high conversion gain.

A more recent development is the introduction of scientific CMOS (sCMOS), which incorporates multiple advanced techniques resulting in CIS with performance comparable to the most advanced CCD and EMCCD cameras suitable for scientific applications [22]. Hybrid approaches, bump-bonding a CCD substrate to a CMOS carrier with readout electronics were also studied [23] for some time but introduced more problems in the fabrication than were solved through advancements in purely CMOS designs.

At this time, there are still large investments being made in the research of CIS coupled in part with generic research in advanced CMOS. There are even CCD like structures now implemented purely in CMOS [24]. This brings us to the main topic of this thesis that is single-photon avalanche diodes in standard CMOS that will compete with the classical CIS.

# 1.3 Single-photon avalanche diode and imager

From the CMOS image sensor and the basic 3T pixel shown in Figure 1.4 a CMOS single-photon avalanche diode (SPAD) based sensor can be understood as a CMOS image sensor with a SPAD in the place of the usual photodiode. This section introduces SPAD based image sensors and the associated terminology used throughout this work.

The SPAD is a silicon diode made like most diodes from a p-n-junction. The avalanche in its name comes from the operating regime of the diode when a large negative bias voltage is applied. In that regime, the electric field in the diode is large enough that a single electron traveling through the diode gains enough energy to free additional electrons on impact and an avalanche of electrons is observed. The single-photon in SPAD then comes from the fact that one single photon is enough – with some probability – to trigger

the avalanche of electrons in the device, causing a macroscopic current to be observed when the photon is absorbed by the SPAD.

#### 1.3.1 Operation of a SPAD

A silicon single-photon avalanche diode is a p-n junction biased above its breakdown voltage and connected to an avalanche quenching and recharge circuit. Figure 1.5 a) shows the simplest such circuit composed of a SPAD, a voltage source and a ballast resistor. Part b) shows the current/voltage characteristic of the SPAD and defines the three operating regimes: breakdown, reverse and forward bias. The voltage at which the diode becomes conductive between the reverse bias and breakdown regime is the diode's breakdown voltage. Parts c) and d) of Figure 1.5 show a SPAD operating cycle and the anode voltage during one photon detection respectively. The duration of a detection cycle is on the order of tens to hundreds nanoseconds.

Figure 1.5: SPAD circuit and operation. a) shows the simplest SPAD circuit for single-photon detection, b) shows the current-voltage characteristic of the SPAD and its operating regimes, c) the idle operating point and one detections cycle and d) the anode voltage v(t) during one detection. (Adapted from [25].)

The SPAD will sustain the voltage above breakdown over its terminals and remain in idle state as long as there are no free charges in the region of high electric field that could start an avalanche. A photon that is absorbed in this region and converted into an electron-hole pair causes the now separated charges to be

rapidly accelerated and multiplied, creating a current through the device. As the current through the device and ballast resistor rises so does the voltage over the resistor according to Ohm's law. This leads to a reduction of the voltage on the terminals of the SPAD, bringing it to the operating point where the electron avalanche is no longer sustained and multiplication stops. The free charges in the diode are then evacuated through the resistor and the voltage over the SPAD restored when it returns to the idle operating point.

Upon photon absorption in the multiplication region of the SPAD and the onset of the avalanche, the voltage across the ballast resistor rises sharply indicating the arrival of a photon. The signal at the anode of the SPAD is directly digitized using a comparator, in the simplest case a CMOS switch or inverter.

The rising edge of the voltage curve indicates precisely the moment when a photon was detected and a timing circuit connected to the digitized signal of the SPAD is used to obtain the photon arrival time in time-correlated single-photon counting applications. In applications where timing information is not needed, the signal is used to increment a photon counter or is directly routed off the sensor.

#### 1.3.2 Fabrication of SPADs

Silicon SPADs are implemented in two main styles. The first style uses a p+ -  $\pi$ -p-n structure [26] and is known as reach-through APD (RAPD) or vertical APD from the extension of the depleted region spanning from anode to cathode vertically through the structure. Thanks to its deep junction the multiplication region is further away from the surface and the RAPD reaches high quantum efficiency up to the absorption limit of silicon around 1.1  $\mu$ m. The drawback of the deep absorption region is higher timing uncertainty due to the charges drifting until they reach the multiplication region.

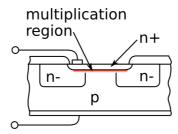

Figure 1.6: Early planar SPAD. A planar SPAD is formed in a CMOS process using a n+ implantation in a p-type substrate. A guard-ring is formed from n- implants. (Image adapted from [27].)

The second implementation style yields shallower structures fabricated in silicon by implanting p and n layers in CMOS compatible processes to form the diodes. The group around Cova have been particularly active in the research of these devices since the 1970s. They describe a variety of structures [28], which were already used to measure fluorescence decay-time constants [27]. The common denominator of these planar structures is a region of high electric field where avalanche multiplication occurs that is surrounded by a guard ring preventing excessive field strength at the extremities to ensure uniform breakdown voltage and sensitivity across the device.

Figure 1.6 shows an early planar SPAD as described by Haitz [29] and implemented by Cova [27]. The multiplication region is formed between the shallow n+ implantation and the p-type substrate and a deeper

n- guard ring is used to achieve uniform electric field. In more recent SPAD structures, all contacts are made from the top using implants unlike shown in the image.

The first SPADs were not fabricated in processes also used for electronic circuits but rather were singular devices or small arrays that had to be connected to interfacing electronic for biasing, avalanche detection and quenching. It was with the integration of SPADs in standard CMOS combined with fully digital readout electronics that they became approachable for more applications and the realization of larger arrays became possible.

The first SPADs implemented in a fully standard CMOS fabrication process was shown by Rochas et al. in 2003 [30] and was made in an 800 nm twin tub technology. After this breakthrough, novel SPAD architectures in smaller technologies and integrated arrays followed in rapid succession. SPADs in 350 nm appeared in 2006 [31], in 180 nm with shallow trench isolation (STI) also in 2006 [32], in 130 nm in 2007 [33], in 90 nm in 2010 [34] and in 65 nm in 2013 [35].

Figure 1.7: SPAD in 65 nm standard CMOS. The multiplication region is defined by the n+ - p-well junction and is surrounded by an n-tub guard ring. (Image redrawn from [35].)

Figure 1.7 shows one of the latest SPADs in standard CMOS integrated in a 65 nm technology [35]. The basic structure explained above is still present with the multiplication region surrounded by a guard ring to prevent premature edge breakdown (PEB). Today SPADs exist in a wide variety of implementations, within n-type or p-type substrates, with shared or isolated wells and with shallower or deeper junctions to optimize certain of the typical characteristics explained in section 1.3.4.

Specially modified CMOS fabrication processes are also investigated for SPADs often targeting better noise performance compared to the standard processes not optimized in this regard. A hybrid approach combining different processes for the SPAD and electronics is also possible at the expense of fabrication complexity.

#### 1.3.3 Integrated quenching and recharge for CMOS SPADs

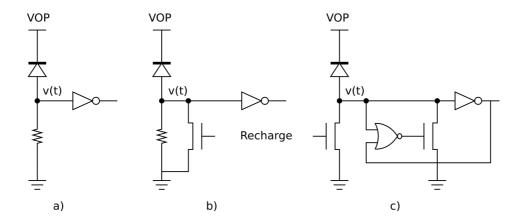

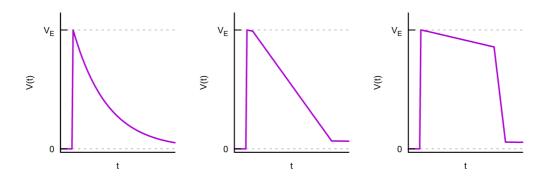

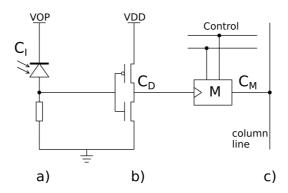

When SPADs are implemented in CMOS, they need to be interconnected such that the desired bias voltage can be applied over the SPAD and that avalanches can be sensed and processed. Figure 1.8 shows three examples of SPAD front-end circuits differentiated by the way, in which the SPAD bias is restored after an avalanche event. Figure 1.9 shows the associated waveforms for the SPAD anode voltage during a detection cycle.

Figure 1.8: SPAD quenching and recharge examples. The SPADs are operated at a bias voltage of  $V_{\rm OP} = V_{\rm bd} + V_{\rm ex}$  above the breakdown voltage. All circuits use passive quenching stopping the avalanche when the voltage over the SPAD drops below the breakdown. Circuit a) shows passive recharge, b) shows single-slope active recharge and c) shows double-slope active recharge [36].

The simplest circuit shown in a) uses a passive recharge. When an avalanche occurs, it is quenched when the voltage over the resistor reaches  $V_{\rm ex}$  and brings the voltage over the SPAD below its breakdown voltage. Once the avalanche is stopped, the bias over the SPAD is restored to  $V_{\rm OP}$  as the avalanche charges drain through the resistor. The circuit in b) adds a simple active recharge in the form of a transistor acting as a current source that recharges the SPAD using a constant current after an avalanche. A more advanced recharge mechanism is shown in c) and named double-slope active recharge [36]. A transistor configured as current source keeps the SPAD biased for detection and starts a slow recharge after an avalanche. A larger transistor accelerates the recharge on a voltage interval chosen through careful sizing of the transistors constituting the inverter and NOR-gate.

Figure 1.9: SPAD anode voltage for different recharge implementations. The waveforms show the SPAD anode voltage for a detection cycle using passive, single-slope active and double-slope active recharge. Typical recharge times are tens of nanoseconds.

The resistors shown in recharge implementation a) and b) are implemented using MOS transistors. Active recharge schemes offer the advantage that the dead time of the SPAD can be better controlled for more uniform detection and timing response in an array, especially under higher illumination. The double-slope recharge offers the added advantage of reducing afterpulsing by giving the avalanche charges more time

to evacuate the SPAD before restoring the bias quickly to return to the idle state ready for the next detection.

Active quenching schemes can also be implemented by adding a switch over the SPAD and using it to reduce the SPAD bias to a set voltage below the breakdown quicker than through the avalanche alone. Active quenching and recharge schemes can be effectively combined into a shutter for the SPAD to define the photosensitive time window with great accuracy.

#### 1.3.4 SPAD metrology

Now it is time to introduce the basic terms of SPAD metrology used throughout the remainder of this thesis in the characterization and comparison of the fabricated SPAD arrays. A much more detailed introduction to the metrology of SPADs can be found in [37].

#### Breakdown, excess and operating voltage

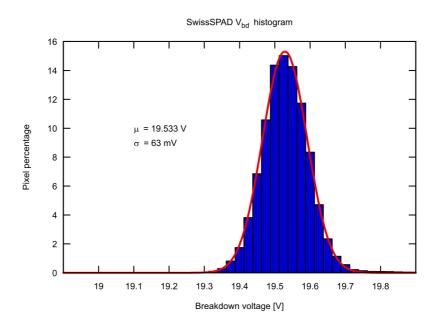

Probably the most important and defining parameter for an avalanche diode is its breakdown voltage  $V_{\rm bd}$ . The breakdown voltage of a SPAD is the voltage above which impact ionization occurs and current multiplication takes place when free charges are present in the diode. The breakdown voltage of an integrated device is measured from the I/V characteristic or, for digital outputs, using its dark count rate and sweeping the bias voltage.

The operating voltage of a SPAD corresponds to the voltage at which the SPAD is in idle state. The operating voltage and the breakdown voltage are related through the excess bias voltage by:

$$V_{\rm ex} = V_{\rm OP} - V_{\rm bd} \tag{1.1}$$

#### Dark count rate (DCR)

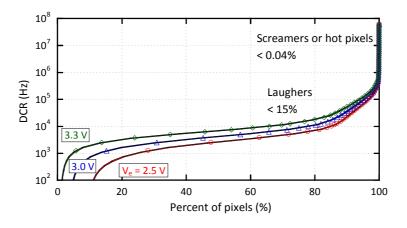

Figure 1.10: Cumulative DCR as a function SPAD population. (Courtesy: Yuki Maruyama, JPL, Pasadena, U.S.A.)

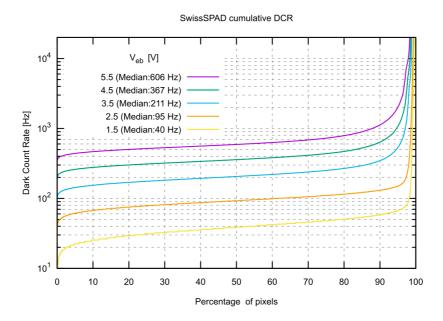

The dark count rate (DCR) of a SPAD measures its noise in the unit of avalanches per second without any incident photons. Dark counts are a result of thermal processes in the SPAD junction and of tunneling effects. Thermal DCR can be reduced by operating the SPAD at a lower temperature such that DCR becomes dominated by tunneling effects. For a given SPAD size and fabrication technology, DCR depends on

$V_{\rm ex}$  and temperature. For an array, it is typically reported as cumulative distribution to show the fraction of hot pixels with very high DCR, as shown in Figure 1.10. Hot pixels are due to defect sites in the silicon, where hot SPADs are recognized as devices with more than two orders of magnitude in DCR above the median and laughers more than one.

#### Photon detection probability (PDP)

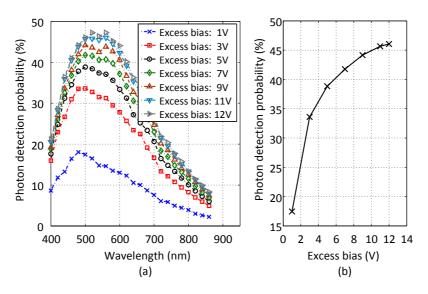

The photon detection probability (PDP) of a SPAD is defined as the probability with which a photon hitting the multiplication region of the SPAD generates an avalanche. PDP is defined as follows:

$$PDP = Pr(avalanche) QE,$$

(1.2)

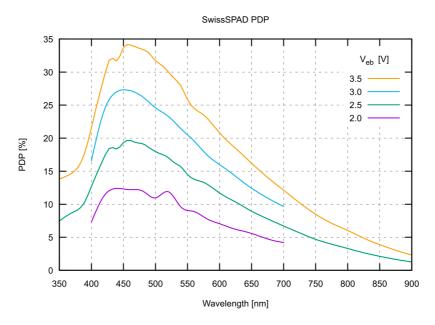

where the quantum efficiency (QE) of a SPAD depends mostly on the wavelength of incoming photons and Pr(avalanche) depends on the excess bias voltage applied to the SPAD. PDP is commonly reported as a function of wavelength, where planar SPADs with shallow junction depth as used in this thesis typically show highest sensitivity between 400 nm and 500 nm. Figure 1.11 shows a typical PDP from a SPAD published by Chockalingam Veerappan as a function of wavelength and excess bias voltage (a). Note the PDP compression at high excess bias voltages (b). This compression is useful in the case of large arrays of SPADs, as it reduces the sensitivity of PDP on variations in the breakdown voltage, thereby enabling high uniformity across large arrays.

Figure 1.11: (a) PDP as a function of wavelength and excess bias voltage. (b) Peak PDP as a function of excess bias voltage. (Courtesy: Chockalingam Veerappan, [38,39])

#### Fill factor and photon detection efficiency (PDE)

When SPADs are implemented as arrays the sensitive area of the detector, the combined multiplication regions, cannot reach 100% due to non-sensitive guard rings and in-pixel electronics. The fill factor is defined as the ratio between the active area in an array of SPADs and the total area occupied by the array. Using the fill factor the photon detection efficiency (PDE) is then defined as:

$$PDE = Fill factor \times PDP. \tag{1.3}$$

In general, fill factor is a function of area, since larger pixels can typically achieve a better fill factor. This is due to the overhead of SPADs in terms of the geometries required for preventing edge breakdown and to reduce crosstalk.

#### Dead time

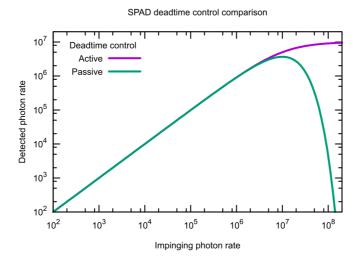

After an avalanche occurs in a SPAD, the bias drops below the breakdown voltage and another photon cannot be detected before the bias is restored above breakdown. This time, during which the SPAD is not sensitive to photons and is effectively dead, is called dead time. In passive recharge, the SPAD insensitivity is not absolute and, even during recharge, the SPAD has a reduced but non-zero PDP. This makes it difficult to determine an exact dead time. In active recharge, on the contrary, the SPAD is held off for a precise time, thus the dead time becomes precise and programmable. The dead time,  $T_{\text{dead}}$ , limits the maximum rate at which photons can be detected, or maximum photon flux  $PF_{\text{max}}$  in a SPAD by imposing a minimum time between consecutive detections, whereas in active recharge the maximum photon flux a SPAD can detect is:

$$PF_{\text{max}} = 1/PDP \times T_{\text{dead}}.$$

(1.4)

In passive recharge,  $PF_{\text{max}}$  is divided by e, due to the partial PDE effect. In addition, the counts reduce upon reaching  $PF_{\text{max}}$ , because photon detections become fused in time, not enabling one to distinguish individual events. This effect, compared to the behavior of active recharge, is shown in Figure 1.12. Typical dead times are in the tens to hundreds of nanoseconds. Even though shorter dead times have been reported, it is usually preferable to keep the dead time relatively long, in order to minimize parasitic effects, such as afterpulsing.

Figure 1.12: Detected vs. impinging photon rate in a SPAD with active and passive dead time control. The detected photon rate is calculated for a dead time of 100 ns and an ideal SPAD with zero noise and 100% PDP according to [40].

#### Timing resolution (Jitter)

The timing resolution of a SPAD is defined by its response to single and multiple photon detections. It measures the time it takes for the output voltage of the SPAD to rise over a threshold (typically 90% of  $V_{\rm ex}$ ) after a photon triggers an avalanche. Ideally, this time would always be identical regardless of the location

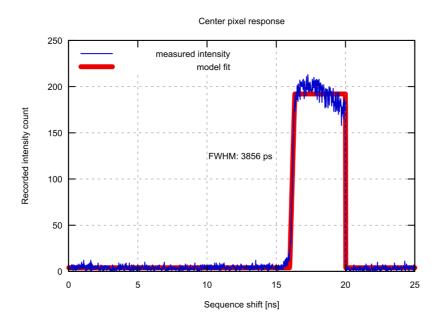

where the photon strikes. The timing uncertainty or jitter depends essentially on the architecture, mainly the size of a SPAD and is typically in the range of a few hundred down to tens of picoseconds. It is measured in many ways, however, the standard one is based on time-correlated single-photon counting (TCSPC), in which successive exposures of a SPAD to 'Dirac' like pulses of light, such as laser pulses, are evaluated in terms of the SPAD response by means of a precise time digitizer. After multiple measurements a histogram is built, which will approach the theoretical time photon response or instrument response function (IRF) of the SPAD when a very large number of measurements are performed. The time uncertainty is usually represented in term of the standard deviation of the Gaussian fit of the IRF or the full-width-at-half-maximum of the same.

#### Afterpulsing and crosstalk

Afterpulsing and crosstalk are noise sources correlated to detections in SPADs. Afterpulsing refers to spurious pulses observed after a detection in the same SPAD and it is explained by avalanche charges trapped in defects and released some time later. Afterpulsing probability in a SPAD is reduced by using fabrication processes with smaller defect rate and it can be mitigated in fabricated devices by imposing longer dead times on the SPADs to give the charges time to evacuate the multiplication region.

Crosstalk occurs in SPAD arrays and is a noise source correlated to detections in neighboring SPADs. It can occur electrically when charges generated by an avalanche diffuse to the multiplication region of another SPAD. Electrical crosstalk is contained by isolating individual SPADs from one another or creating biased diffusions to collect free charges. The other way for crosstalk to occur is optically. When an avalanche occurs in a SPAD, some of the accelerated charges can generate photons instead of freeing additional electrons. When these photons reach the multiplication region of another SPAD, they can trigger an avalanche there [41].

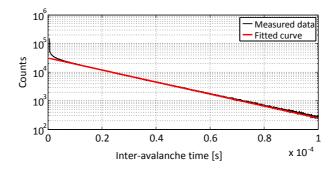

Figure 1.13: Afterpulsing. The plot shows the inter-arrival time histogram measured from a SPAD when exposed to dim light or in the dark. The afterpulsing phenomenon causes counts in excess of the normal exponential response due to Poisson statistics. (Courtesy: Chockalingam Veerappan, [38,39])

#### Non-uniformity

For SPADs integrated in detector arrays, the individual metrics given above are evaluated for every one of them and, ideally, they are the same for all. As this is not the case, non-uniformity measures are introduced to characterize array detectors. Typically the distributions of individual characteristics are reported in a histogram giving the mean value and the spread either as standard deviation ( $\sigma$ ), or as full width at half maximum (FWHM). For a normal distribution, the two are related by FWHM =  $2\sqrt{2 \ln 2} \ \sigma \approx 2.355 \sigma$ .

The most important non-uniformity measures for SPAD arrays are those of breakdown voltage and DCR. Breakdown voltage non-uniformity leads to non-uniformity in excess bias and thus in PDP. DCR non-uniformity also leads to non-uniform light response over the array. DCR non-uniformity can be reduced by operating SPADs at lower temperatures.

#### 1.3.5 SPAD array architectures

When SPADs are assembled into arrays to make an imager, different types of architectures can be chosen depending on the requirements. The first step in the design of a larger array of SPADs is to decide on a pixel architecture and its functionality.

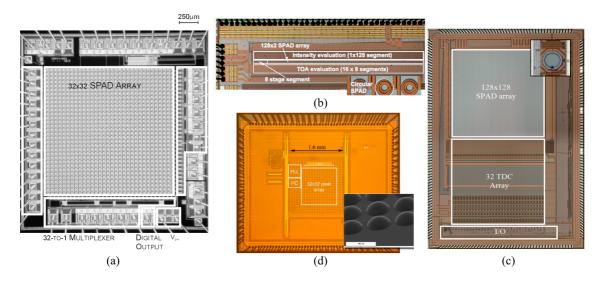

A pixel can be as simple as a SPAD diode and a transistor for passive quenching as in the first SPAD arrays [42] or as complex as a SPAD diode, a Vernier delay line and thermometer coder, a frequency doubler, a 6-bit counter and a 10-bit memory, as in Megaframe [43]. A simpler pixel has the advantage of a higher fill factor, which results in a sensor with higher PDE. A complex pixel on the other hand can for example provide photon timing information concurrently on all pixels or count photon events for a long time and high dynamic range before it needs to be read out. Most SPAD sensor architectures will strike a balance between the two extremes, with a trend to simpler pixels favoring high fill factor and more shared functionality at the column level. Figure 1.14 shows several examples for pixel architectures and resulting sensors.

Functionality typically included in a pixel, besides the mandatory quenching and recharge, are a number of digital counters starting at one single bit memory. Multiple counters can be multiplexed for continuous synchronous operation of the whole sensor or switched at a fast rate to demodulate the received signal [36]. An analog counter can also be advantageous when it offers a larger counting range than a digital counterpart using the same die area. As mentioned before, a timing circuit can also be added to every pixel to generate timestamps for each detected photon.

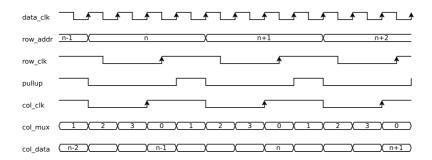

In the second step, the pixels are assembled (at least conceptually) into rows and columns typically assigning control signals to rows and data signals to columns. Global control signals are also possible, and in the majority of designs, the pixels share common bias voltages. Pixels are accessed by addressing their row and then reading the data transferred to the column lines. Data can be for example the event count since the last reset or the recorded timestamp. Pixels without internal storage can only send live events when they are connected to the column lines [44]. This type of pixel is only interesting in high intensity applications as the overall photon efficiency is greatly reduced. The number of output lines on a sensor determines how the data is further handled until it reaches the sensor's interface. In most cases, there is some kind of multiplexing or serialization needed to read the data of a sensor row.

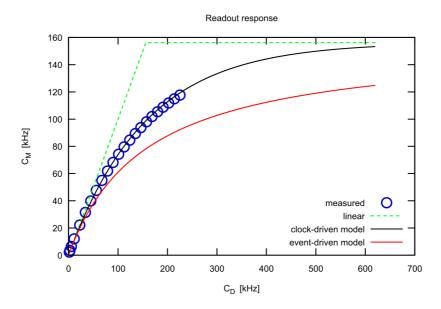

Two different concepts can be employed with respect to the column organization, namely a clock driven or an event driven architecture. In the clock driven architecture, each row of pixels is read out at a fixed rate by cycling over the rows of the sensor. SwissSPAD, presented in Chapter 2, follows this approach. In the event driven approach all pixels of a column are connected in parallel to the column lines and send their row address (and additional information) when an event is detected [45]. Conflict resolution circuitry is needed to prioritize events in the case of multiple events happening at the same time [46]. Hybrid architectures are also a possibility, for example an event counter in each pixel and precise timing circuits shared for each column.

Figure 1.14: SPAD arrays and readout architectures [47]. (a) Random access 32x32 SPAD array [48]; (b) latchless access 128x2 SPAD array [49]; (c) event-driven access with column-parallel TDCs [44]; (d) pixel-parallel TDCs with microlenses in the inset [50]

Advances in CMOS process technologies have resulted in shrinking feature sizes to allow more and more functionality in a sensor and even on a single pixel while maintaining a good fill factor. Additionally, part of the fill factor lost due to in-pixel electronics and guard-rings can be reclaimed by using micro lenses. Another promising avenue for sensors with high functionality and high fill factor are various forms of CMOS 3D integration, which places the photo-sensitive front-end and processing back-end circuits on separate dies [46,51].

LinoSPAD, presented in Chapter 3, is a special sensor architecture in that the SPAD sensor itself is quite simple. It is one row of 256 pixels where each pixel has a dedicated output line. Through the close coupling with a FPGA, we create essentially a reconfigurable pixel that can be optimized in functionality for different applications. The first pixel architecture realized contains 64 column-level TDCs each shared among four pixels. This architecture evolved from event counters for each pixel to TDCs that send timestamps at a high rate, to the current state of integrated histogram engines and processing as described later.

## 1.4 Time-correlated photon counting

The fast time response is one of the characteristics that differentiates SPAD based image sensors from other classes of image sensors. A SPAD detecting a photon delivers a macroscopic signal with a precision in the picosecond range. Measuring the timing information of that signal allows us to assign a timestamp to individual photons and use that information to construct histograms of photon arrival times useful in many measurement applications of short-lived phenomena.

Time-correlated single-photon counting (TCSPC) is generally used in conjunction with a photon source operated synchronously to the detector. The synchronization provides a common timing reference point for the timestamps generated by the photon-counting sensor, such that histograms over multiple illumination periods can be built.

Two main techniques are used for the illumination and correspondingly for the detection. On the illumination side, one has to decide on the modulation scheme between pulsed and continuous excitation. On the detector side, the choice is between direct and indirect time-of-flight detectors. Indirect time-of-flight detectors measure the phase and amplitude for the detected signal without necessarily assigning timestamps to individual photons. This can be done using synchronously gated counters. Direct time-of-flight detectors on the other hand measure the time of arrival of individual photons and report timestamp values. Time-to-digital converter circuits are needed in these detectors.

The SwissSPAD sensor presented later can be used for indirect time-of-flight measurements even though it is not optimized for these kind of measurements, whereas the LinoSPAD sensor with FPGA TDCs is used for direct time-of-flight measurements.

## 1.5 Applications of single-photon cameras

Single-photon cameras are mainly used in applications where the timing of individual photons is important or when the number of photons is very low. Analogous to the advance of conventional CMOS image sensors in more and more areas that were once dominated by early analog sensors or CCDs, CMOS SPAD based sensors make their advance in more and more applications where non solid-state single-photon counting cameras were used before.

The main applications where CMOS SPADs have become increasingly used are the imaging of fast and repetitive phenomena in the basic sciences of physics, chemistry and biology. The applications where the cameras developed and presented in this work have been used are briefly introduced in the following subsections and more details and results will be given in separate sections.

## 1.5.1 Fluorescence lifetime imaging

Fluorescence lifetime imaging microscopy (FLIM) is a standard technique [52] used to distinguish fluorescent molecules either freely diffusing or attached as marker to other molecules. FLIM is not solely interested in the fluorescence intensity captured by the imaging system but also in the lifetime of the fluorophores after they have been excited. The excitation is commonly achieved using a pulsed laser and the fluorescence response of the observed sample is collected using a confocal imaging setup. The fluorescence lifetime depends on the used dye, but also on their environment characterized by pH or concentrations of other molecules. It can also depend on the state of the fluorophore marker, whether it is bound to an acceptor molecule or not.

The SwissSPAD sensor was used to create a wide-field fluorescence lifetime imaging system by using the global shutter circuit for time-gating the photo-sensitivity in synchronous operation. The chip was successfully used in super resolution microscopy, triggering improved data analysis algorithms [53] and enabling industry to develop advanced microlens fabrication processes. The initial methods and algorithms with experimental results of lifetime measurements on dye solutions with different short- and long-lived fluor-ophores are presented in section 5.1.1 and were the subject of several publications [54,55,56].

## 1.5.2 Quantum random number generation

Many algorithms of modern cryptography rely on random numbers to protect our digital secrets. Random numbers are used to generate passwords, cryptographic keys and signatures and to secure transactions in

distributed currencies. Although for some applications like test pattern generation or Monte Carlo simulations, the use of pseudorandom numbers is sufficient, even desirable, true random numbers are increasingly used either due to security concerns or for regulatory reasons.

The increasing demand for applications requiring secure communication like e-banking, credit cards, cell phone encryption calls for high quality and at the same time high speed random numbers. A large network server with thousands of simultaneous connections might require a random number throughput of several Gb/s.

True random number generators (TRNGs) reaching high speeds have been proposed using a number of different mechanisms. Examples include thermal jitter in ring oscillators, RAM write collisions, flip-flop metastability in FPGAs [57] and ASICs [58]. In addition, optical effects based on LEDs and lasers have been proposed as source of entropy at high rates [59,60]. What is needed is a high-speed generator of true random numbers that can be realized at low cost.

To exploit the quantum nature of photons seems to be a good start to create an effective TRNG. Photons are available almost anywhere in abundant quantities and they carry inherent random properties if observed at the individual level.

The SwissSPAD sensor was used to explore the possibility of using SPADs interacting with photons as source of randomness. The high number of SPADs available and the high throughput of the sensor proved to be advantageous to that end. The main outcomes of the experimental work with SwissSPAD as TRNG is described in section 5.1.2 and was the subject of several publications [61,62,63].

#### 1.5.3 3D time-of-flight

3D cameras experienced a popularity boost when Microsoft released the Kinect 3D camera for their game console in 2010. Intel was able to follow up with the release of the RealSense range of 3D cameras putting 3D cameras into the reach of a large public. These 3D cameras use the structured light approach for 3D scene reconstruction that work by projection a known pattern on the scene and analyzing the distortion seen by the camera.

With the LinoSPAD camera, we use the time-of-flight approach to 3D imaging that reconstructs depth information from the time it takes for a flash of photons to travel to an object and back to the sensor. Time-of-flight imaging requires precise timing of the arrival of photons on the camera. For this task, an array of time-to-digital converters has been implemented in the FPGA connected to the LinoSPAD sensor array. The TDCs are connected to histogram engines, which create and process full time-of-arrival histograms in the camera before sending them to a computer. The camera system has been presented for the first time at the SPIE Photonics Europe conference 2016 [64].

#### 1.5.4 Other uses of SPAD imagers

This section lists very briefly other applications that are possible with SPAD based imagers and that have in part been realized with the cameras developed in the work of this thesis.

#### **High-speed intensity**

A SPAD based camera can be used as a normal intensity camera computing an intensity value for each pixel and producing an image on a computer screen. The high speed at which SPAD cameras can do this is

one of the distinctive characteristics. The SwissSPAD camera is essentially limited in the frame-rate it can deliver by the capabilities of the I/O circuits of the sensor. The 128 lines can be operated reliable at frequencies up to 100 MHz and with that, the camera can reach frame rates of almost 200 kHz. Some image sequences are shown and the data rate limits discussed in section 2.5.9.

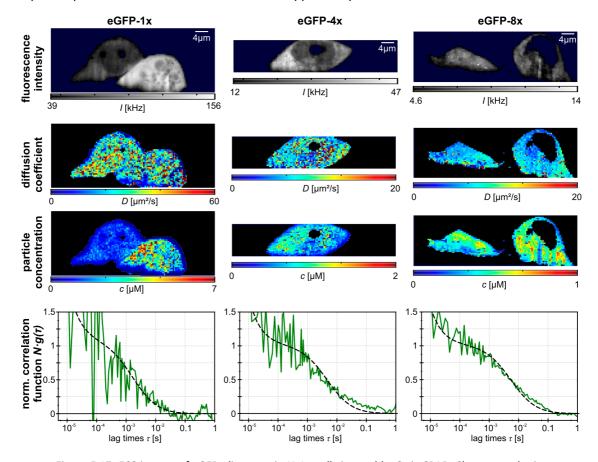

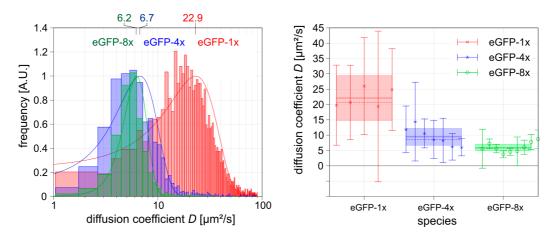

#### Fluorescence correlation spectroscopy

Fluorescence (cross-)correlation spectroscopy, F(C)CS is used to probe the mobility of fluorescing molecules in a small volume defined by the focus of the observation volume of a microscope. Usually confocal microscopes are used for FCCS. One records the fluorescence fluctuations from such a volume with high temporal resolution and then calculates their autocorrelations function. The autocorrelation function of the fluorescence intensity is characterized by the concentration (amplitude for  $\tau=0$ ) and diffusion coefficient (decay) of fluorophores in the observed volume. If several volumes are observed simultaneously (e.g. in a multi-confocal microscope or a TIRF or SPIM), the cross-correlation function between distant volumes can be used to measure the direction and velocity of flows in the sample. In a wide-field setup, the cross-correlation between neighboring pixels can be used to measure directed flow. The combination of single-plane illumination microscopy (SPIM) and FCS was used to build a wide-field FCS setup and SwissSPAD was used as sensor with high temporal resolution to measure short decay times.

Chapter 24 in [65] discusses the theory of FCS in detail. An overview of the SwissSPAD FCS setup and the measurement results is presented in section 5.1.3.

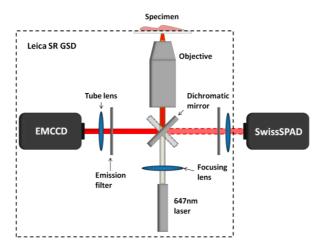

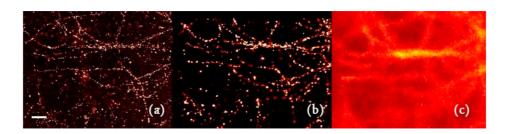

#### Super resolution microscopy

Super resolution microscopy is a collection of resolution enhancement methods for optical microscopy that allow optical instruments to break the diffraction limit. The technique was awarded the Nobel Prize in Chemistry 2014. SwissSPAD has been used in a GSDIM super resolution microscopy setup and has successfully captured super-resolved fluorescence images of labeled cells [66]. Some results are shown in section 5.1.4.

#### PET/SPECT, FRET, Raman spectroscopy

Other notable applications in which SPAD imagers have been shown to perform well include various imaging methods in nuclear science like PET and SPECT [67,68] where SPAD sensors are advantageous because they are insensitive to large magnetic fields present in MRI. This makes it possible to combine SPADs with MRI. There are more biological applications like FRET [69,70] and NIROT [71,72]. Last, but not least, SPAD based imagers are being extensively studied for space application where they will be used for example in Raman spectroscopy [73,74,75].

# Chapter 2 SwissSPAD: a 512x128 timegated single-photon imager

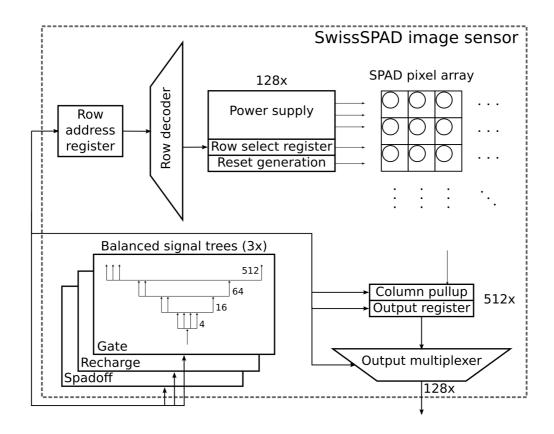

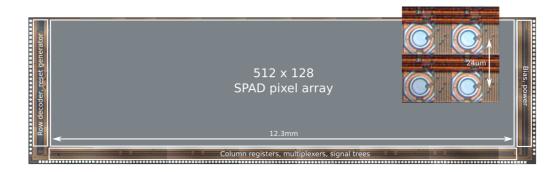

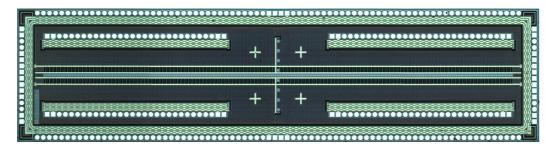

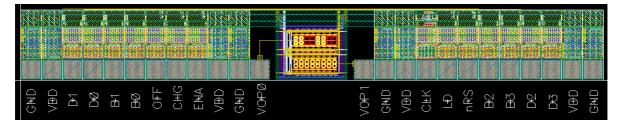

This chapter reports on the design and performance of SwissSPAD, a 512 x 128 SPAD pixel image sensor implemented in 0.35  $\mu$ m CMOS technology. The sensor, which was published in [56] has pixels with integrated 1-bit counters and reaches a frame-rate of over 156 kHz. It has been used for high-speed imaging, fluorescence lifetime imaging and random number generation among other applications and is still being introduced to new applications.

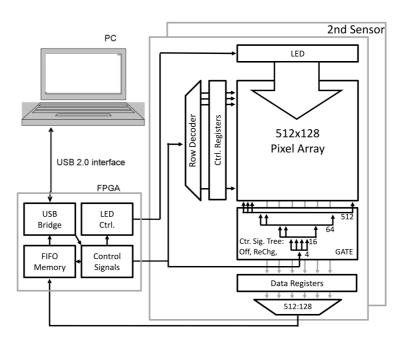

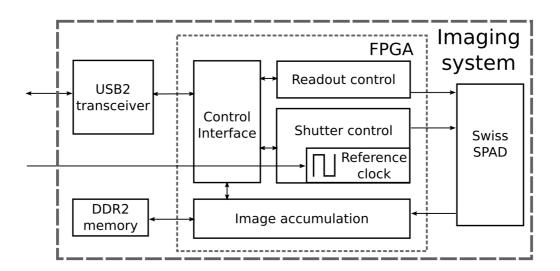

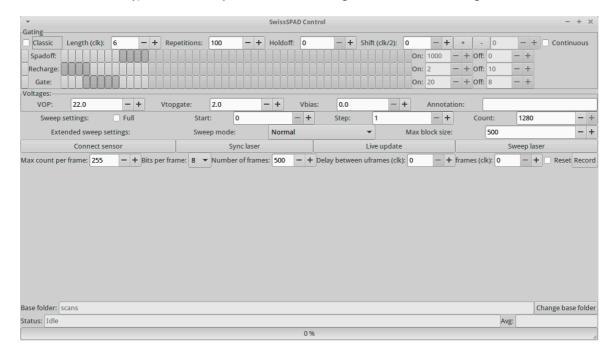

Figure 2.1 illustrates the camera system, including the computer used to control the operation of the camera, the FPGA that provides the connection between computer and sensor, and finally the sensor itself. A LED is shown as it was used to evaluate the sensor for photo-response and random number generation. A second sensor is alluded to in the picture since SwissSPAD was made to be abuttable to double its resolution even though this was not further investigated due to fabrication yield issues.

Figure 2.1: SwissSPAD camera architecture overview. The SwissSPAD sensor is connected to a FPGA implementing the control logic for sensor operation and the interface to a computer. A LED is shown as it was used for photo-response characterization and to generate random number sequences. A second sensor could be abutted to double the resolution of the camera to 512 x 256.

## 2.1 Chip architecture

The architecture of the SwissSPAD sensor is presented following a bottom-up approach from the detection of photons in the SPAD cell through the pixel circuit with the gating and memory functionality to the output registers of the chip and from there to the FPGA for further processing and transmission to a computer.

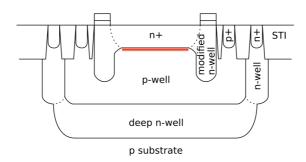

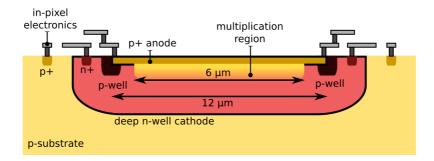

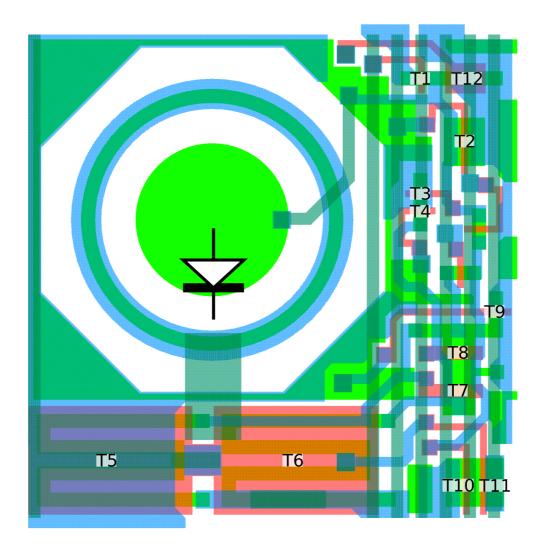

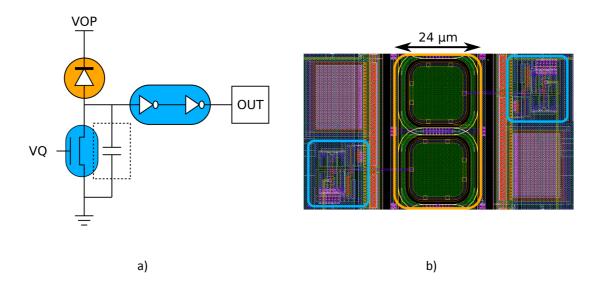

#### 2.1.1 CMOS SPAD

The SPAD cell used for the SwissSPAD pixels is a basic design known from [76] using a p+ anode and a deep n-well cathode implanted in the p-type substrate of a  $0.35~\mu m$  high-voltage CMOS process. A p-well guard ring is used to prevent premature edge breakdown of the high electric field used for the multiplication region. Using this design, as shown in Figure 2.2, has the advantage that both anode and cathode are individually isolated for each SPAD and their voltage can be chosen independently from other working voltages.

Figure 2.2: Cross-section of the SPAD structure used in SwissSPAD. It is fabricated in a  $0.35~\mu m$  high-voltage CMOS process. The p+ - deep n-well junction defines the multiplication region and the p-well guard ring prevents premature edge breakdown. Anode and cathode voltage are isolated from other voltages in their own wells.

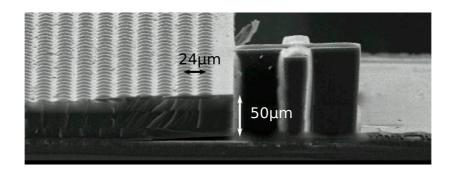

The SPAD structure is of circular shape with a total diameter of 12  $\mu$ m and the active region (where photons are absorbed and induce avalanches) has a diameter of 6  $\mu$ m. In the 24  $\mu$ m x 24  $\mu$ m pixel presented hereafter this results in a fill factor of 5%. An optimized shape of the SPAD could have increased the fill factor, but was not yet verified to work and thus not included in the large SwissSPAD sensor.

#### 2.1.2 Pixel circuit

To be able to detect photons on a large array of SPAD pixels, minimal circuitry must be used per pixel to provide at least avalanche detection and quenching and a way to address the individual SPAD pixels. A photon-induced avalanche in a SPAD results in a macroscopic signal strong enough to activate an integrated transistor and any desired digital processing can be added to the pixel circuit from there. Driven by the need to have a small pixel in order to create a high-resolution area of reasonable size, the SwissSPAD pixels have been kept relatively simple. A gating circuit and a 1-bit memory is implemented in each pixel to reduce transistor count.

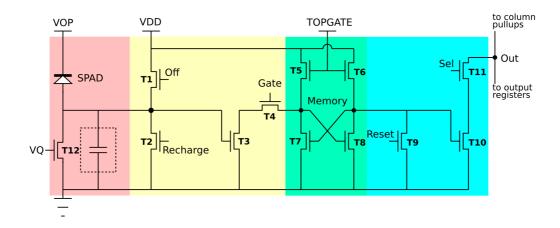

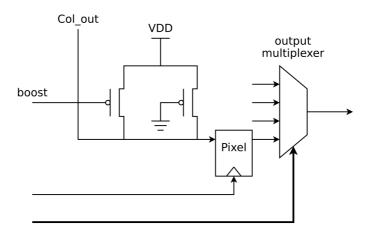

The SwissSPAD pixel is shown in Figure 2.3 and can be described in four parts: from left to right they are 1) the SPAD cell with passive quenching, 2) the gating and detection, 3) a 1-bit memory latch (counter), and 4) the address and reset circuit section.

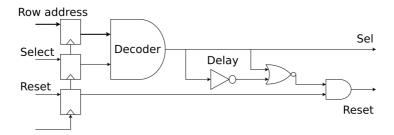

Figure 2.3: Transistor level schematic of the SwissSPAD pixel. From left to right the parts are 1) the SPAD with quenching transistor, 2) the gating circuit controlled by global signals *off, recharge* and *gate*, 3) the 1-bit memory latch (counter), and 4) the readout and reset circuit.

The first part of the circuit contains just the SPAD structure, connected to its operating voltage and a quenching transistor used as resistor to separate the anode from ground. The gate of the quenching transistor is driven with an analog voltage used to control the dead time of the SPAD separate from the gating part of the circuit.

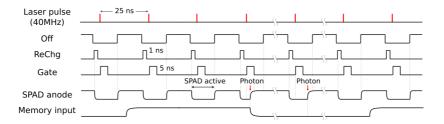

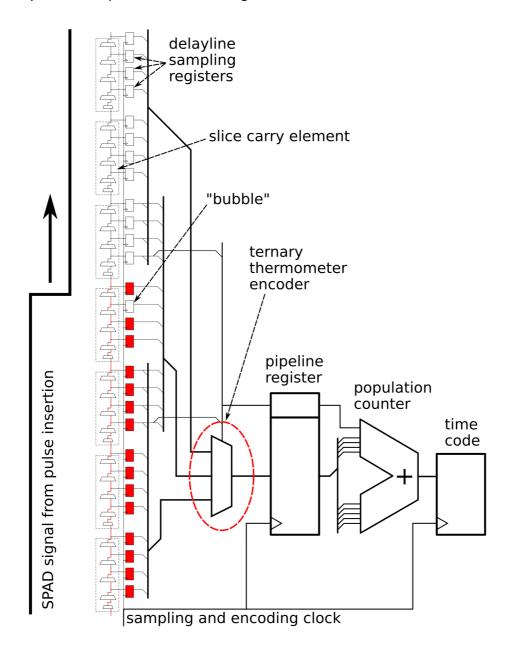

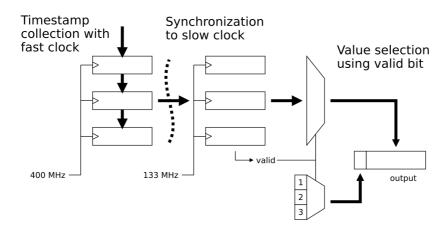

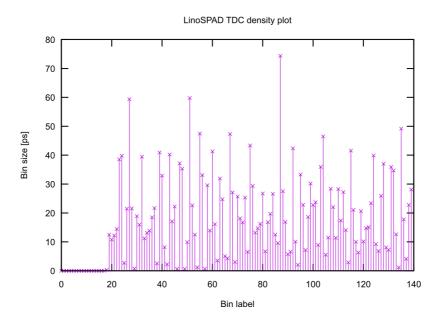

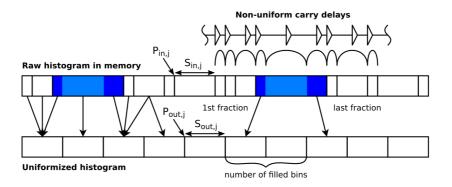

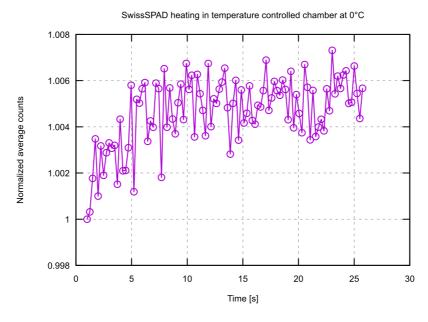

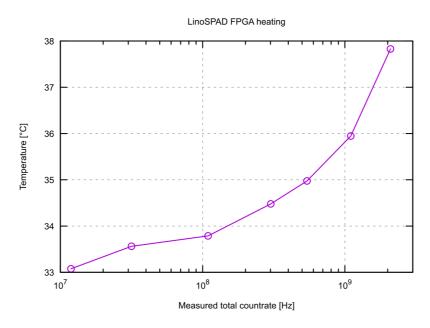

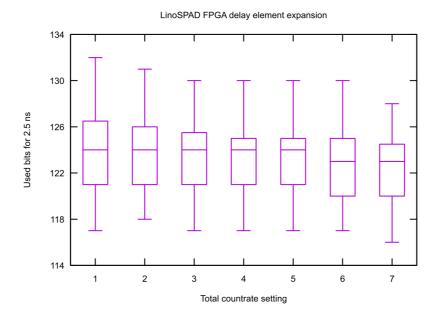

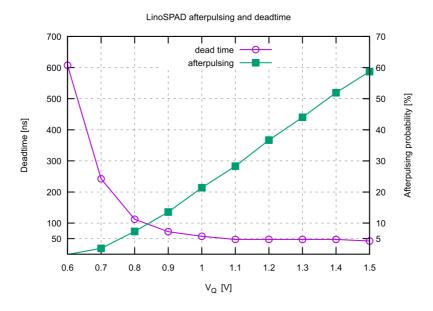

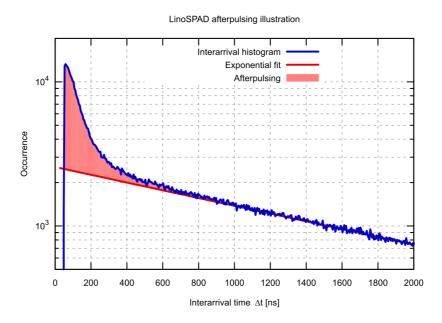

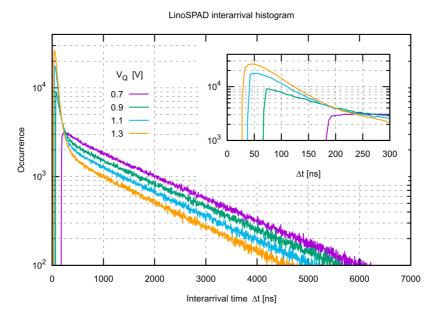

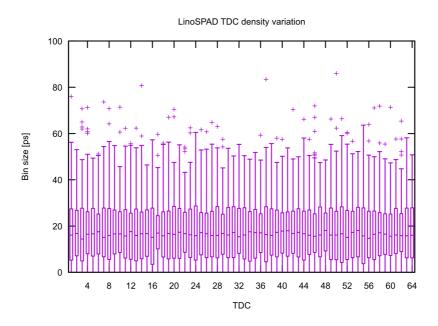

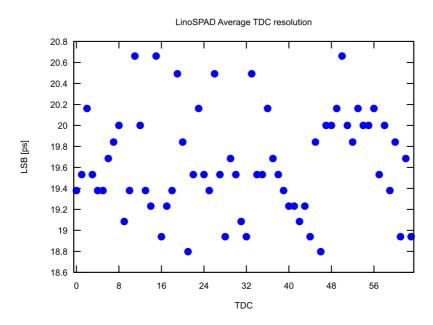

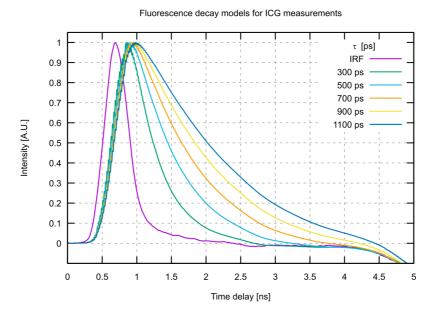

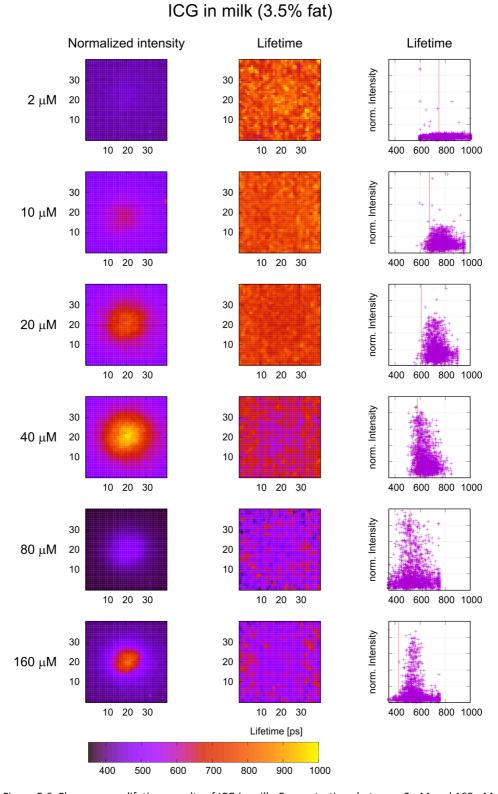

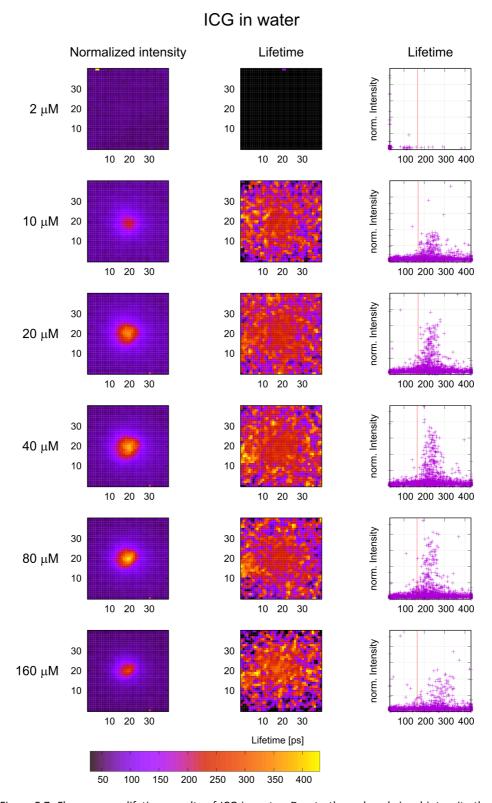

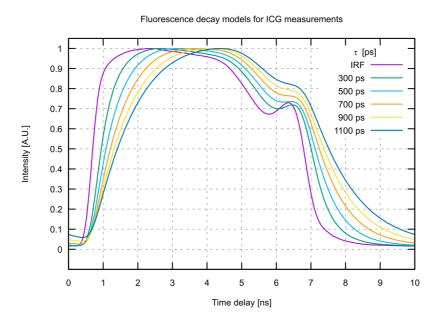

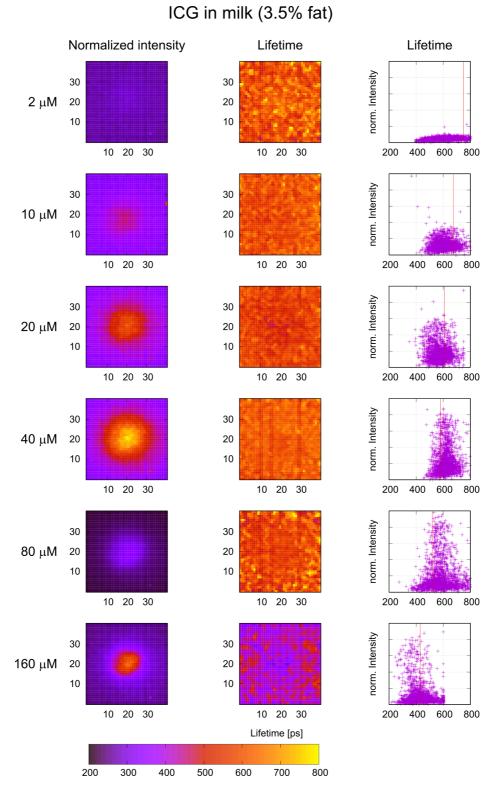

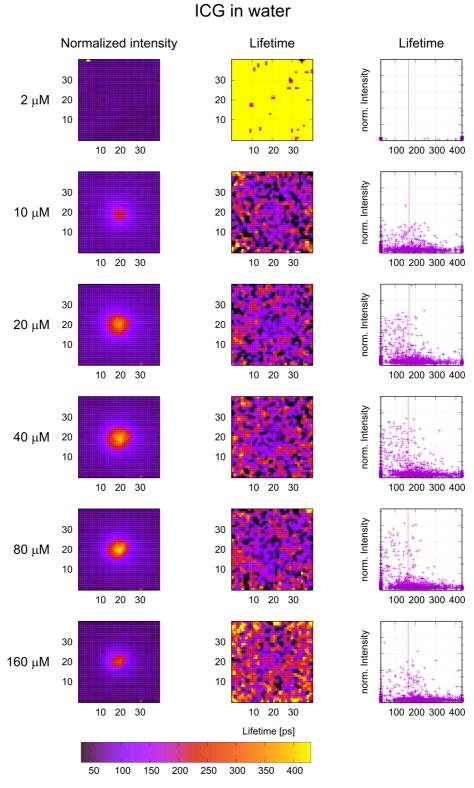

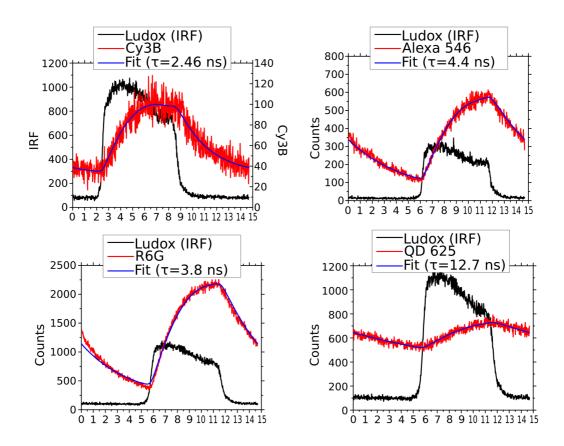

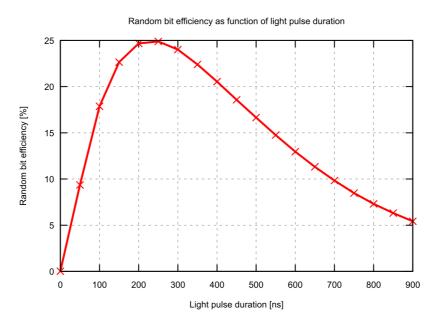

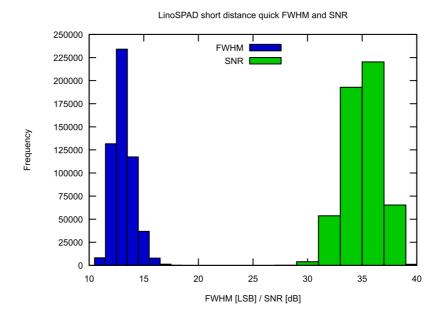

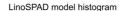

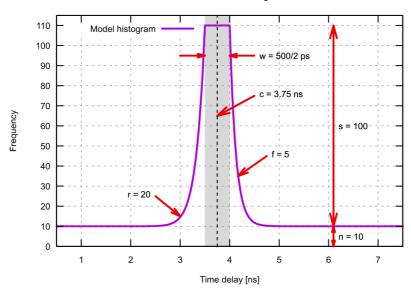

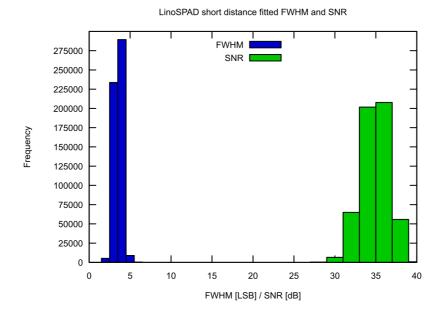

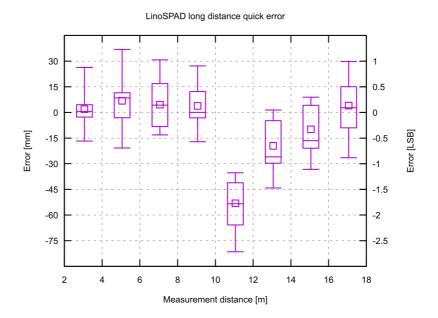

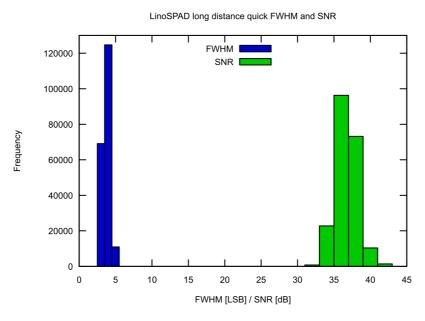

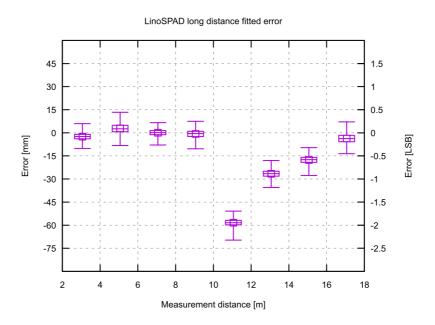

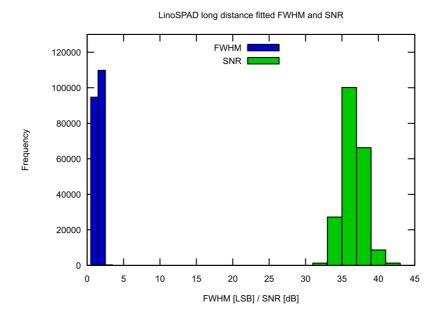

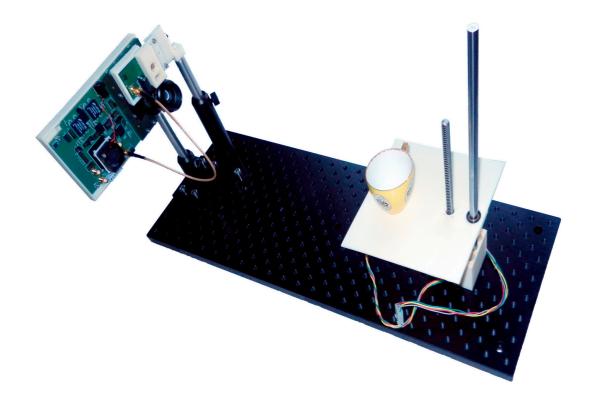

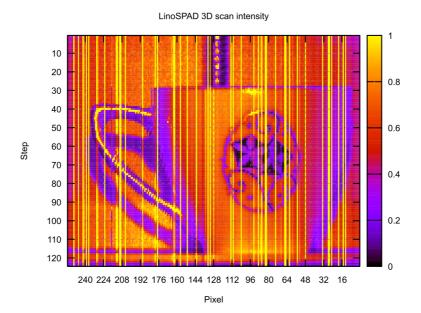

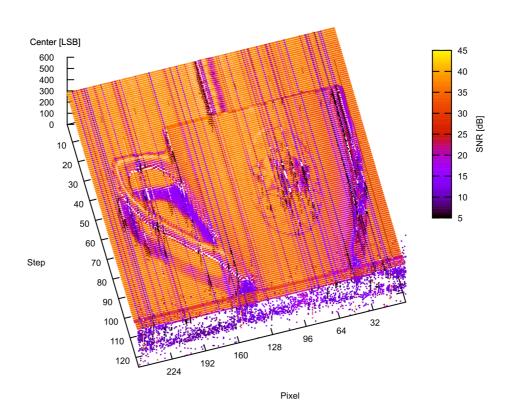

The time gating and photon detection mechanisms consist of four transistors shown in the second section. Using T1, the SPAD operated below an excess bias of  $V_{DD}$  can be switched off by lowering its bias to  $V_{OP}$ - $V_{DD}$ . Using transistor T2 the bias is restored to  $V_{OP}$  reactivating the SPAD. The wider-than-minimum-size transistor T2 provides a fast turn-on of the SPAD, but the asymmetric and larger load on the global signal has its issues as discussed later. Transistor T3 detects the voltage on the SPAD anode and T4 is used to disable photon detection and prevent the counter from incrementing when using T1 to turn off the SPAD. Note that the passive quenching through T12 and the anode recharge through T2 work in parallel and that short-circuits between  $V_{DD}$  and ground through T1 and T2 or T12 need to be prevented.