| RIGOROUS SOFTWARE DESIGN FOR NANO AND |

|---------------------------------------|

| MICRO SATELLITES USING BIP FRAMEWORK  |

| Issue: | 1         | Rev: 1   |

|--------|-----------|----------|

| Date:  | September | 14, 2014 |

| Page:  |           | 1 of 88  |

# **Rigorous** software design for nano and micro satellites using BIP framework

| Prepared by:                                                                      | Master Proje |

|-----------------------------------------------------------------------------------|--------------|

| Marco Pagnamenta                                                                  |              |

| Checked by:                                                                       |              |

| SIMON BLIUDZE                                                                     |              |

| LOUIS MASSON                                                                      |              |

| Approved by:                                                                      |              |

| ANTON IVANOV                                                                      |              |

| •<br>Space Center EPFL<br>Lausanne<br>Switzerland<br>•<br>September 14, 2014<br>• |              |

|                                                                                   |              |

ect

#### Rev: 1 September 14, 2014 2 of 88 Page:

# **Record of Revisions**

| Issue | Revision | Date       | Modifications          | Created/modified by |

|-------|----------|------------|------------------------|---------------------|

| 1     | 0        | 14.08.2014 | First complete version | Marco Pagnamenta    |

| Issue | Revision | Date       | Modifications          | Created/modified by |

| 1     | 1        | 28.08.2014 | Corrections            | Marco Pagnamenta    |

| RIGOROUS SOFTWARE DESIGN FOR NANO AND | Issue: | 1 Rev: 1           |

|---------------------------------------|--------|--------------------|

| MICRO SATELLITES USING BIP FRAMEWORK  | Date:  | September 14, 2014 |

|                                       | Page:  | 3 of 88            |

# Contents

| Lis | t of T                                                     | ables                                                                                                                                                                                                                       | 8                                                                                                                      |

|-----|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Lis | t of F                                                     | igures                                                                                                                                                                                                                      | 9                                                                                                                      |

| 1   | Intro                                                      | oduction                                                                                                                                                                                                                    | 11                                                                                                                     |

| 2   | 2.1<br>2.2                                                 | ETH CDMS         Hardware                                                                                                                                                                                                   | <ol> <li>12</li> <li>12</li> <li>12</li> <li>15</li> <li>15</li> </ol>                                                 |

|     | 3.2                                                        | 3.1.1       State                                                                                                                                                                                                           | 15<br>15<br>16<br>16<br>16<br>16<br>17<br>17<br>17                                                                     |

| 4   | <b>Guid</b><br>4.1<br>4.2<br>4.3<br>4.4                    | lelines for the BIP model design         Variations in hardware components         Modularity         Different BIP engines         Dealing with hardware failure                                                           | <b>17</b><br>18<br>18<br>18<br>18                                                                                      |

| 5   | 5.1<br>5.2<br>5.3                                          | gn of BIP modules for CubETH CDMSConventionsRoles at compound level5.2.1Activity5.2.2Resource5.2.3Triggered activitiesSoftware application5.3.1Software application5.3.2Switch5.3.3Status5.3.4ModeSandard Mixed mode/status | <ul> <li>20</li> <li>20</li> <li>21</li> <li>21</li> <li>22</li> <li>23</li> <li>24</li> <li>24</li> <li>25</li> </ul> |

| 6   | <ul><li>5.4</li><li>Rule</li><li>6.1</li><li>6.2</li></ul> | Connectors and interfaces                                                                                                                                                                                                   | 25<br><b>27</b><br>27<br>27                                                                                            |

|   |       | US SOFTWARE DESIGN FOR NANO AND<br>ATELLITES USING BIP FRAMEWORK | Issue:<br>Date:<br>Page: | 1<br>September | Rev: 1<br>14, 2014<br>4 of 88 |

|---|-------|------------------------------------------------------------------|--------------------------|----------------|-------------------------------|

|   | 6.3   | User access to shared RAM region                                 |                          |                | 28                            |

|   | 6.4   | Simultaneous use of several resources                            |                          |                | 29                            |

| ( | 6.5   | Synchronization with triggered activities                        |                          |                | 30                            |

|   | 6.6   | Rules imposed on the BIP model                                   |                          |                |                               |

|   | BIP 1 | modules description and verification                             |                          |                | 32                            |

|   | 7.1   | CDMS_status                                                      |                          |                | 32                            |

|   |       | 7.1.1 Description                                                |                          |                |                               |

|   |       | 7.1.2 Discussion on correctness                                  |                          |                |                               |

| , | 7.2   | ADCS module                                                      |                          |                |                               |

|   | 1.2   | 7.2.1 Description                                                |                          |                |                               |

|   |       | 7.2.1     Description       7.2.2     Discussion on correctness  |                          |                |                               |

| , | 7.3   |                                                                  |                          |                |                               |

|   | 1.5   | Payload                                                          |                          |                |                               |

|   |       | 7.3.1 Description                                                |                          |                |                               |

| , | 7 4   | 7.3.2 Discussion on correctness                                  |                          |                |                               |

|   | 7.4   | HK_subsystem                                                     |                          |                |                               |

|   |       | 7.4.1 Description                                                |                          |                |                               |

|   |       | 7.4.2 Discussion on correctness                                  |                          |                |                               |

| , | 7.5   | HK_internal                                                      |                          |                |                               |

|   |       | 7.5.1 Description                                                |                          |                | 40                            |

|   |       | 7.5.2 Discussion on correctness                                  |                          |                | 40                            |

| , | 7.6   | I2C_sensor - Sensor connected on the I2C_sens bu                 | s                        |                | 41                            |

|   |       | 7.6.1 Description                                                |                          |                | 41                            |

|   |       | 7.6.2 Discussion on correctness                                  |                          |                | 41                            |

| , | 7.7   | TC_receiver                                                      |                          |                | 42                            |

|   |       | 7.7.1 Description                                                |                          |                | 42                            |

|   |       | 7.7.2 Discussion on correctness                                  |                          |                |                               |

| , | 7.8   | CCSDS                                                            |                          |                |                               |

|   |       | 7.8.1 Description                                                |                          |                |                               |

|   |       | 7.8.2 Discussion on correctness                                  |                          |                |                               |

| , | 7.9   | I2C_sat                                                          |                          |                |                               |

|   | 1.9   | 7.9.1 Description                                                |                          |                |                               |

|   |       | 7.9.2 Discussion on correctness                                  |                          |                |                               |

| , | 7 10  |                                                                  |                          |                |                               |

|   | /.10  | —                                                                |                          |                |                               |

|   |       | 7.10.1 Description                                               |                          |                |                               |

|   | 7 1 1 | 7.10.2 Discussion on correctness                                 |                          |                |                               |

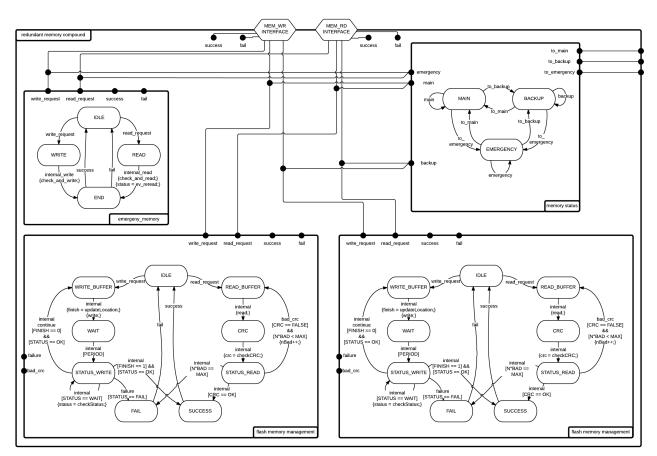

|   | /.11  | Flash memory management                                          |                          |                |                               |

|   |       | 7.11.1 Description                                               |                          |                |                               |

|   |       | 7.11.2 Discussion on correctness                                 |                          |                |                               |

| , | 7.12  | error_log                                                        |                          |                |                               |

|   |       | 7.12.1 Description                                               |                          | •••••          | 49                            |

|   |       | 7.12.2 Discussion on correctness                                 |                          |                | 50                            |

| RIGOROUS SOFTWARE DESIGN FOR NANO AND | Issue: | 1 Rev: 1           |

|---------------------------------------|--------|--------------------|

| MICRO SATELLITES USING BIP FRAMEWORK  | Date:  | September 14, 2014 |

|                                       | Page:  | 5 of 88            |

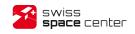

| 11 | -           | osed design flow for a BIP model integrated with the complete system de-<br>oment | 64        |

|----|-------------|-----------------------------------------------------------------------------------|-----------|

|    |             | BIP engine adaptations                                                            | 64        |

|    |             | BIP parser       Cross compilation                                                | 63<br>63  |

| 10 | -           | ementing the BIP model on the satellite hardware                                  | <b>63</b> |

|    | 9.3         | Deminuon of C/C++ functions to implement                                          | 02        |

|    | 9.2<br>9.3  | CDMS global variables                                                             | 62<br>62  |

|    | 9.1         |                                                                                   | 61        |

| 9  |             | to integrate C/C++ functions in BIP                                               | 61        |

| 8  | Exar        | nples of rule violations                                                          | 59        |

|    |             | 7.22.2 Discussion on correctness                                                  | 58        |

|    |             | 7.22.1 Description                                                                | 58        |

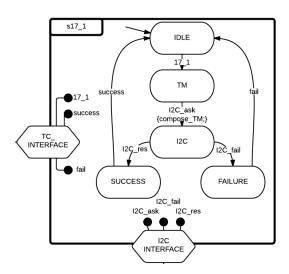

|    | 7.22        | Test service - s17_1                                                              | 58        |

|    |             | 7.21.2 Discussion on correctness                                                  | 58        |

|    |             | 7.21.1 Description                                                                | 57        |

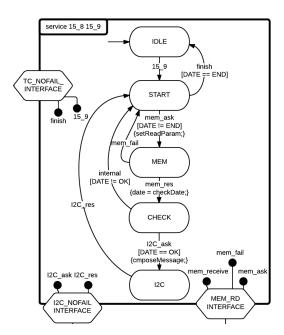

|    | 7.21        | Downlink packet store contents over time period - s15_9                           | 57        |

|    |             | 7.20.2 Discussion on correctness                                                  | 56        |

|    | 1.20        | 7.20.1 Description                                                                | 50<br>56  |

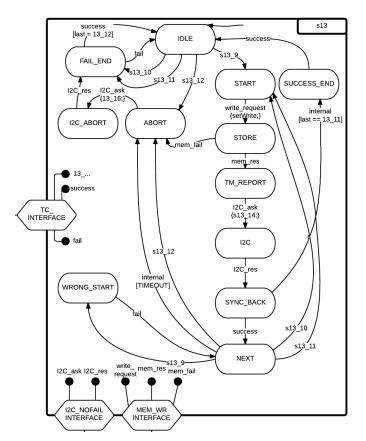

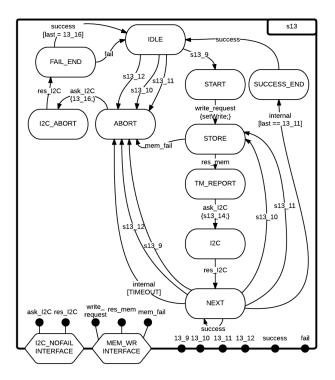

|    | 7 20        | 7.19.2 Discussion on correctness       Large data transfer service - s13          | 55<br>56  |

|    |             | 7.19.1 Description                                                                | 54<br>55  |

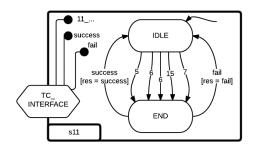

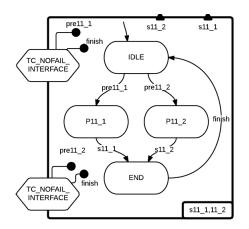

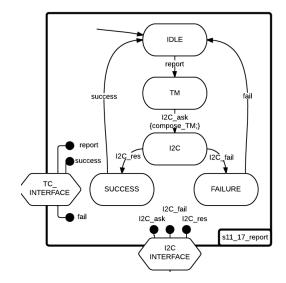

|    | 7.19        | Report command schedule in summary form - s11_17                                  | 54        |

|    | <b>-</b> 10 | 7.18.2 Discussion on correctness                                                  | 54        |

|    |             | 7.18.1 Description                                                                | 54        |

|    | 7.18        | Enable/disable the release of telecommands - s11_switch                           | 54        |

|    |             | 7.17.2 Discussion on correctness                                                  | 53        |

|    |             | 7.17.1 Description                                                                | 53        |

|    | 7.17        | On-board operations scheduling service - s11                                      | 53        |

|    |             | 7.16.2 Discussion on correctness                                                  | 52<br>52  |

|    | /.10        | Function management service - s8                                                  | 52<br>52  |

|    | 7 14        | 7.15.2 Discussion on correctness                                                  | 52<br>52  |

|    |             | 7.15.1 Description                                                                | 52        |

|    | 7.15        | Reset parameter statistics - s4_3                                                 | 52        |

|    |             | 7.14.2 Discussion on correctness                                                  | 51        |

|    |             | 7.14.1 Description                                                                | 51        |

|    | 7.14        | Report parameter statistics - s4_1                                                | 51        |

|    |             | 7.13.2 Discussion on correctness                                                  | 51        |

| 12.1 BIP design considerations       65         12.2 BIP development suggestions       66         13 Future work       67         14 Conclusion       68         A Toolchain for EFM32GG880 code cross compilation       70         A.1 Know issue       70         B List of components       71         C Cfunctions to be developed for CubETH CDMS       73         C.1 CDMS_status       73         C.2 ADCS_module       74         C.3 rayload       74         C.3.2 s128_4       74         C.3.3 s128_5       74         C.3.4 staus_transfer       74         C.3.5 data_verification       74         C.4.1 Process       75         C.4.2 Status       75         C.5 HK_internal       75         C.6.1 Process       75         C.6.2 Status       76         C.7 TC_receiver       76         C.8.2 opid_ditr       76         C.8.3 service_distr       76         C.8.4 other_apid       77         C.10 I2C_sens       77         C.11 Sa_4_3.       78         C.12 Sens       76         C.7 TC_receiver       76         C.8.2 apid_distr                                                               |    |             | US SOFTWARE DESIGN FOR NANO AND<br>ATELLITES USING BIP FRAMEWORK | Issue:<br>Date:<br>Page: | 1<br>September | Rev: 1<br>14, 2014<br>6 of 88 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------|------------------------------------------------------------------|--------------------------|----------------|-------------------------------|

| 14 Conclusion       68         A Toolchain for EFM32GG880 code cross compilation       70         A.1 Know issue       70         B List of components       71         C C functions to be developed for CubETH CDMS       73         C.1 CDMS_status       73         C.2 ADCS_module       74         C.3 Payload       74         C.3.1 s128_1       74         C.3.2 s128_5       74         C.3.3 s128_5       74         C.3.4 staus_transfer       74         C.3.5 data_verification       74         C.4.1 Process       75         C.4.1 Process       75         C.6.1 Process       75         C.6.1 Process       75         C.6.2 Status       76         C.7 TC_receiver       76         C.8.1 CCSDS_state_machine       76         C.8.2 apid_distr       76         C.8.4 other_apid       77         C.11 Flash memory management       77         C.11 Flash memory management       77         C.12 sens       77         C.13 stal_1                                                                                                                                                                   | 12 | 12.1        | BIP design considerations                                        |                          |                |                               |

| A Toolchain for EFM32GG880 code cross compilation       70         A.1 Know issue       70         B List of components       71         C C functions to be developed for CubETH CDMS       73         C.1 CDMS_status       73         C.2 ADCS_module       74         C.3.1 s128_1       74         C.3.2 s128_4       74         C.3.3 s128_5       74         C.3.4 staus_transfer       74         C.3.5 data_verification       74         C.4.1 Process       75         C.4.2 Status       75         C.4.1 Process       75         C.4.2 Status       75         C.6.1 Process       75         C.6.1 Process       75         C.6.2 Status       76         C.7 TC_receiver       76         C.8.1 CCSDS_state_machine       76         C.8.2 apid_distr       77         C.9 12C_sat       77         C.10 12C_sens       77         C.11 Flash memory management       77         C.12 saf_s3_6,s15_1,s15_2       78         C.13 s4_1       78         C.14 s4_3       78         C.16 s11       78         C.18 s13       78 </th <th>13</th> <th>Futu</th> <th>re work</th> <th></th> <th></th> <th>67</th> | 13 | Futu        | re work                                                          |                          |                | 67                            |

| A.1 Know issue       70         B List of components       71         C C functions to be developed for CubETH CDMS       73         C.1 CDMS_status       73         C.2 ADCS_module       74         C.3 Payload       74         C.3.1 s128_1       74         C.3.2 s128_4       74         C.3.3 s128_5       74         C.3.4 staus_transfer       74         C.3.5 data_verification       74         C.4.1 Process       75         C.4.1 Process       75         C.4.2 Status       75         C.6.1 Process       75         C.6.2 Status       76         C.7 TC_receiver       76         C.8.1 CCSDS_state_machine       76         C.8.3 service_distr       76         C.8.4 other_apid       77         C.9 12C_sat       77         C.9 12C_sat       77         C.11 Flash memory management       77         C.12 sa_5.s3_6.s15_1.s15_2       78         C.13 s4_1       78         C.14 s4_3       78         C.15 s8       78         C.15 s8       78         C.12 s1_17.       78         C.15 s813.                                                                                                  | 14 | Conc        | clusion                                                          |                          |                | 68                            |

| B         List of components         71           C         C functions to be developed for CubETH CDMS         73           C.1         CDMS_status         73           C.2         ADCS_module         74           C.3         Payload         74           C.3         payload         74           C.3         size_1         74           C.3.1         size_1         74           C.3.2         size_4         74           C.3.3         size_5         74           C.3.4         staus_transfer         74           C.3.5         data_verification         74           C.3.5         data_verification         74           C.4.1         Process         75           C.4.2         Status         75           C.6.1         Process         75           C.6.1         Process         75           C.6.2         Status         76           C.7         TC_receiver         76           C.8         CCSDS         76           C.8.1         CCSDS_state_machine         76           C.8.2         apid_distr         77           C.9         I2C_sat                                                  | A  | Tool        | chain for EFM32GG880 code cross compilation                      |                          |                | 70                            |

| C C functions to be developed for CubETH CDMS       73         C.1 CDMS_status       73         C.2 ADCS_module       74         C.3 Payload       74         C.3.1 s128_1       74         C.3.2 s128_4       74         C.3.3 s128_5       74         C.3.4 staus_transfer       74         C.3.5 data_verification       74         C.4.1 Process       75         C.4.2 Status       75         C.4.1 Process       75         C.6.1 Process       75         C.6.2 Status       76         C.7 TC_receiver       76         C.8.1 CCSDS_state_machine       76         C.8.2 apid_distr       76         C.8.3 service_distr       76         C.8.4 other_apid       77         C.10 I2C_sens       77         C.11 Flash memory management       77         C.12 sat                                                                                                                                                                                                                                                                                                                                                    |    | A.1         | Know issue                                                       |                          |                |                               |

| C.1       CDMS_status       73         C.2       ADCS_module       74         C.3       Payload       74         C.3.1 $s128_1$ 74         C.3.2 $s128_1$ 74         C.3.3 $s128_5$ 74         C.3.3 $s128_5$ 74         C.3.4       staus_transfer       74         C.3.5       data_verification       74         C.3.5       data_verification       74         C.3.6       data_verification       74         C.4       HK_subsystem       75         C.4.1       Process       75         C.4.2       Status       75         C.6.1       Process       75         C.6.2       Status       76         C.7       TC_receiver       76         C.8       CCSDS       76         C.8.1       CCSDS_state_machine       76         C.8.3       service_distr       76         C.8.4       other_apid       77         C.10       I2C_sens       77         C.10       I2C_sens       77         C.11       Flash memory management       77                                                                                                                                                                                 | B  | List        | of components                                                    |                          |                | 71                            |

| C.1       CDMS_status       73         C.2       ADCS_module       74         C.3       Payload       74         C.3.1 $s128_{-1}$ 74         C.3.2 $s128_{-1}$ 74         C.3.3 $s128_{-5}$ 74         C.3.4       staus_transfer       74         C.3.5       data_verification       74         C.3.5       data_verification       74         C.4       HK_subsystem       75         C.4.1       Process       75         C.4.2       Status       75         C.4.1       Process       75         C.4.2       Status       75         C.6.1       Process       75         C.6.2       Status       76         C.7       TC-receiver       76         C.8       CCSDS       76         C.8.1       CCSDS_state_machine       76         C.8.2       apid_distr       76         C.8.3       service_distr       76         C.8.4       other_apid       77         C.10       I2C_sens       77         C.11       Flash memory management       77                                                                                                                                                                     | С  | C fu        | nctions to be developed for CubETH CDMS                          |                          |                | 73                            |

| C.2       ADCS_module       74         C.3       Payload       74         C.3.1       sl28_1       74         C.3.2       sl28_4       74         C.3.3       sl28_5       74         C.3.3       sl28_5       74         C.3.3       sl28_5       74         C.3.4       staus_transfer       74         C.3.5       data_verification       74         C.4       HK_subsystem       75         C.4.1       Process       75         C.4.2       Status       75         C.4.1       Process       75         C.5       HK_internal       75         C.6.1       Process       75         C.6.2       Status       76         C.7       TC_receiver       76         C.8       CCSDS       76         C.8.1       CCSDS_state_machine       76         C.8.3       service_distr       76         C.8.4       other_apid       77         C.10       I2C_sens       77         C.10       I2C_sens       77         C.11       Flash memory management       77         C.12       s3                                                                                                                                        | -  |             | •                                                                |                          |                | -                             |

| C.3 Payload       74         C.3.1 s128_1       74         C.3.2 s128_4       74         C.3.3 s128_5       74         C.3.4 staus_transfer       74         C.3.5 data_verification       74         C.4       HK_subsystem       75         C.4.1 Process       75         C.4.2 Status       75         C.5 HK_internal       75         C.6 12C_sensor       75         C.6.1 Process       75         C.6.2 Status       76         C.8 CCSDS       75         C.8.1 CCSDS_state_machine       76         C.8.2 apid_distr       76         C.8.3 service_distr       76         C.8.4 other_apid       77         C.10 12C_sens       77         C.11 Flash memory management       77         C.13 s4_1       78         C.14 s4_3       78         C.15 s8       78         C.16 s11       78         C.17 s11_17       78         C.18 s13       78                                                                                                                                                                                                                                                                  |    | C.2         |                                                                  |                          |                |                               |

| C.3.1       s128_1       74         C.3.2       s128_4       74         C.3.3       s128_5       74         C.3.4       staus_transfer       74         C.3.5       dat_verification       74         C.3.6       dat_verification       74         C.3.7       dat_verification       74         C.4       HK_subsystem       75         C.4.1       Process       75         C.4.2       Status       75         C.4.2       Status       75         C.6       I2C_sensor       75         C.6.1       Process       75         C.6.2       Status       76         C.7       TC_receiver       76         C.8       CCSDS       76         C.8.1       CCSDS_state_machine       76         C.8.2       apid_distr       76         C.8.3       service_distr       76         C.8.4       other_apid       77         C.10       I2C_sens       77         C.11       Flash memory management       77         C.12       s3_5,s3_6,s15_1,s15_2       78         C.13       s4_1       78                                                                                                                                 |    | C.3         | —                                                                |                          |                |                               |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |             | -                                                                |                          |                |                               |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |             |                                                                  |                          |                |                               |

| C.3.4 staus_transfer       74         C.3.5 data_verification       74         C.4 HK_subsystem       75         C.4.1 Process       75         C.4.2 Status       75         C.5 HK_internal       75         C.6.1 Process       75         C.6.2 Sensor       75         C.6.1 Process       75         C.6.2 Status       76         C.7 TC_receiver       76         C.8.1 CCSDS_state_machine       76         C.8.2 apid_distr       76         C.8.3 service_distr       76         C.8.4 other_apid       77         C.9 I2C_sat       77         C.10 I2C_sens       77         C.11 Flash memory management       77         C.12 s3_5,s3_6,s15_1,s15_2       78         C.13 s4_1       78         C.14 s4_3       78         C.15 s8       78         C.16 s11       78         C.16 s11       78         C.16 s13       78         C.18 s13       78                                                                                                                                                                                                                                                            |    |             | —                                                                |                          |                |                               |

| C.3.5       data_verification       74         C.4       HK_subsystem       75         C.4.1       Process       75         C.4.2       Status       75         C.5       HK_internal       75         C.6       I2C_sensor       75         C.6.1       Process       75         C.6.2       Status       75         C.6.1       Process       75         C.6.2       Status       76         C.7       TC_receiver       76         C.8       CCSDS       76         C.8.1       CCSDS_state_machine       76         C.8.2       apid_distr       76         C.8.3       service_distr       76         C.8.4       other_apid       77         C.10       I2C_sens       77         C.11       Flash memory management       77         C.12       s3_5,s3_6,s15_1,s15_2       78         C.13       s4_1       78         C.14       s4_3       78         C.15       s8       78         C.16       s1       78         C.16       s1       78         C.16       s13                                                                                                                                                   |    |             |                                                                  |                          |                |                               |

| C.4       HK_subsystem       75         C.4.1       Process       75         C.4.2       Status       75         C.5       HK_internal       75         C.6       I2C_sensor       75         C.6.1       Process       75         C.6.2       Status       75         C.6.2       Status       76         C.7       TC_receiver       76         C.8       CCSDS       76         C.8.1       CCSDS_state_machine       76         C.8.2       apid_distr       76         C.8.3       service_distr       76         C.8.4       other_apid       77         C.10       I2C_sens       77         C.11       Flash memory management       77         C.12       s3_5,s3_6,s15_1,s15_2       78         C.13       s4_1       78         C.14       s4_3       78         C.15       s8       78         C.16       s1       78         C.16       s1       78         C.16       s13       78         C.17       s1_117       78         C.18       s13       78                                                                                                                                                           |    |             | —                                                                |                          |                |                               |

| C.4.1       Process       75         C.4.2       Status       75         C.5       HK_internal       75         C.6       I2C_sensor       75         C.6.1       Process       75         C.6.2       Status       76         C.7       TC_receiver       76         C.8       CCSDS       76         C.8.1       CCSDS_state_machine       76         C.8.2       apid_distr       76         C.8.3       service_distr       76         C.8.4       other_apid       77         C.9       I2C_sat       77         C.10       I2C_sens       77         C.11       Flash memory management       77         C.12       s3_5,s3_6,s15_1,s15_2       78         C.13       s4_1       78         C.14       s4_3       78         C.15       s8       78         C.16       s11       78         C.16       s11       78         C.17       s1_1_17       78         C.18       s13       78                                                                                                                                                                                                                                 |    | <b>C</b> 4  | —                                                                |                          |                |                               |

| C.4.2       Status       75         C.5       HK_internal       75         C.6       I2C_sensor       75         C.6.1       Process       75         C.6.2       Status       76         C.7       TC_receiver       76         C.8       CCSDS       76         C.8.1       CCSDS_state_machine       76         C.8.2       apid_distr       76         C.8.3       service_distr       76         C.8.4       other_apid       77         C.9       I2C_sat       77         C.10       I2C_sens       77         C.11       Flash memory management       77         C.12       s3_5,s3_6,s15_1,s15_2       78         C.13       s4_1       78         C.14       s4_3       78         C.15       s8       78         C.16       s11       78         C.17       s1_1_17       78         C.18       s13       78                                                                                                                                                                                                                                                                                                      |    | 0.1         | •                                                                |                          |                |                               |

| C.5       HK_internal       75         C.6       I2C_sensor       75         C.6.1       Process       75         C.6.2       Status       76         C.7       TC_receiver       76         C.8       CCSDS       76         C.8.1       CCSDS_state_machine       76         C.8.2       apid_distr       76         C.8.3       service_distr       76         C.8.4       other_apid       77         C.9       I2C_sat       77         C.10       I2C_sens       77         C.11       Flash memory management       77         C.12       s3_5,s3_6,s15_1,s15_2       78         C.13       s4_1       78         C.14       s4_3       78         C.15       s8       78         C.16       s11       78         C.16       s11       78         C.17       s11_17       78         C.18       s13       78                                                                                                                                                                                                                                                                                                           |    |             |                                                                  |                          |                |                               |

| C.6       I2C_sensor       75         C.6.1       Process       75         C.6.2       Status       76         C.7       TC_receiver       76         C.8       CCSDS       76         C.8.1       CCSDS_state_machine       76         C.8.2       apid_distr       76         C.8.3       service_distr       76         C.8.4       other_apid       77         C.9       I2C_sens       77         C.10       I2C_sens       77         C.11       Flash memory management       77         C.12       s3_5,s3_6,s15_1,s15_2       78         C.13       s4_1       78         C.14       s4_3       78         C.15       s8       78         C.16       s11       78         C.16       s11       78         C.17       s11_17       78         C.18       s13       78                                                                                                                                                                                                                                                                                                                                                 |    | C 5         |                                                                  |                          |                |                               |

| C.6.1       Process       75         C.6.2       Status       76         C.7       TC_receiver       76         C.8       CCSDS       76         C.8.1       CCSDS_state_machine       76         C.8.2       apid_distr       76         C.8.3       service_distr       76         C.8.4       other_apid       76         C.9       I2C_sat       77         C.10       I2C_sens       77         C.11       Flash memory management       77         C.12       s3_5,s3_6,s15_1,s15_2       78         C.13       s4_1       78         C.14       s4_3       78         C.15       s8       78         C.16       s11       78         C.17       s11_17       78         C.18       s13       78                                                                                                                                                                                                                                                                                                                                                                                                                        |    |             | —                                                                |                          |                |                               |

| C.6.2       Status       76         C.7       TC_receiver       76         C.8       CCSDS       76         C.8.1       CCSDS_state_machine       76         C.8.2       apid_distr       76         C.8.3       service_distr       76         C.8.4       other_apid       76         C.9       I2C_sat       77         C.10       I2C_sens       77         C.11       Flash memory management       77         C.12       s3_5,s3_6,s15_1,s15_2       78         C.13       s4_1       78         C.14       s4_3       78         C.15       s8       78         C.16       s11       78         C.17       s11_17       78         C.18       s13       78                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 0.0         |                                                                  |                          |                |                               |

| C.7       TC_receiver       76         C.8       CCSDS       76         C.8.1       CCSDS_state_machine       76         C.8.2       apid_distr       76         C.8.3       service_distr       76         C.8.4       other_apid       76         C.9       I2C_sat       77         C.10       I2C_sens       77         C.11       Flash memory management       77         C.12       s3_5,s3_6,s15_1,s15_2       78         C.13       s4_1       78         C.14       s4_3       78         C.15       s8       78         C.16       s11       78         C.17       s11_17       78         C.18       s13       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |             |                                                                  |                          |                |                               |

| C.8       CCSDS       76         C.8.1       CCSDS_state_machine       76         C.8.2       apid_distr       76         C.8.3       service_distr       76         C.8.4       other_apid       77         C.9       I2C_sat       77         C.10       I2C_sens       77         C.11       Flash memory management       77         C.12       s3_5,s3_6,s15_1,s15_2       78         C.13       s4_1       78         C.14       s4_3       78         C.15       s8       78         C.16       s11       78         C.17       s11_17       78         C.18       s13       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | <b>C</b> .7 |                                                                  |                          |                |                               |

| C.8.1       CCSDS_state_machine       76         C.8.2       apid_distr       76         C.8.3       service_distr       76         C.8.4       other_apid       77         C.9       I2C_sat       77         C.10       I2C_sens       77         C.11       Flash memory management       77         C.12       s3_5,s3_6,s15_1,s15_2       78         C.13       s4_1       78         C.14       s4_3       78         C.15       s8       78         C.16       s11       78         C.17       s11_17       78         C.18       s13       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |             |                                                                  |                          |                |                               |

| C.8.2 apid_distr       76         C.8.3 service_distr       76         C.8.4 other_apid       77         C.9 I2C_sat       77         C.10 I2C_sens       77         C.11 Flash memory management       77         C.12 s3_5,s3_6,s15_1,s15_2       78         C.13 s4_1       78         C.14 s4_3       78         C.15 s8       78         C.16 s11       78         C.17 s11_17       78         C.18 s13       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | 0.0         |                                                                  |                          |                |                               |

| C.8.3 service_distr       76         C.8.4 other_apid       77         C.9 I2C_sat       77         C.10 I2C_sens       77         C.11 Flash memory management       77         C.12 $s_3 - 5, s_3 - 6, s_1 - 5 - 1, s_1 - 5 - 2$ 78         C.13 $s_4 - 1$ 78         C.14 $s_4 - 3$ 78         C.15 $s_8$ 78         C.16 $s_1 - 1$ 78         C.17 $s_1 - 1 - 1$ 78         C.18 $s_1 - 3$ 78         C.18 $s_1 - 3$ 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |             |                                                                  |                          |                |                               |

| C.8.4 other_apid       77         C.9 I2C_sat       77         C.10 I2C_sens       77         C.11 Flash memory management       77         C.12 s3_5,s3_6,s15_1,s15_2       78         C.13 s4_1       78         C.14 s4_3       78         C.15 s8       78         C.16 s11       78         C.17 s11_17       78         C.18 s13       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |             | 1 =                                                              |                          |                |                               |

| C.9       I2C_sat       77         C.10       I2C_sens       77         C.11       Flash memory management       77         C.12       s3_5,s3_6,s15_1,s15_2       78         C.13       s4_1       78         C.14       s4_3       78         C.15       s8       78         C.16       s11       78         C.17       s11_17       78         C.18       s13       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |             |                                                                  |                          |                |                               |

| C.10 I2C_sens       77         C.11 Flash memory management       77         C.12 s3_5,s3_6,s15_1,s15_2       78         C.13 s4_1       78         C.14 s4_3       78         C.15 s8       78         C.16 s11       78         C.17 s11_17       78         C.18 s13       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | C.9         | - I                                                              |                          |                |                               |

| C.11 Flash memory management       77         C.12 s3_5,s3_6,s15_1,s15_2       78         C.13 s4_1       78         C.14 s4_3       78         C.15 s8       78         C.16 s11       78         C.17 s11_17       78         C.18 s13       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |             | —                                                                |                          |                |                               |

| C.12 s3_5,s3_6,s15_1,s15_2       78         C.13 s4_1       78         C.14 s4_3       78         C.15 s8       78         C.16 s11       78         C.17 s11_17       78         C.18 s13       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |             |                                                                  |                          |                |                               |

| C.13 s4_1       78         C.14 s4_3       78         C.15 s8       78         C.16 s11       78         C.17 s11_17       78         C.18 s13       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |             |                                                                  |                          |                |                               |

| C.14 s4_3       78         C.15 s8       78         C.16 s11       78         C.17 s11_17       78         C.18 s13       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |             |                                                                  |                          |                |                               |

| C.15 s8       78         C.16 s11       78         C.17 s11_17       78         C.18 s13       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |             |                                                                  |                          |                |                               |

| C.16 s11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |             |                                                                  |                          |                |                               |

| C.17 s11_17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |             |                                                                  |                          |                |                               |

| C.18 s13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |             |                                                                  |                          |                |                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |             | —                                                                |                          |                |                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |             |                                                                  |                          |                |                               |

| Rı | GORC  | OUS SOFTWARE DESIGN FOR NANO AND              | Issue: | 1           | Rev: 1   |

|----|-------|-----------------------------------------------|--------|-------------|----------|

| MI | CRO S | SATELLITES USING BIP FRAMEWORK                | Date:  | September   | 14, 2014 |

|    |       |                                               | Page:  | -           | 7 of 88  |

|    |       |                                               |        |             |          |

|    | C 20  | ) 17_1                                        |        |             | 79       |

|    |       | Global variables                              |        |             |          |

|    | 0.21  | C.21.1 I2C_request and I2C_report             |        |             |          |

|    |       | C.21.2 hw_error                               |        |             |          |

|    |       | C.21.3 TC_active                              |        |             |          |

|    |       | C.21.4 write_buffer and read_buffer           |        |             |          |

|    |       | C.21.5 TC_schedule                            |        |             |          |

|    |       | C.21.6 HK_generic_report                      |        |             |          |

|    |       | C.21.7 sens1 and sens2                        |        |             |          |

|    |       |                                               |        |             |          |

| D  |       | volatile memory considerations                |        |             | 81       |

|    | D.1   | Data in MRAM                                  |        |             | 81       |

| Е  | Reco  | overing from CDMS shut down and startup seque | ence   |             | 82       |

| Ľ  | E.1   | Shut down recovery                            |        |             | -        |

|    | L. I  |                                               | ••••   | • • • • • • | 02       |

| F  | Men   | nory redundancy                               |        |             | 84       |

| G  | BIP   | code structure and use                        |        |             | 85       |

| -  | G.1   | Time adaptation                               |        |             |          |

|    | G.2   | Content                                       |        |             |          |

|    | G.3   | How to use the BIP model                      |        |             |          |

|    |       | G.3.1 Building the BIP model                  |        |             |          |

|    |       | G.3.2 Compile                                 |        |             |          |

|    |       | G.3.3 Example                                 |        |             |          |

|    |       | G.3.4 Use the model                           |        |             |          |

# **List of Tables**

| 1 | CDMS time requirements for task execution                                     | 13 |

|---|-------------------------------------------------------------------------------|----|

| 2 | Global variables used in the model, associated with the transitions where the |    |

|   | variable is read or written. The format is "atom.transition_label"            | 62 |

| 3 | Keywords used to highlight only some processes of the BIP model. The de-      |    |

|   | scription column explains what they represents. They can be used by typing:   |    |

|   | \$ ./system   grep -i -e 'keyword1' -e 'keyword2' -e                          | 87 |

| RIGOROUS SOFTWARE DESIGN FOR NANO AND | Issue: | 1 Rev: 1           |

|---------------------------------------|--------|--------------------|

| MICRO SATELLITES USING BIP FRAMEWORK  | Date:  | September 14, 2014 |

|                                       | Page:  | 9 of 88            |

# **List of Figures**

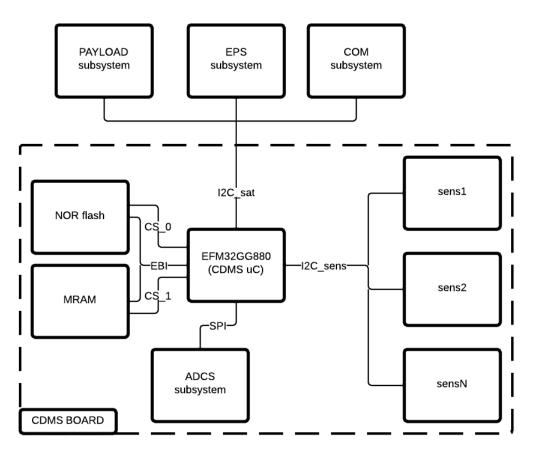

| 1  | Simplified CDMS hardware and connections. CS means "Chip select"                 | 13 |

|----|----------------------------------------------------------------------------------|----|

| 2  | Selected telecommands as from the CubETH ICD                                     | 14 |

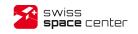

| 3  | BIP atom. The starting place is "WAITING". As soon as the "in" port is           |    |

|    | enabled, the state progress to "PROCESS" following the transition labeled        |    |

|    | by the "in" port itself. Then, the guards ( $x>0$ or $x<=0$ ) for the "internal" |    |

|    | and "compute" transitions are evaluated. The place progresses following the      |    |

|    | transition whose guard evaluates to "true". Assuming that "x" was bigger         |    |

|    | than 0, then the place is "READY" and an "out" transition may be enabled,        |    |

|    | leading the atom back to the "WAITING" place                                     | 16 |

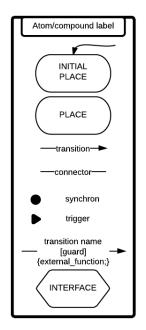

| 4  | Symbols used in the graphical BIP model                                          | 20 |

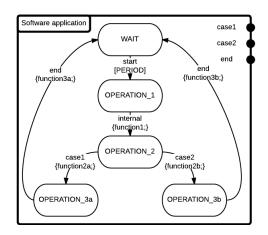

| 5  | Example of a "software application" atom                                         | 23 |

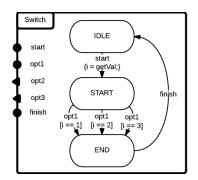

| 6  | Example of a "switch" atom                                                       | 23 |

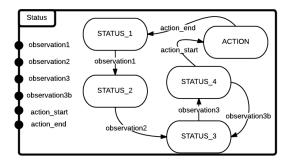

| 7  | Example of a "status" atom                                                       | 24 |

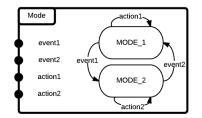

| 8  | Example of a "mode" atom                                                         | 25 |

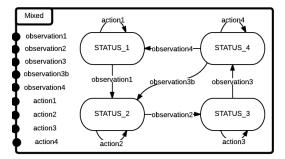

| 9  | Example of a "mixed" atom                                                        | 25 |

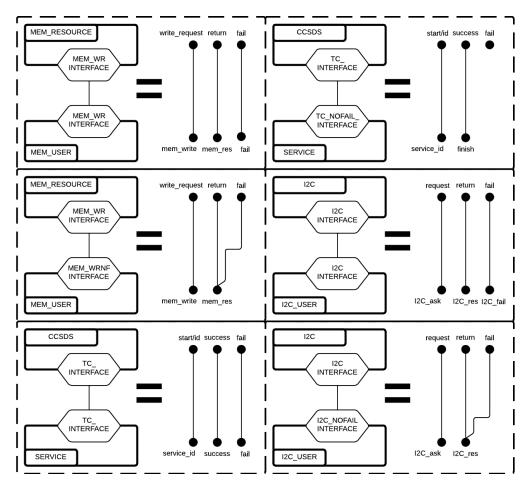

| 10 | Interfaces used in the BIP model                                                 | 26 |

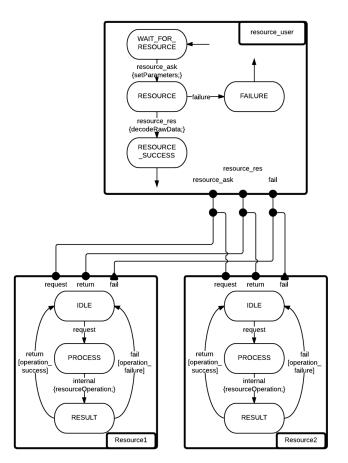

| 11 | BIP model of the relationship between a generic hardware resource and two        |    |

|    | kinds of generic users. One user has a different behavior if the hardware        |    |

|    | peripheral fails, the other one does not care about the success or failure of    |    |

|    | the operation                                                                    | 28 |

| 12 | BIP model of an atom representing a shared memory region. The memory is          |    |

|    | accessible only during the transition of the resource atom                       | 29 |

| 13 | BIP model of an atom representing a shared memory region. One must take          |    |

|    | care in using the token every time that a transition uses this memory region     | 29 |

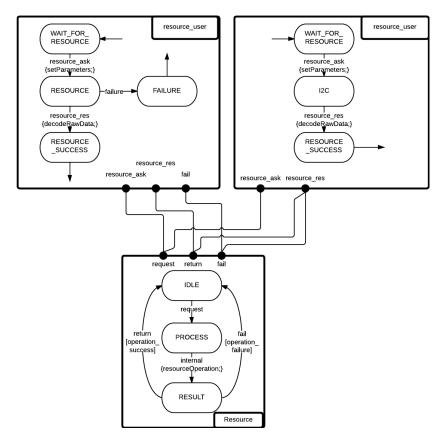

| 14 | BIP model of an user necessitating two resources at the same time                | 30 |

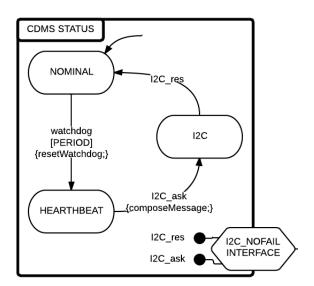

| 15 | CDMS status atom                                                                 | 32 |

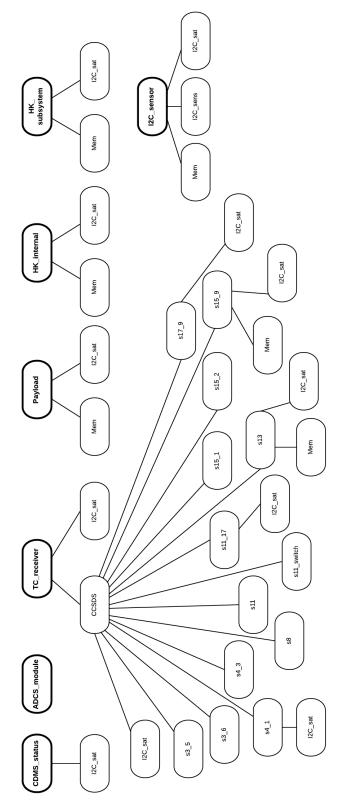

| 16 | Global triggering graph, the activities are represented in bold. HK_subsystem    |    |

|    | and I2C_sensor are represented only once since their structure is always the     |    |

|    | same                                                                             | 33 |

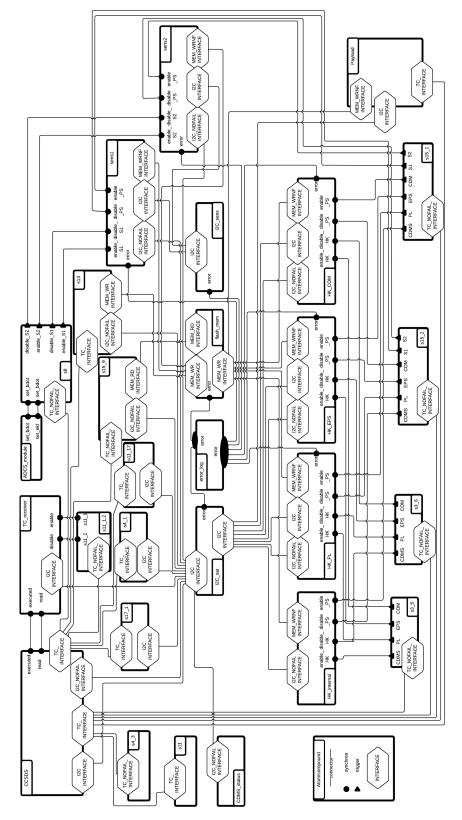

| 17 | "interaction" layer of the BIP CDMS model                                        | 34 |

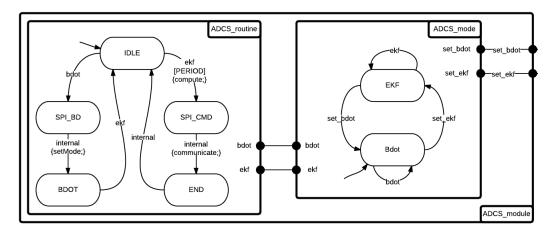

| 18 | ADCS_module, composed of a software application: ADCS_routine and a              |    |

|    | mode atom: ADCS_mode                                                             | 35 |

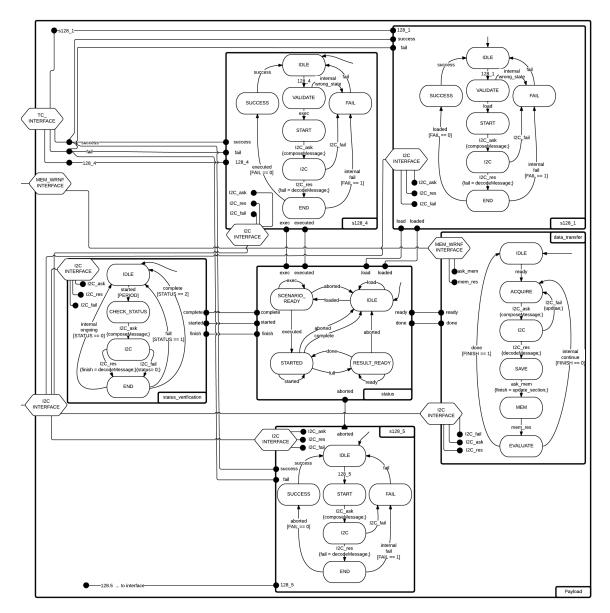

| 19 | Payload BIP model, composed of several software applications: s128_1,            |    |

|    | s128_4, s128_5, data_transfer, status_verification and a status atom: status     | 37 |

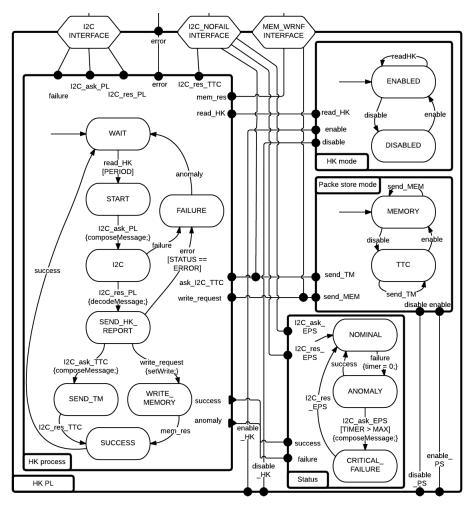

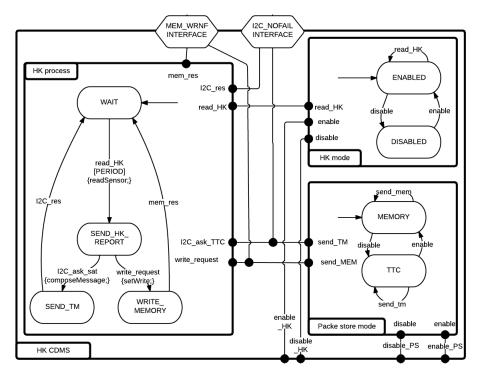

| 20 | <i>HK_subsystem, composed of a software application: HK_process, a status:</i>   |    |

|    | status and two mode atoms: Packet_store_mode and HK_mode                         | 39 |

| 21 | HK_internal, composed of a software application: HK_process and two              |    |

|    | mode atoms: Packet_store_mode and HK_mode                                        | 40 |

| 22 | I2C_sensor, composed of a software application: sens_process, a status:          |    |

|    | status and two mode atoms: Packet_store_mode and SENS_mode                       | 41 |

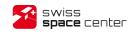

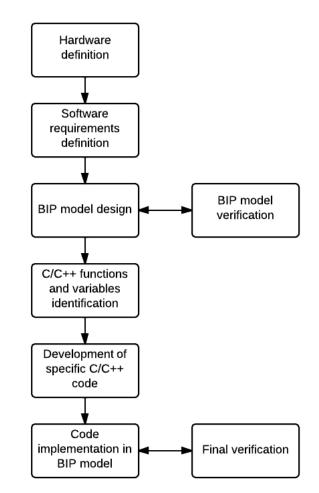

| 23 | TC_receiver, composed of a software application: TC_fetch, a status: TC_buffe    | r  |

|    | and a mode atom: TC_list_mode                                                    | 43 |

| RIGOROUS SOFTWARE DESIGN FOR NANO AND | Issue: | 1 Rev: 1           |

|---------------------------------------|--------|--------------------|

| MICRO SATELLITES USING BIP FRAMEWORK  | Date:  | September 14, 2014 |

|                                       | Page:  | 10 of 88           |

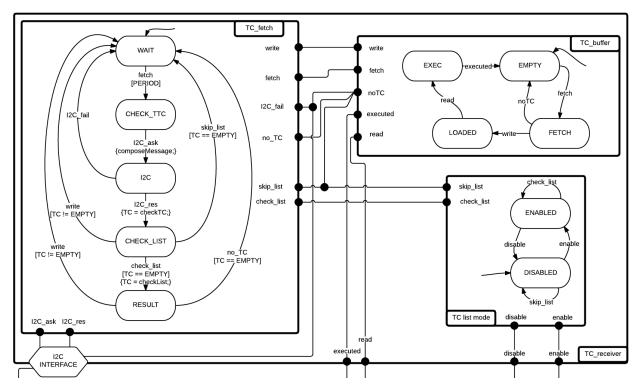

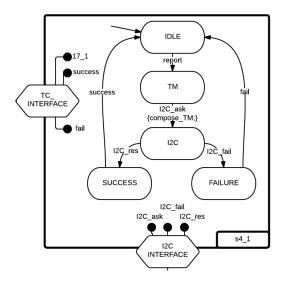

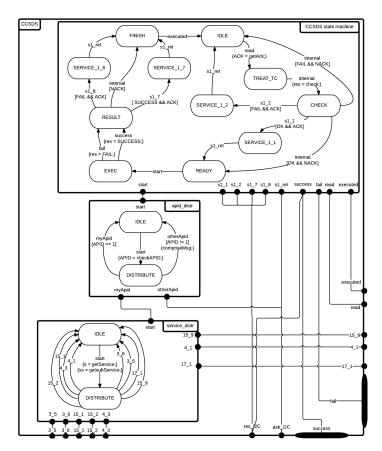

| 24 | BIP model of the CCSDS compound, composed of two software applications:                          |    |

|----|--------------------------------------------------------------------------------------------------|----|

|    | CCSDS_state_machine and other_apid and two switches: apid_distr and                              |    |

|    | service_distr                                                                                    | 45 |

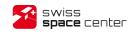

| 25 | BIP model of the atom implementing the I2C satellite high level communica-                       |    |

|    | tion protocol                                                                                    | 46 |

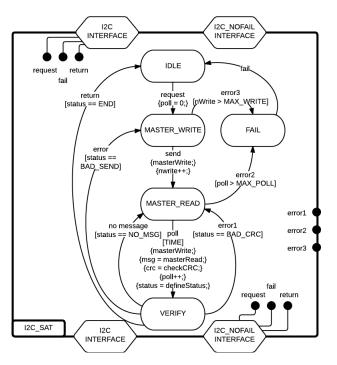

| 26 | BIP model of the atom implementing the I2C sensor high level communica-                          |    |

|    | tion protocol                                                                                    | 47 |

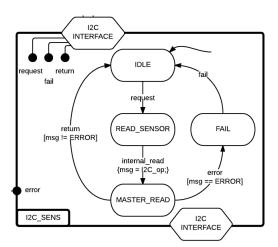

| 27 | BIP model of the atom implementing the high level read and write procedures                      |    |

|    | to an external flash memory                                                                      | 48 |

| 28 | BIP model of the error_log atom                                                                  | 50 |

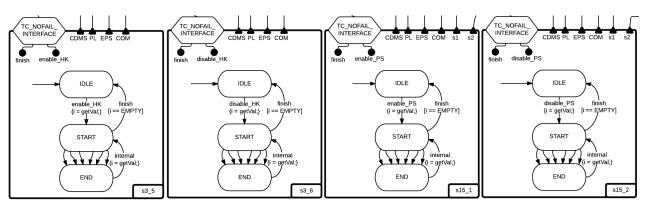

| 29 | BIP models of the s3_5, s3_6, s15_1 and s15_2 subservices                                        | 50 |

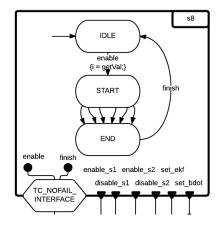

| 30 | BIP model of the s4_1 and s4_2 subservices                                                       | 51 |

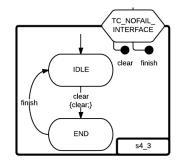

| 31 | BIP model of the s4_3 subservice                                                                 | 52 |