# FPGAs for the Masses: Affordable Hardware Synthesis from Domain-Specific Languages

### THÈSE Nº 7004 (2016)

PRÉSENTÉE LE 3 JUIN 2016

À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS LABORATOIRE D'ARCHITECTURE DE PROCESSEURS PROGRAMME DOCTORAL EN INFORMATIQUE ET COMMUNICATIONS

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

### Nithin GEORGE

acceptée sur proposition du jury:

Prof. M. Odersky, président du jury Prof. P. lenne, directeur de thèse Prof. J. Anderson, rapporteur Prof. K. Olukotun, rapporteur Prof. J. Larus, rapporteur

### **Abstract**

Field Programmable Gate Arrays (FPGAs) have the ability to be configured into applicationspecific architectures that are well suited to specific computing problems. This enables them to achieve performances and energy efficiencies that outclass other processor-based architectures, such as Chip Multiprocessors (CMPs), Graphic Processing Units (GPUs) and Digital Signal Processors (DSPs). Despite this, FPGAs are yet to gain widespread adoption, especially among application and software developers, because of their laborious application development process that requires hardware design expertise. In some application areas, domain-specific hardware synthesis tools alleviate this problem by using a *Domain-Specific* Language (DSL) to hide the low-level hardware details and also improve productivity of the developer. Additionally, these tools leverage domain knowledge to perform optimizations and produce high-quality hardware designs. While this approach holds great promise, the significant effort and cost of developing such domain-specific tools make it unaffordable in many application areas. In this thesis, we develop techniques to reduce the effort and cost of developing domain-specific hardware synthesis tools. To demonstrate our approach, we develop a toolchain to generate complete hardware systems from high-level functional specifications written in a DSL.

Firstly, our approach uses language embedding and type-directed staging to develop a DSL and compiler in a cost-effective manner. To further reduce effort, we develop this compiler by composing reusable optimization modules, and integrate it with existing hardware synthesis tools. However, most synthesis tools require users to have hardware design knowledge to produce high-quality results. Therefore, secondly, to facilitate people without hardware design skills to develop domain-specific tools, we develop a methodology to generate high-quality hardware designs from well known computational patterns, such as map, zipWith, reduce and foreach; computational patterns are algorithmic methods that capture the nature of computation and communication and can be easily understood and used without expert knowledge. In our approach, we decompose the DSL specifications into constituent computational patterns and exploit the properties of these patterns, such as degree of parallelism, interdependence between operations and data-access characteristics, to generate high-quality hardware modules to implement them, and compose them into a complete system design. Lastly, we extended our methodology to automatically parallelize computations across multiple hardware modules to benefit from the spatial parallelism of the FPGA as well as overcome performance problems caused by non-sequential data access patterns and long access latency to external memory. To achieve this, we utilize the data-access properties of the computa-

#### **Abstract**

tional patterns to automatically identify synchronization requirements and generate such multi-module designs from the same high-level functional specifications.

Driven by power and performance constraints, today the world is turning to reconfigurable technology (i.e., FPGAs) to meet the computational needs of tomorrow. In this light, this work addresses the cardinal problem of making tomorrow's computing infrastructure programmable to application developers.

*Keywords*— High-level synthesis, domain-specific languages, computational patterns, FPGA, reconfigurable computing

### Résumé

Les Circuits Logiques Programmables (FPGA) sont uniques dans leur capacité d'être configurable en architectures dédiées à une application. Ces architectures sont donc plus adaptées à ces problèmes computationnels spécifiques, leur permettant ainsi d'atteindre des performances et des efficacités energétiques surclassant d'autres architectures basées sur des processeurs, tels que les Microprocesseurs Multi-coeurs (CMPs), les Processeurs Graphiques (GPUs), et les *Processeurs de traitement du signal* (DSPs). Malgré cela, les FPGA n'ont toujours pas bénéficié d'une grande adoption, particulièrement parmi les developpeurs logiciels. Ceci s'explique principalement par le cycle de developpement d'applications pour FPGAs laborieux, nécessitant souvent des connaissances élevées en développement matériel. Dans certains domaines applicatifs, l'usage d'outils de synthèse matériel dédiés au domaine allègent ce problème en utilisant des langages dédiés (DSL) afin de cacher les détails les plus bas-niveau du matériel, et permettent ainsi d'améliorer la productivité des développeurs. De plus, ces outils tirent profit des connaissances du domaine pour effectuer des optimizations et ainsi produire des designs matériels de haute-qualité. Bien que cette approche soit très prometteur, le coût, ainsi que l'effort significatif requis pour développer de tels outils, la rend inabordable dans beaucoup de domaines applicatifs. Dans cette thèse, nous développons des techniques qui aident à réduire le coût et l'effort requis pour développer des outils de synthèse matériel dédiés à un domaine. Pour démontrer notre approche, nous developpons une suite d'outils pour générer des systèmes matériels entiers à partir de spécifications de haut-niveau décrit dans un langage dédié.

Dans un premier temps, notre approche utilise l'intégration des langages et du "staging" dirigé par types pour développer un langage dédié et un compilateur de manière rentable. Afin de réduire d'avantage l'effort requis, nous développons ce compilateur en composant des modules d'optimization réutilisables, et en l'intégrant avec des outils de synthèse matériel existants. Cependant, la plupart des outils de synthèse matériel nécessitent que les utilisateurs aient des connaissances en design matériel pour produire des systèmes de haute-qualité. Donc, dans un deuxième temps, afin de faciliter le développement d'outils de synthèse matériel dédiés à un domaine pour les personnes ayant peu de connaissances en design matériel, nous développons une méthodologie permettant de générer des designs matériels de haute-qualité à partir de motifs computationnels bien connus tels que map, zipWith, reduce et foreach. Ces motifs computationnels sont des méthodes algorithmiques décrivant la nature des calculs et des communications, et peuvent façilement être compris, ne nécessitent aucune connaissance en design matériel. Dans notre approche, nous décomposons d'abord les spécifications décrits

par le langage dédié en ses motifs computationnels constituants. Ensuite, nous exploitons leurs propriétés telles que le degré de parallelisme, l'interdépendance entre les opérations, et les charactéristiques des accès aux données, pour ainsi générer des modules matériels de haute-qualité, et les composons en un système matériel complet. Dans un dernier temps, nous étendons notre méthodologie pour parallelizer, de manière automatique, les calculs sur plusieurs modules matériels afin de profiter du parallelisme spatiale disponible dans un FPGA, et additionellement, afin de surmonter les problèmes de performances liés à l'accès non-contigu aux données et à la latence élevée des mémoires externes. Pour y parvenir, nous utilisons les propriétés d'accès aux données propre aux motifs computationnels pour identifier automatiquement les conditions de synchronization nécessaires, et ainsi générer ces designs à modules multiples à partir des mêmes spécifications fonctionelles de haut-niveau décrits par le langage dédié.

Porté par des contraintes énergétiques et de performances, le monde d'aujourd'hui se tourne de plus en plus vers les technologies reconfigurables (comme les FPGA) pour satisfaire les besoins computationnels de demain. Dans cette perspective, cette thèse adresse un problème essentiel qui est de rendre l'infrastructure computationnelle de demain programmable aux developpeurs logiciels.

*Mot-clés*— Synthèse matériel à haut-niveau, langages dédiés, motifs computationnels, FPGA, calcul reconfigurable

### Acknowledgements

I would like to express my sincere gratitude to my supervisor, Paolo Ienne, for his guidance and support. He has been a great mentor. His invaluable feedback helped to improve my research methodology and enabled me to grow as a person.

I would like to thank the members of the thesis committee, Jason Anderson, James Larus, Kunle Olukotun and Martin Odersky, for both finding time to review my work, and for their insightful comments and suggestions that significantly improved the quality of this thesis.

I had the good fortune to collaborate with many people during my Ph.D. studies. I would like to especially thank HyoukJoong Lee whose comments and suggestions had a remarkable impact on my work, and Mikhail Asiatici for his help with some of the engineering work. I would like to express my heartfelt gratitude to Joao Andrade, David Novo, Tiark Rompf, Kimon Karras, Philip Brisk, David Andrews, Gabriel Falcao, Kunle Olukotun and Martin Odersky for their help on various publications, some of which are used in this thesis. My sincere thanks also goes to Vipin Kizheppatt, Kermin Flemming, Hsin-Jung Yang, Nehal Bhandari and Mohammad Shahrad for their help on various projects.

I would like to express my deep appreciation to Ross Kory, Ali Galip Bayrak, Ana Petkovska and Grace Zgheib for their comments on this manuscript, and to Sahand Kashani-Akhavan for translating the abstract of the thesis into French.

It has been a great pleasure for me to be a part of LAP (Processor Architecture Laboratory). I had a great time in the company of my fellow LAP member—Ajay, Ali, Ana, Andrew, Chantal, David, Grace, Hadi, Lana, Madhura, Mikhail, Mirjana, Nikola, Paolo, Philip, Rene, Robert, Theo, Xavier, many interns and visiting collaborators. I would like to especially thank Ali, Robert and Chantal for their friendship, guidance, encouragement and support throughout my journey at LAP.

My stay in Switzerland was extremely enjoyable, thanks to the excellent company of friends—Amir, Carlos, Christian, Denys, Francois, Felix, Manohar, Mark, Nada, Olga, Panagiotis, Sandro, Sebastian, Sepand, Thomas, Vagia, Vlad, Vojin and many others. I thank Manohar and Sandro for always being available for discussions, some of which had a direct impact on my work.

It would have been impossible to go through this journey without the support of my family. I am eternally grateful for their unconditional love and limitless support throughout my life.

Lausanne, April 18, 2016

# Contents

| Ał | ostra | t (English)                                                                    | V           |

|----|-------|--------------------------------------------------------------------------------|-------------|

| Ał | ostra | t (French)                                                                     | vii         |

| Ac | knov  | rledgements                                                                    | ix          |

| Ta | ble o | f contents x                                                                   | iii         |

| Li | st of | igures x                                                                       | vi          |

| Li | st of | ables                                                                          | / <b>ii</b> |

| 1  | Intr  | oduction                                                                       | 1           |

|    | 1.1   | High-Level Synthesis                                                           | 3           |

|    | 1.2   | Objective                                                                      | 5           |

|    |       | 1.2.1  Building Domain-Specific Hardware Synthesis Tools With Low Effort  .  . | 5           |

|    |       | 1.2.2 Generating Efficient Hardware Designs from Computational Patterns        | 6           |

|    |       | 1.2.3 Generating Multi-Module Hardware Designs from Computational Patterns     | 7           |

|    | 1.3   | Outline                                                                        | 8           |

| 2  | Bac   | ground and Related Work                                                        | 9           |

|    | 2.1   | High-Level Synthesis Tools                                                     | 9           |

|    |       | 2.1.1 General-Purpose Hardware Synthesis Tools                                 | 11          |

|    |       | 2.1.2 Domain-Specific High-Level Synthesis Tools                               | 16          |

|    | 2.2   | Generating Hardware Designs from Computational Patterns                        | 17          |

|    |       | •                                                                              | 17          |

|    |       | 2.2.2 Using Computational Patterns for Processor-Based Architectures           | 18          |

|    |       | 2.2.3 Using Computational Patterns for Hardware Synthesis                      | 18          |

| 3  | Mal   | ing Domain-Specific Hardware Synthesis Tools Cost-Efficient                    | 21          |

|    | 3.1   | Motivation                                                                     | 21          |

|    | 3.2   |                                                                                | 23          |

|    | 3.3   | •                                                                              | 26          |

|    |       | 3.3.1 Overview of Scala and LMS                                                | 26          |

|    |       | 3.3.2 Hardware Synthesis Workflow Using Scala and LMS                          | 28          |

#### **Contents**

|   | 3.4  | Hardware Designs from Matrix Expressions                     | 28  |

|---|------|--------------------------------------------------------------|-----|

|   |      | 3.4.1 Designing the Optimization Modules                     | 29  |

|   |      | 3.4.2 Managing the Compilation Process                       | 36  |

|   | 3.5  | Evaluation Results                                           | 37  |

|   |      | 3.5.1 Benchmark Designs                                      | 38  |

|   |      | 3.5.2 Evaluating Benefit of Integrating to C-to-RTL Tool     | 38  |

|   |      | 3.5.3 Evaluating Benefit of Integrating to IP-Core Generator | 40  |

|   | 3.6  | Discussion                                                   | 41  |

| 4 | Har  | dware System Synthesis from Computational Patterns           | 43  |

|   | 4.1  | Motivation                                                   | 43  |

|   | 4.2  | Overview of the Methodology                                  | 46  |

|   | 4.3  | Compiling DSL-Programs to Patterns                           | 49  |

|   |      | 4.3.1 Compiler Infrastructure                                | 49  |

|   |      | 4.3.2 Computational Patterns                                 | 50  |

|   |      | 4.3.3 OptiML Application Example: Normalization              | 52  |

|   | 4.4  | Hardware Generation from Patterns                            | 54  |

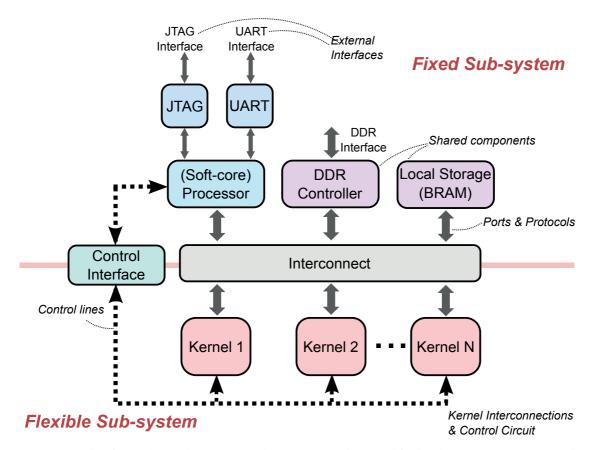

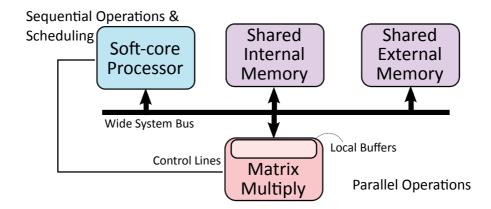

|   |      | 4.4.1 System Architecture Template                           | 54  |

|   |      | 4.4.2 Kernel Synthesis                                       | 55  |

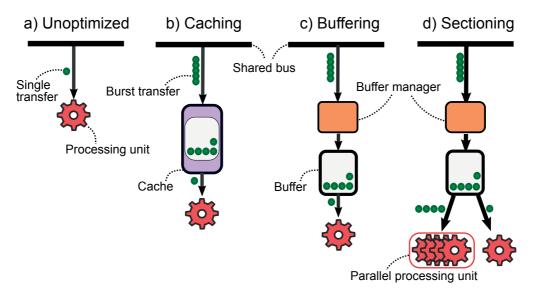

|   |      | 4.4.3 Kernel Optimization                                    | 57  |

|   |      | 4.4.4 System Synthesis                                       | 63  |

|   | 4.5  | Evaluation Results                                           | 65  |

|   |      | 4.5.1 Evaluation Setup and Methodology                       | 65  |

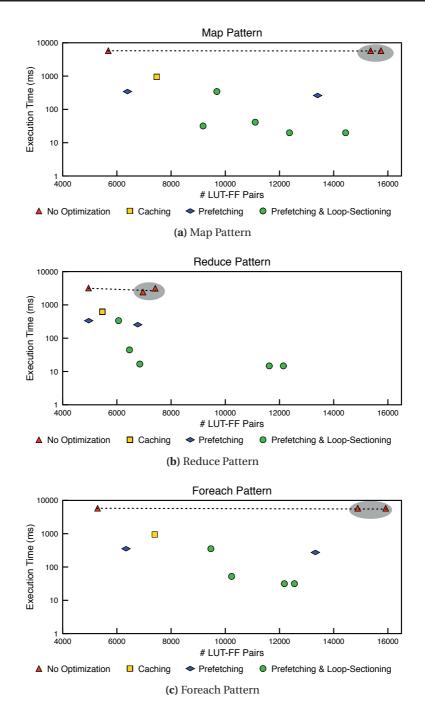

|   |      | 4.5.2 Evaluating with Microbenchmarks                        | 66  |

|   |      | 4.5.3 Evaluating with Application Benchmarks                 | 68  |

|   | 4.6  | Discussion                                                   | 75  |

| 5 | Leve | eraging Multi-Module Parallelism with Computational Patterns | 77  |

|   | 5.1  | Motivation                                                   | 77  |

|   | 5.2  | Modifications to the Hardware Generation Flow                | 81  |

|   | 5.3  | Data Access Properties of Parallel Patterns                  | 84  |

|   | 5.4  | Parallelizing Computation Across Multiple Modules            | 85  |

|   |      | 5.4.1 Identifying Synchronization Requirements               | 85  |

|   |      | 5.4.2 Reducing Synchronization Requirements                  | 88  |

|   |      | 5.4.3 Generating the Complete System                         | 90  |

|   |      | 5.4.4 Managing the Multiple Modules                          | 92  |

|   | 5.5  | Evaluation Results                                           | 94  |

|   |      | 5.5.1 Evaluation Setup and Methodology                       | 95  |

|   |      | 5.5.2 Evaluating with Application Benchmarks                 | 95  |

|   | 5.6  | Discussion                                                   | 99  |

| 6 | Con  | nclusions                                                    | 101 |

|   | 6.1  | Summary                                                      | 101 |

|        |                          | Conte | nts |

|--------|--------------------------|-------|-----|

|        | Benefits of the Approach |       |     |

| Biblio | ography                  | 1     | 07  |

| Curric | culum Vitae              |       |     |

# **List of Figures**

| 1.1  | FPGA design development flow                                                           | 3  |

|------|----------------------------------------------------------------------------------------|----|

| 1.2  | Design generation using HLS                                                            | 4  |

| 3.1  | HLS Tool Design Using Traditional Compiler Frameworks                                  | 23 |

| 3.2  | HLS Tool Design Using Our Approach                                                     | 24 |

| 3.3  | LMS-based workflow for hardware synthesis                                              | 27 |

| 3.4  | Optimizing matrix expression for implementing on hardware                              | 29 |

| 3.5  | Embedding a DSL (MatrixDSL) in Scala                                                   | 30 |

| 3.6  | MatrixDSL-program for a matrix expression                                              | 31 |

| 3.7  | IR-nodes for some operators in MatrixDSL                                               | 31 |

| 3.8  | Staging a MatrixDSL-program using LMS                                                  | 32 |

| 3.9  | Specifying optimization rules using staging-time macros                                | 33 |

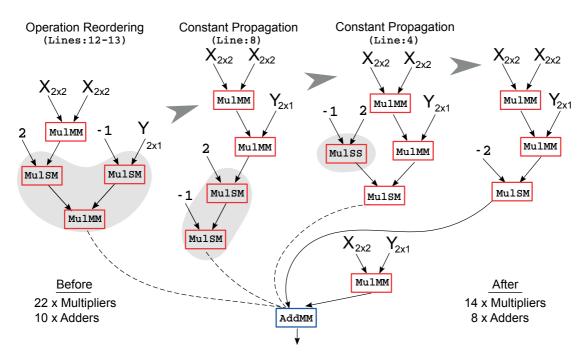

| 3.10 | Automatic application of staging-time macros on the IR-graph                           | 34 |

| 3.11 | Code generation from the IR-graph in LMS                                               | 35 |

| 3.12 | Transforming a ${\tt MatrixDSL-program}$ into an optimized output program              | 36 |

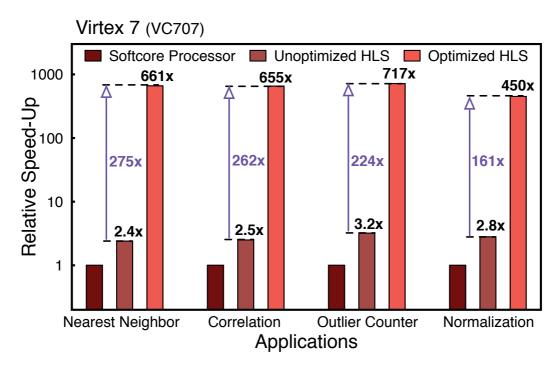

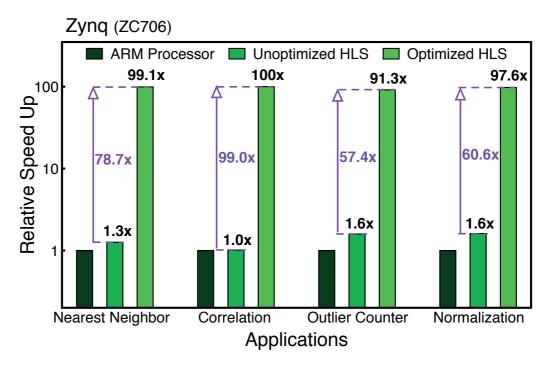

| 4.1  | Comparing optimized HLS, unoptimized HLS and DSL specifications                        | 44 |

| 4.2  | Overview of the hardware generation methodology                                        | 47 |

| 4.3  | Computational patterns used for hardware generation                                    | 51 |

| 4.4  | Normalization application written in OptiML                                            | 52 |

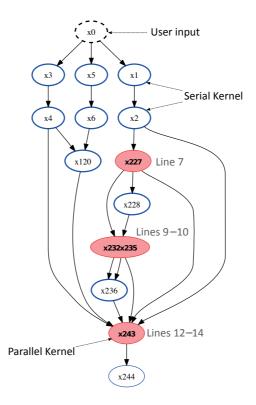

| 4.5  | Dependency graph for the normalization application                                     | 53 |

| 4.6  | System-architecture template for hardware systems generated from $\mbox{\rm OptiML}$ . | 54 |

| 4.7  | Premeditated optimizations that are applied to the kernels                             | 56 |

| 4.8  | Data structures used to perform program analysis                                       | 61 |

| 4.9  | Performance-area trade-off between the different hardware module variants .            | 67 |

| 4.10 | Performance comparison among implementations on a Virtex7 FPGA                         | 70 |

|      | Performance comparison among implementations on a Zynq FPGA                            | 71 |

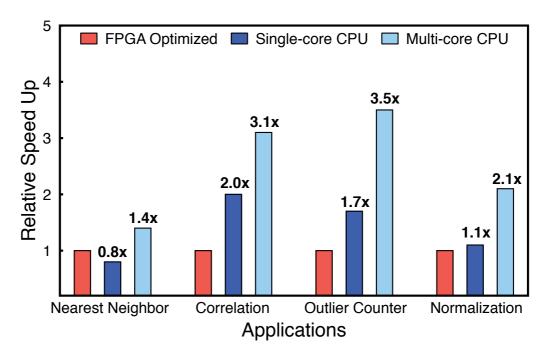

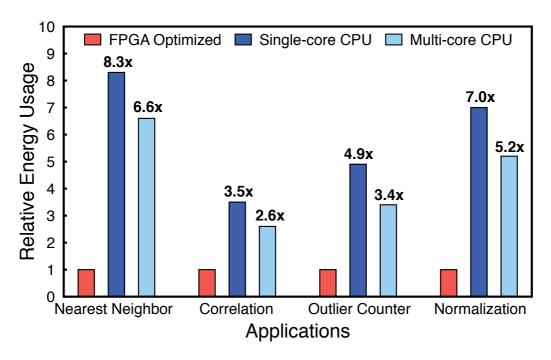

| 4.12 | Performance comparison between FPGA and CPU                                            | 73 |

| 4.13 | Energy-efficiency comparison between FPGA and CPU                                      | 74 |

| 5.1  | Matrix multiplication in OptiML                                                        | 78 |

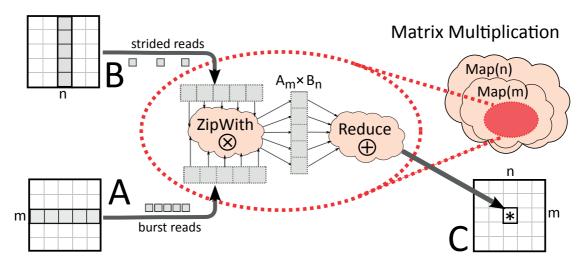

| 5.2  | Expressing matrix multiplication using computational patterns                          | 79 |

| 5.3  | Utilizing multiple hardware modules to improve application performance $\ \ldots \ $   | 80 |

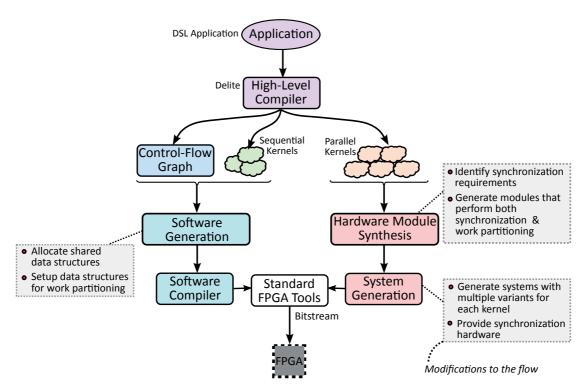

| 5.4  | Modifying the hardware generation flow for multi-module parallelization $$             | 82 |

### List of Figures

| 5.5  | Hardware system for the matrix multiplication with a single module                   | 83 |

|------|--------------------------------------------------------------------------------------|----|

| 5.6  | Data access properties of parallel patterns                                          | 84 |

| 5.7  | Synchronization rules for simple patterns                                            | 86 |

| 5.8  | Synchronization rules for nested patterns                                            | 87 |

| 5.9  | Reducing synchronization overheads for map, zipWith and foreach                      | 89 |

| 5.10 | Employing multiple hardware modules for matrix multiplication                        | 91 |

| 5.11 | Matrix multiplication program using precomputed results                              | 93 |

| 5.12 | Leveraging multi-module parallelism with dynamic workload partitioning $\ \ldots \ $ | 94 |

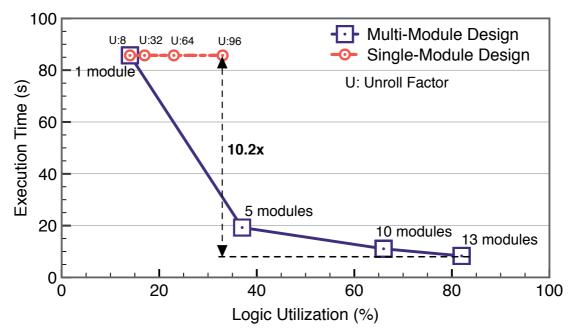

| 5.13 | Performance comparison between single-module and multi-module designs .              | 97 |

## List of Tables

| Comparison of alternatives after applying staging-time macros                           | 35                                       |

|-----------------------------------------------------------------------------------------|------------------------------------------|

| Matrix expressions used for benchmarking                                                | 37                                       |

| Results: extending an HLS tool to generate optimized hardware circuits for              |                                          |

| matrix expressions (fixed point case)                                                   | 37                                       |

| Results: extending an HLS tool to generate optimized hardware circuits for              |                                          |

| matrix expressions (floating point case)                                                | 40                                       |

| Results: integrating to an IP generator to generate optimized hardware circuits         |                                          |

| for matrix expressions (floating point case)                                            | 40                                       |

| Datatype, computation patterns and hardware modules in each application                 | 69                                       |

| Results: percentage utilization of resource in each benchmark application $\ \ . \ \ .$ | 69                                       |

| Parallel operations and computational patterns in each application                      | 96                                       |

|                                                                                         | 98                                       |

|                                                                                         | Matrix expressions used for benchmarking |

### 1 Introduction

Today, we are living in an age where the way we generate wealth, network socially, search for information, conduct research and advance science have all become increasingly data-driven. Naturally, we have come to rely heavily on our computing facilities [Bell et al., 2009, Anderson, 2008] to process this data. In 2007, humankind stored about  $2.9 \times 10^{20}$  bytes of optimally compressed digital data (growing at a rate of 23% annually) and were scaling up the sizable computing infrastructure at a rate of 58% annually [Hilbert and López, 2011]. Now, the increasing cost of operating this massive and growing computing infrastructure has become a major concern [Koomey et al., 2009]. Microprocessors are at the heart of almost all of our computing infrastructure today. Yet, microprocessors have been shown to be quite lacking in energy efficiency compared to Application-Specific Integrated Circuits (ASICs). Additionally, researchers have shown that application-specific modifications to the architecture can considerably improve both the energy-efficiency and performance of microprocessors [Hameed et al., 2010]. However, architecture of the microprocessor was designed to be flexible and perform well for a wide variety of computing tasks for different applications. Hence, it is infeasible to make application-specific alterations to the processor architecture without affecting its suitability to handle this large range of workloads. Field Programmable Gate Arrays (FPGAs) are devices that were designed to be programmed into customized computing architectures. Furthermore, researchers have shown that FPGAs can implement application-specific architectures that achieve both high energy-efficiency and computing performance [Kestur et al., 2010, Betkaoui et al., 2010, Fowers et al., 2012]. The broad objective of

FPGAs can efficiently tackle the data deluge

this thesis is to make it easier to develop FPGA applications and make reconfigurable technology more accessible to users.

FPGA users need to have hardware design expertise FPGAs are used in a number of application areas, including communication, aerospace and defense, automotive, consumer electronics and medicine, but often as ASIC replacements for low volume products or as prototyping platforms. Despite their potential as a high performance and energy efficient computing unit, they are seldom used within datacenters or other general purpose computing infrastructure [Putnam et al., 2014]. To a large extent, this is due to the complicated workflow for developing and implementing applications on an FPGA which is markedly different from *any* software development flow.

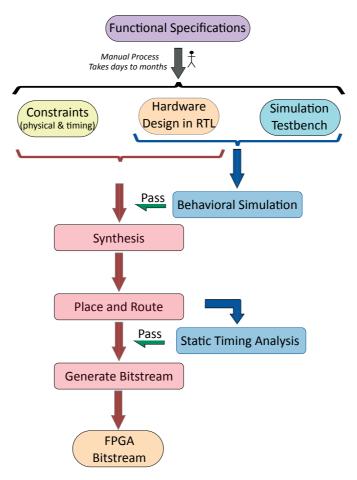

The application implementation workflow for FPGAs is illustrated in Figure 1.1. The first step, as shown in the figure, is to develop a hardware design at a Register Transfer Level (RTL) from high-level functional specifications. This is often a tedious manual process that can easily take a few months. During this step, in addition to the hardware design, one needs to write a test bench to verify correctness of the design and create constraint files that hold the timing and physical placement constraints needed to implement the design on the FPGA. Once the design is verified through simulation, the synthesis step compiles the RTL description into a gate-level netlist and maps these gates to the physical components on the FPGA, such as LUTs, FFs, BRAMs and DSPs. The subsequent place and route step finds physical placements for the components on the device and determines how the wires between these components can be routed on the FPGA's configurable routing fabric. Static timing analysis is performed on the placed and routed design to check if the design meets the timing constraints set by the user. If the timing constraints are satisfied, the generate bitstream step produces the bitstream file that is used to program the FPGA. This file contains the configuration for the logic and routing components to implement the hardware design on the device. This FPGA design implementation workflow bears a lot of similarity to the standard ASIC development flow and warrants a significant amount of hardware design expertise. Therefore, application developers without any hardware design background find it difficult, if not impossible, to develop FPGA applications.

**Figure 1.1:** FPGA design development flow. In the typical FPGA design development flow, the user translates functional specifications into a hardware design, a tedious and error-prone process that can take months. Additionally, steps such as specifying the physical and timing constraints, verifying the design through simulation, and validating and correcting the implementation based on static analysis are all performed at a circuit-level. These aspects make this development flow extremely hard for users without hardware design expertise.

### 1.1 High-Level Synthesis

Developing the hardware design in RTL is perhaps the biggest obstacle that deters users without hardware design expertise from using FPGAs. Even for hardware design experts, developing the RTL specifications is a laborious task that limits their productivity and their ability to scale up to larger design sizes while coping with time-to-market pressures. In recent years, there has been a more concerted effort from the industry to tackle this problem and we have seen the emergence of new *High*-

HLS tool users also need hardware design knowledge

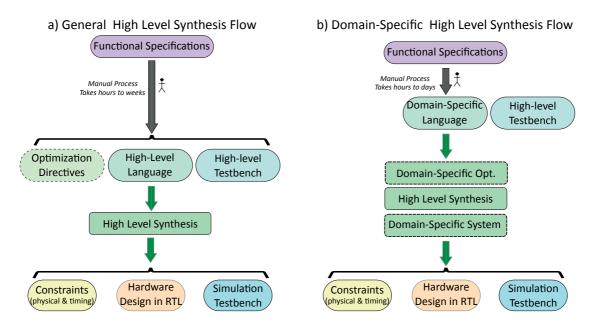

**Figure 1.2:** Design generation using HLS. a) *High-Level Synthesis* (HLS) tools enable users to generate hardware designs from functional specifications in high-level languages, such as C, C++, SystemC and OpenCL, and, therefore, requires less effort and time. b) Domain-specific synthesis tools focus on synthesizing hardware designs for specific application areas. They often use a *Domain-Specific Language* (DSL) for input specifications, perform optimizations based on the domain knowledge and create complete hardware systems for the specific application. This enables them to achieve improved productivity, better design quality and make designing hardware more accessible to users with no hardware design knowledge.

Level Synthesis (HLS) tools. These tools, as illustrated in Figure 1.2a, can generate hardware designs from high-level specifications written in languages such as in C, C++, SystemC and OpenCL, to significantly enhance the productivity of the user [Xilinx, 2013a, Czajkowski et al., 2012, Xilinx, 2015]. While most of these tools can produce hardware designs from high-level functional specifications, they still require the user to refactor the input specifications and provide additional optimization directives to produce good quality hardware designs. However, users require a considerable amount of hardware design expertise to specify these directives and, therefore, these tools are ineffective in enabling non-hardware-experts to develop FPGA applications.

Domain-specific synthesis tools can alleviate the need for hardware design expertise to use FPGAs Some high-level synthesis tools, such as Spiral [Milder et al., 2012], HDL Coder [The MathWorks, 2015], Optimus [Hormati et al., 2008], and MMAlpha [Derrien et al., 2008] target specific application domains in which they make designing hardware more accessible to their users. As

illustrated in Figure 1.2b, compared to other HLS tools domain-specific tools offer the following three important advantages:

- 1. They often use a *Domain-Specific Language* (DSL) for input specifications which provides a suitable syntax and abstraction to make it easier for domain experts to develop applications.

- They leverage the detailed knowledge of the application domain properties to perform optimization and achieve improved quality of results.

- 3. Due to their domain specialization, these tools can automatically package the hardware designs they generate with necessary integration facilities (e.g., hardware interfaces, software *Application Programming Interface* (API) and drivers) to make it directly usable for the intended application.

Therefore, these tools hold great potential in making reconfigurable technology more accessible to users in different application domains. Despite these advantages, developing domain-specific tools incurs significant effort, as well as cost, and it makes this approach impractical in many application areas.

### 1.2 Objective

Our objective in this thesis is to develop a methodology to alleviate the cost and effort needed to develop domain-specific hardware synthesis tools. To demonstrate this methodology, we develop an infrastructure that can be used to generate complete hardware systems from high-level DSL applications.

### 1.2.1 Building Domain-Specific Hardware Synthesis Tools With Low Effort

Developing a new domain-specific HLS tool is a significant effort because it often involves designing an entirely new DSL, compiler, development and debugging environments. However, if the new language is developed as an embedded DSL [Mernik et al., 2005] (i.e., the DSL is created by extending a host language by adding domain-specific language elements), it can share some of the infrastructure of the host language, such as type system, module system, development and de-

Language embedding and type-directed staging can reduce domain-specific tool development cost bugging environments, and avoid repeating this effort. Additionally, we can use type-directed staging [Carette et al., 2009] to reduce the effort needed to develop a compiler for programs written in this new DSL. In our effort, we explore the benefits of this approach using Scala [Odersky et al., 2004] as the host language and *Lightweight Modular Staging* (LMS) [Rompf and Odersky, 2012] infrastructure for developing the compiler. These techniques have been successfully employed for software development [Sujeeth et al., 2014, Ofenbeck et al., 2013, Ackermann et al., 2012], and we investigate how they can be useful for developing domain-specific hardware synthesis tools [George et al., 2013]. Additionally, to reduce the repeated development effort for different toolchains, we propose to develop the tool in a modular fashion by creating reusable optimization modules; these modules, once developed, can be reused in a completely different toolchain with very little effort.

### **1.2.2** Generating Efficient Hardware Designs from Computational Patterns

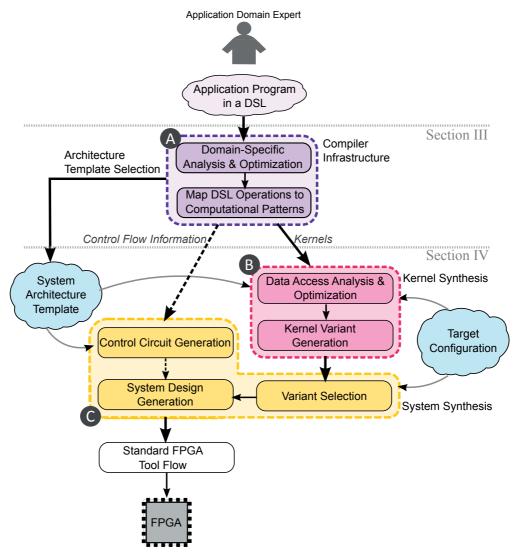

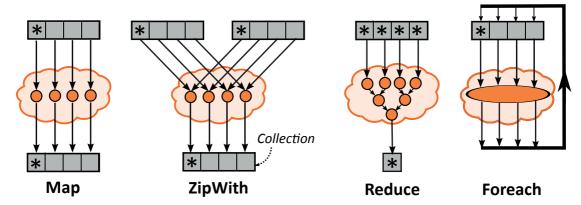

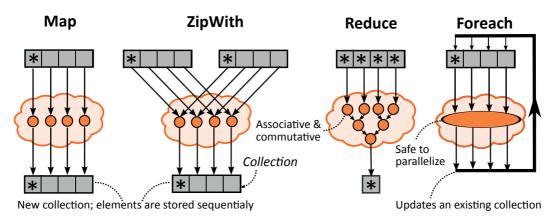

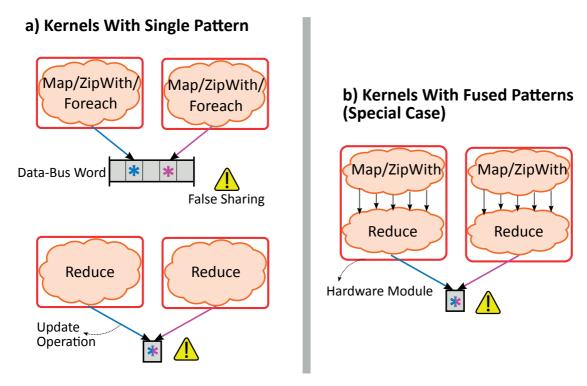

Computational patterns can bridge the divide between high-level applications and highperformance designs Developing new domain-specific tools will become appreciably easier if they can share a common infrastructure for generating hardware. Furthermore, to enable software developers and domain-experts, who might be developing domain-specific tools, to benefit from this infrastructure, it must not demand hardware design expertise from the user. After studying applications from different domains, researchers have determined that they often contain a small set of computational patterns that can be used to express these applications [Asanovic et al., 2006, McCool et al., 2012]. Computational patterns are simple algorithmic methods that capture a pattern of computation and communication which makes them easy to understand and use without any advanced knowledge. These computational patterns have well known properties, such as parallelism, dependency between operations or the nature in which they produce or consume data. There are compilation infrastructures that can leverage these properties to efficiently implement high-level applications on a variety of different platforms, including Chip Multiprocessors (CMPs), Graphic Processing Units (GPUs) and clusters [Sujeeth et al., 2014, Catanzaro et al., 2011]. Similar techniques can be used to map applications on FPGAs where the properties of the computational patterns can be exploited to produce efficient circuit structures to implement them [George et al., 2014]. For instance, computational patterns with a large amount of structured parallelism can leverage the spatial parallelism in the FPGA. Patterns with no parallelism can also benefit from architecture customization, but since these patterns often offer limited scope for acceleration, they can be implemented on a shared processor to conserve resources. When the application is written in a DSL, the domain knowledge can be utilized to perform optimizations as well as to select a suitable architecture template for the system-level integration. This can enable a tool to automatically generate complete hardware systems to implement the application.

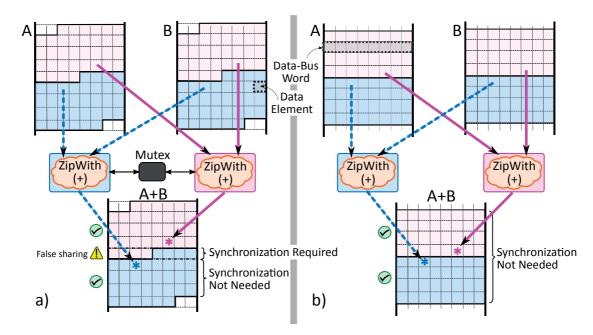

### 1.2.3 Generating Multi-Module Hardware Designs from Computational Patterns

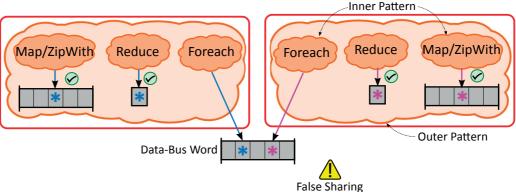

Parallel architectures such as CMPs, GPUs and FPGAs perform particularly well for applications that have sufficient parallelism to leverage all the processing resources on the device. To achieve good performance, the implementation must also ensure a high-bandwidth supply of data to keep the parallel processing resources busy. But, non-sequential data access patterns and long memory access latencies can often cause data starvation at the processing resources and significantly hamper the performance of applications. Parallelizing computation across multiple independent hardware modules is a way to tackle this problem and one that been successfully used in CMPs and GPUs. To achieve this on an FPGA, the application developer must correctly identify how shared data is accessed from different modules and use synchronization schemes to guard access to this data. This can be difficult for large applications and there can be issues such as false sharing [Bolosky and Scott, 1993] that make this process even harder. When an application is decomposed into computational patterns, these patterns capture the data access properties within the application. We leverage these properties to automatically identify when synchronization is needed among the modules and how these synchronization requirements can be relaxed [George et al., 2015]. Armed with this knowledge, a tool can automatically generate complete hardware designs where the computation is parallelized across multiple modules. Moreover, these designs employ a dynamic workload partitioning scheme to effectively leverage these modules and deliver performance improvements.

Computational patterns can enable automated tools to leverage the spatial parallelism of the FPGA

### 1.3 Outline

Outline The rest of the thesis is organized as follows.

- **Chapter 2** provides some background information on different HLS approaches and discusses related work.

- Chapter 3 explores the idea of using language embedding and type-directed staging to reduce the effort needed to develop domain specific hardware synthesis flows. We will illustrate how these ideas can be applied to generate hardware circuits to implement linear algebra expressions.

- Chapter 4 discusses how decomposing high-level applications into computational patterns can enable automatic generation of high performance hardware systems targeting FPGAs. To demonstrate the approach, we extend the Delite compiler infrastructure [Sujeeth et al., 2014, Lee et al., 2011] to develop a tool flow that generates complete hardware systems from high-level functional specifications in a DSL-program.

- Chapter 5 extends the approach developed in Chapter 4 to automatically generate multi-module hardware systems from the same high-level DSL-programs. These hardware systems parallelize the computation across multiple hardware modules to deliver improved performance.

- **Chapter 6** concludes the thesis and presents some ideas for future work.

### 2 Background and Related Work

### 2.1 High-Level Synthesis Tools

Developing hardware designs for FPGAs is an effort intensive process that can stretch into months. Therefore, there has been widespread interest in developing HLS tools to alleviate this development effort and make reconfigurable technology more accessible to application developers. HLS tools enable users to synthesize hardware designs from high-level specifications in languages such as C [Kernighan et al., 1988], C++ [Stroustrup, 1986], OpenCL [Stone et al., 2010], CUDA [NVIDIA Corporation, 2015] and Java [Arnold et al., 1996]. Compared to designing in RTL, the benefits of using HLS tools include the following:

Benefits of HLS tools

- 1. *Productivity and scalability*: HLS tools improve productivity since they accept input specifications at a higher level of abstraction and generate RTL specifications for a hardware design, typically in *Hardware Description Languages* (HDL) such as VHDL or Verilog. This enables users to develop large scale designs at a high level of abstraction.

- Design space exploration: Since HLS tools can reduce the design development time, users can leverage these tools to quickly evaluate many design options and, thereby, explore a much larger design space.

- 3. Accessibility to non-hardware-experts: Many HLS tools use high-level languages (i.e., C, C++, OpenCL, CUDA and Java) which are widely used for software development. Therefore, these tools are more comfortable to use for people with software development

- backgrounds. Although these tools often require hardware design expertise to develop good quality designs, the higher level of abstraction offered by these tools make them much easier to learn for new users.

- 4. Debugging and verification efforts: Many HLS tools also help users to easily generate testbenches¹ to verify the correctness of the generated hardware designs. Since the HLS tools often use popular software development languages, users can also leverage widely used software debugging facilities to easily verify the high-level specifications. More recently, there are also efforts at integrating debugging infrastructure into HLS tools to make it easier to debug the generated designs without delving down to the circuit-level details [Calagar et al., 2014, Goeders and Wilton, 2015].

- 5. *Portability*: Starting from the same input specifications, HLS tools can automatically generate the RTL specifications that are tuned to different implementation targets, e.g., FPGA devices from different product families, vendors or with different resource constraints. Therefore, these tools offer a design portability that is seldom possible when developing the design directly in HDL.

History of HLS tools

Due to these benefits, there has been many efforts, both in academia and industry, to develop such HLS tools. Martin and Smith [Martin and Smith, 2009] provide a good overview of the history of HLS tools. According to the authors, HLS tools have evolved over three generation. During the first generation, tool development occurred mostly in academia and much of the core algorithmic research occurred during this period. In the second generation, the industry took active interest in HLS tools and many commercial tools were developed, but they did not have much economic success, largely because of the bad quality of results and wrong choice of specification languages. In the following third generation, which started in early 2000s, there was a change in focus and many new HLS tools were developed that take specifications in languages such as C, C++ and SystemC to produce good quality hardware designs; This has improved adoption of HLS tools among system-level designers who already have a significant amount of hardware design expertise. However, to further improve the adoption, we need to develop tools that will permit software developers and application domain experts

$<sup>^1</sup>$ Testbenches contain a set of input stimuli as well as expected responses and are used to verify the correctness of a hardware circuit

to create good quality hardware designs despite their lack of hardware design knowledge.

As a result of the rich history, today there exists a large number of HLS tools, each focusing on different aspects, like target application domain, implementation architectures and input languages. Nane et al. [Nane et al., 2016] and Meeus et al. [Meeus et al., 2012] have provided good overviews of the rich selection of hardware synthesis tools that exist today, and Bacon et al. [Bacon et al., 2013] classified some of these tools based on the programming languages they use. We are interested in tools that use domain-specific languages to make programming reconfigurable hardware more accessible to application domain experts and software programmers. Therefore, in this section, we try to classify these efforts into two main categories: general-purpose hardware synthesis tools and domain-specific hardware synthesis tools.

Survey and classification of HLS tools

#### 2.1.1 General-Purpose Hardware Synthesis Tools

The most popular approach today is to offer HLS tools that take input specifications in a C-like language, such as C, C++, OpenCL and CUDA. Among them, the traditional approach was to develop tools to use sequential variants of C, such as C and C++. Later, with the increasing prominence of parallel programming methodology, there have been efforts to use parallel programming models, such as PThreads [Nichols et al., 1996] and OpenMP [Dagum and Menon, 1998], and later, explicitly parallel variants to C, such as OpenCL and CUDA. In addition to these, there have been efforts to use other general-purpose programming languages, such as Python [Van Rossum and Drake, 2003], Java [Arnold et al., 1996], Haskell [Thompson, 1999] and custom developed languages for hardware synthesis.

#### Synthesis from Sequential C-Like Languages

Languages such as C and C++ offer direct and low-level control while developing software for processors. Consequently, these languages are often used to develop performance critical parts of programs. In areas such as embedded systems, these languages are almost defacto standards for application development. Since ASICs and FPGAs can offer improved performance and energy efficiency compared to processors,

Using sequential Clike languages for hardware synthesis there is a lot of interest in developing tools to help port the critical parts of such applications into hardware designs that can be implemented as an ASIC or on an FPGA. Therefore, there are many HLS tools that generate hardware designs from specifications in C and C++. Many of these tools also support SystemC [Grötker et al., 2010] which was developed as set of C++ classes to make it easier to model hardware circuits in C.

Tools that accept C, C++ or SystemC for input specifications include Vivado High-Level Synthesis [Xilinx, 2013a], Handel-C [Mentor Graphics, 2015], Catapult [Calypto Design Systems, 2014], Synphony [Synopsys Inc., 2014], CyberWorkBench [Wakabayashi, 2005], ROCCC [Villarreal et al., 2010], LegUp [Canis et al., 2011] and Trident[Tripp et al., 2007] to name just a few. Among them, Vivado High-Level Synthesis, Handel-C, Catapult, Synphony and CyberWorkBench are commercial tools. Trident focuses on mapping computations rich in floating-point operations on FPGA. ROCCC and LegUp are open-source tools that are being developed in the academia; among them LegUp can generate standalone hardware implementations as well as processor-accelerator architectures targeting different FPGAs.

Drawbacks

FPGA implementations often leverage the spatial parallelism of the device to improve the performance of application. However, extracting parallelism from sequential C-programs is hard [Cong et al., 2011]. Therefore, many of these tools require the user to refactor the code and provide additional information (e.g., compiler directives and configuration parameters) to generate parallel hardware. This makes these tools harder to use for the developer.

#### **Synthesis using Parallel Programming Models**

Using parallel programming models for hardware synthesis FPGAs excel in parallel execution by performing operations in a spatially parallel manner. Therefore, researchers have tried to use parallel programming models, such as OpenMP [Dagum and Menon, 1998] and PThreads [Nichols et al., 1996], to develop applications for FPGAs. These models extend the sequential C-like languages to enable users to programmatically express the parallelism in the computation. Additionally, this also makes the specifications portable between the different tools since the users no longer have to use ad hoc optimization directives or configuration parameters that differ from one tool to another. Efforts

to synthesize hardware using parallel programming models include Leow et al. [Leow et al., 2006] who automate the generation of hardware systems by producing Handel-C and VHDL code from OpenMP programs; Cilardo et al. [Cilardo et al., 2013] who generate C code from OpenMP program and use CoDeveloper [Antola et al., 2007] (another commercial C-to-HDL tool) to generate hardware; and Choi et al. [Choi et al., 2013] who achieve the same from programs using both OpenMP and PThreads by extending LegUp to generate hardware systems.

Other efforts have implemented multi-processor systems on FPGAs and utilized the parallel programming models to program these systems. Among them, efforts such as Hthreads [Andrews et al., 2008], Fuse [Ismail and Shannon, 2011] and ReconOS [Agne et al., 2014] use PThreads and provide generalized operating system services to systems that support hardware and software threads. SPREAD [Wang et al., 2013] utilizes PThreads and provides an integrated solution for streaming applications.

Using parallel programming models to target multi-processor systems on FPGAs

These efforts, especially those that target multi-processor systems, have been successful in enabling software developers to develop and run applications on FPGAs. But, the common problem with these efforts is that they place the tedious and error-prone task of identifying synchronization requirements and correctly parallelizing the application on the programmer. In the case of HLS tools, the users may need to understand details of the generated hardware design to perform optimizations. The processor-based approaches do not fully exploit the application specific customizability offered by FPGAs. Since they use processors as computing units, they also suffer from the energy-inefficiencies of this general-purpose, instruction driven architecture [Hameed et al., 2010]; additionally, these inefficiencies are now worsened because the implementation target is an FPGA and not an ASIC [Kuon and Rose, 2007].

Drawbacks

### **Synthesis from Parallel C-Like Languages**

The growing popularity of using GPUs for general-purpose computation saw the emergence of new parallel C-like languages such as CUDA [NVIDIA Corporation, 2015] and OpenCL [Stone et al., 2010] that were developed to program these devices. Compared to the sequential variants, these languages make the parallelism explicit and therefore much easier for compilers to generate implementations tar-

Using parallel Clike languages for hardware synthesis geting parallel architectures, including FPGAs. Papakonstantinou et al. [Papakonstantinou et al., 2009] demonstrate that CUDA can be used for programing FPGAs. Commercial tools to generate hardware designs from OpenCL programs include Xilinx's SDAccel [Xilinx, 2015] and Altera SDK for OpenCL [Czajkowski et al., 2012]. SOpenCL [Owaida et al., 2011] is an academic tool that generates hardware designs from OpenCL program.

Drawbacks

Languages such as OpenCL and CUDA are good to program applications that have regular, fine-grained data parallelism. Therefore, programs written in these languages can be efficiently mapped to regular architectures such as GPUs and benefit from the vector processor units on modern CPUs. In addition to regular, fine-grained parallelism, FPGAs excel when applications have irregular parallelism and can benefit from architecture customization, such as application-specific memory or compute structures. More recently, extensions, such as OpenCL Pipes, have been proposed and they can potentially improve the suitability of these languages for developing FPGA applications [Altera Corporation, 2015]. However, such extensions also complicate the application development process since there are now many ways to write the same application, each with a different trade-off between cost and performance.

Common problem with C-like languages

HLS tools using the different variant of C-like languages can produce good results [Andrade et al., 2015, Rupnow et al., 2011, Cong et al., 2011, Chen and Singh, 2012]. However, a common problem in these approaches is that their input languages are too low-level; therefore, the user require to have a detailed knowledge of the optimization potential of the application and manually perform some optimizations, such as refactoring the program or adding compiler directives [Rupnow et al., 2011]. There are also sound arguments against using C-like languages for HLS [Edwards, 2006]. Therefore, researchers have investigated using other languages for hardware synthesis.

#### Synthesis from Other General-Purpose Programming Languages

Using other generalpurpose languages for hardware synthesis Researchers have synthesized hardware designs from other programming languages, besides the C-like languages noted above. These efforts include Kiwi [Greaves and Singh, 2008] which uses a parallel programming library to generate hardware circuits from a parallel program

in C# [Hejlsberg et al., 2003]; MyHDL [Decaluwe, 2004] that models concurrency of hardware circuits with generator functions in Python; JHDL [Bellows and Hutchings, 1998] that uses Java to model hardware circuits; and Lava [Bjesse et al., 1998] which leverages functional programming language features, such as monads and type classes, to generate hardware circuits. However, among them, MyHDL and JHDL start from a circuit-level description of the hardware design and offer only a limited productivity advantage.

#### **Synthesis from Custom Programming Languages**

Other researchers have tried to create new languages to generate hardware. Among them, BlueSpec [Nikhil, 2004] uses guarded atomic actions to express concurrent FSM and they excel in generating control dominated circuits. Chisel [Bachrach et al., 2012] was developed as a language embedded in Scala [Odersky et al., 2004] and it provides a more sophisticated language for hardware development. Both these approaches improve the designer productivity compared to using Verilog or VHDL; however, they require the designer to step down from the abstraction level of algorithms to think more in terms of the hardware design and its functioning. Lime [Auerbach et al., 2010] is a Java-based language that uses task-based data-flow programming model to target heterogeneous system that include CPUs, GPUs and FPGAs. When targeting FPGAs, the tasks in Lime becomes separate hardware circuits that are interconnected according to a task-graph.

Using custom languages for hardware synthesis

These tools improve the productivity of the designer and, in many cases, produce reasonably good results. However, the common problem with all general-purpose tools is that they lack domain-knowledge and therefore cannot perform domain-specific optimizations making it difficult to tune the generated hardware design for specific application areas. These tools, therefore, depend on the users to appropriately refine the input specifications, which requires hardware design knowledge, and guide the tool to produce better quality designs. This makes the tool less useful to application domain experts or users with a software development background.

Drawbacks

### 2.1.2 Domain-Specific High-Level Synthesis Tools

Benefits of domainspecific languages for hardware synthesis In contrast to general-purpose tools, domain-specific tools focus on specific application domains where they make hardware synthesis easier and more accessible for their users. Compared to general-purpose tools, these tools offer the following advantages:

- 1. They often use a custom DSL for input specifications. These DSLs have a syntax that makes it easier to express applications in the domain and, thereby, improves the productivity of the user.

- 2. They can leverage advanced domain-knowledge to perform optimizations and/or have custom implementations of common domain operations. This enables them to produce better quality results compared to general-purpose tools.

Tools using domainspecific languages for hardware synthesis These include tools such as PARO [Hannig et al., 2008] and MMAlpha [Derrien et al., 2008] which focus on loop transformations to implement highly parallel systems; Spiral [Milder et al., 2012] which synthesizes hardware for linear transforms in signal processing applications; Optimus [Hormati et al., 2008] which focuses on streaming applications; and HIPAcc [Reiche et al., 2014] that targets image processing applications. All these tools focus on specific application areas and use custom DSLs to elicit input specifications. Some commercial tools in this category include HDL Coder [The MathWorks, 2015] which takes Matlab program or Simulink models and generates hardware designs for them; LabView [Bishop, 2014] that provides a graphical user interface to develop designs for select application areas, such as signal processing, instrument control, embedded system monitoring and control; and SDNet [Brebner and Jiang, 2014, Xilinx, 2014] from Xilinx which focuses on networking applications.

Some efforts have also tried to use existing general-purpose programming languages to target specific application domain. These include efforts such as Gaut [Coussy et al., 2008] that takes specifications in C but performs optimizations to target signal processing, and Streams-C [Gokhale et al., 2000] which also uses C and focuses on stream processing.

Reducing the effort to develop domain-specific tools While domain-specific tools have huge potential in making FPGA more accessible to users without hardware design knowledge, the high effort required to build these tools makes this approach impractical in many

areas. In the software domain, research efforts demonstrate that language embedding and type-directed staging [Rompf and Odersky, 2012] based approaches can be used to reduce domain-specific tool development effort. These efforts include the Delite project [Lee et al., 2011, Sujeeth et al., 2014] which targets portability and high performance for applications running on heterogeneous platforms; a software-only subset of Spiral [Ofenbeck et al., 2013]; and Jet [Ackermann et al., 2012] which targets BigData computation. Inspired by these results, we investigate how similar ideas can be applied to reduce the effort needed to develop hardware synthesis tools [George et al., 2013]. Additionally, we show that developing these tools using reusable optimization modules and integrating with existing general-purpose hardware generation tools can make it significantly easier to build such domain-specific tools.

As noted above, integrating with existing general-purpose HLS tools can significantly lower the effort needed to develop new domain-specific hardware synthesis tools. But, the general-purpose HLS tools require the user to tune the input specification (e.g., by refactoring the code or supplying additional optimization directives) based on hardware design expertise to produce good quality results [Rupnow et al., 2011]. People developing domain-specific tools, however, might be domain-experts or software developers who lack hardware design skills. Therefore, to make it easier for them to create new domain-specific tools, we need to develop a hardware generation tool that does not require hardware design expertise to use and can yet produce good quality designs.

Need for developing hardware synthesis tools that do not require hardware design expertise

# **2.2** Generating Hardware Designs from Computational Patterns

#### 2.2.1 Overview of Computational Patterns

On analyzing applications from different domains, researchers have observed that they contain a few unique patterns of computation and communication. *Computational pattern* [Asanovic et al., 2006, McCool et al., 2012] are algorithmic methods that capture patterns of computation and communication. These patterns have well defined properties, such as parallelism in the operations, interdependence between elemental operations, data access patterns and data-sharing characteristics.

Understanding computational patterns

More importantly, these properties can be leveraged to efficiently map these patterns on different computational architectures, such as CMPs, GPUs, clusters and even FPGAs [Newburn et al., 2011, Sujeeth et al., 2014, Chambers et al., 2010, George et al., 2014].

### 2.2.2 Using Computational Patterns for Processor-Based Architectures

Programming processor-based architectures from computational patterns As noted above, the well defined properties of the computational patterns make it easy to optimize them and map them efficiently on a variety of different architectures. For instance, Intel's Array Building Blocks [Newburn et al., 2011] uses data-parallel patterns to generate parallel code for CMPs; Copperhead [Catanzaro et al., 2011] uses patterns to generate CUDA code from a subset of Python to target GPUs; DryadLINQ [Yu et al., 2008] takes programs in LINQ [Meijer et al., 2006] and executes them over clusters using Dryad [Isard et al., 2007]; Delite [Lee et al., 2011, Sujeeth et al., 2014] decomposes high-level DSL programs to patterns and executes them on heterogeneous machines containing CMPs and GPUs as well as on clusters; and FlumeJava [Chambers et al., 2010] from Google provides a Java library to develop applications which it decomposes into pipelines of MapReduce operations that can be executed on their MapReduce framework [Dean and Ghemawat, 2008].

These efforts demonstrate that the well understood properties offered by computational patterns can be used to generate implementations for different targets. More importantly for our purpose, as seen in the case of Delite, high-level compilers can decompose a DSL program into these computational patterns. Therefore, if we develop a toolchain to generate hardware designs from computational patterns, it can be used along with a high-level compiler to compile DSL programs into hardware designs.

#### 2.2.3 Using Computational Patterns for Hardware Synthesis

Hardware generation from computational patterns

Computational patterns have been used before in the context of hardware designs. Patterns were used to analyze the amenability of accelerating algorithms on FPGAs before implementing them manually [Nagarajan et al., 2011]. Some parallel programming models (e.g., OpenMP)

and languages (e.g., Lime) have constructs to express some patterns, such as map and reduce, to reveal the parallelism in the computation. Developing a tool to generate hardware from computational patterns has the following advantages:

- 1. The tool can leverage the well understood properties of the computational patterns to produce high-quality hardware implementations for them.

- 2. Since the computational patterns are algorithmic methods, they are easily understood by domain-experts or software developers who can use the tool to generate hardware designs. Additionally, they can also develop high-level compilers that will decompose DSL-programs into computational patterns and generate hardware designs.

In our work, we decompose high-level DSL applications into comptuational patterns and develop a toolchain to generate hardware designs from these patterns [George et al., 2014]. To generate high performance designs from this toolchain, we leverage the properties of the patterns and perform additional compiler analysis to infer optimizations and generate a well structured HLS code with all the necessary optimization directives. Our implementation uses Vivado High Level Synthesis [Xilinx, 2013a] to generate hardware modules and Vivado Design Suite [Xilinx, 2013b] to generate bitstreams for the FPGA. Since we automatically generate the input to the HLS tool from the high-level patterns, we can also reduce the syntactic variance in the generated code and, consequently, its impact on the performance of the generated design [Chaiyakul et al., 1992]. Furthermore, we integrated this toolchain with Delite [Lee et al., 2011, Sujeeth et al., 2014, an extensible compiler infrastructure that can be used to easily develop DSLs for new application domains, to compile high-level DSL programs in Delite to complete hardware systems. To generate such complete systems, our approach leverages the domainawareness provided by the DSL to select a suitable system-architecture template for the implementation.

Later, we extended this methodology to automatically generate designs that parallelize computations across multiple independent hardware modules [George et al., 2015]. This enables us to utilize the parallelism revealed by the patterns to overcome performance bottlenecks of designs that only use a single HLS-generated hardware module for each

Multi-module parallelization from computational patterns parallel operation. These include the underutilization of the available system bandwidth either due to the nature of computation in the module [Zhang et al., 2015] or due to the data access patterns when coupled with the long external memory access latency. Our approach exploits the properties of the pattern to automatically parallelize computation and uses a dynamic load-balancing strategy to leverage multiple modules to improve the performance of the application. An orthogonal approach proposed by Winterstein et al. [Winterstein et al., 2015] is to apply program analysis on the HLS code to identify non-overlapping memory regions and parallelize applications.

The multi-module parallelization can benefit applications with irregular data access patterns. Therefore, there have been efforts to develop specialized HLS tools that use techinques such as deep pipelining [Halstead and Najjar, 2013] and context switching [Tan et al., 2014] to improve the performance of such applications. These techniques are also orthogonal to our approach and can be used in conjunction with our work.

Other hardware generation efforts from computational patterns Subsequently, Prabakar et al. [Prabhakar et al., 2015] proposed using tiling and metapipelining optimizations to improve the quality of the designs generated from computational patterns; they used Delite as the front-end and Maxeler's MaxCompiler [Maxeler Technologies, 2011] to generate hardware designs. Ma et al. [Ma et al., 2015] have shown that by decomposing high-level applications into a library of patterns, they can utilize the dynamic reconfiguration ability of FPGAs to enable runtime interpretation of application programs. These efforts reiterate the benefit of generating hardware designs from computational patterns.

### 3 Making Domain-Specific Hardware Synthesis Tools Cost-Efficient

High-level synthesis tools can enhance productivity of FPGA application developers. Among them, tools such as Spiral [Milder et al., 2012], HDL Coder [The MathWorks, 2015], Optimus [Hormati et al., 2008], and MMAlpha [Derrien et al., 2008] target specific application domains in which they make designing hardware even more convenient and accessible to their users. To achieve this, they utilize a high-level Domain-Specific Language (DSL) for the input specifications, such as SPL for Spiral, Matlab/Simulink design for HDL Coder, StreamIt for Optimus and Alpha for MMAlpha, which is more natural to express the applications they target. Additionally, many of these tools also leverage domain knowledge to optimize the hardware designs and deliver better design quality compared to general-purpose tools. A simple tool for synthesizing matrix expressions into hardware circuits can help us to understand these advantages: Firstly, using a DSL that uses concepts like matrices and operations on matrices makes expressing the input design easy, especially for domain-experts. Secondly, since the tool knows that the input is a matrix expression, it can automatically choose ideal data storage formats and operator implementations to ensure higher quality results compared to general-purpose tools. Lastly, the tool can exploit its domain awareness, e.g., knowledge of the rules of matrix algebra, to optimize the design and produce even better results.

Advantages of domain-specific tools

#### 3.1 Motivation

Developing a new domain-specific HLS tool is a significant investment since it may involve designing an entirely new DSL, compiler and ap-

Build domain-specific tools with low effort

plication development environment, such as IDE and debugging tools; developing just the compiler would comprise writing a parser, multiple analysis and optimization phases and output code generators. This large development effort and, consequently, high cost limits the viability of developing new domain-specific HLS tools for new application domains. However, techniques such as language embedding [Mernik et al., 2005] and type-directed staging [Carette et al., 2009] can considerably reduce this development effort. In this chapter, we explore the feasibility of using these techniques to develop domain-specific synthesis tools; we embed the new DSL in Scala [Odersky et al., 2004] and utilize the *Lightweight Modular Staging* (LMS) [Rompf and Odersky, 2012] infrastructure for developing the compiler.

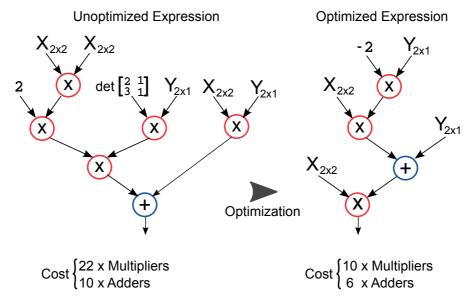

Case study: hardware synthesize from matrix expressions As an illustration of this approach, we create an HLS flow to synthesize matrix expressions into hardware designs. This flow is composed of two optimization modules, one performing optimizations at the matrix-level and the other at the level of matrix elements (scalar-level). Using this flow, we demonstrate the flexibility of the approach by showing how we can easily reuse the optimization modules and by integrating it with external tools like LegUp [Canis et al., 2011], a C-to-RTL compiler, and FloPoCo [De Dinechin and Pasca, 2011], an arithmetic core generator. While we present the concepts using a specific HLS flow, they are indeed quite general and can be used to create domain-specific toolchains and/or to augment existing tool-chains with domain-specific optimizations with a very reasonable development effort.

Chapter outline

The remainder of this chapter is organized as follows. Section 3.2 describes our modular design approach and Section 3.3 provides a brief introduction to LMS and our hardware design generation work-flow. In Section 3.4, we detail the development of the optimization modules. We evaluate our approach in Section 3.5 using a case study of implementing multiple matrix expressions in hardware. The results show that we can leverage high-level optimizations to considerably reduce the implementation area without significant performance loss. We then summarize our findings in Section 3.6.

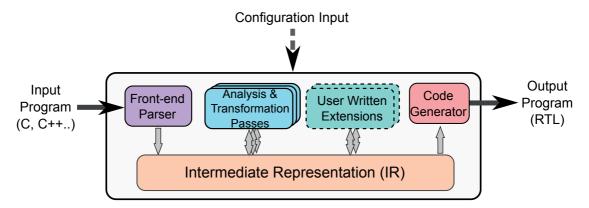

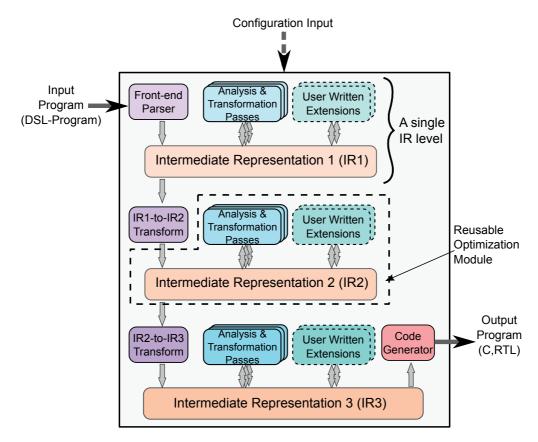

**Figure 3.1:** HLS Tool Design Using Traditional Compiler Frameworks. Typical HLS tools use traditional compiler frameworks like LLVM or GCC which have use one or more low-level IR-formats.

## 3.2 Compiler Frameworks for Domain-Specific Hardware Synthesis

In this section, we discuss the advantages of LMS over popular opensource compiler frameworks, such as LLVM [Lattner and Adve, 2004] and GCC [Stallman et al., 2015], as a common platform for implementing multiple domain-specific synthesis tools.

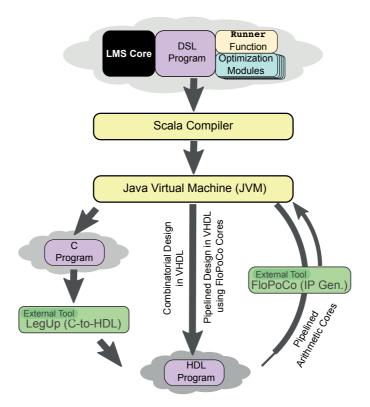

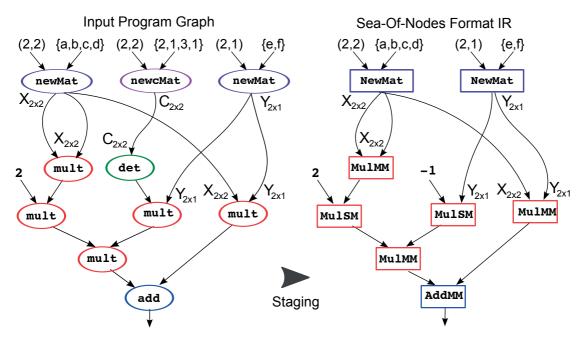

Open-source compiler frameworks like LLVM and GCC have been used to build HLS tools like Vivado HLS [Xilinx, 2013a], OpenCL to FPGA [Czajkowski et al., 2012], LegUp [Canis et al., 2011] and Trident [Tripp et al., 2007]. In these HLS tools, as shown in Figure 3.1, the input program is translated into an *Intermediate Representation* (IR) format by the frontend parser. Various analysis and transformation passes then optimize this IR, maintaining its original format, until the code generator finally uses it to produce the output RTL code. While HLS tool designers often extend the framework by adding additional front-end parsers, analysis and transformation passes, and code generators, they usually use the same low-level IR-format<sup>1</sup> used by the framework since changing it is not easy. By retaining the IR-format, they can reuse some of the standard optimizations that are already available in the framework, but it also introduces limitations.

Overview of traditional compiler frameworks

<sup>&</sup>lt;sup>1</sup>GCC does have multiple IR-formats, but they are all at a low-level; therefore, these multiple IR-formats offer no benefit when performing high-level domain-specific optimizations.

**Figure 3.2:** HLS Tool Design Using Our Approach. In contrast to Figure 3.1, we propose using an architecture based on multiple IR-formats at different levels of abstraction, each used by a unique optimization module, to enable a more efficient hardware synthesis.

Traditional compiler frameworks are unfit for domainspecific tools For instance, many domain-specific tools, like Spiral [Milder et al., 2012] and MMAlpha [Derrien et al., 2008], use multiple IR-formats to perform high-level, domain-specific optimizations at different levels of abstraction. One way to achieve this with a single IR is to perform the high-level, domain-specific optimizations directly at the front-end parser, before the low-level IR is generated. But, these optimizations are now tied to the specific IR used by the developer and, consequently, cannot be reused in a different HLS flow if the IR changes. An alternative is to perform the high-level optimizations using a sequence of optimizations on the low-level IR. But, this can be extremely difficult due to the low-level nature of the IR; for instance, performing simple optimizations using rules of matrix algebra is quite easy when the IR represents operations on matrices, but it becomes hard or just not feasible when the higher-

level information is lost. Furthermore, with a single IR-format, there can also be complex interactions between the different optimization steps, making it harder to add new optimizations or reuse the existing ones selectively for an entirely new flow.

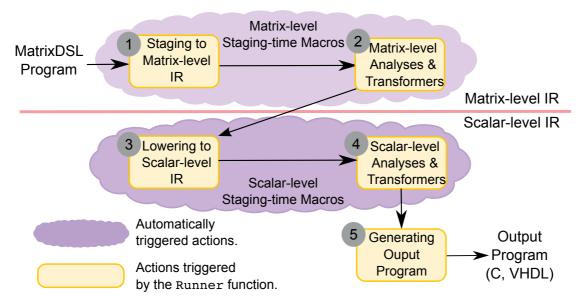

In our approach, we use the extensible LMS compiler framework to define multiple IR-formats, as shown in Figure 3.2, that are often at different levels of abstraction. We create separate standalone *optimization* modules for each unique IR-format. The components of an optimization module include multiple analysis and transformation passes; an optional lightweight, front-end parser for the input DSL; and optional code-generators for the different output formats. Since all these components operate only on the unique IR-format used in the module, we can more easily avoid the possibility of optimizations in different modules affecting each other; this makes it easier to make changes or add/remove optimizations. Additionally, as shown in the figure, we can develop complex HLS flows by connecting multiple optimization modules to each other using a special variant of a transformation pass called IR-to-IR transform [Rompf et al., 2013]. Often, the IR-formats are common across different HLS flows, enabling a natural reuse of optimization modules.

Proposed approach

In the software domain, the Delite project [Lee et al., 2011] employs a similar strategy to target code-generation for multi-core CPUs and GPUs starting from a high-level DSL. In this work, however, we demonstrate that a similar approach can dramatically lower the cost for developing domain-specific HLS flows to achieve efficient hardware generation. In particular, we show that this method of building domain-specific flows fits naturally into the current EDA ecosystem by enabling an easy integration of existing IP-cores and the extension of mature HLS flows by providing domain-specific optimizations.

Contrast with other efforts

Using the proposed approach, we can easily develop domain-specific hardware synthesis tools like Spiral or MMAlpha by creating different optimization modules for each level of abstraction at which we want to apply optimizations. To serve as an example and illustrate this point, we use a simple tool to synthesize matrix expressions into efficient hardware. We implement this flow using two optimization modules, one for performing optimizations at the matrix-level and the other for applying optimizations at the scalar-level. As done in many domain-specific

Case study to demonstrate the benefits of the approach

tools, we also create a simple DSL to the make it easy for the end-user to express design specifications. Our matrix-level optimization module uses an IR that represents computation on matrices (i.e., a matrix-level IR) to reorder multiplications, apply the distributive property, and eliminate common subexpressions at the matrix-level. After that we use an IR-to-IR transform to decompose this matrix-level IR into a scalar-level one that represents operations on individual matrix elements. We then perform standard scalar-level optimizations, such as strength reduction and common subexpression elimination, as done in many HLS tools, before generating the output design. Although this is only a well understood example, it is general enough to show the potential of the proposed methodology.

#### 3.3 Hardware Synthesis Using Scala and LMS

In this section, we first introduce the LMS framework and discuss how we use it to efficiently implement the optimization modules. We then describe our LMS-based workflow for hardware synthesis.

#### 3.3.1 Overview of Scala and LMS

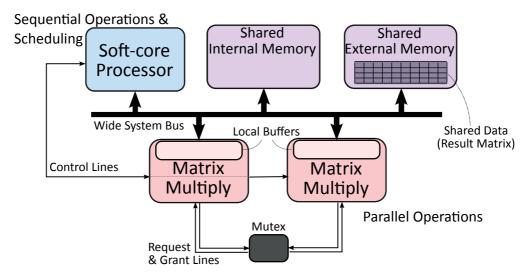

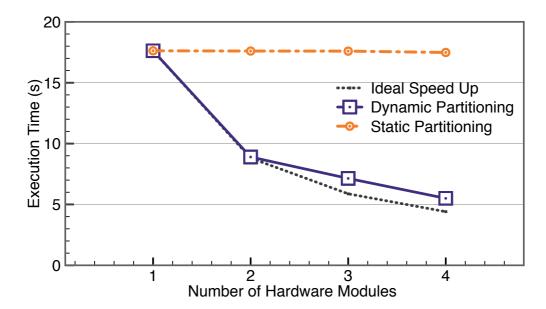

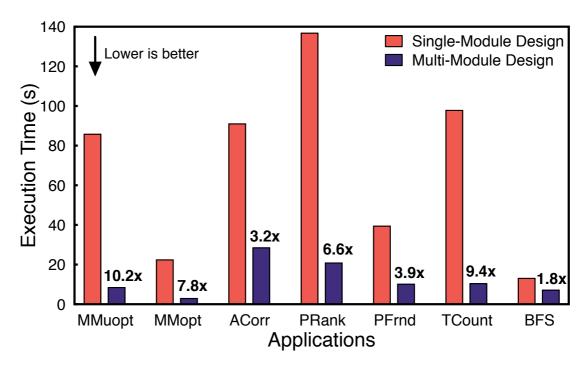

Creating a DSL and custom compiler