Received 24 June 2015; revised 26 August 2015; accepted 16 September 2015. Date of publication 25 September 2015; date of current version 26 October 2015. The review of this paper was arranged by Editor E. Sangiorgi.

Digital Object Identifier 10.1109/JEDS.2015.2482123

# On Temperature Dependency of Steep Subthreshold Slope in Dual-Independent-Gate FinFET

## JIAN ZHANG<sup>1</sup> (Student Member, IEEE), JENS TROMMER<sup>2</sup> (Student Member, IEEE), WALTER MICHAEL WEBER<sup>2</sup>, PIERRE-EMMANUEL GAILLARDON<sup>1</sup> (Member, IEEE), AND GIOVANNI DE MICHELI<sup>1</sup> (Fellow, IEEE)

Integrated Systems Laboratory, École Polytechnique Fédérale de Lausanne, Lausanne 1015, Switzerland

NaMLab gGmbH and Center for Advancing Electronics Dresden, Technische Universität Dresden, Dresden 01187, Germany CORRESPONDING AUTHOR: J. ZHANG (e-mail: jian.zhang@epfl.ch)

This work was supported by the European Research Council under Grant ERC-2009-AdG-246810.

**ABSTRACT** Dual-independent-gate silicon FinFET has demonstrated a steep subthreshold slope (SS) when a positive feedback induced by weak impact ionization is triggered. In this paper, we study the temperature dependency of the steep SS by characterizing the fabricated device from 100 to 380 K. The measured characteristics of SS show a reduced sensitivity to temperature as compared to conventional MOSFETs. Based on the temperature-dependent characterization, we further analyze the steep-SS characteristics and propose feasible improvements for optimizing the device performance.

**INDEX TERMS** FinFET, Schottky barrier, steep subthreshold slope, impact ionization, feedback.

#### I. INTRODUCTION

Lowering the supply voltage is considered as an efficient way to reduce the power consumption of integrated circuits. In this context, transistors with a steep Subthreshold Slope (SS) are expected to maintain good switching properties at very low operation voltage.

In order to break the fundamental limit of the SS in conventional MOSFETs, devices based on different mechanisms are proposed, such as Tunnel FET, IMOS, and NEMFET [1]–[3]. In addition, a class of devices also achieves a super-steep SS (<10 mV/dec) by introducing a positive feedback induced by weak impact ionization. This steep-SS behavior has been demonstrated with various device structures, including partially-depleted SOI MOSFET [4], fully-depleted SOI MOSFET [5], [6], junctionless transistor [7] and Dual-Independent-Gate (DIG) FinFET [8]. We refer to such a class of devices with Super-Steep Subthreshold Slope, as S4-FETs. The S4-FETs demonstrate greatly improved SS over the subthreshold region with good reliability, as well as low leakage and high  $I_{on}/I_{off}$  ratio, showing their potential for low-power applications. In this paper, we study the subthreshold characteristics of the S4-FETs, by performing temperature-dependent characterization on DIG FinFET from 100 K to 380 K. It is observed that the SS shows less sensitivity to temperature than conventional MOSFETs. We also perform an analysis on the SS based on the temperature-dependent characterization. According to the analysis, we suggest that, in addition to enhancing the impact ionization, a better control of the Schottky-barrier bias region and the leakage reduction can further optimize the SS and reduce the required drain bias.

#### **II. DEVICE OVERVIEW**

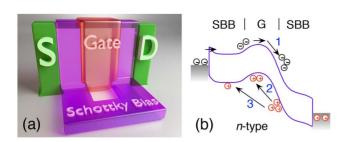

Fig. 1(a) shows the structure of a DIG FinFET. The device exploits a fin-shaped channel with metallic source and drain contacts. The channel electrostatics is controlled by two electrodes: The Schottky-Barrier Bias (SBB) electrostatically modulates the Schottky barriers at source and drain; The Gate (G) controls the potential barrier in the channel to turn the device *on* or *off.* Note that, thanks to its control on the Schottky-barrier injection, the SBB has the capability to

**FIGURE 1.** (a) Conceptual sketch of a DIG FinFET with steep SS. (b) Mechanism of the impact ionization induced positive feedback during transition in *n*-type configuration [8].

determine the polarity of the device by favoring either the conduction of electrons or holes [9].

The DIG FinFET is fabricated with a dopant-free process on a lightly *p*-type doped ( $\sim 10^{15}/cm^3$ ) SOI wafer [8]. The height and the thickness of the fin are 340 nm and 40 nm, respectively. Thus, the fin-shaped channel is fully depleted considering the low doping concentration and the thin thickness. The length of the gate and each SBB region are 200 nm with 15 nm SiO<sub>2</sub> as gate dielectric. Nickel silicide is used to form near-midgap Schottky barriers at source and drain. The large dimensions of the device are used in order to increase the yield in our academic cleanroom environment. However, no physical limitations preclude the use of more aggressive dimensions. In the meantime, the thick gate oxide can also enhance the steep SS as discussed in Section IV.

The steep-SS operation in *n*-type configuration is illustrated in Fig. 1(b). When  $V_{\text{SBB}} > 0$ , electrons are selected to tunnel through the Schottky barrier into the channel. When acquiring enough energy, the electrons can cause weak impact ionization, and electron/hole pairs are generated (step 1). The generated holes accumulate in the potential well under the gate (step 2). This lowers the barrier and provides more electrons for impact ionization, thus forming a positive feedback [5]. In addition to the FinFET structure enhancing carrier multiplication [2], a dynamic modulation of the Schottky barrier also contributes to the steep SS. During the transition, the energy band in the SBB region is lowered by the increased quasi-Fermi potential and the generated holes (step 3). This helps to maintain the potential well for the accumulation, thus improving the average SS over the subthreshold region. The operation of *p*-type configuration is similar but with  $V_{\text{SBB}} < 0$ . Note that, the weak impact ionization only occurs during the transition and vanishes when the device completely turns on, leading to a good reliability of the S4-FETs [5], [8].

#### **III. TEMPERATURE-DEPENDENT CHARACTERIZATION**

In this section, we present the temperature-dependent characterization of the DIG FinFET.

The device characteristics at room temperature are shown in [8]. It demonstrates an average SS of 6 mV/dec over 5 decades of drain current, as well as  $I_{on}/I_{off}$  ratio of 10<sup>7</sup>.

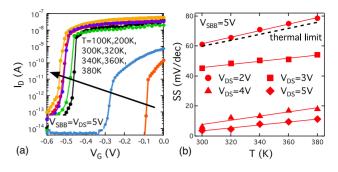

The *n*-type characteristics at different temperatures are shown in Fig. 2(a). The steep SS is observed from 100 K

FIGURE 2. (a) *n*-type characteristics with steep SS at different temperatures, (b) Minimal SS at different temperatures and V<sub>DS</sub>.

to 380 K without significant degradation. The minimal SS values obtained for different  $V_{\text{DS}}$  and temperature conditions are reported in Fig. 2(b). The results show that the SS can be significantly improved by increasing  $V_{\text{DS}}$ . When  $V_{\text{DS}} \ge 3V$ , the device shows a SS well below thermal limit from 300 K to 380 K. In contrast to the normal-SS operation ( $V_{\text{DS}} = 2V$ ), the lines with  $V_{\text{DS}} \ge 3V$  in Fig. 2(b) shows smaller slope, which indicates a reduced sensitivity to temperature.

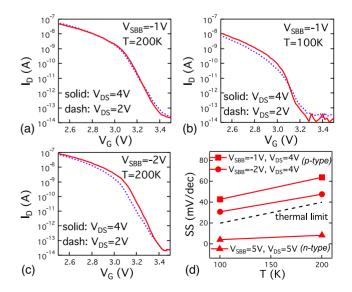

Compared to the steep SS in *n*-type characteristics, the *p*-type behavior of the device at room temperature is similar to normal MOSFETs [8]. The weaker impact ionization in *p*-type characteristics than in *n*-type operation is considered as due to the lower impact ionization rate of holes than electrons, which is caused by a much larger phonon scattering rate of holes than electrons [10], [11]. Since the ionization rate decreases with higher temperature, the high-temperature *p*-type characteristics are also similar to normal MOSFETs. In contrast, the low-temperature results of *p*-type operation are in the most concerned and physical relevant regime. Therefore, we try to also observe the impact ionization induced SS improvement in *p*-type configuration by lowering the temperature. As shown in Fig. 3(a), there is nearly

**FIGURE 3.** (a)–(c) *p*-type characteristics with different  $V_{SBB}$  and  $V_{DS}$  at 100 K and 200 K. (d) SS of *n*-type and *p*-type configurations at low temperatures.

no improvement of SS by increasing  $V_{\text{DS}}$  with  $V_{\text{SBB}} = -1V$ at 200 K. However, by further lowering the temperature to 100 K [Fig. 3(b)] or increasing  $V_{\text{SBB}}$  to -2V [Fig. 3(c)], the  $V_{\text{DS}}$ -dependent SS becomes evident, according to the enhancement of ionization with lower temperature and/or higher electric field. Fig. 3(d) summarizes the SS under low temperatures and different  $V_{\text{SBB}}$  conditions for both *n*-type and *p*-type operations. The steep SS in *n*-type behavior at low temperatures keeps the reduced sensitivity to temperature similar to the high-temperature range. For *p*-type operation, although still above the thermal limit, the SS becomes less sensitive to temperature when  $V_{\text{SBB}} = -2V$ , similarly to the *n*-type behavior.

### IV. DISCUSSIONS ON THE STEEP-SUBTHRESHOLD-SLOPE CHARACTERISTICS

In this section, we analyze the steep-SS behavior and formulate its expressions. Our study builds on the results obtained for SOI-based S4-FET [4]. Similarly to the SOI-based device, the expression of SS in DIG FinFET is derived as:

ŀΤ

$$SS = -\frac{1}{q}\ln 10 \cdot n$$

(1)

where

$$n = \frac{1+r}{1+r\frac{dV_{BS}}{dV_{CS}}}$$

and  $r = \frac{2\varepsilon_{si}t_{ox}}{\varepsilon_{ox}t_{si}}$

In the DIG FinFET,  $V_B$  is the potential at the middle point between the two sidewalls of the fin in the gate-controlled region, and  $V_{BS}$  is the difference between  $V_B$  and the voltage at source. In contrast,  $V_B$  in the SOI-based device stands for the potential at the bottom of the silicon channel [4]. Although the position of  $V_B$  used in this work is different than in [4], they both represent the locations where the accumulated charges are stored, thus having similar effects on the steep-SS operation. The DIG FinFET structure also excludes the influence on the SS from a back bias applied through the SOI wafer. It has been validated on the device by varying the back bias from -4V to +4V. As a result, a consistent subthreshold behavior, i.e., the same SS and  $V_T$ , is observed under different back biases (data no shown).

Eq. (1) shows that when  $dV_{BS}/dV_{GS} < 1$ , a small *r* will lead to a SS approaching the thermal limit. This explains why scaling conventional MOSFET efforts tend to thin the gate oxide. However, when the carriers generated by impact ionization charge the body, it is possible to have  $dV_{BS}/dV_{GS} > 1$ . In this case, a large *r* (i.e., thick oxide) can magnify the feedback and further reduce the SS. Therefore, in this kind of steep-SS devices, the scaling down of  $t_{ox}$  can be relaxed.

In the presented *n*-type characteristics of the DIG FinFET, the SS below thermal limit indicates that  $dV_{BS}/dV_{GS} > 1$ . In contrast, the SS of the *p*-type characteristics is beyond the thermal limit with  $dV_{BS}/dV_{GS} < 1$ . Nevertheless, the improvement of SS with increased  $V_{SBB}$  and  $V_{DS}$  implies that a SS below thermal limit may be also achieved in *p*-type operation by further optimizing  $dV_{BS}/dV_{GS}$ .

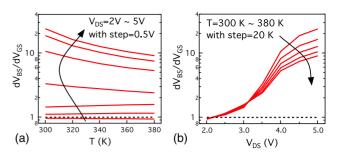

**FIGURE 4.** Extracted  $dV_{BS}/dV_{CS}$  from the *n*-type characteristics at different temperatures and  $V_{DS}$ .

To better understand the operation, Fig. 4 shows  $dV_{BS}/dV_{GS}$  extracted from the *n*-type characteristics according to (1). When  $V_{DS} \ge 2.5V$ ,  $dV_{BS}/dV_{GS}$  starts to be larger than one. When  $V_{DS} \ge 3.5V$ , it is observed that  $dV_{BS}/dV_{GS}$  significantly decreases with higher temperature. In addition,  $dV_{BS}/dV_{GS}$  also increases with larger  $V_{DS}$ .

An expression is then derived to describe the temperaturedependent behavior of  $dV_{BS}/dV_{GS}$ . By extending the analysis on SOI-based device to DIG FinFET [4], we obtain the expression for *n*-type operation as:

$$\frac{\mathrm{d}V_{\mathrm{BS}}}{\mathrm{d}V_{\mathrm{GS}}} \simeq \frac{m}{n} \cdot \frac{1}{1 + I_{gt}/I_{gi}} \\ \propto \frac{m}{n} \exp\left[\frac{q}{kT} \left(\frac{V_{\mathrm{GS}}}{n} - \frac{V_{\mathrm{B}} - V_{\mathrm{B},\mathrm{SBBs}}}{m}\right)\right] \\ \cdot \exp\left(-\frac{\beta_{i}l}{V_{\mathrm{DS}}}\right)$$

(2)

where  $I_{gt}$  is the *off*-state leakage current and  $I_{gi}$  is the impactionization current [4].  $\beta_i$  is a constant and l is a structural parameter. *m* is the ideality factor of the junction between the gated region and the region controlled by the SBB at source (SBBs). Eq. (2) well captures the dependency of  $dV_{BS}/dV_{GS}$  on temperature and drain bias in Fig. 4.

We also notice a significant difference in (2) compared to the SOI-based devices: the centric potential at the SBBs region ( $V_{B,SBBs}$ ) replaces the  $V_S$  in [4]. Compared to the fixed  $V_S$ ,  $V_{B,SBBs}$  continuously increases during the transition thanks to the increase of quasi-Fermi potential and the effects of the holes generated by the impact ionization. Thus, the improved  $dV_{BS}/dV_{GS}$  during the transition can support a better SS over the subthreshold region. As experimentally demonstrated in [8], the DIG FinFET has much better SS compared to the similar device but without the SBB region at source. This proves the importance of the Gate-SBBs junction in the feedback operation. A better control on the SBB region, such as tuning the oxide thickness and the fin width at the SBB region, can thus further optimize the device performance.

Eq. (2) also suggests that lower leakage current  $I_{gt}$  helps to improve the SS. With a very small  $I_{gt}$ ,  $dV_{BS}/dV_{GS} > 1$  may be triggered by a very small impact-ionization current  $I_{gi}$ , and hence, by a low  $V_{DS}$ . Therefore, a gate-all-around nanowire structure may be applicable for future improvements.

Through the study on the temperature dependency of the steep SS, the operation of the device is better understood, and we suggest feasible improvements on the device performance based on the study.

First, the device performance can be improved by applying an optimized process with scaled dimensions and technology boosters, such as strain technology for enhancing the carrier mobility and tuning ionization rates. As a Schottky-barrier device, the drive current is limited by the Schottky-Barrier Height (SBH). Thus, a reduced SBH for electrons improves the drive current of *n*-type configuration. Furthermore, a channel material with smaller bandgap can be used to form lower SBH for both electrons and holes, thus improving the drive currents for both *n*-type and *p*-type configurations [12].

Towards low-power applications, the steep-SS devices are desired to operate with a sufficiently low  $V_{\text{DS}}$ . The strategy to reduce  $V_{\text{DS}}$  for DIG FinFETs is consequently discussed as follows.

First, as demonstrated in [5], a similar steep-SS operation is achieved in a 25 nm SOI device with  $V_{\text{DS}} = 1.2V$ . With the additional aid of the DIG structure, the dynamic modulation of Schottky barriers can further improve the steep SS. Therefore, the DIG FinFET with deeply scaled dimensions and optimized source/drain resistance may require a  $V_{\text{DS}} \leq 1.2V$ , which is close to the threshold energy to trigger impact ionization in silicon as the bandgap of silicon is ~1.12 eV at 300 K.

On the other hand, as discussed above, the steep SS indeed depends on the ratio between the impact-ionization generation and the recombination. Although with fewer generation, the impact ionization can still occur with a sub-bandgap drain bias [13]. Thus, a steep SS below thermal limit is still conceivable with a sub-bandgap drain bias if the feedback is optimized with the improvements for leakage reduction, such as applying a nanowire structure.

In addition, the threshold energy to trigger impact ionization decreases with the decreasing bandgap of the material [10]. Thus, the required  $V_{\rm DS}$  can also be reduced by replacing silicon with other materials with smaller bandgap or higher impact ionization rate, which is consistent with the suggestion for improving the drive current. For instance, the bandgap of germanium is ~0.66 eV at 300 K, giving enhanced ionization rates for both electrons and holes [10]. In this respect, the inherent suppression of *off*-currents in the DIG-FET approach allows to keep  $I_{gt}$  sufficiently low as a further requirement for obtaining steep slopes in (2). Thus, the steep SS can be expected in germanium-based devices with a  $V_{\rm DS}$  below 1 V for both *n*-type and *p*-type conductions.

#### **V. CONCLUSION**

We investigated the temperature dependency of the subthreshold slope in the DIG FinFET through characterization of *n*-type and *p*-type operation from 100 K to 380 K. The steep subthreshold slope shows reduced sensitivity to temperature as compared to conventional MOSFETs. Based on the characterization, we analyzed the epitomized subthreshold slope in the formula and suggested that an improved control on the Schottky-barrier bias region and a reduction of the leakage current can further optimize the device performance.

#### REFERENCES

- K. Tomioka, M. Yoshinura, E. Nakai, F. Ishizaka, and T. Fukui, "Integration of III-V nanowires on Si: From high-performance vertical FET to steep-slope switch," in *IEDM Tech. Dig.*, Washington, DC, USA, 2013, pp. 4.1.1–4.1.4.

- [2] E.-H. Toh *et al.*, "Impact ionization nanowire transistor with multiple-gates, silicon-germanium impact ionization region, and sub-5 mV/decade subthreshold swing," in *IEDM Tech. Dig.*, Washington, DC, USA, 2007, pp. 195–198.

- [3] H. Kam, D. T. Lee, R. T. Howe, and T.-J. King, "A new nano-electromechanical field effect transistor (NEMFET) design for low-power electronics," in *IEDM Tech. Dig.*, Washington, DC, USA, 2005, pp. 463–466.

- [4] J. G. Fossum, R. Sundaresan, and M. Matloubian, "Anomalous subthreshold current—Voltage characteristics of n-channel SOI MOSFET's," *IEEE Electron Device Lett.*, vol. 8, no. 11, pp. 544–546, Nov. 1987.

- [5] Z. Lu et al., "Realizing super-steep subtreshold slope with conventional FDSOI CMOS at low-bias voltages," in *IEDM Tech. Dig.*, San Francisco, CA, USA, 2010, pp. 16.6.1–16.6.3.

- [6] J. G. Fossum and Z. Lu, "Anomalous floating-body effects in SOI MOSFETs: Low-voltage CMOS?" in *Proc. IEEE SOI Conf.*, Tempe, AZ, USA, 2011, pp. 1–2.

- [7] C.-W. Lee *et al.*, "Low subthreshold slope in junctionless multigate transistors," *Appl. Phys. Lett.*, vol. 96, no. 10, 2010, Art. ID 102106.

- [8] J. Zhang, M. De Marchi, P.-E. Gaillardon, and G. De Micheli, "A Schottky-barrier silicon FinFET with 6.0 mV/dec subthreshold slope over 5 decades of current," in *IEDM Tech. Dig.*, San Francisco, CA, USA, 2014, pp. 13.4.1–13.4.4.

- [9] M. De Marchi *et al.*, "Polarity control in double-gate, gate-allaround vertically stacked silicon nanowire FETs," in *IEDM Tech. Dig.*, San Francisco, CA, USA, 2012, pp. 8.4.1–8.4.4.

- [10] S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, 3rd ed. Hoboken, NJ, USA: Wiley, 2007.

- [11] V. M. Robbins, T. Wang, K. F. Brennan, K. Hess, and G. E. Stillman, "Electron and hole impact ionization coefficients in (100) and in (111) Si," J. Appl. Phys., vol. 58, no. 12, pp. 4614–4617, 1985.

- [12] J. Trommer *et al.*, "Material prospects of reconfigurable transistor (RFETs)—From silicon to germanium nanowires," in *Proc. MRS*, vol. 1659. pp. 225–230, 2014.

- [13] P. Su, K.-I. Goto, T. Sugii, and C. Hu, "A thermal activation view of low voltage impact ionization in MOSFETs," *IEEE Electron Device Lett.*, vol. 23, no. 9, pp. 550–552, Sep. 2002.

**JIAN ZHANG** (S'13) received the B.S. degree in microelectronics and the M.S. degree in microelectronics and solid-state electronics from Peking University, Beijing, China, in 2008 and 2011, respectively. He is currently pursuing the Ph.D. degree with the Integrated Systems Laboratory, École Polytechnique Fédérale de Lausanne, Lausanne, Switzerland. His current research interests include the microfabrication, modeling and simulation, and circuit implementation of emerging devices.

JENS TROMMER received the Dipl.-Ing. degree in electronic and sensor materials from TU Bergakademie Freiberg, Freiberg, Germany, in 2011. He is currently pursuing the Ph.D. degree with NaMlab gGmbH, Dresden, Germany. His current research interests include focused on material and circuit development for reconfigurable nanowire devices and electrical characterization.

**WALTER MICHAEL WEBER** received the Ph.D. degree from the Department of Materials Research, Infineon and Qimonda, Neubiberg, Germany, from 2004 to 2008, and the Ph.D. in electrical engineering from the University of Technology Munich, Munich, Germany, in 2008. Since 2008, he has been a Senior Scientist with Namlab gGmbH, Dresden, Germany, leading activities on Beyond-Moore emerging devices and circuits as well as batteries. Since 2013, he has been a Research Group Leader with the Center for

Advancing Electronics, TU Dresden, Dresden. His current research interests include synthesis of nanowires heterostructures and the conception of novel nanowire-based transistors with programmable polarity.

**PIERRE-EMMANUEL GAILLARDON** (S'10–M'11) received the B.Sc. degree from CPE-Lyon, Villeurbanne, France, in 2008, the M.Sc. degree from INSA Lyon, Villeurbanne, in 2008, and the Ph.D. degree from CEA-LETI, Grenoble, France, and the University of Lyon, Lyon, France, in 2011, all in electrical engineering. He is a Research Associate with the Laboratory of Integrated Systems, École Polytechnique Fédérale de Lausanne, Lausanne, Switzerland. He was a Research Assistant with CEA-LETI, Grenoble,

France, and a Visiting Research Associate with Stanford University, Palo Alto, CA, USA. His current research interests include the development of reconfigurable logic architectures and circuits exploiting emerging device technologies and novel EDA techniques. Starting from 2016, he will assume an Assistant Professor position within the Department of Electrical and Computer Engineering, The University of Utah, Salt Lake City, UT, USA. Dr. Gaillardon was a recipient of the C-Innov 2011 Best Thesis Award and the Nanoarch 2012 Best Paper Award. He is an Associate Editor of the IEEE TRANSACTIONS ON NANOTECHNOLOGY. He has been serving as TPC member for many conferences, including DATE'15-16, VLSI-SoC'15, CMOS-ETR'13-15, Nanoarch'12-15, and ISVLSI'14-15 conferences, and is a Reviewer for several journals and funding agencies.

**GIOVANNI DE MICHELI** (F'94) is Professor and Director of the Institute of Electrical Engineering and of the Integrated Systems Centre at École Polytechnique Fédérale de Lausanne, Lausanne, Switzerland. He is Program Leader of the Nano-Tera.ch program. His current research interests include several aspects of design technologies for integrated circuits and systems, such as synthesis for emerging technologies, networks on chips, 3-D integration, heterogeneous platform design including electrical components and biosensors, as well

as in data processing of biomedical information. He has authored *Synthesis and Optimization of Digital Circuits* (McGraw-Hill, 1994), co-authored and/or co-editored eight other books and over 600 technical articles. His citation h-index is 85 according to Google Scholar.

Prof. De Micheli was a recipient of the 2012 IEEE/CAS Mac Van Valkenburg Award for contributions to theory, practice, and experimentation in design methods and tools and the 2003 IEEE Emanuel Piore Award for contributions to computer-aided synthesis of digital systems. He has been serving as Division 1 Director from 2008 to 2009, the Co-Founder and the President Elect of the IEEE Council on EDA from 2005 to 2007, the President of the IEEE CAS Society in 2003, the Editor-in-Chief of the IEEE TRANSACTIONS ON CAD/ICAS from 1997 to 2001. He has been the Chair of several conferences. He is a member of IMEC (Leuven, B), CfAED (Dresden, D), and STMicroelectronics. He is a fellow of the Association for Computing Machinery.