### Memory Systems and Interconnects for Scale-Out Servers

#### THÈSE N° 6682 (2015)

PRÉSENTÉE LE 18 SEPTEMBRE 2015

À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS LABORATOIRE D'ARCHITECTURE DE SYSTÈMES PARALLÈLES PROGRAMME DOCTORAL EN INFORMATIQUE ET COMMUNICATIONS

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Stavros VOLOS

acceptée sur proposition du jury:

Prof. W. Zwaenepoel, président du jury Prof. B. Falsafi, directeur de thèse Prof. R. Balasubramonian, rapporteur Prof. Y. Xie, rapporteur Prof. P. Ienne, rapporteur

## Acknowledgments

My PhD journey would have not been memorable, joyful, and successful if not for the support and friendship of many people. The credit which needs to be given to these people is massive; so, this section will be a bit long.

First and foremost, I would like to thank my academic advisor, Babak Falsafi, for providing me with the opportunity for pursuing a PhD under his supervision. His financial support throughout my studies allowed me to focus on developing my teaching, research, presentation, and writing skills. Pursuing a PhD under Babak's supervision goes beyond academic horizons and feels more like a one-time life experience. Babak's persistence and will to aim always for perfection were two of his characteristics that brought the best out in me. His quotes "Just make it perfect. How hard is it?" and "It will make you a better person" had constantly been inspiring me and guiding me through the long PhD journey. Babak has been a great teacher in and out of the office. His teaching methods might be a bit harsh, but they have been really successful. Babak taught me how to see the big picture, to methodically identify and scientifically solve a research problem, and finally how to talk and write about it. Babak's input was instrumental in understanding how humanity really works, and developing a mature way of thinking. Special thanks for the off-slope skiing sessions during our group's ski retreats. Thanks for helping me to become a researcher and a better person.

I would like to thank Rajeev Balasubramonian, Paolo Ienne, and Yuan Xie for serving as my thesis committee, and for their time and insightful comments and feedback. I wish to thank Willy Zwaenepoel for serving as the jury president of my thesis exam.

I had the fortune to work in a great and fun research group, Parallel Systems Architecture Lab (PARSA), surrounded by amazing people whose assistance, feedback, and support helped me become a researcher while their friendship improved me as a person and guaranteed a memorable PhD journey:

- Cansu Kaynak, Djordje Jevdjic, and Onur Kocberber have been great academic siblings and friends. We enrolled to the PhD program in the same year, and as a result our PhD journeys were fully overlapped. Our relationship can be characterized in one sentence "All for one and one for all". We shared a common office for almost four years, spent unlimited amounts of time at the lab working on team projects, brainstorming, and giving each other insightful and valuable feedback. Besides being great groupmates, collaborators, and teachers, they have been great friends whose friendship kept my sanity intact, moral support helped me overcoming tough moments, and fruitful discussions enriched my knowledge. We spent a lot of time procrastinating, having fun at restaurants and bars, and traveling for conferences and ski retreats. Special tribute to Onur who had to tolerate me as an office-mate for an additional two years, as a beer-mate, and as a ski-mate in the beautiful Alps. Additional thanks to Djordje for boosting my consciousness about green computing. Dudes (and dudette), big thanks for everything. Your input played a pivotal role in ensuring a memorable and joyful PhD journey. This journey would have not been successful if not for you.

- Javier Picorel and Sotiria Fytraki have been great friends and group-mates for over five years. Together, we endured lots of tough moments and had many fun experiences. I will never forget the long psychotherapy sessions with Sotiria in the aftermath of paper rejections. Besides being a great friend, Javier also served as a trustworthy collaborator in various research projects. Javier's life- and academic-wise input was of great importance to me. We had lots of valuable discussions about problems regarding our life and research during dinners, drinking nights, and long days in the lab. I am pretty sure we helped and improved each other considerably in so many ways.

- Special thanks to Boris Grot and Mike Ferdman for everything I learned from them. Boris has been a great mentor. Through our collaboration he taught me how to think, how to write, and many other skills that were instrumental in accomplishing my academic goals. It was always a pleasure talking with him as his positive attitude always inspired me to keep trying. Mike has been a great role model and has served as a great senior student in the first three years of my PhD studies. Mike had the responsibility of enriching our technical and presentation/writing skills. Additional thanks to them for all the nice moments we spent in Lausanne, conferences, and ski retreats.

- Alexandros Daglis has been a great group-mate and friend for over three years. His feedback during paper deadlines and practice talks was valuable and insightful. He has also been a great team-mate during our football games against the Lebanese opponents. Alex has been the only person in Switzerland that understood my passion for trance music, and one of the few who shared my preference for Indian Pale Ales in our drinking and burger nights. Thanks for all the fun moments we shared in Lausanne, conferences, ski retreats, and other places in the world.

- Thanks to Alisa Yurovsky and Effi Georgala for being good friends. Alisa has made many weekend days of the PARSA members more colorful due to her amazing organization skills, including barbecues by the lake and Halloween parties. Thanks to Effi for the fun breaks in the lab, her advice about job interviews and thesis exams, and for having the patience to help me dropping a part of my Greek accent in English.

- Thanks to Adileh Almutaz and Pejman Lotfi Kamran for the fruitful collaborations in the

early stages of my PhD studies. Thanks to other members of the PARSA group Stanko

Novakovic, Georgios Psaropoulos, Nooshin Mirzadeh, Mario Drumond, and Dmitrii

Ustiugov for contributing in various ways to the completion of this thesis.

- I would like to thank Rodolphe Buret for providing technical support, Stéphanie Baillargues and Valérie Locca for providing administrative advice, and Ousmane Diallo for his advice on job finding.

Kudos to our ISOMAC coffee machine which served our lab with the finest espresso in Switzerland for over four years.

I would like to thank the Greek community for making the life in Lausanne more fun and for reminding me my Greek origins:

- Manos Athanassoulis and Yannis Alagiannis have been great friends since my first day in the PhD program. Unfortunately, the work load of the PhD program was prohibitive in some cases, causing my temporal disappearance. Among other things, Manos had been a great host for Euroleague nights; Yannis had been a great team-mate in various courses, including Advanced Algorithms, the core exam required for becoming a PhD candidate. Lots of pain and uncertainty there. Our trip to Barcelona was a memorable one after which they started calling me *Storus the Panoramicus*.

- Thanks to Evangelos Vlachos, Aris Ioannou, and Manos Karpathiotakis for being good friends even if our overlap at EPFL was a short one. Lots of fun and delightful discussions during lunch, dinners, drinking nights, sports, and many other events.

- The list of Greek friends is so long that I would have certainly forgotten someone if I had

tried to name individuals. Thank you all for making my life in Lausanne more colorful.

Thanks to AEGEL for organizing Christmas and carnival parties as well as unforgettable

barbecue events by the lake.

Special thanks to my lifelong friends Tryphon Athanassiades, Christos Dionysiou (and Maria Faladou), Giorgos Vassiliou, and Pambos Yioufkas from Cyprus for making my life joyful and colorful, and for having amazing experiences and fun with them during summer and winter holidays in various places across the world, bars, rocky and sandy beaches, and their apartments in my hometown. Through their friendship, I was able to spend wonderful time during precious time-off necessary for "rebooting" while long-distance interactions with them helped me maintaining my sanity.

Many thanks to my friends, Dimitris Dimitriou and Yiannis Tofis, for long and entertaining chats over Skype and for all the cool drinking nights in bars and other fun moments in sandy beaches.

Kudos to Armin Van Buuren's and Prisma Storm's weekly shows for delivering euphoric sessions of trance music which has been inspiring me for almost a decade now.

I would like to express my appreciation to Georgios Psaropoulos for preparing the German version of my thesis abstract. The thesis was supported by the Swiss National Science Foundation project 200021\_127021 and the NanoTera project "YINS".

Last but not least, I would like to express my deep indebtedness to my family, including my parents, Michael and Maro, and my two elder brothers, Haris and Yiannis. Words cannnot describe my gratitude to these people. Throughout my life, they have been great supporters and teachers in so many ways. Skype calls with them have been reminding me who I am and what my origins are. The constant support and the endless love of my parents have been guiding me throughout my life and helped me overcoming the dark stages of my PhD studies. Haris has been a great role model during my graduate studies. His guidance and support helped me during tough moments of my PhD. Due to mutual research interests, I was lucky to spend lots of time with him during various conferences and in various places across the world. Yiannis' desire for high-risk projects has motivated me to be less conservative in my research and to keep fighting after paper rejections. Papa, Mama, Hari, Yianni thanks for everything!!!

Lausanne, 25 Juillet 2015

S. V.

### **Abstract**

The information revolution of the last decade has been fueled by the digitization of almost all human activities through a wide range of Internet services. The backbone of this information age are scale-out datacenters that need to collect, store, and process massive amounts of data. These datacenters distribute vast datasets across a large number of servers, typically into memory-resident shards so as to maintain strict quality-of-service guarantees.

While data is driving the skyrocketing demands for scale-out servers, processor and memory manufacturers have reached fundamental efficiency limits, no longer able to increase server energy efficiency at a sufficient pace. As a result, energy has emerged as the main obstacle to the scalability of information technology (IT) with huge economic implications.

Delivering sustainable IT calls for a paradigm shift in computer system design. As memory has taken a central role in IT infrastructure, memory-centric architectures are required to fully utilize the IT's costly memory investment. In response, processor architects are resorting to manycore architectures to leverage the abundant request-level parallelism found in datacentric applications. Manycore processors fully utilize available memory resources, thereby increasing IT efficiency by almost an order of magnitude.

Because manycore server chips execute a large number of concurrent requests, they exhibit high incidence of accesses to the last-level-cache for fetching instructions (due to large instruction footprints), and off-chip memory (due to lack of temporal reuse in on-chip caches) for accessing dataset objects. As a result, on-chip interconnects and the memory system are emerging as major performance and energy-efficiency bottlenecks in servers.

#### **Abstract**

This thesis seeks to architect on-chip interconnects and memory systems that are tuned for the requirements of memory-centric scale-out servers. By studying a wide range of data-centric applications, we uncover application phenomena common in data-centric applications, and examine their implications on on-chip network and off-chip memory traffic. Finally, we propose specialized on-chip interconnects and memory systems that leverage common traffic characteristics, thereby improving server throughput and energy efficiency.

Key words: cloud, scale-out, datacenters, interconnects, memory systems, DRAM

### Zusammenfassung

Die Informationsrevolution des letzten Jahrzehnts wurde durch die Digitalisierung aller menschlichen Aktivitäten mittels einer breiten Palette von Internetdienstleistungen befördert. Die Basis dieser Informationszeitalter feststellen die Scale-Out-Rechnenzentren, die große Datenmengen sammeln, speichern und verarbeiten. Diese Rechenzentren verteilen große Datasets über eine große Anzahl von Servern, in speicherresidenter Shards normalerweise, um bestimmte Quality-of-Service-Garantien zu erhalten.

Während Daten die explodierenden Nachfrage für Scale-Out-Server fährt, haben Prozessorund Speicher-Hersteller grundlegende Effizienzgrenzen, denn die Serverenergieeffizienz kann nicht mehr ausreichend steigern. Energie entsteht als das größte Hindernis für die Skalierbarkeit der Informationstechnologie (IT) mit starken wirtschaftlichen und ökologischen Auswirkungen.

Die Lieferung nachhaltiger IT fordert einen Paradigmenwechsel im Computersystementwurf. Wegen der zentralen Rolle des Speichers in IT-Infrastruktur, Speicherorientierte Architekturen sind erforderlich, um die kostspielig Speicher Investition in vollem auszunutzen. Im Gegenzug sind Prozessorarchitekten auf Manycore-Architekturen zurückgegriffen, um die reichliche Anforderungsebenenparallelität datenorientierter Applikationen zu verwenden. Manycore-Prozessoren voll ausnutzen verfügbaren Speicherressourcen, wodurch IT-Effizienz um fast eine Größenordnung verbessert ist.

Denn Manycore-Server-Chips führen eine große Anzahl von gleichzeitigen Anforderungen aus, zeigen sie viele Zugriffe auf die Last-Level-Cache zum Instruktionsabrufen (aufgrund der großen Anweisungsbedarf), und Off-Chip-Speicher (aufgrund fehlenden zeitlichen Wiederverwendung in On-Chip-Caches) für den Zugriff auf Dataset-Objekte. Demzufolge entstehen

Abstract

die Chip-Interconnects und das Speichersystem als große Leistung- und Energieeffizienz-

Engpässe der Server.

Diese These zielt darauf ab, On-Chip-Netzwerke und Speichersystemen zu entwickeln, die für

die Anforderungen der Speicherzentrierten Scale-Out-Servern optimiert werden. Durch das

Studium einer Vielzahl von datenzentrischen Applikationen, wir entdecken gewöhnliche Phä-

nomene dieser Applikationen und untersuchen ihre Auswirkungen auf das Netzwerkverkehr

und das Speicherverkehr. Schließlich schlagen wir spezialisierten On-Chip-Netzwerk und Spei-

chersysteme, die das gemeinsame Traffic Charakteristiken verwenden, um das Throughput

und die Energieeffizienz zu verbessern.

Stichwörter: Cloud, Scale-Out, Rechnenzentren, Netzwerke, Speichersystemen, DRAM

X

## **Contents**

| Ac | knov  | vledgments                                                          | j           |

|----|-------|---------------------------------------------------------------------|-------------|

| Ał | ostra | ct (English/Deutsch)                                                | <b>vi</b> i |

| Li | st of | figures                                                             | χι          |

| Li | st of | tables                                                              | xvi         |

| 1  | Intr  | oduction                                                            | 1           |

|    | 1.1   | Data-Centric Information Technology Meets Energy Wall               | 2           |

|    | 1.2   | Toward Specialized Memory-Centric Servers                           | 3           |

|    |       | 1.2.1 What do data-centric workloads need?                          | 4           |

|    |       | 1.2.2 Processor architecture                                        | 5           |

|    |       | 1.2.3 Efficiency bottlenecks                                        | 6           |

|    | 1.3   | Thesis Goals                                                        | 8           |

|    | 1.4   | Efficient On-Chip Communication                                     | 9           |

|    | 1.5   | Efficient LLC-Memory Communication                                  | g           |

|    | 1.6   | Scalable Off-Chip Memory Systems                                    | 10          |

|    | 1.7   | Thesis Contributions                                                | 10          |

| 2  | Spe   | cialized On-Chip Interconnects for Efficient Core-LLC Communication | 13          |

|    | 2.1   | Multi-Network NoCs: The Way to Specialization and Efficiency        | 13          |

|    |       | 2.1.1 Why multi-network NoCs?                                       | 14          |

|    |       | 2.1.2 Design considerations in multi-network NoCs                   | 15          |

|    |       |                                                                     |             |

#### **Contents**

|   | 2.2               | On-C                                                        | hip Communication Activity                                                                                                                                                                                                                                                                      | 17                                                 |

|---|-------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|   |                   | 2.2.1                                                       | Coherence protocol activity                                                                                                                                                                                                                                                                     | 17                                                 |

|   |                   | 2.2.2                                                       | On-chip network traffic characterization                                                                                                                                                                                                                                                        | 18                                                 |

|   |                   | 2.2.3                                                       | Summary                                                                                                                                                                                                                                                                                         | 20                                                 |

|   | 2.3               | Dual-                                                       | Network NoC Organization                                                                                                                                                                                                                                                                        | 20                                                 |

|   |                   | 2.3.1                                                       | Protocol-level deadlock avoidance                                                                                                                                                                                                                                                               | 21                                                 |

|   |                   | 2.3.2                                                       | Router microarchitecture                                                                                                                                                                                                                                                                        | 22                                                 |

|   | 2.4               | Evalu                                                       | ation                                                                                                                                                                                                                                                                                           | 22                                                 |

|   |                   | 2.4.1                                                       | Methodology                                                                                                                                                                                                                                                                                     | 23                                                 |

|   |                   | 2.4.2                                                       | Comparison to single-network NoCs                                                                                                                                                                                                                                                               | 25                                                 |

|   |                   | 2.4.3                                                       | Comparison to dual-network NoCs                                                                                                                                                                                                                                                                 | 27                                                 |

|   |                   | 2.4.4                                                       | NoC area analysis                                                                                                                                                                                                                                                                               | 30                                                 |

|   |                   | 2.4.5                                                       | Sensitivity analysis                                                                                                                                                                                                                                                                            | 30                                                 |

|   |                   | 2.4.6                                                       | Summary                                                                                                                                                                                                                                                                                         | 31                                                 |

|   |                   |                                                             |                                                                                                                                                                                                                                                                                                 |                                                    |

| 3 | On-               | Chip S                                                      | upport for Efficient LLC-Memory Communication                                                                                                                                                                                                                                                   | 33                                                 |

| 3 | <b>On-</b>        | -                                                           | upport for Efficient LLC-Memory Communication ground and Limitations                                                                                                                                                                                                                            | <b>33</b>                                          |

| 3 |                   | Backg                                                       | •                                                                                                                                                                                                                                                                                               |                                                    |

| 3 | 3.1               | Backg                                                       | ground and Limitations                                                                                                                                                                                                                                                                          | 33                                                 |

| 3 | 3.1               | Backg<br>Memo                                               | ground and Limitations                                                                                                                                                                                                                                                                          | 33<br>36                                           |

| 3 | 3.1               | Backg<br>Memo<br>3.2.1<br>3.2.2                             | ground and Limitations                                                                                                                                                                                                                                                                          | 33<br>36<br>36                                     |

| 3 | 3.1               | Backg<br>Memo<br>3.2.1<br>3.2.2                             | round and Limitations                                                                                                                                                                                                                                                                           | 33<br>36<br>36<br>39                               |

| 3 | 3.1               | Backg<br>Memo<br>3.2.1<br>3.2.2<br>Bulk M                   | round and Limitations                                                                                                                                                                                                                                                                           | 33<br>36<br>36<br>39<br>40                         |

| 3 | 3.1               | Backg Memo 3.2.1 3.2.2 Bulk N 3.3.1                         | round and Limitations                                                                                                                                                                                                                                                                           | 33<br>36<br>36<br>39<br>40<br>40                   |

| 3 | 3.1               | Backg Memo 3.2.1 3.2.2 Bulk N 3.3.1 3.3.2                   | ground and Limitations  Ory Traffic Characterization  Memory reads  Memory writes  Memory Access Prediction and Streaming  Design overview  Bulk memory read prediction and streaming                                                                                                           | 33<br>36<br>36<br>39<br>40<br>40                   |

| 3 | 3.1               | Backg Memo 3.2.1 3.2.2 Bulk M 3.3.1 3.3.2 3.3.3             | round and Limitations  Ory Traffic Characterization  Memory reads  Memory writes  Memory Access Prediction and Streaming  Design overview  Bulk memory read prediction and streaming  Bulk memory write prediction and streaming                                                                | 33<br>36<br>36<br>39<br>40<br>40<br>41<br>43       |

| 3 | 3.1               | Backg Memo 3.2.1 3.2.2 Bulk M 3.3.1 3.3.2 3.3.3 3.3.4 3.3.5 | ground and Limitations  Dry Traffic Characterization  Memory reads  Memory writes  Memory Access Prediction and Streaming  Design overview  Bulk memory read prediction and streaming  Bulk memory write prediction and streaming  Transfer of program counter                                  | 33<br>36<br>36<br>39<br>40<br>40<br>41<br>43<br>44 |

| 3 | 3.1<br>3.2<br>3.3 | Backg Memo 3.2.1 3.2.2 Bulk M 3.3.1 3.3.2 3.3.3 3.3.4 3.3.5 | ground and Limitations  Dry Traffic Characterization  Memory reads  Memory writes  Memory Access Prediction and Streaming  Design overview  Bulk memory read prediction and streaming  Bulk memory write prediction and streaming  Transfer of program counter  Configuration and hardware cost | 33<br>36<br>36<br>39<br>40<br>41<br>43<br>44<br>44 |

|   |      | 3.4.3   | Energy efficiency implications                                   | 51 |

|---|------|---------|------------------------------------------------------------------|----|

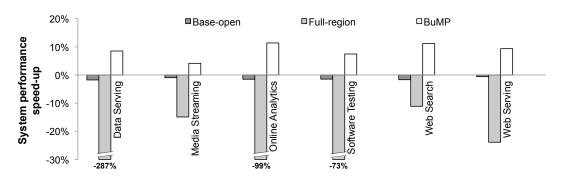

|   |      | 3.4.4   | Performance implications                                         | 52 |

|   |      | 3.4.5   | On-chip bandwidth and energy overheads                           | 53 |

|   |      | 3.4.6   | Sensitivity analysis                                             | 54 |

|   |      | 3.4.7   | Summary                                                          | 56 |

|   | 3.5  | Discu   | ssion                                                            | 57 |

| 4 | Scal | lable O | ff-Chip Memory Systems                                           | 59 |

|   | 4.1  | Motiv   | ation                                                            | 59 |

|   |      | 4.1.1   | Scale-out server requirements                                    | 60 |

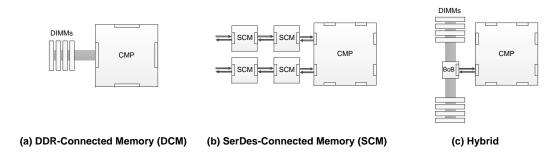

|   |      | 4.1.2   | Conventional and emerging memory systems                         | 61 |

|   |      | 4.1.3   | Summary                                                          | 64 |

|   | 4.2  | Utiliz  | ing SerDes-Connected Memory Modules as a New Level in the Memory |    |

|   |      | Hiera   | rchy                                                             | 64 |

|   | 4.3  | MeSS    | OS: A Memory System Organization for Scale-Out Servers           | 69 |

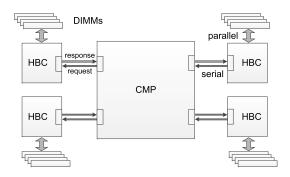

|   |      | 4.3.1   | HBC-main memory interface                                        | 69 |

|   |      | 4.3.2   | High-bandwidth cache organization                                | 70 |

|   |      | 4.3.3   | Processor-HBC interface                                          | 71 |

|   | 4.4  | Exper   | imental Methodology                                              | 71 |

|   |      | 4.4.1   | Scale-out server organization                                    | 71 |

|   |      | 4.4.2   | Performance and energy evaluation                                | 72 |

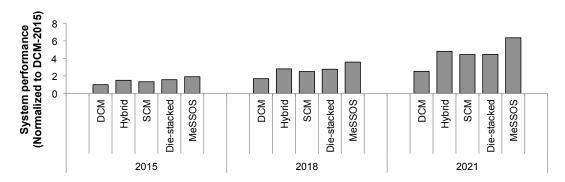

|   |      | 4.4.3   | Projection to future technologies                                | 75 |

|   | 4.5  | Evalua  | ation                                                            | 77 |

|   |      | 4.5.1   | Baseline study                                                   | 77 |

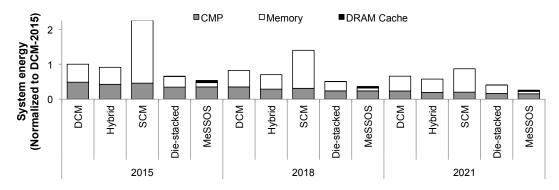

|   |      | 4.5.2   | Projection to future technologies                                | 81 |

|   |      | 4.5.3   | MeSSOS with a die-stacked DRAM cache                             | 82 |

|   | 4.6  | Discu   | ssion                                                            | 83 |

| 5 | Rela | ated Wo | ork                                                              | 85 |

|   | 5.1  | On-Cl   | nip Interconnects                                                | 85 |

|   |      |         |                                                                  |    |

#### **Contents**

|                  | 5.2 | Memo   | ory Systems                 | 86 |

|------------------|-----|--------|-----------------------------|----|

|                  |     | 5.2.1  | Mitigating static power     | 87 |

|                  |     | 5.2.2  | Mitigating activation power | 88 |

|                  | 5.3 | Instru | action-Based Prediction     | 89 |

| 6                | Con | cludin | ng Remarks                  | 91 |

|                  | 6.1 | Futur  | e Directions                | 93 |

| Bibliography     |     |        |                             |    |

| Curriculum Vitae |     |        |                             |    |

# **List of Figures**

| scaling tierius for the transistor count, clock frequency, number of cores, and |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| single-thread performance of processor chip                                     | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Architecture of a specialized memory-centric server                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Efficiency bottlenecks in memory-centric servers                                | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

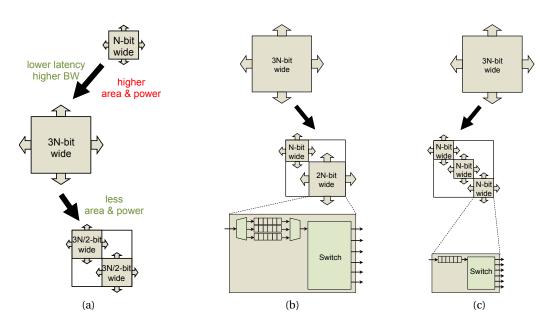

| Multi-network NoCs                                                              | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

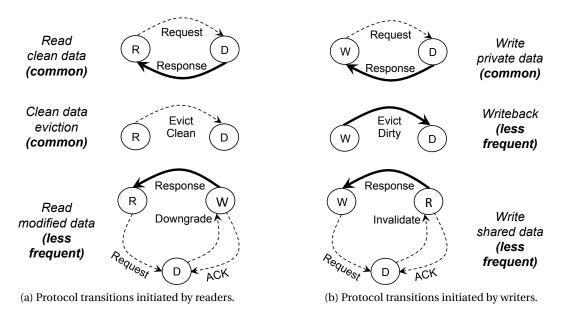

| Cache-coherence protocol transitions                                            | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

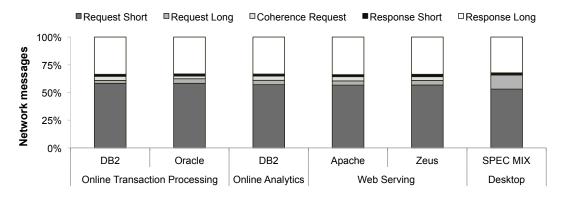

| On-chip network message class and size distribution                             | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

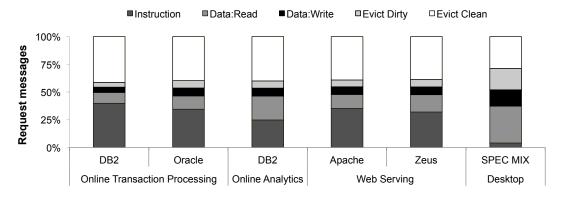

| Request message class distribution                                              | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

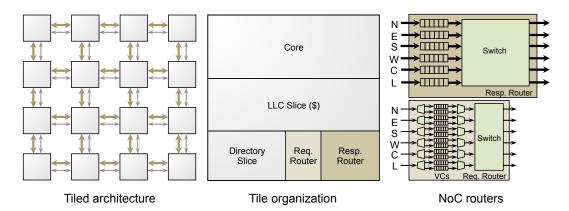

| CCNoC-enabled tiled organization                                                | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

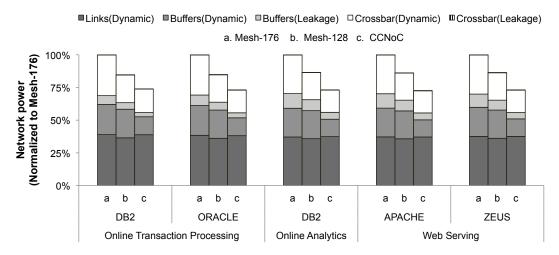

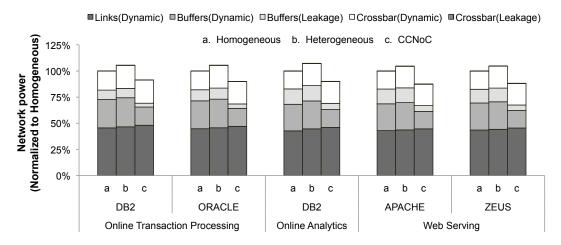

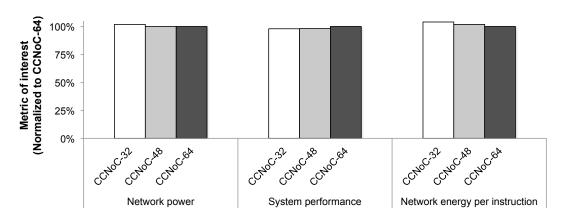

| CCNoC power consumption compared to single-network NoCs                         | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

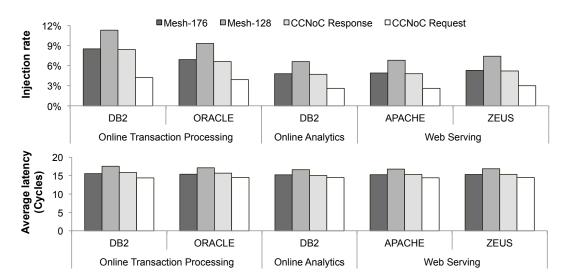

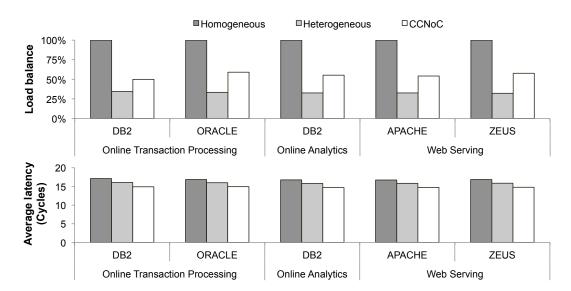

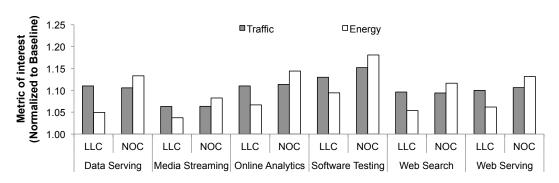

| CCNoC network performance compared to single-network NoCs                       | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

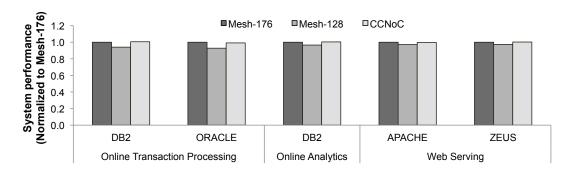

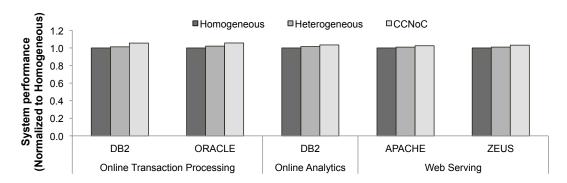

| CCNoC system performance compared to single-network NoCs                        | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CCNoC power consumption compared to dual-network NoCs                           | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CCNoC network performance compared to dual-network NoCs                         | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CCNoC system performance compared to dual-network NoCs                          | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

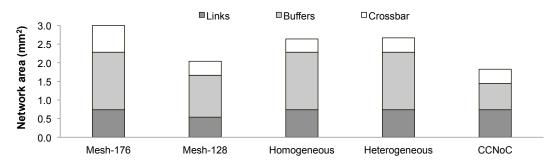

| Network area for single-NoC and dual-NoC networks                               | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Efficiency sensitivity to request network width                                 | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

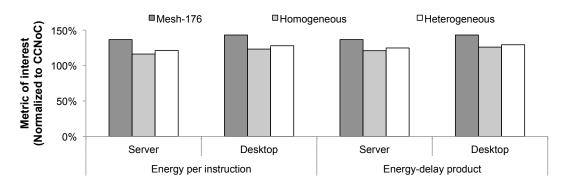

| Network energy per instruction and energy-delay product                         | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

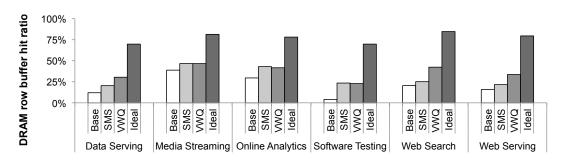

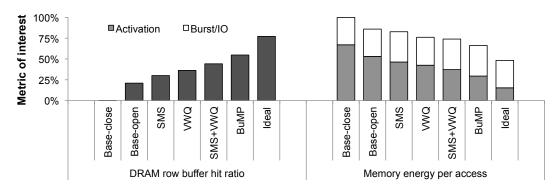

| DRAM row buffer hit ratio in servers                                            | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

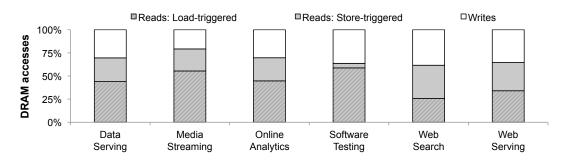

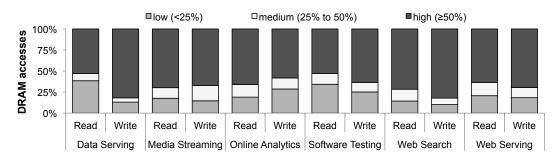

| DRAM access breakdown                                                           | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                 | Architecture of a specialized memory-centric server.  Efficiency bottlenecks in memory-centric servers.  Multi-network NoCs  Cache-coherence protocol transitions  On-chip network message class and size distribution.  Request message class distribution.  CCNoC-enabled tiled organization  CCNoC power consumption compared to single-network NoCs.  CCNoC network performance compared to single-network NoCs.  CCNoC system performance compared to dual-network NoCs.  CCNoC network performance compared to dual-network NoCs.  CCNoC network performance compared to dual-network NoCs.  CCNoC system performance compared to dual-network NoCs.  ECNoC system performance compared to dual-network NoCs.  CCNoC system performance compared to dual-network NoCs.  Efficiency sensitivity to request network width  Network energy per instruction and energy-delay product.  DRAM row buffer hit ratio in servers. |

#### **List of Figures**

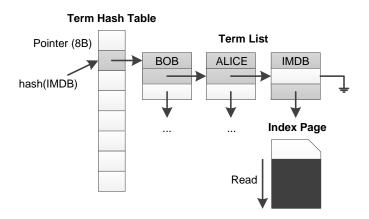

| 3.3          | The inverted index in Web Search                                                | 37       |

|--------------|---------------------------------------------------------------------------------|----------|

| 3.4          | Memory region access density                                                    | 38       |

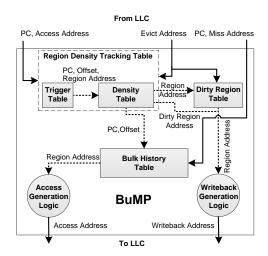

| 3.5          | BuMP design overview                                                            | 40       |

| 3.6          | Example for region density tracking and identifying instructions that access    |          |

|              | high-density regions                                                            | 43       |

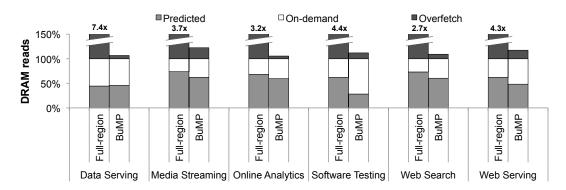

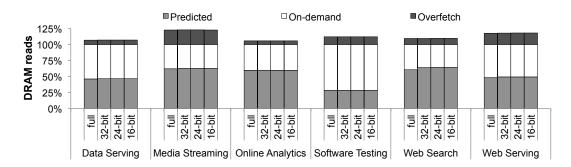

| 3.7          | BuMP memory read prediction accuracy                                            | 49       |

| 3.8          | BuMP memory write prediction accuracy                                           | 50       |

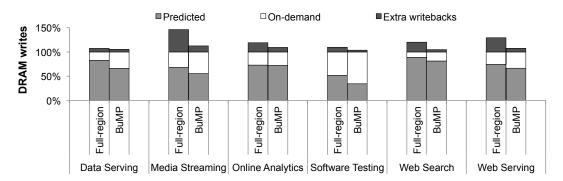

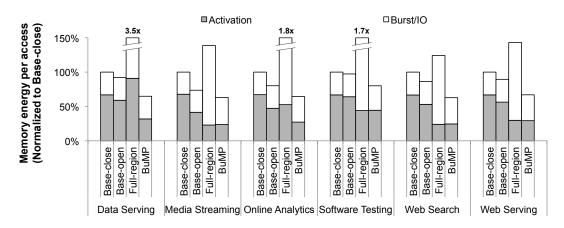

| 3.9          | Memory energy per access for various systems normalized to Base-close           | 51       |

| 3.10         | System performance comparison to Base-close                                     | 53       |

| 3.11         | BuMP's on-chip energy overheads                                                 | 54       |

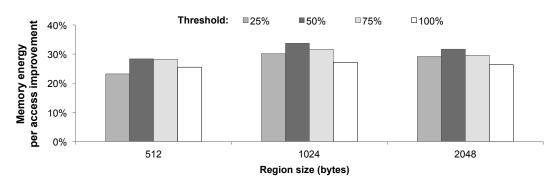

| 3.12         | Memory energy efficiency sensitivity to BuMP's threshold and region size        | 55       |

| 3.13         | Read prediction accuracy sensitivity to the number of program counter bits used |          |

|              | for indexing the bulk history table                                             | 55       |

| 3.14         | Comparison between BuMP and other systems                                       | 56       |

| 4.1          | Conventional and emerging memory systems                                        | 61       |

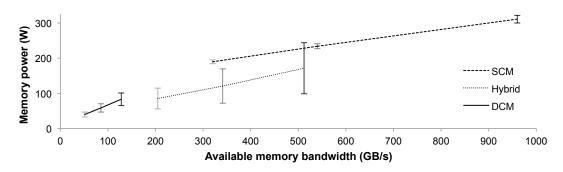

| 4.2          | Memory power–bandwidth trade-off                                                | 63       |

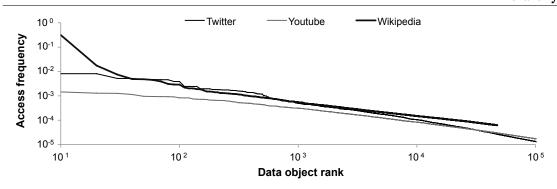

| 4.3          | Dataset accesses in web services exhibit power-law distribution                 | 65       |

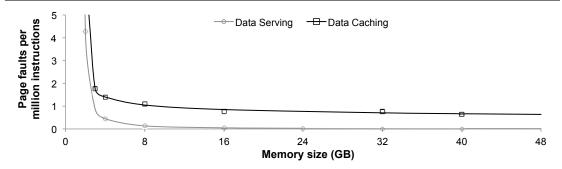

| 4.4          | Page fault rate for various memory sizes                                        | 67       |

| 4.5          | MeSSOS overview.                                                                | 68       |

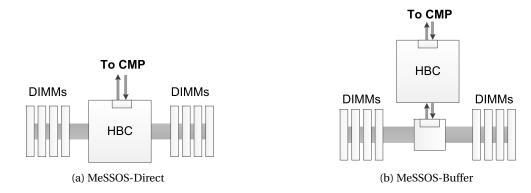

| 4.6          | HBC-Main Memory interface                                                       | 69       |

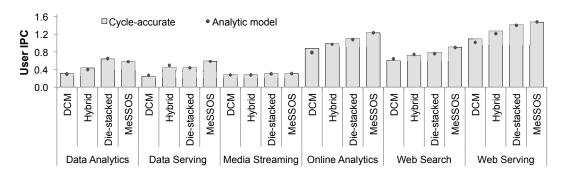

| 4.7          | Validation of analytic models against cycle-accurate simulations                | 73       |

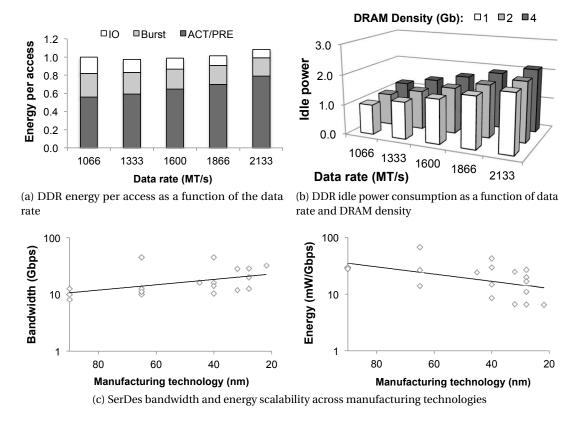

| 4.8          | Impact of technology scaling on memory technology and memory interfaces         | 76       |

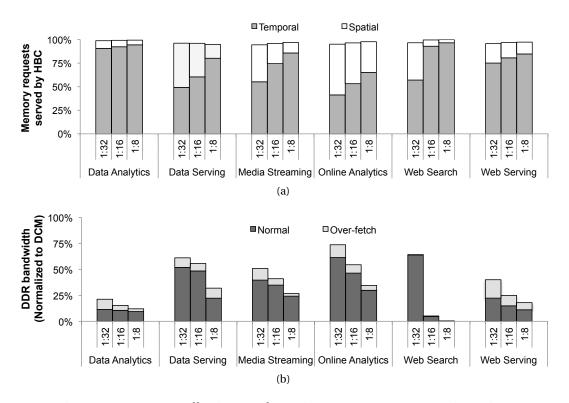

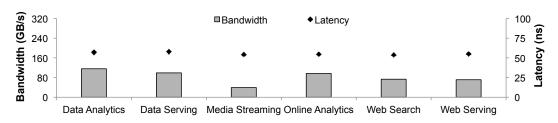

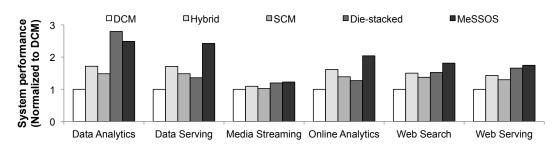

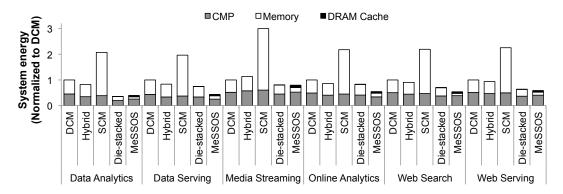

| 4.9          | MeSSOS effectiveness                                                            |          |

| 4 10         | Webbob thetheres                                                                | 77       |

| 4.10         | Bandwidth and memory latency in MeSSOS                                          | 77<br>78 |

|              |                                                                                 |          |

| 4.11         | Bandwidth and memory latency in MeSSOS                                          | 78       |

| 4.11<br>4.12 | Bandwidth and memory latency in MeSSOS                                          | 78<br>79 |

## **List of Tables**

| 2.1 | Message classes and types for the MESI coherence protocol                     | 15 |

|-----|-------------------------------------------------------------------------------|----|

| 2.2 | CMP configuration for cycle-accurate simulations                              | 23 |

| 3.1 | Fraction of LLC blocks of a high-density region that are modified once an LLC |    |

|     | block within the region is evicted                                            | 39 |

| 3.2 | System configuration for cycle-accurate simulations                           | 46 |

| 3.3 | Power and energy for system components                                        | 47 |

| 3.4 | BuMP's DRAM row buffer hit ratio                                              | 50 |

|     |                                                                               |    |

| 4.1 | Requirements of one scale-out server                                          | 60 |

| 4.2 | Systems configuration parameters                                              | 72 |

| 4.3 | System configuration for cycle-accurate simulations                           | 73 |

| 4.4 | System power model in 2015                                                    | 74 |

| 4.5 | Memory requests served by the die-stacked cache in the Die-Stacked system     | 79 |

| 4.6 | Server throughput when adding a die-stacked DRAM cache to a MeSSOS-enabled    |    |

|     | system (2015)                                                                 | 82 |

### 1 Introduction

Over the past five decades, information technology (IT) has gone through multiple phases. Driven by the continuous digitization of human activities, IT has transitioned from being compute-centric, to being network-centric, to being data-centric. IT was born in the form of *mainframes* to fulfill the need for number manipulation. The daily interaction between individuals and computers gave rise to *personal computers*, which were instantly made available in enterprises and homes, and digitized new flavors of activities, such as text writing. The need for fast interaction and communication among individuals in enterprises caused a shift in IT toward *networked computers*. A massive paradigm shift in IT followed when computer networks led to the invention of *Internet* due to the desire of individuals to connect and interact with each other across the world. Today, almost all our daily activities have been digitized through a wide range of Internet services, such as online banking, social networking, and video streaming. The information revolution of the last decade has been fueled by the digitization of all kinds of data, granting to individuals ubiquitous access to data and capturing information of value to business and societies.

Technology innovations and advancements in semiconductor fabrication industry have been powering IT with scalable computing platforms for decades. Two powerful paradigms have enabled computing scalability: *Moore's Law* and *Dennard Scaling*. Moore's Law postulates that fabrication advancements enable reduction in transistor size, doubling transistor density

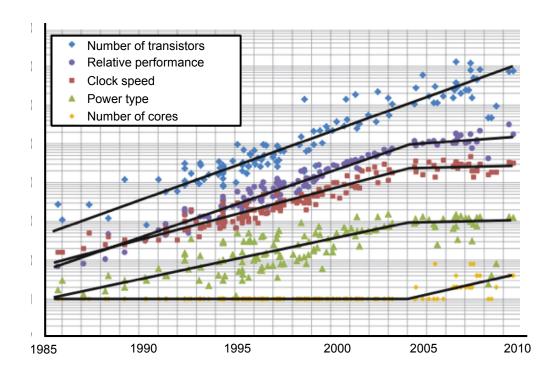

Figure 1.1 – Scaling trends for the transistor count, clock frequency, number of cores, and single-thread performance of processor chips. Source: Graph created by C. Batten based on data from M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten.

for processor and memory chips approximately every two years, while Dennard Scaling states that as transistors get smaller, their power density stays constant due to reduction of chip voltages. As shown in Figure 1.1, smaller and faster transistors have allowed processor designers to scale performance exponentially through higher core clock frequencies and microarchitectural advancements until 2004, and higher core counts for the last decade (2004-today) once frequency scaling became prohibitive due to chip-level cooling, thermal, and power constraints. Moore's Law coupled with Dennard Scaling have enabled an exponential increase in computing energy efficiency, and have been fueling IT with scalable computing platforms for over four decades.

#### 1.1 Data-Centric Information Technology Meets Energy Wall

Data has taken a central stage in our world, driving the skyrocketing demands of the IT sector for computational resources. The backbone of today's IT is large-scale datacenters, which host

a myriad of IT services and consequently collect, store, and process massive amounts of data. State-of-the-art datacenters deployed by technology giants, such as Google and Microsoft, host tens of thousands of servers, and have huge acquisition costs (\$100+ M), occupy enormous space (same as a football-sized pitch), and have vast power footprints (5-20 MW). Datacenter energy footprint has been estimated to be at 1.3% of global energy usage [66], and to grow at 20% per year due to a rapid pace of deployment of new datacenters.

The information revolution of the last decade has been accompanied by three IT colliding trends. First, the central role of data in our world has resulted in a rapid increase in data that needs to be collected, stored, and processed. IDC estimates a 300-fold-increase in the size of the digital universe over the span of 15 years, totaling over 40 zetabytes (i.e., over 40 billion terabytes) by 2020 [47]. Second, memory density and bandwidth cannot scale up at a sufficient pace, no longer satisfying the massive memory requirements of data-centric IT in an energy-efficient way [129]. Third, the semiconductor manufacturing industry has reached its fundamental efficiency limits, entering a post-Dennard Scaling Era, where on-chip voltages cannot be scaled down at a sufficient pace [27, 41, 45], no longer being able to increase energy efficiency of computing platforms exponentially.

With the growth of the digital universe outpacing technology scaling, energy is becoming the main scalability bottleneck to IT with huge economic and ecological implications. Based on projections, a ten-fold-increase in datacenter energy efficiency is required in the next decade to make IT sustainable. Achieving this goal, however, will require rethinking datacenter design, calling for innovation across all layers of the data-centric computing stack.

#### 1.2 Toward Specialized Memory-Centric Servers

Datacenter operators rely on *scale-out* architectures to deliver a scalable data-centric computing platform. In essence, scale-out datacenters distribute the vast datasets of IT services across a large number of servers, and typically exhibit a low degree of inter-server communication as servers mostly handle independent requests that do not share any state. IT services rely on

in-memory processing to boost throughput and lower response latency [12, 19, 94]. As a result, DRAM accounts for a significant share of both acquisition and operating costs of datacenters [9, 66, 83]. Maximizing datacenter efficiency calls for architectures that exhibit high memory resource utilization and minimize the overhead to access memory.

Although there has been a shift toward data-centric IT, servers – the heart of datacenters – still employ processor-centric architectures that were proposed in the early stages of compute-centric IT. In these systems, memory along with storage and networking are built around the processor. The mismatch between the requirements of data-centric IT and traditional computer system architectures [29] leads to severe under-utilization of datacenters' memory resources [28, 67, 80], and consequently poor datacenter efficiency [33].

Delivering sustainable IT infrastructure calls for a paradigm shift in computer system design toward *specialized memory-centric* architectures. Specialized memory-centric architectures seek to ensure efficient usage of memory resources by designing the entire computing stack – including processors [37, 78], networking [93], and software – around memory, and to fit the unique characteristics of data-centric applications [28, 29].

#### 1.2.1 What do data-centric workloads need?

Data-centric workloads, or scale-out workloads, exhibit abundant request-level (e.g., online services) and/or data-level parallelism (e.g., analytics) [21, 28]. The existing parallelism is leveraged through multi-threaded software stacks, where incoming requests in online services are assigned to individual worker threads, and datasets in analytics processing are partitioned and processed by multiple processes or threads [28, 65]. While threads are running on individual cores, they need to access instructions and data.

**Instructions.** These workloads deploy complex and deep software stacks and heavily use third-party libraries, resulting in multi-MB-sized application instruction working sets [2, 28, 29, 30]. Furthermore, the workloads spent significant fraction of their execution time in the operating system, mainly for network activity [28, 29, 73], resulting in even larger instruction

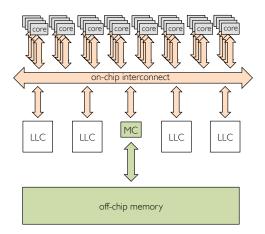

Figure 1.2 – Architecture of a specialized memory-centric server.

working sets. Because of large instruction footprints and their read-only nature, the shared instruction working set is accommodated in the last-level cache (i.e., the last level of the on-chip cache hierarchy). As a result, all cores frequently access the last-level cache (LLC) to fetch instructions.

**Data.** These workloads need to access vast memory-resident datasets for retrieving requestor task-dependent objects. Due to the disparity between dataset sizes (several tens of GBs)

and on-chip cache capacity (few tens of MBs), there is negligible temporal dataset reuse in

on-chip caches, resulting in a high incidence of off-chip memory accesses to fetch dataset

objects. To allow for constant-time (or sub-linear-time) dataset object retrievals, the datasets

are typically organized as pointer-intensive indexing data structures (e.g., a hash table or a

tree). Accesses to pointer-intensive data structures, however, result in a limited degree of ILP

and MLP within each thread due to high data dependency.

#### 1.2.2 Processor architecture

Specialized processors [37, 78] employ a large number of cores with customized complexity to strike for a balance between available instruction-, memory-, and thread-level parallelism (Figure 1.2). Based on the observation that last-level caches in data-centric workloads exploit mostly instruction-level temporal reuse, specialized processors reduce last-level cache ca-

pacity (a few MBs) to free area and power resources in favor of more cores, and to provide fast access to LLC-resident instructions. This specialized processor architecture delivers an order of magnitude higher server throughput over conventional processors while minimizing processor energy consumption in the face of long-latency memory stalls, thereby fully utilizing available memory resources and reducing the energy overhead to access memory.

#### 1.2.3 Efficiency bottlenecks

With specialized processors improving server and datacenter efficiency by almost an order of magnitude [33], the server efficiency bottlenecks are shifting to the memory system, including on-chip interconnects and the on-chip and off-chip memory subsystems. Manycore processors exhibit high incidence of accesses to the last-level-cache (LLC) for fetching instructions, and off-chip memory for fetching dataset objects. Maximizing efficiency calls for on-chip interconnects and memory systems that provide efficient access to LLC-resident instruction footprints and memory-resident datasets.

**On-chip interconnects.** They serve as the means of communication between cores and the last-level cache. They play a pivotal role in ensuring the performance and power scalability of server manycore chips as they provide the path to performance-critical LLC-resident instructions [28, 29], and communication power is emerging as a significant fraction of the total chip power [35, 118]. Designing an efficient on-chip interconnect is challenging as achieving both low latency and high bandwidth objectives comes at the cost of area/power overheads, prohibitive under fixed area/power budgets.

Multicore processors, featuring 2-16 cores, have relied on conventional crossbar interconnects [112] to achieve uniform and low network latency as well as high bandwidth by connecting each core to all last-level-cache banks. However, as the number of cores (and consequently number of ports) grow, crossbar interconnects face scalability limitations as their area and power footprints scale quadratically with the crossbar radix (i.e., number of crossbar ports) [110], and hence require prohibitive amount of on-chip resources.

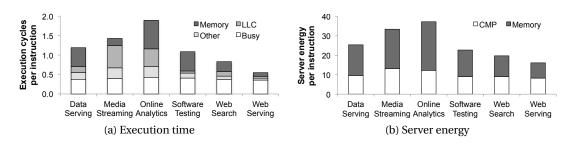

Figure 1.3 – Efficiency bottlenecks in memory-centric servers.

Tiled interconnects, referred to as Networks-on-Chip (NoCs), are emerging as the architecture of choice for providing a scalable interconnect for manycore processors [126] by employing packet-switched architectures and regular topologies, and decoupling the number of cores from the router radix. Their power footprint, however, is emerging as a significant obstacle in the quest for efficient manycore chips [35], accounting for as high as 40% of chip power [39, 118], calling for architectures that maximize NoC performance for a given power budget.

**Memory System.** The memory system plays a key role in IT efficiency as it hosts and provides access to the vast datasets of data-centric applications. With memory capacity driving memory system design, DRAM manufacturing industry has focused on improving DRAM density rather than DRAM efficiency. Over the past decade, DRAM density improved by 16x (256 Mb in 2004 to 4 Gb in 2014) as opposed to other DRAM parameters, such as latency and frequency. For instance, DRAM latency improved only by 50% (60 ns in 2004 to 40 ns in 2014). Due to the ever-increasing reliance of servers on DRAM, memory system is emerging as the major efficiency bottleneck as it has to serve frequent accesses from many cores to DRAM:

- **Latency.** Over the past decades, memory access latency has steadily increased relatively to the computation time, and hence a significant fraction of the server execution time is spent on waiting for memory accesses to be served by main memory (Figure 1.3a).

- Bandwidth. The growth rate in core count outpaces bandwidth scaling of conventional memory interfaces, driving designs into a memory bandwidth wall [49, 105, 129].

Conventional interfaces employ parallel buses to connect the processor to a set of dual-inline memory modules (DIMMs). Unfortunately, parallel interfaces exhibit poor signal

integrity which limits bus frequency [129]. Furthermore, the low pin-count scalability limits the number of memory channels integrated on a commodity processor [49]. Thus, high memory capacity requires that multiple DIMMs are deployed per memory channel, degrading signal integrity, and consequently lowering the bus frequency further.

- Energy. Memory energy is emerging as a major energy-efficiency bottleneck in servers, accounting for 48-62% of total server energy (Figure 1.3b) primarily due to architectural choices in memory interface design and DRAM organization.

- High-speed memory interfaces require energy-intensive DIMM-side clock recovery circuits which are kept active [81] regardless of the bus utilization, resulting in high static power consumption.

- DRAM memory uses a page-based organization, whereby the first access to a page must activate (or open) the page, requiring significant energy. Once a page is open, subsequent accesses to that page are served from the row buffer, avoiding the high energy and latency cost of a page activation. However, inter- and intra-thread contention on row buffer resources in manycore server processors prevent memory systems from fully exploiting row buffer locality. As a result, page activations are a major contributor to memory energy.

#### 1.3 Thesis Goals

This thesis proposes novel on-chip interconnects and memory systems tuned for the requirements of memory-centric scale-out servers.

#### **Thesis Statement**

Architecting high-throughput and energy-efficient memory-centric scale-out servers requires tuning their on-chip interconnect and memory system to fit the common traffic access characteristics of data-centric applications.

#### 1.4 Efficient On-Chip Communication

While today's on-chip interconnects are designed to provide low-latency and high-bandwidth core-to-core and core-to-LLC communication, our study of server workloads demonstrates that their on-chip network activity is dominated by core-to-LLC communication consisting of short requests (for instructions and clean data) and associated long responses.

We propose Cache-Coherence Network-on-Chip (CCNoC), a specialized on-chip interconnect to fit the bimodal network traffic characteristics of servers via a pair of asymmetric request and response networks. The networks are tuned for the type of traffic traversing them and differ in their datapath width and router micro-architecture. CCNoC improves on-chip interconnect area/power efficiency and boosts server throughput under fixed area/power budgets.

#### 1.5 Efficient LLC-Memory Communication

Improving memory system efficiency requires amortizing the costly DRAM page activations over multiple row buffer accesses. Although temporal locality at the LLC in scale-out workloads (due to vast datasets and large reuse distances) is scarce, spatial locality is abundant. Our study of scale-out applications shows that these applications commonly operate on coarsegrained objects (e.g., database rows, memory-mapped files) that are accessed through a pointer-intensive indexing data structure (e.g., a hash table, a tree). However, due to absence of information within the memory hierarchy about memory access patterns, last-level caches and memory controllers fail to exploit the coarse-grained memory accesses of scale-out applications.

We propose Bulk Memory Prediction and Streaming (BuMP) to identify accesses to coarse-grained objects, and trigger bulk transfers of coarse-grained objects between processor and off-chip memory. In doing so, BuMP exploits the spatial locality of scale-out applications and leverages the coarse granularity at which off-chip memory is organized, thereby improving server throughput and memory energy efficiency.

#### 1.6 Scalable Off-Chip Memory Systems

Emerging SerDes-connected memory (SCM) can break the pin bandwidth constraints of modern DDR interfaces and provide the required bandwidth, but at a significant power cost and high latency overhead due to large point-to-point memory networks required to host the vast datasets of scale-out workloads.

Our study of scale-out workloads shows that their memory access distributions are skewed, and hence a small portion of memory accounts for bulk of memory activity. This phenomenon primarily originates from the skewed dataset access distribution found in scale-out applications. For instance, a small fraction of popular users and their pictures in image sharing services account for the majority of user activity. However, in real-world setups with memory sizes of 100s of GBs, the hot dataset exceeds the capacity of on-chip and die-stacked caches.

We introduce MeSSOS, a Memory System for Scale-Out Servers. MeSSOS employs SCM modules as a high-bandwidth cache (HBC) in front of conventional DRAM. As the HBC is effective in filtering most of memory accesses, DCM modules can be clocked at low frequency, thus enabling high memory capacity at relatively low static power overhead. Overall, MeSSOS satisfies the required memory bandwidth and capacity requirements of a scale-out server while minimizing the power consumption of underlying memory technologies and interfaces.

#### 1.7 Thesis Contributions

Through a combination of analytic modeling models, trace-driven analysis, and cycle-accurate full-system simulation of manycore servers, we demonstrate: