# High-level synthesis of dataflow programs for heterogeneous platforms: design flow tools and design space exploration

### THÈSE Nº 6653 (2015)

PRÉSENTÉE LE 29 MAI 2015

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

GROUPE SCI STI MM

PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Endri BEZATI

acceptée sur proposition du jury:

Dr J.-M. Sallese, président du jury Dr M. Mattavelli, directeur de thèse Prof. G. De Micheli, rapporteur Dr J. Janneck, rapporteur Dr M. Raulet, rapporteur

## Acknowledgements

First of all I would like to thank my parents, Dhimiter and Pavlina Bezati for their strong efforts as immigrants to support me during my studies in France. I would like to thank my brother, Dr. Feliks Bezati for helping me with guidance all those years. I thank my uncle Dr. Anesti Duka for his proposition to pursue my studies in France, my path would have been completely different today. I would like to thank my partner Franziska Thoms for all those years of love, happiness, and support.

I wish to express my gratitude to my supervisor Dr. MER Marco Mattavelli for his guidance, support, advice, and criticism during the last four years. I would like to thank Dr. Mickaël Raulet for believing in me and suggesting me to Marco for pursuing a PhD in my Lab. I wish also to express my gratitude to my *spiritual* mentor Dr. Jörn Janneck for his help and guidance. I would like to thank Dr. Ghislain Roquier for his patience and help that he provided me during the first years of my thesis. Also, I would like to thank Dr. Matthieu Wipliez for the Orcc compiler infrastructure, Herve Yviquel and Antoine Lorence for their maintenance and advancement in Orcc. In addition, I would like to thank all previous developers of OpenForge for their excellent work and Xilinx Inc. for open sourcing it.

I would like to thank my *partner in crime* Simone Casale Brunet, both of us have built tools that are working in perfect coordination. Also, I would like to thank all my past and present lab members.

Finally, I would like to thank the Swiss National Science Foundation for founding my research.

Lausanne, 29 April 2015

Endri Bezati

### **Abstract**

The growing complexity of digital signal processing applications implemented in programmable logic and embedded processors make a compelling case the use of high-level methodologies for their design and implementation. Past research has shown that for complex systems, raising the level of abstraction does not necessarily come at a cost in terms of performance or resource requirements. As a matter of fact, high-level synthesis tools supporting such a high abstraction often rival and on occasion improve low-level design. In spite of these successes, high-level synthesis still relies on programs being written with the target and often the synthesis process, in mind. In other words, imperative languages such as C or C++, most used languages for high-level synthesis, are either modified or a constrained subset is used to make parallelism explicit. In addition, a proper behavioral description that permits the unification for hardware and software design is still an elusive goal for heterogeneous platforms. A promising behavioral description capable of expressing both sequential and parallel application is RVC-CAL. RVC-CAL is a dataflow programming language that permits design abstraction, modularity, and portability. The objective of this thesis is to provide a high-level synthesis solution for RVC-CAL dataflow programs and provide an RVC-CAL design flow for heterogeneous platforms. The main contributions of this thesis are: a high-level synthesis infrastructure that supports the full specification of RVC-CAL, an action selection strategy for supporting parallel read and writes of list of tokens in hardware synthesis, a dynamic fine-grain profiling for synthesized dataflow programs, an iterative design space exploration framework that permits the performance estimation, analysis, and optimization of heterogeneous platforms, and finally a clock gating strategy that reduces the dynamic power consumption. Experimental results on all stages of the provided design flow, demonstrate the capabilities of the tools for high-level synthesis, software hardware Co-Design, design space exploration, and power optimization for reconfigurable hardware. Consequently, this work proves the viability of complex systems design and implementation using dataflow programming, not only for system-level simulation but real heterogeneous implementations.

**Key words**: High-level synthesis, Dataflow Programing, Clock-Gating, Co-Design, Design Flow, Design Space Exploration

### Résumé

De nos jours, les applications de traitement numérique du signal sont de plus en plus complexes dans leurs mises en œuvre et leurs conceptions pour des implantations sur des processeurs embarqués contenant de la logique programmable. Ceci demande le développement de nouvelles méthodologies basées sur un langage à haut niveau d'abstraction. Des recherches antérieures ont montré que pour les systèmes complexes, l'élévation du niveau d'abstraction n'augmente pas nécessairement les coûts en termes de ressources ou la dégradation des performances. En général, des outils de synthèse haut niveau avec une telle abstraction, souvent concurrentiels, améliorent dans certains cas la conception de systèmes de niveau hiérarchique très bas. En dépit de ces succès, la synthèse haut niveau s'appuie toujours sur le principe que les programmes doivent s'adapter à la cible souhaitée sans oublier les particularités du système de synthèse. En d'autres termes, les langages impératifs tels que C ou C++, les plus utilisés pour la synthèse haut niveau, sont soit modifiés ou soit adaptés en un sous-ensemble de langages pour faire un parallélisme explicite. De plus, une description comportementale appropriée qui permet l'unification de conception de systèmes hétérogènes est toujours un objectif difficile à atteindre. Une des plus prometteuses, capable d'exprimer à la fois l'application séquentielle et parallèle, est exprimée en RVC-CAL. Ce dernier est donc un langage de programmation en flux de données qui permet l'abstraction de la conception, de la modularité et de la portabilité. Les objectifs de cette thèse sont de fournir une solution de synthèse haut niveau pour des programmes écrits en RVC-CAL et de fournir une solution d'implantation pour des plates-formes hétérogènes. Les principales contributions de cette thèse sont : une infrastructure de synthèse de haut niveau qui prend en charge la spécification complète de RVC-CAL, une stratégie de sélection d'action pour la synthèse haut niveau pour permettre la lecture et l'écriture en parallèle de la liste des jetons, un profilage dynamique à grain fin pour les programmes de flux de données qui sont synthétisés, une structure d'exploration de l'espace pour des programmes de flux de données qui permet l'estimation de performance, l'analyse et l'optimisation des plates-formes hétérogènes et enfin une stratégie de « clockgating » qui réduit la consommation d'énergie dynamiquement. Des résultats expérimentaux sur toutes les étapes du déroulement de la conception, démontrent les capacités des outils de synthèse haut niveau, le Co-Design des parties matériel et logiciel, l'exploration spatiale de l'application, et l'optimisation de puissance pour des plates-formes reconfigurables. En conclusion, ce travail prouve la viabilité de la conception et la mise en œuvre de systèmes complexes en utilisant la programmation de flux de données, pas seulement pour la simulation au niveau du système, mais aussi pour les implémentations hétérogènes.

### Acknowledgements

**Mots clefs** : synthèse de haut niveau, flux de données, clock-gating, co-design, flot de conception, exploration de l'éspace du design

## **Abbreviations**

ALAP As Late As Possible

ANSI American National Standards Institute

ASAP As Soon As Possible

ASIC Application Specific Integrated Circuit

AST Abstract Syntax Tree

BDL Behavioral Description Language

BRAM Block RAM

CAD Computer Aided Design

CAL CAL Actor Language

CAM Computer Aided Manufacturing

CDFG Control-Data Flow Graph

CFG Control Flow Graph

CL Computational Load

CP Critical Path

CPU Central Processing Unit

CUDA Compute Unified Device Architecture

DSL Domain-Specific Language

DSP Digital Signal Processor

EMF Eclipse Modeling Framework

ETG Execution Trace Graph

FDS Force-Directed Scheduling

### Acknowledgements

FF Flip-Flop Register

FPGA Filed-Programmable Gate Array

FSM Finite State Machine

HDL High-Description Language

HLS High-Level Synthesis

HW Hardware

IDE Integrated Developing Environment

ILP Integer Linear Programming

IP Intellectual Property

IR Intermediate Representation

ISPS Instruction Set Processor Specification

LLVM Low Level Virtual Machine

LUB Least Upper Bound

LUT Look-Up Table

LVA Live Variable Analysis

MDE Model-Driven Engineering

MoA Model of Architecture

MPEG Movie Picture Expert Group

Orcc Open RVC-CAL Compiler

QoR Quality of Results

RAM Random Access Memory

ROM Read Only Memory

RTL Register Transfer Layer

RVC Reconfigurable Video Coding

SoC System on Chip

SSA Single Static Assignment

SW Software

xii

UML Unified Modeling Language

VHDL VHSIC Hardware Description Language

VHSIC Very High-Speed Integrated Circuit

VLSI Very-Large-Scale Integration

XLIM XML Language Independent Model

## **Contents**

| Ac | knov  | vledgements                                                                 | V     |

|----|-------|-----------------------------------------------------------------------------|-------|

| Ał | ostra | ct (English/Français/Deutsch)                                               | vii   |

| Ał | brev  | riations                                                                    | хi    |

| Li | st of | figures                                                                     | cviii |

| Li | st of | tables                                                                      | xxi   |

| 1  | Intr  | oduction                                                                    | 1     |

|    | 1.1   | Design of Complex Systems                                                   | 1     |

|    | 1.2   | Problem Statement and Motivation                                            | 3     |

|    | 1.3   | Design Flow for Dataflow Programs                                           | 6     |

|    | 1.4   | Thesis Contributions and Organization                                       | 8     |

| 2  | Stat  | e of the Art                                                                | 11    |

|    | 2.1   | Introduction                                                                | 11    |

|    | 2.2   | Heterogeneous platforms                                                     | 13    |

|    | 2.3   | High-Level Synthesis                                                        | 15    |

|    |       | 2.3.1 HLS tools evolution                                                   | 16    |

|    |       | 2.3.2 Behavioral Description                                                | 18    |

|    | 2.4   | Scheduling of Operators, Operators Pipelining and Power Optimization in HLS | 23    |

|    |       | 2.4.1 Scheduling of Operators                                               | 23    |

|    |       | 2.4.2 Operators Pipelining                                                  | 25    |

|    |       | 2.4.3 Power Optimization                                                    | 26    |

|    | 2.5   | Dataflow Design Flows for HW and SW Co-Design                               | 28    |

|    | 2.6   | Conclusion                                                                  | 31    |

| 3  | CAI   | Dataflow Programming Language                                               | 33    |

|    | 3.1   | Introduction                                                                | 33    |

|    | 3.2   | Process Networks                                                            | 36    |

|    |       | 3.2.1 KPN                                                                   | 36    |

|    |       | 3.2.2 Dataflow Process Network                                              | 37    |

|    |       | 3.2.3 Actor Transition System and Composition                               | 38    |

### **Contents**

|   | 3.3  | CAL Actor Language                                                     |

|---|------|------------------------------------------------------------------------|

|   |      | 3.3.1 CAL Program                                                      |

|   |      | 3.3.2 Execution Model                                                  |

|   |      | 3.3.3 CAL Syntax and Semantics                                         |

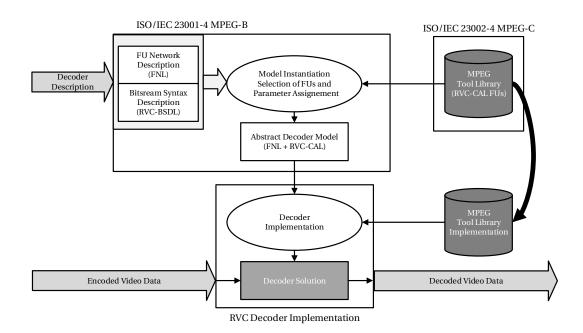

|   | 3.4  | Standardization                                                        |

|   | 3.5  | RVC-CAL Compiler Infrastructure                                        |

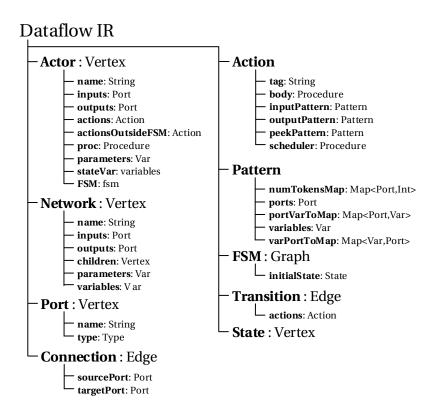

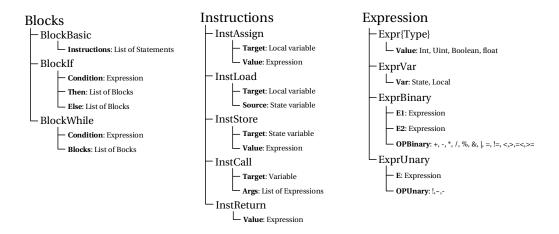

|   | 3.6  | Orcc Intermediate Representation                                       |

|   |      | 3.6.1 Dataflow IR                                                      |

|   |      | 3.6.2 Procedural IR                                                    |

|   |      | 3.6.3 Visitors for Dataflow and Procedural IR and IR Interpreter 54    |

|   | 3.7  | Conclusion                                                             |

| 4 | Higl | n-Level Synthesis of Dataflow Programs: Xronos 57                      |

|   | 4.1  | Introduction                                                           |

|   | 4.2  | Advances on the Orcc compiler infrastructure for Hardware Synthesis 59 |

|   |      | 4.2.1 Control Flow Graph Construction 61                               |

|   |      | 4.2.2 Dominance Graph                                                  |

|   |      | 4.2.3 Reaching Definition                                              |

|   |      | 4.2.4 Live Variable Analysis                                           |

|   |      | 4.2.5 Single Static Assignment, Pruned Form 65                         |

|   | 4.3  | Procedural IR Transformations                                          |

|   |      | 4.3.1 Expression Evaluator/Simplification                              |

|   |      | 4.3.2 Single Read and Write Register Optimization 67                   |

|   |      | 4.3.3 Uninitialized Variables                                          |

|   |      | 4.3.4 Constant Folding/Propagation 69                                  |

|   |      | 4.3.5 Dead Code Elimination                                            |

|   |      | 4.3.6 Type Casting                                                     |

|   |      | 4.3.7 Division and Modulo Implementation                               |

|   | 4.4  | Pipelining                                                             |

|   | 4.5  | Actor's Action Selection Procedure                                     |

|   |      | 4.5.1 Construction of the <i>Action Selection</i> Procedure            |

|   | 4.6  | CDFG Representation of a Procedure                                     |

|   | 4.7  | Language Independent Model (LIM)                                       |

|   |      | 4.7.1 Component                                                        |

|   |      | 4.7.2 Primitives                                                       |

|   |      | 4.7.3 Operation                                                        |

|   |      | 4.7.4 Memory                                                           |

|   |      | 4.7.5 Module                                                           |

|   |      | 4.7.6 Design                                                           |

|   |      | 4.7.7 Clock Domains                                                    |

|   |      | 4.7.8 Scheduling                                                       |

|   | 4.8  | Mapping of Dataflow and Procedural IR to LIM                           |

|   |      |                                                                        |

|   |            | 4.8.1 Network construction and Actor to Design                                                                         | 89                |

|---|------------|------------------------------------------------------------------------------------------------------------------------|-------------------|

|   |            | 4.8.2 State variable to Memory Allocation                                                                              | 89                |

|   |            | 4.8.3 Action to Task                                                                                                   | 90                |

|   |            | 4.8.4 Operation to Node                                                                                                | 90                |

|   |            | 4.8.5 Expression to CDFG                                                                                               | 90                |

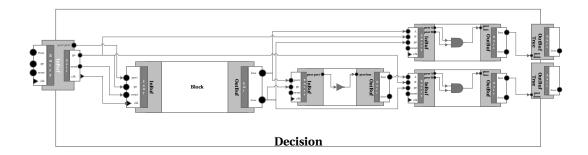

|   |            | 4.8.6 BlockBasic to Block                                                                                              | 92                |

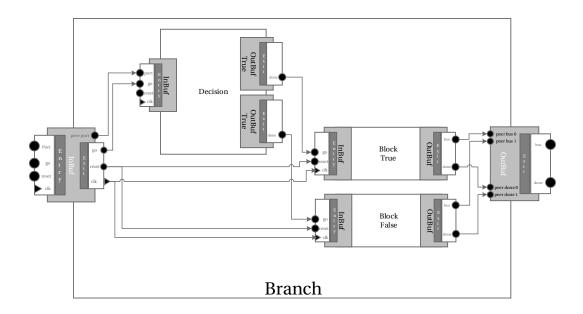

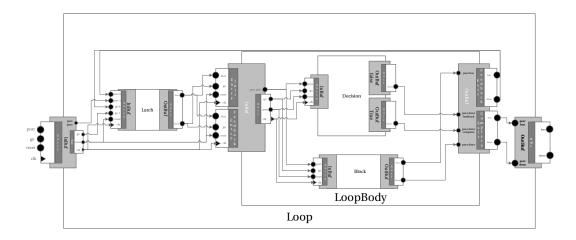

|   |            | 4.8.7 BlockIf to Branch and BlockWhile to Loop                                                                         | 92                |

|   |            | 4.8.8 CDFG to Block                                                                                                    | 93                |

|   |            | 4.8.9 Behavioral HDL Code Generation                                                                                   | 93                |

|   | 4.9        | Xronos SystemC Code Generation                                                                                         | 95                |

|   |            | 4.9.1 SystemC Actor Template                                                                                           | 96                |

|   |            | 4.9.2 SystemC Actor Composition Template                                                                               | 98                |

|   | 4.10       | Xronos C++ Code Generation for Embedded Platforms                                                                      | 100               |

|   | 4.11       | Mapping HW-SW and Interface Synthesis                                                                                  | 104               |

|   | 4.12       | TestBench Generation and Profiling Data Extraction                                                                     | 105               |

|   | 4.13       | Experimental Results                                                                                                   | 107               |

|   |            | 4.13.1 StreamBench: a benchmark suite for streaming applications                                                       | 108               |

|   |            | 4.13.2 Xronos versus state-of-the-art RVC-CAL to hardware synthesis                                                    | 113               |

|   |            | 4.13.3 Multi-core performance on an embedded platform                                                                  | 115               |

|   |            | 4.13.4 Hardware and Software Co-Design on Heterogeneous platforms                                                      | 116               |

|   | 4.14       | Conclusion                                                                                                             | 117               |

| 5 | Itera      | ative Design Space Exploration for Xronos                                                                              | 119               |

| Ū | 5.1        | Introduction                                                                                                           |                   |

|   | 5.2        | Profiling and Execution Trace Garph                                                                                    |                   |

|   |            | Model of Architecture, Mapping and Constraints                                                                         |                   |

|   |            | ETG Analysis                                                                                                           |                   |

|   |            | 5.4.1 Critical Path Evaluation                                                                                         |                   |

|   |            | 5.4.2 Impact Analysis                                                                                                  |                   |

|   |            | 5.4.3 Queue Size Minimization                                                                                          |                   |

|   | 5.5        | ETG Post-Processor                                                                                                     |                   |

|   |            | 5.5.1 An event-based trace simulator                                                                                   |                   |

|   |            | 5.5.2 Performance Estimation                                                                                           |                   |

|   |            | 5.5.3 Mapping                                                                                                          |                   |

|   | 5.6        | Optimization by Design Refactoring in IDSE                                                                             |                   |

|   |            |                                                                                                                        |                   |

|   |            | 5.6.1 Levels of parallelism                                                                                            | 134               |

|   |            | 1                                                                                                                      |                   |

|   |            | 5.6.2 Complexity and issues of automating refactoring optimizations                                                    | 134               |

|   | 5.7        | 5.6.2 Complexity and issues of automating refactoring optimizations 5.6.3 A refactoring strategy using impact analysis | 134<br>135        |

|   | 5.7<br>5.8 | 5.6.2 Complexity and issues of automating refactoring optimizations                                                    | 134<br>135<br>137 |

### **Contents**

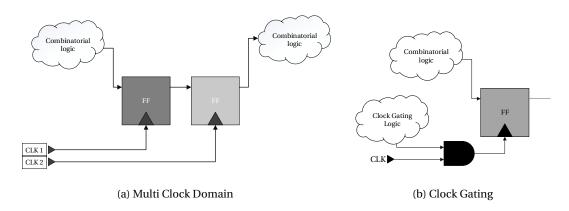

| 6  | Pow    | er Opt | imization                                                             | 141 |

|----|--------|--------|-----------------------------------------------------------------------|-----|

|    | 6.1    | Introd | luction                                                               | 141 |

|    | 6.2    | Clock  | buffers on Xilinx FPGA's                                              | 143 |

|    | 6.3    | Coars  | e-Grain Clock Gating Strategy                                         | 145 |

|    |        | 6.3.1  | Clock enabling controller                                             | 146 |

|    |        | 6.3.2  | Clock Enabler Circuit                                                 | 146 |

|    | 6.4    | Exper  | imental Study                                                         | 149 |

|    | 6.5    | Concl  | usion                                                                 | 152 |

| 7  | Con    | clusio | n and Future Work                                                     | 153 |

|    | 7.1    | Concl  | usion and Summary                                                     | 154 |

|    | 7.2    | Futur  | e Work                                                                | 157 |

|    |        | 7.2.1  | Component Library Database                                            | 157 |

|    |        | 7.2.2  | SDC Scheduling for LIM                                                | 158 |

|    |        | 7.2.3  | Integration of state of the art procedural optimizations              | 158 |

|    |        | 7.2.4  | Memory Partitioning                                                   | 159 |

|    |        | 7.2.5  | Multi-Actor hierarchical memory management                            | 159 |

|    |        | 7.2.6  | Multiplexing and De-multiplexing queue channels for heterogeneous     |     |

|    |        |        | targets                                                               | 159 |

|    |        | 7.2.7  | Clock Gating on input conditions and Multi-Clock Domains Partitioning | 160 |

|    |        | 7.2.8  | Dataflow Machines: An alternative Intermediate Representation         | 160 |

| Bi | bliog  | graphy |                                                                       | 176 |

| Cı | ırricı | ulum V | Vitae                                                                 | 177 |

# **List of Figures**

| 1.1  | Simplified design now of a flatdware and Software neterogeneous system              |    |

|------|-------------------------------------------------------------------------------------|----|

| 1.2  | RVC-CAL Design Flow. Two directional flows, in <i>black</i> top to down implementa- |    |

|      | tion and in <i>grey</i> the iterative feedback                                      | 7  |

| 2.1  | Gajski's Y-Chart, for different types of synthesis                                  | 11 |

| 2.2  | Generic FPGA architecture.                                                          | 13 |

| 2.3  | Slice found on Virtex-4 FPGAs                                                       | 14 |

| 2.4  | Xilinx DSP48E1 (image courtesy of Xilinx Inc.)                                      | 14 |

| 2.5  | Xilinx Zynq 7000 Architecture (image courtesy of Xilinx)                            | 15 |

| 2.6  | A generic High-Level Synthesis Flow.                                                | 15 |

| 2.7  | The CMU design system, one of the earliest HLS                                      | 17 |

| 2.8  | Three of the most used third generation HLS in the market. The three of them        |    |

|      | focuses on HLS for ASICs. Catapult and recently CyberWorkbench offers also          |    |

|      | FPGA support                                                                        | 19 |

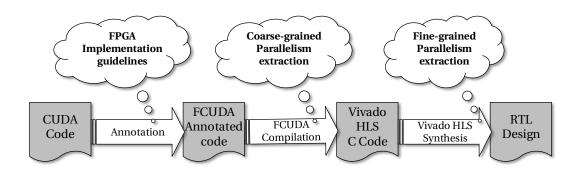

| 2.9  | FCUDA: CUDA to FPGA Flow                                                            | 21 |

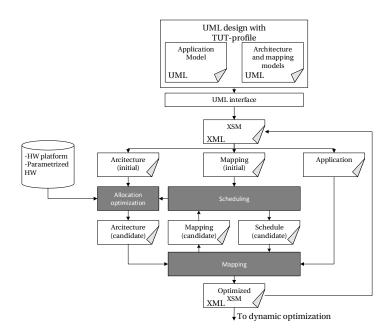

| 2.10 | Koski a UML based Design Flow for HW-SW prototyping                                 | 22 |

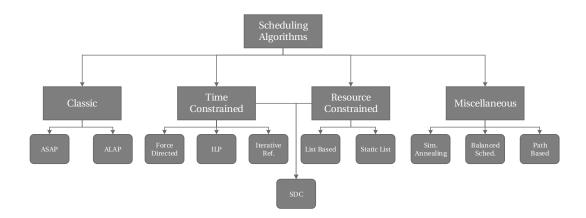

| 2.11 | Classification of the most known scheduling algorithms                              | 23 |

| 2.12 | Matlab HDLCoder HLS tool                                                            | 29 |

| 2.13 | Daedalus Design Flow a unified environment for rapid system-level architectural     |    |

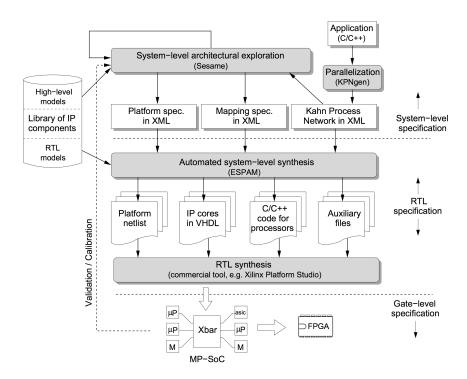

|      | exploration                                                                         | 30 |

| 3.1  | RVC-CAL as the Behavioral Description in the Design Flow                            | 33 |

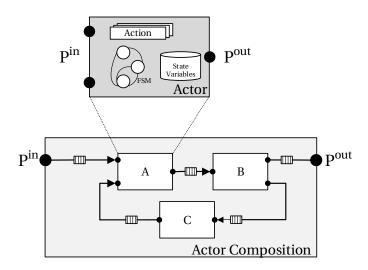

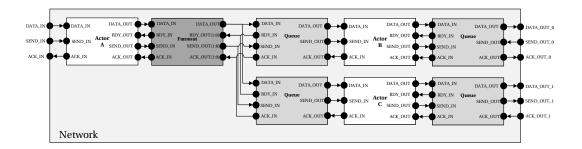

| 3.2  | Actor Composition and Actor Structure                                               | 40 |

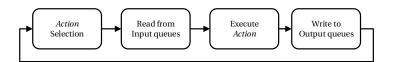

| 3.3  | Actor Execution Model                                                               | 42 |

| 3.4  | Reconfigurable Video Coding.                                                        | 48 |

| 3.5  | Open RVC-CAL Compiler Infrastructure                                                | 49 |

| 3.6  | Class tree for Blocks, Instruction and Expression classes of the Procedural IR      | 51 |

| 3.7  | Class tree for Blocks, Instruction and Expression classes of the Procedural IR      | 52 |

| 4.1  | Xronos in the Design Flow.                                                          | 58 |

| 4.2  | Detailed Xronos Compiler Infrastructure, white boxes indicates personal contri-     |    |

|      | butions                                                                             | 60 |

| 4.3  | Single Read and Write Register Optimization. Only a single read and a single        |    |

|      | write for a, b, and c state variables                                               | 68 |

### **List of Figures**

| 4.4  | Constant Propagation (CP) and Constant Folding (CF)                                   | 69  |

|------|---------------------------------------------------------------------------------------|-----|

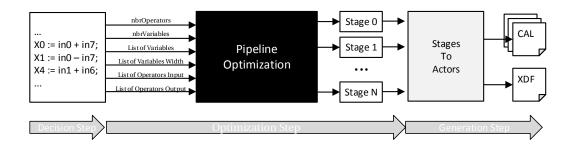

| 4.5  | Pipelining Optimization, from decision to generation                                  | 72  |

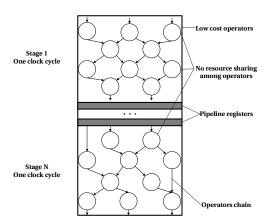

| 4.6  | One clock per stage pipeline scheduling with chaining and without sharing             |     |

|      | resources                                                                             | 73  |

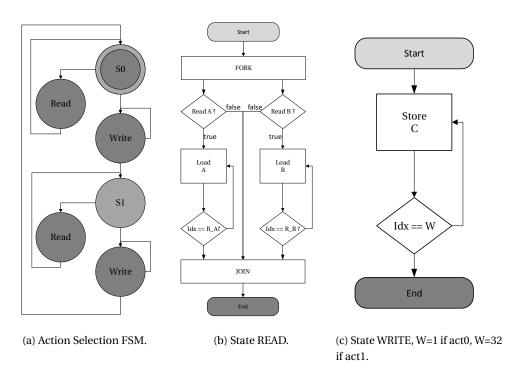

| 4.7  | Finite State Machine of Action Selection                                              | 74  |

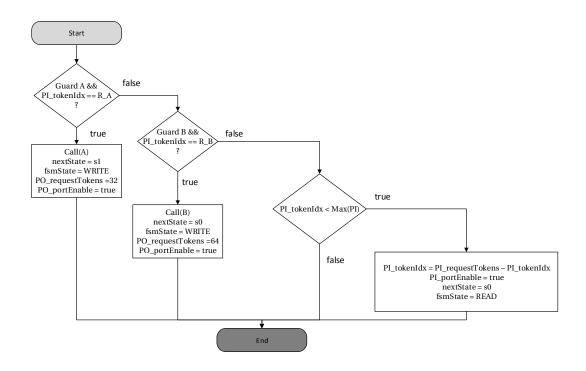

| 4.8  | Foo actor Action Selection                                                            | 76  |

| 4.9  | A State that contains two transitions                                                 | 78  |

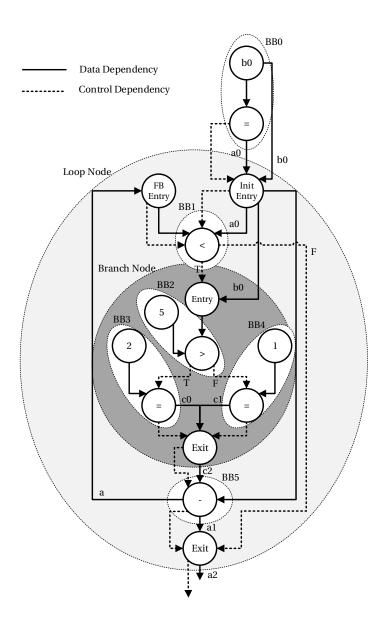

| 4.10 | Partial CDFG of the Listing 4.3                                                       | 80  |

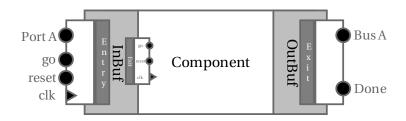

| 4.11 | LIM Component                                                                         | 81  |

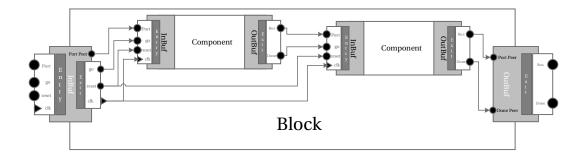

| 4.12 | A $Block$ with two components that they are execute one after the other               | 84  |

| 4.13 | A Decision Module                                                                     | 85  |

| 4.14 | A <i>Branch</i> with a true and a false part that both of them does not have an input |     |

|      | port. The decision input is connected to a data dependency from the peer bus of       |     |

|      | the Branch input port to its input port. The Branch has an exit with two control      |     |

|      | dependencies, 0 from the Exit's Done of the true Block and 1 from the false Block.    | 85  |

| 4.15 | A <i>Loop</i> Module, that contain a WhileBody                                        | 86  |

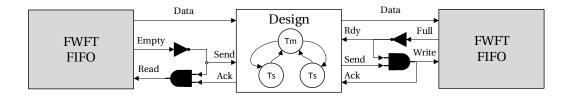

| 4.16 | Design I/O Fifo Interface                                                             | 87  |

| 4.17 | Network representation of three Actors. The Actor A's output port is connected        |     |

|      | to the input of Actor B and Actor C. It is woth mentioning that if an output port     |     |

|      | is connected to more than one input port a fanout is added. As depicted, each         |     |

|      | connection has its proper queue                                                       | 95  |

| 4.18 | Internal Modules Representation of the Actor Acc of Listing 4.4                       | 96  |

| 4.19 | Header file of the SystemC inverse quantification actor                               | 98  |

| 4.20 | Action Selection process of the inverse quantification actor                          | 99  |

|      | ,                                                                                     | 105 |

|      | 1 3                                                                                   | 105 |

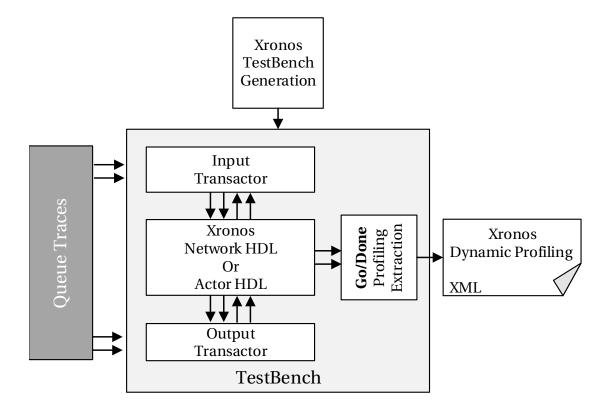

| 4.23 | Xronos TestBench and Profiling                                                        | 106 |

| 4.24 | Load and Store Instruction Reduction after Single Read and Write Register Pro-        |     |

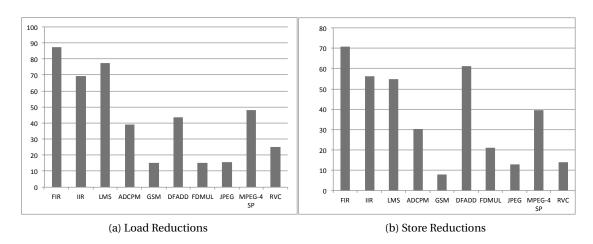

|      | cedural IR Optimization                                                               | 111 |

|      | • •                                                                                   | 112 |

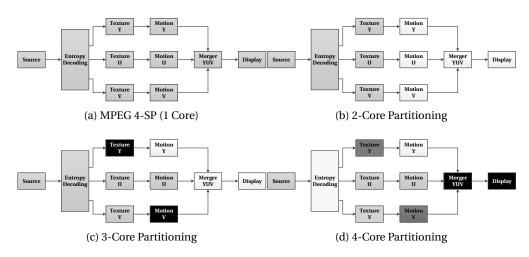

| 4.26 | The RVC MPEG 4 SP decoder and its partitioning from 1 to 4 cores                      | 15  |

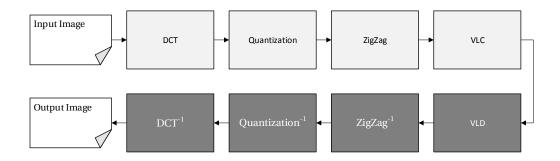

| 4.27 | JPEG codec functional units and the partitioning for the platforms                    | 16  |

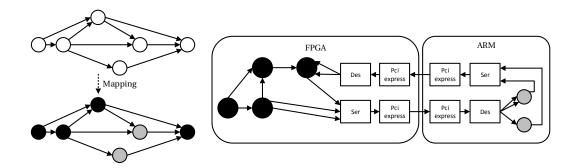

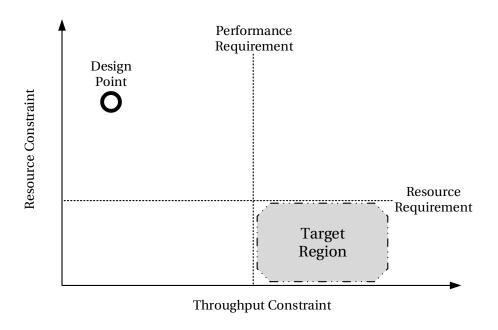

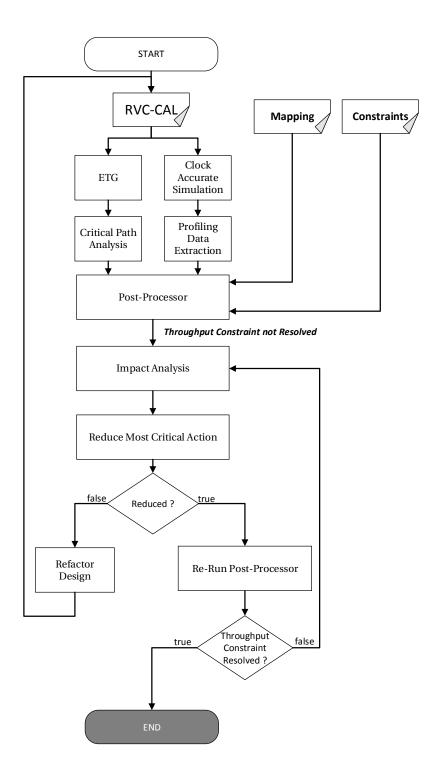

| 5.1  | Iterative Design Space Exploration on the RVC-CAL design flow by using TURNUS.        | 19  |

| 5.2  | Representation of the design space according to two constraints                       |     |

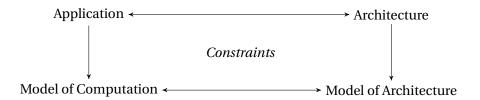

| 5.3  | Mapping from an application to an architecture. Constraints represent the             |     |

|      |                                                                                       | 123 |

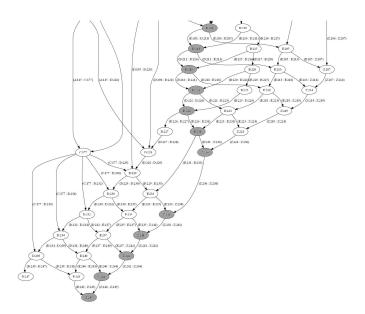

| 5.4  | Critical Path on partial execution trace graph                                        | 124 |

| 5.5  |                                                                                       | 126 |

| 5.6  | •                                                                                     | 128 |

| 5.7  | Atomic Actor FSM                                                                      | 130 |

| 5.8  | Post-Processor Mapping of a heterogeneous platform.                                   | 33  |

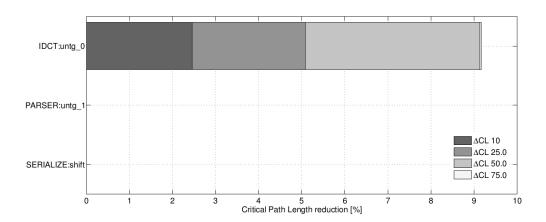

| 5.9  | Iterative Design Space Exploration methodology.                                         | 136 |

|------|-----------------------------------------------------------------------------------------|-----|

| 5.10 | TURNUS analysis results.                                                                | 138 |

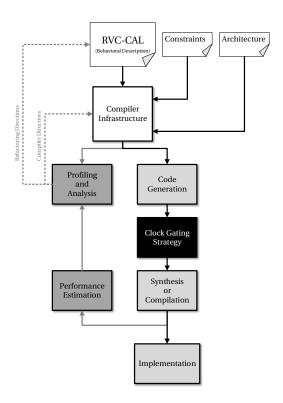

| 6.1  | Clock-Gating Strategy applied in the Design Flow                                        | 141 |

|      | Power Reduction Strategies                                                              |     |

|      | View of an FPGA die, clocking trees and different clocking buffers found on a           | 112 |

|      | Xilinx 7 family                                                                         | 144 |

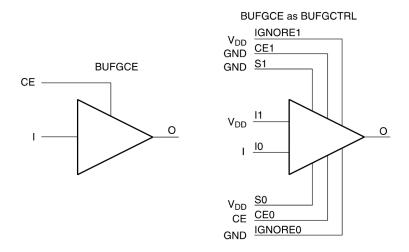

| 6.4  | Xilinx BUFGCE primitive for user clock gating                                           | 144 |

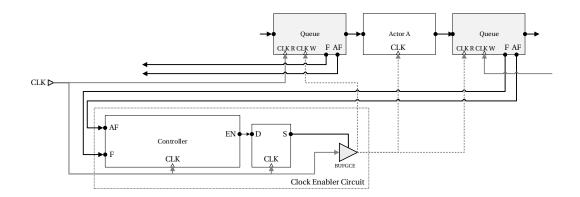

| 6.5  | Clock gating methodology strategy for Actor A with one output port. The Clock           |     |

|      | Enabler has as inputs the Almost Full and Full signal of each queue and a clock         |     |

|      | from a clock domain, and as a result it is going to activate or deactivate the clock    |     |

|      | of Actor A depending the FSM state of the controller                                    | 146 |

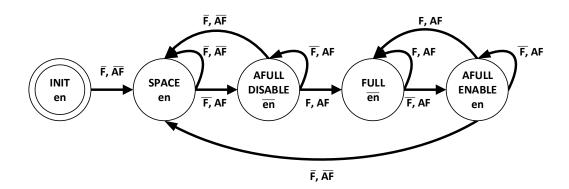

| 6.6  | State machine of the clock enabling controller. The controller has two inputs, <b>F</b> |     |

|      | for full, <b>AF</b> for almost full and one output <b>en</b> as the enable signal       | 147 |

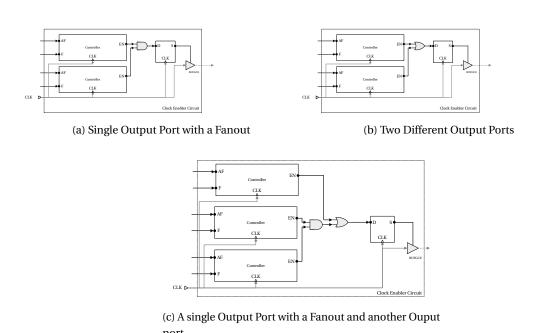

| 6.7  | Clock Enabler Circuit in three different configurations                                 | 147 |

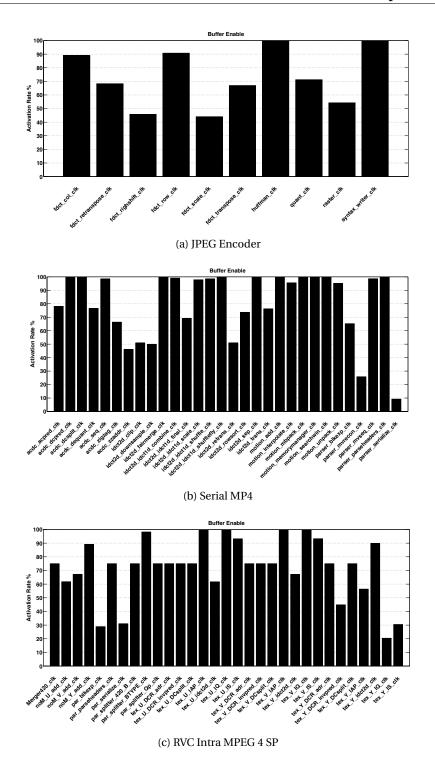

| 6.8  | Activation rates of each CG clock for each design with all their actors being clock     |     |

|      | gated. Average values retrieved from different QCIF input stimuli for all designs.      | 151 |

# **List of Tables**

| 3.1        | System-Level Requirements and Coverage. With Supported, partially supported, and Onot supported        | 35  |

|------------|--------------------------------------------------------------------------------------------------------|-----|

| 3.2        | CAL lexical tokens                                                                                     | 43  |

| 4.1        | Xronos features versus the state of the art. The contributions of this thesis is                       |     |

|            | related to the high-level synthesis of dataflow programs which are highlighted in                      | =0  |

|            | bold.                                                                                                  | 59  |

| 4.2        | Algebraic identities for Expression Simplificator. With $\wedge$ and logic and operator,               | 67  |

| 4.2        | and $\bigvee$ or logic or operator                                                                     | 67  |

| 4.3        | Lest Upper Bound on Types                                                                              | 70  |

| 4.4<br>4.5 | Brief description and source of the Streambench benchmark RVC-CAL programs Program Characteristics - 1 | 110 |

| 4.6        | Program Characteristics - 2                                                                            | 110 |

| 4.7        | Xronos HLS - Synthesis and Simulation Results                                                          | 111 |

| 4.8        | Xronos C++ Code generation Throughput results in Zynq 7045 ARM with a                                  | 111 |

| 1.0        | frequency of 999MHz.                                                                                   | 112 |

| 4.9        | Three-way comparison of the same RVC Intra MPEG-4 SP decoder on a Virtex                               |     |

| 1.0        | 4 FPGA, using the old Orc2HDL framework with the M2M source to source                                  |     |

|            | transformation, Xronos with the M2M and Xronos. (All results are post-place-                           |     |

|            | and-route, using Xilinx XST.)                                                                          | 114 |

| 4.10       | Xronos versus Orcc C backend + Vivado HLS, synthesis and throughput results                            |     |

|            | on Virtex 4 FPGA                                                                                       | 114 |

| 4.11       | Framerate of the RVC MPEG-4 SP decoder at QCIF, SD and HD resolutions                                  | 115 |

| 4.12       | Framerate of the JPEG codec with a 512x512 video resolution on P4080 and two                           |     |

|            | FPGA boards with 2 different interfaces                                                                | 117 |

| 5.1        | Initial Critical Actions Ranking. E%: number of executions of the action as a percent-                 |     |

| 0.1        | age of the total number of steps in the profiled run, CL%: computational load as a share               |     |

|            | of the total load, CPE%: the number of executions of that action on the critical path as a             |     |

|            | share of its length, CPP%: the share of the computational load of those executions on                  |     |

|            | the critical path relative to its total load                                                           | 137 |

| 5.2        | The modifications steps by most critical actor on the MPEG4 SP decoder. Syn-                           |     |

|            | thesis results for Xilinx Virtex 4 FPGA                                                                | 138 |

|            |                                                                                                        |     |

6.1 Synthesis and power results of three designs, a JPEG encoder, the RVC Intra MPEG 4 SP decoder and a full serial mpeg 4 sp decoder. The dynamic power reduction is given as the clock gated design over the non clock gated one. . . . 150

## 1 Introduction

This thesis reports the research work done by the candidate with the aim of yielding a complete high level synthesis (HLS) design flow entirely based on a dataflow computation paradigm that includes functionality and optimizations supporting heterogeneous system designs. Despite continued scaling of silicon technology, individual sequential processors are not becoming faster. Thereupon, rather than building complex single processors, manufacturers have used the space gained from scaling the technology by adding more processors and incorporating reconfigurable parts onto a single chip. Thus, making multi-core and reconfigurable machines a nearly ubiquitous commodity in a full (and increasing) range of computing applications. Therefore, the performance gains of modern heterogeneous platforms are primarily due to an increase in the available parallelism. However, one of the main obstacles that may prevent the efficient usage of heterogeneous platforms is the fact that the traditional sequential specification formalisms and all existing software and IPs, legacy of several years of the continuous successes of the sequential processor architectures, are not the most appropriate starting point to program such parallel platforms. Moreover, such specifications are no more suitable for unified specifications when targeting both processors and reconfigurable hardware components. Another problem is that portability of applications on different platforms becomes a crucial issue, and such property is not appropriately supported by the traditional sequential behavioral description and associated methodologies.

### 1.1 Design of Complex Systems

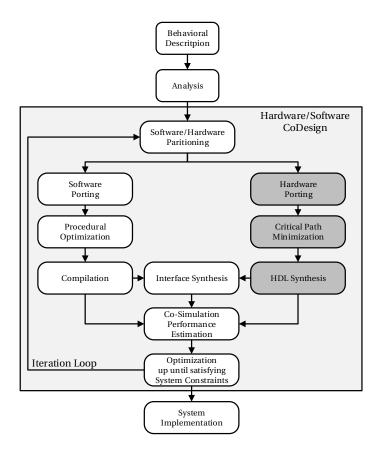

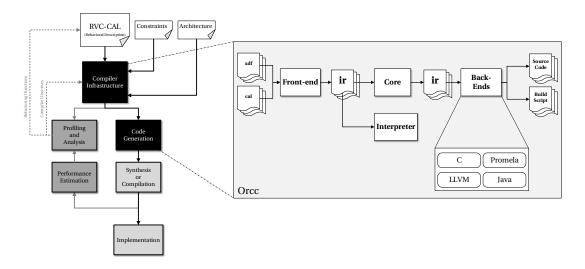

The availability of heterogeneous parallel platforms that combines the processing features of FPGAs with multi-core CPUs in a single silicon die offers a potential amount of computing power for embedded designs. That by far exceeds what was available in the past years. However, such possibility can only be fully used if design flows can support heterogeneous architectures. Figure 1.1 depicts a typical Co-Design design flow. The design flow starts by choosing a behavioral description for implementing a chosen algorithm. A preliminary analysis for such a design flow is to decide which parts of the algorithm should be ported in either software and/or hardware processing elements. All relevant information has to be extracted

Figure 1.1 - Simplified design flow of a Hardware and Software heterogeneous system

from the behavioral description of several thousand source code lines. This initial step of the design flow has an enormous impact on the necessary optimization iteration needed to satisfy the system constraints for the final target implementation.

The selection of the parts of the algorithm to be implemented by software, or hardware components is a fundamental step that has serious consequences of the other steps of the design flow. In fact, algorithmic parts for SW processing elements require to be revised (i.e. rewritten) according to platform specific SW optimization objectives. The other parts selected for execution on hardware components (i.e., FPGA or ASIC) need to undergo different, even more tedious, heavy transformations because specific timing constraints, that greatly affects the quality and required expressiveness of the HDL description, need to be explicitly introduced. In general, the optimization process of the hardware elements consists of reducing the critical path of the circuit. The critical path of a circuit is defined as the longest combinatorial path between two registers. This path represents the frequency of the circuit. Once the timing constraints are satisfied, then an interface need to be implemented for connecting the hardware and software components. An interface is characterized by two factors: its availability of it on the processing element and the interface bandwidth. Once all the system

parts are complete, then the first iteration of co-simulation begins and can give indications of an achievable performance for the developed design.

If the co-simulation results do not satisfy the defined constraints of the system, then parts of software and hardware elements should migrate from one to the other. An additional problem may also occur on the interface bandwidth or its handling. As a consequence, the design space points explode. In addition, if an initial partition is chosen poorly then the number of optimization iteration might increase rapidly. Finally, if a design space point is found that satisfies the constraints, then the system is implemented on the chosen target.

#### 1.2 Problem Statement and Motivation

As stated, the porting of software and hardware part is difficult and a tedious work. A behavioral description must be capable of abstracting the architecture characteristics and must encompass both hardware and software design concepts. Today current design flows requires completely different abstractions for each processing element.

In addition, the average design time necessary for developing and optimizing designs for heterogeneous platforms is, as a result, much higher due to the separation of work in hardware and software parts. A common practice is to partition "a priori" a part of the design to be executed by the CPU and then discover that it does not satisfy the system constraints. In this case, it is necessary to rewrite from scratch a part of the design and rewrite it in a way that it can be executed on the hardware component of the platform. The drawback of the approach is that the two successive specifications of the design, although expressing the same semantic behavior in terms of input and output data, have to make use of two different abstractions for being executed on programmable hardware or on a processing unit. Not only is such a work error-prone, but also the functional design verification should be effectuated by combining both parts. In summary, the main problems in heterogeneous system designs are flexibility and maintainability that both can be expressed as Design Abstraction, Reuse, and Modularity.

- **Design Abstraction**: What level of abstraction should be used for the specification, the design, and the implementation? In the case of heterogeneous platforms, the question is not trivial given the diverse nature of the platform. Different levels of abstraction may be employed depending on the nature and level of requirements and constraints. Thus, behavioral descriptions should be able to seamlessly express both parallel and sequential computation paradigms.

- **Modularity**: In modular design, such as dataflow designs, the system functionality is split into communicating components that divide the complexity of the overall application. The design abstraction should be able to support modularity as a data and task parallelism.

- Reuse: Design abstraction and the modularity of an application should permit the reuse

of components that can be described for hardware and software parts and at the same time allow the reuse of parts of the same application family. As an example, many audio codecs share part of the same functional units such as a direct cosine transform, which makes the modularity a necessity for a developer who maintains a library of audio codecs.

The essential difference between hardware and software is the execution model. In hardware everything is executed concurrently; conversely software follows a sequential memory based execution model which is derived from Turing machines. Sequential execution is very efficient in software but a bad choice for hardware in most of the cases. This has a serious implication when designing hardware from software programmers, their familiar algorithms are mostly expressed sequentially. Even thought multi-core and many-core platforms are evolving and becoming the mainstream in all computing devices (even low-cost ones), the last half of the century programmers codes sequentially. C and C-likes programming languages have conquered the sequential software programming, but today there is disagreement about the preferred parallel model of computation that takes on consideration of different parallel architectures. In addition, C or C-like languages have become the mainstream programming languages for heterogeneous computing. Many vendors provide high-level synthesis solutions based on C for the hardware part of their heterogeneous toolchain. As stated in [1], C and C-like languages have the following problems:

- Sequentiality: One fundamental problem with C-like High-Level Synthesis tools today is that they encourage the programmer to program algorithms sequentially with the promise that the tool has techniques that will automatically expose the parallelism of a sequential code. Unfortunately those techniques are limited to descriptions that contains few operation dependencies. Concurrency is either supported by libraries or pragmas or automatically detected by the tool, to use non standard C types and to deal with different communication issues. Although a lot of research has been done to support C features and make it as the default language for HLS, in the end all tools have a different implementation of C except some tools that supports a subset of ANSI C. Although SystemC is supporting all features above and it is a useful language for high-level synthesis it is not ideal for multi-core/many-core programming due to its library that is intentioned for circuit simulation. All these different implementation have lead the research community to develop languages based on model of computations that adapts to the hardware development specifics and parallel programming but also to be portable on different platforms.

- Language Limitations: Due to the C language concurrency limits, most HLS extends C with statements and/or parallel constructs, pragmas and libraries. Extending C with statements or adding non standardized constructs introduces a fundamental and farreaching change to the language which makes it incompatible with standard C compilers and other C HLS tools. A less intrusive way is to use tool specific pragmas. Finally, the

use of tool specific libraries locks the developer to a single tool which makes it very difficult for a company to switch HLSs.

• **Bitwise Types**: Each base type in C or C++ is one or more bytes stored in memory. C types can be implemented in hardware but types smaller than a byte can not be specified, expect for defining the number of bits in the field of a structure. HLS tools approach of supporting bitwise types is exactly the same as concurrency. They either change the C language or their provide proprietary libraries.

A potential candidate which is not limited only to hardware development is the CAL dataflow programming language. CAL offers the hardware developer the necessary constructs for expressing parallel and sequential code, bitwise types, a consistent memory model, and a lossless communication between parallel tasks through queues. Thus, CAL can be used as a single behavioral description for SW and HW processing elements. Most of all, CAL comes with a model of computation that enables the programmer to express applications as network processes. The following points describe the properties of CAL:

- Concurrency & Parallelism Scalability: In parallel programming, programs either scale with the size of the problem or with the size of the code. Developing concurrent parts of a program without much interference is a well known problem for von Neumann architectures. As a solution, the explicit concurrency of the actor model provides a parallel composition mechanism that tends to lead to more parallelism as the size of an application grows.

- Modularity: The hierarchical structure and the encapsulation of actors provides high

potential of parallelism. In addition, changing an actor will not have an impact on other

actors.

- **Scheduling**: Like procedural programming languages, actors offers a full control on the order of execution of actions (i.e. the imperative part of actors).

- **Portability**: For heterogeneous platforms portability is still en elusive goal. Using a single representation permits the maintainability and reuse of code between HW and SW processing elements.

CAL dataflow programming is a challenging programming paradigm, it offers a flexible development approach to deal with the increasing complexity of the applications, and offers a large degree of parallelism to exploit the massive parallel capabilities available in modern architectures. The use of a programming language based on the dynamic dataflow model is more advantageous compared to static approaches. This is due to the fact that the developer can be more flexible when expressing their design. Dynamicity, facilitates the conception of complex applications with non-constant data structures. Moreover, these dynamic dataflow

languages offer a large expressive power along with a practical syntax that are both required for an industrial-scale development.

**Thesis:** Dataflow Programming contains the necessary features for heterogeneous computing that circumvent the imperative (MoC) limitations of C or C-like programming language because it offers **abstraction**, **concurrency**, **modularity**, **analyzability** and **portability** for different processing elements.

To support this statement this dissertation provides the following contributions:

- 1. A High-Level Synthesis solution of dataflow programs for heterogeneous platforms.

- 2. System methodologies for optimization of implementations at high abstraction level.

- 3. An iterative design space exploration with the purpose to minimize the initial partitioning and assignments to software and hardware processing elements.

- 4. A design flow supporting all the above features.

Moreover, the thesis describes the implementation of the integrated high-level design flow that embeds new features, optimization tools, and methodological advances into an integrated open source HLS solution for programming heterogeneous platforms. The complete environment called Xronos is available under open source license at: https://github.com/orcc/xronos and has been used by two European projects (ACTORS and VAMPA) and research groups such as INSA of Rennes, Lund University, University of Oulu, University of Cagliari, and Harriot Watt University.

### 1.3 Design Flow for Dataflow Programs

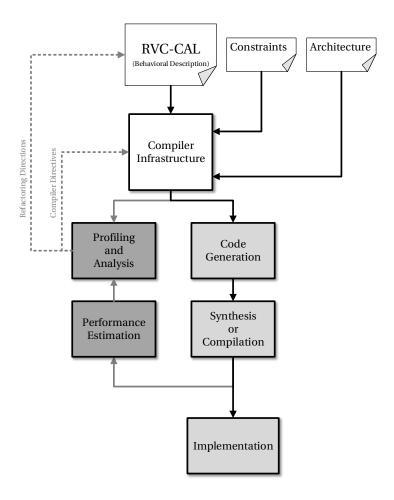

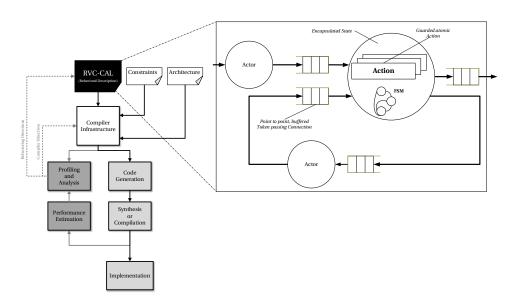

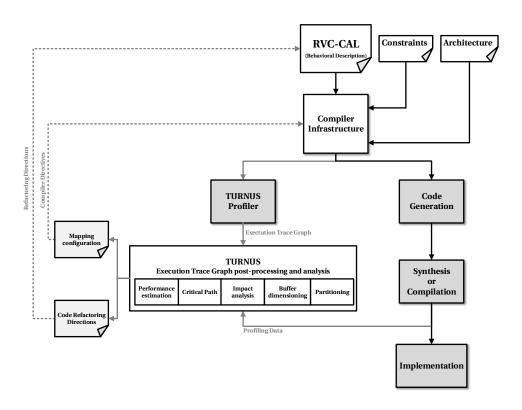

The architecture of the high-level synthesis design flow and associated design space exploration that offers a complete design flow methodology for programming heterogeneous platforms is illustrated in Figure 1.2. A design contains a set of stages by which, from an abstract representation of the application (i.e. the dataflow program), it is possible to accomplish the synthesis of an integrated circuit or the implementation onto a SW processing unit, or any combination of both elements. Each stage is composed by a single tool or the integration of a composition of tools.

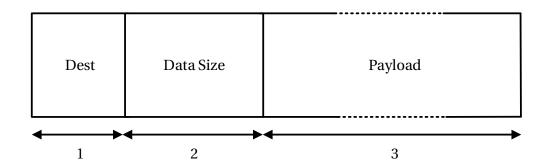

The RVC-CAL design flow is composed by eight stages. The stages are respectively:

1. **Behavioral Description, Architecture, and Constraints**: The design is expressed by the RVC-CAL dataflow programming language based on process network principles. The architecture defines on which kind of platform the design is implemented. The architecture contains operators, media, and links. An operator defines the type of the

Figure 1.2 – RVC-CAL Design Flow. Two directional flows, in *black* top to down implementation and in *grey* the iterative feedback.

processing element; the media defines the way that this platform is communicating, and the links are the connection between operators and media. In addition, the constraints are applied to the architecture and defines the clocking for each operator and the input and output data consumption and production of the design.

- Compiler Infrastructure: The abstract design specification is verified for algorithmic

correctness. The design can also be statically profiled for complexity analysis and for

identifying the longest computational path occurring when a set of input vectors are

processed.

- 3. **Code Generation**: According to the architecture defined at the abstract level, the code generation stage generated the source code for execution on the SW architecture and HDL code for configuring the HW architectures, FPGAs and/or ASICs.

- 4. Synthesis or Compilation: Generates code which is then synthesized or compiled using

standard tools to obtain software executables and/or hardware binary files/netlists for physical implementations.

- 5. **Performance Estimation**: At this stage platform specific software profilers and/or HDL testbenches are used to measure the performance of individual dataflow processing components.

- 6. **Analysis & Profiling**: At this stage, the design bottlenecks are iteratively identified and analyzed. Initially, in the early phase of the design process, the buffer size for the different dataflow elements, the memory defined in the architecture given by the constraints are estimated and allocated. In a second phase, a more in-depth design space exploration including all dataflow components is applied to the design and profiling information is extracted. For a software architecture, the design can be partitioned into different processing units according to an optimization objective functions for the given set of an input vector and design constraints. For hardware architectures, different multi-clock domain partitioning are identified with the goal for reducing power dissipation and respecting throughputs constraints. Finally, the performance of the composition of hardware and software architectures can be analyzed with the purpose of verifying the satisfaction of the overall system design constraints.

- 7. **Code Refactoring Directions and Compiler Directives**: After the Profiling & Analysis stage, feedback is provided on how the dataflow program components, at a high abstraction layer, should be modified to satisfy the design constraints.

- 8. **Implementation**: The structure of the design flow is composed by two main paths. The first is a direct path from the top to bottom linking the high-level dataflow program abstraction to the synthesized executable implementation and the second is the iterative system-level design exploration and optimization cycle.

The structure of the design flow is composed by two main paths. The first is a direct path from the top to bottom linking the high level dataflow program abstraction to the synthesized executable implementation and the second is the iterative system-level design exploration and optimization cycle.

### 1.4 Thesis Contributions and Organization

The main contributions and the publications (related to each original contribution) of the thesis can be summarized as follows:

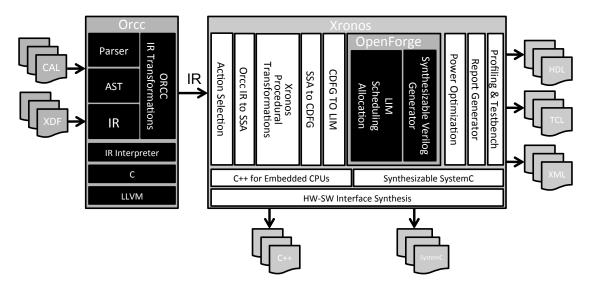

1. A high-level synthesis compiler infrastructure that supports the full specification of RVC-CAL dataflow programming language. The compiler infrastructure is based on two open source projects: Orcc for the RVC-CAL fronted, and OpenForge for the Verilog

backend. Research in [2, 3, 4, 5, 6] extends Orcc to a state-of-the-art compiler and provides the necessary transformations and optimizations to produce a close to hardware intermediate representation for OpenForge.

- 2. An Action selection algorithm for the actor execution model. Research in [3, 4] provides support for RVC-CAL "repeat" statements and guarded conditions on values of an input list. In addition, parallel read and write of list tokens for hardware synthesis accelerates the consumption and production of tokens.

- 3. Static and dynamic fine-grain profiling data extraction from RTL simulation of synthesized RVC-CAL dataflow programs [3, 7]. The structure of the generated code permits the extraction of timing profiling of the individual execution of each action.

- 4. A design flow that contains an iterative design exploration framework for RVC-CAL dataflow programs for heterogeneous embedded platforms (FPGA + multi-core CPU). Research in [8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18] offers a complete design flow for hardware and software from a single RVC-CAL behavioral description. In addition, the design flow includes an open source design space exploration tool that reduces the refactoring iterations for meeting the design constraints.

- 5. A clock gating strategy that reduces the dynamic power dissipation in synthesized circuits for processes that communicates through queues [19].

This dissertation is divided into six parts that represent each step of the design flow:

Chapter 2 describes the state of the art on the high-level synthesis and design flows for heterogeneous platforms. An introduction to different types of synthesis and a brief description of heterogeneous architectures is discussed. Moreover, the definition of high-level synthesis is provided as well as the high-level synthesis tools evolution. In addition, the state-of-the-art of principal high-level synthesis blocks such as scheduling, pipelining, and power optimization is given. Furthermore, the state of the art of design flow for co-design is also provided. The chapter concludes, by justifying why the RVC-CAL dataflow programming language is chosen for describing the behavioral description of the proposed design flow.

Chapter 3 Reports CAL and the standardized version of it the RVC-CAL. After that, examples that demonstrate the expressiveness of CAL are given. Furthermore, Orcc, the compiler infrastructure for RVC-CAL is presented and its Dataflow and Procedural Intermediate Representations are analyzed in depth.

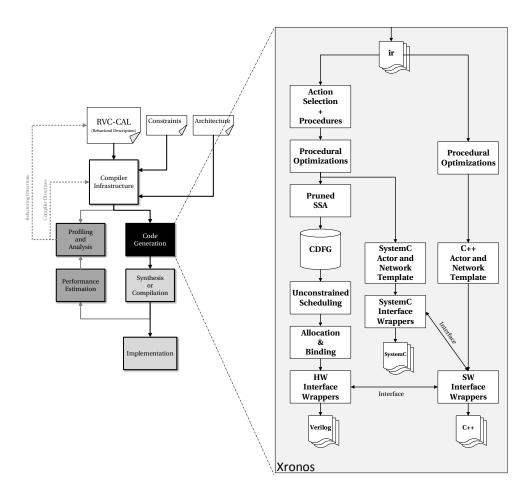

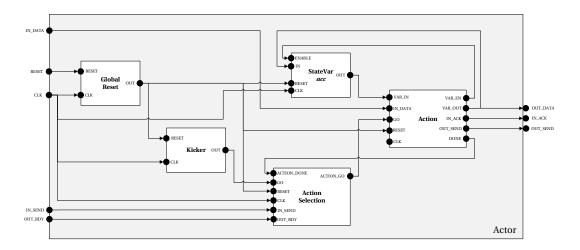

Chapter 4 describes Xronos the high-level synthesis and embedded software synthesis tool of dataflow programs for heterogeneous platforms. The evolution of Xronos tool is discussed. After that, the advancements and completion that were introduced to Orcc's compiler infrastructure for enabling hardware synthesis are covered. An analysis in depth is also given for the construction of the *Action Selection* procedure that allows a hardware friendly execution model of the actor transition system that support the concurrent reading and writing

#### **Chapter 1. Introduction**

of multi-tokens in actions. In addition, the Language Independent Model (LIM), a close to hardware intermediate representation, and the mapping of the Dataflow and Procedural IR to LIM is presented and examined. With the purpose to give a detailed overview of the Xronos synthesis process. Subsequently, the embedded software and synthesizable SystemC code generation are described. Finally, experimental results demonstrate the capabilities of the tool for behavioral synthesis and heterogeneous software and hardware synthesis.

Chapter 5 describes the TURNUS tool for the iterative design space exploration of dataflow programs. The chapter focuses on design exploration and optimization functionalities. It is also demonstrated how run-time profiling data is extracted from heterogeneous platforms. Design performance is estimated by the use of an execution trace post-processor. It is illustrated how estimation results are used in order to guide the optimization heuristic during the exploration phases. Furthermore, the concept of design space critical path is defined and used as primary metric of the optimization heuristics that are incorporated through TURNUS. Finally, the iterative design space exploration methodology is presented, and experimental results demonstrate the tool capabilities and its usefulness for optimizing the throughput of a dataflow program for hardware synthesis.

Chapter 6 describes a clock-gating strategy that reduces the dynamic power dissipation on systems described as processes that communicates through buffers. Moreover, the FPGA clocking architecture is given, and the kind of clock buffers used for enabling coarse-grain clock gating is described. Finally, experimental results demonstrate that the throughput of a particular design is not modified by the clock-gating strategy, and does not at all affect the design flow.

Finally, chapter 7 summarizes the thesis and highlights future work and potential improvements in the overall design flow for hardware, software, and interface synthesis.

## 2 State of the Art

### 2.1 Introduction

As the race of minimizing the transistor footprint close to a single atom still goes one, the number of transistor on future chip will furthermore increase. The need for new design automation methodologies on more abstract levels, where cost to market/functionality and trade-offs is easier to comprehend, is a must for developing future chips generations. Today, VLSI technology has reached maturity level, and it is well understood and no longer provides a competitive edge by itself [20]. The industry now is focusing at the product development cycle with the purpose to increase productivity, where high-level synthesis (HLS) plays a central role. Thus, enabling the automatic synthesis of high-level untimed or partially timed to low-level cycle-accurate RTL specifications for efficient implementation in reconfigurable hardware.

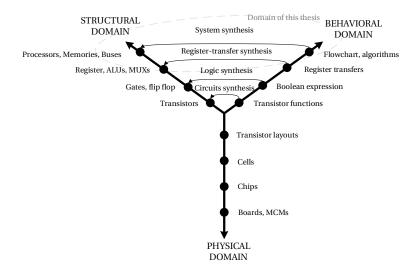

Figure 2.1 – Gajski's Y-Chart, for different types of synthesis.

Driven by this complexity, there has been a renewed interest (from 2000) in high-level synthe-

sis of digital circuits from behavioral descriptions. A key change that has taken place since HLS was first explored in the 70s is that now RTL languages such as Verilog and VHDL are widespread accepted. Design synthesis is a process that translates a behavioral description into a structural one. In [21, 20] Gajski and al. used the Y-chart (Figure 2.1), a tripartite representation of design. The axes in the Y-chart represents three different domains of description: behavioral, structural, and physical. Gajski describes that the level of description becomes more abstracts as we move farther away from the center of the Y-chart. So a design tool and what information is used by the tool can be represented as arcs along domain's axis or between the axes. Today, the industry masters solutions for both the structural and physical domains, but in behavioral domain of high-level synthesis there are still open problems that have not yet being fully solved. Despite the past failure of early generations of commercial HLS tool, there is a demand for high-quality HLS solutions for:

- An increasing silicon capacity: requires a higher level of abstraction. Design abstraction is one of the most effective method for controlling complexity, maintainability, reuse, modularity, and improving design productivity. A recent study [22] shows that code density can be reduced 7 to 10 times when moved from an RTL to a high-level C specification.

- Embedded processors in SoC: FPGA market leaders offers heterogeneous processors and reconfigurable logic on the same die. In addition, the programmable logic part offers digital signal processors (DSPs), memories and custom logic. That is to say, more software elements can be involved in the process of designing complex embedded heterogeneous systems. An HLS, included in a design flow, allows developers to specify functionality in high-level behavioral description for both embedded software and reconfigurable hardware. In other words, developers can quickly experiment software/hardware partitioning and explores trade-offs such as performance, area, and power from a single behavioral description.

- IP reuse: improves design productivity. As opposed to RTL Intellectual Property (IP) which has a fixed interface protocols and mirco-architecture, behavioral IP can be repurposed to different technologies (a greater range of FPGA families and constructors) or system requirements.

The rest of this chapter summarizes the state-of-the art of HLS and hardware and software design flows that partially solves the previous problems. In the following, the HLS tools generations through the years, and cites previous work that have been effectuated for each step in high-level synthesis flow. In addition, several dataflow design flows that permits the HW and SW co-Design are also cited. This chapter concludes on the need for a new behavioral description programming language that does not only fit for HLS but also for parallel architectures such as many cores/multi-cores and hybrid hardware and software architectures.

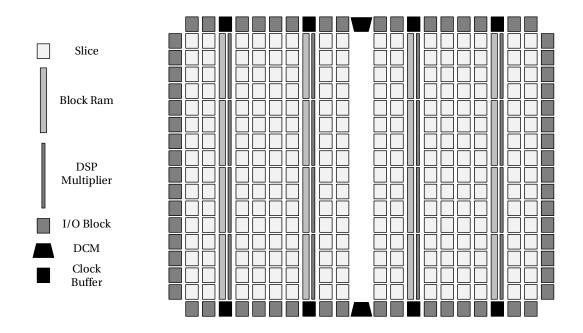

## 2.2 Heterogeneous platforms

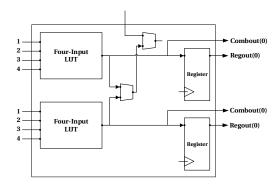

FPGA or Filed-Programmable Gate Array is an integrated circuit designed to be a reconfigurable circuit. The very first FPGA, the XC2064, was constructed by Xilinx and announced on November 1, 1985. An FPGA is essentially a matrix of logic cells called slices. A generic FPGA architecture is depicted in Figure 2.2. Slices, depicted in Figure 2.3, are connected among themselves with Input/Output (IO) blocks through routing channels. Therefore, they are distributed in the FPGA in horizontal and vertical form, and its connection are fixed using a programmable switch matrix.

Figure 2.2 – Generic FPGA architecture.

Each slice contains Look-Up Tables (LUT) and several Flip-Flops (FF) and programmable multiplexers (MUX). These elements vary for each FPGA family. General parallel circuits and complex functions are implemented in FPGA when these elements are associated among themselves. Also, FPGAs contains RAM blocks (BRAM) that can be configured in different combination and also acts as ROMs and hard-cabled arithmetic circuits. New Xilinx architecture have added the notion of Configurable Logic Block, which contains two kinds of Slices: SLICEM and SLICEL. SLICEL and SLICEM support LUTs, eight storage elements, widefunction multiplexers and carry logic. In addition, SLICEM supports two additional functions: storing data using distributed RAM (memory in LUTs) and shifting data with 32-bits registers. In Altera FPGAs, the equivalent to SLICE is called ALM or Adaptive Logic Module.

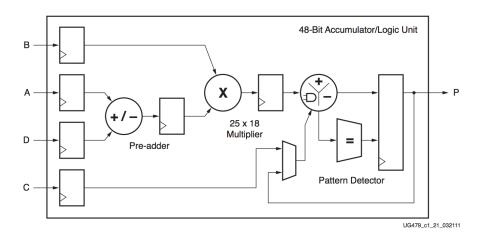

All new Xilinx FPGAs incorporate DSP48s arithmetic modules. A DSP48 slice has a two-input multiplier connected to multiplexers and a three-input adder/subtractor. The multiplier accepts two 18-bit, two's complement operands producing a 36-bit, two's complement result.

Figure 2.3 – Slice found on Virtex-4 FPGAs

The result is a sign-extended to 48 bits and can optionally be fed to the adder/subtractor. The adder/subtractor accepts three 48-bit, two's complement operands and produces a 48-bit two's complement result. In addition, Altera is adding cabled-circuit floating-point DSP in their FPGAs.

Figure 2.4 – Xilinx DSP48E1 (image courtesy of Xilinx Inc.)

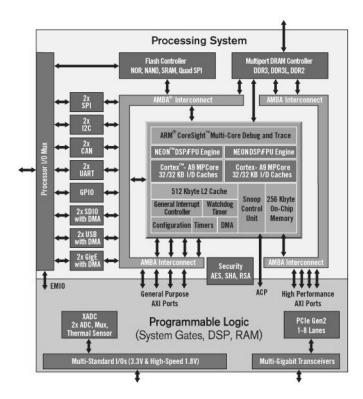

A new trend in both Xilinx and Altera is to add ARM cores along in the same die with the FPGA. The architecture of Xilinx Zynq 7000 is depicted in Figure 2.5 Both of them had already added PowerPC cores but back then, those FPGAs were too expensive, and they had a poor adoption. New Altera SoCss and Zynq FPGA have seen a great adoption by the open source community and companies for co-design applications. The design flow presented in Figure 1.2 fits these architectures perfectly because using a single behavioral description it is possible to target both the CPUs cores and the FPGA.

Finally, most of the commercial HLS tools supports both FPGA and Application Specific Integrated Circuit (ASIC) as a target architecture. An ASICs is an integrated circuit customized for a particular use that is not reconfigurable. Those ICs exists in different types such as Standard Cell, Full Custom ASIC, Gate-Array ASICs. It should be noted that the design flow

Figure 2.5 – Xilinx Zynq 7000 Architecture (image courtesy of Xilinx)

of this thesis is oriented for FPGAs, but it can also be applied with ASICs too. Even though, it has not been not verified by the author. The interested reader may consult the following references for more information on the ASIC architecture [23] and HLS for ASICs in [20, 24].

# 2.3 High-Level Synthesis

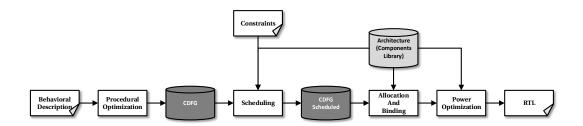

Figure 2.6 – A generic High-Level Synthesis Flow.

A High-Level Synthesis flow consists of a set of steps that from an abstract behavioral representation to a Register Transfer Layer netlist is created. The flow starts with a behavioral description, in which the designer specifies in a formal language the design algorithm. The next step is the compiler infrastructure that parses the behavioral description and produces a single or several Intermediate Representation(s) (IR) of it. In which the compiler is applying a

set of procedural optimizations for reducing and optimizing the description. One of the most used procedural optimization is the pipelining. The next is to create a graph called CDFG (Control-Data Flow Graph) which captures all the control and data-flow dependencies of the given IR. From this graph scheduling is applied. Scheduling is the process that partitions this CDFG into subgraphs so that each subgraph is executed in one control step by taking on account the designer's constraints applied to the behavioral description. Thus, then scheduling converts the behavioral description into a set of register transfers that can be described by an FSM. From the FSM it is derived the control step sequence and the conditions used to determine the following control step sequence, the data path is derived from each register transfer that is assigned to each control step. The datapath in the FSM is a netlist composed of three types of register transfer components such as functional, storage and interconnection. Functional units, such as adders, subtractors, shifts, multipliers etc., execute the operation that are specified in the behavioral description. Storage units, such as registers, RAMs, and ROMs, hold the values of variables generated and consumed during the execution. Interconnections units, such as buses and multiplexers, transports the data between functional units to other functional units and storage units to functional units. After that, allocation and binding follow. Allocation consists of selecting the number and types of components to be used in the design. Binding involves the mapping of the variables and operations in the scheduled CDFG into function, storage, and interconnection units. The next step that is optional, and not effectuated by all HLS is the power optimization. The power optimization optimizes the dynamic and static power dissipation(if an ASIC is the target architecture). The dynamic power dissipation is caused by transistors switching, and as a result charges are being moved along wires. The static is the outcome of the current leakage of the transistors. Power optimization is either optimizing both kinds of dissipations or only the dynamic one. Finally, an RTL netlist is generated by the HLS. The final step of the design is the interfacing of the RTL netlist, and the logic synthesis is applied to the final implementation.

#### 2.3.1 HLS tools evolution

Grant Martin and Gary Smith on [25] have divided the evolution of High-Level Synthesis into three generation and a primal one. The current generation is the third, and most of the tools are C based (including C++ and SystemC). Late 1970s up until 1980s is the primal period, first generation is from 1980s to 1990s, second generation goes from mid-1990s to early 2000s and the third from early 2000s to today.

The first generation was oriented mainly on data-path research. The second generation, mainly commercial products were driven by high description languages (HDL). Third and current generation follows the trend of C-based HLS oriented on datapath applications.

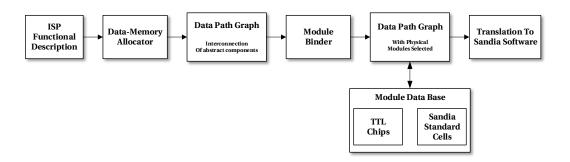

The pioneer tool in "primal" period is the Carnegie-Mellon University design automation or CMU-DA HLS. The design flow is represented in Figure 5.4 and was built by Carnegie Mellon University in the 1970s [26, 27]. Their work focuses on design specification, simulation, and

RTL synthesis. Common software code-transformation, which are used by today tools, like dead-code and redundant sub-expression elimination, constant propagation, code motion are used in the synthesis process. The instruction set processor specification (ISPS) language is used as the design specification [28]. The data-memory allocators perform a mapping function from the algorithmic ISPS description to the data-path part of the hardware implementation. Then the module selection binds the abstract components to a database of specified modules and finally a controller of components is produced.

Figure 2.7 – The CMU design system, one of the earliest HLS.

Although it was a groundbreaking research, this old work had a little impact on the industrial design. This is because large electronics companies were not still using or starting adopting CAD/CAM systems at that period.

During the first generation, a plethora of tools for research and prototyping were built. MI-MOLA [29, 30] a design method with a purpose to produce digital processors from high-level behavioral specification. The design system combines both compiler construction and hardware oriented concepts. Advance Design AutoMation or ADAM [31, 32] was a unified framework with restricted natural language interface (a dataflow graph representing the behavioral specification) which contained program tools which synthesized RTL designs from behavioral descriptions and the prediction tools which guides the designer in exploring the design space. In addition, the Sehwa [33] tool in ADAM can generate pipelined implementations by exploring the design space. The tool is able to synthesize and perform high-level estimates on the area-delay characteristics of designs and to determine the best design that meets the given constraints. Hardware ALlocater or HAL [34] is a data path synthesis tool with three characteristics. Firstly, it offers the analysis of the input data flow graph and attempts to evenly distribute operations with similar resources with a load balancing technique. Secondly, it provides a global pre-selection of operator cells to full fill speed constraints and register and multiplexer optimizations. Finally, HAL proposed a well-known scheduling technique called the force-directed scheduling on [35] and conflict-graph graph coloring technique for sharing resources in the datapath [34]. Flamel [36], a Pascal to gates HLS, extracts parallelism from block-level transformations.

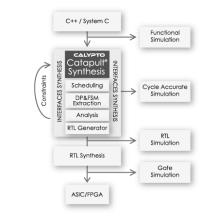

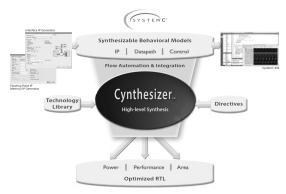

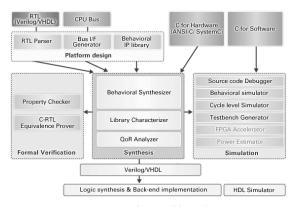

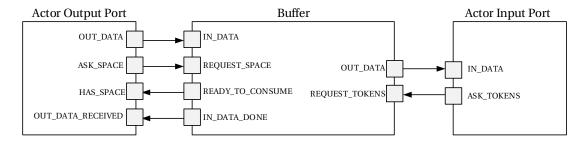

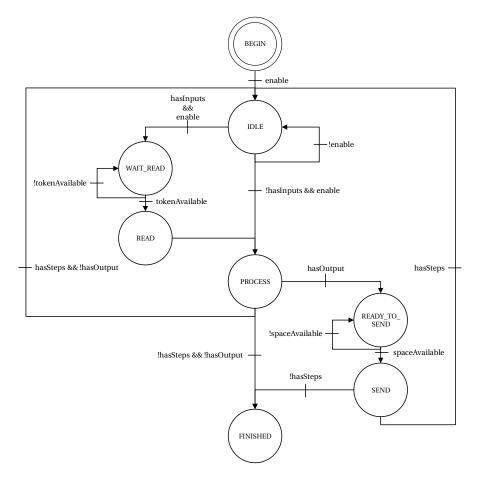

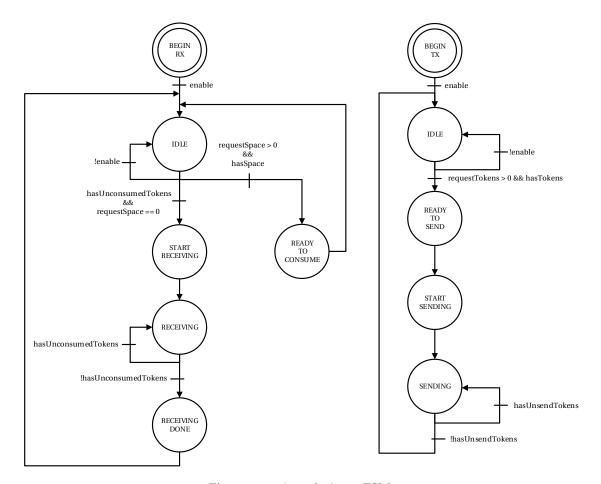

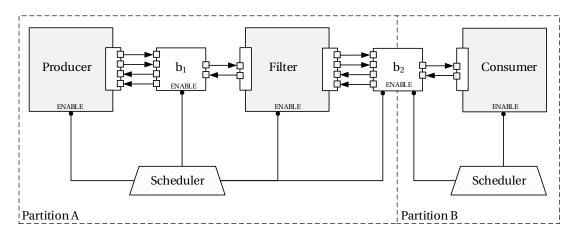

Hercules/Hebe [37, 38] is a C to gates HLS. Hercules introduced a method called Reference