provided by Infoscience - École polytech

#### Jungsoo Kim, Mohamed M. Sabry, Martino Ruggiero and David Atienza

#### 1 Introduction

This continuous growth in demand for computing has resulted in larger collections of servers machines, referred to as clusters or server farms, being hosted in denser datacenters thus having a higher computational and storage capability per occupied unit volume. While projections indicate a continued scaling of server density and manufacturing cost for another decade, the semiconductor manufacturing industry has already renounced following *Dennard scaling*<sup>1</sup> and almost reached the physical limits of voltage scaling in Complementary Metal-Oxide-Semiconductor (CMOS) technologies, which results in an energy-scalability wall that makes transistor power

J. Kim (🖂)

DMC Research Center, Samsung Electronics, Suwon, Republic of Korea e-mail: jungsoo9.kim@samsung.com

M. M. Sabry · M. Ruggiero · D. Atienza Embedded Systems Laboratory, EPFL, Lausanne, Switzerland e-mail: mohamed.sabry@epfl.ch

M. Ruggiero

$e\hbox{-mail: martino.ruggiero@epfl.ch}$

D. Atienza

e-mail: david.atienza@epfl.ch

© Springer Science+Business Media New York 2015 S. U. Khan, A. Y. Zomaya (eds.), *Handbook on Data Centers*, DOI 10.1007/978-1-4939-2092-1\_29 857

J. Kim was also affiliated with ESL-EPFL during the period this research was developed.

<sup>&</sup>lt;sup>1</sup> The scaling theory he and his colleagues formulated in 1974 postulated that MOSFETs continue to function as voltage-controlled switches while all key figures of merit (such as layout density, operating speed, and energy efficiency improve provided geometric dimensions, voltages, and doping concentrations) are consistently scaled to maintain the same electric field. This property underlies the achievement of Moore's Law and the evolution of microelectronics over the last few decades.

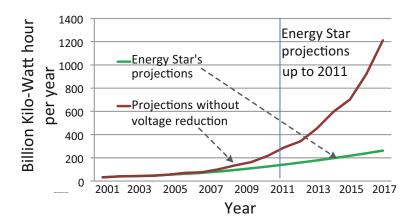

Fig. 1 Datacenters current energy use and projection [2]

consumption increase with further increases in density. At a large-scale, this "economic meltdown trend of Moore's law" for servers and datacenters [1], translates in a dramatic increase in computation and cooling electricity costs.

Energy-efficiency constraints have therefore become the dominant limiting factor for datacenters because their growing size and electrical power demands cannot be met with state-of-the-art design practices and their electricity bill is skyrocketing, as Fig. 1 shows. This figure depicts the *Energy Stars* [2] electricity usage measured and projected up to 2011. If we extrapolate these values linearly up to 2017, as voltages stop scaling down according to the current *International Technology Roadmap for Semiconductors* (ITRS) projections, the electricity use would exponentially increase. Moreover, the expected increase in energy prices would only exacerbate the cost of using datacenters. Thus, datacenter operation will require more money per year on energy costs than on IT equipment replacement. In 2007, datacenters in Western Europe consumed an estimated total of 56 terawatt-hours (TWh) of power per year. The European Union (EU) estimates that this figure is likely to reach 124 TWh by 2020 [2].

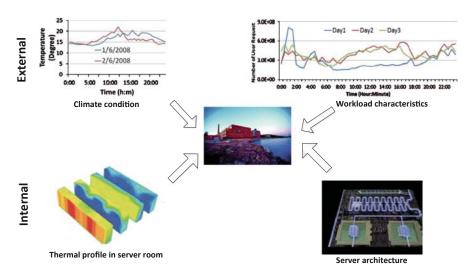

Power and thermal monitoring and control play a key role to reduce the power consumption of datacenters while maintaining the performance requirements and the maximum temperature constraints by manipulating multiple control knobs in the systems. As monitoring and control solutions are developed by being tightly coupled with hardware architecture and workload characteristics running on datacenters, we first revisit the datacenter structures (Sect. 1.1) and the workload characteristics running on current datacenters (Sect. 1.2). Then, we present an energy efficiency figure of state-of-the-art datacenters (Sect. 1.3), which motivates us to develop effective power and thermal monitoring and control solutions by manipulating multiple control knobs to achieve further global/holistic energy savings in datacenters.

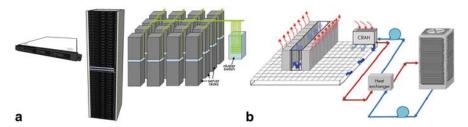

Fig. 2 Organization of datacenters: computing and cooling systems (a) and server organization (b) [3]

#### 1.1 Overall Datacenter Architecture

A datacenter can largely be decomposed into three parts: (1) IT, i.e., aggregation of servers, (2) cooling, and (3) power distribution units. Servers are the key constituent of datacenters and produce a significant amount of heat as they provide the capability of data manipulation and processing. In a server room, there is a large number of servers to sustain performance requirements. Figure 2a shows an example of typical server organization in a server room with a typical 1 U<sup>2</sup>. Server are typically placed in 42 U racks such that the servers are interconnected with local rack Ethernet switch, and then, connected to cluster-level Ethernet switches, which can potentially span more than ten thousand individual servers [3].

Datacenter cooling systems are deployed to remove heat generated by the servers along with additional amount of heat inside a server room, which needs to be removed as well. Power is delivered to servers through power distribution units (PDUs) and stored in un-interruptible power supply (UPS) systems to cope with power black-out. In this chapter, we focus on IT and cooling parts of datacenters. As shown in Fig. 2b, in a typical datacenter, a cooling system consists of computer room air conditioning/handler (CRAC/CRAH) in a server room and heat exchanger (namely, chiller) and cooling tower outside the server room. CRAC/CRAH provides cold air, such that the air condition of server rooms maintains safe operating temperature and humidity through the exchange of hot air exhausted by servers in the room with cold air (or water) provided from a chiller. According to the *American Society of Heating, Refrigerating and Air-Conditioning* (ASHRAE) 2009 recommendation, it is recommended to maintain the server room air condition as follows:

- Temperature: 64.4–80.6 °F

- Humidity: 41.9 °F at dew point (DP) to 60 % RH and 59 °F DP.

However, these values are quite conservative as they are determined by assuming that servers in a server room are fully utilized, which rarely happens as will be explained

<sup>&</sup>lt;sup>2</sup> A rack unit, **U** or **RU**, is a unit of measure to describe the height of rack-mount servers placed in 19-in. or a 23-in. rack, where 1U corresponds to 1.75 in. (44.45 mm) high.

in Sect. 1.2. Due to the over-provisioning of cooling capability to server rooms, huge amount of power are now wasted in datacenters, which motivates us to develop an efficient system control solution that adaptively adjusts cooling configurations along with existing power and thermal management solutions developed for servers to achieve further energy savings. The effective control solution is only obtained through accurate-yet-efficient monitoring of power consumption and temperature of multiple points of datacenters, which urges to develop an efficient monitoring system for datacenters.

#### 1.2 Datacenter Workload Characteristics

Many types of applications are running on datacenters, ranging from high-performance computing (HPC) to large-scale services, e.g., web search, streaming service, etc. Recently, due to the big advancements on cloud service providers (e.g., Amazon, Microsoft, Google, etc.), it becomes easier to deploy large-scale services, which leads to the drastic increase on servers hosting large-scale applications. The common characteristics of the large-scale services are that they are unprecedentedly parallel as it uses big chunk of data by splitting into small chunk. Figure 3 illustrates the overall operation which manipulates big chunk of dataset. In [4], Ferdman et al., examined applications running on today's clouds and presented top six most commonly found applications as follows:

- Data serving: serving as the backing store for large-scale web applications, e.g.,

Facebook inbox, Google Earth, etc.

- *MapReduce*: large-scale data analysis by first performing filtering and transformation of the data (namely, *map* procedure) and then aggregate the results (namely, *reduce* procedure)

- *Media streaming*: streaming services by packetizing and transmitting media files ranging from megabytes to gigabytes

- *SAT solver*: large-scale computations for solving complex algorithms, e.g., symbolic execution

- Web frontend: web services which schedule independent client requests across a large number of stateless web servers

- *Web search*: web search engines such as those powering Google and Microsoft Bing, which indexes terabytes of data obtained from online sources.

Up to now, most of the control solutions have been developed by targeting HPC workload characteristics. However, the workload characteristics of such large-scale applications are quite different from traditional HPC applications in both macroscopic and microscopic scales [4], which mandates us to develop the control solutions for the large-scale applications.

In a macroscopic scale, the application, first, is user-interactive, thereby, the amount of required computing capacity is highly variable and fast-changing [6] due to the dependence with external factors, i.e., number of clients/queries, etc. The

Fig. 3 An example of scale-out applications [5]

characteristics of the workload traffic are well analyzed in [7]. In the coarse-grained time interval (few tens of minutes to hours), the characteristics of users' requests are distinctly different over time while the global pattern has a strong correlation with adjacent time periods as well as the same period in different days. On the other hand, in the fine-grained time interval (less than few seconds), the characteristics of user requests depend on burstiness of traffic and arrival patterns and we can model the characteristics of users' request at the microscopic scale with (1) ON/OFF periods and (2) inter-arrival time between two consecutive requests during ON period. ON period is defined as the longest continual period during which all the request inter-arrival times are smaller than predefined value. Accordingly, OFF period is defined as a period between two on periods. As presented in [7], ON/OFF period and inter-arrival time are time-varying and uncertain while each of them forms lognormal distribution.

Second, the responsiveness (or latency) should come at the first criteria to be satisfied as the level of user satisfaction leads to the success of the business [10]. Third, the amount of required resources is usually far beyond the level that single server can sustain; thereby, massively parallel nodes are cooperatively working by forming a cluster architecture [8]. For instance, in a web search application, a big chunk of search index is divided into multiple smaller datasets, and then, allocated into multiple VMs (or servers) each of which is called a *index searching node (ISN)*. Once a query is arrived, each ISN independently searches matched data with the allocated dataset and a master node gathers the search results from multiple ISNs, then sends the results to clients. Due to the deployment of multiple nodes for a single application, such workload is called *scale-out* applications [4].

Microscopic-scale characteristics of the application are well studied in [4]. The following summarizes the four distinctive micro-architectural workload characteristics in the applications:

- High instruction cache miss rates

- · Low instruction- and memory-level parallelism

- · Large memory footprint far exceeding the capacity of on-chip caches

- Low on-chip and off-chip bandwidth requirements.

Due to the lack of the control solutions accounting for the distinctive workload characteristics of large-scale cloud application, in this chapter, we will present a power management solution optimized for the workload characteristics of the large-scale cloud applications.

## 1.3 Energy Efficiency of Datacenters

Due to the conservative cooling provision and lack of the consideration on workload characteristics, vast amount of energy is wasted in todays' datacenter. *Power usage efficiency* (PUE) is the most widely used metric to quantify the power efficiency of datacenters, which is defined as follows:

$$PUE = \frac{\text{Total power consumed by a datacenter}}{\text{Power consumed by servers}} \tag{1}$$

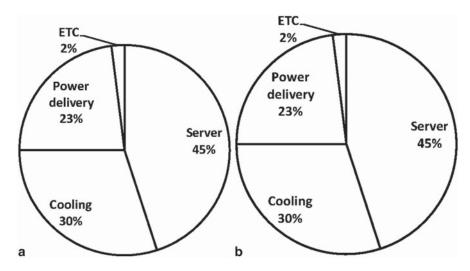

Thus, the lower, the better and it can ideally be reached to 1.0 According to US Environmental Protection Agency (EPA) report [2], the PUE of average datacenters around world amounts to 1.9, which means that for every watt of power consumed in the computing equipment, an additional 0.9 W of power is needed for cooling and power delivery. Figure 4a shows the breakdown of energy usage of typical datacenters (The PUE value amounts to 1/0.45 = 2.22) when assuming  $10 \sim 30\%$  IT load scenario [3]. Cooling system, comprised with chiller and CRAC/CRAH, consumes around 30 % of energy consumption while the power system spends additional 23 % of energy caused by uninterruptible power supply (UPS), power distribution unit (PDU) and AC-DC conversion losses. Other facility elements, e.g., humidifier, lighting, transformers, contribute around 2 % of total energy consumption. Such inefficiency corresponds to waste of money in the business sense. Figure 4b shows the monthly costs breakdown in a state-of-the-art datacenter assuming a 3-year server amortization and a 15-year infrastructure amortization [9]. This figure illustrates that, in less than three years, the accumulated cooling costs are higher than the actual server deployment costs, thus datacenters energy and thermal management is directly related to effective cooling and power delivery.

Among the various reasons contributing to the poor energy efficiency (e.g., voltage conversion loss in UPS, excessive cooling provision, etc.), the loss in the datacenter cooling facility caused by the over-provisioned cooling capability takes the most significant portion in the entire loss as it is adjusted to guarantee safe operating conditions of servers targeting the worst-case workload scenario which happens rarely. In order to improve the energy ineffectiveness, datacenter designers and a large set of recent search works in the literature have identified three key guidelines as follows:

Fig. 4 a Breakdown of datacenter energy overheads [3]. b Datacenter costs breakdown assuming a 3-year servers and 15-year infrastructure amortization model [9]

- Fine-grained monitoring of PUE

- Server rack layout minimizing hot and cold air mixing by cold-aisle/hot-aisle layout, containment, duct, and analysis of computational fluid dynamics (CFD)

- Adjustment of thermostat of server room to the highest level where servers can be safely operated

However, there still exist huge gap until it reaches to its ideal value, i.e., 1.0, which necessitates the energy- and thermal-aware design in unprecedented ways. The main reason is that all these practices are still focused only on worst-case cooling scenarios designs without any holistic view that considers the dynamic cooling needs of the computing infrastructure at run-time. These results pose very drastic consequences in the design and modes of operation for next-generation datacenters.

#### 1.4 Chapter Organization

In this chapter, we focus on presenting solutions to reduce the energy consumptions of servers and cooling systems through effective power and thermal control solutions based on accurate yet efficient power and temperature modeling and monitoring solutions. The rest of the chapter is organized as follows. Section 2 reviews state-of-the-art datacenters, especially focused on computing and cooling parts of datacenters to understand state-of-the-art technologies and figure out control knobs which are manipulated in control solutions. Section 3 shows approaches of modeling and monitoring power and temperature in servers as well as datacenters. Section 4 explains dynamic power and thermal management solutions for single servers, ranging from

**Table 1** Server power breakdown [3]

| Component  | Proportion (%) |

|------------|----------------|

| CPU        | 33             |

| DRAM       | 30             |

| Disk       | 10             |

| Networking | 5              |

| Etc.       | 22             |

conventional air-convection cooled servers to liquid cooled ones. Section 5 explains power and thermal management solutions for large-scale computing server clusters in a datacenter. Section 6 explains the joint power and thermal management solutions for large-scale datacenters including both of computing and cooling power consumptions, especially targeting a hybrid cooling architecture which selectively uses free cooling according to required cooling capability. Section 7 summarizes the chapters.

#### 2 State-of-the-Art in Datacenter Design

In this section, we explain state-of-the-art techniques to improve the energy efficiency of datacenters while meeting the temperature constraint, especially focusing on the two biggest energy consumers in datacenters, i.e., computing servers and datacenter cooling facility.

### 2.1 Computing Servers

1) Energy-Proportional Server Designs Server architectures have traditionally target performance optimization to support the ever-increasingly IT services demands and energy-efficiency has only become an important concern in the last five years. Due to the continuous technology scaling-driven performance improvement and the fact that single microprocessor architectures recently reached its performance limits [11], server designs have evolved since 2005 towards multi-cores architectures. A good example of this trend in state-of-the-art server designs is the HP DL980 blade server, which includes eight CPU sockets and each of them can support up to 10 cores [12]. Currently, the power consumed by servers takes more than 50 % of total power consumed by datacenters [3]. Table 1 shows the power breakdown of existing servers, which outlines that the largest portion of total power consumption in servers is taken by the CPU, but also DRAM memories must be considered as important blocks to develop power and thermal management strategies at server level.

In addition, future server designs trends by major server vendors, e.g., Sun Labs-Oracle, IBM, etc., show an evolution towards 3D-stacked technology integration

programs [11], which enables the integration of a larger number of processing cores in very limited chip volumes and can significantly reduce the memory access latency by stacking memory layers on top of processing cores. Furthermore, 3D integration enables easier development of heterogeneous computing architectures because it is possible to integrate multiple memory types (e.g., 3D-stacked DRAM, phase change memory), and storage (e.g., solid-state disk) devices from different manufacturing processes, as in the EuroCloud server project [13]. However, as a side effect, power density is expected to significantly increase in 3D multi-core computing systems (i.e., up to 300 W/cm³ [14]), which will make extremely difficult to properly dissipate the generated heat with current air-based cooling systems [15]. In particular, if free cooling is used, it will be a must to consider jointly the conception of the cooling and computing architecture.

One of the recent topics in server research is achieving energy-proportional components, which implies that computing systems should consume different amounts of active power according to their actual utilization. Nowadays, although servers are currently optimized to handle high-performance computation demands, most of the servers in a datacenter run at or below 40 % utilization during a significant part of the time, yet still draw almost full power during the process [16]. Therefore, latest server designs include many sensors (e.g., power, temperature, etc.) to accurately detect the current server utilization state [17]. Also, server components (i.e., processor, memory, and disk) now provide various operating states (e.g., active/idle/sleep/dormant) as well as various voltage and frequency (v/f) levels in processor and memory [18]. Therefore, recent works [19, 20] have shown the potential of developing energy proportionality in servers by exploiting the different power states and v/f levels according to the performance demand of local server utilization. Nonetheless, all these approaches focus on power consumption optimization of computing systems, thus they do not formally guarantee an optimal v/f point under thermal-induced power variations or can provide thermal damage prediction.

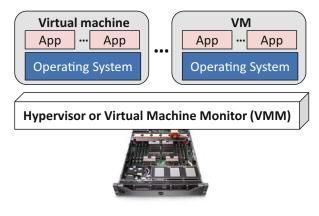

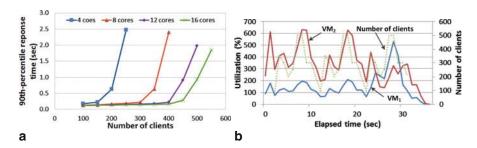

In order to reduce idle-time (leakage) power consumption, server processors provide nowadays hardware support for virtualization (e.g., AMD-V, Intel VT-x), which is a technique to enable increased physical server utilization by running applications from multiple OS instances in the so-called virtual machines (VMs) [21]. Moreover, on top of the hardware support, several virtualization software frameworks (e.g., Citrixs XenServer, Microsofts Hyper-V, VMWare ESXi, etc) have been recently developed to host multiple VMs with negligible performance degradation. Figure 5a illustrates the server virtualization. Recent improvements in the server virtualization techniques enable to run applications in a virtualized server within acceptable performance loss, i.e.,  $\sim 20\,\%$  for running CPU intensive workload [22] compared to running on a native system, while it is known to be degraded further when running memory- and disk-intensive workloads [23].

These various control options described above, i.e., power state, v/f level, VM placement, etc., give us great opportunities to achieve further power savings by fully utilizing the various control options while posing the challenges to develop an efficient control solution at the same time due to the large solution space, which necessitates us to develop an effective yet low-complexity control scheme.

Fig. 5 Concept of server virtualization: hosting multiple VMs with the aid of hypervisor

**Fig. 6** Hot- and cold-aisle isolation [9]

## 2.2 Cooling Infrastructure

In order to achieve energy-efficient datacenter cooling, various solutions have been presented. In this section, we address the three most widely used and effective solutions: (1) hot- and cold-aisle isolation, (2) closed-coupled cooling, and (3) free cooling. Then, we present how to utilize the cooling solutions more effectively to achieve further energy savings.

1) Hot- and Cold-Aisle Isolation Figure 6 shows a typical way of server room cooling. The cold air is provided by computer room air conditioning (CRAC) units through a raised floor, a steel grid resting on stanchions installed 2–4 ft. above the concrete floor. The cold air flows into racks through perforated tiles, and then, hot air is exhausted through a rear side of rack after absorbing heat generated by servers in the rack. One way of improving cooling efficiency is to prevent mixing the cold air provided from CRAC and hot air exhausted by servers. It is realized by a solution, so called hot- and cold-aisle isolation, which arranges server racks such that the intakes of cold air in server racks are faced each other, i.e., cold aisle, while preventing the mixture of hot air in different aisle side, i.e., hot aisle. The hot air is eventually drawn by the CRAC, and then, cold air is again provided to cold aisles by exchanging the heat with cold air (or water) provided from chillers.

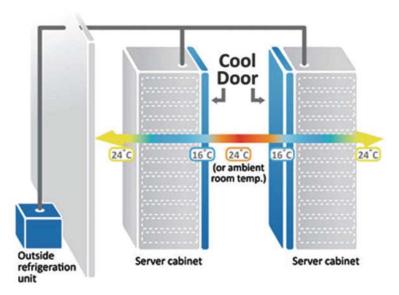

Fig. 7 In-rack cooling [24]

- 2) Closed-Coupled Cooling Closed-couple cooling solutions place cooling units more closely to computing units so as to remove any losses incurred throughout the delivery of cooling medium and quickly react to spatial temperature distribution. In this cooling solution, there are largely two classifications according to the granularity of computing cluster covered by single cooling unit, i.e., in-row and in-rack coolings. An in-row cooling adjusts cooling condition at every row according to the corresponding conditions while an in-row cooling adapts its cooling configuration according to operating condition at each rack. Figure 7 shows an example of an in-rack cooling solution where the cold air is directly fed into the front door of racks, namely, CoolDoor while the hot air is drawn by the CRAC with the same way in Sect. 2.2. The effectiveness of the solution is quite obvious in terms of the energy efficiency in that it can adjust only necessary parts instead of adjusting whole cooling configuration based on the worst-case scenario. It is reported that PUE of this cooling solution can reach down to  $1.1 \sim 1.2$  [3]. However, the capital expenditure for the installation is quite high.

- 3) Free Cooling A recent approach to improve energy efficiency in datacenters is the concept of free cooling, which relies on the use of outside cold air and/or water for cooling instead of electricity. This is a promising architectural innovation for datacenter cooling infrastructure that can enable PUE to approach values near 1.0. Google has recently constructed two datacenters in Ireland and Belgium based on this concept and reports drastically improved PUE figures up to 1.09 [3].

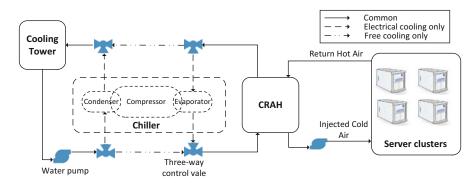

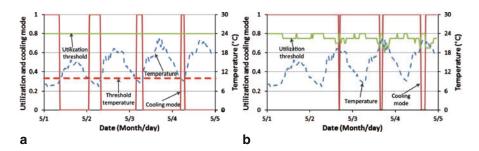

Fig. 8 Datacenter cooling architecture [43]

Despite the promising advantages on cooling-energy efficiency, the fundamental issue of free cooling is its limited applicability, as it can only be used in a very limited set of geographical locations because the cooling capability is tightly coupled with climate condition (e.g., temperature and humidity). Thus, it suffers from wide variations of cooling efficiency during the year, which translates in significantly high computing systems failure rates [25]. Hybrid cooling, which provisions backup cooling infrastructure along with free cooling, is an intuitive solution to extend the usability of free cooling. Two main types of hybrid cooling architectures exist [26, 27]. The first architecture switches between free- and electricity-based cooling according to the outside temperature: if the outside temperature is lower than a certain threshold, free cooling is used; otherwise, chiller-based electricity cooling is employed as shown in Fig. 8. However, in real-life conditions, datacenters can use free cooling in very limited periods of the year and the average reported PUE is approximately 1.5. The second proposed architecture uses a cooperative hybrid cooling solution to increase the time free cooling is used. In this case, free cooling complements the chiller by pre-cooling hot return water with cold outside water before entering the chiller. This second architecture enables using free cooling, at least partially, for the entire year, and provides up to 50 % energy savings in cooling infrastructure (PUE $\simeq$ 1.25). However, it still suffers from significant higher failure rate than chiller-based solution due to lack of efficiency in the combined cooling scheme, which makes the current computing systems to operate at higher and variable temperatures. Moreover, due to the continuous increase in server power density, driven by the ever-increasing IT demand, the applicability of current free cooling will be even more limited in the future.

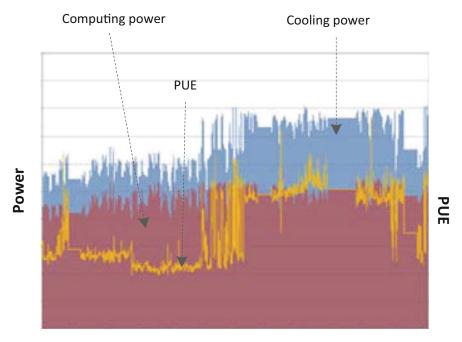

Figure 9 shows the variation of the power consumed by computing and cooling facilities as well as PUE measured for a datacenter equipped with hybrid cooling architecture deployed in Finland. As indicated the PUE line, PUE value varies 1.09  $\sim$  1.60 and can be largely classified into three periods according to the PUE value. In this datacenter, free cooling is used only when the outside temperature is lower than 8  $^{\circ}$ C, which is set to very conservative value so as to cope with the worst-case

Fig. 9 Variations of power and PUE throughout a year [28] measured by a datacenter equipped with hybrid cooling architecture deployed in Finland

scenario. First, during the winter, PUE value is low as the free cooling is used for the most of the time period while it becomes increased during the summer as the electrical cooling is more frequently used as the temperature goes up.

Thus, free cooling as such cannot provide the ultimate solution to improve datacenter energy efficiency due to the limitation of the cooling capability and the dependency on outside temperature. In order to be generally applicable it must be combined in synergistic ways with innovative energy-proportional server design and cooling solutions, as well as holistic datacenter thermal control.

#### 3 Power and Temperature Modeling and Monitoring

Accurate-yet-efficient modeling and monitoring on power and temperature of datacenters are necessary to develop control solutions for target systems. In this section, we first explain how we can model the power consumption and the temperature of existing servers and cooling facility in datacenters. Then, we address scalable and cost-effective power and temperature monitoring systems for large-scale datacenters.

### 3.1 Server Modeling

1) Power Modeling A server consists of various components, i.e., CPU, DRAM, disk, network interface (NIC), etc. As presented in Table 1, vast amount of the power is consumed by CPUs, memory, and disk, i.e., more than 70 %. Extensive works have been presented to accurately model power consumption of each component. McPAT is micro-architectural power model for chip multiprocessor (CMP), including in-order and out-of-order processor cores, networks-on-chips, shared caches, integrated memory controllers, and multiple-domain clocking, while tacking into account various process characteristics, e.g., bulk CMOS, SOI, and double-gate transistors, based on the forecast in the ITRS roadmap. The accuracy is validated using various processor implementations, i.e., Niagara, Niagara2, Alpha 21364, and Xeon Tulsa, whose errors range  $10.84 \sim 22.61$  %, compared to the measured values. DRAMSim [29] and Micron's System Power Calculator [30] provide accurate and detailed timing and power models of various types of DRAM, e.g., DDR, DDR2. DDR3, Mobile LPDRAM, etc., accounting for the operations.

Although such accurate power models exist to model individual component of servers, it is difficult to use all such accurate models together due to the speed of the simulation. It becomes more exacerbated when we target to simulate the large number of servers in datacenters. Thus, high-level power models are widely used to track and estimate the power consumption of servers based on the observation that the power consumption for a given server is highly correlated with distinctive workload characteristics, e.g., CPU-, memory-, or disk-intensive, stressed on servers. To capture the relationship, various works have presented high-level power model which estimates the power consumption based on the utilizations [31–33]. Among them, Economous et al. [31] present a linear regression power model which estimates the server power consumption with respect to utilizations of CPU ( $u_{cpu}$ ), memory ( $u_{mem}$ ), and disk ( $u_{disk}$ ), and network interface ( $u_{net}$ ) as follows.

$$P_{server} = C_0 + C_1 u_{cpu} + C_2 u_{mem} + C_3 u_{disk} + C_4 u_{net}$$

(2)

where  $\{C_0, C_1, C_2, C_3\}$  is a set of fitting parameters, which varies according to the target server system. This model is validated through two types of servers: (1) blade servers containing 2.2 GHz AMD Turion processor, 512 MB SDRAM, 40 GB HDD, 10/100 MBit Ethernet and (2) Itanium servers containing four Itanium2 chips, 1 GB DDR, 36 GB HDD, 10/100 MBit Ethernet. According to their evaluations, the errors are within 10% in most of test cases using various benchmark suites, i.e., SPECcpu200, SPECjbb2000, SPECweb2005. Further evaluations for developing the high-level server power modeling have been conducted in [32] by comparing five different forms of power models as follows:

$$Type1: P_{server} = C_0 (3)$$

$$Type2: P_{server} = C_0 + C_1 u_{cpu} \tag{4}$$

$$Type3: P_{server} = C_0 + C_1 u_{cnu}^r \tag{5}$$

$$Type4: P_{server} = C_0 + C_1 u_{cpu} + C_2 u_{disk}$$

(6)

$$Type5: P_{server} = C_0 + C_1 u_{cpu} + C_2 u_{mem} + C_3 u_{disk} + C_4 u_{net}$$

(7)

Type 1 modes the power consumption in a static value. Type 2 and 3 model the power consumption with respect to CPU utilization, i.e.,  $u_{cpu}$ , in linear and nonlinear manners, respectively. Type 3 and 4 add additional term to take into account the variations caused by disk ( $u_{disk}$ ), memory ( $u_{mem}$ ), and network ( $u_{net}$ ). It concludes that Type 2 power model is enough for modeling CPU-intensive workload while Type 5 power model, using both of OS-reported component utilizations and CPU performance counters, is needed to cover broad workload characteristics, i.e., memory-and disk-intensive workloads, and aggressively power-managed servers.

In [33], Pedram et al. further enhance the accuracy of the power model by adjusting the fitting parameters according to various operating voltage and frequency and the number of active cores. It used Intel Xeon E5410 processor for the validation with various test cases, i.e., combination of the number of active cores and operating voltage and frequency level. Recently, *Joulemeter* is provided to automatically tune the parameters in power models by measuring battery usage in laptop or measuring power consumption in servers.

Fans also consume significant amount of power in servers. Indeed, it is well known that the fan power consumption has a cubic relationship with fan speed [34], as follows:

$$P_{fan} = C_0 + C_1 s_{fan}^3 (8)$$

where  $\{C_0, C_1\}$  is a set of fitting parameters and  $s_{fan}$  represents fan speed. Thus, lowering the fan speed enables us to reduce drastic amount of power consumption.

2) Temperature Modeling Accurate temperature models for servers are required to capture the temporal and spatial temperature variations. Especially, due to the high area and cost of placing thermal sensors in a silicon die as well as frequent failures of thermal sensors, the needs for the accurate temperature modeling becomes more important. Computational fluid dynamics (CFD) simulation is known to be a solution to develop accurate and complete 3D thermal map of servers by using numerical methods and algorithms to solve and analyze problems that involve fluid flows. In [35], Choi et al. present a CFD-based thermal modeling solution of servers by solving the governing transport equations shown in the following conservation law form:

$$\frac{\partial \rho \phi}{\partial t} + \frac{\partial \rho U_j \phi}{\phi \partial x_j} = \frac{\partial}{\partial x_j} \left( \Gamma_{phi,eff} \frac{\partial \phi}{\partial x_j} \right) + S_{\phi}$$

(9)

where  $\phi$  is a general variable used for different context, e.g., mass, velocity, temperature, or turbulence properties;  $\rho$  is a fluid (air) density; t is a time for transient simulations;  $x_j$  is a coordinate x, y, or z direction when j is 1, 2, or 3,  $U_j$  is the velocity in each direction;  $\Gamma$  is the diffusion coefficient; S is the source for a particular variable such as the heat flux from a target system when the air temperature is  $\phi$ . The four terms in Eq. (9) corresponds to transient, convection, diffusion, and source

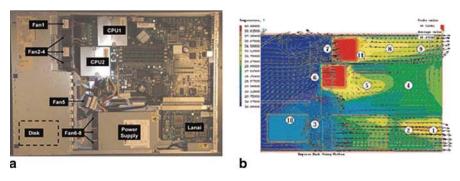

Fig. 10 Layout of IBM X335 server (a) and temperature map (b) [35]

parts of transport phenomenon at the spatial domain/extent. Figure 10a and b show pictures of IBM X335 server comprising of multiple components and its temperature map, respectively. As shown in Fig. 10, the spatial temperature variation can be accurately modeled. Despite the high accuracy of the CFD simulation, the simulation complexity is quite high because it does not have any closed-form solution for solving the differential equation in Eq. (9), which leads to adopt computer-based numerical procedures.

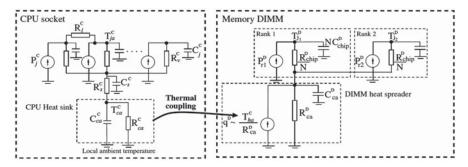

In [36], T. Heath et al. present a solution of constructing temperature map of servers while relieving the complexity of CFD simulation with negligible accuracy degradation, i.e., within 0.32 °C compared to CFD simulation. The simplification is achieved by abstracting heat- and air-flow with simplified graphs. Recently, a further simplified temperature model for servers has been presented in [38], especially targeting the CPU and memory sub-system of servers considering varied heat removal capability as a fan speed changes. It is developed by constructing thermal RC network of the system based on well-known duality between thermal and electrical phenomena [37], as shown in Fig. 11. In the RC network of CPU socket,  $P_i^c$  represents the power consumption of each core in a socket;  $R_I^c$  and  $R_V^c$  represent the lateral and vertical thermal resistance, respectively, where  $R_l^c$  is normally ignored as  $R_{\nu}^{c} << R_{l}^{c}; R_{s}^{c}$  and  $R_{ca}^{c}$  are thermal resistance of heat spreader and case-to-ambient (i.e., heat sink), respectively.  $C_i^c$ ,  $C_s^c$ , and  $C_{ca}^c$  are thermal capacitances of die, heat spreader, and heat sink, respectively;  $T_{ja}^{c}$  represents the junction temperature which is used as an input to dynamic thermal management (DTM) units such that  $T_{ia}^c$  is lower than  $T_{max}$ .  $R_{ca}^c$  is the sum of the thermal resistances of heat sink and convective resistance, i.e.,  $R_{ca}^c = R_{hs}^c + R_{conv}^c$ , where  $R_{conv}$  is changed according to the fan speed as follows:

$$R_{conv}^{c} \propto \frac{1}{A \cdot s_{fan}^{\alpha}}$$

(10)

where A is the effective area and  $\alpha$  is a factor with a range of 0.8 $\sim$ 1.0.

In the RC network of memory part,  $P_{chip}^D$  is the power consumed in each DRAM chip;  $R_{chip}^D$  and  $C_{chip}^D$  are thermal resistance and capacitance of each chip;  $T_j^D$  is

Fig. 11 RC network based temperature model [38]

the junction temperature of a DRAM chip; N is the number of ranks in a single DRAM chip. In addition, they observe that the temperature of DRAM is correlated with the temperature of CPU as the air inside a server flows from CPU to DRAM, thereby, air absorbing heat in CPU socket affects to the temperature of DRAM as it is equivalent to raising ambient temperature at DRAM. This phenomenon is called thermal coupling and modeled as follows:

$$q^D \propto \frac{T_{ha}^C}{R_{ca}^D} \tag{11}$$

where  $q^D$  is the dependent coupling heat source of the memory;  $T_{ha}^C$  is the heat sink sink temperature of the CPU;  $R_{ca}^D$  is the thermal resistance of the case to ambient of the memory DIMMs. This model is validated using Intel dual socket Xeon server, which shows a strong match between the actual measurement and the model within a  $0.27\,^{\circ}\text{C}$  average error.

#### 3.2 Datacenter Modeling

1) Computing Facility Basically, the temperature of servers in datacenter can be calculated using models in Sect. 3.1. However, for accurate temperature estimation for servers in a datacenter, we need to take into account interactions of generated heats among multiple servers in a server rack because servers are placed in a server rack in vertical direction and cold air flows from bottom to top of the server rack such that the heat generated at bottom is recirculated and affects to servers placed at upper side of the server rack. We call it heat recirculation in a datacenter. The amount of heat recirculation in a datacenter can be described by a cross-interference matrix, which is represented by  $\Phi_{N\times N}=\{\phi_{i,j}\}$  where N is the number of servers in a server rack.  $\phi_{i,j}$  indicates the contribution of the outlet heat rate of the i-th server in the inlet heat rate of the j-th one. Assuming  $Q_i^{out}$  and  $Q_j^{in}$  are, respectively, the

outlet and inlet heat rates for the i-th and j-th server, the inlet heat rate for j-th server can be calculated as follows [39]:

$$Q_j^{in} = \sum_{i=1}^{N} \phi_{i,j} Q_{out}^i + Q_{amb} + P_j$$

(12)

where  $Q_{amb}$  represents the heat rate delivered from cold aisle of a server room and  $P_i$  denotes the power consumed by j-th server.

In the vector form, we can write this relationship as follows:

$$\boldsymbol{Q}_{in} = \boldsymbol{\Phi}^T \boldsymbol{Q}_{out} + \boldsymbol{Q}_s + \boldsymbol{P} \tag{13}$$

Based on the heat rate, we can calculate the temperature at each server within a server rack using temperature models in Sect. 3.1.

2) Cooling Facility The typical cooling facility consists of a cooling tower, a chiller, and CRAH (or CRAC) as explained in Sect. 1.1. The heat generated by servers in a server room is absorbed by cold air provided from CRAH, and then, drawn by CRAH. CRAH exchanges the heat drawn from the server room with cold water (or air) provided from a chiller based on refrigeration cycle. In [42], A. Qouneh et al. provide a comparative and quantitative analysis of cooling power as varying processor utilization and adjusting the server room temperature accordingly. For further analysis of the power consumption of the cooling facility, some models have been presented in [40, 41] which model the power consumption based on thermo-fluid principles.

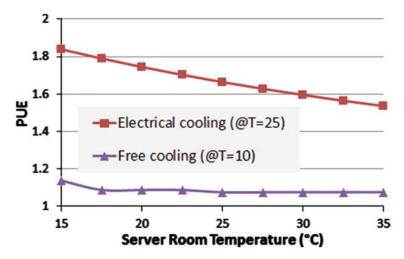

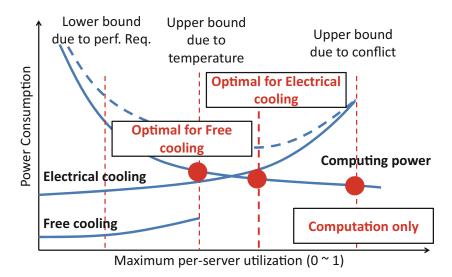

However, based on our analysis of real datacenter setups of our industrial partners in this work, we have observed that an alternative procedure can be used, where PUE mainly depends on the temperature set-point of server room ( $T_{room}$ ), outside temperature ( $T_{out}$ ), and total power consumed by servers ( $P_{cl}$ ). Moreover,  $T_{room}$  is the dominant factor compared to the others. Thus, we can simply characterize PUE with respect to  $T_{room}$ . Figure 12 shows PUE with respect to  $T_{room}$ . As shown in this figure, the PUE of electrical and free cooling ranges  $1.53 \sim 1.83$  and  $1.08 \sim 1.14$ , respectively. Assuming that  $T_{room}$  is set to the highest temperature of which servers in active mode can satisfy the maximum temperature limit, i.e.,  $T_{pm}^{max}$ , we can model PUE as a function of the power consumption of servers, i.e.,  $P_{pm}$ . By matching the results shown in Fig. 12, we can approximate the PUE with a relatively simple form, namely:

$$PUE = a_1 P_{pm}^2 + a_2 P_{pm} + a_3 (14)$$

where  $a_1, a_2$ , and  $a_3$  are curve fitting parameters. In the case of electrical and free cooling, the sets we have obtained for  $\{a_1, a_2, a_3\}$  are  $\{3.32 \times 10^{-5}, -9.45e \times 10^{-4}, 1.30\}$  and  $\{0, 0, 1.08\}$ , respectively. Then, the maximum (average) root mean square (RMS) error amounts to 4.38 % (0.76 %) and 0.56 % (0.56 %), respectively.

Fig. 12 Power usage effectiveness (PUE) in electrical and free cooling as power consumption of server varies [43]

Finally, the temperature of the server room,  $T_{room}$ , depends on CRAH efficiency,  $\epsilon_{CRAH}$ , which is defined as follows [43]:

$$\epsilon_{CRAH} = \frac{T_{CRAH}^{air} - T_{room}}{T_{CRAH}^{air} - T_{CRAH}^{water}} \tag{15}$$

where  $T_{CRAH}^{air}$  represents temperatures of air exhausted from server room;  $T_{CRAH}^{water}$  is the temperature of chilled water flowing into the CRAH, which corresponds to the set-point of chiller and outside temperature when electrical and free cooling is used, respectively. Note that these values can be calculated using the procedure in [40], which depends on server power consumption, outside temperature, etc. Since  $\epsilon_{CRAH}$  is always less than 1,  $T_{room}$  is always higher than  $T_{CARH}^{water}$ .

#### 3.3 Monitoring System for Datacenters

Power management in datacenters is an area of increasing interest from several viewpoints as it is backed up by real concerns on energy usage and cost by modern computing systems. Data center computing applications and platforms have been typically designed without regard to power consumption. With increased awareness of energy cost, power consumption tracking and management is now an issue even for compute-intensive server clusters.

Datacenters ecosystem is facing an increasing need for decision support systems for datacenter management. Building and administration of datacenters are indeed evolving towards increasingly complex scenarios. IT infrastructure managers have

to optimize the datacenter utilization and costs, under several constraints generated by heterogeneous and diverging technical challenges: customer requirements, infrastructure costs, energy costs, physical space available, etc.

Datacenters that have some energy measuring capabilities carry out those monitoring tasks through Data-Center Infrastructure Management (DCIM). This concept includes the integration of IT and Facility Management, with the aim of centralising monitoring, management and intelligent capacity planning of data centre systems. Capacity planning focuses primarily on energy but also on power, space, network, IT equipment, cabling, cooling and environmental factors (temperature and relative humidity).

Understanding total capacity of all factors ultimately gives the optimal position where equipment should be moved, added or changed for optimised use of the available capacity. It also directly indicates where potential capacity is still present but unused (stranded capacity). Currently, in many datacenters this task is carried out manually or through site audits. This is a tedious, time-consuming and labour-intensive process, with a high risk of human error. An advanced DCIM system automates and simplifies this process, benefiting to IT and facility staff, but also to the energy efficiency of the datacenter.

A DCIM system can in particular map and manage the complete power chain and hence the energy capacity of the datacenter. Starting at the power sources (grid power or alternative power sources) up to the outlets on a rack Power Distribution Unit (PDU) or even the components within the servers, including all devices in between, DCIM systems are essential to plan energy flows and perform trending and analysis. They bring full access to all available devices, from facility to IT, as well as life cycle management, support contracts, and logical and physical cable connections.

Whereas DCIM systems are usually a good fit for large datacenters, the needs of small to medium-size urban datacenters are not adequately met today. Existing systems are generally too complex, pricy, difficult to use and not modular enough for urban facilities. In addition, solutions offered on the market today are generally proprietary and tend to lock their users in to single vendors. Innovative DCIM support systems for datacenter management are thus needed. PMSM (i.e., Power Monitor System and Management) [44–56], developed at EPFL in cooperation with Credit Suisse [45], is an example of such an innovation.

#### 4 Power and Thermal Managements of Servers

As the servers operating workloads are time-varying, the accompanying power consumption and thermal profile vary as well. In order to maintain controlled power consumption and thermal dissipations, run-time dynamic power and thermal management (DPM and DTM) mechanisms are required. These management schemes exploit the utilization of power and temperature-affecting control knobs that exist in different layers of abstraction of the system, to aid in power and thermal reduction. In

addition, a fundamental challenge of any developed power or thermal management scheme is to have minimal, or preferably zero percent, performance degradation. If any management mechanism has a significant impact on the processing performance, it interferes with the architectural characteristics, hence considered a degrading rather than a managing element.

In this section, we explore the various power and thermal management mechanisms for server architectures. We first start by showing the state-of-the-art in power and thermal management solutions in Sect. 4.1. In Sect. 4.2, we explore our recent development in hierarchical power and thermal management schemes. Finally, we show our advances in power and thermal management in liquid-cooled server architectures.

# 4.1 Overview of CPU Power and Thermal Management Techniques

Power and thermal management solutions have been extensively existing in literature, which has been reflected in the various power and thermal management schemes [71, 72]. Nevertheless, we explore the recent works on power and thermal management in the state-of-the-art.

- 1) Temperature-Affecting Control Knobs As mentioned earlier, run-time management schemes utilize various control knobs that either reduce the causes of high heat generation, or increase the ability of the utilized cooling methodology. In the case of 3D MPSoCs, these control knobs are classified as follows.

- a) Workload Activity Knobs At the software-level (application, system software, and OS), workloads can be altered and customized such that they can be thermally-aware. For example, task scheduling and task migration [73] have been extensively used to balance the workload on planar 2D MPSoCs [74]. Another example involves the intra-task instruction scheduling to prevent the processing element temperature from elevating to alarming values.

- b) Circuit Switching Activity Knobs This class of control knobs affects the operating conditions of the processing element. These knobs may stall the processing element temporarily to reduce the heat generation, such as clock gating [75]. Alternatively, these knobs may reduce the operating speed of the processing element, which implies lower power consumption, hence lower heat generation, such as dynamic frequency scaling (DFS) or dynamic voltage and frequency scaling (DVFS) [75, 76].

- c) Thermal Package Control Knobs The knobs at the thermal package level are responsible of changing the cooling capabilities, which is related to the injected fluid in the case of 3D MPSoCs with liquid cooling. For instance, the volumetric flow rate of the injected fluid can be varied by changing either the liquid pumping power [77], or varying the value of a flow-control valve [78].

2) Power and Thermal Management of Air-Cooled 2D and 3D MPSoCs Ogras et al. [79] proposes the control of power usage in processing elements (PEs) and routers by using model predictive control at design time, and Bogdan et al. [80] elaborate further this approach by considering both PEs and routers in the control scheme for voltage and frequency. However, they only consider power management and do not explore thermal control aspects. In fact, consolidating the power consumption in processing elements could undermine temperature issues while the power consumption is reduced. Thus, explicit thermal management schemes that include temperature as a key role in optimization or imposing temperature as a constraint are required for thermal balancing.

Initial research efforts have been focusing on combined power and thermal management by presenting a set of scheduling mechanisms for MPSoCs that perform temperature management at the system-level [81], using thread migration techniques to achieve temperature reduction in localized hot spots [75], or using a temperature-aware dynamic scheduling algorithm with negligible performance overhead [74]. These methods do not exploit history information and take reactive control actions based on the current thermal profile and frequency setting of the MPSoC.

However, recent works exploit history information to improve thermal management policies. Previous work [82] exploits a temperature forecast technique based on an auto-regressive moving average model. Another work proposes a novel technique that adapts the thermal management policy to the current workload characteristics [76], where the adaptation is done online exploiting information related to the workload history. Two recent approaches [83, 84] describe two methodologies to achieve thermal prediction by combining the information of thermal model, thermal sensors and power consumption statistical properties. These approaches rely on open-loop search or optimization where it is assumed that power can be estimated accurately.

More advanced solutions apply the concepts of *model-predictive control* (MPC) to turn the control from open-loop to closed-loop [87]. A chip-level power control algorithm based on optimal control theory is proposed [85], where the power consumption of the MPSoC is controlled to maintain the temperature of each core below a specified threshold. A recent work [86] proposes MPC utilization to solve the thermally-aware frequency assignment problem of a planar MPSoC.

However, most previous policies do not completely avoid hot-spots, but they simply reduce their frequency, because the interaction among the prediction method, the thermal behavior of the MPSoC and the frequency assignment of the MPSoC have not been addressed as a joint optimization problem.

In a similar vein, recent work considers dynamic thermal management for 3D MPSoCs. Previous work evaluates several policies for task migration and DVFS [88]. This previous work explores thermal profiles of adjacent processing elements being on the same vertical column (interlayer adjacent) or within the same layer (intralayer). Based on this analysis, a combined DVFS and a task migration policy, named *THERMOS*, is implemented. However, this work do not consider controlling the thermal packaging knobs, whether it is air or liquid cooling. Another work [89] integrates a thermally-aware task scheduler with DVFS on a two-tier 3D MPSoC

with eight cores. A recent paper proposes a temperature-aware scheduling method specifically designed for air-cooled 3D MPSoCs [91]. This method takes into account the thermal heterogeneity among the different layers of the system, but there is no study on the effect of the thermal packaging control knobs as active thermal management parameters. The resulting temperatures obtained in these papers are significantly high (85–120 °C). These results imply that 3D MPSoCs are prone to high temperatures, and with increasing power densities conventional thermal management techniques and air-based cooling are incapable of controlling the temperature while preserving system performance.

3) Thermal Management of Liquid-Cooled 3D MPSoCs Prior liquid cooling work [90] evaluates existing thermal management policies on a 3D MPSoC with a fixed-flow rate setting, and also investigates the benefits of variable flow using a policy to increment or decrement the flow rate based on temperature measurements, but without considering pump energy consumption.

Thermal management methods for 3D MPSoCs using a variable-flow liquid cooling have been recently proposed [77]. These policies use experimentally-driven sets of rules to control the temperature profile of the 3D MPSoC while ensuring performance requirements to be satisfied. These approaches use a centralized control concept, which is inappropriate if the controlled parameters increase [92], as in the case of targeted 3D MPSoC designs with liquid cooling in this work.

Recently, Qian et al. explore the use of a cyber-physical approach 3D MPSoCs thermal management with inter-tier liquid cooling [93]. They construct their control mechanism with software-based thermal estimation and prediction. They use a non-uniform liquid flow in different microchannels to meet the cooling demands of different modules. They take their control decisions on software-based thermal estimation and prediction. They use a non-uniform liquid flow in different microchannels, to meet the cooling demands of different modules. However, they have not shown the overhead of their software-based thermal estimation. Moreover, they do not show the feasibility of having a non-uniform flow in different channels, as a physical implementation.

## 4.2 Run-Time Hierarchical Power and Thermal Management for Server Architectures

We have proposed another proactive management scheme that relies on model predictive controller (MPC) [94]. In this work, we have developed a thermal management scheme that controls task scheduling, DVFS, and the cooling infrastructure. In particular, we target the cooling infrastructure case of interlayer liquid cooled 3D MPSoC, where we can alter dynamically the injected liquid flow rate. At each time interval, a new set of workloads arrive, and the management scheme allocates these tasks to various cores and sets the corresponding flow rate such that the predicted peak temperature is reduced while minimizing the 3D MPSoC power consumption (cooling

and computation power). Then for each processing element it applies MPC to the assigned workload such that the local predicted temperature is reduced while using the minimum computing energy possible via DVFS. The formulation of this problem is stated as follows:

$$J = \sum_{\tau=1}^{h} \left( \|\mathbf{R}\mathbf{p}_{\tau}\| + \|\mathbf{T}\mathbf{u}_{\tau}\| \right)$$

(16)

$$min J$$

(17)

subject to:

$$f_{\min} \leq \mathbf{f}_{\tau} \leq \mathbf{f}_{\max} \ \forall \ \tau$$

(18)

$$\mathbf{x}_{\tau+1} = \mathbf{A}\mathbf{x}_{\tau} + \mathbf{B}\mathbf{p}_{\tau} \ \forall \ \tau \tag{19}$$

$$\tilde{\mathbf{C}}\mathbf{x}_{\tau+1} \leq \mathbf{t}_{\max} \ \forall \ \tau$$

(20)

$$\mathbf{u}_{\tau} \succeq \mathbf{0} \ \forall \ \tau$$

(21)

$$\mathbf{u}_{\tau} = \mathbf{w}_{\tau} - \mathbf{f}_{\tau} \ \forall \ \tau \tag{22}$$

$$\mathbf{l}_{\tau} \succeq \mu \mathbf{f}_{\tau}^{2} \ \forall \ \tau \tag{23}$$

$$-\mathbf{w} \leq \mathbf{m}_{\tau+1} - \mathbf{m}_{\tau} \leq \mathbf{w} \ \forall \ \tau \tag{24}$$

$$0 \le \mathbf{m}_{\tau} \le 1 \ \forall \ \tau \tag{25}$$

$$\mathbf{p}_{\tau} = [\mathbf{l}_{\tau}; \mathbf{m}_{\tau}] \ \forall \ \tau \tag{26}$$

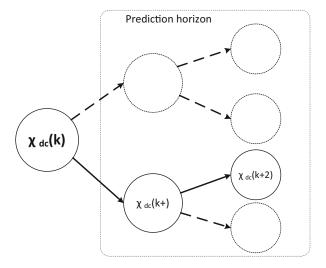

where matrices A, B are related to the overall 3D MPSoC system description. These matrices represent the 3D MPSoC system using a coarse granularity of the thermal cells and where the sampling time of the resulting discrete-time system is  $T_{GC}$ . The horizon of this predictive policy is defined as h [87]. Then, the objective function J is expressed by a sum over the horizon.

In the cost function (Eq. (16)), the first term  $\|\mathbf{Rp}_{\tau}\|$  is the norm of the power input vector p weighted by matrix  $\mathbf{R}$ . Power consumption is generated here by two main sources. Vector p is a vector containing normalized power consumption data the p tiers and the pumping power. Matrix  $\mathbf{R}$  contains the maximum value of the power consumption of the tiers and the cooling system. The second term  $\|\mathbf{Tu}_{\tau}\|$  is the norm of the required workload, but not yet executed. To this end, the weight matrix  $\mathbf{T}$  quantifies the importance that executing the required workload from the scheduler has in the optimization process. Then, Inequality (18) defines a range of working frequencies to be used, but this does not prevent from adding in the optimization problem a limitation on the number of allowed frequency values.

Equation (19) defines the evolution of the 3D MPSoC according to the present state and inputs. Equation (20) states that temperature constraints should be respected at all times and in all specified locations. Since the system cannot execute jobs that have not arrived, every entry of  $\mathbf{u}_{\tau}$  has to be greater than or equal to 0 as stated by Eq. 21. The undone work at time  $\tau$ ,  $u_{\tau}$  is defined by Eq. 22. Equation 23 defines the relation between the power vector  $\mathbf{l}$  and the working frequencies.  $\mu$  is a technology-dependent constant.

Fig. 13 Schematic diagram of the four-tier liquid-cooled 3D MPSoC used in the thermal evaluation of the proposed thermal management scheme

Then, Eqs. 24–25 define constraints on the liquid cooling management. The normalized pumping power value ( $\mathbf{m}$ ) scales, and any time instance  $\tau$ , from 0 (no liquid injection) to 1 (power at the maximum pressure difference allowable), as shown in Eq. 25. Moreover, the maximum increment/decrement change in the pumping power value from time ( $\tau$ ) to ( $\tau + 1$ ) is limited by a another normalized value  $\mathbf{w}$ , as shown in Eq. 24, which models the mechanical dynamics of the pump.

Equation 26 defines formally the structure of vector  $\mathbf{p}$ . Vector  $\mathbf{l} \in \Re^{\mathbf{p}}$  is the power input vector, where p is the number of tiers of 3D MPSoC.

Finally, the control problem is formulated over an interval of h time steps, which starts at current time  $\tau$ . Indeed the result of the optimization is an optimal sequence of future control moves (i.e., amount of workload to be executed in average for each tier of the 3D MPSoC which is stored in vector  $\mathbf{f}$ ). Then, only the first samples of such a sequence are applied to the target 3D MPSoC, while the remaining moves are discarded. Thus, at each next time step, a new optimal control problem based on new temperature measurements and required frequencies is solved over a shifted prediction horizon (e.g., the "receding-horizon" [87] mechanism), which represents a way of transforming an open-loop design methodology into a feedback one, as at every time step the input applied to the process depends on the most recent measurements.

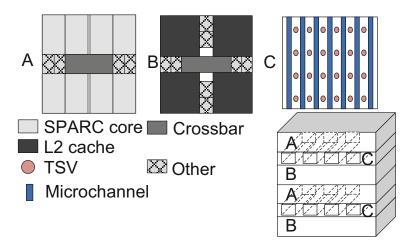

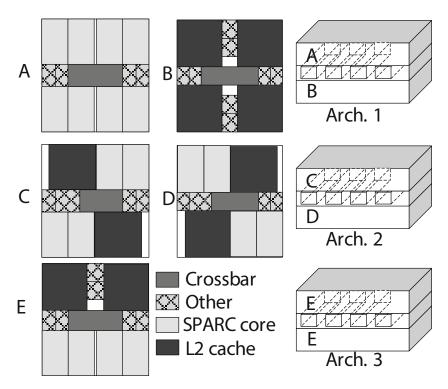

To evaluate the effectiveness of this thermal control, we apply this management scheme on a four-tier 3D MPSoC based on the UltrsSPARC T1 MPSoC [112], which is shown in Fig. 13. In addition, we compare it against different state-of-the-art thermal management techniques, which are as follows:

• Liquid cooling with LB (LC\_LB) [95]: It applies the maximum cooling flow rate, while the jobs are scheduled with load balancing policy (LB). LB balances the workload by moving threads from a core's queue to another if the difference in queue lengths is over a threshold.

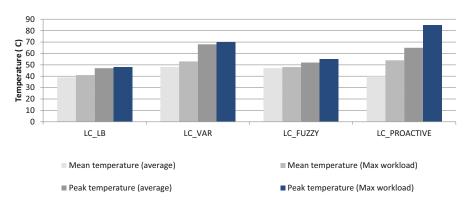

Fig. 14 Peak and average temperatures observed using all the policies, both for the average case across all workloads and maximum workload on four-tier 3D MPSoC [94]

- LUT-based flow rate control with LB (LC\_VAR) [77]: It dynamically changes the flow rate based on the predicted maximum temperature, while the jobs are scheduled with LB.

- Fuzzy-logic control (LC\_FUZZY) [96]: This mechanism utilized fuzzy logic in deriving thermal management mechanism that controls the variable liquid flow rate and DVFS.

In addition we refer to this management scheme as *LC\_PROACTIVE* in the following paragraphs. In this evaluation of different thermal management policies, *LC\_PROACTIVE* is compared with respect to the other management techniques mentioned above based on the:

- Maximum and average temperatures.

- Computational and cooling power consumption.

Thermal impact of all the policies on a four-tier 3D MPSoC (cf. Fig. 13) is shown in Fig. 14. This figure shows that LC\_LB reduces the peak temperature to 47 °C, whereas LC\_FUZZY and LC\_VAR push the system into a higher peak of 52 and 67 °C, respectively, but still avoids any hot-spots. This is the similar case in LC\_PROACTIVE, where the peak temperature reaches 84 °C. The alteration between the peak temperature comes from the fact that main target is to reduce the peak temperature to any value below 85 °C. However, since each technique has a different management policy, with different control elements, the peak and average temperatures are affected.

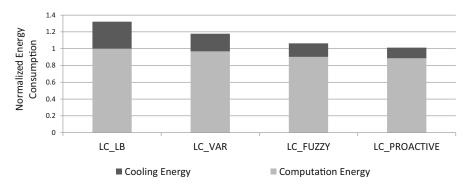

Figure 15 shows the total consumed power when running the various policies on the four-tier MPSoC with the average workload [94]. Energy consumption values are normalized with respect to the load balancing policy on the 3D-MPSoC with LC\_LB. In this figure, LC\_PROACTIVE manages to reduce the cooling power and the overall system power by 60 and 23 %, respectively, with respect to LC\_LB. Moreover, LC\_PROACTIVE even reduces the cooling energy more than LC\_VAR and LC FUZZY by 40 and 22 %, respectively.

Fig. 15 The normalized energy consumption in the whole system (chip and cooling network) [94]

#### 4.3 Design-Time Power and Thermal Optimizations

In addition to run-time management schemes, several works conduct power and thermal optimizations at design-time. In the case of MPSoCs, several approaches have been taken to optimize the power utilization and heat generation or dissipation. At the platform level, different modules can be designed to reduce the overall power density, hence heat generation, while preserving the system functionality. This approach has been taken recently in low-power (hence low temperature) processor designs such as ARM big.LITTLE processing architecture [97]. Another approach at the platform level is to reduce the operating power supply of the platform to near-threshold values [98]. Near-threshold computing allows the processing units to operate close to the voltage threshold value of the used transistor, hence reducing the overall power and thermal density.

In the case of 3D MPSoCs, recent work proposes multiple supply voltages utilization to optimize the voltage islands distribution in 3D MPSoCs [99]. In this work, a temperature-aware voltage island generation methodology is proposed that formulates this problem as a mixed-integer linear programming (MILP) problem. The main aim in this work is to minimize the thermal hotspots in 3D MPSoCs while keeping the performance and timing requirements satisfied. The interdependency between power and heat densities made it feasible to formulate this problem and achieve significant results.

Another work utilizes various microarchitectural techniques to control the thermal hotspots in 3D MPSoCs via thermal herding [100]. This technique explores different architectural disciplines by spitting several microarchitectural blocks between the different layers of 3D MPSoC to enhance the throughput while controlling the thermal hotspots such as, register file splitting. This splitting is based on general application trends and the significance of particular instructions or data locations to the execution flow.

Previous works have investigated the rearrangement of various hardware modules within the MPSoC to minimize the global thermal impact, which is also known in

literature as *temperature-aware floorplanning*. Initial work on temperature-aware floorplanning [101] has shown its significant impact on reducing the peak temperature. This work has defined a metric called *thermal diffusion* that resembles the lateral heat dissipation. This metric has been used in an optimization problem to maximize the gains of *thermal diffusion*. Other similar works have proposed simulated annealing utilization [102] or genetic algorithms [103] to achieve temperature-aware floorplanning.

In the context of 3D MPSoCs, temperature-aware floorplanning has also been extended by including the interlayer thermal dissipation and interconnect characteristics [102, 104–106]. For example, initial work has been proposed [107] for temperature-aware microarchitectural floorplanning. The main objective in this work is to place the processing submodules of a single processor in several layers such that the wire lengths and the temperatures are minimized. To achieve this, a mixed integer linear programming (MILP) problem is formulated to minimize the weighted sum of performance, area and thermal-related aspects. Another work uses simulated annealing to minimize the temperature of 3D MPSoC via floorplanning [105] by considering the additional power consumption of the interconnects.

As for liquid-cooled 3D MPSoCs, Mizunuma et al. use their thermal model to explore floorplanning solutions to homogenize temperature distributions in this architecture [108]. The results in this work, which is further assisted by the observations in other work [96], show that in the case of liquid cooled 3D MPSoC, temperature-aware floorplanning follows the trend of placing more heat dissipating modules at the fluid inlet port, while lower heat dissipating modules at the outlet port. In other words, the optimal heat dissipation pattern for temperature-aware floorplanning would be monotonically decreasing from the distance of the fluid inlet port.

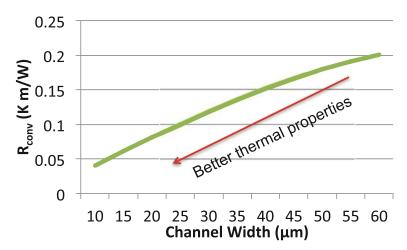

Our recent proposed framework, namely *GREENCOOL*, optimizes the active cooling path of microchannel-based iterlayer liquid cooled 3D MPSoCs to balance the thermal profile of the target 3D MPSoC while significantly reducing the active cooling energy demands [109]. This design-optimization methodology uses the concept of channel modulation, where we change the microchannel aspect ratio (channel width/channel height) to enhance the heat transfer capability from the target 3D MPSoC via changing the convective thermal resistance [110]. Using the conventional CMOS fabrication process for etching the channels, such as deep reactive iron etching [111], it is possible to modulate the width of the channel from inlet to outlet (and hence its aspect ratio) and create any kind of channel width profile, while keeping the height of the channels constant. Thus, channel width modulation requires only a change in the patterns on the masks used for etching channels amounting to minimal additional fabrication costs. To summarize, using careful design it is possible to modify the local channel aspect ratios so as to contain the pumping power while constraining the thermal gradients.

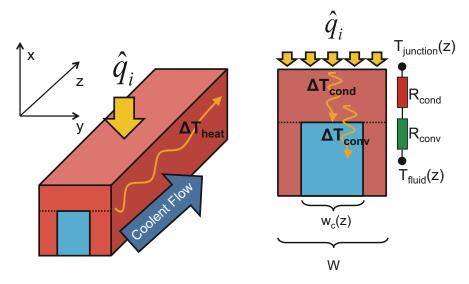

To understand how the channel width affects the change in temperature due to convection ( $\Delta T_{conv}$ ) in detail, an analysis is performed on a single microchannel shown in Fig. 16. We start by the following set of equations governing the Nusselt number (a dimensionless form of heat transfer coefficient), and the product of friction factor

Fig. 16 Test structure: a single microchannel cooling a strip of an IC with uniform heat flux distribution. The figure shows both the 3D and the cross-sectional views [109]

**Fig. 17**  $R_{conv}$  as a function of the channel width for the structure in Fig. 16

and Reynold's number for microchannels, under fully developed conditions [110]:

$$Nu = 8.235 \cdot (1 - 2.0421AR + 3.0853AR^{2} - 2.4765AR^{3} + 1.0578AR^{4} - 0.1861AR^{5})$$

$$fr \cdot Re = 24 \cdot (1 - 1.3553AR + 1.9467AR^{2} - 1.7012AR^{3} + 0.9564AR^{4} - 0.2537AR^{5}),$$

(27)

where AR is the aspect ratio reciprocal (height/width) of the channel. Using the Nusselt number, the heat transfer coefficient (a measure of the amount of heat transferred per unit area for one Kelvin difference in temperature between the fluid and the microchannel wall surface, expressed in  $W/m^2K$ ) can be written as:

$$h = \frac{k_{coolant} \cdot Nu}{d_h} \tag{28}$$

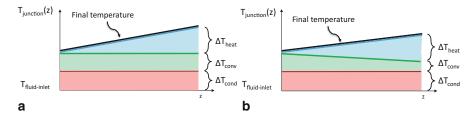

Fig. 18 Junction temperature distribution for the structure in Fig. 16. a With uniform non modulated channel width. b With modulated channel width to compensate for sensible heat absorption [109]

where  $k_{coolant}$  is the thermal conductivity of the coolant and  $d_h$  is the hydraulic diameter of channel. The effective heat transfer coefficient as seen by the junction looking down the channel from the top can be written by projecting the heat transfer coefficient above from the side wall surfaces onto the top as follows:

$$h_{eff} = h \frac{2 * H_C + w_C}{W} \tag{29}$$

where  $H_C$  is the height and  $w_C$  is the width of the channel, and W is the total width of the structure as shown in Fig. 16. The convective resistance  $R_{conv}$  for this structure can be obtained as a reciprocal of this quantity. The  $R_{conv}$  for this structure is plotted as a function of  $w_C$  in Fig. 17, assuming water as the coolant,  $H_C = 100 \, \mu \text{m}$ ,  $W = 100 \, \mu \text{m}$  and varying  $w_C$  from 10 to 50  $\mu \text{m}$ .

Figure 17 shows that the convective resistance (and also  $\Delta T_{conv}$ ) drops quickly as the channel width is reduced. Since the goal is to modify the convective resistance to compensate for  $\Delta T_{heat}$ , it can be postulated that the channel width must no longer be a constant but instead should be a function of the distance along the channel  $w_C(z)$ . The width must be larger near the inlet where the fluid temperature is low and smaller near the outlet where the fluid temperature is high. Hence, theoretically, for the case of uniform heat flux, it is possible to lower the final thermal gradient by steadily modulating the channel width from inlet to outlet, as shown in Fig. 18b.

GREENCOOL uses this principle in formulating an optimal control problem to find the optimal channel width profile for each microchannel, from the fluid inlet to outlet ports. The target of this optimization is to minimize the peak temperature and thermal gradients of the 3D MPSoC, as well as reducing the energy needed by cooling. When applied various 3D MPSoC architectures, significant thermal gradient reductions as well as cooling power savings, with respect to worst-case designs.

Fig. 19 Layout of the 3D-MPSoCs used in our experiments [113]

For instance, when *GREENCOOL* is applied to different architectural layouts of the UltraSPARC T1 Niagara MPSoC [112], a 31% thermal gradient reduction is observed. Figure 19 shows the layout of the different two-dies 3D-MPSoCs used in this experiment. The dies are of size 1 cm  $\times$  1.1 cm and the heat flux densities range from 8 to 64 W/cm² in the two dies. Further details about the floorplan and power dissipations can be found in pervious works [77, 96, 112].

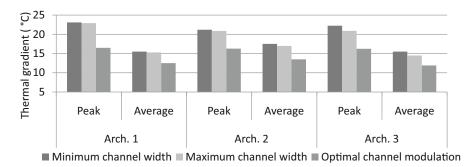

In this experiment, the worst-case (peak) power dissipation of the 3D-MPSoC functional elements [77, 96, 112] (obtained using measurements) are used in the optimization process. *GREENCOOL* achieves a thermal gradient reduction of 31 % (23 °C to 16 °C). When the peak heat flux levels were replaced by average values, this same optimal channel modulation configuration manages to reduce the thermal gradient by 21 % compared to the uniform channel width case. The thermal gradients obtained for the different cases and for various channel types are plotted in Fig. 20.

In another set of experiments to demonstrate the energy-efficiency of *GREEN-COOL*, significant cooling energy savings that reach up to 80 % has been achieved [109]. Furthermore, *GREENCOOL* aids in developing efficient cooling layout in the cases where uniform cavity utilization is infeasible.

Fig. 20 Thermal gradients observed in the different 3D-MPSoC architectures dissipating peak and average level heat fluxes, using maximum, minimum and optimally modulated channel widths [113]

**Fig. 21** Concept of server consolidation

#### 5 Power and Thermal Managements for Server Clusters

## 5.1 Conventional Solution to Minimize Power Consumption for Server Clusters

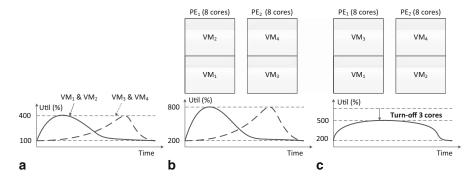

In datacenters, servers are normally severely under-utilized, less than 30% in more than 90% of the total time [3]. In addition, as explained in Sect. 3, the power consumption of servers is not proportional to the utilization, i.e., the idle power consumes around 50% of the peak power consumption. Due to the poor energy-proportionality, the power consumed by servers in datacenters can be reduced as we minimizes the number of active servers by packing workloads into the minimal number of active servers [46]. The technique is called *Server consolidation*. The key enabler to realize the solution is server virtualization, explained in Sect. 2.1, as it enables to migrate workloads easily by encapsulating workloads with a form of virtual machines (VMs) and run multiple VMs in a single physical server with the aid of hypervisor. Figure 21 shows the concept of the server consolidation in a virtualized server environment.

In the server consolidation, we need to take care such that the performance after the consolidation should not be degraded, or within an acceptable range. To achieve this goal, many works have developed the consolidation solutions such that the sum of the peak required utilization among co-located VMs does not exceed the server's capability [46]. However, as analyzed in many works [6], the peak utilization happens rarely and much higher than off-peak (e.g., 90th/95th/99th percentile) values. Thus,

the server consolidation based on the peak value makes us to lose the opportunity for further power savings. To overcome the conservative solution, some works [6, 47] presents server consolidation solution which packs VMs into servers based on offpeak (e.g., 90th/95th/99th percentile) of server utilization.

The advantage obtained from the server consolidation is obvious in terms of power savings. However, it may cause unexpected performance degradation due to the conflict of using shared resources among co-located VMs, especially last-level cache (LLC) [48, 49]. Tickoo et al. [49] analyzed how the performance is degraded as VMs are allocated to share LLC with others using SpecJBB and Sysbench benchmark suites in order to evaluate the amount of the performance degradation caused by different cache usage characteristics of co-located VMs. The results show that sharing LLC between two copies of VMs both hosting SpecJBB leads to  $\sim 30\%$  performance degradation while a case of sharing LLC between VMs hosting SpecJBB and Sysbench leads to  $\sim 20\%$  degradation. In [50], Govindan et al. characterize the amount of interference with a set of parameters, i.e., effective number of used sets and ways. Then, it presents a solution to allocate VMs by accounting for the amount of the interference such that the performance interference becomes minimized while meeting the required performance requirement.

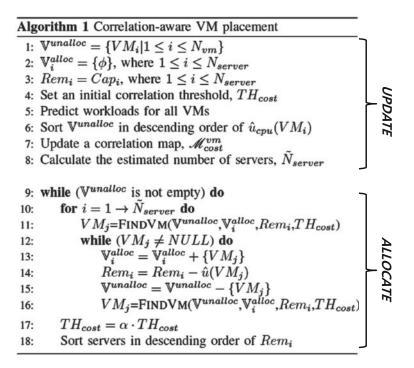

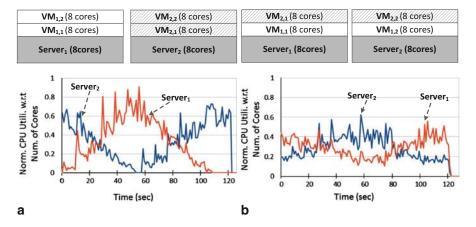

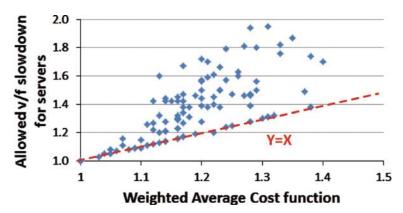

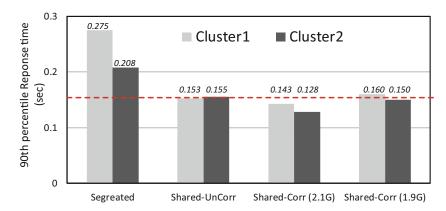

### 5.2 Correlation-Aware Power and Temperature Management