# Real-Time High-Resolution Multiple-Camera Depth Map Estimation Hardware and Its Applications

### THÈSE Nº 6573 (2015)

PRÉSENTÉE LE 16 AVRIL 2015

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DE SYSTÈMES MICROÉLECTRONIQUES PROGRAMME DOCTORAL EN GÉNIE ÉLECTRIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

### Abdulkadir AKIN

acceptée sur proposition du jury:

Prof. J.-Ph. Thiran, président du jury Prof. Y. Leblebici, Dr A. Schmid, directeurs de thèse Prof. L. Claesen, rapporteur Prof. P. Frossard, rapporteur Prof. J.-I. Guo, rapporteur

| Nature is not on the surface, it is in the depths.  Colors are an expression of these depths on the surface.  They rise from the roots of the world.  — Paul Cezanne                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                          |

| If one day, real-time depth perception of machines becomes always better than human, at that time, intelligence and learning ability of human will not be needed anymore to develop technology.  — Kadir |

|                                                                                                                                                                                                          |

|                                                                                                                                                                                                          |

| To my family                                                                                                                                                                                             |

|                                                                                                                                                                                                          |

### Acknowledgements

First of all, I would like to thank my thesis director Prof. Yusuf Leblebici who gave me the opportunity to pursue my research in Microelectronic Systems Laboratory (LSM). Prof. Leblebici always encouraged me to implement my creative ideas, and he always provided his aspiring guidance and advices. In addition, I am cordially thankful to him, since he established a laboratory with brilliant ambiance, friendship, collaboration and passion. I know that, the fabulous culture of this laboratory is an output of his intensive efforts, and the positive synergy of LSM led me to pursue successful research during my PhD studies.

I would like to thank my thesis co-director Dr. MER. Alexandre Schmid especially for his guidance on the organization of my research. His suggestions on task scheduling and risk/benefit analysis kept me on the correct research path. In addition, his valuable comments on my papers significantly helped me to have attractive publications.

I would like to thank my thesis committee members, Prof. Jean-Philippe Thiran, Prof. Luc Claesen, Prof. Jiun In Guo and Prof. Pascal Frossard, who have evaluated this thesis and provided constructive comments. I would like to thank Melinda Mischler, Corine Degott and Patricia Vonlanthen for their support in the administrative works at EPFL. I would like to thank Alain Vachoux for his technical helps and advices.

During my research, I have collaborated with several PhD students, master students, interns and engineers on different aspects of my studies. I would like to present my grateful thanks to my these precious friends and collaborators. First, I would like to thank master students that I supervised: İpek Baz for the algorithm development of two- and three-camera disparity estimation (DE), Luis Gaemperle for the development of ethernet interface of DE system and development of graphical user interface (GUI), Raffaele Capoccia for the three-camera DE hardware implementation, Jonathan Narinx for the ASIC implementation of two-camera DE hardware, Jonathan Masur for the hardware implementation of free viewpoint synthesis, and Halima Najibi for the hardware implementation of the Caltech rectification algorithm. In addition, I would like to thank interns that I supervised: Gremaud Xavier Louis for the improvement of GUI, İrem Boybat for the algorithm development of two-camera DE and compressed rectification, Baris Hüseyin Atakan for the algorithm development of two-camera DE, Elif Erdede for the implementation of enhanced omnidirectional image reconstruction

algorithm. Moreover, I would like to thank PhD students: Youngjoo Seo for the development of depth estimation based head/body tracking applications, Omer Cogal for his intensive collaboration on the development of ultra high resolution omnidirectional camera, and Kerem Seyid, Selman Ergünay, Hossein Afshari and Vladan Popovic for their useful technical helps, comments and advices. Furthermore, I would like to thank Tuğba Demirci for her co-supervision of Jonathan Narinx on ASIC implementation, Peter Brühlmeier for the design of all the PCB boards that are fabricated and used in the research, and Sylvain Hauser for the establishment of fabulous mechanical set-ups. While I was working with my collaborators, all the heavy work turned out just a fun thanks to their passion on their profession and friendship.

Being part of LSM gave me a chance to have great friends. Therefore I would like to extend my special thanks with former and current LSM members, especially Mustafa Kılıç, Gülperi Özsema, Can Baltacı, Zuhal Taşdemir, Şeniz Esra Küçük, Gözen Köklü, Clemens Nyffeler, Kiarash Gharibdoust, Nikola Katic, Mahsa Shoaran, Cosimo Aprile, Jury Sandrini, Gain Kim, Behnoush Attarimashalkoubeh, Reza Ranjandish, Elmira Shahrabi and Sebastian Rodriguez. I had a great time in Lausanne with my all friends. I would like to thank to Ece Boran, Ziya Köstereli, Ahmed Doğan, Nezihe Merve Gürel, Alp Yurtsever, Metin Kaycı, Ivan Beretta, Baran Gözcü, Florence Fraigneau, Emine Can, Enver Kılınç, Onur Yürüten, Ruben Braojos, Egeyar Bağcıoğlu, Elodie Lamothe, George Foustouskos and Özlem İpek for their friendship. The friendship of all these people made Lausanne a lovely city to me.

Finally, I would like to present my special thanks to my family, my mother Ayla, my father Ömer and my sisters Büşra, Şeyma and Elif Naz for their love and support during all my life. Particularly I want to thank again to my sister Elif Naz for the figure below that she drew using paint while she was 8 years old. While I was working on my thesis, she was upset that she could not have enough time to play with me. She told that she can help me to finish my works, then we would play some games together. I showed her the video results of my depth estimation system, then I asked her to draw a picture to summarize my work which I can put in my thesis. That was what I told just to make her busy, but now I keep my promise, here it is my beloved sister.

### **Abstract**

Depth information is used in a variety of 3D based signal processing applications such as autonomous navigation of robots and driving systems, 3D geographic information systems, object detection and tracking, computer games, 3D television, and free view-point synthesis. These applications require high accuracy and speed performances for depth estimation. Depth maps can be generated using disparity estimation methods, which are obtained from stereo matching between multiple images.

The computational complexity of disparity estimation algorithms and the need of large size and bandwidth for the external and internal memory make the real-time processing of disparity estimation challenging, especially for high resolution images. This thesis proposes a high-resolution high-quality multiple-camera depth map estimation hardware. The proposed hardware is verified in real-time with a complete system from the initial image capture to the display and applications. The details of the complete system are presented.

This thesis proposes binocular and trinocular hardware-oriented adaptive window size disparity estimation algorithms, which target high-resolution video with high-quality disparity results. The algorithms are carefully designed to be suitable to real-time hardware implementation by allowing efficient parallel and local processing while providing high-quality results.

The proposed binocular and trinocular disparity estimation algorithms are implemented in hardware. The hardware implementation of the proposed binocular disparity estimation algorithm can process 60 frames per second on a Virtex-5 FPGA at a  $1024 \times 768$  XGA video resolution for a 128 pixel disparity range. The hardware implementation of the proposed trinocular disparity estimation algorithm can process 55 frames per second on a Virtex-7 FPGA for the same resolution and disparity range. The implementation details of these efficient binocular and trinocular disparity estimation hardware are presented. The proposed binocular disparity estimation hardware provides best quality compared to existing high-resolution disparity estimation hardware implementations.

Rectification is an important pre-processing step of the disparity estimation to remove the distortions in the lens and to solve the camera misalignments. A novel compressed-look up

table based rectification algorithm and its real-time hardware implementation are presented. The proposed compression scheme is able to fit the look-up-tables into the on-chip BRAMs of the Virtex-5 FPGA. The low-complexity decompression process of the rectification hardware utilizes a negligible amount of LUT and DFF resources of the FPGA while it does not require the existence of external memory.

The first real-time high-resolution free viewpoint synthesis hardware utilizing three-camera disparity estimation is presented. The proposed hardware generates high-quality free viewpoint video at 55 frames per second using a Virtex-7 FPGA at a  $1024 \times 768$  XGA video resolution for any horizontally aligned arbitrary camera positioned between the leftmost and rightmost physical cameras.

The full embedded system of the depth estimation is explained. The presented embedded system transfers disparity results together with synchronized RGB pixels to the PC for application development. Several real-time applications are developed on a PC using the obtained RGB+D results. The implemented depth estimation based real-time software applications are: depth based image thresholding, speed and distance measurement, head-hands-shoulders tracking, virtual mouse using hand tracking and face tracking integrated with free viewpoint synthesis.

The proposed binocular disparity estimation hardware is implemented in an ASIC. The ASIC implementation of disparity estimation imposes additional constraints with respect to the FPGA implementation. These restrictions, their implemented efficient solutions and the ASIC implementation results are presented.

In addition, a very high-resolution (82.3 MP)  $360^{\circ} \times 100^{\circ}$  omnidirectional multiple camera system is proposed. The hemispherical camera system is able to view the target locations close to horizontal plane with more than two cameras. Therefore, it can be used in high-resolution  $360^{\circ}$  depth map estimation and its applications in the future.

**Keywords:** Depth Estimation, Disparity Estimation, Rectification, Free Viewpoint Synthesis, Multiple Camera, Hardware Implementation, Real-Time, FPGA, ASIC.

### Résumé

L'estimation de la profondeur (distance mesurée depuis l'observateur par rapport à chaque objet) est utilisée dans de multiples applications de traitement de signaux basés sur la 3D, comme par exemple les systèmes de pilotage automatique de robots et de véhicules, les systèmes d'information géographique 3D, la détection et le suivi d'objets, les jeux d'ordinateurs, la télévision 3D ou encore la synthèse d'images d'un point de vue virtuel. Ces applications nécessitent de grandes performances en précision et en vitesse dans l'estimation de profondeur de champ. En utilisant des méthodes d'estimation de la disparité obtenues à l'aide d'une comparaison entre plusieurs images stéréo, une cartographie complète de cette profondeur peut être calculée.

La complexité de calcul des algorithmes d'estimation de la disparité ainsi que le besoin de mémoires internes et externes de grande capacité et à forte bande passante rendent difficile le traitement en temps réel de l'estimation de la disparité, particulièrement pour les images à haute résolution. Cette thèse propose un hardware d'estimation de la cartographie de profondeur à haute résolution et de haute qualité utilisant plusieurs caméras. Ce dernier est vérifié en temps réel avec un système complet, depuis la capture de l'image initiale jusqu'à l'affichage et ses applications correspondantes. Tous les détails concernant ce système sont présentés.

Cette thèse propose des algorithmes binoculaires et trinoculaires d'estimation de la disparité orientés hardware à l'aide de fenêtres de tailles adaptatives qui ciblent la vidéo de haute résolution avec des résultats de haute qualité pour l'estimation de la profondeur. Les algorithmes sont soigneusement développés pour être adaptés à une implémentation en temps réel, permettant un calcul en parallèle efficace et local, tout en fournissant des résultats de haute qualité.

Les algorithmes d'estimation de disparité binoculaires et trinoculaires proposés sont implémentés en hardware. L'implémentation hardware de l'algorithme d'estimation de la disparité binoculaire proposé peut traiter 60 images par seconde sur une FPGA Virtex-5 dans une résolution vidéo XGA de  $1024 \times 768$  pixels pour une plage de disparité de 128 pixels. L'implémentation hardware de l'algorithme d'estimation de la disparité trinoculaire proposé peut traiter 55 images par seconde sur une FPGA Virtex-7, pour la même résolution et la

même plage de la disparité. Les détails de l'implémentation hardware de ces deux algorithmes sont présentés. Le matériel proposé délivre la meilleure qualité d'estimation de disparité comparée aux implémentations hardware existantes.

La rectification est une étape de prétraitement importante pour estimer la disparité afin de supprimer les distorsions dans les lentilles et de corriger l'alignement imparfait des caméras. Un nouvel algorithme, basé sur table de transcorrespondance (LUT) compressée, ainsi que son implémentation dans un hardware temps réel sont présentés. Un algorithme de compression est proposé et est capable d'accommoder les tables de transcorrespondance dans les BRAMs internes de la FPGA Virtex-5. Grâce à la faible complexité du processus de décompression, le hardware de la rectification utilise une quantité négligeable de LUTs et de DFFs de la FPGA, tout en ne nécessitant aucune mémoire externe.

Le premier hardware en temps réel et à haute résolution pour la synthèse de point de vue virtuel utilisant l'estimation de la disparité à trois caméras est présenté. Le hardware proposé génère une vidéo à point de vue virtuel de haute qualité à 55 images par seconde, utilisant la FPGA Virtex-7 à une résolution video XGA de 1024×768, pour toute caméra virtuelle alignée horizontalement entre les caméras physiques situées aux extrémités gauches et droites.

Le système embarqué complet d'estimation de la profondeur est présenté. Ce dernier transfère les résultats de manière synchrone avec les pixels RGB vers le PC pour le développement d'applications. Plusieurs applications temps réel sont développées sur PC en utilisant les résultats RGB+D obtenus. Les applications software implémentées sur l'estimation de profondeur de champ en temps réel sont les suivantes : seuillage d'image de profondeur de champ, mesure de la vitesse et de la distance, suivi de la tête, des mains et des épaules, souris virtuelle en utilisant le suivi de la main, suivi de la tête intégré avec la synthèse de point de vue virtuel.

Le hardware d'estimation de la profondeur binoculaire est implémenté dans un ASIC. Cette implémentation en ASIC impose des contraintes additionnelles par rapport à l'implémentation sur FPGA. Ces restrictions et leurs solutions efficaces, ainsi que les résultats de cette implémentation, sont présentés dans cette thèse.

De plus, un système omnidirectionnel  $360^\circ \times 100^\circ$  à caméras multiples de très haute résolution (82.3 MP) est proposé. Ce système de caméra hémisphérique est capable de voir les emplacements cibles proches du plan horizontal avec plus de deux caméras. Il peut donc être utilisé dans une estimation de profondeur de  $360^\circ$  à très haute-résolution dans le futur.

Mots clefs : Estimation de la profondeur, Estimation de la disparité, Rectification, Synthèse de point de vue virtuel, caméras multiples, implémentation hardware, temps réel, FPGA, ASIC.

## **Contents**

| Ac | cknov | wledgements                                                                 | j    |

|----|-------|-----------------------------------------------------------------------------|------|

| Ał | ostra | ct (English/Français)                                                       | iii  |

| Li | st of | figures                                                                     | xi   |

| Li | st of | tables                                                                      | kvii |

| 1  | Intr  | roduction                                                                   | 1    |

|    | 1.1   | Large Angle of View Image Capture Systems                                   | 2    |

|    | 1.2   | Depth Estimation Systems                                                    | 4    |

|    | 1.3   | Contribution of the Thesis                                                  | 8    |

|    |       | 1.3.1 Proposed Depth Map Estimation Systems                                 | 8    |

|    |       | 1.3.2 Proposed Large Angle of View Image Capture and Reconstruction Systems | 14   |

|    | 1.4   | Thesis organization                                                         | 14   |

| 2  | Stat  | te of the Art                                                               | 15   |

|    | 2.1   | Hemispherical Multiple Camera Image Reconstruction Systems                  | 15   |

|    | 2.2   | Binocular Stereo Matching Algorithms and Their Hardware Implementations .   | 19   |

|    |       | 2.2.1 Camera Calibration                                                    | 22   |

|    |       | 2.2.2 Rectification                                                         | 26   |

|    |       | 2.2.3 Matching Cost Computation                                             | 27   |

|    |       | 2.2.4 Cost Aggregation                                                      | 30   |

|    |       | 2.2.5 Disparity Selection and Optimization                                  | 30   |

|    |       | 2.2.6 Disparity Refinement                                                  | 32   |

|    | 2.3   | Trinocular Stereo Matching Algorithms and Their Hardware Implementations .  | 33   |

|    | 2.4   | Thesis Goals                                                                | 36   |

| 3  | Bin   | ocular Adaptive Window Size Disparity Estimation Algorithm and Its Hardware |      |

|    | Imp   | plementation                                                                | 39   |

|    | 3.1   | Binocular Hardware-Oriented Adaptive Window Size Disparity Estimation       |      |

|    |       | Algorithm                                                                   | 39   |

|    |       | 3.1.1 Window Size Determination                                             | 40   |

### **Contents**

|   |     | 3.1.2 Disparity Voting                                                                 | 41  |

|---|-----|----------------------------------------------------------------------------------------|-----|

|   |     | 3.1.3 Disparity Refinement                                                             | 43  |

|   | 3.2 | Hardware Implementation of Proposed Binocular AWDE Algorithm                           | 44  |

|   |     | 3.2.1 Overview                                                                         | 44  |

|   |     | 3.2.2 Data Allocation and Disparity Voting                                             | 46  |

|   |     | 3.2.3 Disparity Refinement                                                             | 51  |

|   | 3.3 | Iterative Refinement for the Enhanced AWDE implementation $\ \ldots \ \ldots \ \ldots$ | 52  |

|   | 3.4 | Implementation Results                                                                 | 54  |

| 4 |     | nocular Adaptive Window Size Disparity Estimation Algorithm and Its Hardwar            | e   |

|   | Imp | olementation                                                                           | 63  |

|   | 4.1 | Trinocular Hardware-Oriented Adaptive Window Size Disparity Estimation                 |     |

|   |     | Algorithm                                                                              | 63  |

|   | 4.2 | Trinocular Adaptive Window Size Disparity Estimation Hardware                          | 65  |

|   | 4.3 | Implementation Results                                                                 | 69  |

| 5 |     | npressed Look-Up-Table Based Rectification Algorithms and Their Hardwar                | e   |

|   | -   | olementations                                                                          | 73  |

|   | 5.1 | Compressed Look-Up-Table based Rectification Algorithm                                 | 74  |

|   | 5.2 | Real-Time De-Compression Hardware of CLUTR                                             | 82  |

|   | 5.3 | Limitations of the CLUTR                                                               | 85  |

|   | 5.4 | Enhanced Compressed Look-Up-Table based Rectification Algorithm                        | 88  |

|   | 5.5 | Real-Time De-Compression Hardware of E-CLUTR                                           | 91  |

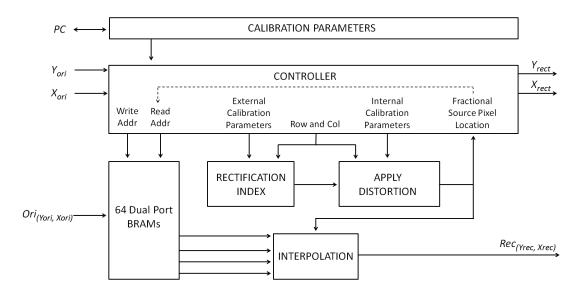

|   | 5.6 | Real-Time Hardware of Caltech Rectification                                            | 94  |

|   | 5.7 | Implementation Results                                                                 | 96  |

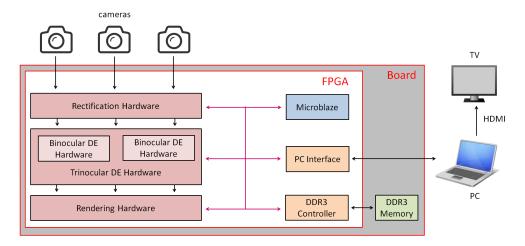

| 6 | Eml | bedded System for Depth Map Estimation                                                 | 103 |

|   | 6.1 | The Overview of the Depth Map Estimation System                                        | 103 |

|   | 6.2 | Video Processing Hardware Cores and Circuits                                           | 104 |

|   | 6.3 | Peripherals of the Embedded System                                                     | 109 |

|   | 6.4 | Embedded Software                                                                      | 116 |

| 7 | Har | dware and Software based Applications of Disparity Estimation                          | 119 |

|   | 7.1 | Free View Synthesis Hardware Using Trinocular Disparity Estimation                     | 119 |

|   |     | 7.1.1 Hardware-Oriented Three-Camera Free Viewpoint Synthesis Algorithm                | 119 |

|   |     | 7.1.2 Real-Time Free Viewpoint Synthesis Hardware                                      | 122 |

|   |     | 7.1.3 Implementation Results                                                           | 125 |

|   | 7.2 | System GUI and Software Based Real-Time Applications                                   | 127 |

|   |     | 7.2.1 Capture and the display of the video                                             | 127 |

|   |     | 7.2.2 Front-end of the GUI                                                             | 128 |

|   |     | 7.2.3 Software based real-time applications                                            | 129 |

| 8  | ASI   | C Implementation of Binocular Disparity Estimation                        | 133 |

|----|-------|---------------------------------------------------------------------------|-----|

|    | 8.1   | Disparity Estimation ASIC Specifications                                  | 133 |

|    | 8.2   | Adaptation of Disparity Estimation Hardware for ASIC                      | 141 |

|    | 8.3   | ASIC Design                                                               | 144 |

|    |       | 8.3.1 Synthesis                                                           | 145 |

|    |       | 8.3.2 Placement and Routing                                               | 146 |

|    | 8.4   | Test System                                                               | 151 |

| 9  | Hig   | h-Quality Omnidirectional Multi-Camera Systems                            | 153 |

|    | 9.1   | Enhanced Omnidirectional Image Reconstruction Algorithm and Its Real-Time |     |

|    |       | Hardware Implementation                                                   | 153 |

|    |       | 9.1.1 Equal Area Distribution Algorithm                                   | 153 |

|    |       | 9.1.2 Hardware Implementation of Equal Area Distribution Algorithm        | 157 |

|    |       | 9.1.3 Implementation Results                                              | 162 |

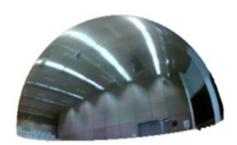

|    | 9.2   | Giga-Eye Camera                                                           | 163 |

|    |       | 9.2.1 System Parameters and Requirements                                  | 164 |

|    |       | 9.2.2 System Architecture                                                 | 167 |

|    |       | 9.2.3 Implementation Results                                              | 170 |

| 10 | Con   | nclusion                                                                  | 175 |

| A  | Hig   | h-Resolution Visual Results of Proposed Systems                           | 183 |

|    | A.1   | Visual Results of the Depth Estimation System                             | 183 |

|    | A.2   | Visual Results of the Giga-Eye Multiple-Camera System                     | 183 |

| Bi | bliog | graphy                                                                    | 192 |

| Ab | brev  | viations                                                                  | 193 |

| Cu | ırric | ulum Vitae                                                                | 197 |

# **List of Figures**

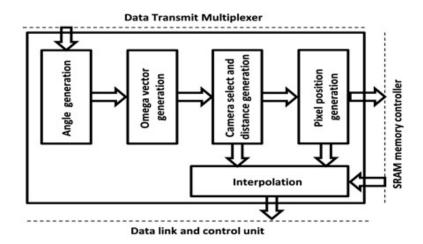

| 1.1  | Simplified block diagram of the complete depth map estimation system                                      | ç  |

|------|-----------------------------------------------------------------------------------------------------------|----|

| 2.1  | Ladybug3 multiple camera system                                                                           | 16 |

| 2.2  | R7 multiple camera system of Google for Street View application                                           | 16 |

| 2.3  | Panoptic camera                                                                                           | 17 |

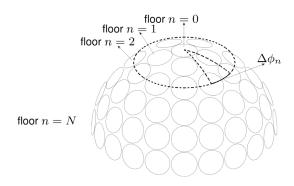

| 2.4  | Hemispherical structure with multiple floors                                                              | 18 |

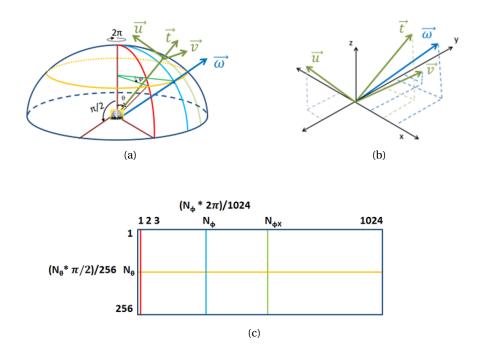

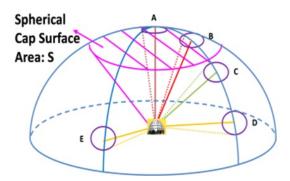

| 2.5  | (a) hemispherical surface showing $\theta$ and $\varphi$ angles and unit vectors used                     |    |

|      | in omnidirectional image reconstruction calculations, (b) $\omega$ vector and                             |    |

|      | corresponding unit vectors; $t$ (focus direction of the camera), $u$ (vertical direction                  |    |

|      | in the pixel representation of the camera), $\nu$ (horizontal direction in the pixel                      |    |

|      | representation of the camera) (c) 2D reconstruction using linear pixelization $$ .                        | 18 |

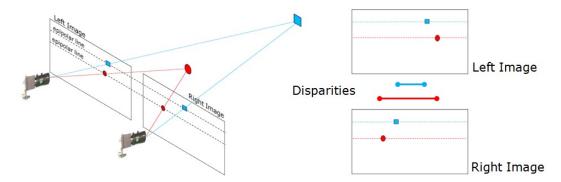

| 2.6  | Inverse relationship between the depth and disparity                                                      | 19 |

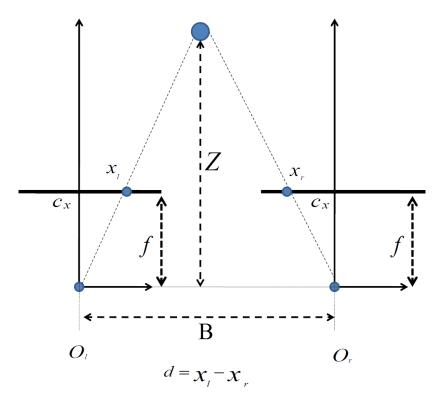

| 2.7  | Geometrical relationship between disparity and depth                                                      | 20 |

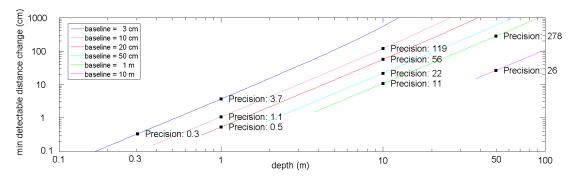

| 2.8  | $Distance\ measurement\ precision\ of\ disparity\ estimation\ based\ depth\ estimation.$                  | 21 |

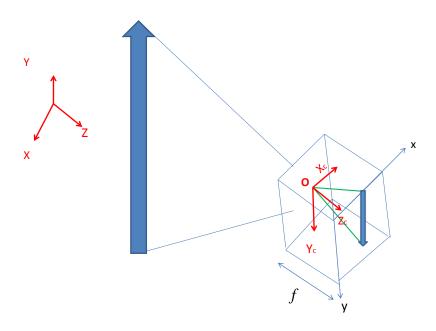

| 2.9  | Coordinate systems for pinhole camera model                                                               | 23 |

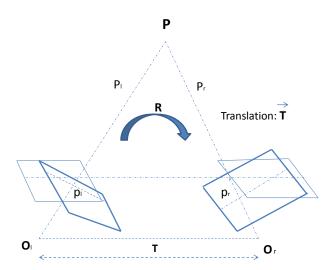

| 2.10 | Mathematical alignment of the two cameras into an unique image plane                                      | 26 |

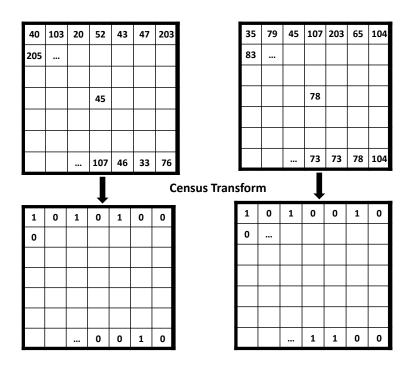

| 2.11 | Census transform computation                                                                              | 29 |

| 2.12 | Disparity selection                                                                                       | 31 |

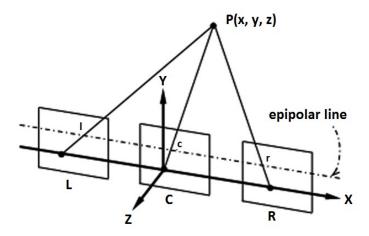

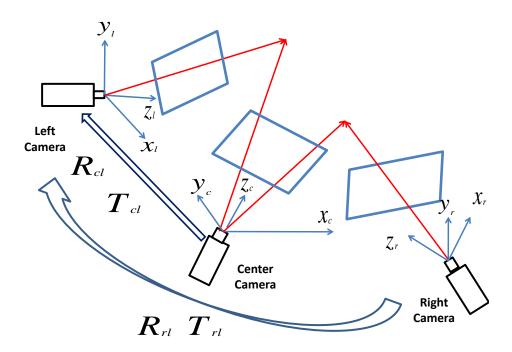

| 2.13 | Collinear placement of three cameras for disparity estimation                                             | 33 |

| 2.14 | Triangular placement of three cameras for disparity estimation                                            | 33 |

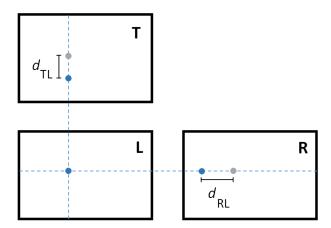

| 2.15 | $Geometrical\ relationship\ between\ the\ cameras\ of\ the\ trinocular\ stereo\ system\ .$                | 34 |

| 3.1  | 9 selected pixels in a block for BW-SAD calculation. 49 pixels in a block are                             |    |

|      | searched in parallel in hardware.                                                                         | 40 |

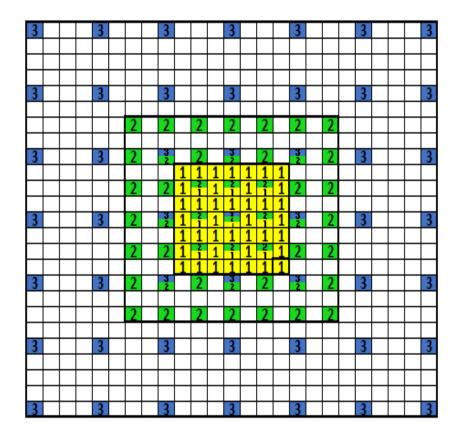

| 3.2  | 49 selected pixels of adaptive windows (yellow (1): $7 \times 7$ , green (2): $13 \times 13$ and          |    |

|      | blue (3): 25×25)                                                                                          | 41 |

| 3.3  | Examples for selecting 17 contributing pixels for $7 \times 7$ , $13 \times 13$ and $25 \times 25$ window |    |

|      | sizes during the disparity refinement process (yellow (1): $7 \times 7$ , green (2): $13 \times 13$       |    |

|      | and blue (3): 25×25 )                                                                                     | 43 |

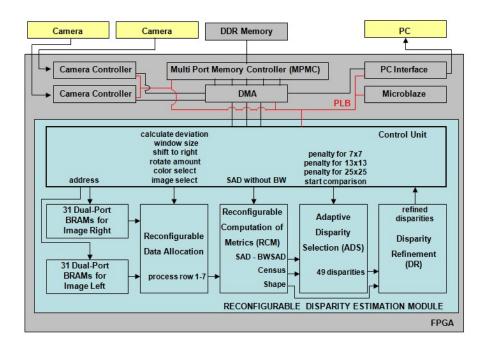

| 3.4  | Top level block diagram of the disparity estimation module                                                | 45 |

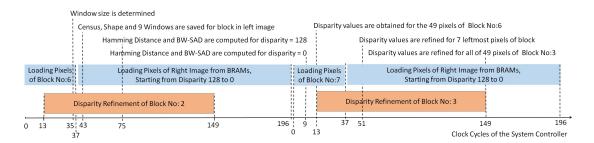

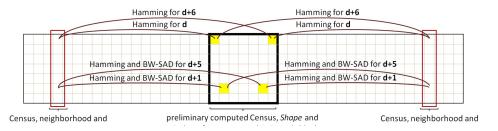

| 3.5  | Timing diagram of the system                                                                              | 46 |

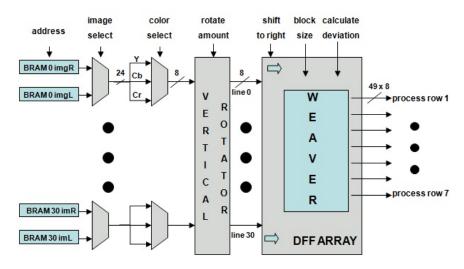

| 3.6  | Block diagram of the Reconfigurable Data Allocation Module                                                | 46 |

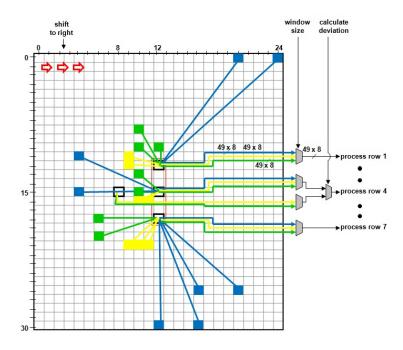

| 3.7  | DFF Array and the Weaver (yellow: $7 \times 7$ , green: $13 \times 13$ and blue: $25 \times 25$ )                                         | 47 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

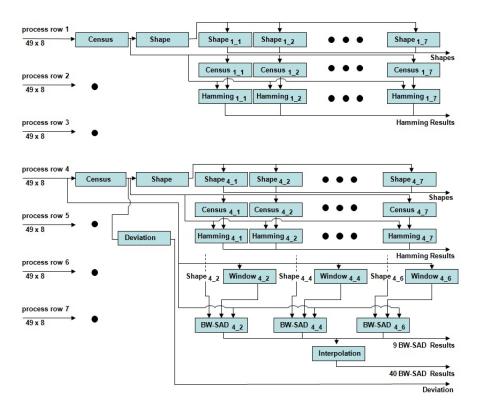

| 3.8  | Block diagram of the Reconfigurable Computation of Metrics                                                                                | 49 |

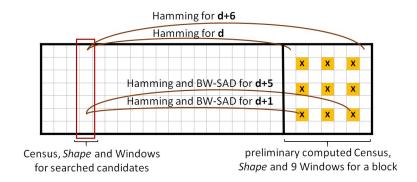

| 3.9  | Processing Scheme ("x" indicates 9 selected pixels in a block for BW-SAD                                                                  |    |

|      | calculations)                                                                                                                             | 49 |

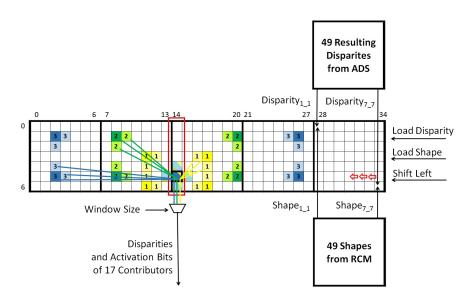

| 3.10 | Disparity Refinement-Array of the Disparity Refinement Module (yellow (1): $7 \times 7$ ,                                                 |    |

|      | green (2): $13 \times 13$ and blue (3): $25 \times 25$ )                                                                                  | 51 |

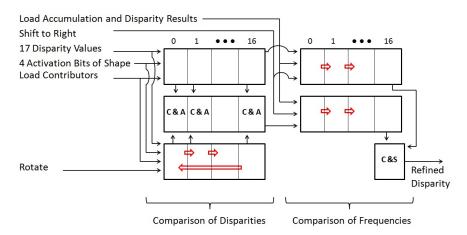

| 3.11 | Processing Element of the Disparity Refinement Module. The Highest Frequency                                                              |    |

|      | Selection Module includes seven of these DR-PE elements                                                                                   | 52 |

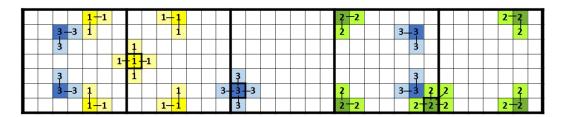

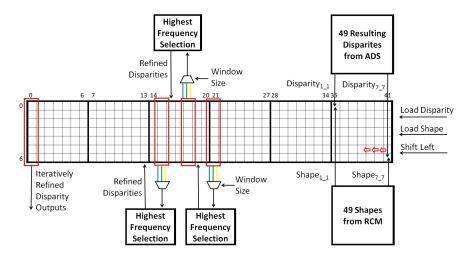

| 3.12 | DR-Array of the Iterative Disparity Refinement Module (yellow line: $7 \times 17$                                                         |    |

|      | candidates for $7 \times 7$ window, green line: candidates for $13 \times 13$ , and blue line:                                            |    |

|      | candidates for $25 \times 25$ )                                                                                                           | 53 |

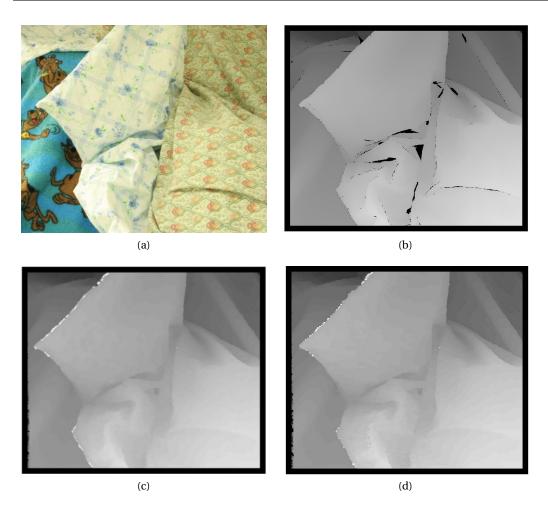

| 3.13 | Visual disparity estimation results of AWDE and AWDE-IR algorithms for HR                                                                 |    |

|      | benchmark Clothes. Black regions in the ground truths are not taken into                                                                  |    |

|      | account for the error computations as explained in Middlebury evaluation. (a)                                                             |    |

|      | left image (b) ground truth (c) DE result of AWDE (d) DE result of AWDE-IR                                                                | 58 |

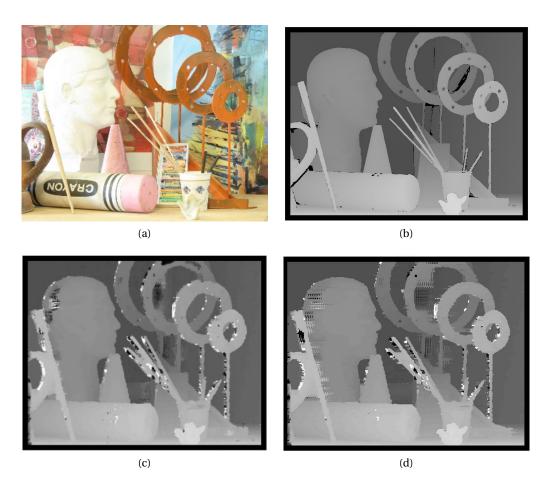

| 3.14 | Visual disparity estimation results of AWDE and AWDE-IR algorithms for HR                                                                 |    |

|      | benchmark Art. Black regions in the ground truths are not taken into account                                                              |    |

|      | for the error computations as explained in Middlebury evaluation. (a) left image                                                          |    |

|      | (b) ground truth (c) DE result of AWDE (d) DE result of AWDE-IR                                                                           | 59 |

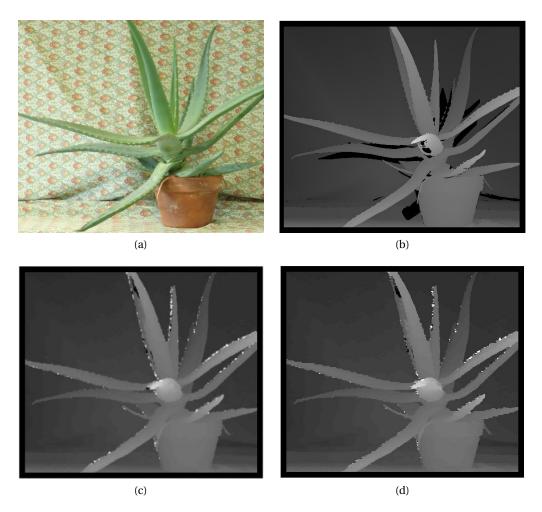

| 3.15 | Visual disparity estimation results of AWDE and AWDE-IR algorithms for HR                                                                 |    |

|      | benchmark Aloe. Black regions in the ground truths are not taken into account                                                             |    |

|      | for the error computations as explained in Middlebury evaluation. (a) left image                                                          | co |

| 0.10 | (b) ground truth (c) DE result of AWDE (d) DE result of AWDE-IR                                                                           | 60 |

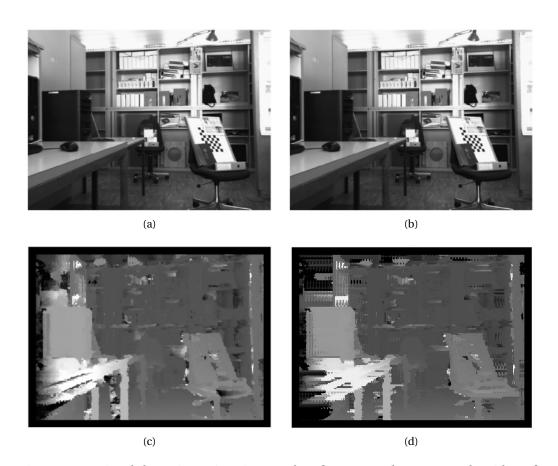

| 3.16 | Visual disparity estimation results of AWDE and AWDE-IR algorithms for the                                                                |    |

|      | 1024 × 768 resolution pictures captured by the implemented stereo camera                                                                  |    |

|      | system. The ground truth for these images is not available. (a) left image (b) right image (c) DE result of AWDE (d) DE result of AWDE-IR | 61 |

|      | right image (c) DE result of AWDE (d) DE result of AWDE-ik                                                                                | 01 |

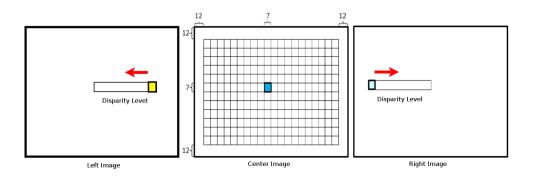

| 4.1  | Matching directions of the T-AWDE algorithm                                                                                               | 64 |

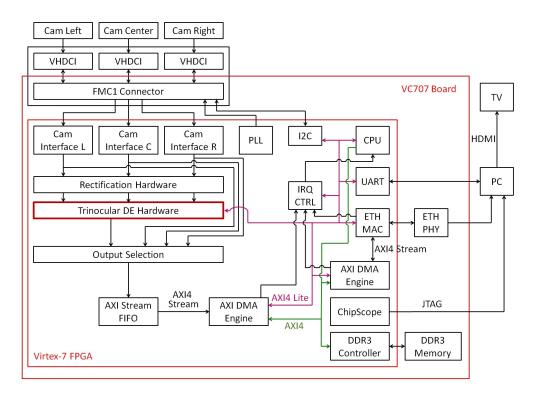

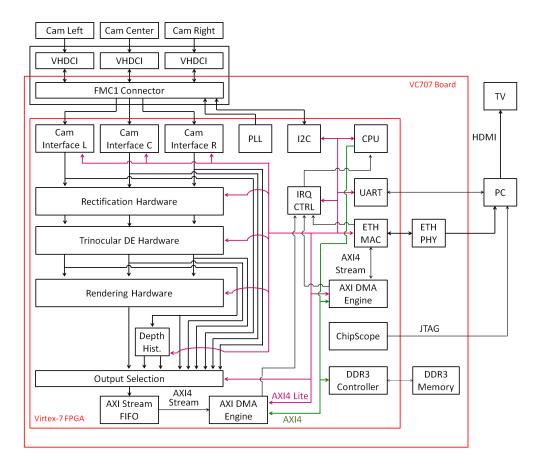

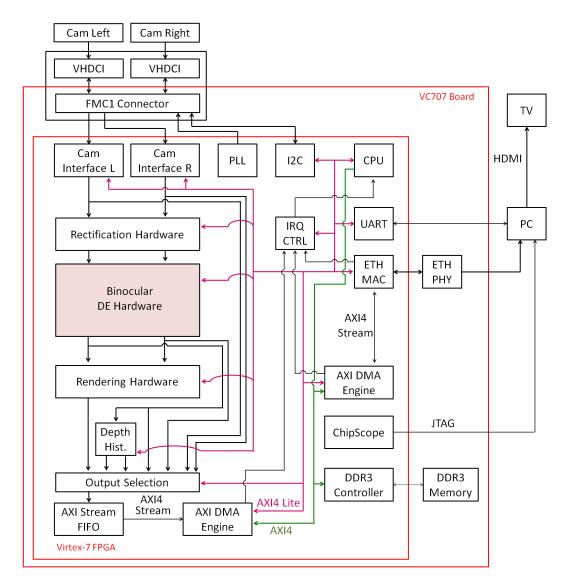

| 4.2  | Block diagram of the full system                                                                                                          | 66 |

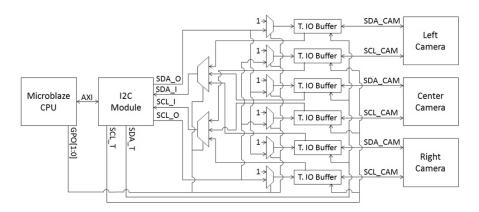

| 4.3  | $I^2C$ multiplexing hardware (resistors and level-shifters are not drawn)                                                                 | 67 |

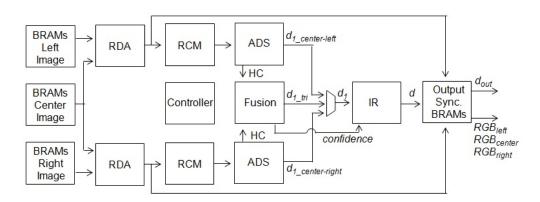

| 4.4  | Block diagram of trinocular DE hardware                                                                                                   | 68 |

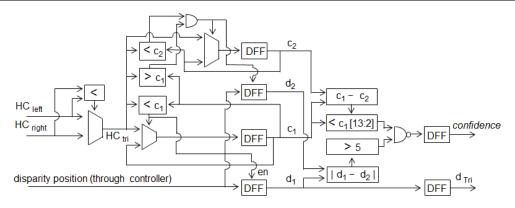

| 4.5  | Parallel processing scheme for two pairs                                                                                                  | 69 |

| 4.6  | Processing element of the fusion module (PE-F). The fusion module includes 49                                                             |    |

|      | PE-F elements.                                                                                                                            | 70 |

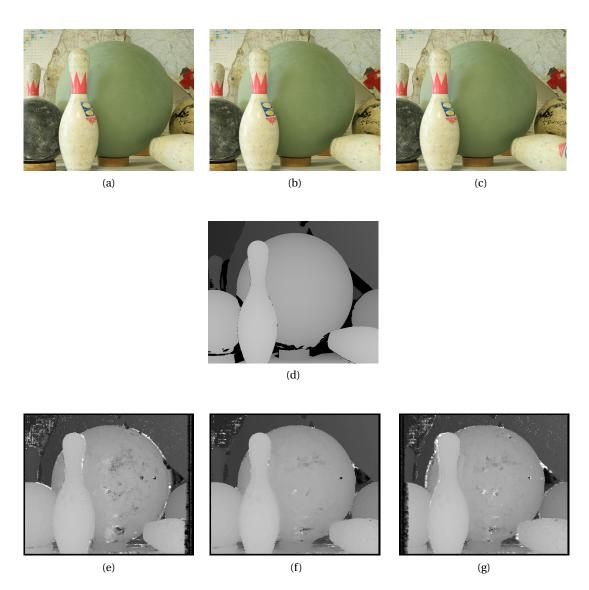

| 4.7  | DE results obtained by MATLAB for Middlebury benchmarck image set                                                                         |    |

|      | "Bowling2" (a) Left Image (b) Center Image (c) Right Image (d) Ground Truth                                                               |    |

|      | (black pixels are ignorable) (e) IR-AWDE for center-left (18.01%) (f) T-AWDE                                                              |    |

|      | (9.41%) (g) IR- AWDE for center-right (15.60%)                                                                                            | 71 |

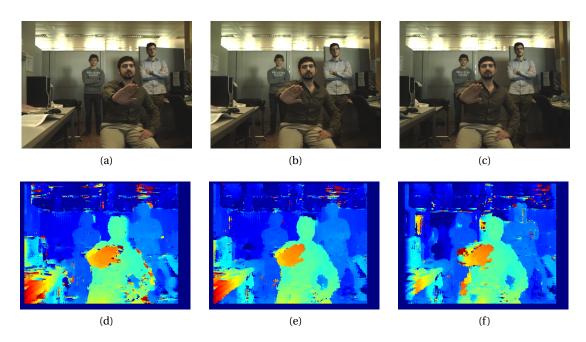

| 4.8  | Real-time snapshots captured by the proposed system. A ground truth for these                                                             |    |

|      | images is not available. (a) Left Image (b) Center Image (c) Right Image (d) AWDE                                                         |    |

|      | for center-left (e) T-AWDE (f) AWDE for center-right                                                                                      | 72 |

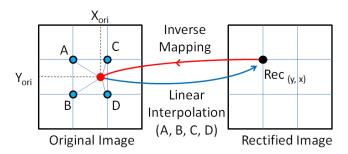

| 5.1         | Inverse mapping with fractional precision coordinates. Corners indicate integer pixel coordinates                                                                                                                                                                                                         | 7 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 5.2         | Forward mapping with fractional precision coordinates                                                                                                                                                                                                                                                     | 7 |

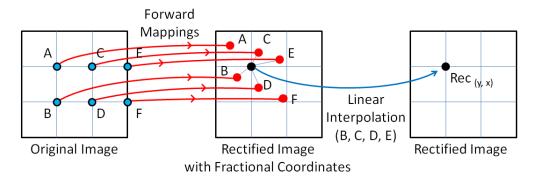

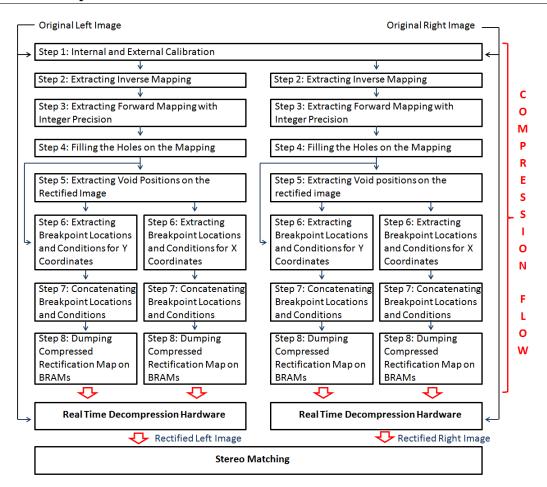

| 5.3         | Flow-chart of the proposed compressed look-up-table based stereo image                                                                                                                                                                                                                                    |   |

|             | rectification process                                                                                                                                                                                                                                                                                     | 7 |

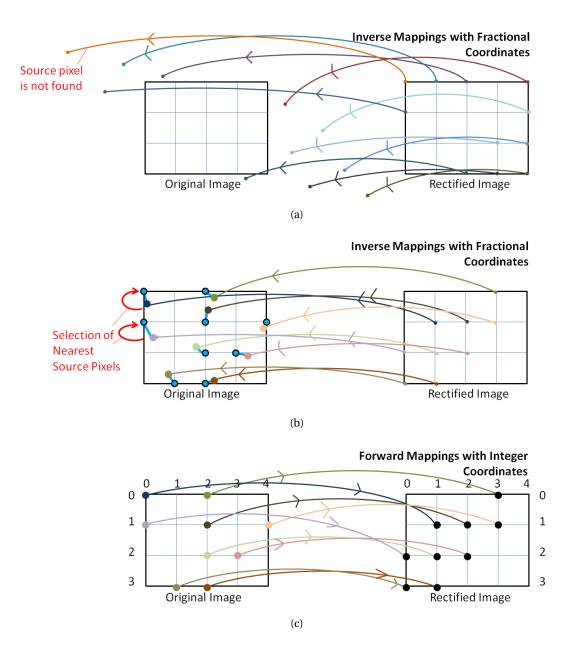

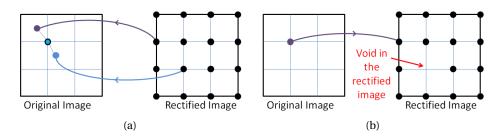

| 5.4         | Third step of the compression flow (a) Due to the 3D rotation, some of the pixels in the rectified image cannot be related to their source pixels in the original image (b) selection of nearest source pixels from fractional inverse mapping (c) extraction of forward mapping with integer coordinates | 7 |

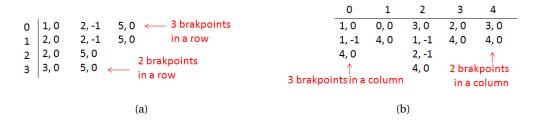

| 5.5         | Integer coordinate precision forward mapping look-up-tables after the third step. Regular orders are shown with red ellipses (a) mapping of Y coordinates (b) mapping of X coordinates                                                                                                                    | 7 |

| 5.6         | Coded regular orders after the third step (a) coded mapping of Y coordinates (b) coded mapping of X coordinates                                                                                                                                                                                           | 7 |

| 5.7         | Look-up-tables after filling the NT pixels using the fourth step (a) mapping of Y                                                                                                                                                                                                                         | • |

|             | coordinates (b) mapping of X coordinates                                                                                                                                                                                                                                                                  | 7 |

| 5.8         | Coded regular orders after filling the NT pixels using the fourth step (a) coded mapping of Y coordinates (b) coded mapping of X coordinates                                                                                                                                                              | 7 |

| 5.9         | Visualization of the reason for the voids in the rectified image (a) inverse mappings with fractional coordinates (b) forward mapping with integer                                                                                                                                                        |   |

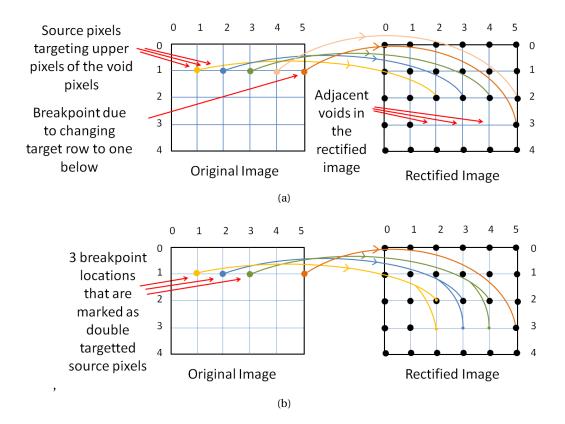

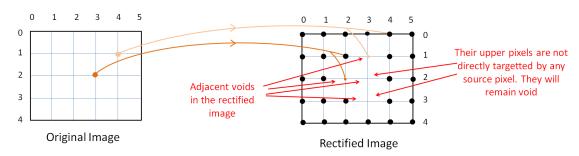

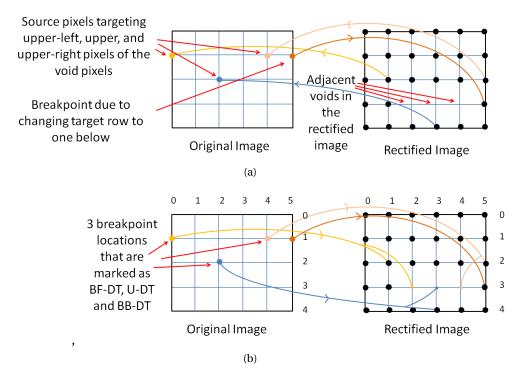

|             | coordinate                                                                                                                                                                                                                                                                                                | 8 |

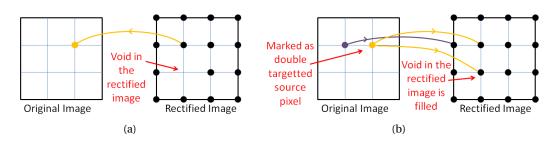

| 5.10        | Filling the voids in the rectified image in the fifth step (a) finding the source                                                                                                                                                                                                                         |   |

|             | location of a pixel at one row above the void (b) marking the source pixel as                                                                                                                                                                                                                             |   |

|             | double targeted pixel                                                                                                                                                                                                                                                                                     | 8 |

| 5.11        | Coding the behavior of breakpoints at the sixth step (a) coded mapping of Y                                                                                                                                                                                                                               |   |

| <b>5</b> 10 | coordinates (b) coded mapping of X coordinates                                                                                                                                                                                                                                                            | 8 |

| 5.12        | Concatenation of the locations and behaviors at the seventh step (a) for the                                                                                                                                                                                                                              |   |

| F 10        | mapping of Y coordinates (b) for the mapping of X coordinates                                                                                                                                                                                                                                             | 8 |

|             | Utilization example of the proposed rectification hardware                                                                                                                                                                                                                                                | 8 |

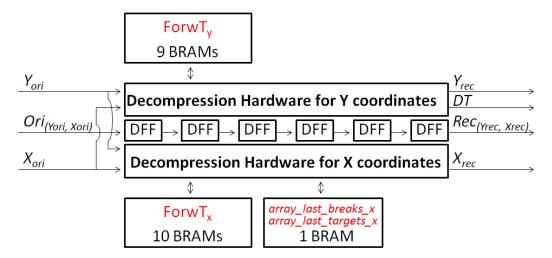

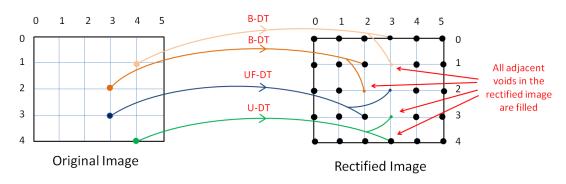

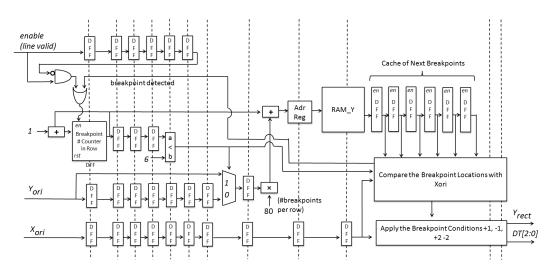

|             | Top-level block diagram of the proposed rectification hardware of CLUTR                                                                                                                                                                                                                                   | 8 |

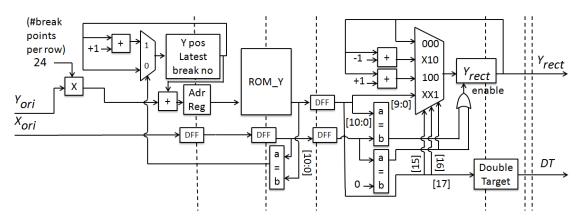

| 5.15        | Block diagram of the proposed rectification hardware for decompressing the                                                                                                                                                                                                                                | r |

| F 10        | table of Y coordinates. Pipeline stages are presented with dashed lines                                                                                                                                                                                                                                   | 8 |

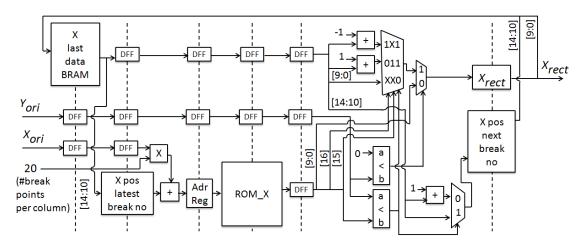

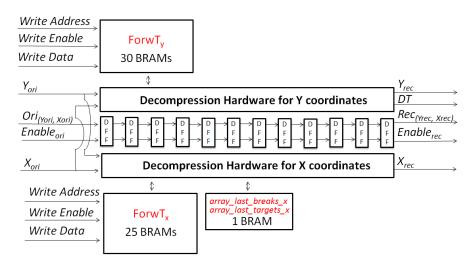

| 5.16        | Block diagram of the proposed rectification hardware for decompressing the table of X coordinates                                                                                                                                                                                                         | c |

| 5 17        | Visualization of the breakpoint frequency capacity of the X and Y coordinate                                                                                                                                                                                                                              | 8 |

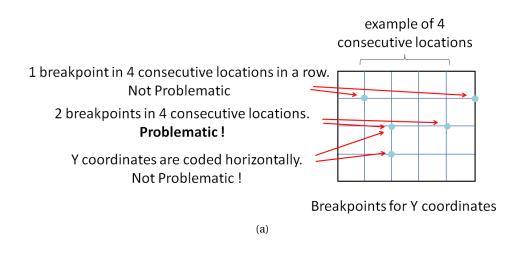

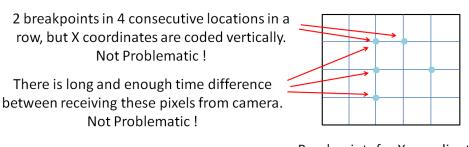

| 5.17        | mappings (a) breakpoints for the mapping of Y coordinates (b) breakpoints for                                                                                                                                                                                                                             |   |

|             | the mapping of X coordinates                                                                                                                                                                                                                                                                              | 8 |

| 5.18        | Visualization of the reason for the frequent breakpoints (a) finding the source locations of three pixels that are targeting one row above of the three consecutive                                                                                                                                       |   |

|             | voids (b) four break-points in consecutive five locations                                                                                                                                                                                                                                                 | 8 |

| 5.19        | Visualization of the reason for the voids which can not be filled by CLUTR                                                                                                                                                                                                                                | 8 |

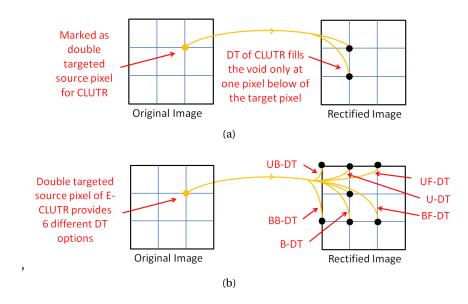

| 5.20        | Filling the voids in the rectified image in the fifth step (a) DT option of CLUTR (b) DT options of E-CLUTR                                                                                                                                         | 89  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.21        | Reducing the frequency of breakpoints using multiple DT options of E-CLUTR (a) finding alternative source locations for void pixels of rectified image (b) reduced                                                                                  |     |

|             | frequency of breakpoints for the same row of the look-up-table of Y coordinates.                                                                                                                                                                    | 89  |

| 5.22        | Vertically adjacent void pixels can be filled by E-CLUTR using multiple DT options.                                                                                                                                                                 | 90  |

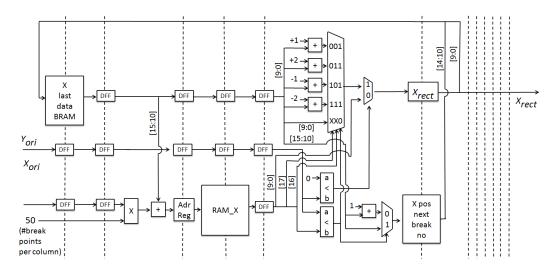

| 5.23        | Brief representation for the concatenation of the locations and behaviors it the seventh step of E-CLUTR for the mapping of Y coordinates                                                                                                           | 91  |

| 5.24        | Concatenation of the locations and behaviors at the seventh step for E-CLUTR for the mapping of Y coordinates (a) Concatenation scheme for DT options (b) Concatenation scheme for the breakpoint conditions for changing the last targeted row     | 91  |

| 5.25        | Concatenation of the locations and behaviors at the seventh step of E-CLUTR for the mapping of X coordinates.                                                                                                                                       | 91  |

| 5.26        | Top-level block diagram of the proposed rectification hardware of E-CLUTR                                                                                                                                                                           | 92  |

| 5.27        | Block diagram of the proposed rectification hardware for decompressing the table of X coordinates                                                                                                                                                   | 93  |

| 5.28        | Block diagram of the proposed rectification hardware for decompressing the table of Y coordinates. Pipeline stages are presented with dashed lines                                                                                                  | 93  |

| 5.29        | Block diagram of the proposed hardware implementation for Caltech rectification algorithm                                                                                                                                                           | 95  |

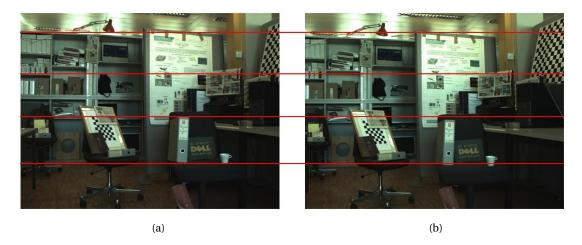

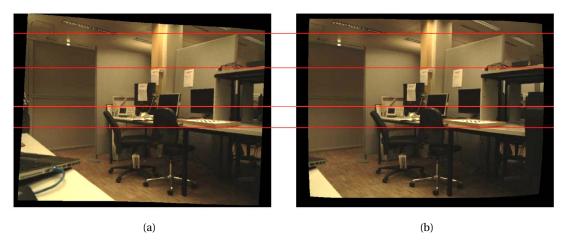

| 5.30        | Visual results of the first test using roughly aligned cameras: Original images have still distortions as observed near the lamp, bag, folder and cup; horizontal epipolar lines are displayed in red near the edge of these objects (a) left image |     |

|             | (b) right image                                                                                                                                                                                                                                     | 97  |

| 5.31        | Visual results of the first test using roughly aligned cameras: The proposed CLUTR algorithm corrects distortions (a) left image (b) right image                                                                                                    | 97  |

| 5.32        | Visual results of the first test using roughly aligned cameras: Breakpoint locations obtained by CLUTR for the left image (a) breakpoints of the targeted Y coordinates; coded row-by-row. (b) breakpoints of the targeted X coordinates;           | 00  |

| <b>5</b> 00 | coded column-by-column.                                                                                                                                                                                                                             | 98  |

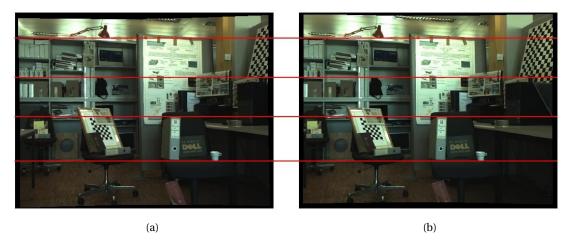

| 5.33        | Visual results of the second test using excessively misaligned cameras: Original images have excessive distortions as observed on the lines (a) left image (b) right image                                                                          | 99  |

| 5.34        | Visual results of the second test using excessively misaligned cameras: E-CLUTR corrects distortions as observed on the lines (a) left image (b) right image                                                                                        | 99  |

| 5.35        | Visual results of the second test using excessively misaligned cameras: Breakpoint locations of the left image (a) breakpoints of the targeted Y coordinates; coded row-by-row. (b) breakpoints of the targeted X coordinates;                      | 55  |

|             |                                                                                                                                                                                                                                                     | 100 |

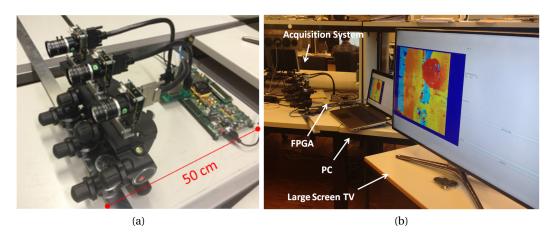

| 6.1  | Demonstration of the system set-up. (a) close-up to the three cameras and the FPGA board (b) full demonstration system also including a PC and large-screen TV                                                                                                                                                                  | .103 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

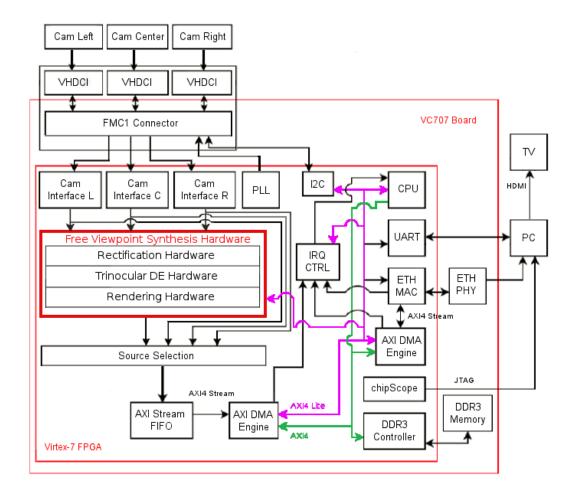

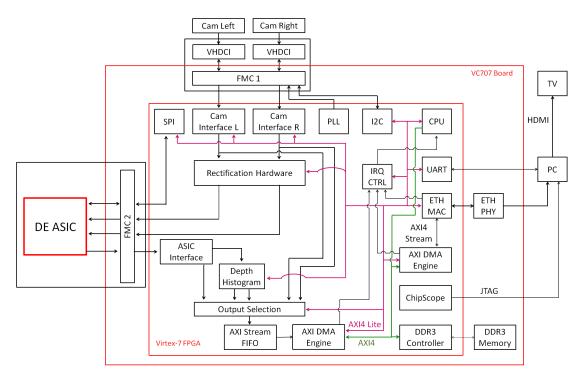

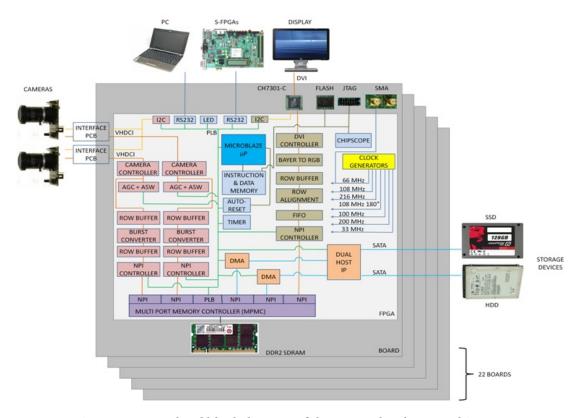

| 6.2  | Block diagram of the full system setup.                                                                                                                                                                                                                                                                                         | 105  |

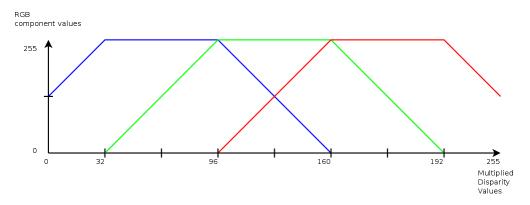

| 6.3  | RGB component values in function of the multiplied disparity values, used for                                                                                                                                                                                                                                                   |      |

|      | the color representation                                                                                                                                                                                                                                                                                                        | 108  |

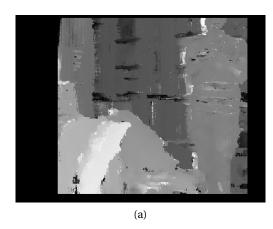

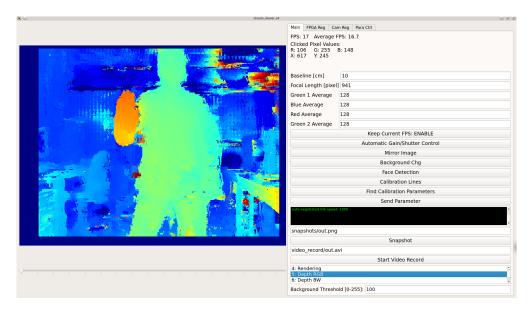

| 6.4  | Snapshot of the DE result of binocular disparity estimation system. The hardware is able to switch between to representations: (a) Gray scale disparity map (brighter color is closer, darker color is further), (b) Color mapped disparity map (hotter color is closer, colder color is further)                               | 109  |

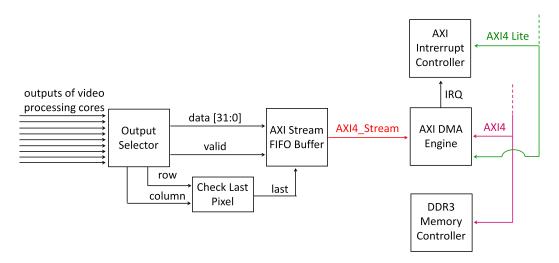

| 6.5  | Block-diagram of the interface between the disparity estimation hardware and                                                                                                                                                                                                                                                    | 114  |

| C C  | the DDR3 memory.                                                                                                                                                                                                                                                                                                                | 114  |

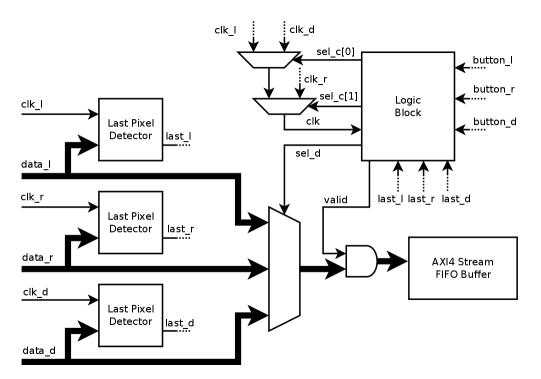

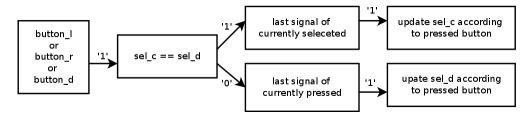

| 6.6  | Block-diagram of the Output Selection circuit for three possible outputs                                                                                                                                                                                                                                                        | 114  |

| 6.7  | Flowchart representation of the logic block functionality.                                                                                                                                                                                                                                                                      | 115  |

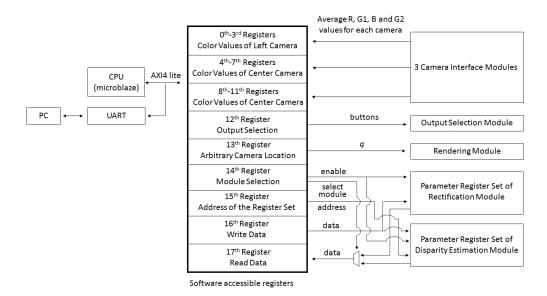

| 6.8  | Top-level schematic of software accessible registers                                                                                                                                                                                                                                                                            | 117  |

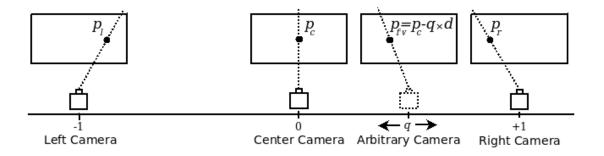

| 7.1  | Definition of the three-camera free viewpoint synthesis setup. $\dots \dots$                                                                                                                                                                                                                                                    | 120  |

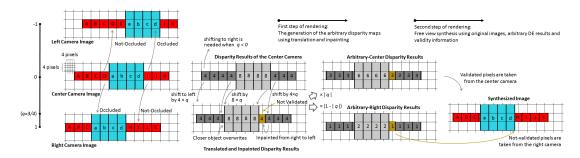

| 7.2  | The illustration of free viewpoint synthesis algorithm that utilizes trinocular disparity estimation. (Each square grid represents 4×4 pixels. Only one out of four column/row grids are represented to improve the clarity of the representation)                                                                              | 121  |

| 7.3  | Block diagram of the free viewpoint synthesis system                                                                                                                                                                                                                                                                            | 123  |

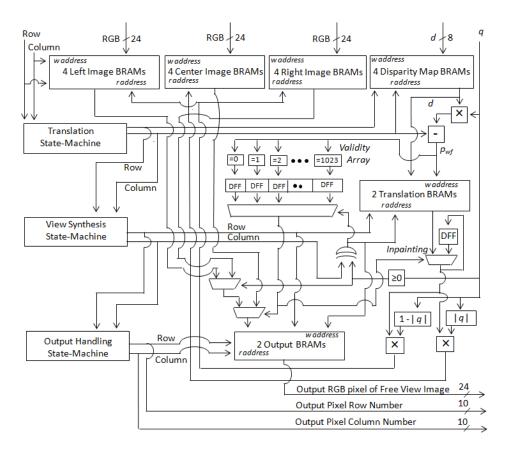

| 7.4  | Rendering hardware (pipeline stages are not shown)                                                                                                                                                                                                                                                                              | 124  |

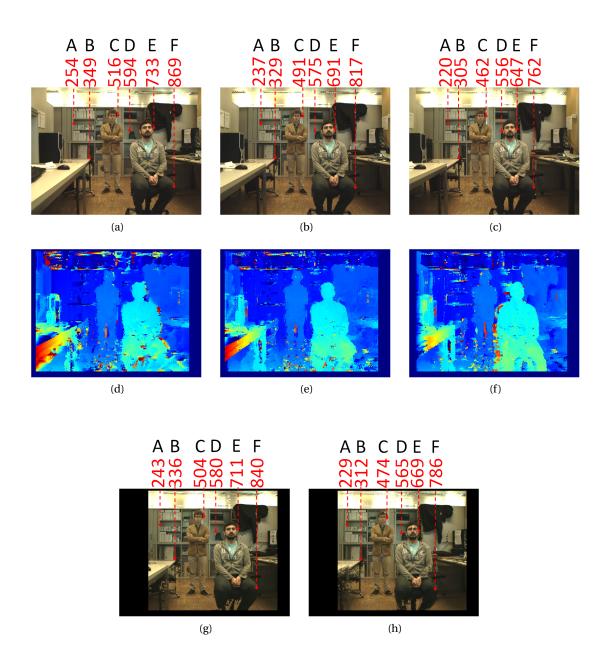

| 7.5  | Real-time snapshots captured by the proposed system. (a) Left image (b) Center image (c) Right image (d)IR-AWDE for center-left (e) T-AWDE (f)IR-AWDE for center-right (g) synthesized free viewpoint image for an arbitrary camera located at $q$ =(-0.5) (h) synthesized free viewpoint image for an arbitrary camera located |      |

|      | at $q$ =(0.5) (images best viewed in high resolution from the pdf files)                                                                                                                                                                                                                                                        | 126  |

| 7.6  | Screen shot of the stream viewer software running on Linux                                                                                                                                                                                                                                                                      | 128  |

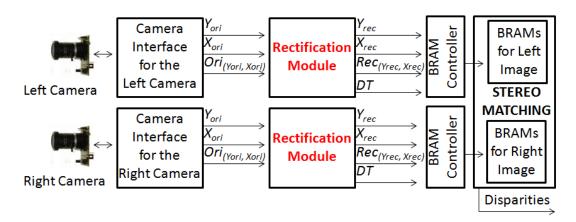

| 8.1  | Depth estimation system that is utilizing two cameras                                                                                                                                                                                                                                                                           | 134  |

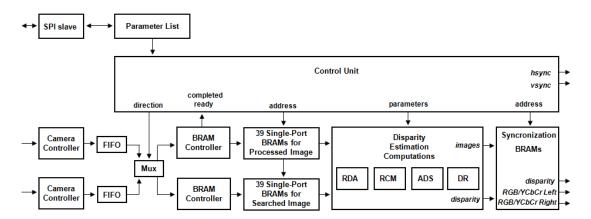

| 8.2  | Modules present in the Disparity Estimation ASIC                                                                                                                                                                                                                                                                                | 136  |

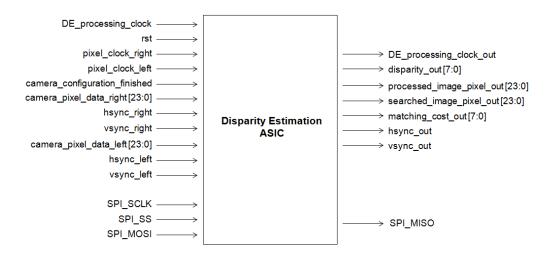

| 8.3  | top level inputs and outputs of the disparity estimation final ASIC                                                                                                                                                                                                                                                             | 136  |

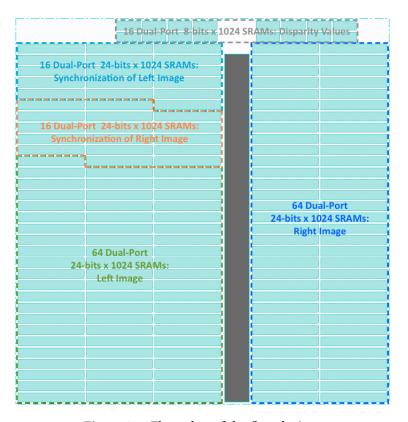

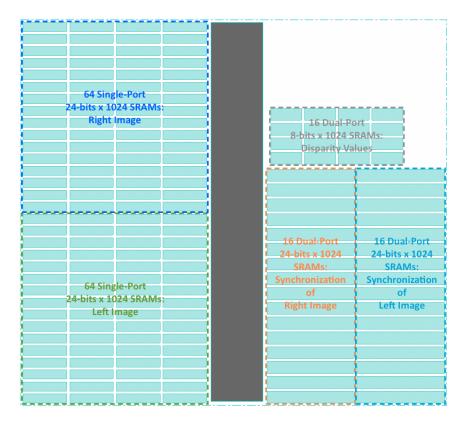

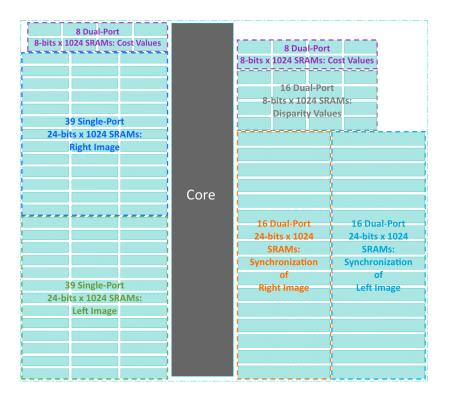

| 8.4  | Floorplan of the first design                                                                                                                                                                                                                                                                                                   | 147  |

| 8.5  | Floorplan of the second design                                                                                                                                                                                                                                                                                                  | 148  |

| 8.6  | Floorplan of the third design                                                                                                                                                                                                                                                                                                   | 149  |

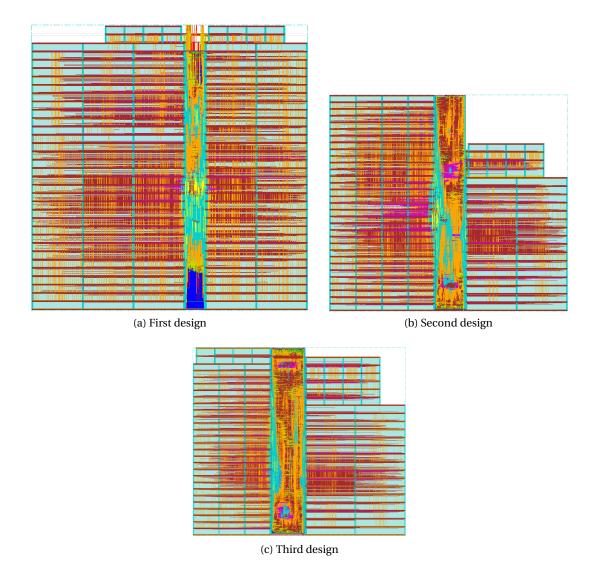

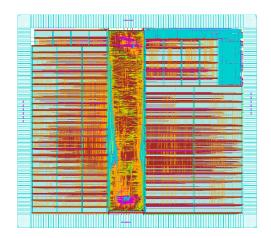

| 8.7  | The three disparity estimation ASIC designs after P&R. For visual comparison, $$                                                                                                                                                                                                                                                |      |

|      | the proportions have been kept. (a)First design (b)Second design (c) Third design                                                                                                                                                                                                                                               | ι150 |

| 8.8  | The final ASIC design after P&R and placing the IO pads                                                                                                                                                                                                                                                                         | 151  |

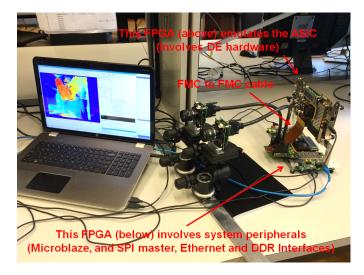

| 8.9  | Top-level diagram of the test system of ASIC. One VC707 board is connected to                                                                                                                                                                                                                                                   |      |

|      | the test-board containing the ASIC package                                                                                                                                                                                                                                                                                      | 152  |

| 8.10 | The emulation and verification set-up of the ASIC                                                                                                                                                                                                                                                                               | 152  |

### **List of Figures**

| 9.1  | 256 × 1024 resolution omnidirectional 2D reconstructions using a) <i>Linear</i>      |      |

|------|--------------------------------------------------------------------------------------|------|

|      | pixelization b) Equal area distribution                                              | 155  |

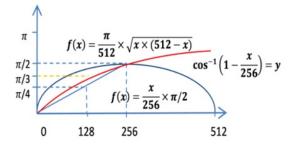

| 9.2  | Captured images from two different cameras a) top camera b) side camera              | 155  |

| 9.3  | Hemispheric structure for resolution calculation in terms of ppaa                    | 156  |

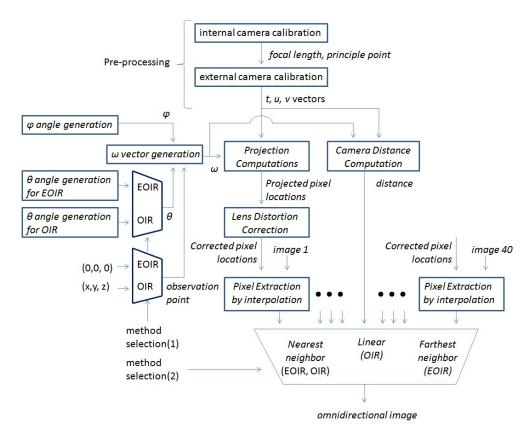

| 9.4  | Relationship between N and - angle for different methods of pixelization             | 156  |

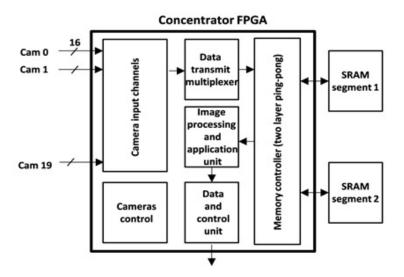

| 9.5  | Block diagram of omnidirectional image reconstruction algorithms $\ \ldots \ \ldots$ | 158  |

| 9.6  | Block diagram of the Concentrator FPGA                                               | 159  |

| 9.7  | Block diagram of the omnidirectional vision reconstruction unit inside the image     |      |

|      | processing and application block                                                     | 160  |

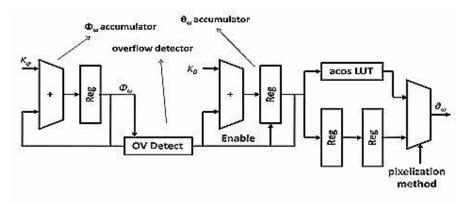

| 9.8  | $	heta$ and $\phi$ angle generation module architecture for the OIR and EOIR         |      |

|      | implementations                                                                      | 160  |

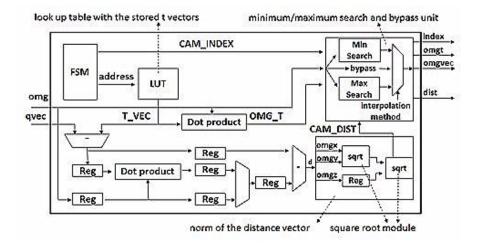

| 9.9  | Architecture of the camera select and distance generation sub-block for the EOIR     |      |

|      | algorithm                                                                            | 160  |

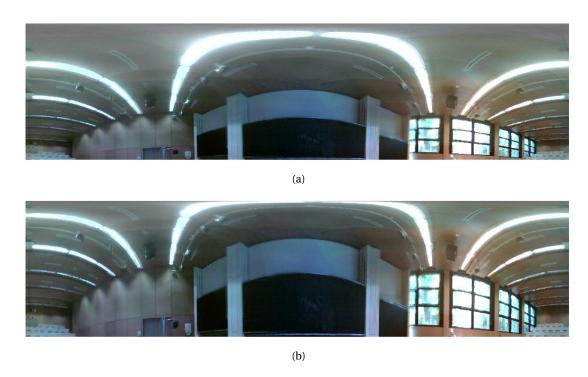

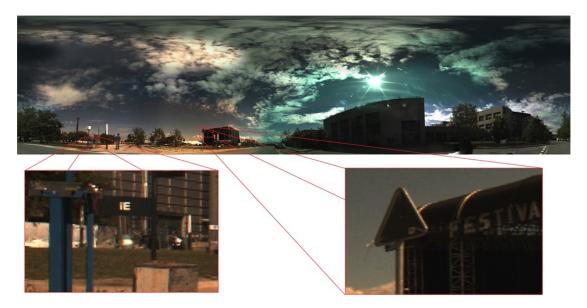

|      | Reconstructed 360° views                                                             | 162  |

|      | Top-level block diagram of the system hardware architecture                          | 169  |

| 9.12 | The complete omnidirectional imaging and recording system (Giga-Eye), overall        |      |

|      | system dimensions are 56x48x78 cm                                                    | 171  |

| 9.13 | Omnidirectional image obtained with the Giga-Eye system at 21.6 MP resolution        |      |

|      | showing the central campus square of EPFL, and two selected details                  |      |

|      | (sub-regions) in this image. This omnidirectional image corresponds to one           |      |

|      |                                                                                      | 172  |

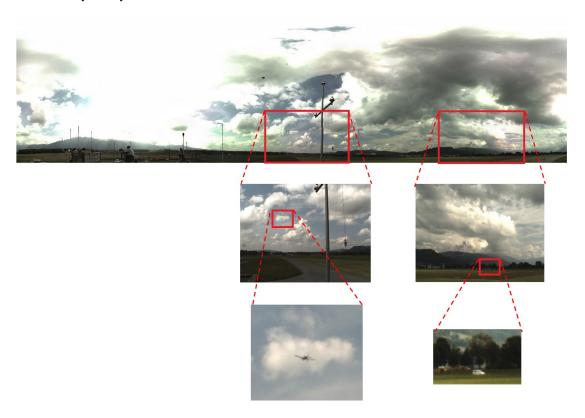

| 9.14 | Omnidirectional image obtained with the Giga-Eye system at 82.3 MP resolution.       |      |

|      | This omnidirectional image corresponds to one single frame of the 9.5 fps video      |      |

|      | obtained by the system. Flying plane and the moving car are shown in sub-window      | s172 |

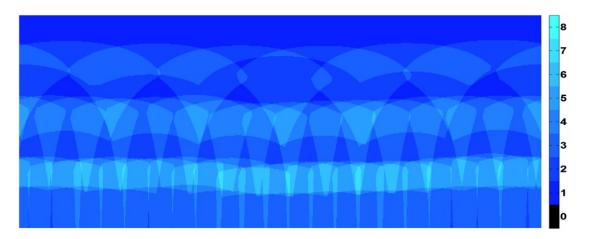

| 9.15 | Measured coverage map of the omnidirectional imaging system showing a high           |      |

|      | pixel redundancy especially close to the equator. The color labels indicate the      |      |

|      | number of the overlapping individual camera AOVs                                     | 173  |

## **List of Tables**

| 3.1 | Parameters of the AWDE                                                                     | <b>5</b> 4 |

|-----|--------------------------------------------------------------------------------------------|------------|

| 3.2 | Disparity Estimation Performance Comparisons. Error rates (%) are provided                 |            |

|     | compared to DE ground truths of the benchmark pictures                                     | 55         |

| 3.3 | Hardware Performance Comparison                                                            | 57         |

| 5.1 | Bit-size Parameters of the Caltech rectification hardware                                  | 95         |

| 5.2 | Numerical results of the first test using roughly aligned cameras: PSNR ( <i>dB</i> ) with |            |

|     | the rectified images produced by Caltech rectification algorithm                           | 98         |

| 5.3 | Numerical results of the first test using roughly aligned cameras: PSNR ( <i>dB</i> )      |            |

|     | Comparison of the Disparity Estimation Results Using Different Disparity                   |            |

|     | Estimation Algorithms                                                                      | 98         |

| 5.4 | Numerical results of the second test using excessively misaligned cameras: PSNR            |            |

|     |                                                                                            | 100        |

| 5.5 | Hardware Resource Comparison of the Rectification Hardware Implementations                 | 101        |

| 8.1 | ARM SRAMs Area Configuration Comparison (in $\mu m^2)$                                     | 137        |

| 8.2 | Approximate power consumption for the different SRAM types of the ASIC design              |            |

|     | (in mW)                                                                                    | 137        |

| 8.3 | Register list and default values. *1 = always 1; 0 = always 0; d = programmable; –         |            |

|     | = read only                                                                                | 138        |

| 8.4 | Core Registers descriptions                                                                | 139        |

| 8.5 | Area report of the three synthesized hardware                                              | 146        |

| 8.6 | Total power of the DE ASIC (in mW)                                                         | 149        |

| 8.7 | Dimensions of ASIC designs                                                                 | 150        |

| 9.1 | Surface Area Coverage (%) with respect to $\theta$ angles (radians) for Possible           |            |

|     |                                                                                            | 154        |

| 9.2 | Resolution values [ $ppaa$ ] for different $\theta$ angles                                 | 156        |

| 9.3 |                                                                                            | 162        |

| 9.4 | •                                                                                          | 164        |

| 9.5 |                                                                                            | 166        |

| 9.6 |                                                                                            | 167        |

|     |                                                                                            |            |

### List of Tables

| 9.7 | Comparison of the Giga-Eye with existing high-resolution omnidirectional |     |

|-----|--------------------------------------------------------------------------|-----|

|     | camera systems                                                           | 174 |

### 1 Introduction

The stereoscopic depth perception is first described by the British scientist and inventor Charles Wheatstone in 1838. Wheatstone made a device called stereoscope to provide stereoscopic vision to a human observer. He used a pair of mirrors mounted with an angle of 45° with respect to the two drawings at the sides to reflect the drawings to the observer. He showed that brain makes the fusion of these drawings and perceives a three dimensional image. In 1850s, the American physician Oliver Wendell Holmes used glasses with two prismatic lenses to provide stereocopic vision. The invention of this portable device led to the development of rotating cardboard disks with image pairs which became a popular entertainment and virtual tourism tool until mid-20<sup>th</sup> century.

In the very early times of the stereoscopy, pictures were taken by a single camera, moving it along its horizontal axis. Later, stereo cameras were manufactured following an increasing demand of stereo vision. In the late  $19^{th}$  century, a stereo camera called Verascope was invented. In 1967, a color stereo camera called Stereo Realist was invented. This invention was followed by the development of 3D displayers for color images and videos.

Color analyph-based 3D glasses were popular in the late  $20^{th}$  century. These glasses include two chromatically opposite colors (red and cyan) in each glass, which filter the left and right images separately for each eye. The brain operates the fusion and forms a three dimensional color scene.

In the late  $20^{th}$  century, the artificial presence in a computer-generated or real-world environment, so-called virtual reality systems, became an important demand of medical, gaming and military applications and cinema industry. This demand was supported by the advances in digital photography and video which led to the development of advanced 3D vision and display systems.

Active shutter based glasses are mainly used today for 3D cinematography. Active shutter glasses works by rapidly showing two images to the left or right eye by blocking one of them. Meanwhile the image on the monitor shifts to the view of right or left eye synchronously to form stereoscopic view.

Head-mounted displays (HMD) are one of the popular 3D display devices available today. HMDs include optics and a wearable digital monitor to display computer generated video or movie transferred from a PC. HMDs may utilize active-shutter based multiplexing or side by side multiplexing to provide depth perception. HMDs are mainly used for military and video gaming applications to view the scene with 360° × 90° angle of view (AOV) in 3D.

3D TVs can utilize different type of methods to provide depth perception. The previously developed 3D TVs needed color analyph based 3D glasses for proper operation. Currently, most of the 3D TVs operate with active shutter based glasses. However, the requirement to wear 3D glasses is usually perceived uncomfortable which impedes any wide usage of stereoscopic 3D displays. Recently, autostereoscopic displays have emerged to provide glasses-free depth perception [1]. The autostereoscopic technology or so-called free viewpoint television (FVT) utilizes physical parallax barriers to display multiple views that provide a stereo pair regardless of the positions of the viewer. Although increasing the number of views decrease the limited distance range of these displays, broadcasting all the views is challenging in terms of bandwidth limitations. [2] demonstrates that standard 2D displays can act as 3D displays by deceiving human perception without using intricate autostereoscopic technique if the free view is generated efficiently considering the position of the head of the viewer. [2] presents the efficiency of this method using computer generated images and pre-computed depth map.

The emerging technology of virtual reality applications should be supported not only by the displays, but also from high-quality video capture, coding and processing technologies should be developed. Large AOV image capture systems and depth measurement are important requirements of advanced virtual reality and video processing applications, which should progress in parallel to the advances on display technologies.

### 1.1 Large Angle of View Image Capture Systems

In order to support the wide AOV requirement of virtual reality applications, recent research has mainly focused on developing complex lenses, mirrors and multiple-camera systems. Fish-eye lenses are major lens types that provide an AOV between 180° to 200° using a single

camera. However, distortion in the edges of the images limits the use of single complex lenses.

In [3], a camera system with a convex mirror is developed in order to create 360° omnidirectional images. This method does not require intricate hardware or software for constructing omnidirectional images, and is thus widely cited in literature related to omnidirectional image reconstruction. In [4], the real-time panoromic image reconstruction hardware utilizing a system consisting of a convex mirror placed over a single camera is presented. The hardware presented in [4] provides 360° panoramic images of 3200×768 resolution at 40fps. The presented hardware fits into a Spartan 3 FPGA. Nevertheless, the resolution of omnidirectional images is limited to the resolution of a single camera. Moreover, it is incapable of showing the overall top view since the AOV of the camera is restricted to the area located below the mirror. Also, the convex mirror provides distortion at the edges of the image. Furthermore, the platform cannot be used for depth estimation and 3D reconstruction due to its single observation point feature.

An alternate method enabling wide AOV image acquisition is based on a single-camera multiple-lens optical sensors system [5–7]. Devices taking advantage of this technique and presenting very large AOVs are mainly inspired by the insect faceted eyes. Faceted insect eyes consist of hundreds to thousands channels, each called ommatidia [8]. These channels capture light within a defined angle and transmit it to light sensitive receptor cells. In [5], artificial insect eyes, cluster eyes and artificial apposition compound eyes (APCO) are fabricated using wafer-scale techniques. In [6], the AOV of eye clusters and APCOs is improved to 124° by using two additional micro-lenses in each channel, thereby causing significant distortion. In [7], a system named Krill-eye is presented. The Krill-eye utilizes 180 gradient-index lenses and hence, provides distortion-free 180° AOV. However, designing a Krill-eye composed of 180 lenses is not trivial, while the AOV remains significantly limited under 360°.

Multiple-camera systems are proposed as an alternative method, which enables obtaining wide AOVs. The synchronization of the cameras and the very large data bandwidth impose challenges for the implementation of these systems. Some camera array systems were developed for recording; the recordings were processed at a later time offline on a PC[9]. Many multiple-camera systems are only used for object tracking and detection, where the goal does not involve the creation of single omnidirectional images [10–12]. Each image obtained from multiple cameras should be appropriately combined in order to prevent unrealistic discontinuity. An image mosaic algorithm and its real-time hardware implementation are presented in [13]. This multi-camera system supports three cameras, and is capable of reaching an AOV smaller than 180°. The system operates in real-time benefiting from the utilization of digital signal processors (DSPs). Furthermore, the resulting omnidirectional image does not exhibit significant distortion or discontinuity.

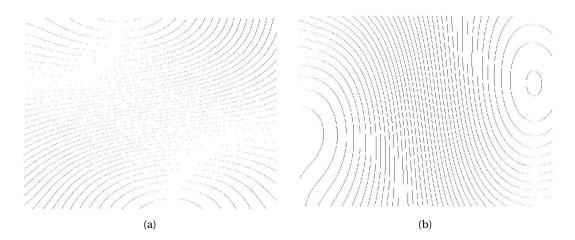

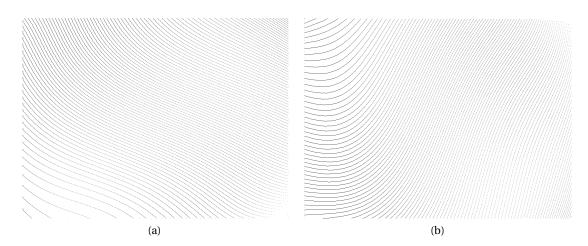

In [14], a planar multiple-camera system composed of 100 cameras is presented as a solution to reach high resolution, high frame rates and high AOV. The presented platform consisting of 100 FPGAs is aimed to record large amounts of data to process offline, and thus provides limited local processing at the camera level. However, it reaches less than 180° AOV due to its planar structure.