## Politecnico di Milano

Scuola di Ingegneria dell'Informazione Corso di Laurea Magistrale in Ingegneria Elettronica

# Low-Power and Compact Successive Approximation ADC for Bio-Electronic Chips

Relatore: Prof. Marco SAMPIETRO Correlatore: Prof. Andreas HIERLEMANN

> Tesi di Laurea di: Andrea BONETTI matricola 750696

Anno Accademico: 2010-2011

## Acknowledgments

First of all, I would like to thank my supervisor Prof. Marco Sampietro of Politecnico di Milano for his continuous support and for making my stay at ETH Zürich. I am particularly grateful to Prof. Andreas Hierlemann who gave me the unique opportunity to carry out my Master's Thesis at his laboratory. Dr. Yihui Chen deserves special thanks for his intelligent guidance through the world of the analog-to-digital converters. I also would like to express my gratitude to Pascal Meinerzhagen for his helpful suggestions and to Vijay Viswam for his insightful comments during the completion of the project. I was truly fortunate to have the possibility to work at the Bio Engineering Laboratory (BEL) and I owe sincere thanks to all the people I worked with.

# Contents

| 1        | Intr | roduction                                                 | 1  |

|----------|------|-----------------------------------------------------------|----|

|          | 1.1  | Motivation                                                | 1  |

|          | 1.2  | MEA Chips Developed at BEL                                | 1  |

|          |      | 1.2.1 Interfacing Electrogenetic Cells in Vitro with CMOS |    |

|          |      | Microelectrode Arrays                                     | 1  |

|          |      | 1.2.2 The High-Density MEA Chip                           | 3  |

|          | 1.3  | Thesis Organization                                       | 5  |

| <b>2</b> | Spe  | cifications and ADC Topologies                            | 6  |

|          | 2.1  | Required ADC for the New Version of the Chip              | 6  |

|          | 2.2  | Elaboration of Specifications                             | 6  |

|          | 2.3  | Low Power ADC Topologies Overview                         | 7  |

|          | 2.4  | Fully Differential Switched-Capacitor SAR ADC             | 10 |

| 3        | Des  | ign implementation                                        | 13 |

|          | 3.1  | •                                                         | 13 |

|          | 3.2  |                                                           | 13 |

|          |      |                                                           | 17 |

|          | 3.3  |                                                           | 27 |

|          |      |                                                           | 27 |

|          |      |                                                           | 30 |

|          |      |                                                           | 34 |

|          | 3.4  |                                                           | 35 |

|          |      |                                                           | 35 |

|          |      |                                                           | 36 |

|          |      |                                                           | 39 |

|          | 3.5  | -                                                         | 50 |

|          |      |                                                           | 50 |

|          |      |                                                           | 53 |

|          |      |                                                           | 54 |

|          | 3.6  |                                                           | 55 |

| <b>4</b> | $\mathbf{Sim}$ | ulations and Conclusions                                          | <b>58</b> |

|----------|----------------|-------------------------------------------------------------------|-----------|

|          | 4.1            | Simulation Results                                                | 58        |

|          | 4.2            | Conclusions                                                       | 62        |

| <b>5</b> | App            | pendix                                                            | 64        |

|          | 5.1            | Effects of the parasitic capacitances in the DAC                  | 64        |

|          | 5.2            | Standard deviation estimation of the DAC output voltage $\ . \ .$ | 65        |

| Bi       | bliog          | raphy                                                             | 68        |

# List of Figures

| $\begin{array}{c} 1.1 \\ 1.2 \end{array}$                                    | Packaged MEA chip on a custom-designed printed circuit board.<br>(a) Schematic of a cell attached to a sensor surface. (b) Mi-<br>crograph of an acute cerebellar brain slice (parasagittal cut)<br>placed on a CMOS high-density electrode chip for measure-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2                                                                                                                                  |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|                                                                              | ments.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                                                                                                  |

| 1.3                                                                          | Micrograph of the MEA chip $(7.5 \times 6.1 \text{ mm}^2)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\frac{2}{3}$                                                                                                                      |

| $1.3 \\ 1.4$                                                                 | Block diagram of the MEA chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3<br>4                                                                                                                             |

| 1.4                                                                          | block diagram of the MEA clip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4                                                                                                                                  |

| 2.1                                                                          | Single-slope ADC [4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8                                                                                                                                  |

| 2.2                                                                          | Successive-approximation ADC structure [4] and a 4-bit analog-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                    |

|                                                                              | to-digital conversion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9                                                                                                                                  |

| 2.3                                                                          | First-order sigma-delta ADC [4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                                                                                                                                  |

| 2.4                                                                          | 3-bit single-ended switched-capacitor SAR ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10                                                                                                                                 |

| 2.5                                                                          | 4-bit fully differential switched-capacitor SAR ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11                                                                                                                                 |

| 2.6                                                                          | Voltages at $V_{ipA}$ and $V_{inA}$ during the sampling and conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                    |

|                                                                              | phases for the 4-bit fully differential switched-capacitor SAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                    |

|                                                                              | ADC [8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12                                                                                                                                 |

|                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                    |

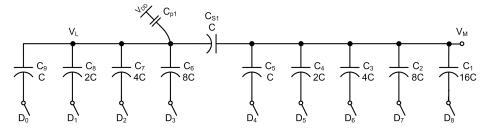

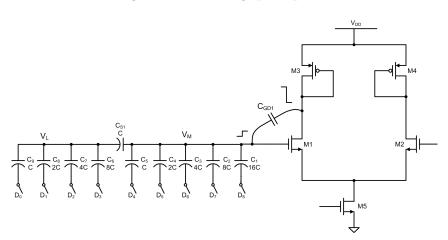

| 3.1                                                                          | Binary weighted switched-capacitor array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15                                                                                                                                 |

| $3.1 \\ 3.2$                                                                 | Binary weighted switched-capacitor array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $15 \\ 16$                                                                                                                         |

| 3.2                                                                          | Binary weighted switched-capacitor array equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16                                                                                                                                 |

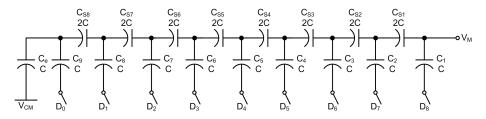

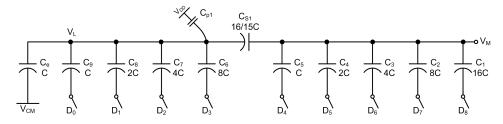

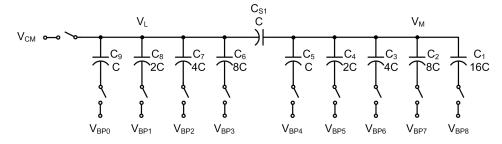

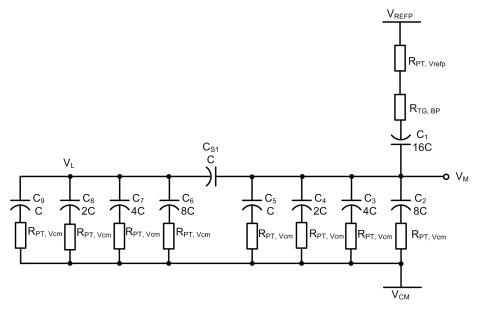

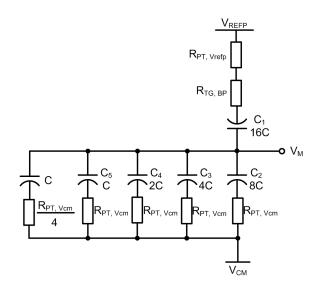

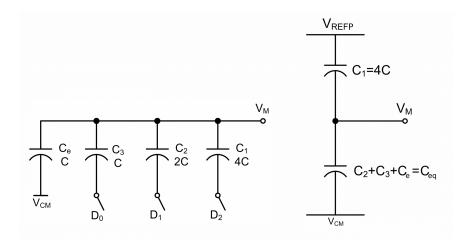

| $\begin{array}{c} 3.2\\ 3.3 \end{array}$                                     | Binary weighted switched-capacitor array equivalent circuit<br>2bw1Cs capacitive array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\begin{array}{c} 16 \\ 16 \end{array}$                                                                                            |

| $3.2 \\ 3.3 \\ 3.4$                                                          | Binary weighted switched-capacitor array equivalent circuit.2bw1Cs capacitive array.5bw4Cs capacitive array.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16<br>16<br>16                                                                                                                     |

| 3.2<br>3.3<br>3.4<br>3.5                                                     | Binary weighted switched-capacitor array equivalent circuit.2bw1Cs capacitive array.5bw4Cs capacitive array.C2C capacitive array.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\begin{array}{c} 16 \\ 16 \end{array}$                                                                                            |

| $3.2 \\ 3.3 \\ 3.4$                                                          | Binary weighted switched-capacitor array equivalent circuit.2bw1Cs capacitive array.5bw4Cs capacitive array.C2C capacitive array.2bw1Cs switched-capacitor array with the bottom-plate par-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16<br>16<br>16<br>16                                                                                                               |

| $3.2 \\ 3.3 \\ 3.4 \\ 3.5 \\ 3.6$                                            | Binary weighted switched-capacitor array equivalent circuit.2bw1Cs capacitive array.5bw4Cs capacitive array.C2C capacitive array.2bw1Cs switched-capacitor array with the bottom-plate parasitic capacitance added.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16<br>16<br>16<br>16                                                                                                               |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                                       | Binary weighted switched-capacitor array equivalent circuit.2bw1Cs capacitive array.5bw4Cs capacitive array.C2C capacitive array.2bw1Cs switched-capacitor array with the bottom-plate parasitic capacitance added.2bw1Cs switched-capacitor array equivalent circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16<br>16<br>16<br>16<br>18<br>19                                                                                                   |

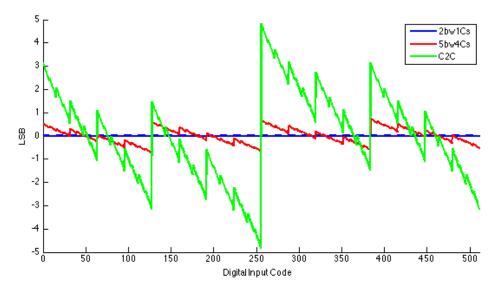

| $3.2 \\ 3.3 \\ 3.4 \\ 3.5 \\ 3.6$                                            | Binary weighted switched-capacitor array equivalent circuit.2bw1Cs capacitive array.5bw4Cs capacitive array.C2C capacitive array.2bw1Cs switched-capacitor array with the bottom-plate parasitic capacitance added.2bw1Cs switched-capacitor array equivalent circuit.2bw1Cs switched-capacitor array equivalent circuit.1NL graph estimation of each split capacitive array.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16<br>16<br>16<br>18<br>19<br>20                                                                                                   |

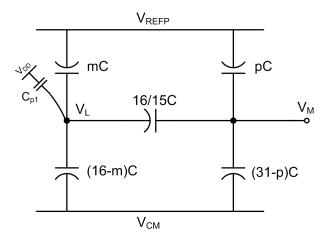

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                                | Binary weighted switched-capacitor array equivalent circuit.2bw1Cs capacitive array.5bw4Cs capacitive array.C2C capacitive array.2bw1Cs switched-capacitor array with the bottom-plate par-asitic capacitance added.2bw1Cs switched-capacitor array equivalent circuit.2bw1Cs switched-capacitor array equivalent circuit.Modified split capacitive array.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16<br>16<br>16<br>18<br>19<br>20<br>23                                                                                             |

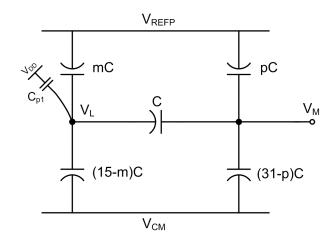

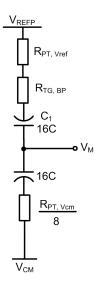

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10                 | Binary weighted switched-capacitor array equivalent circuit.2bw1Cs capacitive array.5bw4Cs capacitive array.C2C capacitive array.2bw1Cs switched-capacitor array with the bottom-plate par-asitic capacitance added.2bw1Cs switched-capacitor array equivalent circuit.2bw1Cs switched-capacitor array equivalent circuit.Modified split capacitive array.Modified split capacitive array equivalent circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16<br>16<br>16<br>18<br>19<br>20<br>23<br>23                                                                                       |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11         | Binary weighted switched-capacitor array equivalent circuit.2bw1Cs capacitive array.5bw4Cs capacitive array.C2C capacitive array.2bw1Cs switched-capacitor array with the bottom-plate par-asitic capacitance added.2bw1Cs switched-capacitor array equivalent circuit.2bw1Cs switched-capacitor array equivalent circuit.Modified split capacitive array.Split | 16<br>16<br>16<br>16<br>18<br>19<br>20<br>23                                                                                       |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11         | Binary weighted switched-capacitor array equivalent circuit.2bw1Cs capacitive array.5bw4Cs capacitive array.C2C capacitive array.2bw1Cs switched-capacitor array with the bottom-plate par-asitic capacitance added.2bw1Cs switched-capacitor array equivalent circuit.2bw1Cs switched-capacitor array equivalent circuit.Modified split capacitive array.Modified split capacitive array equivalent circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16<br>16<br>16<br>18<br>19<br>20<br>23<br>23                                                                                       |

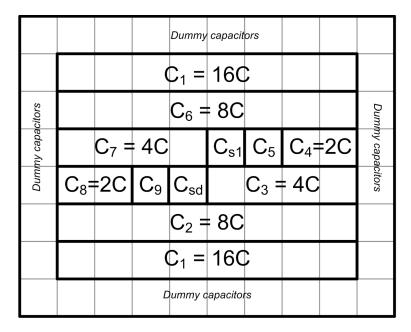

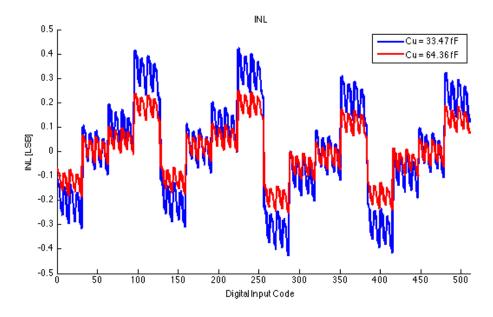

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12 | Binary weighted switched-capacitor array equivalent circuit.2bw1Cs capacitive array.5bw4Cs capacitive array.C2C capacitive array.2bw1Cs switched-capacitor array with the bottom-plate par-asitic capacitance added.2bw1Cs switched-capacitor array equivalent circuit.2bw1Cs switched-capacitor array equivalent circuit.NL graph estimation of each split capacitive array.Modified split capacitive array.Modified split capacitive array.Floorplan of the capacitive array.INL graphs of the 9-bit DAC comparing two different values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ol> <li>16</li> <li>16</li> <li>16</li> <li>16</li> <li>18</li> <li>19</li> <li>20</li> <li>23</li> <li>23</li> <li>25</li> </ol> |

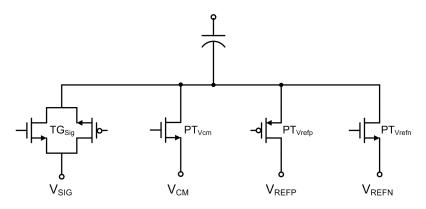

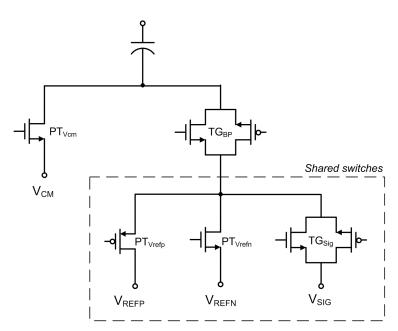

| 3.15 | Shared-block structure for the switches of the capacitive array.     | 29 |

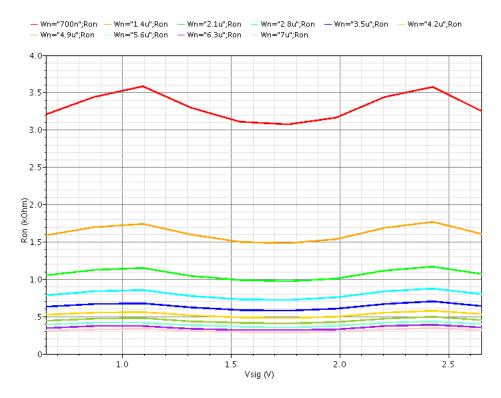

|------|----------------------------------------------------------------------|----|

| 3.16 | Dependance of the on-resistance value of the transmission-           |    |

|      | gate on the input voltage value. While maintaing the rela-           |    |

|      | tion (3.26), the value of $W_N$ has been swept from 0.7 $\mu$ m to   |    |

|      | $7 \mu\mathrm{m}$ .                                                  | 31 |

| 3.17 | Equivalent RC model of the 9-bit DAC for $D_{IN} = 256$              | 32 |

|      | Simplified equivalent RC model of the 9-bit DAC for $D_{IN} = 256$ . | 32 |

|      | First-order equivalent RC model of the 9-bit DAC for $D_{IN} =$      |    |

| 0.20 | 256                                                                  | 33 |

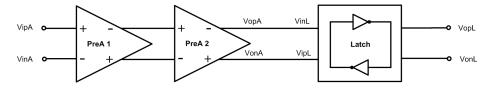

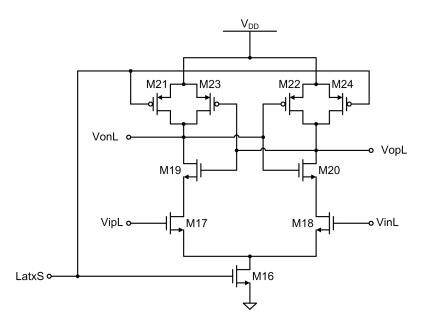

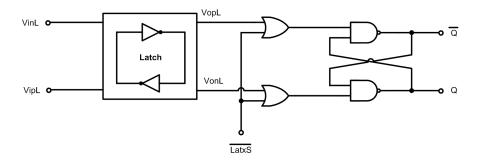

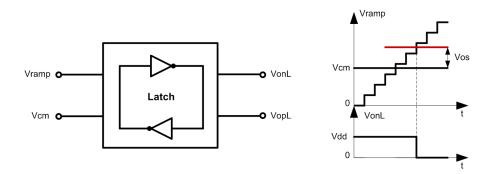

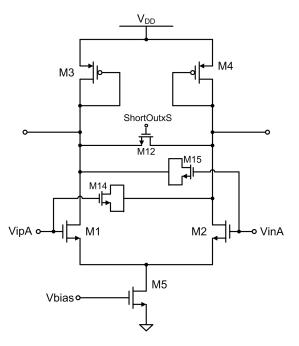

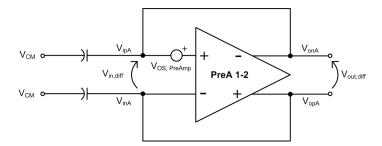

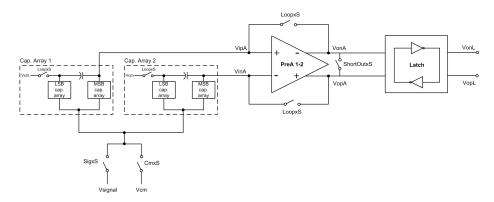

| 3.20 | Structure of the comparator stage.                                   | 35 |

|      | Dynamic latch.                                                       | 36 |

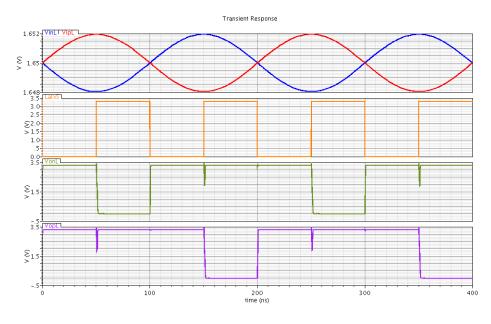

|      | Output response of the latch for a differential sinusoid input       |    |

|      | signal.                                                              | 37 |

| 3.23 | Load of the dynamic latch.                                           | 37 |

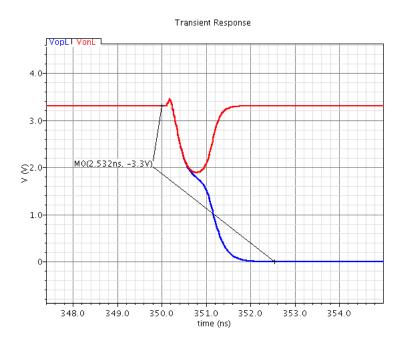

|      | Output response of the latch during the regeneration phase.          | 38 |

|      | Test bench for the input-referred offset voltage estimation of       |    |

|      | the latch.                                                           | 39 |

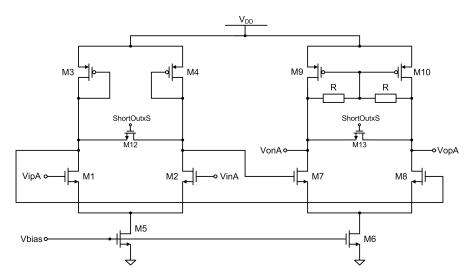

| 3.26 | Two-stage preamplifier.                                              | 41 |

|      | Kickback noise in the first stage of the preamplifier                | 41 |

|      | First preamplifier stage with dummy transistors using the            |    |

|      | capacitive neutralization technique.                                 | 42 |

| 3.29 | Closed-loop operation of the preamplifier performing the in-         |    |

| 0.20 | put offset storage.                                                  | 44 |

| 3.30 | Simplified equivalent circuit of the analog part of the ADC.         | 45 |

|      | Sampling timing diagram example.                                     | 45 |

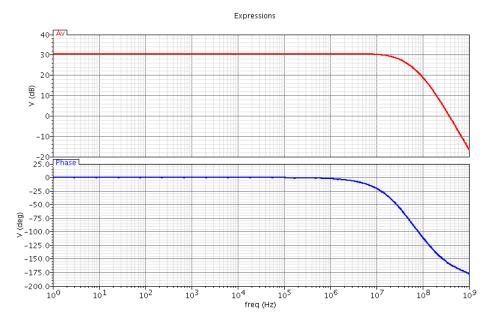

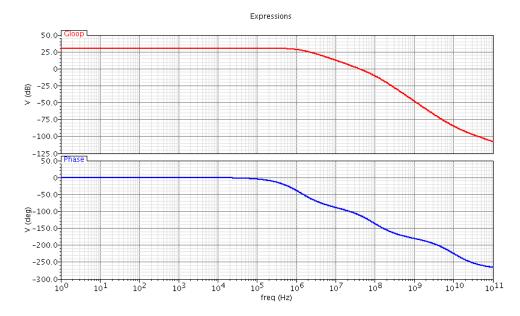

|      | Magnitude and phase diagrams of the open-loop preamplifier           |    |

|      | transfer function.                                                   | 47 |

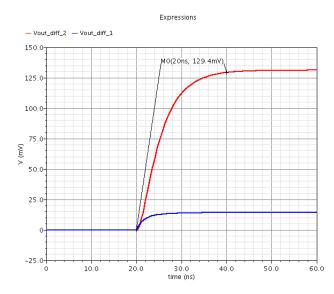

| 3.33 | Step responses of the preamplifier stages for a $LSB_{d-e}$ differ-  |    |

|      | ential input. The blue trace represents the differential output      |    |

|      | voltage of the first stage, while the red trace shows the differ-    |    |

|      | ential output voltage of the second stage.                           | 48 |

| 3.34 | Magnitude and phase diagrams of the loop gain transfer func-         |    |

|      | tion                                                                 | 50 |

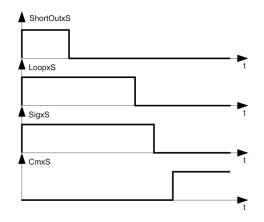

| 3.35 |                                                                      | 52 |

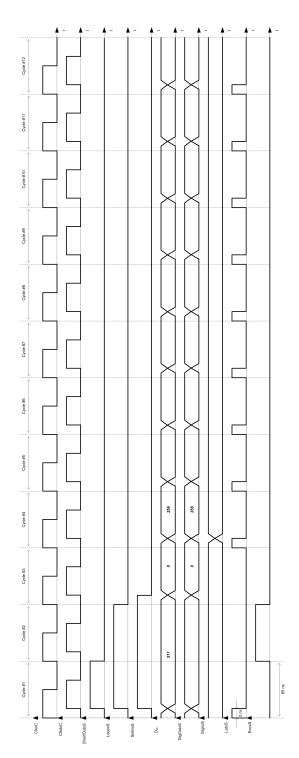

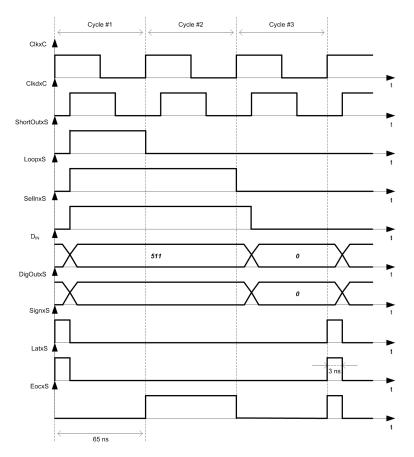

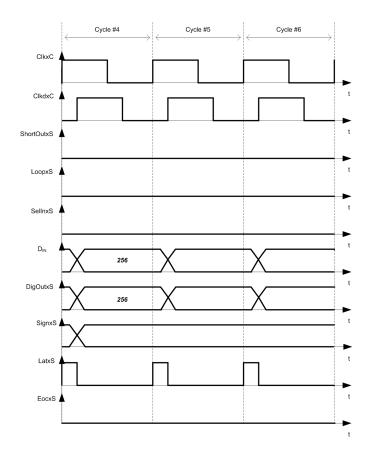

| 3.36 | Timing diagrams for the first three cycles of a conversion           | 53 |

|      | Timing diagrams of the cycles used to determine the last 9           |    |

|      | bits of the digital output.                                          | 54 |

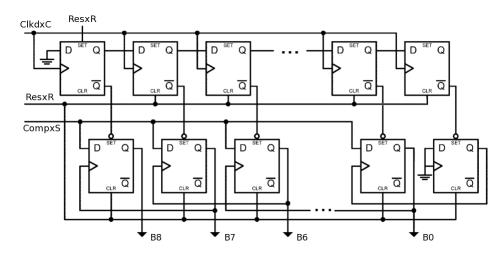

| 3.38 | Successive approximation register for binary search.                 | 55 |

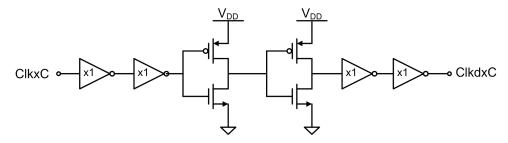

|      | Chain of inverters to generate the delayed clock signal              | 55 |

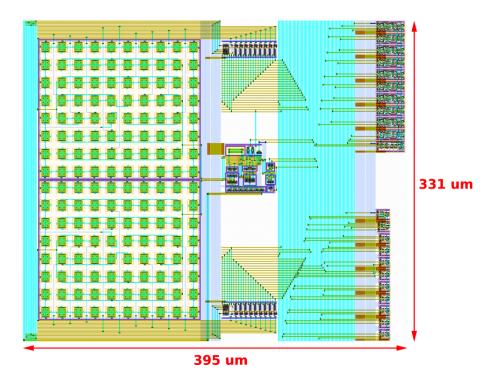

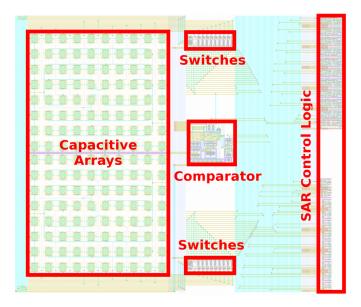

|      | Floorplan of the SAR ADC.                                            | 56 |

|      | Analog and digital blocks composing the SAR ADC                      | 57 |

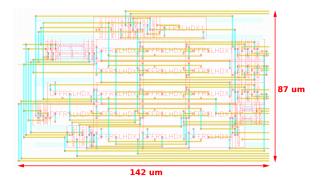

|      | Layout of the shared digital logic among all the ADCs on chip.       | 57 |

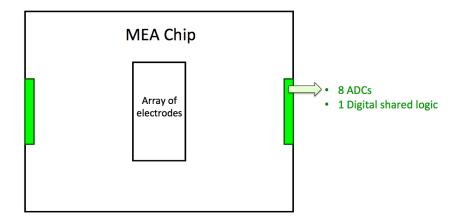

|      | Floorplan of the ADCs integrated on the MEA chip                     | 57 |

|      |                                                                      |    |

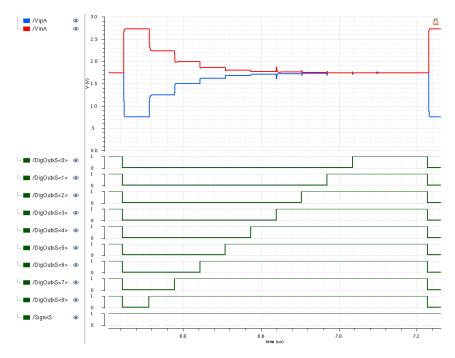

| 4.1 | Example of an analog-to-digital conversion performed by the |    |

|-----|-------------------------------------------------------------|----|

|     | SAR ADC.                                                    | 59 |

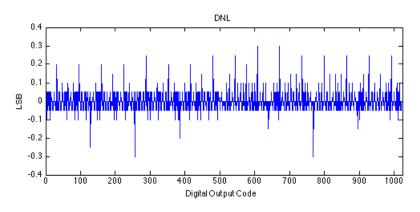

| 4.2 | DNL histogram plot of the SAR ADC                           | 59 |

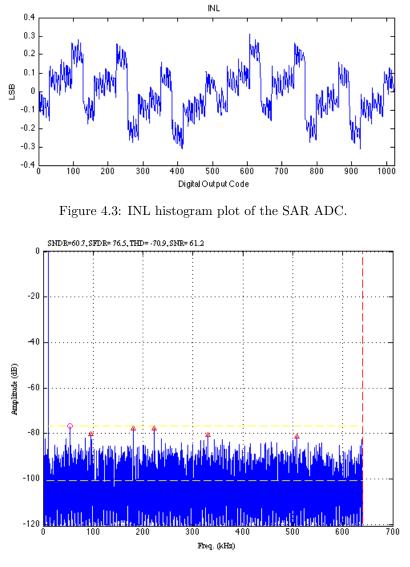

| 4.3 | INL histogram plot of the SAR ADC.                          | 60 |

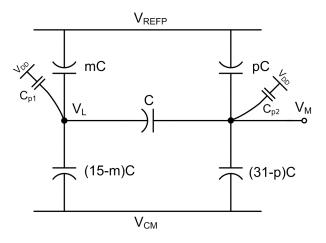

| 4.4 | 2'048-points FFT output of the SAR ADC                      | 60 |

|     |                                                             |    |

| 5.1 | Switched-capacitor DAC equivalent circuit.                  | 64 |

| 5.2 | 3-bit switched-capacitor DAC and its equivalent circuit     | 66 |

# List of Tables

| 1.1 | Performance summary of the MEA chip presented in [1]. The reported values are based on experimental measurements             | 5  |

|-----|------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Specifications for a single ADC                                                                                              | 7  |

| 3.1 | Summary of the most relevant parameters for the available types of capacitors.                                               | 14 |

| 3.2 | Examples of the resulting parametric estimation of $\sigma(V_{M,D_{IN}=256})$<br>for the bw and 2bw1Cs capacitive arrays.    | 21 |

| 3.3 | Summary of the results for the design of the capacitive array.                                                               | 22 |

| 3.4 | Calculated and simulated settling time for $D_{IN}$ transiting                                                               |    |

|     | from 0 to 256                                                                                                                | 34 |

| 3.5 | Preamplifier specifications                                                                                                  | 47 |

| 4.1 | Summary of the ADC power consumption                                                                                         | 60 |

| 4.2 | Requirements and estimated performance of a single SAR ADC.                                                                  | 61 |

| 4.3 | Specifications of the single-slope data-conversion system cur-<br>rently implemented on chip, compared to the performance of |    |

|     | the SAR ADCs                                                                                                                 | 61 |

|     |                                                                                                                              |    |

## Abstract

For both the electrical stimulation and recording of cultured neurons, the CMOS-based microelectrode arrays (MEAs) are one of the most promising electronic devices used nowadays. To ensure a robust transmission of the information between the chip and external devices, the MEA chip requires integrated analog-to-digital converters (ADCs). Moreover, the presence of a large number of read-out channels on chip poses stringent requirements on both area and power consumption for the design of the ADCs. Thus, this Master's thesis work proposes a low-power and compact successive approximation register (SAR) ADC for such bio-electronic chips.

In this thesis, some low-power ADC topologies are first investigated and the SAR ADC is finally chosen, that is the optimum solution for the application. The choice of multiplexing the read-out channels of the MEA chip for the analog-to-digital conversion is then presented while the requirements for the ADC are derived. In this work, the design of each part of the converter is described, starting from the switched-capacitor array which is usually used as a sample and hold (S/H) as well as a digital-to-analog converter (DAC). The size of the switches that are providing the signals to the DAC is optimized considering the timing requirements. Furthermore, low power solutions are proposed for the comparator while good performances are achieved for both noise and speed. A successive approximation register logic is finally used to provide the digital control signals.

The performance of the SAR ADC is evaluated with post-layout simulations. All the preliminary requirements are met and the proposed converter represents a promising solution for low-power applications. In conclusion, the specifications of the entire data-conversion system are compared with the ADCs currently implemented on the MEA device and a possible improvement of the chip is presented.

**Key words**: Microelectrode Array (MEA), Switched-Capacitor (SC) Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC), Low-Power, Split Capacitor Array, Offset Cancellation.

## Sommario

Fra i dispositivi che permettono la stimolazione e la misura dell'attività elettrica di colture neuronali, i CMOS microelectrode array (MEA) sono una delle migliori soluzioni utilizzate oggigiorno. Per una sicura trasmissione di informazioni dal chip ai dispositivi esterni, il dispositivo MEA richiede convertitori analogico-digitali (ADC) da integrare nel chip. In particolare, la progettazione di tali circuiti deve essere eseguita limitando il consumo di area e potenza in quanto il numero di canali di lettura integrati è elevato. Per questo motivo, la presente tesi propone un ADC ad approssimazioni successive (SAR) compatto e a basso consumo di potenza per chip bioelettronici.

In questa tesi, diverse tipologie di ADC a risparmio di potenza sono inizialmente investigate e il modello SAR è infine scelto, in quanto dimostra di essere la soluzione ottimale per l'applicazione studiata. La scelta di utilizzare il multiplexing dei canali di lettura per la conversione analogico-digitale è quindi presentata assieme alle specifiche dell'ADC. La progettazione di ogni componente elettronico del convertitore è poi descritta, iniziando dall'array a capacità commutate che è usato sia come sample and hold (S/H), sia come convertitore digitale-analogico (DAC). Le dimensioni degli interruttori che forniscono i segnali al DAC sono ottimizzate considerando le specifiche del tempo di assestamento. Una soluzione a basso consumo di potenza è proposta per il comparatore e un registro ad approssimazioni successive è usato per generare i segnali digitali di controllo.

Le prestazioni dell'ADC SAR sono valutate con simulazioni post-layout. Tutte le specifiche stabilite sono soddisfatte e il convertitore proposto rappresenta una promettente soluzione per applicazioni a basso consumo di potenza. La performance dell'intero sistema di ADC integrabile nel dispositivo MEA è dunque confrontata con quella degli ADC a singola rampa al momento implementati sul chip e un possibile miglioramento del dispositivo è presentato.

**Parole chiave**: Microelectrode Array (MEA), Convertitore Analogico-Digitale (ADC) ad Approssimazioni Successive (SAR) a Capacità Commutate (SC), Basso Consumo di Potenza, Array a Capacità Commutate, Cancellazione dell'Offset.

## Chapter 1

## Introduction

### 1.1 Motivation

The CMOS-based microelectrode arrays (MEAs) [1] are sophisticated devices, which can be used to bidirectionally communicate with cultured neurons. They can perform measurements at a high spatial and temporal resolution, which is hardly achievable with passive MEAs. A switch-matrix-based high-density MEA chip [2] has been developed at Bio Engineering Laboratory of ETH Zürich. With the switch-matrix scheme, an arbitrary subset of around 11'000 electrodes can be selected for recording and stimulation. By placing the front-end amplifiers outside the array, a high signal-to-noise ratio (SNR) has been achieved together with a subcellular spatial resolution.

To ensure robust and stable transmissions of the information between the chip and other devices on the printed circuit board (Figure 1.1), the amplified and filtered neural signals are usually digitized by on-chip analogto-digital converters (ADCs). The number of neural signals which can be recorded simultaneously is limited by the number of read-out channels integrated on the chip, hence, in order to observe the electrical activity of a large scale neural network, the 126 read-out channels of the previous design are not sufficient. Therefore, the new version of the chip integrates much more channels, posing stringent area and power consumption constraints on the individual read-out channel and ADC.

### 1.2 MEA Chips Developed at BEL

### 1.2.1 Interfacing Electrogenetic Cells in Vitro with CMOS Microelectrode Arrays

Complementary semiconductor-metal-oxide (CMOS) technology is a very powerful technology used to realize substrate-integrated microelectrode arrays. These devices are arrangements of electrodes that can be more or

Figure 1.1: Packaged MEA chip on a custom-designed printed circuit board.

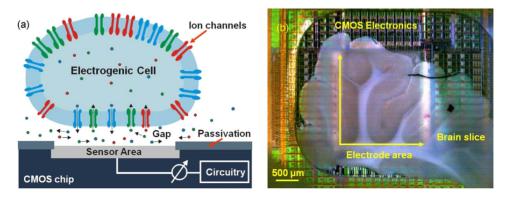

less directly interfaced to electrogenetic cells, like heart or brain cells. It is therefore possible to study fundamentals of learning processes and assess the behavior of electrogenetic cells *in vitro* by culturing or placing them directly atop the electronic chips, as shown in Figure 1.2.

Figure 1.2: (a) Schematic of a cell attached to a sensor surface. (b) Micrograph of an acute cerebellar brain slice (parasagittal cut) placed on a CMOS high-density electrode chip for measurements.

The CMOS technology plays an important role for such devices since it allows the possibility to address a large number of microelectrodes on the same chip, leading to a spatial sub-cellular resolution. Another advantage of using CMOS integrated circuits (ICs) is the high signal quality provided and the relative low-noise electrophysiological recordings that can be performed from a variety of biological preparations. Many functions can be programmed via software and digital interfaces. The recording technique is extracellular and noninvasive, enabling long-term measurements.

Applications areas for such devices include neuroscience as well as medical diagnostics and pharmacology. The most common biological preparations studied using microelectrode arrays are *acute* tissue preparations (e.g, slices) which are recorded from immediately after they have been cut from the animal and *cell cultures*.

#### 1.2.2 The High-Density MEA Chip

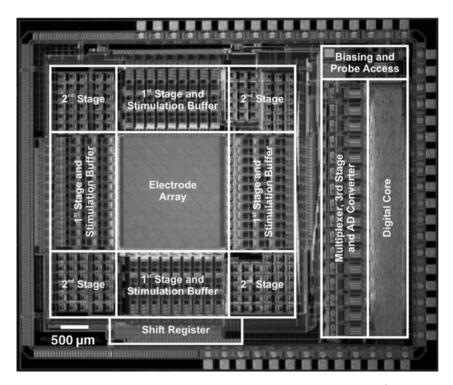

The Bio Engineering Laboratory (BEL) of ETH Zürich designed a CMOSbased microelectrode array [1] featuring 11'011 metal electrodes and 126 read-out channels for extracellular bidirectional communication with electrogenetic cells. The micrograph of the chip is shown in Figure 1.3. The most important features include:

- High spatial resolution at (sub)cellular level with 3'150 electrodes per mm<sup>2</sup>. The electrode diameter is 7  $\mu$ m and the electrode pitch is 18  $\mu$ m.

- A reconfigurable routing of the recording sites to the 126 read-out channels.

- A low front-end input referred noise of 2.4  $\mu$ V<sub>rms</sub>.

Figure 1.3: Micrograph of the MEA chip  $(7.5 \times 6.1 \text{ mm}^2)$ .

The high-density arrays are usually CMOS-based devices that overcome the connectivity limitation by making use of on-chip signal multiplexing. The simultaneous recording from all electrodes requires the frontend amplifiers being placed in each pixel (recording site), which, due to area constraints, entails rather high noise levels. Instead of scanning the entire electrode array, the approach of this device provides a reconfigurable electrode/readout-channel routing to select an arbitrary subset of electrodes for recording and stimulation. This enables both, low-noise signal recording, and cellular or subcellular resolution, since the front-end circuitry can be placed outside the array.

Figure 1.4: Block diagram of the MEA chip.

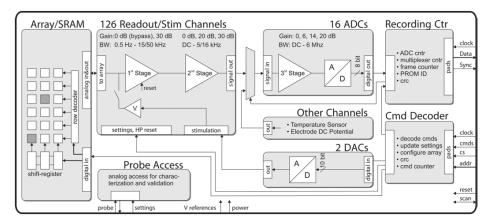

In the MEA chip designed by BEL [2] the read-out 126 channels and the associated signal amplification and stimulation circuitry are located outside the reconfigurable electrode array, where sufficient area for a low-noise circuit implementation is available (Figure 1.3). The readout channels includes two amplification and filter stages. Both stages feature digitally configurable gain and filter settings. The first stage provides bandpass filtering (BPF) and a gain of 30 dB. The second stage provides an additional gain of either 0 dB, 20 dB or 30 dB with a second LPF. Eight channels are then multiplexed and buffered by a third stage with an additional gain of 0 dB, 6 dB, 14 dB or 20 dB, and finally digitized at 20 kHz using successive-approximation analog-to-digital converters (ADCs) with a resolution of 8-bit. The digital recording controller then transfers the data off chip by means of a 9-bit bus together with chip-status information and a CRC (cyclic redundancy check) for error detection.

The chip was fabricated in an industrial 0.6  $\mu$ m 3-metal 2-polysilicon CMOS-process. The total area of the device is 7.5 × 6.1 mm<sup>2</sup>, while the electrode array covers an area of 2.0 × 1.75 mm<sup>2</sup>. The front-end inputreferred noise within the band of 1 Hz to 100 KHz is 2.4  $\mu$ V<sub>rms</sub>. The maximum gain of the entire read-out circuit is 80 dB. The power consumption of the front-end (first and second stage) is 160  $\mu$ W/channel while the overall power consumption of the chip is 135 mW. The most relevant specifications characterizing the chip are summarized in Table 1.1.

| Parameter                                        | Value                          |

|--------------------------------------------------|--------------------------------|

| Technology                                       | $0.6 \mu m 3M2P CMOS$          |

| Area                                             | $7.5 \times 6.1 \text{ mm}^2$  |

| Supply voltage analog                            | 5.0 V                          |

| Supply voltage digital                           | 3.0 V                          |

| Clock frequency recording controller             | 3.2 MHz                        |

| Clock frequency comand controller                | 8 MHz                          |

| Number of electrodes                             | 11'011                         |

| Sensor area                                      | $2.0 \times 1.75 \text{ mm}^2$ |

| Electrode density                                | $3'150 \ 1/mm^2$               |

| Power consumption overall                        | $135 \mathrm{mW}$              |

| Power consumption front-end (stage 1&2)          | 160 $\mu W/channel$            |

| Front-end input-referred noise (1 Hz to 100 kHz) | $2.4 \ \mu V_{rms}$            |

| Amplification                                    | 0-80 dB (18 steps)             |

Table 1.1: Performance summary of the MEA chip presented in [1]. The reported values are based on experimental measurements.

## 1.3 Thesis Organization

Requirements and specifications of the ADC for the new version of the MEA chip are defined in Chapter 2 where different topologies of converters are analyzed. Chapter 3 presents the design of the SAR ADC, showing the analysis and simulations of the switched-capacitor array, switches, comparator and SAR control logic. The characterization of the converter is shown in Chapter 4 where the conclusions are reported. Finally, Chapter 5 is reserved for the appendix.

## Chapter 2

# Specifications and ADC Topologies

This chapter provides the key design aspects for the new version of the chip. The choice of multiplexing the read-out channels for the analog-to-digital conversion is then presented and the requirements for the ADC are derived. Finally, some low-power ADC topologies are investigated and the optimum solution for our application is chosen.

## 2.1 Required ADC for the New Version of the Chip

The presence of on-chip ADCs is an essential requirement for allowing a robust signal transmission between the chip and the printed-circuit board (PCB). For the MEA chip presented in [2], 16 successive approximation ADCs with a 8-bit resolution have been employed.

In order to observe the electrical activity of a large-scale neural network, the new version of the chip needs to provide an increased number of channels  $N_{Channels}$  equal to 1'024, which poses stringent area and power consumption constraints on the individual read-out channel and ADC. In order to improve the signal quality, in the new design, the number of bits is increased to 10. For this reason, a thorough noise and offset analyses of the converter are key aspects that have to be considered during the design.

### 2.2 Elaboration of Specifications

The frequency band for typical neural signals is roughly 10 Hz  $\sim 5$  KHz [3]. In order to avoid aliasing and ease spike sorting, the sampling frequency for a single read-out channel is set to 20 KHz. The number of ADCs is reduced by multiplexing the signals before their effective conversion. For the new design, a number of 16 ADCs has been aimed to be integrated on the chip, leading to the following sampling frequency  $f_S$  for each converter:

$$f_S = \frac{N_{Channels}}{N_{ADCs}} f_N = \frac{1024}{16} \times 20kHz = 1.28 \ MS/s \tag{2.1}$$

Due to limited chip area, the area for each ADC is restricted to  $1 \text{ mm}^2$ . To reduce quantization error, 10-bit resolution is chosen while the signalto-noise and distortion ratio (SNDR) is set to be larger than 56 dB, which corresponds to an effective number of bits (ENOB) equal to 9. The new version of the chip will be designed using a 0.35  $\mu$ m CMOS technology and a 3.3 V power supply, aiming to a maximum power consumption of 1 mW for each ADC. The preliminary specifications are summarized in Table 2.1.

| Parameter         | Value                 |

|-------------------|-----------------------|

| Resolution        | 10 bits               |

| Sampling rate     | $1.28 \mathrm{~MS/s}$ |

| SNDR              | $\geq 56 \text{ dB}$  |

| Power consumption | $\leq 1 \text{ mW}$   |

| Supply voltage    | 3.3 V                 |

| Technology        | $0.35 \ \mu m \ CMOS$ |

| Area              | $\leq 1 \text{ mm}^2$ |

Table 2.1: Specifications for a single ADC.

### 2.3 Low Power ADC Topologies Overview

In order to evaluate to evaluate which ADC architecture [4] best satisfies the presented requirements, some of the most important topologies are briefly reviewed in this section.

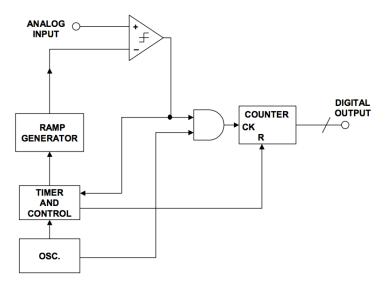

#### Integrating ADC

The Integrating ADC can be an appropriate solution for low-speed applications where low power consumptions are required. A possible implementation of this topology is the single-slope architecture, shown in Figure 2.1, where the input signal is compared with a voltage ramp. Counting the time required by the ramp to reach the signal value, it is possible to perform the analog-to-digital conversion. Even if this solution presents a very simple structure (a comparator, the voltage ramp generator and the counter in principle), it suffers from several drawbacks. A stable and precise ramp generator is required since voltage and temperature coefficients can affect the linearity of the conversion. Moreover, a high clock frequency is desired in order to reach a sufficient resolution.

Figure 2.1: Single-slope ADC [4].

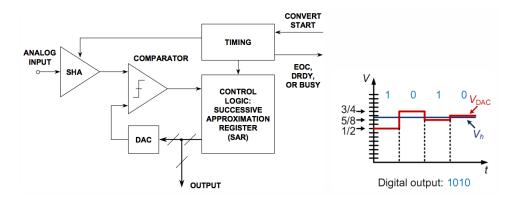

#### Successive-Approximation ADC

The successive-approximation ADC is based on the binary search algorithm and it requires a simple structure based on a sample and hold (S/H), comparator, digital-to-analog converter (DAC) and the successive approximation register (SAR). This is a topology mostly used to design medium-high resolution ADCs for medium-low speed applications. The DAC is controlled by the SAR logic and its output voltage varies depending on the decision of the comparator, as shown in Figure 2.2. Besides the simple structure, the converter presents a low power consumption as well.

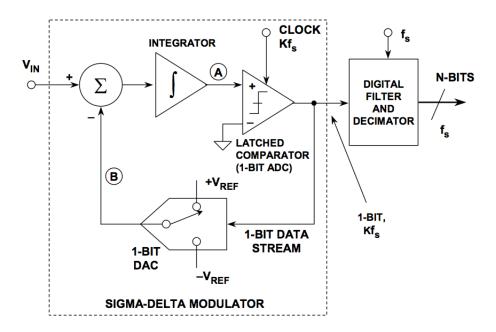

#### Sigma-Delta ADC

The Sigma-Delta ADC is one of the best solutions if high resolution is required in low frequency applications. The converter is based on the oversampling and noise shaping techniques and it can achieve high signal-to-noise ratio (SNR). The analog part of the circuit is simple since only a comparator, voltage reference, integrators and analog summing circuits are required. On the other hand, the digital circuitry is quite complex and it consists of a digital signal processor (DSP) which acts as a digital filter and decimator (Figure 2.3). The delta modulation is used to achieve higher transmission efficiency by transmitting the changes (delta) in value between consecutive samples. Combining the oversampling with the sigma-delta modulator it

Figure 2.2: Successive-approximation ADC structure [4] and a 4-bit analog-todigital conversion.

is possible to obtain a high SNR at low frequencies by shaping the quantization noise such that most of it occurs outside the bandwidth of interest. The noise outside the frequency bandwidth of interest will be removed by the digital filter while the decimator will reduce the output data rate back to the Nyquist rate. Some of the disadvantages of this structure are the high clock frequency required and the large silicon area consumed by the digital part.

Figure 2.3: First-order sigma-delta ADC [4]

### 2.4 Fully Differential Switched-Capacitor SAR ADC

Considering the ADC specifications mentioned in Section 2.2, the successive approximation ADC has been preferred among the three different low-power ADC topologies presented. The most relevant advantages of this topology are the following:

- Low power consumption: Since the SAR ADC does not contain any power-hungry operational amplifiers (OpAmps), it is a well-known topology for its power efficiency. In fact, the comparator usually consumes less than an OpAmp since it does not need linear settling.

- Simple structure: The low complexity of the circuit ease its implementation on chips where compact realizations are required. This is also due to the very simple principle on which the ADC is based, the binary search algorithm. Moreover, promising solutions can also be evaluated in order to reduce even more the total area required by the ADC.

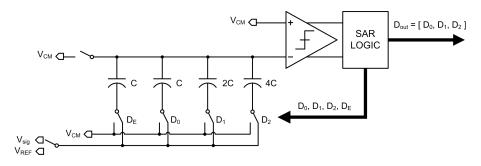

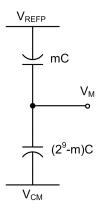

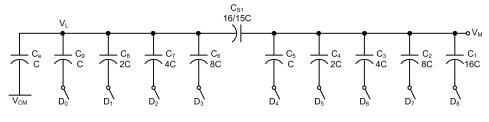

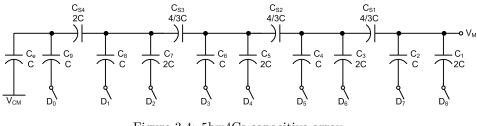

In particular, the converter presented in this work is a fully differential switched-capacitor or charge-redistribution SAR ADC [5]. This circuit incorporates an array of capacitors that is usually used as a S/H as well as a DAC. In order to better understand the operation, we first consider a simple single-ended 3-bit switched-capacitor ADC with a binary weighted capacitive array [6], which is shown in Figure 2.4. The main parts of the circuit are: the capacitive array, the switches, the comparator and the SAR control logic.

Figure 2.4: 3-bit single-ended switched-capacitor SAR ADC.

During the sampling phase, the top plates of the capacitors are reset to the common voltage  $V_{CM}$  while all the bottom plates of the capacitors are connected to the input signal source  $V_{sig}$  that is equal to the sum of  $V_{CM}$ and the input signal component  $\Delta V_{sig}$ . The switches resetting the input node of the comparator are then turned off and all the bottom plate nodes are connected to  $V_{CM}$ , performing the so-called 'bottom plate sampling' [7]. Now that the voltage  $V_{CM} - \Delta V_{sig}$  is stored on the top plate node of the capacitors, the switch controlled by  $D_2$  is connected to  $V_{REF}$  and a voltage equal to  $V_{REF}/2$  is added to  $V_{CM} - \Delta V_{sig}$ . The comparator can therefore determine the most significant bit (MSB) by comparing this value with  $V_{CM}$ . The SAR control logic either leaves the switch controlled by  $D_2$  connected to  $V_{REF}$  or connects it back to  $V_{CM}$  depending on the comparator output. A similar process is followed for the remaining two bits leading to the determination of the digital output value. All the switches are then reset again to the initial positions and the converter can start another cycle of conversion [4]. Note that the extra LSB capacitor (C in the case of the 3-bit DAC) is required to make the total value of the capacitive array equal to 8C, so that binary division is accomplished when the individual bit capacitors are manipulated.

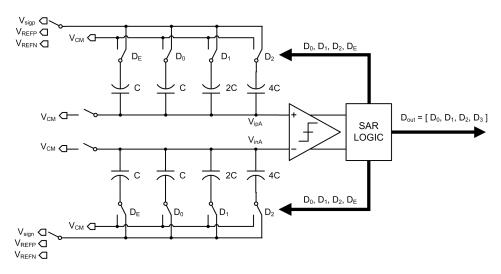

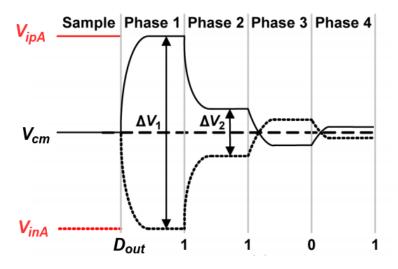

Using the same switched-capacitor array of the previous example and considering a fully differential topology of the circuit, the 4-bit ADC shown in Figure 2.5 is obtained. This new structure differs from the single-ended one in Figure 2.4 in various aspects, i. e., the differential input signal for the comparator, two identical capacitive arrays and two different references voltages  $V_{REFP}$  and  $V_{REFN}$ . Note that this structure gains an additional bit  $D_3$  that is the 'sign bit' and it is determined once the differential input signals are sampled on the input nodes of the comparator. Hence, the MSB bit corresponds to the sign of the output digital value. Each reference voltage is assigned to a capacitive array depending on the result of the sign bit decision. At this point, the switch controlled by  $D_2$  in each array is connected to the respective reference voltage and the values of the remaining 3 bits are determined using the binary search algorithm, as explained in the singleended example. The voltages at the input nodes of the comparator,  $V_{ipA}$  and  $V_{inA}$ , during the sampling and conversion phases are shown in Figure 2.6.

Figure 2.5: 4-bit fully differential switched-capacitor SAR ADC.

Figure 2.6: Voltages at  $V_{ipA}$  and  $V_{inA}$  during the sampling and conversion phases for the 4-bit fully differential switched-capacitor SAR ADC [8].

Since the overall accuracy and linearity of the SAR ADC is primarily determined by the internal DAC, the switched-capacitor realizations of it have become very popular in newer SAR ADCs due to their high accuracy and linearity. A high degree of temperature stability is another advantage of these capacitive DACs. Moreover, the fully differential analog signal path has been preferred respect to a single-ended one for the following main reasons:

- Immunity to common-mode noise.

- The input dynamic range is doubled, which relaxes the design requirements of the comparator.

## Chapter 3

## **Design** implementation

### 3.1 Design Guidelines

The design of the SAR ADC has been conducted focusing on the power and area constraints while maintaining good linearity performances for the analog-to-digital conversion. Switched-capacitor arrays are used to implement both the S/H and DAC while minimizing the area of the unit capacitor. Parasitic capacitances and matching properties have been taken into account during the analysis. Switches are providing the signals to the DAC and their size has been optimized focusing on the timing requirements. A low power solution is proposed for the comparator while achieving good noise performances and speed requirements. The input-offset storage technique has been chosen for this stage and a dynamic latch has been preferred. The digital control signals are provided by a successive approximation register.

### 3.2 Switched-Capacitor Array