# High-K Dielectric FinFETs on Si-Bulk for Ionic and Biological Sensing Integrated Circuits

#### THÈSE Nº 6134 (2014)

#### PRÉSENTÉE LE 2 MAI 2014

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

LABORATOIRE DES DISPOSITIFS NANOÉLECTRONIQUES

PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

#### Sara RIGANTE

acceptée sur proposition du jury:

Prof. Ph. Renaud, président du jury Prof. M. A. Ionescu, directeur de thèse Prof. M. Gijs, rapporteur Prof. E. Kan, rapporteur Prof. C. Schönenberger, rapporteur

Io, eterno studente perché la materia di studio sarebbe infinita e soprattutto perché so di non sapere niente. Francesco Guccini To all the beloved who made me smile during my Ph.D.

## **Abstract**

Nanotechnology is a broad branch of science dedicated to the manipulation of matter featuring critical dimension below 100 nm. Despite the futuristic common mindset towards nanotechnology, anybody using an electronic device able of computing and processing data is using nanotechnology. Transistors, the smallest units of a microprocessor, have reached critical gate lengths in the tenths of nanometers. Lately, the idea of nanotechnology has been associated with small robots capable of exploring and operating within the human body. Though this type of technology may have to wait several years and overcome many obstacles, the idea does arise from several solid and proved emerging applications of nanotechnology in the field of life sciences.

Field-Effect Transistors (FET) based on Silicon Nanowires (SiNW) have emerged as promising candidates for a new generation of label-free real-time sensors for the detection of chemical and biological species. Many areas of science such as nanoelectronics, chemistry, physics, biology and medicine have been collaborating together in these recent developments. Despite SiNWs' potential has been largely proven and the knowledge of sensing mechanisms widely extended, mass-production and integration of such sensors has still to face many challenges.

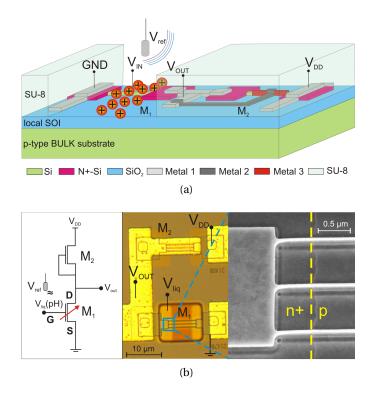

The demonstration of a state-of-the-art FET sensor, compatible with CMOS Integrated Circuits, is addressed in this thesis. A *fully-depleted n-channel Fin Field-Effect Transistor* (FinFET) has been implemented as sensor in a liquid environment, according to the working principle of the Ion Sensitive Field-Effect Transistor (ISFET). Its vertical architecture and multiple gate control provide high stability and high signal-to-noise ratio. Moreover, such an architecture works under low applied voltages and currents, taking into consideration the power constraints of the semiconductor industry.

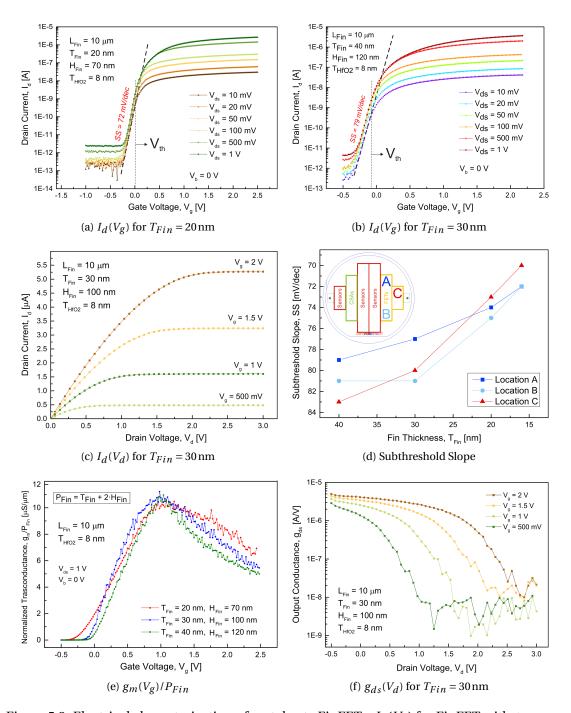

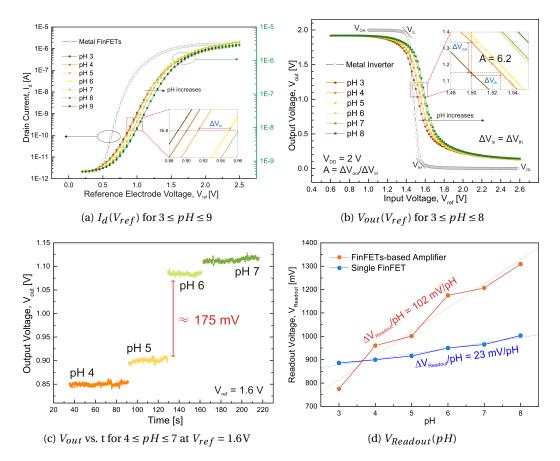

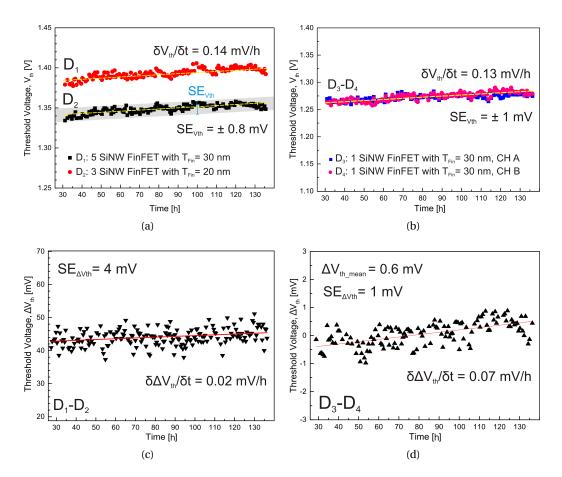

In this thesis, FinFETs with critical dimensions of the order of 30 nm have been designed, fabricated and characterized for their implementation as both circuit and sensing units in a microfluidic platform. A challenging fabrication process has been carried out on Si-bulk substrates where vertical transistors have been defined and then insulated by the so-called  $Si_3N_4$  spacer technology. FinFETs featuring a metal-gate have been successfully characterized, showing excellent electrical properties in terms of subthreshold slope, SS= 72 mV/dec, and on-off current ratio,  $I_{on}/I_{off}=10^6$ . These FinFETs have then been validated as pH sensors. Sensitivity close to the Nernst limit, S = 57 mV/pH, and high current variation at the readout,  $S_{out}=60\%$ , have been achieved. Long-term measurements have been performed over 4.5

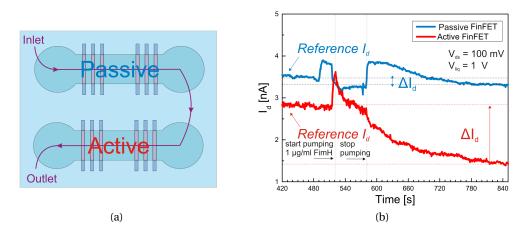

days, demonstrating that stability and reliability are key-advantages of the FinFETs. The drift over time has been calculated to be  $\delta V_{th}/\delta t = 0.13\,\mathrm{mV\,h^{-1}}$  with accuracy of 0.012 pH. FimH protein has been successfully detected with a differential pair of FinFETs.

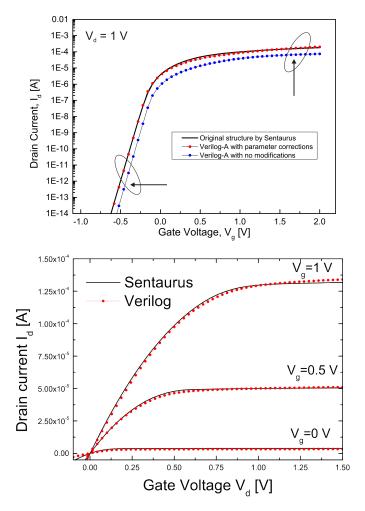

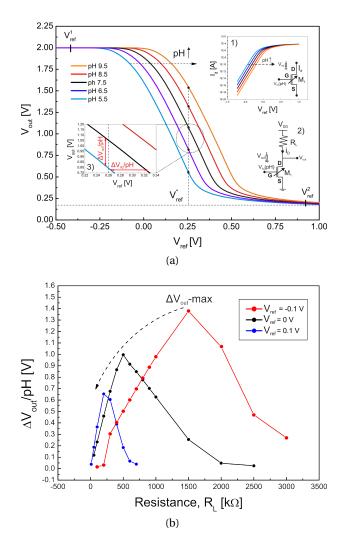

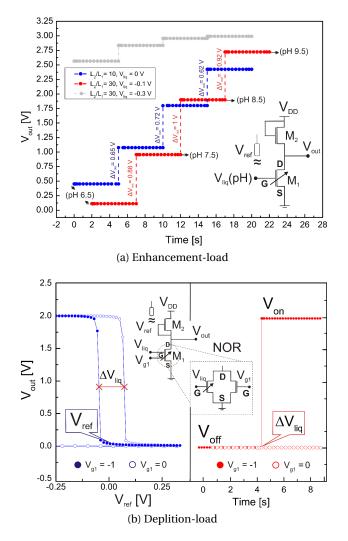

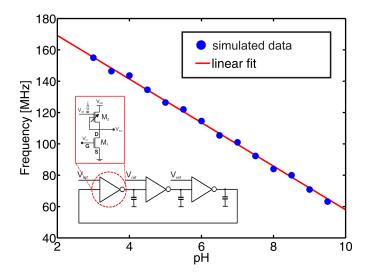

Finite Element Analysis (FEA) simulations have been performed to optimize the geometrical and electronic properties of the FinFETs. They have also proven to be a reliable tool for the calibration of fabrication steps, such as ion implantation and bulk wet oxidation. SPICE simulations, implementing analytical equations in Verilog-A, have been used to connect two or more devices together. A sensing common source amplifier, a ring oscillator and a pseudo-differential amplifier have been demonstrated.

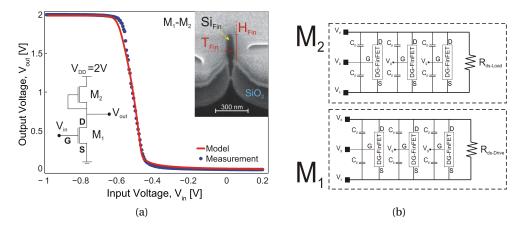

Moreover, from the idea developed through circuit simulations, a device consisting of a metalgate FinFET and a liquid-gate FinFET has been fabricated and demonstrated as sensing amplifying stage. If the sensing FinFET with liquid-gate is implemented as driver transistor and the metal-gate FinFET as load, the sensing variation at the input is amplified with a gain  $A = \Delta V_{out}/\Delta V_{in} = 6.6$ .

Low power consumption has been guaranteed for both single (tens of nW) and pair of FinFETs (few hundreds of nW), and without the use of a back-gate.

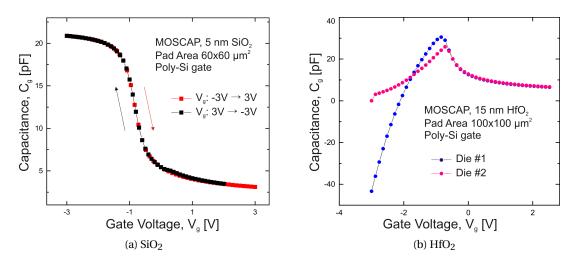

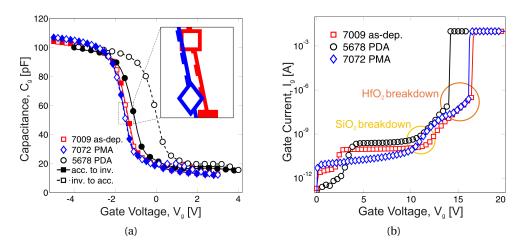

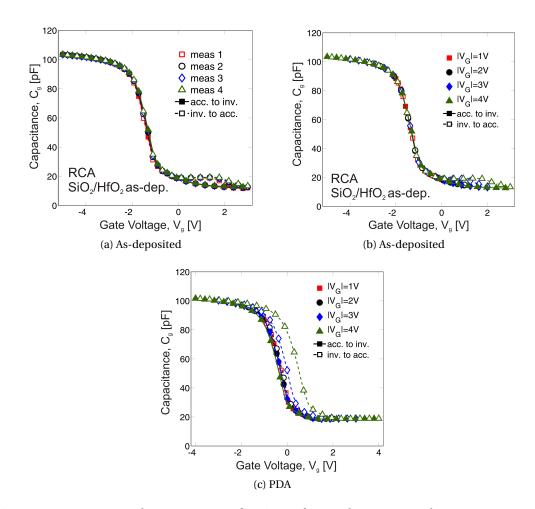

All devices feature an HfO<sub>2</sub> high-k gate dielectric. High-k oxides allow the continuous CMOS scaling process and they also provide the best sensitivity for pH applications. An electrical characterization based on HfO<sub>2</sub> MOS capacitor has been performed to investigate the impact of some fabrication factors on the oxide features. Good dielectric constant,  $\varepsilon_{HfO_2}$  = 19, high breakdown voltage,  $V_{BD}$  = 14V, and negligible values of hysteresis have been achieved.

**Keywords:** Field Effect Transistor (FET) sensors, FinFET, ISFET, label-free sensor, nanoelectronics, pH sensor, biochemical sensing, Si-bulk, high-k dielectric, hafnium oxide, fully-depleted device, low power, Nernst limit, sensing integrated circuits, sensing common source amplifier, signal amplification, long-term stability.

## Riassunto

La nanotecnologia è un ampio ramo della scienza dedicato alla manipolazione della materia con dimensioni critiche inferiori ai 100 nanometri. La Nanotecnologia non è una visione scientifica futuristica, chiunque usi un dispositivo elettronico in grado di calcolare e processare dati ne fa uso. Al giorno d'oggi, i transistors, gli elementi più piccoli di un microprocessore, hanno raggiunto dimensioni critiche di qualche decina di nanometro. Recentemente, il concetto di nanotecnologia è stato associato a quello di piccoli robot in grado di esplorare e di operare nel corpo umano. Questo dovrà aspettare qualche anno e sormontare molti ostacoli, ma l'idea sorge da concrete emergenti applicazioni della nanotecnologia alla biologia.

I transistor a effetto di campo (FET) basati su nanofili di silicio (SiNW) sono emersi come candidati promettenti per una nuova generazione di sensori label-free per il rilevamento in tempo reale di specie chimiche e biologiche. Molti settori scientifici come nanoelettronica, chimica, fisica, biologia e medicina hanno collaborato a questi recenti sviluppi. Nonostante il potenziale dei SiNW e le sempre piu diffuse conoscenze dei meccanismi di rivelazione, la produzione di massa e l'integrazione di questi sensori rimane confrontata a molte sfide.

In questa tesi, viene affrontata l'implementazione come sensore di un transistor all'avanguardia tecnologica e compatibile con circuiti integrati CMOS. Un fully-depleted n-MOS FinFET, viene qui dimostrato come sensore in ambiente liquido, sul principio di funzionamento dell'Ion Sensitive FET (ISFET). La sua architettura verticale ed il controllo dato da molteplici gate, sono in grado di fornire stabilità ed un buon rapporto segnale-rumore. Inoltre, una tale architettura funziona con basse tensioni di alimentazione e correnti, tenendo in considerazione i bisogni di basso consumo dell'industria dei semiconduttori.

In questa tesi, FinFETs con dimensioni critiche dell'ordine di 30 nm sono stati progettati, fabbricati e caratterizzati per essere implementati come unità circuitali e unità sensoristiche in una piattaforma microfluidica. Un laborioso processo di fabbricazione è stato condotto su substrati di silicio, sui quali i transistor verticali sono stati creati e isolati con spaziatori di  $Si_3N_4$ . I FinFETs con gate metallici sono stati caratterizzati per primi, dimostrando eccellenti proprietà elettroniche di Subthreshold Slope SS= 72 mV/dec, e un'ottimo rapporto di correnti on-off,  $I_{on}/I_{off}=10^6$ . In seguito, è stato quindi dimostrato come questi FinFETs possano essere usati come sensori di pH. Sono state ottenute una sensibilità vicina al limite di Nernst, S= 57 mV/dec, ed un' alta variazione di corrente all'uscita pari al 60%. Una misura a lungo termine è stata condotta per un periodo di 4.5 giorni, dimostrando la stabilità e l'affidabilità

di questi FinFET. Sono state calcolate una deriva nel tempo di soli  $\delta V_{th}/\delta t = 0.13$  mV/h con un'accuratezza di 0.013 pH.

La proteina FimH è anche stata rivelata per mezzo di una coppia differenziale di FinFET.

Le caratteristiche geometriche ed elettroniche dei FinFETS sono state ottimizzate grazie a simulazioni ad elementi finiti (FEA). Tale analisi si è rivelata essere uno strumento affidabile per la calibrazione di vari fasi del processo di fabbricazione come l'impiantazione ionica e l'ossidazione termica del silicio. Sono state effettuate anche simulazioni con SPICE, implementando equazioni analitiche scritte in Verilog-A, per collegare due o più FinFET, ottenendo quindi un'amplificatore common source, un ring oscillator, ed un amplificatore pseudo-differenziale con capacità di sensing.

In seguito a queste simulazioni è stato fabbricato un dispositivo composto da un FinFET con gate metallico e un FinFET con gate liquido e ne è stato dimostrato l'uso in quanto modulo di amplificazione. Implementando il FinFET con gate liquido come driver tranistor ed il FinFET con gate metallico come carico, la variazione all'ingresso è stata amplificata con un guadagno  $A = \Delta V_{out}/\Delta V_{in} = 6.6$ . La potenza totale dissipata è molto bassa, sia per un FinFET singolo (decina di nW) che per una coppia di FinFET (centinaia di nW), e non è stato fatto uso di back-gate.

Tutti i dispositivi fabbricati presentano un gate isolante ad alta costante dielettrica (high-k) in  $HfO_2$  che consente non solo la compatibilità con la continua miniaturizzazione CMOS, ma anche una migliore sensibilità per applicazioni pH. Una caratterizzazione elettrica basata su condensatori MOS in  $HfO_2$  ha inoltre permesso di definire l'impatto di vari fattori del processo di fabbricazione sulle caratteristiche dell'ossido. Sono quindi state ottenute una costante dielettrica  $\varepsilon_{HfO_2}$  = 19, una tensione di rottura dell'ossido  $V_{BD}$  = 14V e un'isteresi trascurabile.

**Parole chiave:** sensori Field-Effect Transistor (FET), FinFET, ISFET, sensori label-free, nanoelettronica, sensori di pH, sensori biochimici, Si-bulk, dielettrici ad alta costante dielettrica (high-k), ossido di afnio, dispositivi fully-depleted, basso consumo, limite di Nernst, circuiti integrati sensoristici, sensori ad amplificazione common source, amplificazione del segnale, stabilità a lunga durata.

# Acknowledgements

I would first like to thank my advisor, Prof. Ionescu for giving me the possibility of undertaking this incredible journey into such advanced field of technology. Most of all, I would like to thank him for the chance of being involved in a valuable project such as Nanotera and participating to high level conferences in the field of sensors.

Thanks to all my present and former Nanolab colleagues. In particular, A. Bazigos, L. De Michielis, H. Guerin, E. Buitrago, W. Vitale, A. Biswas and M. Berthomé for being so patient with all my questions and doubts especially in the last year of my thesis. I. Buzzi and K. Jaymes for being there at the time and situations you don't expect them to be. Thanks to Prof. Sallese for receiving me every time I was getting lost in theoretical aspects. Thank to M. Halm and Prof. Gijs for being solid supports of the EDMI school.

The work here presented is the result of a long journey...

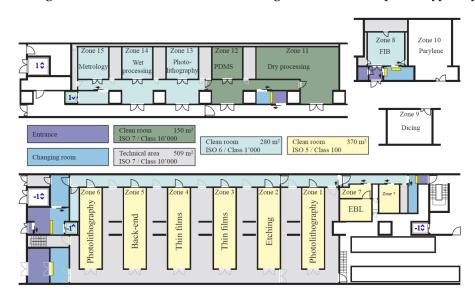

Everything started at CMi, where a wide team of valuable experts helped me to go through apparently insurmountable obstacles every day. In particular, I would like to thank P. Fluckiger for his capability of managing the cleanroom and D. Bouvet for an uncountable number of hours spent with me discussing the best technology solutions. Thanks to V. Ruhaut and A. Guillet for promptly assisting me with the Ritetrack and the AMS at anytime, and Claudia for her quick interventions outside the cleanroom. Thanks to all the CMi users, staff and ex-staff with whom I shared many technological issues and fun hours.

Thanks to A. Pezous for every time I scheduled and canceled the umpteenth hot phosphoric acid etching to be performed at CSEM, in Neuchatel.

In the south of France, the Ibs team helped me to get along with the challenge of Si-Bulk implantation.

Back to Switzerland, I would like to thank PSI and especially K. Bedner for the first RTAs. Even further... KTH in Sweden for other RTAs and in particular Prof. Östling and Prof. Hellström for the useful discussion on high-k dielectrics. ETHZ, and A. Stettler for the first bonding tests, G. Corradini at EPFL for many others.

Thanks to A. Mapelli for carefully dicing such small things and for not allowing me to give up in cleanroom when I really was going to.

Thanks to LPM and C. Jacq for the availability and allowing me to use their tools during the platform assembly.

#### Acknowledgements

Last stop at the University of Basel, where finally I could see my devices in action at the Nanoelectronics group. I would like to thank Prof. Schönenberger and Prof. M. Calame for allowing to me to collaborate so actively with their team. A big team, with whom I shared a lot of working (and not) hours: O. Knopfmacher, A. Tarasov, K. Bedner, R.L. Stoop and G. Navarra. A special thanks to M. Wipf for the experiments done together, for the long-term stability measurements and the endless phone conversations to explain me electrochemistry. Basel is also location of the BSSE department of ETHZ where I had the pleasure to work with P. Livi on circuit simulations, thanks also to Prof. Hierlemann who attentively corrected many pages of our Italian-English papers. Thank to P. Scarbolo for his great contribution to the oxide characterization and to make me discover Matlab (better late than never).

Thank to all of you for your cooperation who contributed so much in the realization of this work.

Thanks to Prof. L. Santorum, because he was the first one teaching me how much science is all around us and, most important, that not every question has an answer.

Thanks to Prof. V. Germano, because she taught me that if we stop smiling at children we stop smiling at our future.

Thanks to Prof. F. Pirri, Prof. M. Cocuzza and Prof. P. Allia for being such valuable resources of the (at the time) Physics Department of Politecnico of Turin and active promoters of the master in Micro and Nanotechnologies for Integrated Systems.

Thanks to my city, Turin, for hosting me so peacefully every time I was looking for comfort. Thanks to my mum Agnese for allowing me to be, sometimes, still a child and to my dad Pino to remind me to make fun of myself. Thanks to Mario, Marta and Daniele, simply, because you exist. Thanks to all my cousins and friends, Carola, Celeste, Diego, Andrea, Gianluca for the nice evenings full of laughs and their love, their children and parents, my grandma, you are all my friends. Thanks to Alice, Giada, Stefi, Simo, Ste, Raghu, Fazzo because no matter where we are and what we are going through, I know you'll always be there. Thanks to Alessandro for making me realize how many things seem, but they are not, impossible and giving me the love I have always dreamt of.

Lausanne, 10 Décembre 2013

Sara

# **Symbols and Abbreviations**

| Symbols or Abbreviation | Meaning                     |

|-------------------------|-----------------------------|

|                         |                             |

| a                       | Ion Activity                |

| A                       | Area                        |

| A/D                     | Analog to Digital           |

| $A_{pad}$               | Capacitance Area            |

| $A_{v}$                 | Voltage Gain                |

| AC                      | Alternating Current         |

| Al                      | Aluminum                    |

| ALD                     | Atomic Layer Deposition     |

| ANP                     | Acetic Nitric Phosphoric    |

| $Al_2O_3$               | Aluminum Oxide              |

| AlSi                    | Aluminum-Silicon            |

| BGA                     | Blood Gas Analyzer          |

| BHF                     | Buffered Hydrogen Fluoride  |

| $C_a$                   | Adsorption Capacitance      |

| $C_{acc}$               | Accumulation Capacitance    |

| $C_{dep}$               | Depletion Capacitance       |

| $C_{dif}$               | Diffuse Layer Capacitance   |

| $C_{DL}$                | Double Layer Capacitance    |

| $C_{g}$                 | Oxide Gate Capacitance      |

| $C_{inv}$               | Inversion Capacitance       |

| $C_{it}$                | Interface-State Capacitance |

| $C_{max}$               | Maximum Capacitance         |

| $C_{min}$               | Minimum Capacitance         |

| $C_{ox}$                | Oxide Capacitance           |

| $C_p$                   | Parasitic Capacitance       |

| $C_s$                   | Semiconductor Capacitance   |

| $C_{Si}$                | Silicon Capacitance         |

| $C_{Stern}$             | Stern Capacitance           |

| CD                      | Critical Dimension          |

| $CF_4$                  | Tetrafluoromethane          |

#### **Symbols and Abbreviations**

$C_4F_8$  Octafluorocyclobutane

$CH_3COOH$  Acetic Acid  $Cl_2$  Chlorine

CMOS Complementary Metal–Oxide–Semiconductor

CMP Chemical Mechanical Polishing

*CP* Costant Power

CSA Common Source Amplifier

$D_{etching}$  Si Etching Depth  $D_{imp}$  Implantation Depth  $d_{NW}$  Distance Between Fins

DC Direct Current

DELTA Depleted Lean-Channel Transistor

DG Double Gate

DI Deionized

DRIE Deep Reactive Ion Etching

$E_G$  Energy Band Gap

$E_{ref}$  Reference Electrode Potential  $E_S$  Surface Transverse Electric Field

E1 Critical Electric Field, Phonon Scattering

E2 Critical Electric Field, Surface Scattering

EBL Electron Beam Lithography

EDA Electronic Design Automation

ELISA Enzyme-Linked ImmunoSorbent Assay EOS Electrolyte-Oxide-Semiconductor

EOT Equivalent Oxide Thickness FEA Finite Element Analysis FET Field Effect Transistor FIB Focused Ion Beam

FinFET Fin Field Effect Transistor

G Gibbs Energy

$g_{ds}$  Output Conductance  $g_m$  Trasconductance GAA Gate-All-Around GAO Gastric Acid Output

GPIB General Purpose Interface Bus

H Hydrogen

$h_D$  Driving Transistor Height

$h_S$  Sensor Height  $h_{Si}$  Si Body Height  $H_{Fin}$  Fin Heigth  $H_{Ribbon}$  Ribbon Heigth HCl Hydrogen chloride

$HClO_4$  Perchloric Acid HF Hydrogen Fluoride  $HfO_2$  Hafnium Oxide  $HNO_3$  Nitric Acid  $H_2O$  Water

$H_2O_2$  Hydrogen Peroxide  $H_3PO_4$  Phosphoric Acid HIR High Resolution  $H_2SO_4$  Sulfuric Acid

HSQ Hydrogen Silsesquioxane

*I*<sub>b</sub> Bond Ionicity

$I_{bs}$  Bulk to Source Current  $I_c$  Compliance Current

$I_d$  Drain Current

$I_{d_0}$  Initial Drain Current

$I_g$  Gate Current  $I_{th}$  Threshold Current IC Integrated Circuit

ISFET Ion Sensitive Field Effect Transistor

k Boltzmann Constant

$K_a$  Acid Dissociation Constant  $K_b$  Base Dissociation Constant

L Length

$egin{array}{ll} I_B & & & ext{Bjerrum Length} \\ L_{Fin} & & ext{Fin Length} \\ \end{array}$

$L_{imp}$  Implantation Lateral Extension

$L_{Ribbon}$  Ribbon Length  $l_{Si}$  Si Body Length  $La_2O_3$  Lanthanum Oxide

LPCVD Low Pressure Chemical Vapour Deposition

*LR* Low Resolution

LTO Low Temperature Oxide

*MG – FET* Multi Gate FET

MOCVD Metal Organic Chemical Vapor Deposition

MOSCAP Metal-Oxide-Silicon Capacitor

MOSFET Metal-Oxide-Silicon Field Effect Transistor

$n_A$  Acceptor Dopant Dose

$N_S$  Surface Site Density

$N_2$  Nitrogen

#### **Symbols and Abbreviations**

*NH*<sub>4</sub>*OH* Ammonium Hydroxide

OH HydroxideP Power

$P_{dep}$  Depletion Load Power  $P_{enh}$  Enhancement Load Power

$P_{Fin}$  Fin Power

PCBPrinted Circuit BoardPDAPost Deposition AnnealingPDMSPolydimethylsiloxane

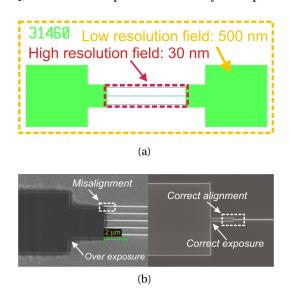

PEC Proximity Effect Correction

PGMEA Propylene Glycol Monomethyl Ether Acetate

PMA Post Metallization Annealing

$POCl_3$ Phosphoryl ChloridePSAProstate Specific AntigenPTFEPolytetrafluorethylenpzcPoint of Zero ChargeqElementary Charge $Q_{ox}$ Oxidation Quality Factor

$Q_D$  Depletion Charge  $R_L$  Load Resistor

$R_{ds}$  Source and Drain Resistance

*R<sub>out</sub>* Output Resistance

RCA Radio Corporation of America

RIE Reactive Ion etching RTA Rapid Thermal Annealing

S Sensitivity

S/V Surface to Volume Ratio  $S_{out}$  Readout Sensitivity SE Standard Error

SEM Scanning Electron Microscopy

Si Silicon

$SF_6$  Sulfur Hexafluoride  $Si_3N_4$  Silicon Nitride SiNW Silicon Nanowire  $SiO_2$  Silicon Oxide  $SiO_x$  IL Oxide

SOI Silicon-On-Insulator

SPICE Simulation Program with Integrated Circuit Emphasis

SS Subthreshold Slope

*T* Temperature

$t_{bot}$  Bottom Fin Thicness

$T_{Fin}$  Fin Thickness

$t_{HfO_2}$  Hafnium Oxide Thickness  $t_{IL}$  Interfacial Layer Thickness

$t_{ins}$  Insulator Thickness  $t_{ox}$  Oxide Thickness

$T_{ox}$  Oxidation Temperature

t<sub>shell</sub> Thickness of N-doped Triangular Shell

$t_{Si}$  Si Body Thickness  $t_{SiO_2}$  Silicon Oxide Thickness  $t_{SiO_x}$  IL Oxide Thickness  $t_{spacer}$  Sil $_3N_4$  Spacer Thickness  $T_{Ribbon}$  Ribbon Thickness  $t_{top}$  Top Fin Thickness  $t_{a_2O_5}$  Tantalium Oxide

TCADTechnology Computer Aided DesignTEMTransmission Electron MicroscopyTEMAHTetrakis-Ethyl-Methyl-Amino-Hafnium

*Ti* Titanium

$time_{ox}$  Si Oxidation Time  $TiO_2$  Titanium Oxide UV Ultraviolet

$egin{array}{lll} V_b & & {

m Back-gate\ Voltage} \ V_{BD} & & {

m Breakdown\ Voltage} \ V_{DD} & & {

m Supply\ Voltage} \ V_d & & {

m Drain\ Voltage} \ \end{array}$

$egin{array}{lll} V_{ds} & & ext{Source to Drain Voltage} \ V_{FB} & & ext{Flat Band Voltage} \ V_g & & ext{Gate Voltage} \ \end{array}$

$V_H$  Hysteresis Amplitude

$V_{IH}$  Minimum Input High Voltage  $V_{IL}$  Maximum Input Low Voltage

$V_{in}$ Input Voltage Liquid Voltage  $V_{liq}$  $V_{off}$ Inverter OFF Voltage  $V_{on}$ Inverter ON Voltage **Output Voltage**  $V_{out}$ Reference Voltage  $V_{ref}$  $V_{\mathcal{S}}$ Source Voltage Threshold Voltage  $V_{th}$

W Width

$W_{Ribbon}$  Ribbon Width  $x_{den}$  Depletion Width

*x*<sub>dmax</sub> Maximum Depletion Width

#### **Symbols and Abbreviations**

$egin{array}{ll} z_i & & ext{Ion Valence} \\ ZrO_2 & & ext{Zirconium Oxide} \end{array}$

# **Greek Letters**

| Greek Letters       | Meaning                           |

|---------------------|-----------------------------------|

|                     |                                   |

| $\alpha$            | Sensitivity Parameter             |

| $oldsymbol{eta}$    | Surface Buffer Capacitance        |

| $eta_e$             | Substrate Correction for EBL      |

| $arepsilon_0$       | Vacuum Permittivity               |

| $arepsilon_{HfO_2}$ | Silicon Oxide Dielectric Constant |

| $\varepsilon_{ins}$ | Insulator Dielectric Constant     |

| $\varepsilon_{ox}$  | Oxide Dielectric Constant         |

| $arepsilon_{Si}$    | Silicon Dielectric Constant       |

| $arepsilon_{SiO_2}$ | Silicon Oxide Dielectric Constant |

| $arepsilon_{SiO_x}$ | IL Oxide Dielectric Constant      |

| $\eta_{\it e}$      | Density Correction for EBL        |

| $\lambda_D$         | Debye Length                      |

| $\mu_n$             | Electron Mobility                 |

| $\mu_0$             | Maximum Mobility                  |

| $\mu_S$             | Surface Mobility                  |

| $ ho_i$             | Ion Density                       |

| $\sigma$            | Standard Deviation                |

| $\chi_{sol}$        | Surface Dipole Potential          |

| Ψ                   | Oxide-Electrolyte Potential       |

| $\Phi_M$            | Metal Work Function               |

| $\Phi_{Si}$         | Silicon Work Function             |

| $\phi_S$            | Surface Potential                 |

| $\phi_f$            | Fermi Potential                   |

# **Contents**

| Al | ostra  | ct      |                                                                          | 1            |

|----|--------|---------|--------------------------------------------------------------------------|--------------|

| Ri | iassu  | nto     |                                                                          | vi           |

| Ac | cknov  | wledge  | ments                                                                    | į            |

| Sy | mbo    | ls and  | Abbreviations                                                            | xi           |

| Gı | reek 1 | Letters |                                                                          | <b>xvi</b> i |

| Co | onter  | ıts     |                                                                          | XX           |

| Li | st of  | figures |                                                                          | XXI          |

| Li | st of  | tables  | x                                                                        | xvi          |

| 1  | Intr   | oducti  | on: Narrowing the Gap between Nanoelectronics and Electronics for Sens   | ;-           |

|    | ing    |         |                                                                          | 1            |

|    | 1.1    | Fin Fi  | eld Effect Transistor in nanoelectronics                                 | 1            |

|    |        | 1.1.1   | Full depletion in silicon thin-films                                     | 2            |

|    |        | 1.1.2   | Subthreshold slope for thin-film FETs                                    | 5            |

|    | 1.2    | Ion Se  | ensitive Field Effect Transistor                                         | 6            |

|    |        | 1.2.1   | The Nernst limit in pH sensing applications                              | 8            |

|    |        | 1.2.2   | Fundamental models of the EOS interface                                  | g            |

|    | 1.3    | A con   | nmon parameter for the limit of FET devices in pH sensing applications . | 11           |

|    | 1.4    | High-   | k dielectrics                                                            | 12           |

|    |        | 1.4.1   | Advantages of high-k oxides in electronics                               | 12           |

|    |        | 1.4.2   | Advantages of high-k oxides in pH sensing applications                   | 14           |

|    | 1.5    | Motiv   | rations for using FETs in sensing applications                           | 16           |

|    |        | 1.5.1   | State-of-the-art of SiNWs for sensing applications                       | 18           |

|    | Bibl   | liograp | hy                                                                       | 20           |

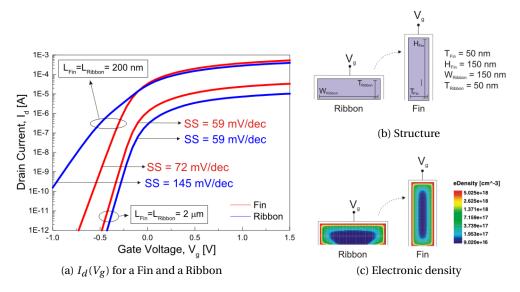

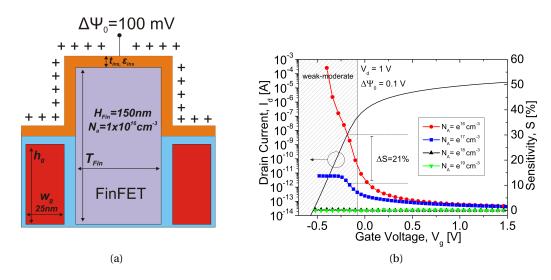

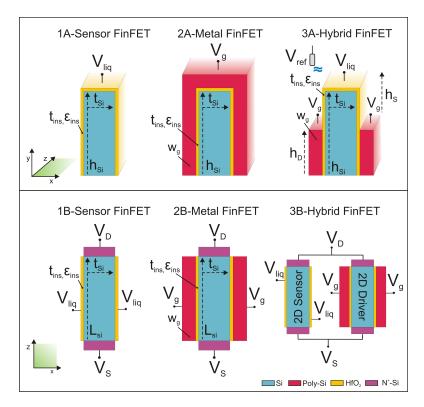

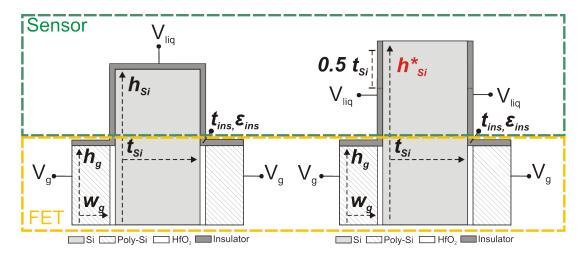

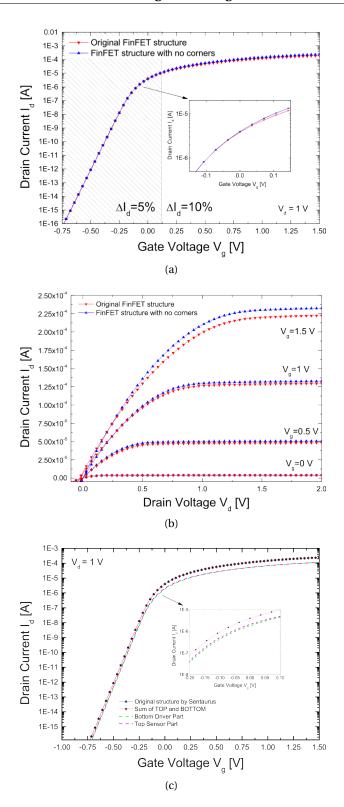

| 2  | TCA    |         | ulations for the Design and Integration of FinFETs                       | 27           |

|    | 2.1    | FinFE   | T design considerations by FEA TCAD simulations                          | 27           |

|    |        | 2.1.1   | Scalability of FinFETs versus Nanoribbons                                | 27           |

|    |        | 2.1.2   | Hybrid partially gated FinFET                                            | 29           |

#### **Contents**

|   | 2.2  | Low power sensing circuits by EDA simulations                                                         |

|---|------|-------------------------------------------------------------------------------------------------------|

|   |      | 2.2.1 From 3D FEA to 2D device analytical models                                                      |

|   |      | 2.2.2 A sensing common source amplifier                                                               |

|   |      | 2.2.3 A sensing NOR gate                                                                              |

|   |      | 2.2.4 A sensing ring oscillator and pseudo-differential amplifier 42                                  |

|   | 2.3  | Doping strategies for triangular nanowires                                                            |

|   | 2.4  | Summary                                                                                               |

|   | Bibl | liography                                                                                             |

| 3 | Tec  | hnological Development of FinFETs for Sensing Applications 51                                         |

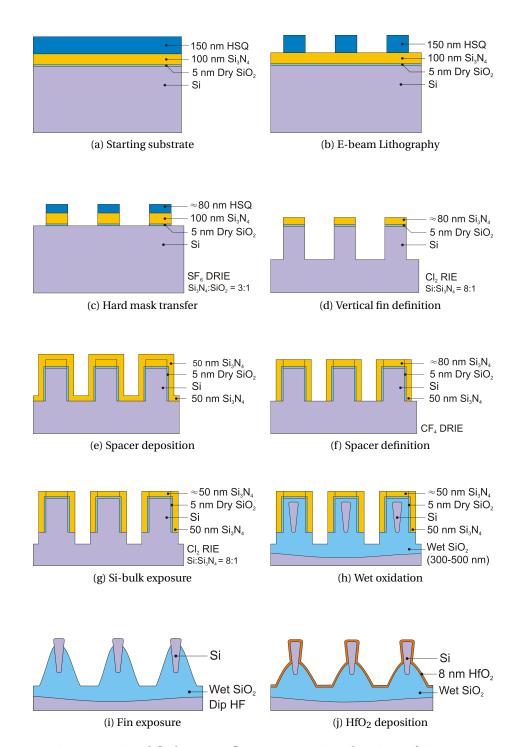

|   | 3.1  | Overview of the process flow                                                                          |

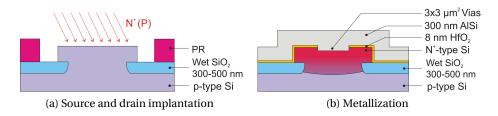

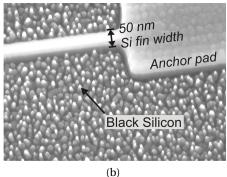

|   | 3.2  | E-beam lithography for sub-20 nm resolution                                                           |

|   | 3.3  | Wet and dry etching optimization                                                                      |

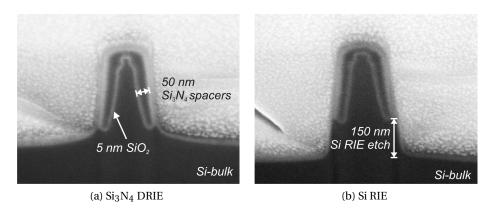

|   |      | 3.3.1 Si <sub>3</sub> N <sub>4</sub> etching based on SF <sub>6</sub> for T <sub>Fin</sub> definition |

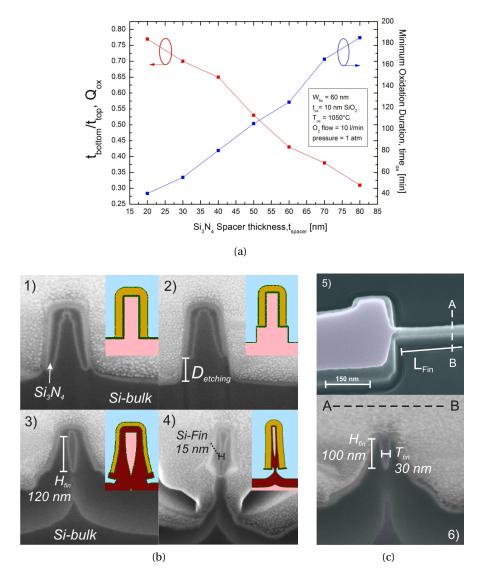

|   |      | 3.3.2 Vertical Si etching based on $Cl_2$ for $H_{Fin}$ definition                                    |

|   |      | 3.3.3 $Si_3N_4$ etching based on $C_4F_8$ for spacer creation                                         |

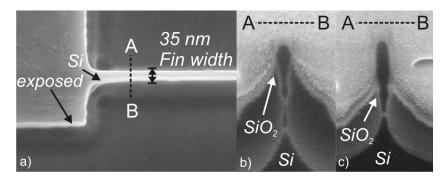

|   |      | 3.3.4 Fin surface exposure by dip HF                                                                  |

|   |      | 3.3.5 Vias etching by Ar ion milling                                                                  |

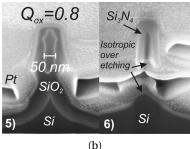

|   | 3.4  | Oxidation of Si-bulk aided by FEA simulations 60                                                      |

|   |      | 3.4.1 Results and comparison with fabrication 60                                                      |

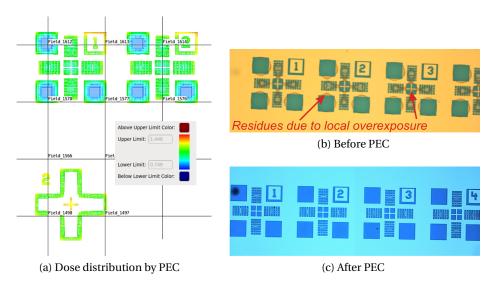

|   | 3.5  | Source and drain implantation                                                                         |

|   |      | 3.5.1 Photoresist removal after ion impact                                                            |

|   | 3.6  | Photolithography techniques                                                                           |

|   |      | 3.6.1 Lift-off for device contacts 67                                                                 |

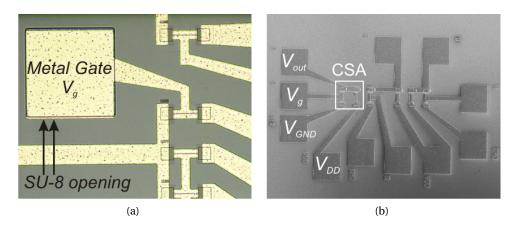

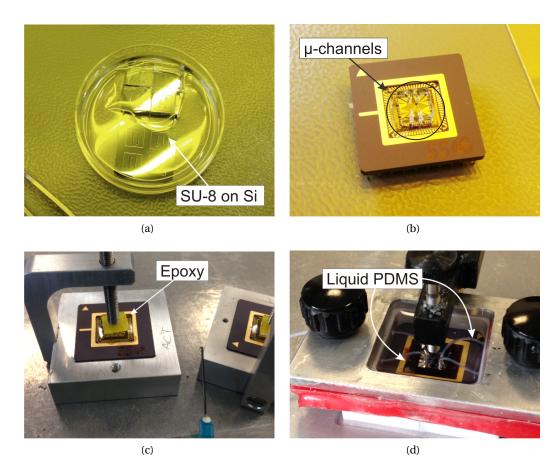

|   |      | 3.6.2 SU-8 microfluidic channels                                                                      |

|   | 3.7  | Wafer layout                                                                                          |

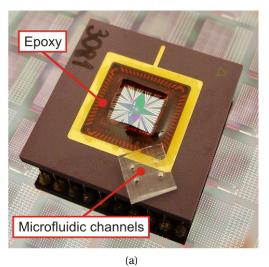

|   | 3.8  | Chip-carrier assembly                                                                                 |

|   | 3.9  | Summary                                                                                               |

|   | Bibl | liography                                                                                             |

| 4 | Cha  | aracterization of ALD HfO <sub>2</sub> thin layers 75                                                 |

|   | 4.1  | Description of the MOSCAP                                                                             |

|   | 4.2  | Fabrication process of MOSCAPs                                                                        |

|   |      | 4.2.1 Insulated Si trenches and Poly-Si gate                                                          |

|   |      | 4.2.2 A low temperature process with Al-gate 80                                                       |

|   |      | 4.2.3 Atomic layer deposition of $HfO_2$                                                              |

|   |      | 4.2.4 Layout and fabricated devices                                                                   |

|   | 4.3  | Measurement set-up and parameters                                                                     |

|   | 4.4  | Characterization of MOSCAPs based on HfO <sub>2</sub>                                                 |

|   |      | 4.4.1 Comparison of HfO <sub>2</sub> estimation methods 85                                            |

|   |      | 4.4.2 Charge nature of the $HfO_2$ hysteresis                                                         |

|   |      | 4.4.3 Impact of annealing treatments 89                                                               |

|   |      | 4.4.4 Impact of RCA cleaning procedures                                                               |

| Lis | st of  | t of Publications                                                              |     |  |  |

|-----|--------|--------------------------------------------------------------------------------|-----|--|--|

| Cı  | ırricı | rriculum Vitae 153                                                             |     |  |  |

| В   | Pro    | cess simulation code for local SOI oxidation                                   | 151 |  |  |

| A   | The    | e center of microNanoTechnology (CMi)                                          | 149 |  |  |

|     | Bibl   | liography                                                                      | 146 |  |  |

|     |        | Concluding remarks                                                             |     |  |  |

|     | C 4    | 6.3.2 Potential diagnostics applications                                       |     |  |  |

|     |        | 6.3.1 Technology                                                               |     |  |  |

|     | 6.3    | Outlook                                                                        |     |  |  |

|     |        | element                                                                        |     |  |  |

|     | 6.2    | Critical discussion of the main advantages of the FinFET on Si-bulk as sensing |     |  |  |

|     | 6.1    | Main achievements                                                              | 139 |  |  |

| 6   |        | nclusions and Outlook                                                          | 139 |  |  |

|     |        |                                                                                |     |  |  |

|     |        | liography                                                                      |     |  |  |

|     | 5.7    | Summary                                                                        |     |  |  |

|     | 5.6    | Comparison with other works                                                    |     |  |  |

|     | 5.5    | FinFET long-term stability                                                     |     |  |  |

|     | 5.4    | Preliminary biosensing application: FimH detection                             |     |  |  |

|     |        | 5.3.4 Sensing common source amplifier                                          |     |  |  |

|     |        | 5.3.3 pH measurements at different biasing point                               |     |  |  |

|     |        | 5.3.2 Fully pH-responsive FinFETs                                              |     |  |  |

|     | J.J    | 5.3.1 Single liquid gate FinFETs                                               |     |  |  |

|     | 5.3    | pH sensing measurements                                                        |     |  |  |

|     |        | 5.2.2 Definition of the experimental outputs                                   |     |  |  |

|     | 5.2    | Measurements in a liquid environment                                           |     |  |  |

|     | E 2    | 5.1.2 Two-component common source amplifiers                                   |     |  |  |

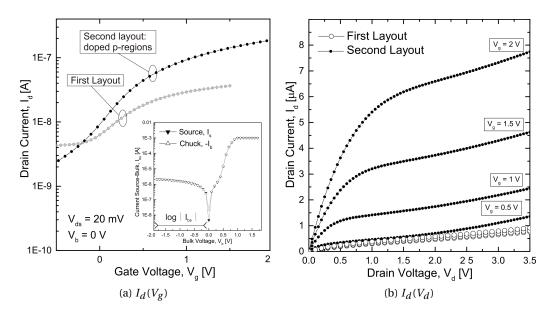

|     |        | 5.1.1 Single metal gate FinFETs                                                |     |  |  |

|     | 5.1    | Electrical characterization of metal gate FinFETs                              |     |  |  |

| 5   | -      | perimental Results: Metal and Liquid Gate FinFETs                              | 105 |  |  |

|     | Bibi   | liography                                                                      | 102 |  |  |

|     | 4.6    | Summary                                                                        |     |  |  |

|     |        | 4.5.1 Hysteresis-free MOSCAPs                                                  |     |  |  |

|     | 4.5    | MOSCAPs based on SiO <sub>2</sub> /HfO <sub>2</sub> stack                      |     |  |  |

|     |        | 4.4.5 Impact of the metal gate photolithography                                |     |  |  |

|     |        |                                                                                |     |  |  |

# **List of Figures**

| 1.1  | DELTA and FinFET devices                                          |

|------|-------------------------------------------------------------------|

| 1.2  | Distinction between bulk, thick- and thin-film                    |

| 1.3  | MOSFET and $I_d(V_g)$                                             |

| 1.4  | ISFET and $I_d(V_{ref})$                                          |

| 1.5  | Fundamental EOS models                                            |

| 1.6  | Site-dissociation model                                           |

| 2.1  | Scalability of FinFET versus Ribbon FET                           |

| 2.2  | $I_d(V_g)$ of a partially gated FinFET                            |

| 2.3  | FEA simulations of a partially gated FinFET 31                    |

| 2.4  | Single circuit components                                         |

| 2.5  | Top corner approximation                                          |

| 2.6  | Simulations of single devices for 2D modelling                    |

| 2.7  | Comparison between 3D FEA and 2D SPICE simulations                |

| 2.8  | Sensing common source amplifier realized with a resistor          |

| 2.9  | Sensing common source amplifiers based on two n-MOS components 41 |

| 2.10 | Sensing ring oscillator                                           |

| 2.11 | Sensing differential amplifier                                    |

| 2.12 | Triangular SiNWs                                                  |

| 2.13 | Sensitivity of triangular SiNWs                                   |

| 2.14 | Electron density of triangular SiNWs                              |

| 3.1  | Simplified process flow for the fabrication of FinFETs            |

| 3.2  | Simplified process flow for contact formation                     |

| 3.3  | EBL resolution fields                                             |

| 3.4  | PEC result on alignment marks                                     |

| 3.5  | Si fins etched by RIE                                             |

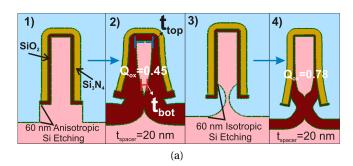

| 3.6  | $Si_3N_4$ spacers formation by DRIE                               |

| 3.7  | Fin exposure by dip HF                                            |

| 3.8  | Vias etching by Ar Ion Milling                                    |

| 3.9  | FEA simulations for wet oxidation                                 |

| 3.10 | Wet oxidation at different process steps                          |

| 3.11 | Layout strategies                                                 |

#### **List of Figures**

| 3.12 | FEA simulations for ion implantation                                             | 64  |

|------|----------------------------------------------------------------------------------|-----|

| 3.13 | Photoresist removal after ion implantation                                       | 66  |

| 3.14 | Chromium mask tests                                                              | 67  |

|      | Lift-off process                                                                 | 68  |

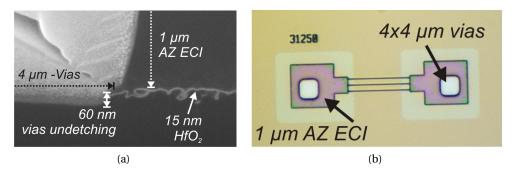

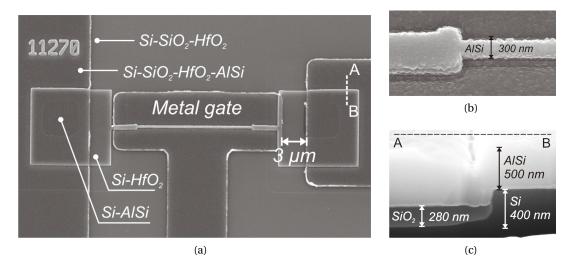

| 3.16 | Final fabricated FinFETs                                                         | 70  |

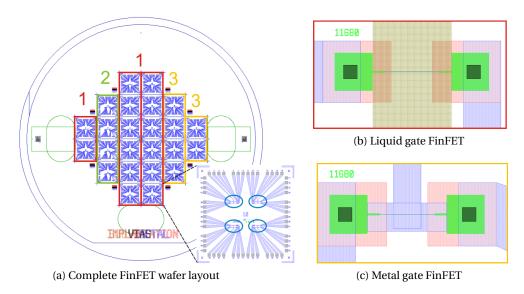

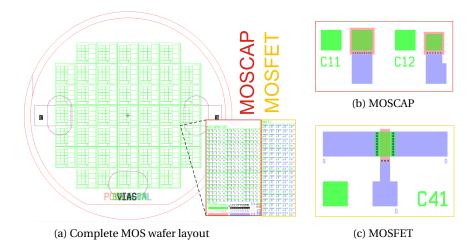

| 3.17 | Wafer layout and available devices                                               | 71  |

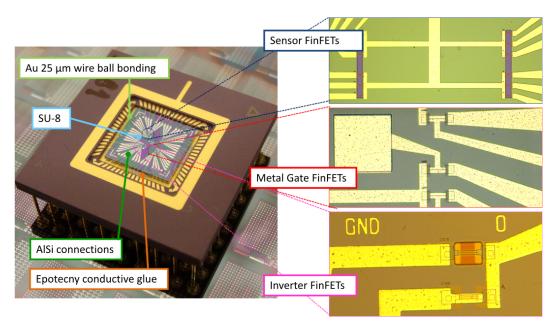

| 3.18 | Chip carrier assembly                                                            | 72  |

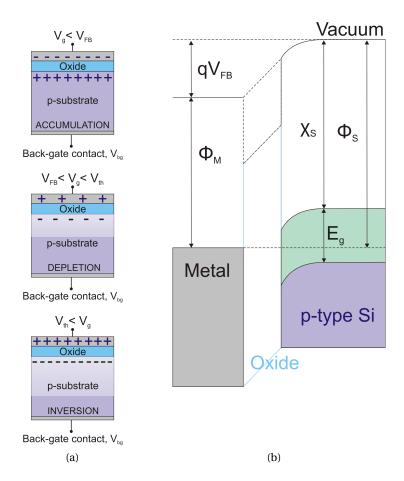

| 4.1  | The MOSCAP structure and its band diagram                                        | 76  |

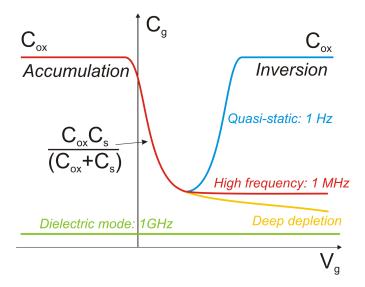

| 4.2  | C-V curves of the MOSCAP as a function of frequency                              | 78  |

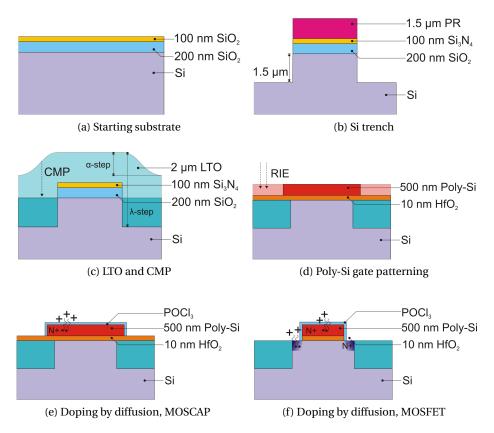

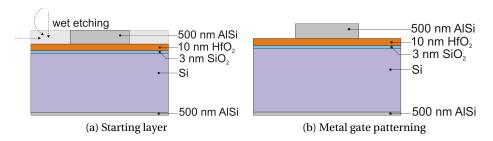

| 4.3  | Simplified process flow of MOSCAPs with Poly-Si gate                             | 80  |

| 4.4  | C-V curves of MOSCAP with Poly-Si gate                                           | 81  |

| 4.5  | Simplified process flow of MOSCAP with Al gate                                   | 81  |

| 4.6  | Wafer layout and available devices                                               | 83  |

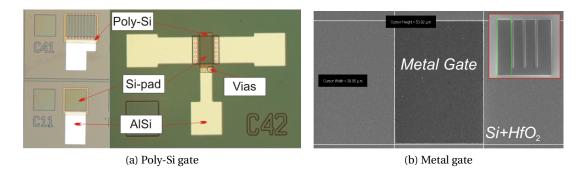

| 4.7  | Fabricated MOS devices                                                           | 83  |

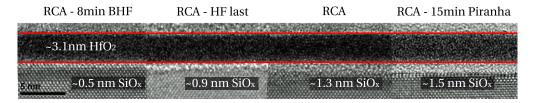

| 4.8  | Interfacial layer after RCA cleaning                                             | 86  |

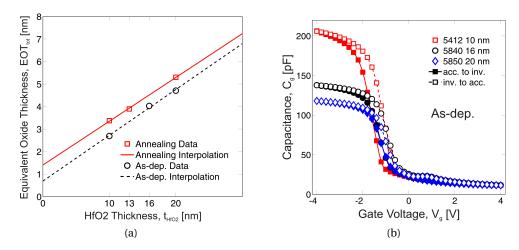

| 4.9  | Estimation of the dielectric constant by linear increase of $t_{HfO_2}$          | 88  |

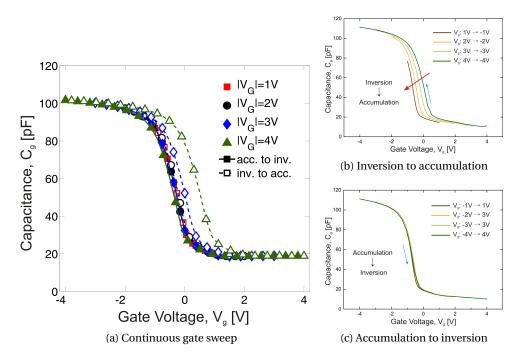

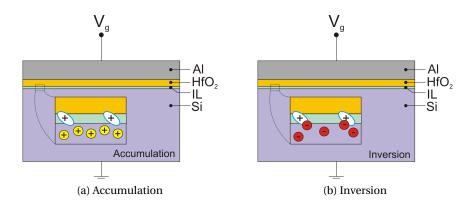

|      | C-V repeated measurements for different sweep range                              | 89  |

| 4.11 | MOS charge trapping mechanism                                                    | 90  |

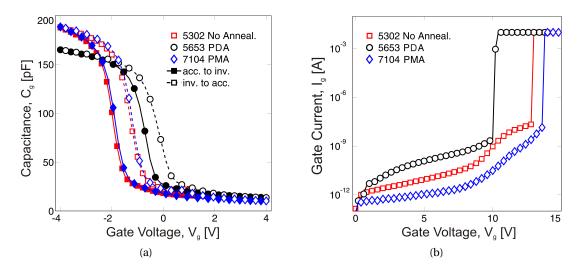

|      | Impact of annealing on the electrical properties of HfO <sub>2</sub> MOSCAPs     | 91  |

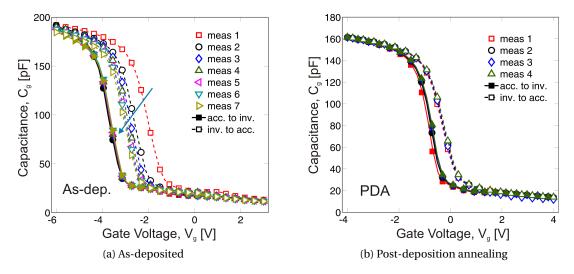

|      | Impact of annealing on C-V repeated measurements                                 | 92  |

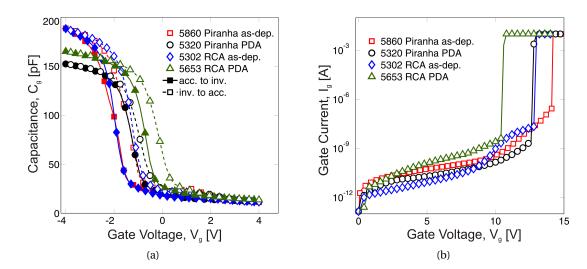

|      | Effect of Piranha cleaning on MOSCAP                                             | 93  |

|      | Effect of HF-last and Piranha cleaning on HfO $_2$ MOSCAP $\ldots \ldots \ldots$ | 94  |

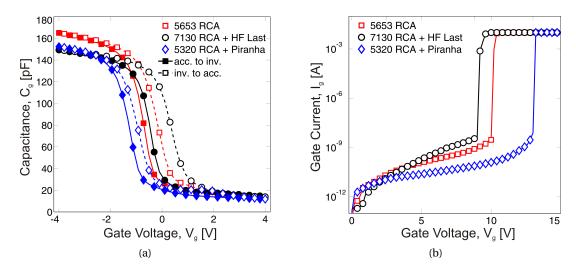

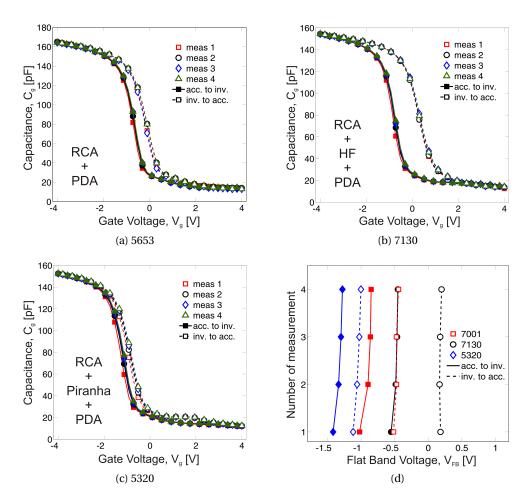

|      | Repeated measurements for different RCA cleaning procedures                      | 95  |

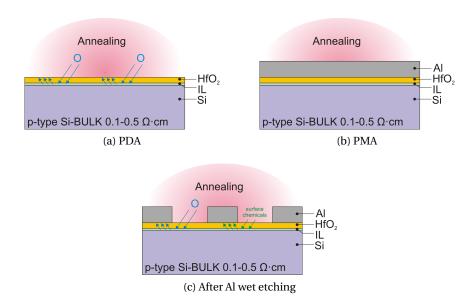

|      | Different annealing scenarios                                                    | 96  |

|      | Effect of annealing after Al wet etching                                         | 97  |

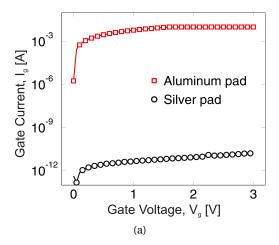

|      | C-V and I-V measurements for the $SiO_2/HfO_2$ stack                             | 98  |

| 4.20 | C-V repeated measurements for $SiO_2/HfO_2$ stack                                | 99  |

| 5.1  | Metal gate FinFETs: devices                                                      | 106 |

| 5.2  | Metal gate FinFETs: measurements with non-optimized layout                       |     |

| 5.3  | Electrical characterization of optimized metal gate FinFETs                      | 108 |

| 5.4  | Output characteristics of metal gate amplifiers                                  | 110 |

| 5.5  | Comparison of simulations versus experiments for the metal gate CSA              | 111 |

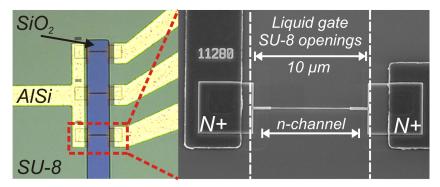

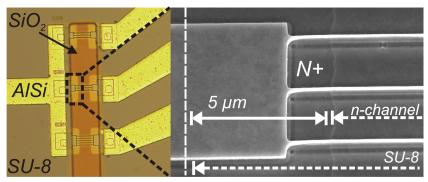

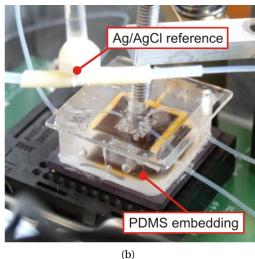

| 5.6  | Assembly of the microfluidic platform                                            | 113 |

| 5.7  | Microfluidic platform                                                            | 114 |

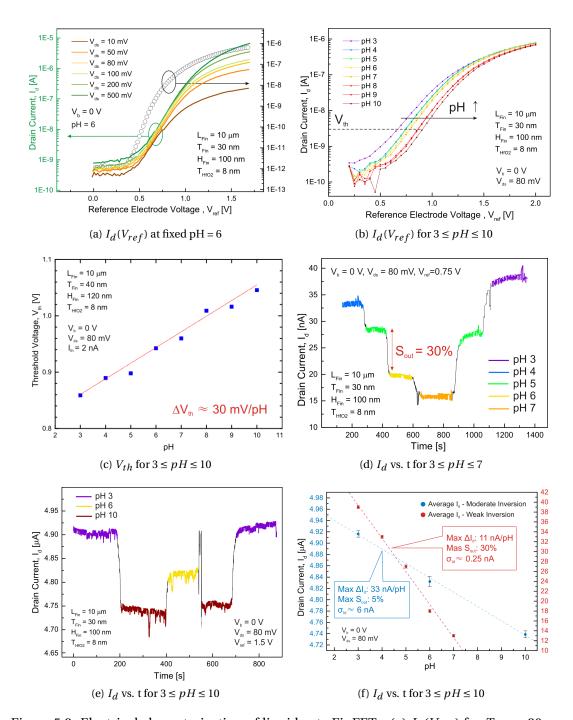

| 5.8  | Characterization of liquid gate FinFETs: preliminary measurements                | 117 |

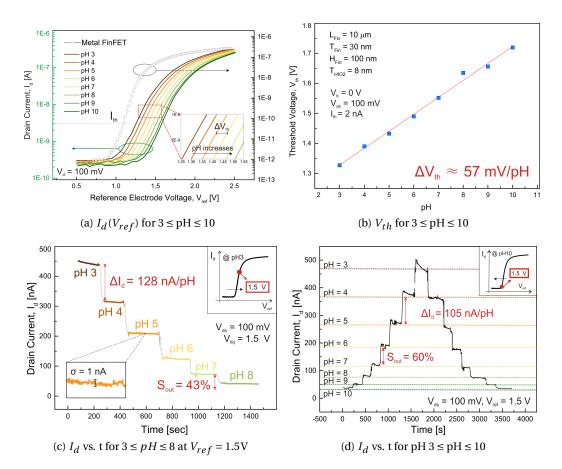

| 5.9  | Electrical characterization of liquid gate FinFETs: full pH response             | 120 |

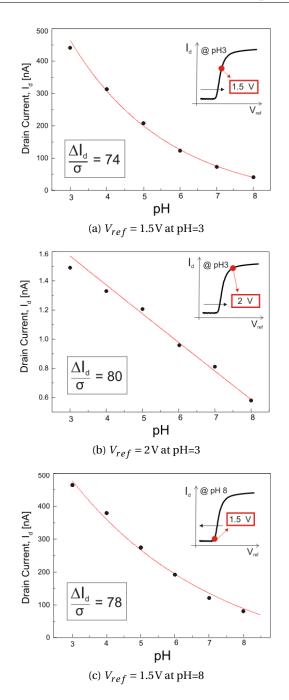

| 5.10 | FinFET response according to different $V_{ref}$ bias                            | 121 |

| 5.11 | Common source amplifier: device                                                  | 124 |

|      | Sensing common source amplifier: measurements                                    | 126 |

|      | FimH protein detection                                                           | 128 |

| 5.14 | FinFET long-term stability                                                       | 130 |

| List of Figures |  |

|-----------------|--|

|                 |  |

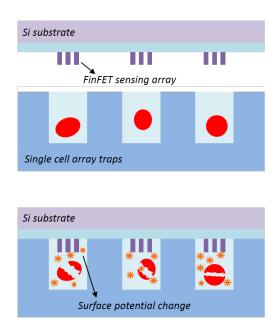

| 6.1 | Single-cell analysis  | 144 |

|-----|-----------------------|-----|

| A.1 | CMi cleanroom complex | 149 |

# **List of Tables**

| 1.1 | High-k dielectrics                                                           | 13  |

|-----|------------------------------------------------------------------------------|-----|

| 1.2 | Sensing properties of high-k dielectrics                                     | 16  |

| 1.3 | State-of-the-art of SiNWs for sensing applications                           | 19  |

| 2.1 | FinFET parameters implemented in analytical models                           | 34  |

| 3.1 | Optimized parameters for wet oxidation                                       | 61  |

| 4.1 | ALD temperature parameters for HfO <sub>2</sub>                              | 82  |

| 4.2 | C-V meter set-up parameters                                                  | 84  |

| 4.3 | Effect of annealing on the electrical properties of HfO <sub>2</sub> MOSCAPs | 90  |

| 4.4 | Electrical properties of $HfO_2$ MOSCAPs for different RCA procedures        | 93  |

| 4.5 | Electrical properties of SiO <sub>2</sub> /HfO <sub>2</sub> MOSCAPs          | 98  |

| 5.1 | Electrical features of metal gate FinFETs                                    | 109 |

| 5.2 | FinFET pH sensor: readout sensitivity                                        | 122 |

| 5.3 | FinFET pH sensor: current variation                                          | 122 |

| 5.4 | FinFET pH sensor: signal-to-noise ratio                                      | 122 |

| 5.5 | FinFET pH sensing CSA: gain                                                  | 127 |

| 5.6 | Comparison of FinFET sensitivity, stability and accuracy with other works    | 13  |

| 5.7 | Comparison of FinFET voltage supplies with other works                       | 132 |

| 5.8 | Comparison of FinFET readout amplification with other works                  | 133 |

# I Introduction: Narrowing the Gap between Nanoelectronics and Electronics for Sensing

Field Effect Transistors (FET) based on Silicon Nanowires (SiNW) are emerging as ultrasensitive sensors for direct and label-free detection of chemical and biological species. Providing a quick response, durability, reliability and reproducibility of the fabrication process, they have become promising candidates competing with their mechanical and optical counterparts. Their potential has been widely demonstrated, but large-scale production and circuit integration are still challenging. The aim of this thesis is to create a more solid bridge between state-of-the-art nanoelectronics and the sensing field based on FET devices, looking forward to a definitive integration of sensing units in everyday electronic technology at the service of personal healthcare.

In this section, the main properties of a well-defined electronic device, namely the *n-channel fully depleted FinFET*, are introduced. Such architecture is recognized to be one of the best performing nanoelectronic device, thanks to the excellent electrostatic control provided by the multi-gate structure. The working principle of the ISFET is then presented together with a discussion on how the optimal performance of the FinFET could be an asset for the sensing field. The state-of-the-art related to SiNW sensing applications follows, focusing on the technology used to realize the SiNWs and their applications. The last sections describe the role of high-k dielectrics in CMOS scaling and in pH sensing applications, which are the main targets of this work.

#### 1.1 Fin Field Effect Transistor in nanoelectronics

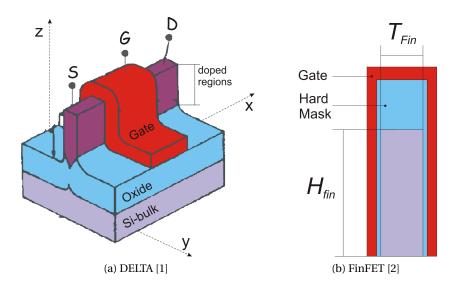

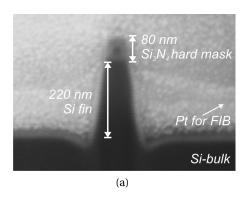

The first fabricated non-planar FET was proposed in 1989 as "fully DEpleted Lean-channel TrAnsistor (DELTA)" by Hisamoto et *al.* [1], as illustrated in Fig. 1.1a. The term Fin Field Effect Transistor (FinFET) was actually referring to the same DELTA structure but with an additional top hard-mask [2] used to avoid parasitic inversion at the corners, as shown in

# Chapter 1. Introduction: Narrowing the Gap between Nanoelectronics and Electronics for Sensing

Fig.1.1b. Commonly today and herein, the term FinFET is used also for the DELTA, that is technically the one implemented in this work. The DELTA and the FinFET are part of a group of transistors which can generally be referred to as multi-gate FETs (MG-FET) including double-gate (DG), triple and surrounding gate transistors [3]. These architectures have been developed to overcome the adverse effects that come along with CMOS scaling according to Moore's law [4] towards higher switching speeds and more densely integrated circuits. Some of the non-ideal effects have been identified as: (i) short-channel effects including voltage roll-off, (ii) drain-induced barrier lowering (DIBL), (iii) subthreshold slope degradation and (iv) non-negligible parasitic components [5]. Using a multi-gate architecture, a better control of the channel depletion is obtained with respect to a standard MOSFET and, most important, the influence of the drain electric field on the channel is reduced [6]. In the presented work, the

Figure 1.1: (a) Illustration of the DELTA [1] and (b) cross-section of a FinFET [2], as they were originally proposed.

FinFET length  $L_{Fin} = 10 \, \mu \text{m}$  is not directly subjected to the side effects of scaling but looking towards CMOS integration, the scaling compatibility is an indispensable feature. Moreover, the advanced channel control provided by the FinFET architecture will result in excellent sensor properties, as it will be shown in Chap. 5.

#### 1.1.1 Full depletion in silicon thin-films

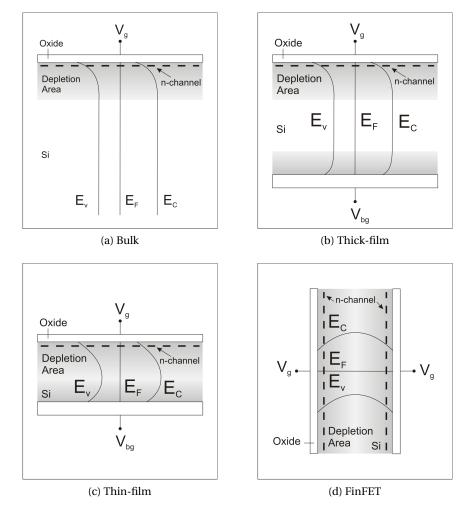

To better understand the advantages of the FinFET, it is worth to introduce the concept of full depletion of thin-films [5]. Figure 1.2 illustrates the band diagram of four different possible devices defined by the thickness of the silicon layer and the gate bias. It is important to notice that for a vertical thin-film, its dimension along the Y-axis (Fig. 1.1a) is, here, called "thickness" ( $T_{Fin}$ ) and the one along the Z-axis is called "height" ( $H_{Fin}$ ), avoiding the use of "width", commonly used in electronics for the dimension lying in a perpendicular plane with respect to the conduction direction. For an horizontal thin-film, the standard definition of width

and silicon thickness applies. In this way, the term "thickness" always refers to the thinnest dimension which determines the condition of fully depletion. In Fig. 1.2 the following devices have been considered:

- Bulk MOSFET

- Thick-film on SOI

- Horizontal thin-film on SOI

- · Vertical thin-film on SOI

The SOI condition is assumed to be valid also for Si-bulk where a local insulation has been performed, as it has been done in the FinFET fabrication process presented in Chap. 3. The only difference may rise at the junction level that, in the case of SOI, they are completely separated from the bulk, while for the local SOI are still connected.

For a standard bulk device (Fig. 1.2a), the depletion zone (the region where the charge carriers

Figure 1.2: Distinction between bulk, thick- and thin-film: band diagram with depletion regions in a bulk (a), a thick-film (b), a thin-film with back-gate (c) and a FinFET (d).

# Chapter 1. Introduction: Narrowing the Gap between Nanoelectronics and Electronics for Sensing

have been repulsed away from the gate electric field) extends from the Si-Oxide interface to a maximum depletion width given by:

$$x_{dmax} = \sqrt{\frac{4\varepsilon_{Si}\phi_F}{qN_A}} \tag{1.1}$$

where  $\varepsilon_{Si}$  is the silicon dielectric constant,  $\phi_F$  is the Fermi potential,  $N_A$  the channel doping and q the elementary charge. The Fermi potential  $\phi_F$  for p-type silicon is given by:

$$\phi_F = \frac{kT}{q} \ln \left( \frac{N_A}{n_i} \right) \tag{1.2}$$

where k is the Boltzmann constant, T the temperature and  $n_i$  the intrinsic carrier concentration of silicon. The potential outside the depletion regions becomes linear in the bulk, known as body, characterized by a neutral space charge distribution.

For a *thick film*, the back-gate is biased to create another depleted (or accumulated) region. The silicon thickness becomes comparable to  $x_{dmax}$ , but the depleted regions are still divided by a portion of neutral silicon (Fig. 1.2b). Such a condition is defined **partial depletion** (PD). When the two depleted regions start to interact, i.e.  $x_{dmax}$  has become larger than the silicon film, the condition of **full depletion** (FD) applies and the device is referred to as *thin-film* (Fig. 1.2c). If the structure is rotated by 90° and a common gate controls the conduction on the vertical channels, the potential distribution is directly symmetric, which is the case for FinFETs (Fig. 1.2d). Moreover, for vertical structures the use of a back-gate is less needed, since almost the whole surface of the vertical structure is controlled by the front gate.

As for bulk MOSFET (Fig. 1.3a), the potential distribution  $\Phi(x, y, z)$  inside the FinFET channel can be obtained by solving the Poisson's equation using the depletion approximation:

$$\frac{d^{2}\Phi(x,y,z)}{dx^{2}} + \frac{d^{2}\Phi(x,y,z)}{dy^{2}} + \frac{d^{2}\Phi(x,y,z)}{dz^{2}} = \frac{qN_{a}}{\varepsilon_{Si}}$$

(1.3)

For a double-gate device,  $\frac{d\Phi}{dz}=0$  [3], and the Poisson's equation becomes:

$$\frac{d^2\Phi(x,y)}{dx^2} + \frac{d^2\Phi(x,y)}{dy^2} = \frac{qN_a}{\varepsilon_{Si}}$$

(1.4)

An approximate solution of Eq. 1.4 can be found by assuming a parabolic potential distribution in the y-direction [7]. However, a more detailed solution should take into account the top gate of a FinFET as reported in [8], where a complex 3D analytical solution of the Poisson's equation is proposed, comparing the results to numerical solutions.

It is also worth mentioning how the threshold voltage  $V_{th}$  of a FinFET can be modified from the MOSFET equivalent one. The  $V_{th}$  is usually defined as the voltage at which strong inversion

occurs. For a MOSFET it is expressed by [9]:

$$V_{th} = V_{FB} + 2\phi_F + \frac{qN_A x_{dmax}}{C_{ox}} \tag{1.5}$$

where  $V_{FB}$  is the flatband voltage equal to the workfunction difference between metal and silicon,  $\phi_M - \phi_{Si}$ , and  $C_{ox}$  is the gate capacitance per unit area (surface and oxide charges are neglected). The term  $qN_Ax_{dmax}$  represents the depletion charge  $Q_D$ .

In a fully depleted FinFET,  $Q_D$  is constant and it becomes [3]:

$$Q_{D_{Fin}} = q \frac{1}{2} T_{Fin} N_A \tag{1.6}$$

The above expression is valid as long as the thickness of the inversion layer is small with respect to the silicon film thickness. Also, for ultra-thin devices ( $T_{Fin} \approx 10 \, \text{nm}$ ) more complex interactions should be taken into account, especially volume inversion [10].

The final gate and threshold voltage can then be expressed as:

$$V_g = \phi_S + V_{FB} + \frac{Q_{D_{Fin}}}{C_{ox}} \tag{1.7}$$

and, at threshold,

$$V_{th} = 2\phi_f + V_{FB} + \frac{Q_{D_{Fin}}}{C_{ox}}$$

(1.8)

where  $\phi_S$  is the surface potential equal to  $2\phi_f$  in strong inversion.

For pH sensing applications, the theoretical definition of  $V_{th}$  will not be used. The threshold voltage will be arbitrarily defined at constant  $I_{th}$  (Sec. 5.2.2), thus the use of Eq. 1.7 instead of Eq. 1.8 is more consistent.

#### 1.1.2 Subthreshold slope for thin-film FETs

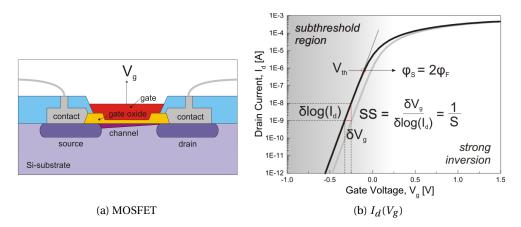

One of the most well-known feature of a FET device is the semi-logarithmic plot of the drain current  $I_d$  as a function of the gate voltage  $V_g$ , called  $I_d(V_g)$  transfer characteristic, as illustrated in Fig. 1.3b. For  $V_g < V_{th}$ , one can define the subthreshold region, a region of particular interest for sensing applications. An explicit expression for the  $I_d$  in the subthreshold region for a double-gate thin-film is provided in [11]:

$$I_{d} = \frac{W}{L} \mu_{n} 4C_{Si} \left(\frac{kT}{q}\right)^{2} (1 - e^{(-q/kT)(Q_{D}/8C_{Si})}) \cdot [1 - e^{-(qV_{ds}/kT)}] \cdot e^{q/kT(V_{g} - V_{FB} - [(Q_{D}/2)/C_{ox}] - 2\phi_{f})}$$

$$\tag{1.9}$$

where  $\mu_n$  is the electron mobility,  $C_{Si} = \epsilon_{Si}/t_{Si}$  is the capacitance per unit area associated to

# Chapter 1. Introduction: Narrowing the Gap between Nanoelectronics and Electronics for Sensing

the silicon film,  $V_{ds}$  and  $V_g$  the voltage at the drain and gate contacts. The variation of the  $I_d$  current according to  $V_g$  in the subthreshold region is expressed by the subthreshold slope (inverse or the real slope of  $I_d(V_g)$ ), defined as:

$$SS = \frac{\delta V_g}{\delta (log I_d)} = \frac{\delta V_g}{\delta \Phi_S} \cdot \frac{\delta \Phi_S}{\delta (log I_d)}$$

(1.10)

where  $\frac{\delta V_g}{\delta \phi_S}$  is called body m-factor and it describes the coupling between the gate and the surface potential, while  $\frac{\delta \phi_S}{\delta (log\,I_d)}$ , known as n-factor is limited to a minimum value according to the Fermi-Dirac distribution. For a bulk MOSFET the subthreshold slope can further be expressed as:

$$SS = n \cdot m = \frac{kT}{q} \ln(10) \left( 1 + \frac{C_D + C_{it}}{C_{ox}} \right) = 59 \left( 1 + \frac{C_D + C_{it}}{C_{ox}} \right) \text{mV/dec}$$

(1.11)

where  $C_D$  and  $C_{it}$  are the capacitances associated to the depletion region and the interface trap states, respectively. The subthreshold slope is constant and independent from the drain and gate voltage. An ideal FET device has a subthreshold slope of  $SS_0$  =59 mV/dec at room temperature (300 K). The full-depletion condition allows thin-film to get closer to the ideal value. In first approximation, the variation of the depletion charge with the front gate is, in fact,  $\delta Q_D/\delta V_g = 0$ , meaning that  $C_D \approx 0$  and the subthreshold slope approaches its theoretical limit [12] with m=1:

$$SS \cong \frac{kT}{q} \ln(10) \equiv SS_0 \tag{1.12}$$

which is valid for small thicknesses ( $t_{Si} < x_{dmax}$ ) [5] and neglecting the interface traps. Under scaling, the subthreshold slope of a thin-film device with the same parameters of a bulk device or thick-film will be steeper. In turns, in the subthreshold regime any variation of gate voltage  $\delta V_g$  is perfectly coupled to the surface potential  $\phi_S$ , giving rise to an equal increase. In a real device, the theoretical limit is never reached due to the presence of traps at the Si-Oxide interface.

In [13], the subthreshold slope limit is derived starting from the Fermi-Dirac distribution which describes the distribution of particles (fermions) obeying the Pauli exclusion principle. In the next section, Sec. 1.2, dedicated to the ISFET, an equivalent limit will be introduced for the change of surface potential caused by the variation of charge in an electrolyte solution.

#### 1.2 Ion Sensitive Field Effect Transistor

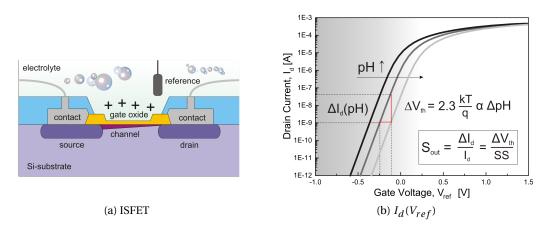

Ion Sensitive Field Effect Transistors (ISFET) were first developed in the 1970s, as an alternative to the glass electrodes for pH and ion measurements. In comparison to a MOSFET, the gate electrode is replaced by a reference electrode immersed in an aqueous solution in contact

Figure 1.3: (a) Cross-section of a planar MOSFET and (b)  $I_d(V_g)$  characteristic for a thin-film with  $t_{Si}$ =100 nm and definition of subthreshold slope.

with the gate oxide, as illustrated in Fig. 1.4a. The potential at the silicon surface is then function of the reference electrode and the amount of charges present in the solution as long as their contribution is not negligible at the ISFET surface. With respect to Eq. 1.7, additional contributions should be considered [14]:

$$V_g = E_{ref} - \Psi + \chi^{sol} - \frac{\Phi_{Si}}{q} - \frac{Q_D}{C_{ox}} + \phi_S$$

$$\tag{1.13}$$

and, at threshold,

$$V_{th} = E_{ref} - \Psi + \chi^{sol} - \frac{\Phi_{Si}}{q} - \frac{Q_D}{C_{ox}} + 2\phi_f$$

(1.14)

where  $E_{ref}$  is the potential of the reference electrode,  $\Psi$  is the chemical potential at the solution-oxide interface,  $\chi^{sol}$  is the surface dipole potential of the solvent (usually constant),  $\Phi_{Si}$  is the work function of the silicon which has been separated from the  $\Phi_M$  of the metal gate now included in  $E_{ref}$  and  $\phi_S$  is the surface potential at the Si-Oxide interface which will finally determine the  $I_d(V_g)$  transfer characteristics, always according to Eq. 1.9 for a double-gate thin-film. It is important to notice that  $\Psi$  and  $\phi_S$  are both surface potentials but they refer to two different interfaces in series. Any chemical variation in the solution modifies  $\Psi$ , which in the case of pH can be expressed as  $\Psi(pH)$ , but it can depend on any other electrical charges related to other ions or biological entities (DNA, proteins). The contribution of  $\Psi$  is linearly added to  $\phi_S$ , meaning that the electronic properties of the FET expressed by the  $I_d(V_{ref})$  relation are not modulated by  $\Psi$  but only shifted by a  $\Delta\Psi$ . Viceversa,  $\Delta\Psi$  is independent from the electronic and geometrical properties of the FET and it is exclusively controlled by the surface chemistry of the gate oxide. As illustrated in Fig. 1.4b, a change in  $\Psi$  will result in a change of the ISFET threshold voltage  $\Delta V_{th}$ , which can be measured by sweeping the reference electrode or by monitoring the  $I_d$  value at fixed  $V_{ref}$  value.

# Chapter 1. Introduction: Narrowing the Gap between Nanoelectronics and Electronics for Sensing

Figure 1.4: (a) Cross-section of a planar ISFET and (b)  $I_d(V_{ref})$  characteristic for a thin-film with  $t_{Si}$ =100 nm and definition of threshold voltage variation,  $\Delta V_{th}$ , and readout sensitivity,  $S_{out}$ .

#### 1.2.1 The Nernst limit in pH sensing applications

It has been mentioned that a  $\Delta\Psi$  occurs at the ISFET surface due to a chemical modification in the bulk solution if such a variation is transduced from the solution to the gate oxide surface. Such a modification can be related to any chemical or biological species containing a certain amount of charge able to reach the sensor surface. The modification of the pH in a solution is the most straightforward experiment because the gate oxide does not need any functionalization and it can be continuously repeated. The pH is a measure of the acidity or basicity of an aqueous solution and it is equal to:

$$pH = -\log_{10}(a_{H^+}) = \log_{10}\left(\frac{1}{a_{H^+}}\right) \tag{1.15}$$

where  $a_{H^+}$  is the activity, or effective concentration, of  $H^+$ . The relation between  $\Delta\Psi$  and the change of pH is established by:

$$|\Delta\Psi(pH)| = \frac{\ln(10)kT}{q}\alpha \cdot \Delta pH_B \longrightarrow \alpha \cdot 59mV/pH \tag{1.16}$$

with

$$\alpha = \frac{\beta}{\beta + 1} \tag{1.17}$$

where  $\beta$  symbolises the surface buffer capacitance (Sec.1.4.2) and  $\Delta pH_B$  is the pH change in the bulk solution. Eq. 1.16 is usually referred to as Nernst equation or Nernst limit. This relation derives from the proton concentration difference caused by the potential between the bulk solution of the oxide surface [15, 16]. According to Boltzmann statistics that can be used

as approximation to Fermi-Dirac statistics in the classical regime, the proton concentration is:

$$a_{H_S^+} = a_{H_B^+} exp \frac{-q\Psi_0}{kT} \tag{1.18}$$

or

$$pH_S = pH_B + \frac{q\Psi_0}{(2.3kT)} \tag{1.19}$$

where S and B denote surface and bulk. In turns, such potential difference arises from the surface reactions occurring at the oxide surface necessary to reach the electrochemical equilibrium. Specific surface sites, called amphoteric sites, are responsible for the chemical reactions. According to their density, specific for each oxide, the parameter  $\alpha$  will approach the unit. Assuming oxides with  $\alpha=1$ , Eq. 1.16 shows its maximum Nernstian sensitivity reaching 59 mV/pH, while for oxides having  $\alpha<1$ , a sub-Nernstian response is expected. Only an ideal coupling between the solution and the device through the sensing oxide, expressed by  $\alpha$ , can guarantee the maximum change in the solution to be transduced to the device and being read out in terms of threshold voltage variation  $\Delta V_{th}$ .

Equations 1.16, 1.18 and 1.19 have been derived specifically for pH, but the Nernst equation actually refers to a more general relation between the potential and the Gibbs free energy  $\Delta G$  of the overall reaction [17], as the Boltzmann statistics applies for general material particles. The Nernst limit also applies for all types of ions as Na, Cl, K, through  $pK_a = -\log_{10} K_a$  instead of the pH, where  $K_a$  is the acid dissociation constant.

In Tab. 1.3 many works based on SiNWs related to both pH and salt sensing applications are reported.

#### 1.2.2 Fundamental models of the EOS interface

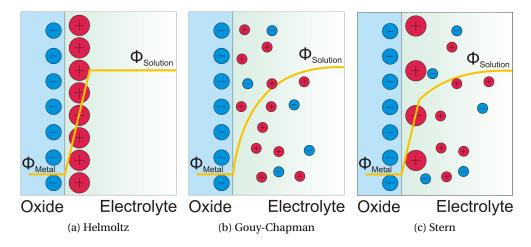

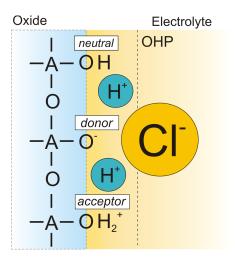

This section cites the fundamental models that followed one another in history, modelling the extremely complex Electrolyte-Oxide-Silicon (EOS) system. When an object (metals, alloys, semiconductors, insulators) is immersed in an electrolyte, a potential is set up across the two phases, at the object/electrolyte interface. The more common terminology in electrochemistry is that a double layer is set up at the interface. All models aim at the description of this Electrical Double Layer (EDL) [18]:

- Helmholtz: The earliest model of the EDL is usually attributed to Helmholtz, who mathematically treated the EDL as a capacitor. In this model, a single layer of ions, known as the *surface charge layer*, is adsorbed at the surface of an object, as illustrated in Fig. 1.5a. The remaining counterions in the bulk solution do not contribute to the potential difference  $\Phi_{surface} \Phi_{solution} = Q/C$  and the surface charge potential is linearly dissipated from the surface to the bulk.

- Gouy-Chapman: Gouy and Chapman proposed independently the idea of a diffuse dou-

# Chapter 1. Introduction: Narrowing the Gap between Nanoelectronics and Electronics for Sensing

ble layer [15, 19] to interpret the capacitive behaviour of a surface/electrolyte interface. The solution contains an excess of charge which is equal in value to that on the solid state surface but, due to their large-radius, a single layer of these charges will not be enough to screen the electric field. The ions in the solution are therefore electrostatically attracted, but the attraction is weak and counteracted by the random thermal motion. This finite width of charges gives rise to an exponential electrostatic potential drop within this layer as shown in Fig. 1.5b. However, this model considers the ions as point charges. As a consequence, it overestimates the capacitance, causing unrealistic high concentrations of ions near the surface.

• Stern: Stern [20] provided an adjustment to the previous model, introducing the concept that ions cannot approach the surface closer than their ionic radius. Such a distance has been called the Outer Helmoltz Plane (OHP) [21]. Close to the surface an ion depletion region gives rise to a constant capacitance, known as Stern capacitance with typical value of  $20\,\mu\text{F}\,\text{cm}^{-2}$  [22, 23]. The total differential capacitance is then made up of two components, the Stern and diffuse layer contributions in series:

$$C_{DL} = \frac{C_{dif}C_{Stern}}{C_{dif} + C_{Stern}} \tag{1.20}$$

where  $C_{dif}$  is mainly determined by the ionic strength.

Figure 1.5: Illustrative view of EOS models: (a) Helmoltz theory with large radius ions forming a surface charge layer opposite to the oxide charge layer assumed to be negative due to the presence of O<sup>-</sup> groups, (b) Gouy-Chapman model (c) Stern theory with both diffusion and constant contributions.

Several other contributions to the total potential drop have also been developed [24] such as (i) specific adsorption of ions onto the surface (Gouy-Chapman-Stern-Graham model), (ii) non-specific adsorption, (iii) polarization of solvent and (iv) surface complexation. However, their effects can generally be neglected.

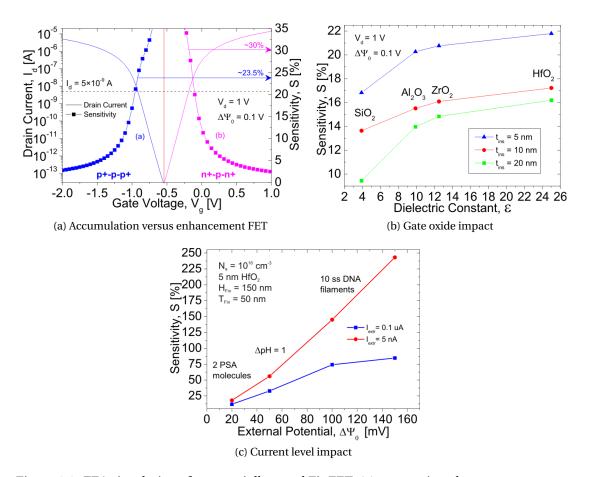

# 1.3 A common parameter for the limit of FET devices in pH sensing applications

In the previous sections, the classic physical limit that neither a MOSFET nor an ISFET can overcome has been introduced. For a MOSFET such a limit specifically translates to one decade of current, 59 mV/dec, whilst for an ISFET to one decade of H<sup>+</sup> concentration, 59 mV/pH. The transduction of the pH variation in the solution,  $\Delta pH_B$  through the sensor surface into a surface potential change  $\Delta\Phi$  is the *intrinsic sensitivity* of the sensor. Such a sensitivity can be read out by monitoring the variation of the threshold voltage of a FET,  $\Delta V_{th} = \Delta\Phi$  or, alternatively, the drain current  $\Delta I_d$ , at fixed  $V_{ref}$ . For the latter case, the two physical limits of the MOSFET and the ISFET can be merged together into a common parameter describing, at the same time, the quality of the surface transduction and the readout capability of the FET device. Throughout the whole thesis, this parameter will be called *readout sensitivity*,  $S_{out}$ , and it will be equal to the relative drain current variation before and after a change in the solution. The parameter  $S_{out}$  can be developed as follows:

$$S_{out} = \frac{\delta I_d}{I_d} = \frac{\delta I_d}{\delta V_g} \cdot \frac{\delta V_g}{I_d} = \frac{\delta I_d}{I_d \cdot \delta V_g} \cdot \delta V_g = \frac{\delta \ln(I_d)}{\delta V_g} \cdot \delta V_g = \frac{\delta V_g}{SS} \Rightarrow \frac{\Delta V_{th}}{SS}$$

(1.21)

In details:

- For a surface oxide featuring at least full coupling with  $\Delta p H_B \Rightarrow \frac{\Delta V_{th}}{SS} = S_{out} \le 1$

- For a FET device featuring at least the ideal  $SS_0 \Rightarrow \frac{\Delta V_{th}}{SS} = S_{out} \leq 1$

- For a FET device with fully responsive surface oxide and ideal  $SS_0 \Rightarrow \frac{\Delta V_{th}}{SS} = S_{out} = 1$

The  $S_{out}$  parameter can be defined for all types of chemical and biological sensing applications with the difference that each one of them will provide a specific  $\Delta V_{th}$ , subjected to different physical principles. Moreover,  $S_{out}$  involves all the information necessary to characterize a FET sensor. The subthreshold slope includes all electronic properties of a transistor such as doping, silicon width and gate length, interface states, thickness and dielectric constant of the gate oxide. Furthermore,  $S_{out}$  can be written as:

$$S_{out} = \frac{\Delta V_{th}}{SS} = \frac{g_m}{I_d} \cdot \Delta V_{th} \cdot \ln(10)$$

(1.22)

where  $\frac{g_m}{I_d}$  is the transcoductance-to-current ratio which is used in analog IC design [25, 26]. On the other hand, the threshold voltage variation always provides the transduction capability of the sensor surface.

## 1.4 High-k dielectrics

In this section, another important element of the presented work, i.e.  $HfO_2$ , is introduced. Such an oxide is part of the group of oxides called "high-k". First, the role of high-k dielectrics in microelectronics and their fabrication challenges are described. Later, the influence of different oxides on pH sensing is also discussed. Despite the fact that it is not common to talk about high-k dielectrics for pH sensing applications, it is not a coincidence that  $HfO_2$  represents one of the best option for both fields. Commonly, the term high-k describes a bulk property, while, on the other hand, pH sensing is a surface phenomenon. A physical correlation between bulk and the surface is, indeed, traceable.

#### 1.4.1 Advantages of high-k oxides in electronics

The increase of the calculating capacity of electronic devices has been realized with the continuous miniaturization of MOS transistors. The transistor scaling process has not only increased the package density of integrated circuits, but it also improved the circuit speed. According to Moore's law [4], the number of transistors within integrated circuits doubles approximately every two years and the Semiconductor Roadmap provides the factor scaling of each design parameter. How much the scaling can continue over time is not defined. However, the limits were envisaged to be in lithography, but it turns out that materials have also strict constraints to be taken into account. In the scaling process, the thickness of SiO<sub>2</sub>, which has been used for more than 40 years, has shrunk to as little as five atomic layers (1.2 nm). These very thin layers brought along many disadvantages such as:

- Too high leakage current through direct tunneling, resulting in energy waste and a build-up of heat;

- Reduction of the breakdown voltage and the oxide reliability;

- Control growth and uniformity of such small thicknesses.

As a solution, new gate oxides with physically thicker layer but higher permittivity started to replace SiO<sub>2</sub>:

$$C_{ox} = \frac{\varepsilon_0 kA}{t_{ox}} \tag{1.23}$$

where  $\varepsilon_0$  is the vacuum permittivity, k the relative permittivity, k the capacitance area and k0x1 the oxide thickness. Intel announced the integration of hafnium-based high-k1 dielectrics in conjunction with a metallic gate for the 45 nm node in 2007. However, such a replacement entails many difficulties and loss of many advantages. Indeed, the k20k3, except when it becomes too thin, is an excellent material, with few electronic defects, excellent interface, high thermal stability and high band offset with k3. All these properties are physically and chemically connected with the low permittivity and, moving towards an higher dielectric constant, it involves losing such privileges. Moreover, the choice of a high-k6 oxide should take

#### into account [27, 28]:

- Enough high dielectric constant to be used for a reasonable number of years;

- Large band offset with Si ( $E_G$  is inversely proportional to  $\varepsilon$ );

- Thermodynamic and kinetic stability;

- No reaction with Si and the metal gate;

- Good interface with Si, low lattice mismatch and similar thermal expansion coefficient;

- Few electrically active defects in its bulk;

- Negligible CV hysteresis.

The static dielectric constant and the band gap of some interesting high-k dielectrics are reported in Tab. 1.1 [29]. Considering the constraints listed above, HfO2, ZrO2 and La2O3 are the most promising candidates. Al<sub>2</sub>O<sub>3</sub> and Si<sub>3</sub>N<sub>4</sub> provide, in fact, a too low k-value to be implemented for several years, while TiO2 and Ta2O5 have a too small energy band offset with Si. La<sub>2</sub>O<sub>3</sub> has a higher k-value and band offset than HfO<sub>2</sub>, but it has been found to be highly hygroscopic, meaning that it attracts and holds water molecules from the surrounding environment. HfO2 and ZrO2 are very similar in their electronic structure. Zr and Hf have both 8 oxygen neighbours and each oxygen has 4 Zr/Hf neighbours. All the parameters usually used to describe an oxide are the result of this intrinsic electronic nature. Low-k oxides, as SiO<sub>2</sub>, are in fact characterized by a prevalence of covalent bonding with a low coordination number. On the other hand, high-k are characterized by ionic bonding with high coordination number [30]. Such a difference is not only the origin of the different bulk permittivity but it has also a large impact on the concentration of defects. The SiO<sub>2</sub> network, in fact, is much more able to relax, to rebound dangling bonds and remove defects, providing an excellent interface with Si. Finally, the analysis of the thermodynamic stability has revealed that ZrO<sub>2</sub> is actually unstable and reacts with Si and Poly-Si [31], leaving HfO2 as the preferred high-k oxide.

Table 1.1: High-k dielectrics

| Oxide            | K   | Gap[eV] | CB offset[eV] <sup>1</sup> |

|------------------|-----|---------|----------------------------|

| SiO <sub>2</sub> | 3.9 | 9       | 3.2                        |

| $Si_3N_4$        | 7   | 5.3     | 2.4                        |

| $Al_2O_3$        | 9   | 8.8     | 2.8                        |

| $Ta_2O_5$        | 22  | 4.4     | 0.35                       |

| $ZrO_2$          | 25  | 5.8     | 1.5                        |

| $HfO_2$          | 25  | 5.8     | 1.4                        |

| $La_2O_3$        | 30  | 6       | 2.3                        |

| TiO <sub>2</sub> | 80  | 3.5     | 0                          |

<sup>&</sup>lt;sup>1</sup>Conduction Band offset

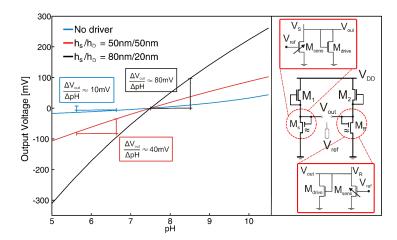

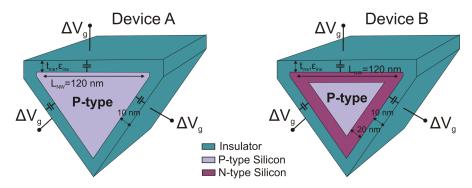

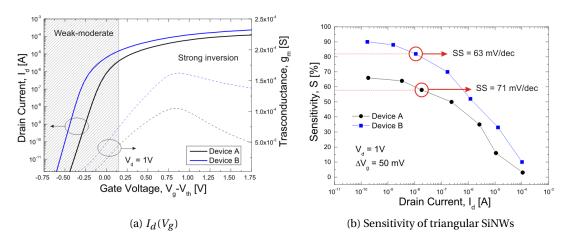

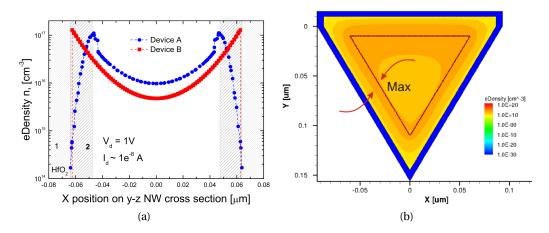

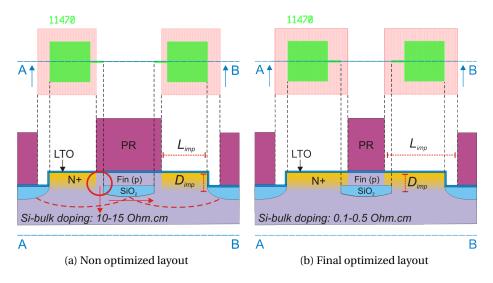

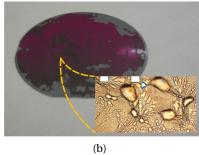

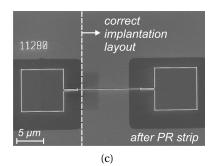

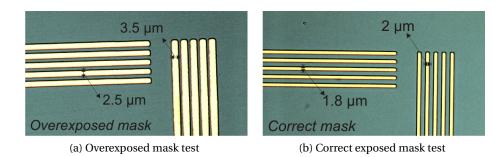

#### 1.4.2 Advantages of high-k oxides in pH sensing applications