Foundations and Trends<sup>®</sup> in Electronic Design Automation Vol. 8, No. 2 (2014) 117–197 © 2014 M. M. Sabry and D. Atienza DOI: 10.1561/1000000032

# Temperature-Aware Design and Management for 3D Multi-Core Architectures

Mohamed M. Sabry and David Atienza Embedded Systems Lab (ESL) Ecole Polytechnique Fédérale de Lausanne (EPFL) 1015, Lausanne, Switzerland mohamed.sabry@epfl.ch, david.atienza@epfl.ch

## Contents

| intro | oduction                                                                                                            | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1   | 3D-ICs for Augmented Performance Per Unit Area                                                                      | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.2   | Thermal Issues in 3D MPSoCs                                                                                         | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.3   | Thermal Impact on 3D MPSoC Reliability and Performance                                                              | 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.4   | Advanced Cooling Technologies for 3D MPSoCs                                                                         | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5   | Survey Overview and Outline                                                                                         | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| The   | rmal Modeling for 3D MPSoCs                                                                                         | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.1   | Heat Transfer Principles                                                                                            | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.2   | Thermal Modeling Frameworks for 2D/3D ICs                                                                           | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.3   | Compact Thermal Modeling for 3D MPSoCs                                                                              | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.4   | Summary                                                                                                             | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Tem   | perature-Aware Design Optimizations for 3D MPSoCs                                                                   | 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.1   | On-Chip Design-Time Optimizations                                                                                   | 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.2   | Off-Chip Design-Time Optimizations                                                                                  | 152                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.3   | Summary                                                                                                             | 162                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Tem   | perature-Aware Runtime Management for 3D MPSoCs                                                                     | 163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.1   | Temperature-Affecting Control Knobs                                                                                 | 165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

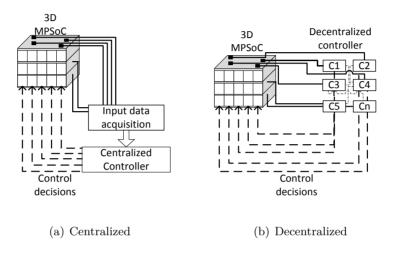

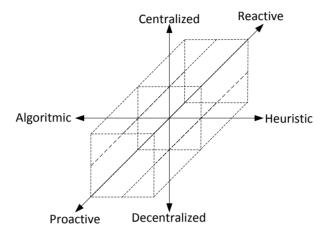

| 4.2   | Centralized Versus Decentralized Management Schemes                                                                 | 166                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

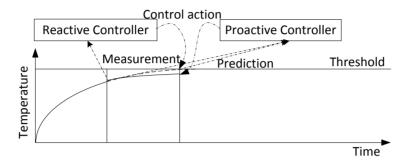

| 4.3   | Reactive Versus Proactive Management Schemes                                                                        | 171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>The<br>2.1<br>2.2<br>2.3<br>2.4<br>Tem<br>3.1<br>3.2<br>3.3<br>Tem<br>4.1<br>4.2 | 1.2 Thermal Issues in 3D MPSoCs 1.3 Thermal Impact on 3D MPSoC Reliability and Performance 1.4 Advanced Cooling Technologies for 3D MPSoCs 1.5 Survey Overview and Outline  Thermal Modeling for 3D MPSoCs 2.1 Heat Transfer Principles 2.2 Thermal Modeling Frameworks for 2D/3D ICs 2.3 Compact Thermal Modeling for 3D MPSoCs 2.4 Summary  Temperature-Aware Design Optimizations for 3D MPSoCs 3.1 On-Chip Design-Time Optimizations 3.2 Off-Chip Design-Time Optimizations 3.3 Summary  Temperature-Aware Runtime Management for 3D MPSoCs 4.1 Temperature-Affecting Control Knobs 4.2 Centralized Versus Decentralized Management Schemes |

| 4.4              | Heuristic Versus Algorithmic Management Schemes | . 176 |

|------------------|-------------------------------------------------|-------|

| 4.5              | The Global Perspective on Thermal Management    | . 182 |

| 4.6              | Summary                                         | . 184 |

| Conclusion       |                                                 | 185   |

| Acknowledgements |                                                 | 188   |

| Referen          | ices                                            | 189   |

#### **Abstract**

Vertically-integrated 3D multiprocessors systems-on-chip (3D MP-SoCs) provide the means to continue integrating more functionality within a unit area while enhancing manufacturing yields and runtime performance. However, 3D MPSoCs incur amplified thermal challenges that undermine the corresponding reliability. To address these issues, several advanced cooling technologies, alongside temperature-aware design-time optimizations and run-time management schemes have been proposed. In this monograph, we provide an overall survey on the recent advances in temperature-aware 3D MPSoC considerations. We explore the recent advanced cooling strategies, thermal modeling frameworks, design-time optimizations and run-time thermal management schemes that are primarily targeted for 3D MPSoCs. Our aim of proposing this survey is to provide a global perspective, highlighting the advancements and drawbacks on the recent state-of-the-art.

**Keywords:** System-Level Design, Thermal Management, MPSoC Cooling, Temperature Optimization, Reliability, Vertical Integration.

DOI: 10.1561/1000000032.

M. M. Sabry and D. Atienza. Temperature-Aware Design and Management for 3D Multi-Core Architectures. Foundations and Trends<sup>®</sup> in Electronic Design Automation, vol. 8, no. 2, pp. 117–197, 2014.

## 1

#### Introduction

The last decades have seen a revolution in data gathering, processing, information storage and communication. This revolution has been caused by electronic computing systems, which nowadays are one of the key building blocks of the world's information technology (IT) infrastructure. In fact, computing systems and IT services are an essential pillar of the developed world, contributing up to 50% of its economy [1]. The IT and computing systems revolutions have been the result of the advancements in IC processing technology, where the number of components (transistors) on the same die area have been doubled every 18 months [2], which is also known as Moore's law. This has been the drive to generate more complicated computing systems with higher performance and computational functionality.

As feature sizes scale with advanced processing technologies, the performance of processing units has increased because of greater functionality and higher computational capabilities. This functionality augmentation was accompanied by an increase in the operating frequency of the processing unit. Micro-architects have conventionally used operating frequency as a measure for the processing unit performance, as higher frequency implies more instructions executed per unit time.

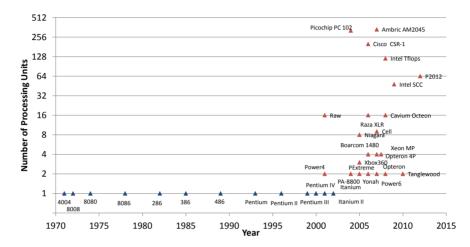

**Figure 1.1:** Number of processing units integrated in a single IC, as evolved with time. Blue-labeled ICs are single-core architectures, while red-labeled ICs are multicore architectures.

However, at the sub-micron level, the circuit-level delays are getting dominated by wiring and interconnect delays, which led to frequency flattening. If the operating frequency would increase with this technology, significant additional power consumption is required by the processing unit, which results in an increased heat generation. For example, a 90 nm fabricated AMD processing unit would require 60% additional power consumption to increase the operating frequency by  $400\mathrm{MHz}$  [3].

Multi-core architectures have been proposed as an alternative design paradigm to frequency increase in single-core architectures, to continue performance improvement with technology scaling [4]. Multi-core architectures integrate two or more processing units, with shared or distributed memory modules, interconnected through an on-chip bus or a network-on-chip [5]. As feature sizes scale with advanced processing technologies, the number of processing units in multi-core architectures dramatically increases. Fig. 1.1<sup>1</sup> shows that the number of cores inte-

$<sup>^1{\</sup>rm This}$  figure is based on a similar figure found in the course slides given by Prof. S. Amarasinghe of MIT http://groups.csail.mit.edu/cag/ps3/pdf/6.189-info-session.pdf

grated in a single IC has started to ramp-up in the beginning of the  $21^{st}$  century. Recent multi-core architectures integrate a number of processing units, multi-level memory hierarchy, an interconnect module, and in the case of embedded domain, special peripherals such as analog-to-digital converters (ADC), co-processors, or wireless RF antennas. This architecture, which is known as *Multiprocessor Systems-on-Chip* (MPSoC), has been widely used in various domains. An example of recent MPSoC utilization at the high performance computing systems level is data-intensive computing systems, which is also known as the fourth paradigm [6]. Another example for MPSoC utilization is found at the embedded systems domain, with small- or tiny-size computing systems, such as on-body [7] or in-body [8] health monitoring systems.

#### 1.1 3D-ICs for Augmented Performance Per Unit Area

While the performance of computing architectures has been enhanced by MPSoCs, MPSoCs' performance has been recently challenged by increased propagation delay, primarily due to longer interconnects [9]. This is mainly due to the increased wire-to-gate delay ratio. This delay would lead to degraded MPSoC performance or increased energy consumption.

This delay limitation, combined with the continued demands for increased integrated functionality while preserving the performance and area efficiency, have led to the development of vertically-integrated 3D ICs. 3D integration is viewed as an attractive solution to provide increased functionality with better yield, as well as a technique of combining several technologies in a single enclosure (package) [10]. From a design perspective, 3D integration can be split into the following categories:

• Monolithic 3D integration [11]. This integration technology fabricates the tiers serially at the transistor granularity, within a single fabrication process. From the bottom tier, the corresponding transistors are fabricated then a substrate layer is placed on top where another tier is fabricated. These layers are connected with vertical interlayer vias. Thus, this integration technology is

promising in terms of providing higher density and performance gains.

• 3D stacking (also referred to as Parallel 3D integration) [10]. This integration technology stacks vertically 2D die layers to form a single 3D IC. To enable the communication and power delivery to these dies, there are several techniques adopted such as wire bonding, microbumps, and through-silicon vias (TSVs). TSVs are vertical wires that carry power and signals between different dies, which are etched in the silicon substrate between the 2D dies.

In this survey, we primarily target 3D stacked ICs with several digital logic dies and TSV-based interlayer communication. We refer to the targeted 3D ICs throughout this review by 3D multiprocessors systems-on-chip, or 3D MPSoCs.

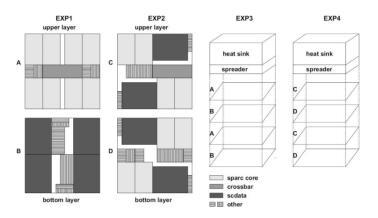

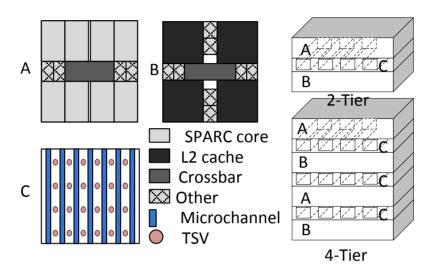

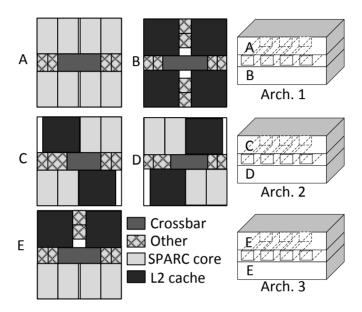

3D MPSoCs are multi-layered stacked 3D ICs, where each die contains a number of processing units, memory modules, and other peripheral and interconnection units. Examples of typical 3D MPSoCs integrate a number of processing layers that contain all the processing units, and a number of memory layers. Another 3D MPSoC example is where the processing units and the memory modules are co-placed in each die of the 3D stacked layers. These examples have been shown in previous works [12, 13], and are shown in Fig. 1.2, which includes an UltraSPARC T1 [14] version of a 3D MPSoC. This vertical integration of logical modules brings several benefits to multi-core architectures, which are as follows:

- Vertical stacking shortens the wiring length between two modules. In this respect, the propagation delays, which are recently dominated by interconnect delays [15], are dramatically reduced leading to an increased performance of 3D MPSoCs. Thus, 3D MPSoCs would outperform 2D MPSoCs.

- 3D MPSoCs allow heterogenous integration of different components, such as DRAM on multi-core architectures [13]. 3D MPSoCs enhance the memory access bandwidth and throughput, by bringing the memory modules (e.g. DRAM) to the top or bottom

Figure 1.2: Schematic view of a 4-tier 3D MPSoC with different architectures [12].

of processing layers. This would enable high-speed, massively-parallel data access to these stacked DRAM layers.

#### 1.2 Thermal Issues in 3D MPSoCs

Despite the performance and throughput enhancements that 3D MP-SoCs bring, 3D MPSoC designs face major challenges, particularly in the extreme elevated temperatures accompanied with high-performance designs.

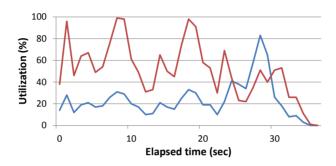

While technology continues to scale-down the transistor features, MPSoCs voltage supply  $(V_{dd})$  could not be scaled down accordingly [16]. Recent work [17] (Fig. 1.3(a)) has shown that the supply voltage scaling is saturating that, if combined with increased integration within a unit area due to reduced transistor features, leads to an increase in power consumption. In this respect, multi-core architectures design trends have taken the direction of increasing the power density by integrating more processing units on the chip (with a fixed chip area), as shown in Fig. 1.3(b). If the MPSoC power density keeps increasing, it will eventually reach the same magnitude of nuclear power plants [4, 18].

With such increased power densities, MPSoCs face a tremendous

Figure 1.3: Voltage/Energy [17] and power density [18] scaling trends.

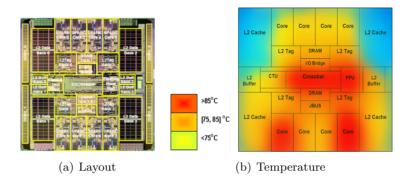

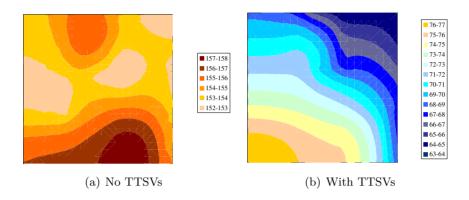

increase in heat generation that has a direct impact on the lifetime of MPSoCs. This increased heat generation leads to high temperature in the MPSoCs. While high-frequency single processing units have faced the similar case of high temperatures, the thermal profile of MPSoCs can have a more severe impact. This is mainly related to the localized heat generation of the several processing units of MPSoCs. Thus, the localized heat generation creates several localized high temperatures, which is known as thermal hot spots. The existence of several thermal hot spots would imply that there are other localized cold spots, which leads to the creation of the undesirable spatial thermal gradients. Moreover, the time-varying nature of workload processing requirements, or even when the processing goes to power-up and power-down cycles, leads to temporal thermal cycles [19] formation. To demonstrate the MPSoC thermal issues, an example of various hot spots location and thermal gradient is shown in Fig. 1.4(b). This figure shows a thermal response snapshot of the UltraSPARC T1 (Niagara) [20] MPSoC to a typical workload execution.

While high-density 2D MPSoCs face strong thermal challenges, these challenges are more prominent in the vertically-stacked 3D MPSoCs [21, 12]. Due to the vertical stacking of different dies, the thermal resistance of 3D MPSoCs is significantly increased to alarming values [12], compared to the increased temperature we demonstrate in the case of 2D MPSoCs. This is mainly due to the increased and non-

Figure 1.4: Floorplan layout and thermal response of the UltraSPARC T1 MP-SoC [20].

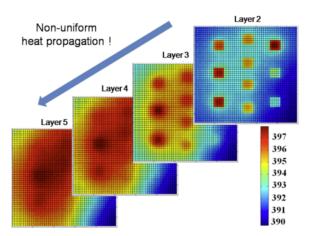

uniform thermal resistance at different stacked layers, based on their relative heat dissipation paths using conventional techniques such as placing heat sink on top of the top-most layer. For example, Fig. 1.5 shows the temperature of an emulated 3D MPSoC. This emulator is built by stacking 4 heat dissipation tiers on a substrate tier. In each of the heat dissipation tiers there is a number of controllable microheaters that are used to emulate the heat generation pattern of processing units similar to the actual pattern of each processing unit. In addition to these micro-heaters, there is a number of thermal sensors to capture the thermal profile of this emulator. This 3D thermal emulator has a heat sink placed at the top-most layer. The temperatures shown in this figure indeed confirm the expected high temperature and thermal gradient values of prospective high-performance 3D MPSoCs.

Thus, it is expected that high-density high-performance 3D MP-SoCs are more prone to hot spots and thermal gradients. The existence of hot spots, thermal gradients, and thermal cycles heavily affect the MPSoC (2D and 3D) operation and lifetime, as shown in the following section.

## 1.3 Thermal Impact on 3D MPSoC Reliability and Performance

High temperature is undesirable in 3D MPSoCs operation due to the different device and interconnect reliability and degraded performance

Figure 1.5: Thermal state of a 5 tier (4 thermal dissipating tiers + 1 substrate base tier) high-density MPSoC thermal emulator. Temperature values are in Kelvin [22].

sources that are highly affected, directly and indirectly, by this rise in temperature. These sources would affect the reliability of 3D MP-SoCs by accelerating the processor aging or the *Mean-Time to Failure* (MTTF) [23], which is the statistical average time for the MP-SoC to breakdown permanently, as well as creating irreversible functional failures in the computation modules (e.g., storage) that limit the full utilization of these modules. In addition to the impacted reliability, high 3D MPSoC temperature would eventually lead to degraded performance by reducing the operating frequency due to increased propagation delays or reduced energy-efficiency resulted from the increased leakage power consumption. Thus, it is important to identify the temperature-induced reliability and degraded performance sources and elaborate more on their corresponding impact. The following paragraphs give an overview of these sources:

Bias Temperature Instability (BTI) [24]. This factor causes instabilities in the device behavior, due to the stress applied on the bias (e.g., a negative bias on the gate source voltage of a PMOS transistor). BTI can be split to two types, namely Negative BTI, which is related to the PMOS device stress, and Positive BTI, which is related to the NMOS device stress. The main degraded parameter due to BTI is the

threshold voltage, as shown in prior work [24]. The change in threshold voltage during stress (increase in threshold voltage) and release times (decrease in threshold voltage) has a dependency on a number of factors, which includes temperature [25]. Higher operating temperatures indeed have a direct impact on the threshold voltage based on BTI, which results in longer circuit delays and increase in dynamic power consumption.

Hot-Carrier Injection [26]. Hot-carrier injection occurs when a carrier gains enough energy to tunnel from the transistor source or drain to the dielectric material. This even accompanied with a rise in the device temperature. Hot-carrier injection occurs at normal temperature range, but the injection rate is increased as the operating (or stress) temperature is increased [27]. Based on the above observations, hot-carrier injection could lead to thermal positive feedback loop situation, i.e., the injection leads to increase in temperature that may trigger an increase in the injection rate. Consequently, hot-carrier injection would lead to thermal run-away.

Time-Dependent Dielectric Breakdown (TDDB) [28, 29] in high-k device dielectric and low-k interconnect dielectric. This is modeled as trap generated that leads to a leakage path through the oxide layer of the transistor. This is also referred in literature as gate oxide breakdown. TDDB has an exponential dependency on temperature [28] that accelerates the failure of a transistor by breaking down the dielectric, hence forming a constant conducting path. As a consequence, the faulty transistor would be permanently in a conducting state.

**ElectroMigration (EM)** in metallic interconnect [30]. Electromigration is a phenomenon that occurs in the IC interconnects (metal layers) due to high current densities. EM leads to a shift in the conducting ions location, hence causing a breakdown in the interconnects. EM has a strong dependency on the temperature resulted from the utilization of the IC and the joule self-heating of the interconnects due to the high current density. In this respect, higher operating temperatures would

eventually lead to a breakdown of the metal layer, which may result in a complete failure of the IC.

Subthreshold Leakage Current [31]. Subthreshold leakage current is one of the sources of leakage current, and hence static power consumption in MPSoCs. It is the drain-source current of a transistor operating in the weak inversion region. Unlike the strong inversion region in which the drift current dominates, the subthreshold conduction is due to the diffusion current of the minority carriers in the channel. Subthreshold leakage is found to be the dominant component in the overall leakage current sources [32]. Subthreshold leakage current has a strong dependency on the operating temperatures with a sensitivity of  $8 - 12x/100^{\circ}C$  [31].

The aforementioned sources can lead to system failure if no proper measures are taken. But these sources also degrade the MPSoCs (2D and 3D) operation from its original (also called time-zero) operating conditions. The following paragraphs highlight more on these affected parameters:

Mean-Time To Failure [23, 31]. The mean-time to failure would be heavily impacted due to the temperature impact on Time-Dependent Dielectric Breakdown (TDDB), Electromigration (EM), as well as stress migration and thermal cycling.

Temperature-Dependent Propagation Delays [33]. This change in the time required for a signal to travel between two modules is related to the thermally-induced delays in the logic gates (e.g. resulted from BTI), as well as the increase of the interconnect resistivity (e.g. resulted from Electro-migration). Another cause for the propagation delay is in the clock skew between different modules experiencing diverse thermal stress. In this respect, propagation delays have a strong dependency not just on the overall thermal state of the IC, but on the spatial thermal gradient as well. Indeed, previous work reports that a spatial gradient of  $40^{\circ}C$  would create a 10% clock skew between different modules within a single IC.

Temperature-Dependent Leakage Power [31]. Leakage power is one of the sources of static power consumption in MPSoCs. The leakage power is a cause of various elements, such as the reverse-biased junction leakage current and the subthreshold leakage. These elements have a strong dependency on the operating temperatures. In fact, it has been shown by previous work that the leakage power has an exponential [34] dependency on temperature. Thus, it is crucial to prevent the operating MPSoCs from entering thermal runaway situations. Temperature-dependent leakage power may not be viewed as a failure mechanism, but high leakage power would cause a significant degradation in the power efficiency, as it would surpass the dynamic power consumption, where dynamic power is the effective power used in computations and is mainly workload dependent.

#### 1.4 Advanced Cooling Technologies for 3D MPSoCs

To address the increasing thermal rise of 3D MPSoCs, several research initiatives have explored several advancing cooling strategies for the target architectures. For instance, there has been several research efforts to insert dummy thermal through-silicon vias (TTSVs) [35] to dissipate the heat generated from the layers further from the heat sink in a more efficient way.

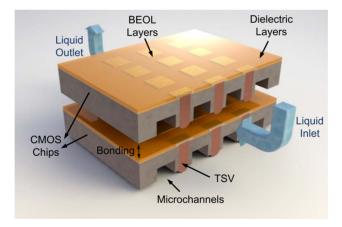

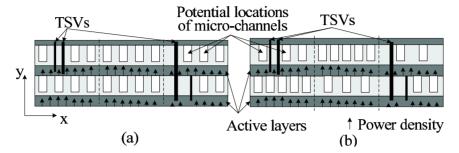

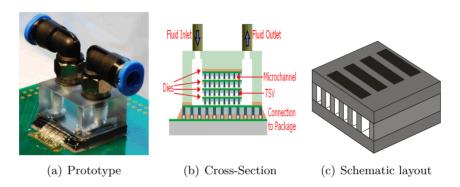

Another advanced cooling technology uses injected fluids (single- or two-phase), between the different layers of the 3D MPSoCs. This cooling methodology, which is also known as interlayer liquid cooling [36], is achieved by manufacturing a cavity layer, for example rectangular microchannels or micro pin-fin structures [37], on the back-side of each silicon layer. A typical structure of 3D MPSoCs consists of two or more silicon tiers, which contain the processing and storage elements of the system. The communication between these tiers is realized with through-silicon vias (TSVs) that are etched in the residual silicon slab. To account for inter-tier liquid cooling, the porous cavity is realized by etching porous structures of different form and shapes (cf. Fig. 1.6). In the example shown in Fig. 1.6, the micro-channels are built, and distributed uniformly, in between the vertical layers for liquid flow. The

Figure 1.6: Layouts of the interlayer liquid-cooled 3D MPSoCs [38].

fluid flows through each channel at the same flow rate, but the liquid flow rate provided by the pump can be dynamically altered at runtime.

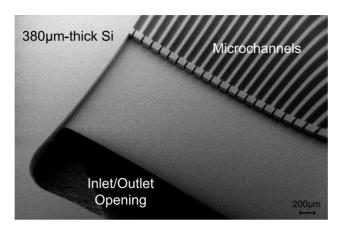

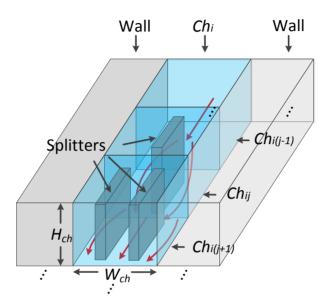

Manufacturing 3D MPSoCs with TSV interconnections and microchannels requires a series of microfabrication processes, namely (1) deep-reactive-ion-etching (DRIE) process for anisotropic silicon etching of both TSV openings and backside microchannels (cf. Fig. 1.7); (2) conformal thin film deposition for TSV sidewall insulation; (3) electroplating for conductive layer formation; (4) grinding for chip thinning, and finally (5) wafer- or die-level bonding for the stacking. A simplified illustration of a 3D stack with inter-tier liquid cooling is shown in Fig. 1.8.

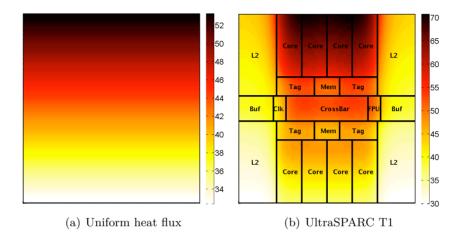

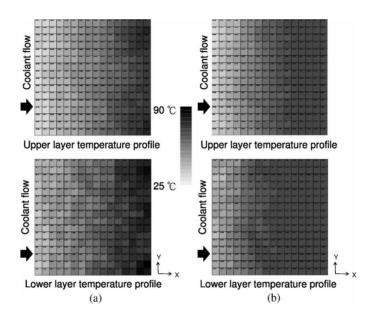

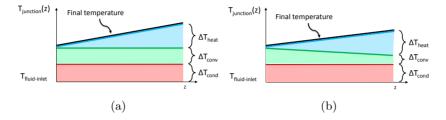

Despite the benefits that liquid cooling brings in terms of significant thermal reduction, liquid cooling adds additional challenges to obtain a balanced thermal state with low spatial thermal gradients. As the coolant flows in microchannels, it experiences sensible heat absorption along the path [41]. This results in the coolant temperature increase from inlet to outlet, which causes a thermal gradient formation on the MPSoC surface even when the heat dissipation is uniform, as shown in Fig. 1.9(a). More commonly, in 3D MPSoCs with non uniform heat

Figure 1.7: SEM photos the wafer Back-side with the inlet-outlet openings while showing the micro-channels [39].

Figure 1.8: Simplified illustration of 3D stack with inter-tier liquid cooling [39].

dissipations, the existing thermal gradients and hot spots are aggravated by this characteristic of interlayer liquid cooling, as shown in Fig. 1.9(b). As a result, thermal gradients proliferate in 3D MPSoCs with liquid cooling. These gradients cause uneven thermally-induced stresses on different parts of the MPSoC, significantly undermining overall system reliability [31] (cf. Section 1.3.

From these observations we deduce that these new advanced cooling technologies bring both additional benefits and challenges. Thus,

**Figure 1.9:** Steady-state temperature distribution of a 14mm x 15mm two-die 3D IC with (a) uniform (combined) heat flux density of  $50 \text{W/cm}^2$  and (b) the Ultra-SPARC T1 (Niagara-1) chip architecture [14]- the (combined) heat flux densities range from  $8 \text{W/cm}^2$  to about  $64 \text{W/cm}^2$ . Direction of the coolant flow is from the bottom to the top of the figure [40].

it is crucial to find an optimized methodology to apply these technologies, alongside conventional 2D temperature balancing techniques in the context of resource-efficient temperature-aware 3D MPSoCs. Our interest in resource-efficiency varies from area to applied energy.

#### 1.5 Survey Overview and Outline

In this survey, we provide an extensive survey that covers temperature-aware design optimizations and run-time management schemes for 3D MPSoCs, to avoid the rapid degradation of these architectures due to the thermal impact on reliability. The survey shows how the state-of-the-art tackles the thermal issues in the emerging 3D MPSoCs that include advanced cooling mechanisms, such as thermal-through-siliconvias (TTSVs) and interlayer liquid cooling. We perform this survey exploration in a top-down manner to cover all the temperature-aware aspects in the target architecture. In particular, we provide two main research directions that tackle the thermal issues, namely:

1. Design-time technological solutions and temperature-aware optimizations. In this category we explore various techniques that address, at *design-time*, the means of generating and dissipating heat in 3D MPSoCs. This includes the optimization of new advanced cooling and heat dissipation mechanisms, temperature-aware floorplanning, and design-time optimization of different parameters that would affect the thermal behavior of 3D MPSoCs.

2. Run-time thermal management mechanisms. We show in this category the various temperature-affecting knobs in the target 3D MPSoC, and how the state-of-the-art utilizes these knobs in developing several *run-time* thermal management mechanisms.

#### 1.5.1 Related Survey Works

Our proposed survey overlaps with several surveys that exist in literature. An initial survey in thermally-aware design [42] explores the various design-optimization mechanisms for MPSoCs, both planar 2D and vertical 3D. In particular, this previous survey explains the various modeling framework approaches and explores thermal-aware floorplanning, and the means to recover from temperature-induced parameters degradation such as run-time shifts. However, there is no exploration for advanced cooling mechanisms, other design-time optimization mechanisms, or run-time thermal management techniques, which are explored in our proposed survey.

There is a recent survey work that explores various thermal management mechanisms for processing architectures [43]. In this previous survey, several mechanisms for balancing temperatures in 2D and 3D MPSoCs are explored, namely thermal sensor placement, run-time thermal management, floorplanning, operating system/compilation techniques, and a brief exploration on liquid cooling. However, this survey does not provide a systematic classification of the temperature optimization research field. In our proposed survey, however, we provide our classification in a more systematic methodology that follows a top-down reasoning to cover most of the research directions in 3D MPSoC

temperature optimization.

Finally, another survey explores thoroughly vertical integration in 3D ICs [44]. This previous work explores the various electronic-design automation tools needed for 3D architectures. Then it explores the various architecture flavors in 3D ICs, namely 3D field programmable gate arrays (FPGA) and 3D MPSoC designs. Thus, this previous survey work is complementary to our proposal.

#### 1.5.2 Survey Organization

This survey starts with providing an overview of the recent thermal modeling approaches developed for the target 3D MPSoC architectures in Section 2. In Section 3, we explore the design-time optimization schemes to minimize the temperature-oriented issues in 3D MPSoCs. Section 4 shows our exploration in run-time thermal management schemes for 3D MPSoCs. We first start by stating the various temperature-affecting control knobs, then we show the classification of different management schemes that use these knobs to balance the dissipated heat in the target architecture. Finally, we summarize our work in this survey in the conclusion.

### Thermal Modeling for 3D MPSoCs

In this section, we explain the fundamentals of heat transfer of the targeted 3D MPSoCs, as it is a basic requirement for developing the appropriate thermally-aware optimization schemes. Based on these heat transfer fundamentals, we highlight on the state-of-the-art thermal modeling frameworks.

#### 2.1 Heat Transfer Principles

Due to the hybrid solid-fluid material composition of the targeted 3D MPSoCs that may include interlayer liquid cooling (solids in the silicon dies, fluids in the used cooling material), the heat transfer in this target architecture is based on three factors, which are as follows:

- 1. Heat flow via **conduction in solids**, which occurs between the adjacent die layers or within the layer.

- 2. Convective heat transfer at the solid-liquid interface at the microchannel walls.

- 3. Sensible heat transport via mass flow of fluids from inlet to

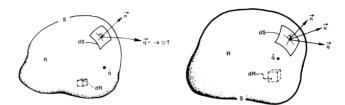

**Figure 2.1:** (a) Control volume of a solid with heat conduction. (b) Control volume of a liquid (coolant) with heat conduction and convection [45].

outlet inside the microchannels (or liquid-carrying cavity structures).

The modeling of heat flow via **conduction in solids** begins with Fourier's law [46, 45]. Consider a control volume of a solid R as shown in Fig. 2.1(a). The energy balance for this control volume can be written using the following integral equation:

$$\frac{\partial}{\partial t} \int_{R} \rho \ \hat{u} \ dR + \int_{S} (-k\nabla \ T) . \vec{n} \ dS = \int_{R} \dot{q} \ dR, \tag{2.1}$$

where  $\rho$  is the density of the material,  $\hat{u}$  is the enthalpy, S is the surface area of the control volume, k is the thermal conductivity of the material,  $\vec{n}$  is the unit normal vector on the surface of the volume and  $\dot{q}$  is the volumetric heat generation rate inside the volume. In the above equation (Eq (2.1)), the first term on the left hand side is a volume integral representing the amount of heat energy stored in the volume. The second term is a surface integral representing the loss of heat from the volume due to heat conduction. The term on the right hand side is a volume integral representing the heat generation rate inside the volume due to conversion from another form of energy, which is the electric switching activity in the case of the target 3D MPSoC. Thus, taking the limit  $R \to 0$ , applying Stoke's theorem [45], and assuming the material has isotropic thermal conductivity (that is, the same value of thermal conductivity in all directions), the above integral equation reduces to the following diffusion equation:

$$c_v \frac{\partial T}{\partial t} + \left(-k\nabla^2 T\right) = \dot{q}, \tag{2.2}$$

Figure 2.2: Convective heat transfer at the solid-liquid interface of a microchannel.

where  $c_v$  is the volumetric specific heat of the material and T is the temperature of the control volume.

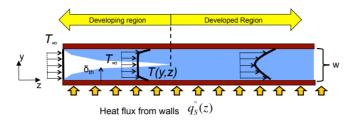

Modeling the **convective heat transfer** at the interface between a microchannel wall and a flowing liquid (as seen in Fig. 2.2) traditionally begins with the Newton's law of cooling as described by the following equation [47]:

$$q_s'' = h \left( T_s - T_\infty \right), \tag{2.3}$$

where  $q_s''$  is the heat flux at the surface entering/leaving the solid,  $T_s$  is the temperature of the solid surface,  $T_{\infty}$  is the temperature of the fluid bulk and h is the heat transfer coefficient at the surface. Combining the above equation with the Fourier's law at the interface in steady state assuming one dimensional heat transfer (Fig. 2.2):

$$q_s'' = -k_f \frac{\partial T}{\partial y} \bigg|_{y=0}, \tag{2.4}$$

Then we can write the heat transfer coefficient as:

$$h = \frac{-k_f \partial T/\partial y|_{y=0}}{T_s - T_{\infty}},\tag{2.5}$$

where  $k_f$  is the fluid thermal conductivity. The heat transfer coefficient in (2.5) is derived by studying the fluid flow nature, the hydrodynamic and thermodynamic developing layers and the thermal properties of the fluid to compute the terms on the right-hand side. It is then typically expressed in the form of a dimensionless parameter of the flow called the Nusselt number Nu [47, 45].

Once the parameters for convective heat transfer at solid-liquid interfaces are computed, they can be combined with Fourier's law to solve for the temperatures in the entire structure. While inside the solid parts of the structure (2.1) are used for this purpose, inside the fluid parts an additional term must be included to account for the heat transfer associated with the liquid flow, in order to account for the rise in  $T_{\infty}$  as it flows from inlet to outlet absorbing heat (sensible heat transport), as shown below:

$$\frac{d}{dt} \int_{R} \rho \, \hat{u} \, dR + \int_{S} \left( -k\nabla T \right) . \vec{n} \, dS + \int_{S} \left( \rho \, \hat{h} \right) \, \vec{u} \cdot \vec{n} \, dS = \int_{R} \dot{q} \, dR, \tag{2.6}$$

#### 2.2 Thermal Modeling Frameworks for 2D/3D ICs

The mentioned factors in Section 2.1 have been used before in various modeling techniques. For heat conduction modeling, numerical techniques involve the discretization of the above partial differential equation (Eq. 2.2) first in space, creating ordinary differential equations. Next, the ordinary differential equations are numerically integrated in time to solve for the temperature at the relevant points in space and time in a given computational domain. The first step is usually accomplished by either finite-element [48] or using compact finite-difference frameworks such as HotSpot [46]. In the case of alternate direction implicit method (ADI) [49], the discretizations in space and time are done simultaneously and the solving in both domains are intertwined.

In the case of convective heat transfer modeling, finite-volume methods are used in traditional numerical fine grained simulators such as ANSYS CFX [50], where the microchannel and the surrounding structures are divided into very small cells, and the three-dimensional fluid velocity profile and the temperatures are simultaneously computed by solving the flow of fluids, governed by the Navier-Stokes equations, and the Fourier's law equations respectively in three dimensions. Hence, the computations of convective heat transfer at solid-liquid interfaces (i.e. terms in (2.5)) are implicit in this method. Such methods, while being accurate, are extremely slow and are not desirable in complex structures such as interlayer liquid-cooled 3D MPSoCs.

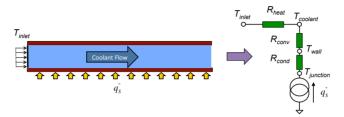

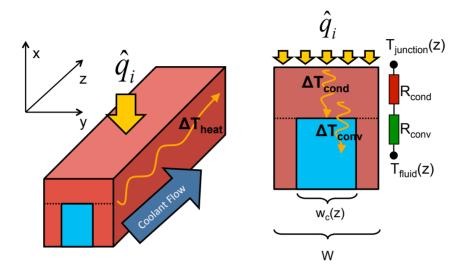

To model the thermal behavior of the target architectures, many other approaches have been proposed for this problem. For example, one dimensional methods such as [36] can be used to simplify the heat

Figure 2.3: A simple one-dimensional model for forced convective cooling in microchannels [36].

transfer problem by assuming that heat enters vertically from the silicon surface into the fluid in the microchannel via a vertical thermal resistance that combines the conduction resistance and the convective resistance at the solid-liquid interface. This is illustrated in Fig. 2.3. In order to take into account the rise in fluid temperature as it accumulates heat from inlet to outlet, another thermal resistance  $(R_{heat})$  is used to represent the sensible heat absorption connecting to the inlet of the microchannel where a constant temperature boundary condition is applied. This method, while being easy to build and solve for, oversimplifies the problem and does not account for non-uniform heat fluxes generated by the heterogenous multi-core 3D MPSoC, and the three-dimensional spreading of heat in the structure surrounding the microchannel. Hence, the applicability of this model is limited.

#### 2.3 Compact Thermal Modeling for 3D MPSoCs

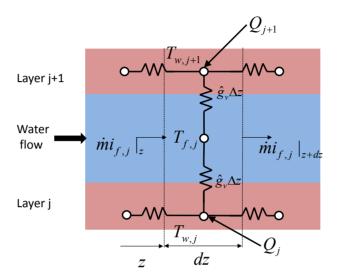

Compact thermal models for MPSoCs have been widely used in designspace thermal explorations [52] and developing thermally-aware optimization schemes [12], as they provide superior speed-ups with acceptable accuracy compared to the finite-element methods. Initial work on faster modeling approach has been conducted by Koo et al. [51]. In this modeling approach the governing heat transfer equations are employed via the finite difference method and applied to a discretized volume of the 3D ICs. The main assumption in this work is that the heat is dissipated vertically from the silicon tiers to the microchannels. As shown

**Figure 2.4:** Schematic of microchannels and implemented in a 3D circuit and thermal modeling of microchannel cooling for a 3D circuit. Only one channel is analyzed in a cooling layer by geometric and thermal symmetries. Dotted lines indicate the discretized control volume used the model [51].

in Fig. 2.4, a resistive network is generated which is governed by the following equations:

where  $q_j''$  is the applied heat flux at the jth layer,  $T_{w,j}$  and  $T_{f,j}$  are the average local temperatures of the solid wall and the fluid, respectively. The subscript (j) indicates the property of the jth layer. The pitch of microchannels (distance between two adjacent microchannels) is denoted as (p). The depth and width of the microchannel are represented as (d) and (w), respectively. The forced convection coeffi-

cient for heat transfer between the solid wall and the working fluid is  $h_{conv,j}$ . The fluid enthalpy per unit mass  $(i_f)$  is expressed in terms of local thermodynamic equilibrium fluid quality (x). The effective thermal conductivity of solid in the (z) direction is  $k_{w,z,j}$  and  $A_{w,j}$  is the effective solid cross-sectional area.  $R_{th,j}$  is the conduction thermal resistance between control points on layers (j) and (j+1) and  $\eta_0$  is the overall surface efficiency, which is employed to simplify the temperature variation in the (y) direction within the channel walls.

This work while seems promising at its publication time, has not provided any validation support to the models. Moreover, this model could only provide steady-state thermal profiles without any transient thermal behavior insights. Thus this model is indeed limited to be applied as-is for realistic 3D MPSoC thermal exploration and run-time thermal analysis and management.

To enhance the previous model, Kim et al. [53] have extended the previous model to account for lateral thermal dissipations and non-uniform heat flux distribution scenarios. This work explores several fluid inlet configurations, as well as the potential of two-phase cooling. This advancement however, is still applicable to the steady-state case.

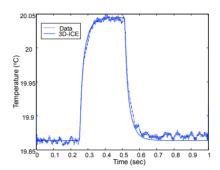

The 3D-ICE [41] compact thermal modeling framework has been proposed for transient thermal simulation of 3D MPSoCs with interlayer liquid cooling. This model has been extensively validated for accuracy against fine-grained numerical simulations as well as measurements from real liquid-cooled emulated ICs [41, 54].

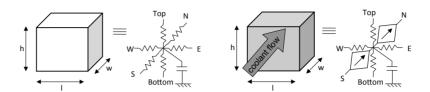

In this modeling framework, finite-difference approximations are applied to the aforementioned equations (2.2) and (2.6). When finite-difference approximation is applied to (2.2), the given volume of solid is discretized into "thermal cells" along the 3 cartesian coordinates to generate a thermal grid. Thus, electrical analogy is invoked here with the temperature represented by voltage, heat flow represented by electric current [46], the first term on the left hand side in (2.2) as a capacitor and the rest of the discretized represented as conductances, giving rise to an RC circuit [41, 45]. Then, for a given thermal cell of length l, width w and height h as shown in Fig. 2.5(a), the compact thermal model consists of six resistances representing the conduction of

**Figure 2.5:** (a) Equivalent electrical circuit for heat conduction in a solid thermal cell. (b) The 3D-ICE model for a liquid thermal cell [41].

heat in all the six cartesian directions and a capacitance representing the heat storage inside the cell.

In the case of liquid cells, the microchannel layers in the 3D MPSoC are divided into thermal cells similar to the other solid layers as described before. Next, for each thermal cell inside the microchannel, an equivalent electrical representation similar to Fig. 2.5(a) is constructed. The only difference of this cell with respect to the solid cell is the average velocity of the fluid through the cell with fluid entering from the front end and exiting from the rear end of the fluid cell as indicated in Fig. 2.5(b). Based on the discretization of (2.6) and by invoking the electrical analogy, the velocity-related term can be translated into a voltage-controlled current source in the equivalent RC circuit. These voltage controlled current sources model the transport of heat from the inlet to the outlet of the microchannel and, hence, account for the rise in temperature of the coolant as it flows through the microchannel.

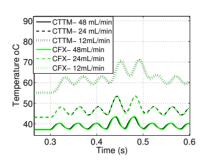

3D-ICE has been shown its accuracy when validated against the commercial computational fluid dynamics (CFD) simulation framework, i.e. Ansys CFX [50]. Simulation results show that 3D-ICE achieves peak temperature error of only 3.4% while providing 975x speed-ups when compared to CFD simulations [41] (cf. Fig. 2.6(a)). More advances show that 3D-ICE can even reach speed-ups up to 13478x with 10% peak temperature error [54]. Finally, the recent validations against a realistic test bed [55] show that 3D-ICE achieves an average error of 8.5% with respect to experimental thermal measurements of the test bed (cf. Fig. 2.6(b)).

Despite the accuracy of 3D-ICE, recent work [56] highlights the lim-

**Figure 2.6:** Validation of 3D-ICE simulations against (a) Ansys CFX CFD simulation [41]. (b) Experimental measurements of a 3D test bed [55].

itations of this tool. For instance, 3D-ICE ignores the fluid entrance and the accompanying thermo-hydrodynamic developing region. Thus, 3D-ICE tends to under-estimate the liquid-cooling thermal gradient. Moreover, 3D-ICE neglects the thermal effects of TSVs on the overall 3D-IC thermal profile. In this respect, Qian et al. propose 3D-ACME [56] a compact thermal modeling framework that takes into consideration the impact of TSVs and the microchannels entrance region. By taking these two factors, 3D-ACME manages to reduce the error with respect to finite-element methods to 0.2% which is one order of magnitude less than the error of 3D-ICE with respect to finite-element methods (4.1%). However, 3D-ACME is a steady-state modeling framework that has a higher runtime for large problem size compared to 3D-ICE. Thus, 3D-ACME cannot be used for runtime thermal monitoring of 3D MPSoCs with time-varying workload conditions.

#### 2.4 Summary

In this section, we have shown the basic heat transfer principles that are used in various thermal modeling frameworks. We have shown the thermal conduction in solids, convection and sensible heat absorption in fluids. These factors are later used in the different modeling frameworks we have shown, which are either dedicated to 3D MPSoCs or

2.4. Summary 143

generalized to various modeled platforms. We have elaborated more on the compact thermal modeling concepts of 3D MPSoCs, due to their effective utilization in various temperature-aware explorations.

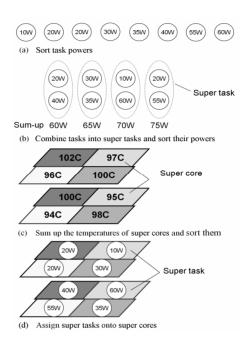

# Temperature-Aware Design Optimizations for 3D MPSoCs

The continued scaling and integration in Multiprocessor Systems-on-Chip (MPSoCs) designs have caused an increase in the power density. This increase has augmented the heat generation in MPSoCs, hence higher operating temperatures. These temperatures lead to accelerated degradation rates in various thermally-induced parametric factors [31] (cf. Section 1.3), such as electro-migration (EM) [30], biastemperature instability (BTI) [24], gate oxide breakdown [29], propagation delays [57, 58], leakage power [59], and power/ground integrity [31]. Thus, it is crucial to design these high-power density MPSoCs in a thermally-aware manner to abate the mentioned degradation factors, even before experiencing the non-homogenous time-varying workload characterizations. It is worth mentioning that these thermally-aware designs should be designed to handle two pivotal parameters, namely the overall thermal state of the system defined by peak temperatures (hot spots) and balancing the temperature distribution within the MP-SoC platform (thermal gradients).

While the mentioned thermal issues are alarmingly rising in high power-density MPSoCs, they are even more furious in the prospective vertically-stacked 3D MPSoCs [21, 12]. This is mainly due to the in-

creased and nonuniform thermal resistance at different stacked layers, based on their relative heat dissipation paths using conventional techniques such as placing heat sink on top of the top-most layer. With limited surface exposure to the heat sink, temperature in 3D MPSoCs exacerbates since the inner layers do not have a direct access to heat sink for effective heat removal.

The accompanied high temperatures of these 3D MPSoCs have triggered the research and development of design-time cooling solutions. Research directions include better heat dissipation paths such as thermal through-silicon vias (TSV) insertion [35, 60], temperature-aware floorplanning [61], and using active cooling techniques such as forced convective liquid cooling [36, 62, 63, 53] and thermoelectric cooling [64, 65] techniques.

Despite the benefits that new cooling technologies bring to 3D MP-SoCs, these techniques can bring additional challenges if not optimized properly. Moreover, if these techniques are applied to arbitrary 3D MP-SoC architectures, without any temperature-aware consideration, several resources such as cooling energy can be over-utilized. Thus, it is crucial to optimize, at design-time several temperature-related features of 3D MPSoCs, which has been already performed in literature through several directions and approaches.

In this Section we provide a detailed state-of-the-art review on the design-time optimization techniques of 3D MPSoCs that target thermal attenuation and balancing. At the outset, temperature-aware design optimization can be classified to mechanisms that optimize the heat generation and the flow in the 3D MPSoC, and techniques that optimize the heat dissipation paths from the 3D MPSoC to the surrounding environment. In this review, we refer to these mechanisms as on-chip and off-chip design-time optimizations, respectively. We start by the on-chip optimization mechanisms in Section 3.1. Then, we explore the off-chip optimization mechanisms in Section 3.2. Finally, we summarize the contents in Section 3.3.

#### 3.1 On-Chip Design-Time Optimizations

The first category we elaborate in this survey is related to the heat generation and dissipation patterns inside the 3D MPSoC, hence the term on-chip optimization. It is important to mention that this exploration does not include how the heat is removed from the target system. In the case of targeted 3D MPSoCs, on-chip design optimization can be classified to the following categories. The first category is related to the heat generation of each computational module. This can be optimized either by the way the modules are designed or utilized. The second category elaborates the thermal impact different modules have on each other, which we refer to as on-chip heat dissipation. Please note that this category is different from off-chip heat dissipation as the former category is related to the intra-chip heat dissipation inside the 3D MP-SoC, while the latter category is concerned with the inter-chip heat dissipation between the 3D MPSoC and the surrounding environment. In the following subsections, we explore the state-of-the-art works that belong to the mentioned categories.

#### 3.1.1 Heat Generation Optimization

Power, or heat, generation in computing systems can be adjusted at design-time to prevent reaching any thermally-based critical situation. Since computing systems design is defined by the target platform architecture and application characteristics, addressing the power (or heat) generation at design-time can be split between techniques that are applied at the *platform* level and techniques that are applied at the *application and mapping* level. These general trends can be followed in 2D and 3D MPSoC design optimizations. Thus, we demonstrate the state-of-the-art in these directions in the case of both planar 2D and 3D MPSoCs.

**Platform Oriented** At the platform level, different modules can be designed to reduce the overall power density, hence heat generation, while preserving the system functionality. This approach has been taken recently in low-power (hence low temperature) processor designs such as

ARM big.LITTLE processing architecture [66]. Another approach at the platform level is to reduce the operating power supply of the platform to near-threshold values [17]. Near-threshold computing allows the processing units to operate close to the voltage threshold value of the used transistor, hence reducing the overall power and thermal density.

In the case of 3D MPSoCs, recent work proposes multiple supply voltages utilization to optimize the voltage islands distribution in 3D MPSoCs [67]. In this work, a temperature-aware voltage island generation methodology is proposed that formulates this problem as a mixed-integer linear programming (MILP) problem. The main aim in this work is to minimize the thermal hot spots in 3D MPSoCs while keeping the performance and timing requirements satisfied. The interdependency between power and heat densities made it feasible to formulate this problem and achieve significant results.

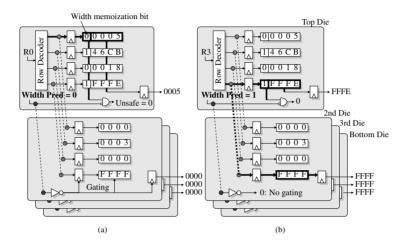

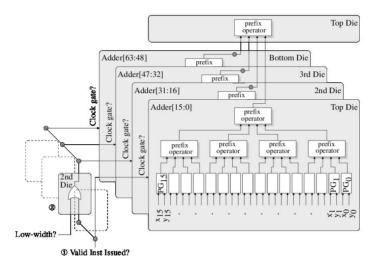

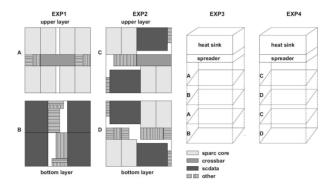

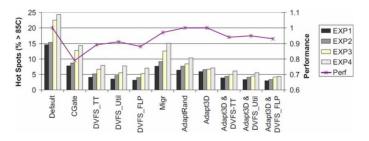

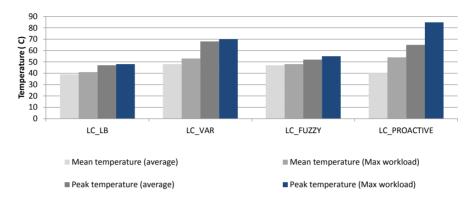

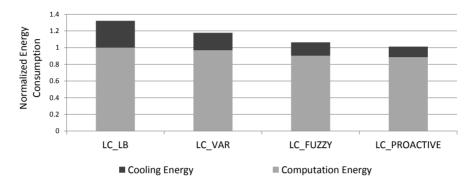

Another work utilizes various microarchitectural techniques to control the thermal hot spots in 3D MPSoCs via thermal herding [68]. This technique explores different architectural disciplines by splitting several microarchitectural blocks between the different layers of 3D MPSoC to enhance the throughput while controlling the thermal hot spots such as register file and integer adder splitting, as shown in Fig. 3.1 and Fig. 3.2. This splitting is based on general application trends and the significance of particular instructions or data locations to the execution flow. When thermal herding is applied to a 2-tier 3D MPSoC, significant enhancement in the performance figures is obtained when compared to conventional 3D integration, by 51% mean performance improvements. This performance improvement is accompanied with 12% power savings, with 5K peak temperature reduction.

Application and Mapping Oriented In addition to platform level techniques, the operating applications can be designed to alleviate the heat generation of the processing unit. For example, recent work [69] distributes the idle time between the tasks running on the same processing unit to allow for a cool-down period between running tasks. This work applies a distribution time heuristic and non-linear program-

Figure 3.1: Thermal Herding in register files: examples where (a) a low-width value only requires circuit activity on the top die, and (b) a full-width value requiring reading state from all four die [68].

ming to optimize the idle time placement. Other work [70] proposes a pseudo instruction scheduling technique for VLIW processors that maps parallel instructions to the coolest functional units, and gives for each instruction a possible list of thermally-inactive functional units for temperature reduction.

#### 3.1.2 On-Chip Heat Dissipation Optimization

As mentioned earlier, this subclass achieves thermal reduction via intra-MPSoC (or inter-module) heat dissipation adjustments. Such adjustments can be done at the **platform level**, where the microarchitecture of the MPSoC (2D and 3D) modules and the accompanying middle-ware have major impact on the heat flow and propagation of the target architecture. Additionally, the adjustment of heat flow can be managed by **application level** customizations, both algorithmic and mapping, such that the application impact on heat spreading is minimized.

Figure 3.2: Thermal Herding in an integer adder with the most active least significant bits placed on the top die [68].

Platform Level . Previous works have investigated the rearrangement of various hardware modules within the MPSoC to minimize the global thermal impact, which is also known in literature as temperature-aware floorplanning. Initial work on temperature-aware floorplanning [71] has shown its significant impact on reducing the peak temperature. This work has defined a metric called thermal diffusion that resembles the lateral heat dissipation. This metric has been used in an optimization problem to maximize the gains of thermal diffusion. Other similar works have proposed simulated annealing utilization [72] or genetic algorithms [73] to achieve temperature-aware floorplanning.

In the context of 3D MPSoCs, temperature-aware floorplanning has also been extended by including the interlayer thermal dissipation and interconnect characteristics [74, 72, 75, 61]. For example, initial work has been proposed [76] for temperature-aware microarchitectural floorplanning. The main objective in this work is to place the processing submodules of a single processor in several layers such that the wire lengths and the temperatures are minimized. To achieve this, a mixed integer linear programming (MILP) problem is formulated to minimize the weighted sum of performance, area and thermal-related aspects.

**Figure 3.3:** Power profile of two layered (a) microchannel cooled and (b) conventional air cooled 3-D ICs with thermal aware placement [52].

Results show that this floorplanning approach reduces the peak temperature by 24% when compared with performance-driven floorplanning approach. Another work uses simulated annealing to minimize the temperature of 3D MPSoC via floorplanning [75] by considering the additional power consumption of the interconnects.

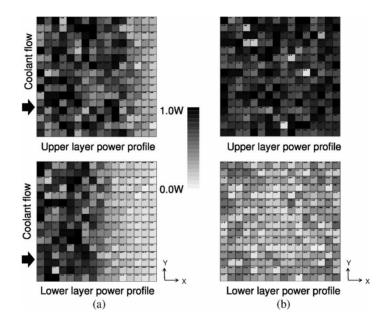

As for liquid-cooled 3D MPSoCs, Mizunuma et al. use their thermal model to explore floorplanning solutions [72] to homogenize temperature distributions in this architecture [52]. In particular, this work explored the impact of the Polish expressions-based, simulated annealing (SA) thermal placer [72] on the allocation of modules in liquid-cooled 3D MPSoCs. The results in this work, which is further assisted by the observations in other work [38], show that in the case of liquid cooled 3D MPSoC, temperature-aware floorplanning follows the trend of placing more heat dissipating modules at the fluid inlet port, while lower heat dissipating modules at the outlet port, which is different than the

**Figure 3.4:** Temperature profile of two layered liquid-cooled 3-D ICs with (a) random and (b) thermal aware placement [52].

case of air cooling as shown in Fig. 3.3. In other words, the optimal heat dissipation pattern for temperature-aware floorplanning would be monotonically decreasing from the distance of the fluid inlet port, which would generate the optimal thermal map as shown in Fig. 3.4.

Application Level. The application mapping to a specific MPSoC has a significant impact on the corresponding thermal behavior. This mapping can be performed at design-time, where several temperature-aware compilation schemes have been proposed. Previous work [77] proposes register file reallocation technique for VLIW processors to homogenize the resulted temperature distribution within a VLIW processor. This work uses register renaming and variable live range splitting to achieve uniform thermal distribution. In addition, other work on thermally-aware register file utilization [78] targets the homogenous use of register window-based processing architectures. This work vir-

tually splits the application to a number of smaller sub-applications, where each sub-application is assigned to a different register window for better thermal dissipation. This work manages to reduce the peak temperature by 11% and the thermal gradient by 38%. While this research branch has shown its effectiveness in the case of planar 2D MPSoCs, it is yet to be explored for 3D MPSoCs.

# 3.2 Off-Chip Design-Time Optimizations

Off-chip optimizations primarily target the customization of heat dissipation paths of the different tiers in 3D MPSoCs to the heat sink layer(s). Significant research efforts have been invested to find techniques that aid in heat removal (also referred by vertical dissipation) from the 3D MPSoC. In the context of this survey, heat removal is defined as dissipating the local generated heat of a certain module to the surrounding environment outside the 3D MPSoC. These techniques aid in better heat removal by providing better means of thermal dissipation without any external effort (power) requirements, which is referred to in this text by *Passive* heat removal techniques. Alternatively, heat removal can be enforced by the use of *Active* techniques, where an external effort (power) and medium are required to enhance this off-chip heat dissipation. Typical examples of active cooling mechanisms involve liquid [36] and thermoelectric [65] cooling methods, while passive cooling examples include thermal through-silicon vias (TTSVs) [35].

#### 3.2.1 Passive Heat Dissipation Optimization

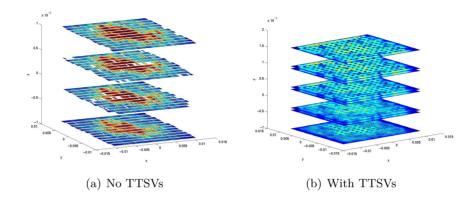

Prior work related to this category has investigated using new materials, with better thermal properties than silicon, in the fabrication process. For example, Carbon nanotubes [79] and Graphene [80, 81] are recently proposed materials to be used in the transistor fabrication, which are characterized by high thermal conductivity values. Another approach introduces other passive elements in the ICs. Particularly, thermal through-silicon-vias (TTSVs) [60, 35, 82] have been recently proposed to alleviate the corresponding thermal issues for 3D MPSoCs. Thermal TSVs provide a good thermal conducting medium to transfer

Figure 3.5: The thermal profile of multi-tier 3D IC with and without TTSVs [82].

the generated heat from the lower layers to the heat sink for an overall better thermal performance.

An early work on thermal vias insertion and optimization has been performed [82]. This work has used an iterative method of TTSVs insertion while deducing the resulted thermal state by finite-element analysis. The resulted thermal vias density determines the thermal conductivity of the surrounding region. Results have shown the significant temperature enhancement with the TTSV insertion. As shown in Fig. 3.5, this work manages to significantly reduce the 3D IC thermal profile by up to 47.1% while incurring 1.19% area overhead for TTSVs occupation.

Previous work [35] proposes the optimization of the thermal TSVs (TTSVs) locations both horizontally and vertically in 3D MPSoCs. This work formulates the horizontal placement of TTSVs as a constrained nonlinear programming problem, while providing a fast solving heuristic for this formulation. This formulated heuristic achieves near-optimal solution (within 1% deviation from the optimal one) while achieving 200x solution time speed-ups. In addition, this work formulates the vertical placement of TTSVs as a convex optimization problem, hence guaranteeing a global minimization of the vertical heat dissipation from the lower layers to the heat sink. This work manages to reduce the TTSV density demand to satisfy a certain thermal constraint by 68%

Figure 3.6: Temperature distribution of 3D-IC top layer [35].

compared to the state-of-the-art [74], with significant reduction in the thermal profile as demonstrated in Fig. 3.6.

Another work [83] uses the previous algorithm and combines it with another optimization problem that targets whitespace redistribution to optimize further the TTSV insertion, with better heat dissipation properties and reduced performance degradation. This work deduces the TTSV requirements for each block and uses this deduced information to formulate a linear programming problem to distribute the whitespace in the targeted 3D MPSoC to meet the TTSVs requirements. This optimization is also combined with performance requirements as another objective.

Temperature-aware routing of lateral thermal wires and vertical thermal vias has been proposed [84]. This work adds the utilization of lateral thermal wires, which are signal non-carrying wires thus have no electric functionality. These thermal wires utilize the residual routing tracks from signal wires routing to distribute the heat more evenly in 3D MPSoCs. Thermal wires provide direct connectivity to vertical thermal vias for more heat dissipation capabilities. The insertion of thermal vias and wires in this work has been formulated as a linear programming problem to minimize the temperature of thermal hot spots, while using the minimal thermal vias and wires.

Another recent work studies the impact and utilization of power

distribution networks (PDN) to remove the generated heat in 3D MP-SoCs [85]. This work shows that power distribution network populated with interlayer vias can aid significantly in reducing the temperatures of 3D MPSoCs and monolithic 3D ICs. Significant thermal reductions are observed that can enable various dies of a 3D MPSoC to operate at higher power density figures while keeping the thermal constraints.

#### 3.2.2 Active Heat Dissipation Optimization

In some cases where passive techniques are not sufficient, active cooling methodologies provide the required support. A typical example in active cooling techniques is injected air cooling [86]. Forced air cooling injects air at different volumetric flow rates through the mounted heat sink to augment the convective heat transfer between the hot plate and the surrounding environment. Thermoelectric cooling is another active technique that removes the heat from the IC by using a series of actively-connected devices on top of the target IC [65]. When these devices are electrically active, they transfer the heat from the IC to the surrounding environment using the *Peltier effect*. Other active techniques involve cooling the targeted computing system by fluids, single or two-phase. For example, a recent cooling methodology proposes using hot water to cool-down server processing units [87], which is now deployed in the AQUASAR data-center. More recent research efforts propose interlayer liquid cooling for 3D MPSoCs [36], where a single phase coolant is injected in silicon-etched microchannels within the integrated layers. This injection causes the forced convective heat transfer from the processing elements to the coolant. This methodology is being extended to incorporate two-phase cooling [88], where the fluid phase change absorbs significant thermal energy values, hence cooling down the target 3D MPSoC. Additional research efforts have investigated micro pin-fin structures [89, 90] for enhanced single-phase fluid cooling potential. While these active cooling mechanisms are shown to be effective in heat removal, these techniques can be over utilized, hence resulting in resources (e.g. energy) inefficiency. In this respect, active cooling mechanisms require design optimization for their efficient application.

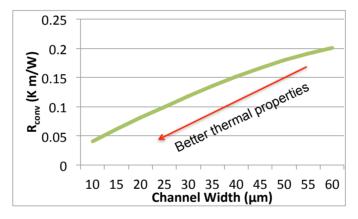

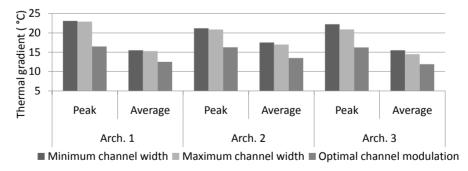

Figure 3.7: Potential locations of micro-channels: (a) uniform spreading, (b) non-uniform spreading [94].