provided by Infoscience - École polytechnique fédéra

brought to you

ata, citation and similar papers at core.ac.uk

##

# **IETE Journal of Research**

Volume 58 • No. 3 • May-June 2012

www.ietejournals.org Subscriber Copy : Not for Resale

### **RF Compact Modeling of High-voltage MOSFETs**

Antonios Bazigos, François Krummenacher, Jean-Michel Sallese, Matthias Bucher<sup>1</sup>, Ehrenfried Seebacher<sup>2</sup>, Werner Posch<sup>2</sup>, Kund Molnár<sup>2</sup> and Mingchun Tang<sup>2</sup>

Ecole Polytechnique Fédérale de Lausanne, CH-1015, Ecublens, Switzerland, <sup>1</sup>Technical University of Crete, 73132 Chania, Greece, <sup>2</sup>Austriamicrosystems AG, 8141 Unterpremstaetten, Austria

#### ABSTRACT

The High-Voltage MOSFET is used in a wide variety of applications covering from power systems up to RF-IC. Compact models that describe the high-frequency behavior of the device are required to predict high-frequency operation and switching capabilities of these elements in HV state-of-the-art systems. In this paper, an RF model is presented and verified against extensive Y-parameter measurements, which were carried out on a long channel Lateral double-Diffusion MOS device. Assessment of the model with measurements confirms the validity of this approach.

#### Keywords:

Drift region, High-frequency regime, High-Voltage MOSFET, HV-MOS, LDMOS, Physics-based analytical compact model, RF.

#### 1. INTRODUCTION

The importance of the High-Voltage (HV-MOS) as a device in state-of-the-art applications has been reported extensively in scientific literature [1-5]. One of the reasons is that modern HV-MOS devices, like Lateral double-Diffusion MOS (LDMOS), may be integrated together with low-voltage modules in CMOS processes [3,5]. The systems, where such devices are used, range from power components for automotive and consumer products [2] up to radio frequency applications [6-8]. Therefore, compact modeling of HV-MOS is an enabling factor that will help in predicting how these devices can be optimally integrated in complex architectures [9-26]. More particularly, the RF characterization and modeling of HV-MOS should receive extra attention since the high-frequency behavior is, still, a quite demanding and challenging issue. The results presented here are a continuation of a previous work that has already been published [27].

#### 2. MODEL DESCRIPTION

The structure of an HV-MOS, if simplified, may be regarded as the in series combination of two simpler elements. On one side lays the low-voltage part which closely resembles to a classical MOSFET, except for the relatively high longitudinal doping gradient across the channel [9,27]. On the other side, beyond the inner drain of the low-voltage part there is the high-voltage section which protects the low-voltage MOSFET from excessively high potentials. This part, also called drift region, has the same type doping as the outer drain and source of the HV-MOS. Its quite long extension, i.e., a few

microns, ensures safe operation needed for the device to function at dozens of volts [26].

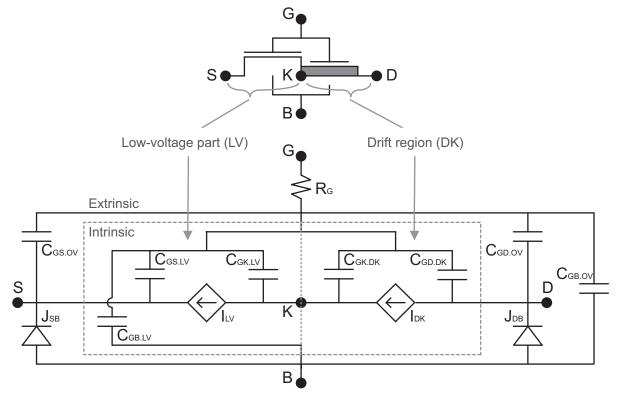

The compact model used in this work takes advantage of the above simplification, describing the whole structure as a macromodel of two basic elements. The connection of these two elements takes place at a node called the K-point, which is, in physical terms, the metallurgical junction point where the doping profile changes its type, between the channel of the low-voltage part and the drift region [14,25]. In order to model the device at RF, additional extrinsic components must be added. Among them, there are a gate resistance and two asymmetrical junction diodes between the source and the drain terminals and the substrate. In addition, it has been observed that overlap capacitances between the gate and other nodes are not negligible. These overlap capacitances become even more important for specific small geometries.

The elements of the intrinsic part of the model can be considered as a small signal equivalent network built upon transcapacitances and current sources. For the core of the model, and omitting higher order effects like impact ionization current, the low-voltage part of the device can be represented by three transcapacitances between the gate and other nodes, and a current source between the K-point and the source node. In addition, a similar representation can de adopted for the drift region. Here, again a current source is needed between the outer drain and the K-point, and also two transcapacitances, one between the gate and the K-point that describes the charge behavior of the carriers just below the oxide, and one more between the gate node and the outer drain, which accounts for the charges laying in the rest of the drift region. This is sketched in the small signal equivalent circuit schematic of Figure 1.

#### 2.1 Dynamic Charge Behavior of the Drift Region

The dynamic behavior of the low-voltage part of the device including a MOSFET with lateral non-uniform doping is analyzed in [9,28-30], while a detailed analysis of the charge has been discussed in [27]. In this article, the discussion on the dynamic behavior of the HV-MOS devices will be pursued by giving a transcapacitance representation of the charges in the drift region.

Considering the charge-sheet approximation [31], the charge of the drift region may be considered as the sum of two components. The first component  $(q_k)$  is the charge accumulated just below the thin oxide and has been analyzed in [27]. If  $W_{DK}$  and  $L_{OV,DK}$  are the width and the effective gate length overlap the drift region, respectively, and  $T_{OX}$  is the effective thickness of the thin oxide above the drift region, then the total charge at the K-point is calculated from:

$$Q_{K,DK} = \frac{\varepsilon_{OX} \cdot W_{DK} \cdot L_{OV,DK}}{T_{OX}} \cdot q_{k'}$$

(1)

Where,  $\varepsilon_{OX}$  is the permittivity of the oxide, and  $q_k$  and  $Q_{K,DK}$  are respectively the normalized and absolute charge densities [32].

On the other hand, the sum of the charge in the drift region will be equal (in absolute value and opposite in sign) with the charge that will accumulate at the gate node ( $Q_{G,DK}$ ). If  $Q_{D,DK}$  denotes the charge at the inner part of the drift region, we get:

$$Q_{G.DK} = -(Q_{K.DK} + Q_{D.DK}).$$

<sup>(2)</sup>

Note that  $Q_{G,DK}$  stands only for the part of the gate charge that is connected with the drift region, and does not represent the whole charge of the gate node. This charge may be calculated after the following equation.

$$Q_{G,DK} = \frac{\varepsilon_{OX} \cdot W_{DK} \cdot L_{OV,DK}}{T_{OX}} \cdot \left( V_G - V_{FB,DK} - \Psi_K \right). \quad (3)$$

In the above equation,  $V_{FB,DK}$  denotes the Flat-Band voltage of the drift region and the  $\Psi_{K}$  is the surface potential at the K-point. The latter is calculated from the potential of the internal node of the K-point ( $V_{K}$ ), which is evaluated considering the continuity of the current at the K-point [27]. Therefore, the above set of equations form the core of the model for the dynamic behavior of the drift region.

Figure 1: Small Signal equivalent circuit of the macromodel for the HV-MOS. The intrinsic and extrinsic parts are shown, while the intrinsic part is further divided into the low-voltage part and the drift region. For the intrinsic part, transcapacitances and current sources are used, while the extrinsic part consists of junction-diodes, resistors, and capacitors.

#### 3. COMPARISON WITH MEASUREMENTS

The model has been verified against numerical simulations of Technology Computer-Aided Design (TCAD) tools and real measurements [27]. Few selected results will be presented in this section in order to demonstrate its capabilities. For this purpose, an LDMOS device has been chosen with a minimum gate length of L = 500 nm. The gate width is W = 40  $\mu$ m, while the thickness of the oxide is T<sub>ox</sub> = 15 nm in order to withstand a gate potential up to 5 V.

#### 3.1 Static Current Aspects

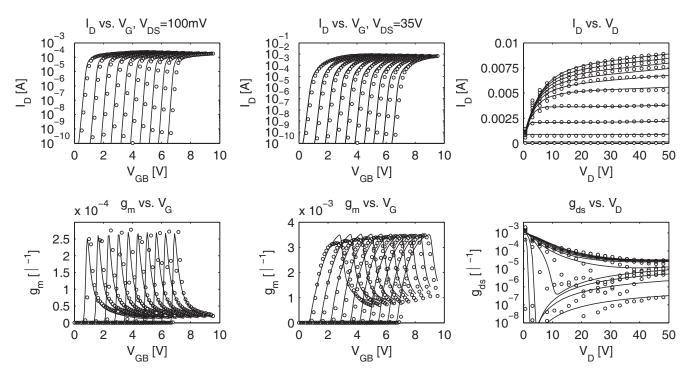

In Figure 2, a comparison between the model and measurement for various static current conditions is presented. The model shows good capabilities under all bias conditions. The device's behavior is more complicated than the classical MOSFET case since there is a continuous balance between the two parts of the device that sets the quasi-fermi potential of the K-point. In principle, it could be said that for low gate potential, when the channel of the low-voltage MOSFET of the device is in weak inversion, the overall device acts similarly to a classic MOSFET having a resistive load at its drain. As the inversion level increases and the low-voltage part gets deeper in strong inversion, more and more carriers can be provided to the drift region. Under

these bias conditions, it is the drift region that will govern the overall behavior of the device, especially for high  $V_{\rm DS}$  values, and the device differentiates importantly from the classic MOSFET.

#### 3.2 Dynamic Behavior Analysis

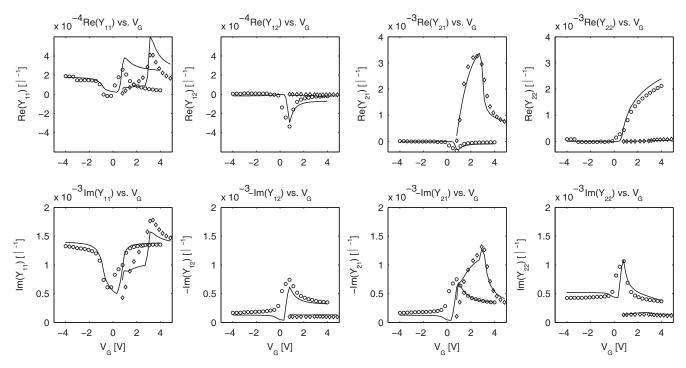

In order to validate the model according to its dynamic behavior, the LDMOS device was also measured at high frequencies. Considering the device as a twoport network, where the input (port 1) is between gate and source, and the output (port 2) is between drain and source (which is connected to the ground), S-parameter measurements were performed up to 6 GHz. The measurements were done under various bias conditions. When  $V_{DS}$  was zero, the gate potential varied between -4V and 4V, while with positive  $V_{DS}$ the gate potential swept between 0.8V and 4.8V. The S-parameters were transformed to Y-parameters, which are better suited for the voltage-to-current terminology already used in static analysis. Figure 3 shows some selective results of the above measurements for a specific frequency, f = 1.2 GHz, displayed along with the simulation obtained from the model. The model covers adequately the high-frequency behavior of the device under an extended range of bias conditions providing good results in terms of Y-parameters for all modes of operation.

Figure 2: Static current measurements (markers) and model behavior (lines) of an LDMOS (L=500 nm, W=40  $\mu$ m, TOX=15 nm). The two plots on the left are an  $I_p$  vs.  $V_g$  analysis with a low value for  $V_{ps}$ =100 m and for various VSB values between 0V and 4.5V. The two plots in the middle repeat the same analysis with high value for  $V_{ps}$ =35 V. The two plots on the right illustrate and  $I_p$  vs.  $V_p$  where  $V_{ss}$ =0V and  $V_{gs}$  ranges between 1V and 5.5V. The upper graphs show the current while the lower either the transconductance, gm for the analyses  $I_p$  vs.  $V_{gr}$  or the output conductance, gds, for the  $I_p$  vs.  $V_p$  analysis.

Figure 3: Y-parameters, in real and imaginary part, of an LDMOS device with geometric parameters of L=500 nm, W=40  $\mu$ m, and  $T_{ox}$ =15 nm. The markers ( $V_{os}$ =0V:  $\circ$  and  $V_{os}$ =30V:  $\diamond$ ) are for measurements while the lines are the model's behavior. Port 1 is gate-to-source and port 2 is drain-to-source, and  $V_{ss}$ =0V. The results are shown for frequency f=1.2GHz.

#### 4. EXTRINSIC NETWORK AND RF PARAMETER EXTRACTION

In this section, a short analysis on the parameter extraction procedure will be discussed. It shall be focused on the extraction of the parameters related to the extrinsic part of the device which may benefit from the highfrequency analysis of the device [33-36]. Although the core of the following techniques is based on the classic MOSFET, it shall be shown that there is enough space for its application to HV-MOS devices.

#### 4.1 Gate Resistance

By analyzing the small signal equivalent circuit, and its functionality under small signal conditions, the gate resistance can be estimated by the following equation [33,37].

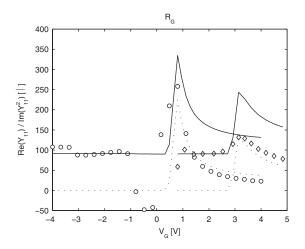

$$R_{\rm G} = \frac{{\rm Re}(Y_{11})}{{\rm Im}(Y_{11})^2} \,. \tag{4}$$

In Figure 4, the estimation of the gate resistance is plotted against the gate potential for the LDMOS device under test. The extraction of the value of the gate resistance is best performed under negative gate bias conditions and with  $V_{DS} = 0V$ , since this bias minimizes the influence of the rest of the device. For the simulations shown here, a value of 90 $\Omega$  has been used for  $R_G$  which is very close to the estimation of (4) for low enough values of the gate

Figure 4: The Gate Resistance ( $R_{G}$ ) as estimated by (4) under various bias conditions with  $V_{SB}$ =0V and f=1.2 GHz, for an LDMOS device with L=500 nm, W=40 µm and  $T_{OX}$ =15 nm. Markers stand for measurements ( $V_{DS}$ =0V:  $\circ$  and  $V_{DS}$ =30V:  $\diamond$ ), while lines are model simulations. The accurate value of the resistance is best extracted under negative gate bias and zero drain-to-source difference potential, as these conditions minimize the influence of the rest of the device. Here, the RG used for the model is 90 $\Omega$ . The dotted line is for the simulation of the model minimizing the gate resistance.

potential. These results verify that this equation is valid for the HV-MOS devices as well.

#### 4.2 Capacitances

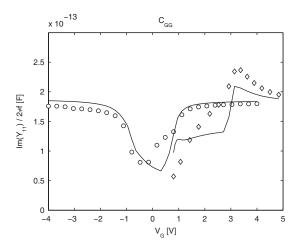

Viewing the transistor as a two-port network, the imaginary parts of the Y-parameters hold information on the capacitances and the transcapacitances of the devices. This way, the following equation, which contains  $Im(Y_{11})$ , can be used as an estimation of the capacitance seen from the gate node, meaning the total gate capacitance.

$$C_{\rm GG} = \frac{\rm Im(Y_{11})}{2\pi f} \,. \tag{5}$$

In Figure 5, an estimation of the total gate capacitance is shown against the gate potential. The profile resembles to the classical MOSFET one, where the regions of operation of the device according to the gate potential are well separated, especially for the  $V_{\rm DS}$  = 0V case. For the lowest values of the gate potential, the gate capacitance is maximized as the device works in accumulation. As the gate potential increases, the area below the thin oxide gets depleted and the device enters in depletion. Further increment of the gate potential leads to an inversion layer where the total gate capacitance reaches again its maximum value [38]. Under a positive  $V_{DS'}$  the device shows some clear deviation with respect to corresponding basic MOSFET device. Due to Miller effect, the total gate capacitance exceeds the maximum expected and exhibits a different shape [9].

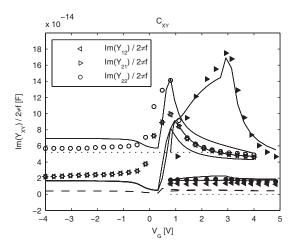

The rest of the Y-parameters can be used in order to extract information on the extrinsic capacitances, see Figure 6. These can be obtained from the following relationships.

$$C_{\rm GD} = \frac{\rm Im(Y_{12})}{2\pi f},$$

(6)

$$C_{\rm DG} = \frac{\rm Im(Y_{21})}{2\pi f},$$

(7)

$$C_{\rm DD} = \frac{\rm Im(Y_{22})}{2\pi f} \,. \tag{8}$$

Similarly, to the total gate capacitance, the  $Im(Y_{22})$  represents the capacitance of the device seen from the drain node. A major component of  $C_{DD}$  is the junction diode capacitance. On the other hand, one can see that at low and negative gate potentials, the estimations of  $C_{GD}$  and  $C_{DG}$  coincide. By inspection of the equivalent small-signal circuit,  $C_{DD}$  may be regarded as the sum of the extrinsic overlap capacitance between the gate and the drain ( $C_{GD OV}$ ) with the gate-to-drain capacitive

load of the drift region. If this sum is substracted from  $C_{DD}$ , under the same bias conditions, the rest holds for the drain-to-substrate parasitic junction diode ( $C_{J}$ .  $_{DB}$ ) capacitance. Again, these parasitic elements are magnified for negative gate biases, where the channel does not influence the overall behavior of the device. Note that, under positive  $V_{DS}$ , the reciprocity between these two transcapacitances breaks down due to the saturation of the device from the drain side.

Figure 5; Total Gate Resistance ( $C_{GG}$ ) as estimated by (5), under various bias conditions with  $V_{SB}$ =0V and f=1.2 GHz, for an LDMOS device with L=500 nm, W=40  $\mu$ m, and  $T_{OX}$ =15 nm. Markers stand for measurements ( $V_{DS}$ =0V:  $\circ$ ) and  $V_{DS}$ =30V:  $\diamond$ ), while lines are model simulations.

Figure 6: Various capacitances and transcapacitances as estimated by (6), (7), and (8), under various bias conditions with  $V_{SB}$ =0V and f=1.2 GHz, for an LDMOS device with L=500 nm, W=40 µm, and  $T_{OX}$ =15 nm. The non-filled markers stand for measurements with  $V_{DS}$ =0V and the filled markers for  $V_{DS}$ =30V, while the lines show the model simulation. The dotted lines represent the contribution of the junction diode capacitance to  $C_{DD}$ , while the dashed lines stand for the contribution of the extrinsic, gate-to-drain, overlap capacitance to  $C_{DD}$ .

#### Table 1: Analysis parameters

| Parameter           | Value   | Description/Comments                                                              |

|---------------------|---------|-----------------------------------------------------------------------------------|

| T <sub>ox</sub>     | 15 nm   | Thickness of the gate oxide                                                       |

| W                   | 40 µm   | Drawn gate width of the device                                                    |

| L                   | 500 nm  | Nominal gate length of the device                                                 |

| L <sub>eff.LV</sub> | 1.2 µm  | Effective gate length of the device <sup>1</sup>                                  |

| L                   | 120 nm  | Effective overlap length of the drift region <sup>1</sup>                         |

| V <sub>FB.DK</sub>  | -350 mV | Flat-Band Voltage of the Drift Region <sup>1</sup>                                |

| R <sub>g</sub>      | 90 Ω    | Scalable gate resistance <sup>2</sup>                                             |

| C <sub>J.DB</sub>   | 50 fF   | Scalable bias-depended junction diode capacitance <sup>2,3</sup>                  |

| $C_{gd.ov}$         | 3.5 fF  | Scalable bias-depended overlap gate-to-drain extrinsic capacitance <sup>2,3</sup> |

| C <sub>gd.dk</sub>  | 13.5 fF | Scalable bias-depended gate-to-drain drift region capacitance <sup>2,3</sup>      |

|                     |         |                                                                                   |

$^1\text{Model}$  fitting parameter.  $^2\text{Value}$  for the specific geometry.  $^3\text{Value}$  under zero bias conditions

Table 1 displays the related models parameters used for the above analyses.

#### 5. CONCLUSION

Compact modeling of High-Voltage MOS devices is critical and merits a careful analysis at RF. In this work, we present an RF HV-MOS model along with its core equations that provides good results up to the GHz range of frequency. Further analysis of the dynamic behavior of the HV-MOS verifies the adequacy of the foundations of our RF model in terms of equivalent circuit built upon passive elements.

#### 6. ACKNOWLEDGMENT

The research leading to these results has received funding from the European Community's Seventh Framework Programme (FP7/2007-2013) under grant agreement N°218255.

#### REFERENCES

- R A Bianchi, C Raynaud, F Blanchet, F Monsieur, and O Noblanc, "High voltage devices in advanced CMOS technologies", in *Custom Integrated Circuits Conference*, 2009. CICC '09. IEEE, vol. 1, pp. 363-70, Sep. 2009.

- J A van der Pol, A W Ludikhuize, H G Huizing, B van Velzen, R J Hueting, and J F Mom, et al., "A-BCD: An economic 100V RESURF silicon-on-insulator BCD technology for consumer and automotive applications", in Power Semiconductor Devices and ICs, 2000. Proceedings. The 12<sup>th</sup> International Symposium on, pp. 327-30, 2000.

- G Toulon, I Corts, F Morancho, E Hugonnard-Bruyre, B Villard, and W Toren, "Design and optimization of high voltage LDMOS transistors on 0.18um SOI CMOS technology", *Solid-State Electronics*, Vol. 61, no. 1, pp. 111-5, 2011.

- J Ma, and L Yang, "High-voltage MOSFET modeling and simulation considerations", in *Solid-State and Integrated-Circuit Technology*, 2008. ICSICT 2008. 9<sup>th</sup> International Conference on, pp. 280-3, Oct. 2008.

- M Gross, M Stoisiek, T Uhlig, C Ellmers, and F Furnhammer, "Lateral HV-MOS transistors (50V) for integration in a 0.18 um CMOSprocess", in *Solid State Device Research Conference, 2007. ESSDERC* 2007. 37th European, pp. 179-82, Sep. 2007.

- P Wilson, "A novel high voltage RF vertical MOSFET for high power applications", in EDMO 2002: 10<sup>th</sup> IEEE International Symposium on Electron Devices for Microwave and Optoelectronic Applications, Manchester, England, pp. 95-100, Nov. 2002.

- H M Nemati, C Fager, M Thorsell, and H Zirath, "High-efficiency LDMOS Power-amplifier design at 1 GHz using an optimized transistor model", *Microwave Theory And Techniques, IEEE Transactions on*, Vol. 57, no. 7, pp. 1647-54, Jul. 2009.

- W J Hwang, S W Shin, G W Choi, H J Kim, and J J Choi, "2.46 GHz solidstate high-power oscillator with planar cavity resonator", in *Microwave Conference, 2008. APMC 2008. Asia-Pacific*, pp. 1-4, Dec. 2008.

- Y S Chauhan, F Krummenacher, R Gillon, B Bakeroot, M J Declercq, and A M Ionescu, "Compact modeling of lateral nonuniform doping in high-voltage MOSFETs", *Electron Devices, IEEE Transactions on*, Vol. 54, no. 6, pp. 1527-39, Jun. 2007.

- A Canepari, G Bertrand, A Giry, M Minondo, F Blanchet, and H Jaouen, et al., "LDMOS modeling for analog and RF circuit design", in Solid-State Device Research Conference, 2005. ESSDERC 2005. Proc. of 35<sup>th</sup> European, pp. 469-72, Sep. 2005.

- Y S Chauhan, R Gillon, B Bakeroot, F Krummenacher, M Declercq, and A M Ionescu, "An EKV-based high voltage MOSFET model with improved mobility and drift model", *Solid-State Electronics*, Vol. 51, no. 11-12, pp. 1581-8, 2007, special Issue: Papers Selected from the 36<sup>th</sup> European Solid-State Device Research Conference - ESSDERC'06.

- S F Frere, P Moens, B Desoete, D Wojciechowski, and A J Walton, "An improved LDMOS transistor model that accurately predicts capacitance for all bias conditions", in *Microelectronic Test Structures*, 2005. ICMTS 2005. Proceedings of the 2005 International Conference on, pp. 75-9, Apr. 2005.

- Y S Chauhan, "Compact modeling of high voltage MOSFETs", (No. 3915) Ph.D. dissertation, Lausanne: Ecole Polytechnique Fédérale de Lausanne, Dec 2007.

- C Anghel, "High voltage devices for standard MOS Technologies - Characterisation and Modelling", (No. 3116) Ph.D. dissertation, Lausanne: Ecole Polytechnique Fédérale de Lausanne, Oct. 2004.

- A C Aarts, and W J Kloosterman, "Compact modeling of high-voltage LDMOS devices including quasi-saturation", *IEEE Transactions on Electron Devices*, Vol. 53, no. 4, pp. 897-902, Apr. 2006.

- A Aarts, N D'Halleweyn, and R van Langevelde, "A surfacepotential-based high-voltage compact LDMOS transistor model", *IEEE Transactions on Electron Devices*, Vol. 54, no. 5, pp. 999-1007, May 2005.

- H J Mattausch, T Kajiwara, M Yokomichi, T Sakuda, Y Oritsuki, and MMiyake, et al., "HiSIM-HV: A compact model for simulation of High-Voltage-MOSFET circuits", in Proceedings of the 9th International Conference on Solid-State and Integrated-Circuit Technology (ICSICT) 2008, vol. 1, pp. 276-9, Oct. 2008.

- Y Oritsuki, M Yokomichi, T Kajiwara, A Tanaka, N Sadachika, and M Miyake, *et al.*, "HiSIM-HV: A Compact model for simulation of high-voltage MOSFET circuits", *Electron Devices, IEEE Transactions on*, no. 99, pp. 1-8, 2010.

- M Knaipp, G Rohrer, R Minixhofer, and E Seebacher, "Investigations on the high current behavior of lateral diffused high-voltage transistors", *Electron Devices, IEEE Transactions on*, Vol. 51, no. 10, pp. 1711-20, Oct. 2004.

- T Myono, E Nishibe, S Kikuchi, K Iwatsu, T Suzuki, and Y Sasaki, et al., "Modelling technique for uni-directional HVMOS devices based on BSIM3v3", *Electronics Letters*, Vol. 35, no. 14, pp. 1200-1, Jul. 1999.

- T Myono, E Nishibe, K Iwatsu, S Kikuchi, T Suzuki, and Y Sasaki, et al., "Modelling technique for High-Voltage MOS devices with BSIM3v3", *Electronics Letters*, Vol. 34, no. 18, pp. 1790-1, Sep. 1998.

- C Na, W Rui, and Z Guoxiang, "A new modeling and parameter extraction technique for uni-directional High-Voltage MOS devices", in Proc. 5<sup>th</sup> Int. Conf. ASIC, Vol. 2, pp. 984-7, Oct. 2003.

- C Anghel, N Hefyene, A M Ionescu, M Vermandel, B Bakeroot, and J Doutreloigne, *et al.*, "Investigations and physical modelling of saturation effects in lateral DMOS transistor architectures based on the concept of intrinsic drain voltage", *Solid-State Device Research Conference, 2001. Proceeding of the 31st European*, vol. 1, pp. 399-402, Sep. 2001

- N Hefyene, E Vestiel, B Bakeroot, C Anghel, S Frere, and A M Ionescu, et al., "Bias-dependent drift resistance modeling for accurate DC and AC simulation of asymmetric HV-MOSFET", Simulation

of Semiconductor Processes and Devices, 2002. SISPAD 2002. International Conference on, vol., no., pp. 203-6, 2002

- 25. N Hefyene, J M Sallese, C Anghel, A M Ionescu, S F Frere, and R Gillon, "EKV compact model extension for HV lateral DMOS transistors", *Advanced Semiconductor Devices and Microsystems, 2002. The Fourth International Conference on*, vol. 1, pp. 345-8, Oct. 2002

- W Grabinski, and T Gneiting, Editors., "POWER/HVMOS Devices Compact Modeling", Dordrecht, Heidelberg, London, New York: Springer, 2010.

- A Bazigos, F Krummenacher, J M Sallese, M Bucher, E Seebacher, and W Posch, et al., "A Physics-Based Analytical Compact Model for the Drift Region of the HV-MOSFET", *IEEE Transactions on Electron Devices*, Vol. 58, no. 6, pp. 1710-21, Jun. 2011.

- D Ward, and R Dutton, "Charge-Oriented Model for MOS-Transistor Capacitances" *IEEE Journal Of Solid-State Circuits*, Vol. 13, no. 5, pp. 703-8, 1978.

- S Y Oh, D Ward, and R Dutton, "Transient analysis of MOS transistors", *Electron Devices, IEEE Transactions on*, Vol. 27, no. 8, pp. 1571-8, Aug. 1980.

- A S Roy, C C Enz, and J M Sallese, "Source-drain partitioning in MOSFET", *IEEE Transactions on Electron Devices*, Vol. 54, no. 6, pp. 1384-93, Jun. 2007.

- J Brews, "Charge-Sheet Model of MOSFET", Solid-State Electronics, Vol. 21, no. 2, pp. 345-55, 1978.

- 32. C C Enz, F Krummenacher, and E A Vittoz, "An analytical MOS-

Transistor Model valid in all regions of operation and dedicated to low-voltage and low-current applications", *Analog Integrated Circuits and Signal Processing*, Vol. 8, no. 1, pp. 83-114, Jul. 1995.

- I Kwon, M Je, K Lee, and H Shin, "A simple and analytical parameterextraction method of a microwave MOSFET", *Microwave Theory and Techniques, IEEE Transactions on*, Vol. 50, no. 6, pp. 1503-9, Jun. 2002.

- 34. G A Ivarez Botero, R Torres-Torres, and R Murphy-Arteaga, "Using S-parameter measurements to determine the threshold voltage, gain factor, and mobility degradation factor for microwave bulk-MOSFETS", *Microelectronics Reliability*, Vol. 51, no. 2, pp. 342-9, 2011, 2010 Reliability of Compound Semiconductors (ROCS) Workshop; Prognostics and Health Management.

- S M Jen, C Enz, D Pehlke, M Schroter, and B Sheu, "Accurate modeling and parameter extraction for MOS transistors valid up to 10 GHz", *Electron Devices, IEEE Transactions on*, Vol. 46, no. 11, pp. 2217-27, Nov. 1999.

- M A Chalkiadaki, and M Bucher, "Large-signal RF modelling of MOSFETs with the EKV3 MOSFET model", *Journal of Telecommunications and Information Technology (JTIT)*, Vol. 1, pp. 25-8, 2010.

- M Bucher, A Bazigos, S Yoshitomi, and N Itoh, "A scalable advanced RF IC design-oriented MOSFET model", *International Journal of RF* and Microwave Computer-Aided Engineering, Vol. 18, no. 4, pp. 314-25, Jul. 2008.

- Y Tsividis, "Operation and modeling of the MOS", New York, NY, USA: McGraw-Hill, Inc., 1987.

#### **AUTHORS**

Antonios Bazigos was born in Athens, Greece, in 1980. He received the Diploma in electrical and computer engineering and the Ph.D. degree from the National Technical University of Athens (NTUA), Athens, in 2003 and 2008, respectively. His Ph.D. thesis is on the field of compact modeling of the MOS transistor. Currently, he is a Postdoctoral Researcher with the Ecole

Polytechnique Federale de Lausanne, Lausanne, Switzerland, on high-voltage MOS field-effect transistor modeling, within the framework of the Compact Modeling Network project. He has worked on the development and the code implementation of the EKV3 MOS transistor compact model, and he is still working on the further improvement of the model.

E-mail: antonios.bazigos@epfl.ch

**François Krummenacher** was born in Lausanne, Switzerland, in 1955. He received the M.S. and Ph.D. degrees in electrical engineering from Swiss Federal Institute of Technology (EPFL), Lausanne, in 1979 and 1985, respectively. He has been with the Electronics Laboratory, EPFL, since 1979, working in the field of low-power analog and mixed-signal complementary

metal-oxide-semiconductor (MOS) integrated circuit (IC) design, as well as in deep submicron and high-voltage MOS field-effect transistor device compact modeling. Since 1989, he has been also working as an Independent Consultant, providing scientific and technical expertise in IC design to numerous local and international industries and research laboratories. He is the author or coauthor of more than 100 scientific publications in these fields.

E-mail: francois.krummenacher@epfl.ch

Jean-Michel Sallese received the M.Sc. degree from the Institut National des Sciences Appliques, Toulouse, France, and the Ph.D. degree in physics from the Centre National de la Recherche Scientifique, University of Nice-Sophia Antipolis, Nice, France, where he worked on deep-level characterization in semiconductors. He has been with the Ecole Polytechnique Federale de Lausanne, Lausanne, Switzerland, since 1991, where he was involved in III-V laser diode activities and modeling interdiffusion phenomena in quantum wells and quantum wire structures. He currently gave lectures in the modeling of semiconductor devices in the context of circuit design, and his research activities concern compact modeling of bulk and multigate metal oxide-semiconductor field-effect transistors, as well as modeling of emerging microelectromechanical systems.

E-mail: jean-michel.sallese@epfl.ch

**Matthias Bucher** received the Diploma in electrical engineering and the Ph.D. degree from the Swiss Federal Institute of Technology (EPFL), Lausanne, Switzerland, in 1993 and 1999, respectively. The subject of his Ph.D. thesis was the analytical metal-oxidesemiconductor (MOS) transistor modeling for analog circuit simulation.

In 1997, he was an Invited Researcher with Large Scale Integration Logic, Milpitas, CA. From 2000 to 2003, he was a Visiting Researcher with the National Technical University of Athens, Athens, Greece, and was a Consultant for the microelectronic industry. In 2004, he was an Assistant Professor with the Department of Electronic and Computer Engineering, Technical University of Crete, Chania, Greece, where he currently is the Director of the Electronics Laboratory. His research interests are in the design of lowvoltage low-power analog/radio-frequency integrated circuits and in the broadband characterization and advanced compact modeling of nanoscale complementary-MOS devices. He has also coordinated the EKV3 MOS transistor compact model code development. He has authored or coauthored numerous scientific papers.

E-mail: bucher@electronics.tuc.gr

**Ehrenfried Seebacher** was born on September 3, 1966. He received the M.Sc. degree in physics from the Technical University of Graz, Graz, Austria, in 1993.

From 1994 to 1998, he was with the Department of Research and Development, austriamicrosystems, Unterpremstätten, Austria, working on compact

modeling of complementary metal-oxide-semiconductor (CMOS), bipolar CMOS, and high-voltage CMOS processes. Since 1999, he has been the Section Manager of the said group at austriamicrosystems. The group is responsible for compact modeling, process characterization, verification run sets, and Simulation Program with Integrated Circuit Emphasis (SPICE) simulator support. He has supervised a number of students in research dealing with compact modeling and SPICE simulation. His research interests include modeling of MOS, bipolar transistors, and passive elements.

E-mail: ehrenfried.seebacher@austriamicrosystems.com

Werner Posch was born in Tamsweg, Austria, in 1974. He received the M.S. degree in applied physics from Graz University of Technology, Graz, Austria, in 2002. He is currently working toward the Ph.D. degree at Graz University of Technology, with an emphasis on mismatch modeling for high-voltage (HV) complementary metaloxide-semiconductor (CMOS) processes.

He is currently with the Process and Device Characterization Group, austriamicrosystems, Unterpremstätten, Austria, where his primary activity is HV laterally diffused (LD) MOS transistor Simulation Program with Integrated Circuit Emphasis modeling. His research interests include matching characterization of HV-LD MOS transistors and capacitor arrays.

E-mail: Werner.Posch@austriamicrosystems.com

Kund Molnár was born in Nyiregyhaza, Hungary, in 1970. He studied solid-state electronics and received the Dipl.-Ing. degree in electrical engineering from the Technical University of Ilmenau, Ilmenau, Germany, in 1994, and the Ph.D. degree in applied physics from Budapest University of Technology and Economics, Budapest, Hungary, in 2002. Between 1995 and 1998, he was a Research Assistant with the Research Institute for Technical Physics and Materials Science (MFA), Budapest, investigating carrier transport in porous silicon light-emitting diodes. In 1999, he became a Member of the Budapest Design Center, austriamicrosystems AG, Unterpremstätten, Austria. In 2000, he joined the headquarters in Unterpremstätten, where he is currently working on analog/radio frequency Simulation Program with Integrated Circuit Emphasis modeling of semiconductor devices.

E-mail: Kund.Molnar@austriamicrosystems.com

Mingchun Tang was born in Fushun, China, in 1979. He received the B.S. degree in applied physics from Jilin University, Changchun, China, in 2002, and the M.S. and Ph.D. degree in the field of compact modeling of advanced metal-oxide-semiconductor transistors, such as fin-shaped field-effect transistors, from the University of Strasbourg, Illkirch, France, in 2006 and 2009, respectively.

Since 2010, he has been with austriamicrosystems, Unterpremstaetten, Austria, as Simulation Program with Integrated Circuit Emphasis Modeling Engineer.

E-mail: Mingchun.Tang@austriamicrosystems.com

DOI: 10.4103/0377-2063.97329; Paper No JR 417\_11; Copyright © 2012 by the IETE