# Modular DC/DC Converter for DC Distribution and Collection Networks

## THÈSE N° 5430 (2012)

PRÉSENTÉE LE 13 JUILLET 2012

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

LABORATOIRE D'ÉLECTRONIQUE INDUSTRIELLE

PROGRAMME DOCTORAL EN ENERGIE

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

# Stephan KENZELMANN

acceptée sur proposition du jury:

Prof. A. Skrivervik Favre, présidente du jury Prof. A. Rufer, directeur de thèse Prof. J. C. Clare, rapporteur Dr D. Dujic, rapporteur Prof. Y. Perriard, rapporteur

# **Preface**

A PhD is a long journey and many people contributed to bringing mine to a successful end. First of all I would like to thank Prof. Alfred Rufer for accepting me as his PhD student. Since the very beginning of his tutoring, he surprised me with his vision and the confidence he had in me investigating my ideas.

I would also like to thank the jury committee, Prof. Anja Skrivervik, Prof. Jon Clare, Dr. Drazen Dujic and Prof. Yves Perriard, who agreed to judge my work and who contributed with their comments to the improvement of the thesis.

Special thanks go to the industrial partner, ABB Switzerland Ltd, Corporate Research that initiated this research project. Invaluable advice came from my supervisors Dr. Yales R. de Novaes, Dr. Drazen Dujic and Dr. Francisco Canales. Many thanks for the excellent collaboration and the many ideas and comments they brought up during the last 3 and a half years. Despite his densely packed time schedule, Drazen was always finding the time to discuss technical matters with me.

In the Industrial Electronics Laboratory a big thanks goes to the "MMC Special Force", namely Nicolas Cherix and Michail Vasiladiotis. We spent uncountable hours on creative discussions and building our prototypes and thanks to the hardware expertise of Nicolas, we were often finding solutions that saved us hours or even days. From the other colleagues I particularly would like to thank my office colleague Dr. Antoine Beguin, with whom I shared a lot of thoughts and discussions, which were not always of technical nature. Together with Michail we founded the "LEI Band", which sadly came to a premature end. Dr. Philippe Barrade was always a source of good advice and impregnated me with his "method" [10]. Thanks also to soon to be Dr. Behrooz Bahrani for the excellent collaboration on several publications. Thanks to all the other colleagues for creating the good atmosphere at the LEI, namely Simon, Sebastien, Yannick, both Daniels, Christian, Martel, Fabienne and Roberto.

Life consists not only of work, that is why I want to thank the people that often (or too often) changed my mind: The members of the PeauPow Team Aline, Benoit, Chloé, Geraud, Marc, Patrick, Remy and my other mountaineering friends Jérôme, Louis and Renzo. Thanks also to the friends from the Tango scene Patrick and the members of Architango with whom I spend many resourceful lunch breaks.

And last but not least my gratitude goes to my brothers and my sister for setting an example as well as my girlfriend Larissa for her constant encouragement.

However, the fact that I even have gotten this far I owe to my parents, who supported

### Preface

me unconditionally in every activity and who were always a guide for me.

Lausanne, June 2012

Stephan Kenzelmann

# Abstract

A major change in the electrical transmission and distribution system is taking place in Europe at the moment. The shift from a centralised energy production to a distributed generation profoundly changes the behaviour of the grid. Environmental or social issues associated with the construction of new power lines to relieve bottlenecks, together with aged equipment dating from the 1960s, pose some serious challenges to government, the research community and the economy. Concepts of reactive compensation, harmonic cancellation, voltage stability, power quality and bulky low-frequency transformers need to be redefined for power exchange and transmission in the future. Photovoltaics, wind turbines, fuel cells, storage systems and uninterruptible power supplies use many power electronic interface circuits, where DC intermediate levels already exist. Large photovoltaic- or wind- powered installations, which are connected to a cable network, are characterised by non-negligible distances due to their low power-by-surface density. On the side of the consumer, current trends show an increasing use of DC in end-user equipment.

In such a context, the numerous advantages of power electronics and DC cables may sometimes out-weigh their higher cost. In the future, high-power semiconductor devices that allow higher switching frequencies of the converters may make it possible to down-size even more the passive components. This would significantly reduce raw material consumption and therefore cost, something that is crucial for the market to accept the technology.

In the first part of this PhD thesis, the advantages of DC distribution in terms of transmission losses are illustrated with the help of three case studies.

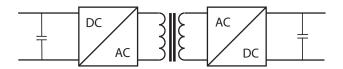

The second part and the main contribution of this thesis is the analysis of a promising candidate for a power electronic transformer, the key component of any DC based grid. It is a bidirectional isolated DC/DC converter based on modular multilevel converters, which are well suited for medium or even high voltage range. The motivation was to investigate a converter operation with important voltage elevation ratios, capable of adapting the voltage level between low, medium and high voltage. A medium-frequency isolation stage provides the possibility of downsizing the passive components. Two modulation methods, a multilevel and a two-level operation, were analysed and compared in terms of losses.

The modular DC/DC converter is an attractive solution for the sensitive aspect of the short-circuit behaviour of classical DC links and power lines. The converter can also

#### Abstract

handle short circuits without the need for additional protection devices, such as circuit breakers.

Given the many advantages of DC systems (reduced environmental impact, reduced space requirements, reduced raw material use, high power quality, power flow control, low transmission losses), this new technology must, at least, be considered when assessing the extension or the renovation of conventional AC grids.

**Keywords:** DC Distribution and Collection, DC/DC Converter, HVDC transmission, Power Electronic Transformer, Multilevel Converter, Medium-Frequency Transformer, DC Grid Protection

# Zusammenfassung

Die Europäische Stromversorgung steht im Zeichen des Wandels. Im Stromnetz verteilte, erneuerbare Energiequellen stellen die herkömmliche, zentralisierte Energieproduktion in Frage. Um das grösstenteils in den 60er Jahren erbaute Wechelstromnetz zu erweitern, müssen administrative Hürden überwunden werden. Sozial- und umweltverträgliche Einschränkungen erschweren diesen Vorgang zusätzlich. Dies stellt grosse Herausforderungen an Regierung, Forschung und Industrie.

Blindleistungskompensation, Energiequalität, Netzstabilität und materialintensive Spannungsumformer verlangen zudem eine Wiederbewertung der konventionellen Wechselstromversorgung. Erneuerbare Energien wie Photovoltaik und Windkraft, Brennstoffzellen und unterbrechungsfreie Stromversorgungen weisen oft schon eine Gleichstrometage in der Wandlerstufe auf. Durch die relativ niedrige Leistungsdichte der Wind- und Sonnenenergieanlagen drängt sich zudem ein effizientes Energiesammelnetz auf, welches wenig Verluste in den verkabelten Leitung aufweist. Auch zeigt sich auf der Verbraucherseite eine Tendenz zum vermehrten Gebrauch von Geräten welche Gleichstrom benötigen.

In diesem Zusammenhang scheint eine Gleichstromversorgung basierend auf Kabelsystemen und Leistungselektronik oft die Nachteile der erhöhten Kosten aufzuwiegen. Zukünftige Hochleistungshalbleiter, die höherfrequent getaktet werden können, werden diese Entwicklung nur beschleunigen, da mit geringerem Materialverbrauch die Kosten sinken.

Der erste Teil dieser Doktorarbeit zeigt die Vorteile eines Gleichstromnetzes im Mittelspannungsbereich auf und wertet diese anhand dreier konkreter Beispiele aus. Der zweite Teil beinhaltet den wesentlichen Beitrag dieser Arbeit. Der wichtigste Bestandteil eines Gleichstromnetzes ist der leistungselektronische Spannungsumformer, welcher das Bindeglied zwischen den verschiedenen Spannungsebenen ist. Es ist ein isolierter Gleichstromwandler, basierend auf dem Konzept eines modularen Stromrichters, welcher sich besonders für Mittel- und Hochspannungsnetze eignet. Besonderes Interesse lag in der Analyse der Spannungserhöhungseigenschaften dieses Wandlers, welche es ermöglichen sollten, die hohen Spannungsunterschiede zwischen Nieder-, Mittel- und Hochspannung zu meistern. Eine mittelfrequente Isolationsstufe ermöglicht zudem die Reduzierung der passiven Bausteine und somit des Gewicht und Volumen der Anlage. Zwei Modulationsmethoden, eine Mehrpunkt- sowie eine Zweipunktschaltung werden vorgestellt, welche es zum Ziel haben die Taktfrequenz der Leistungselektronik auf ein Minimum herabzusetzen. Die zwei Modulationsmethoden werden in Bezug auf die Schaltungsverluste verglichen.

### Zusammenfassung

Das für konventionelle Gleichstromwandler und Gleichstromnetze heikle Fehlerverhalten bei Kurzschlüssen wird mit der vorgeschlagenen Wandlerstruktur entschieden entschärft. Der Wandler ermöglicht es Kurzschlüsse ohne zusätzliche Sicherheitsvorrichtungen oder Gleichstromschalter handzuhaben.

Die Vorteile eines Gleichstromnetzes (bessere Umweltverträglichkeit, geringer Platzverbrauch, niederiger Materialverbrauch, gute Versorgungsqualität, Anpassungsfähigkeit, genaue Kontrolle des Leitsungsflusses, geringe Übertragungsversluste) müssen unbedingt in Betracht gezogen werden bei der Erweiterung oder Erneuerung des herkömmlichen Wechselstromnetzes.

**Stichworte :** Gleichstromnetze, Gleichstromwandler, Leistungselektronische Spannungsumformer, Hochspannungs-Gleichstromübertragung, Mehrpunktschaltungen, Mittelfrequente Spannungsumformer, Gleichstromnetzschutz

# Résumé

Le réseau électrique européen est dans une phase de changement radical. Le passage d'un concept de production centralisée à une génération d'énergie distribuée affecte profondément les notions de contrôle et de stabilité du réseau. Les barrières administratives suscitées par les enjeux environnementaux et sociaux pour construire de nouvelles lignes électriques accentuent les difficultés d'évolution/adaptation du système. De plus le fait que les équipements en place aient été en grande partie construits dans les années 60 pose de sérieux défis aux gouvernements, chercheurs et industriels. La compensation d'énergie réactive, la qualité de tension, la stabilité du réseau, ainsi que l'utilisation de grands transformateurs basse-fréquence requièrent une réévaluation des technologies actuelles basées sur des grandeurs courant/tension alternatives. Les sources renouvelables telles que le photovoltaïque et l'énergie éolienne d'une part, ainsi que les systèmes de stockage et de sauvegarde d'autre part, utilisent souvent des interfaces d'électronique de puissance où un étage continu est déjà présent. La faible densité de puissance des installations photovoltaïques et éoliennes nécessite un réseau de collection d'énergie A haut rendement. Du coté des consommateurs, on note une transition vers l'utilisation d'équipements alimentés en continu.

Dans un tel contexte, les nombreux avantages de l'utilisation de l'électronique de puissance et des réseaux continus peuvent souvent compenser le prix plus élevé inhérent à de cette technologie. En revanche, des futurs composants semi-conducteur de haute puissance, qui permettent une fréquence de commutation plus élevée, permettront de réduire le volume et donc le coût des matières premières, paramètre crucial pour l'acceptation de cette technologie.

Dans la première partie de cette thèse de doctorat, les avantages d'un réseau de distribution continu sont démontrés et illustrés par trois exemples.

La deuxième partie est dédiée à l'analyse d'un candidat de convertisseur continu-continu prometteur, contribution novatrice de cette thèse. Le convertisseur est l'élément clé d'un réseau continu, car il adapte les niveaux de tension. Une topologie modulaire permet son utilisation, que ce soit pour la moyenne ou bien la haute tension. Dans l'analyse, un soin particulier est porté à l'examen des propriétés d'élévation de tension à fort rapport. L'utilisation d'un étage alternatif à moyenne fréquence permet la réduction de la taille des composants passifs. Deux méthodes de modulations ont été analysées, une modulation multi-niveau et une modulation deux-niveau, ayant comme but de minimiser le nombre de commutations dans le convertisseur. Les deux méthodes ont été comparées par rapport

aux pertes dans les éléments semi-conducteurs. La topologie proposée est une solution attractive pour résoudre le comportement de convertisseur continu-continu standard ou de réseaux continus en cas de court-circuit. Le convertisseur est en effet capable de tolérer de telles fautes sans moyen de protection additionnel.

Dans l'éventuelle extension ou rénovation du réseau alternatif conventionnel, compte tenu des avantages des systèmes à courant continu (impact environnemental réduit, peu d'espace occupé, utilisation réduite des matières premières, bonne qualité et flexibilité du réseau, contrôle exacte des flux de puissance et peu de pertes de transmission), les technologies à courant continu doivent au moins être prises en compte.

**Mots-Clés :** Réseau de Collection et Distribution Continu, Convertisseur continucontinu, Transmission à Haute Tension Continue, Transformateur à base de l'Électronique de Puissance, Convertisseur Multiniveau, Transformateur Moyenne Fréquence, Protection des Réseaux Continus

# Contents

| Pı           | refac         | е                      |                                              | j   |

|--------------|---------------|------------------------|----------------------------------------------|-----|

| $\mathbf{A}$ | bstra         | ct                     |                                              | iii |

| Zι           | ısam          | menfa                  | ssung                                        | v   |

| R            | ésum          | é                      |                                              | vi  |

| Co           | onter         | $_{ m nts}$            |                                              | ix  |

| $\mathbf{G}$ | lossa         | $\mathbf{r}\mathbf{y}$ |                                              | xii |

| A            | crony         | ms                     |                                              | xix |

| 1            | Intr          | oducti                 | ion                                          | 1   |

|              | 1.1           | Histor                 | ical Development                             | 1   |

|              | 1.2           | AC ve                  | ersus DC                                     | 1   |

|              |               | 1.2.1                  | Transmission                                 | ]   |

|              |               | 1.2.2                  | Distribution                                 | 2   |

|              |               | 1.2.3                  | Actual State                                 | 3   |

|              | 1.3           | Object                 | tives                                        | 3   |

|              | 1.4           | Outlin                 | ne                                           | 4   |

| 2            | $\mathbf{DC}$ | Grid .                 | Applications and Case Studies                | 7   |

|              | 2.1           | Efficie                | ency of DC Distribution Systems              | 7   |

|              |               | 2.1.1                  | Cable Parameters                             | 8   |

|              |               | 2.1.2                  | Current Carrying Capacity                    | 14  |

|              | 2.2           | DC Co                  | ollection Grid for Wind Power, PV and Cities | 19  |

|              |               | 2.2.1                  | Wind Power                                   | 19  |

|              |               | 2.2.2                  | Solar Power                                  | 31  |

|              |               | 2.2.3                  | Urban DC Distribution                        | 36  |

|              |               | 2.2.4                  | Conclusions                                  | 38  |

### Contents

| 3 | Mea           | ans of  | Power Electronic Interfaces between HV, MV and LV | 41        |

|---|---------------|---------|---------------------------------------------------|-----------|

|   | 3.1           | Requi   | rements for DC Networks                           | 41        |

|   | 3.2           | Conve   | entional Converters                               | 43        |

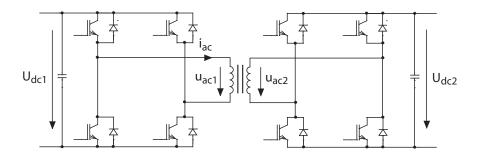

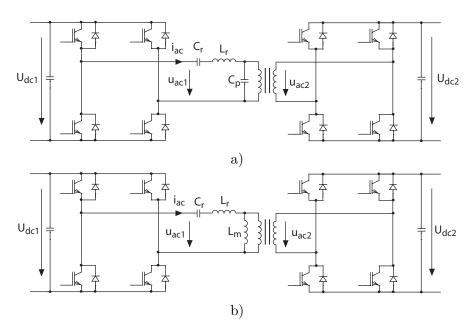

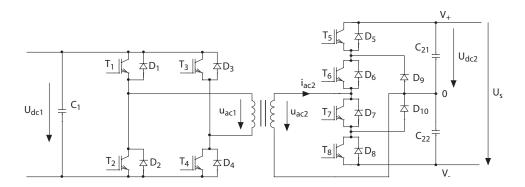

|   |               | 3.2.1   | Dual Active Bridge Converter                      | 43        |

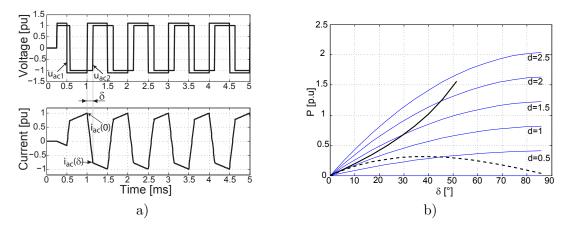

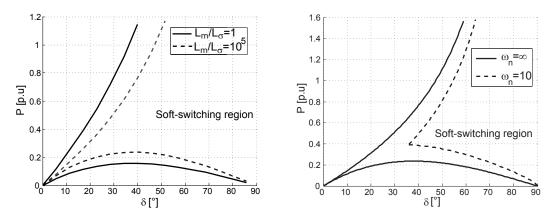

|   |               | 3.2.2   | Resonant Converters                               | 45        |

|   | 3.3           | Multil  | level Converters                                  | 47        |

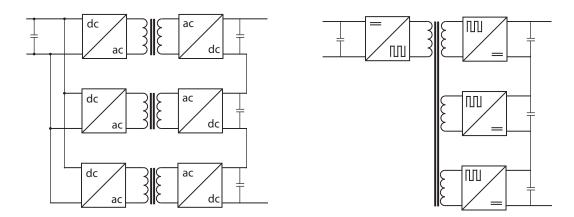

|   |               | 3.3.1   | Cascaded Converters                               | 48        |

|   | 3.4           | Concl   | usion                                             | 49        |

| 4 | Mo            | dular l | Multilevel Converter                              | <b>51</b> |

|   | 4.1           | Modu    | lation Methods                                    | 53        |

|   |               | 4.1.1   | High Switching Frequency PWM                      | 54        |

|   |               | 4.1.2   | Mixed Switching Frequency                         | 59        |

|   |               | 4.1.3   | Fundamental Frequency                             | 59        |

|   | 4.2           | Mathe   | ematical Description                              | 64        |

|   |               | 4.2.1   | Considerations                                    | 64        |

|   |               | 4.2.2   | Natural Balancing of the Branch Energies          | 67        |

|   |               | 4.2.3   | Idealised Model                                   | 70        |

|   | 4.3           | Intern  | al Controller                                     | 73        |

|   |               | 4.3.1   | Direct Modulation                                 | 74        |

|   |               | 4.3.2   | Branch Energy Controller                          | 74        |

|   | 4.4           | Comp    | onent Sizing                                      | 76        |

|   |               | 4.4.1   | Capacitor Design                                  | 76        |

|   |               | 4.4.2   | Inductance Design                                 | 77        |

|   | 4.5           | Curre   | nt Research                                       | 78        |

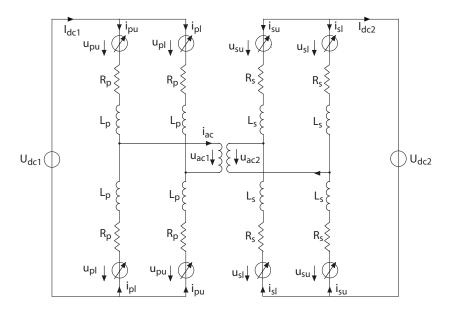

| 5 | $\mathbf{DC}$ | /DC S   | Structure                                         | 81        |

|   | 5.1           | Mathe   | ematical Description                              | 84        |

|   |               | 5.1.1   | Steady-State Analysis                             | 84        |

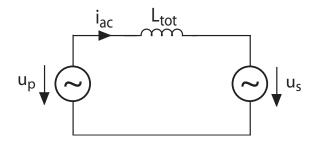

|   |               | 5.1.2   | AC Stage Equations                                | 87        |

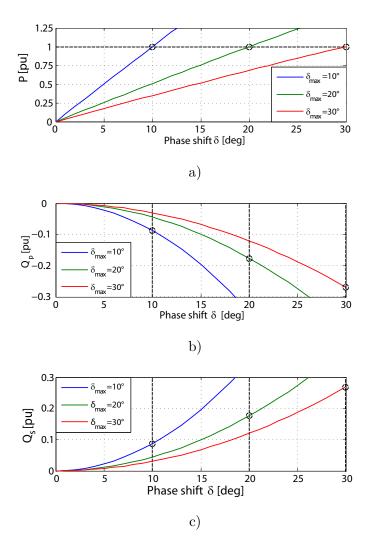

|   | 5.2           | Param   | neter Design                                      | 88        |

|   |               | 5.2.1   | General Capacitor Design                          | 89        |

|   |               | 5.2.2   | Inductance Design                                 | 92        |

| 6 | Cor           | ntrol a | nd Protection of the Modular DC/DC Converter      | 95        |

|   | 6.1           | Multil  | level Modulation Strategies                       | 95        |

|   |               | 6.1.1   | Modulation Strategy                               | 96        |

|   |               | 6.1.2   | Control Strategy                                  | 100       |

|   |               | 6.1.3   | Simulation Results                                | 104       |

|   |               | 6.1.4   | Start-Up Strategy                                 | 106       |

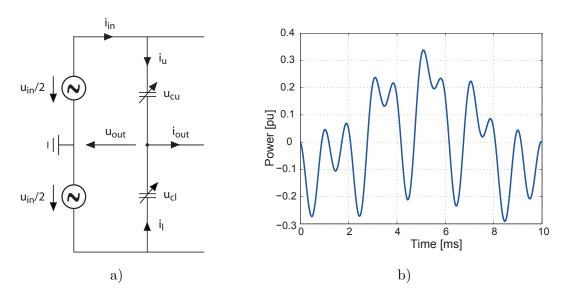

|   | 6.2           | Two-L   | Level Modulation Strategies                       | 108       |

|   |               | 6.2.1   | Modulation Strategy                               | 109       |

|   |               | 6.2.2   | Control Strategy                                  | 116       |

|     |       | 6.2.3         | Simulation Results                                              | . 120 |

|-----|-------|---------------|-----------------------------------------------------------------|-------|

|     |       | 6.2.4         | Start-Up Strategy                                               | . 122 |

|     | 6.3   | Protec        | etion                                                           | . 125 |

|     |       | 6.3.1         | Short-Circuit Behaviour                                         | . 126 |

|     |       | 6.3.2         | Fault on the AC Side                                            | . 126 |

|     |       | 6.3.3         | Fault on the DC Side                                            | . 127 |

| 7   | Effi  | ciency        | of the Modular DC/DC Converter                                  | 131   |

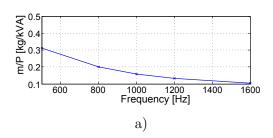

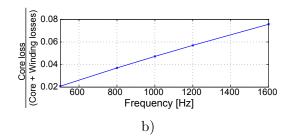

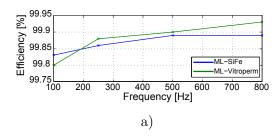

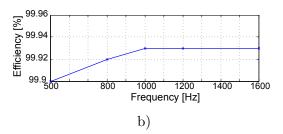

|     | 7.1   | Influer       | nce of the Medium Frequency Transformer                         | . 131 |

|     |       | 7.1.1         | Generalities                                                    | . 131 |

|     |       | 7.1.2         | Design Optimisation Procedure                                   | . 134 |

|     |       | 7.1.3         | Design Comparison                                               | . 135 |

|     | 7.2   | Semice        | onductor Loss Evaluation                                        | . 137 |

|     |       | 7.2.1         | Loss Calculation Model                                          | . 137 |

|     |       | 7.2.2         | Case Study                                                      | . 139 |

|     | 7.3   | Conclu        | usions                                                          | . 149 |

| 8   | Pra   | ctical        | Verification                                                    | 151   |

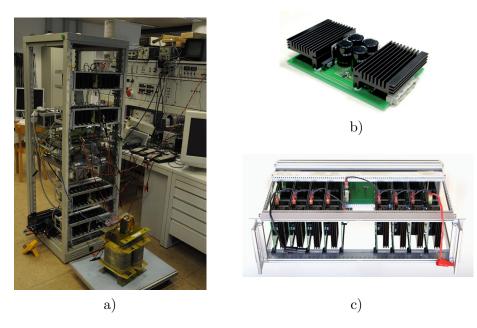

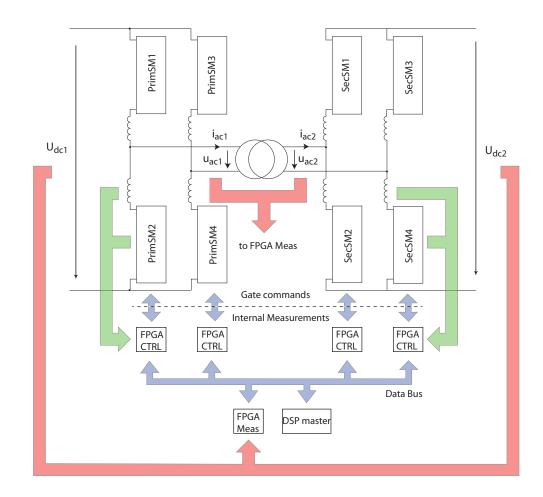

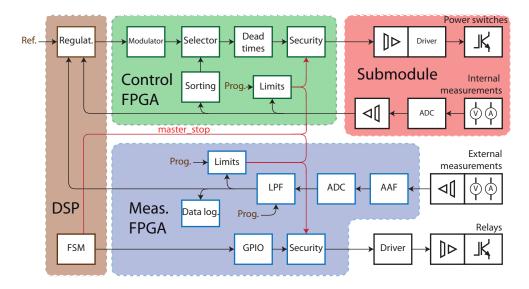

|     | 8.1   | Protot        | type Design                                                     | . 151 |

|     | 8.2   | Transf        | former                                                          | . 154 |

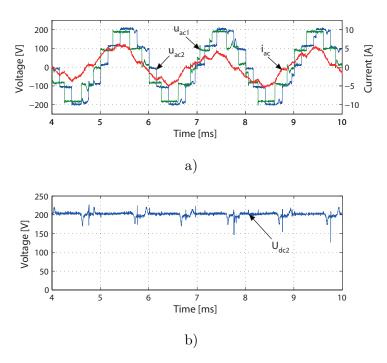

|     | 8.3   | Multil        | evel Modulation - Experimental Results                          | . 155 |

|     | 8.4   | Two-L         | evel Modulation - Experimental Results                          | . 156 |

| 9   | Cor   | clusio        | ns and Future Work                                              | 159   |

| •   | 9.1   |               | ary and Contributions                                           |       |

|     | 9.2   |               | e Work                                                          |       |

| Δ   | Δnr   | oendix        |                                                                 | 161   |

| 11  |       |               | s on the Branch Energy Balancing                                |       |

|     | 11.1  |               | Determination of the Current Coefficient due to an Unbalance of | . 101 |

|     |       | 11.1.1        | the Branch Energies                                             | . 161 |

|     |       | A.1.2         | Relating AC and DC Quantities                                   |       |

| Lis | st of | Figure        | es                                                              | 163   |

| Lie | st of | Tables        |                                                                 | 169   |

|     |       |               |                                                                 |       |

| Bi  | bliog | graphy        |                                                                 | 183   |

| Cı  | ırric | ulum <b>'</b> | Vitae                                                           | 185   |

# Glossary

| $A_e$          | Cross section of the core of a transformer                    | 131,          |

|----------------|---------------------------------------------------------------|---------------|

|                |                                                               | 132           |

| $A_w$          | Cross section of the windings of a transformer                | 131,          |

|                |                                                               | 132           |

| D              |                                                               | 101           |

| $B_{max}$      | Maximum flux density in the transformer core                  | 131           |

| $\cos \phi$    | Power factor of an AC system                                  | 76            |

| C'             | Capacity of a high voltage cable per unit length              | 13            |

| δ              | Phase between primary and secondary voltage waves             | 43, 87,       |

| U              | Thase between primary and secondary voltage waves             | 43, 87,       |

| $\delta_{max}$ | Maximal phase shift considered for converter design           | 92, 94        |

|                | 37.1/                                                         | 70            |

| $\epsilon$     | Voltage ripple on a capacitor in percent                      | 76            |

| $f_p$          | Switching frequency                                           | 119           |

| :              | AC current on the level of the transfermen on AC lead         | 64 66         |

| $i_{ac}$       | AC current on the level of the transformer or AC load         | 64, 66,       |

|                |                                                               | 86, 113, 115, |

|                |                                                               | 115,<br>121,  |

|                |                                                               | 156,          |

|                |                                                               | 167           |

| $i_C$          | Collector current of the IGBT                                 | 137,          |

|                | Conceilor ourrent of the 10D1                                 | 138           |

| $i_{circ}$     | Current difference between the upper and lower branch current | 72, 74,       |

| circ           |                                                               | 75            |

| $I_{dc}$       | DC current                                                    | 68, 162       |

| $I_{dc1}$      | DC current of the primary MMC                                 | 120           |

|                |                                                               |               |

| $I_{dc2}$    | DC current of the secondary MMC                                                                           | 88, 120                         |

|--------------|-----------------------------------------------------------------------------------------------------------|---------------------------------|

| $i_F$        | IGBT diode current                                                                                        | 138                             |

| $I_{ki}$     | Additional DC current due to the unbalance of the branch energies                                         | 68, 162                         |

| $i_l$        | Current in the lower branch of a single phase leg of the MMC                                              | 65, 66,<br>165                  |

| $i_u$        | Current in the upper branch of a single phase leg of the MMC                                              | 65, 66,<br>165                  |

| k            | Parameters which indicates the degree of DC unbalance between the upper and lower branch voltage in a MMC | 68                              |

| $\kappa$     | Number of periods that are considered for the loss evaluation                                             | 137                             |

| $k_{core}$   | Coefficient that represents the scale of the core losses                                                  | 134                             |

| $k_d$        | Coefficient that represents the scale of the dielectric losses                                            | 134                             |

| $k_i$        | Parameters which indicates the degree of DC unbalance between the upper and lower branch current in a MMC | 68, 162                         |

| $k_p$        | Elevation factor of the primary MMC                                                                       | 91, 108,<br>111,<br>118–<br>120 |

| $k_s$        | Elevation factor of the secondary MMC                                                                     | 91, 109,<br>118,<br>119         |

| $k_W$        | Coefficient that represents the scale of the winding losses                                               | 134                             |

| $L_i'$       | Metric inductance of a cable                                                                              | 13                              |

| $L_m$        | Magnetizing inductance of the transformer                                                                 | 45                              |

| $L_{\sigma}$ | Leakage inductance of a transformer                                                                       | 43, 86                          |

| m            | Modulation index                                                                                          | 67, 70,<br>74, 99,<br>162       |

| $m_{2L}$     | Equivalent modulation index for the two-level operation of the MMC                                        | 108                             |

| $m_l$        | Modulation index of the lower branch of a MMC                                                             | 70, 74                          |

| $m_u$        | Modulation index of the upper branch of a MMC                                                             | 70, 74                          |

| $\mu$        | Conductivity of a conductor in Siemens per meter [S/m]                                                    | 9                               |

| n            | Scaling factor relating the AC quantities with the DC quantities                                          | 67. 162                         |

| $N_{ac}$                      | Number of cells connected in the "AC-loop"                          | 111      |

|-------------------------------|---------------------------------------------------------------------|----------|

| $N_{dc}$                      | Number of cells connected in the "DC-loop"                          | 111,     |

|                               |                                                                     | 118      |

| $N_p$                         | Number of submodules per branch in the primary MMC                  | 112      |

| $N_s$                         | Number of submodules per branch in the secondary MMC                | 112      |

|                               |                                                                     |          |

| $\phi_l$                      | Phase shift between voltages at the terminals of an electrical line | 17       |

| $Q_p$                         | Reactive power on the primary side                                  | 88       |

| $Q_s$                         | Reactive power on the secondary side                                | 88       |

| 40                            |                                                                     |          |

| $R'_{ac}$                     | Effective metric AC resistance due to the skin effect               | 9        |

| $R_{ac,90^{\circ}\mathrm{C}}$ | AC resistivity at 90 °C                                             | 15       |

| $R_{dc}$                      | DC resistance of a cable                                            | 8        |

| $R_{dc,90^{\circ}\mathrm{C}}$ | DC resistivity at 90 °C                                             | 15       |

| $\rho$                        | Resistivity of a conductor                                          | 8        |

|                               |                                                                     |          |

| SiFe                          | Silicon-Steel, material used for transformer cores                  | 136,     |

|                               |                                                                     | 168      |

| $S_{rms}$                     | Current density in the transformer windings                         | 132      |

|                               |                                                                     |          |

| T                             | Period of an AC signal given by $T = \frac{1}{F}$                   | 69       |

| $T_{Calc}$                    | Calculation and measurement delay                                   | 104,     |

|                               |                                                                     | 119      |

| $T_{cm}$                      | Command organ time delay                                            | 104,     |

|                               |                                                                     | 119      |

| $T_f$                         | Filter time constant                                                | 104      |

| $T_i$                         | Integral time constant of PI controller                             | 103,     |

|                               |                                                                     | 119      |

| $T_n$                         | Proportional time constant of PI controller                         | 103,     |

| _                             |                                                                     | 119      |

| $T_{pE}$                      | Equivalent time constant that summarises the small time             | 104,     |

|                               | constants in the system                                             | 119      |

|                               |                                                                     | a=       |

| $u_{ac}$                      | Generic AC voltage waveform                                         | 67       |

| $u_{ac1}$                     | Primary transformer terminal voltage                                | 86, 110, |

|                               |                                                                     | 112,     |

|                               |                                                                     | 113,     |

|                               |                                                                     | 120,     |

|                               |                                                                     | 121,     |

|                               |                                                                     | 123,     |

|                               |                                                                     | 167      |

## Glossary

| $u_{ac2}$           | Secondary transformer terminal voltage                                                                                                                   | 86, 111,<br>114,<br>115,<br>120,<br>121, |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

|                     |                                                                                                                                                          | 123,                                     |

|                     |                                                                                                                                                          | 167                                      |

| $u_{ce}$            | Collector- Emitter voltage of the IGBT                                                                                                                   | 137                                      |

| $u_{circ}$ $u_{cl}$ | Voltage on the branch impedance due to the circulating current<br>Sum of the voltages at the terminals of the submodules of the<br>lower branch of a MMC | 72<br>68                                 |

| $u_{cu}$            | Sum of the voltages at the terminals of the submodules of the upper branch of a MMC                                                                      | 68                                       |

| $U_{dc}$            | Generic DC voltage                                                                                                                                       | 162                                      |

| $U_{dc1}$           | Primary DC voltage                                                                                                                                       | 110,                                     |

|                     |                                                                                                                                                          | 112                                      |

| $U_{dc2}$           | Secondary DC voltage                                                                                                                                     | 110,                                     |

|                     |                                                                                                                                                          | 111,                                     |

|                     |                                                                                                                                                          | 118,                                     |

|                     |                                                                                                                                                          | 120,                                     |

|                     |                                                                                                                                                          | 126                                      |

| $\hat{U}_p$         | Amplitude of the sinusoidal part of the primary branch voltage                                                                                           | 85                                       |

| $u_p$               | Primary transformer voltage without considering the branch impedance                                                                                     | 87                                       |

| $\hat{U}_s$         | Amplitude of the sinusoidal part of the primary branch voltage                                                                                           | 85                                       |

| $u_s$               | Secondary transformer voltage without considering the branch impedance                                                                                   | 87                                       |

| $U_{sm}$            | Submodule voltage                                                                                                                                        | 53, 62,                                  |

|                     |                                                                                                                                                          | 76, 91,                                  |

|                     |                                                                                                                                                          | 124,                                     |

|                     |                                                                                                                                                          | 138                                      |

| $u_x$               | Terminal voltage of one submodule                                                                                                                        | 53, 116                                  |

| VITROPERM           | Nano-crystalline alloy used for transformer cores                                                                                                        | 136,                                     |

|                     |                                                                                                                                                          | 168                                      |

| $W_c^{circ}$        | Difference of the energies in the upper and lower branch                                                                                                 | 73, 76                                   |

| $W_c^{sum}$         | Sum of the energies in the upper and lower branch                                                                                                        | 73, 76                                   |

| $W_l \ W_u$     | Energy variation over a period of the lower branch of a MMC Energy variation over a period of the upper branch of a MMC | 70<br>70 |

|-----------------|-------------------------------------------------------------------------------------------------------------------------|----------|

| $y_{proximity}$ | Empirical factor influencing the AC resistivity of a line due to<br>the proximity effect                                | 10       |

| $y_{skin}$      | Empirical factor influencing the AC resistivity of a line due to the skin effect                                        | 10       |

# Acronyms

| AAF  | Anti-Aliasing filter                     | 154      |

|------|------------------------------------------|----------|

| AC   | Alternative Current                      | 1        |

| ADC  | Analogue-to-Digital Converter            | 154      |

| APOD | Alternative Phase Opposition Disposition | 55       |

| ARW  | Anti-Reset Windup                        | 103      |

| DAB  | Dual Active Bridge                       | 43, 45-  |

|      |                                          | 47, 108, |

|      |                                          | 109,     |

|      |                                          | 126-     |

|      |                                          | 128      |

| DC   | Direct Current                           | 1        |

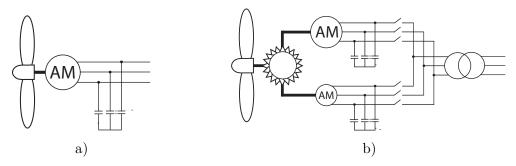

| DFIG | Double Fed Injection machine             | 22, 29,  |

|      |                                          | 31       |

| DSP  | Digital Signal Processor                 | 151,     |

|      |                                          | 152,     |

|      |                                          | 154      |

| ESR  | Equivalent Series Resistance             | 65       |

| FLC  | Flying Capacitor converter               | 47, 49   |

| FMEA | Failure Mode and Effects Analysis        | 160      |

| FPGA | Field-Programmable Gate Array            | 151,     |

|      |                                          | 152,     |

|      |                                          | 154      |

| HV   | High Voltage                             | 3        |

| HVAC | High Voltage Alternative Current         | 2        |

| HVDC | High Voltage Direct Current              | 2, 51,   |

|      |                                          | 159      |

| IGBT       | Insulated Gate Bipolar Transistor                                       | 47, 49,<br>145 |

|------------|-------------------------------------------------------------------------|----------------|

| LCC        | 3th order resonant converter based on one inductance and two capacitors | 46             |

| $_{ m LF}$ | Low Frequency                                                           | 3              |

| LLC        | 3th order resonant converter based on two inductances and one capacitor | 46             |

| LV         | Low Voltage                                                             | 3              |

| LVDC       | Low Voltage Direct Current                                              | 2, 159         |

| MF         | Medium Frequency                                                        | 4, 41,         |

|            |                                                                         | 42, 48,        |

|            |                                                                         | 59, 81,        |

|            |                                                                         | 88, 131        |

| MLC        | Multilevel Converter                                                    | 47             |

| MMC        | Modular Multilevel Converter                                            | 4, 51,         |

|            |                                                                         | 65, 67,        |

|            |                                                                         | 70, 73,        |

|            |                                                                         | 76–79,         |

|            |                                                                         | 81, 82,        |

|            |                                                                         | 84, 86,        |

|            |                                                                         | 89, 94-        |

|            |                                                                         | 96, 100,       |

|            |                                                                         | 101,           |

|            |                                                                         | 106-           |

|            |                                                                         | 110,           |

|            |                                                                         | 112,           |

|            |                                                                         | 113,           |

|            |                                                                         | 116,           |

|            |                                                                         | 120,           |

|            |                                                                         | 122,           |

|            |                                                                         | 126,           |

|            |                                                                         | 140,           |

|            |                                                                         | 147            |

|            |                                           | Acronyms      |

|------------|-------------------------------------------|---------------|

| MDDT       | Mariana Dana Daiat Tarakina               | 22 24         |

| MPPT<br>MV | Maximum Power Point Tracking              | 33, 34        |

|            | Medium Voltage                            | 3             |

| MVDC       | Medium Voltage Direct Current             | 2, 159        |

| NLC        | Nearest Level Control                     | 59, 60,<br>62 |

| NPC        | Neutral Point Clamped converter           | 34, 47,<br>49 |

| PCC        | Point of Common Connection                | 21, 25,<br>26 |

| PD         | Phase Disposition                         | 55, 56        |

| POD        | Phase Opposition Disposition              | 55            |

| PRC        | Parallel Resonant Converter               | 46            |

| PSPWM      | Phase Shifted Carriers PWM                | 55            |

| PV         | Photovoltaic                              | 2             |

| PWM        | Pulse Width Modulation                    | 53 – 55       |

| RMS        | Root Mean Square                          | 66, 74        |

| SDRAM      | Synchronous Dynamic Random-Access Memory  | 154           |

| SHE        | Selective Harmonic Elimination            | 59, 62,       |

|            |                                           | 64, 96,       |

|            |                                           | 99            |

| SMC        | Stacked Multi-Cell converter              | 47, 49        |

| SMPS       | Switched-Mode Power Supply                | 36            |

| SPI        | Serial Peripheral Interface               | 151,          |

|            | 1                                         | 152           |

| SPRC       | Series Parallel Resonant Converter or LCC | 46            |

| SRC        | Series Resonant Converter                 | 46            |

| SVC        | Space Vector Control                      | 59, 60,       |

| ~          | Space Testor Control                      | 62            |

| SVM        | Space Vector Modulation                   | 55, 57,       |

| ~ 111      | Space Tourist Frontainer                  | 58, 60-       |

|            |                                           | 62            |

| THD        | Total Harmonic Distortion                 | 62, 96,       |

|            |                                           | 98            |

|            |                                           |               |

### Acronyms

| UPS | Uninterruptible Power Supply | 3, 36 |

|-----|------------------------------|-------|

| ZCS | Zero Current Switching       | 45    |

| ZVS | Zero Voltage Switching       | 45    |

# 1 Introduction

## 1.1 Historical Development

The first electrical systems were used to power lights in industrial and commercial buildings. With the intention of building lighting that requires less maintenance, Thomas A. Edison conceived 1882 an entire lighting system including electrical generation and distribution based on Direct Current (DC) [1]. At that time it was not possible to step up the DC voltage, therefore limiting the use of DC to local production and consumption. However the introduction of the transformer and polyphase Alternative Current (AC) motors by Nikola Tesla was a game changer. Now it was possible to transport electrical energy over large distances and the land-stone for our today's AC network has been laid. Since the Chicago's World Fair in 1893 [2] where an AC based power system was used to power more than 100'000 incandescent light bulbs, AC quickly eclipsed the DC power system technology. Even if the use of AC became the dominant technology, DC systems remained in operation. For example in Stockholm, Sweden, the residential DC distribution grid was replaced by AC only in the 1970's [3]. Telecommunication systems are still based on 48Vdc. DC offered speed control to the electrical machines for trams, subways, trains and other industrial drive systems and is still used nowadays. Since the introduction of the semiconductor technology in the 1970, DC systems have become again an attractive alternative to AC systems.

### 1.2 AC versus DC

### 1.2.1 Transmission

The AC distribution and transmission system has been in place almost for 100 years now and only since the 1970's DC has become in some cases a real alternative.

The today's AC transmission faces several challenges. First the entire grid infrastructure

is rather old, most of it has been built in the 1960's. Modernization is urgently needed, but there are many constraints for building new lines. Many bottlenecks exist that lead to serious congestion problems. Reactive power compensation decreases the transmission capacity of AC lines. Furthermore the deregulation of the market has led to a declining investment in the infrastructure.

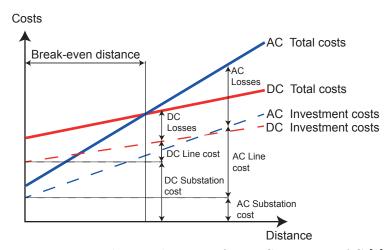

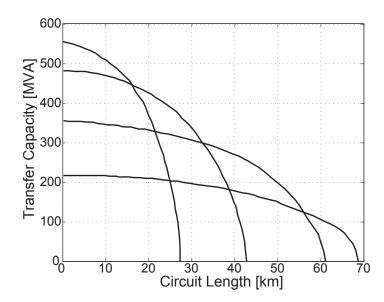

DC lines could solve or at least relieve some of the problems in transmission. However, for short distances the cost is still higher for a High Voltage Direct Current (HVDC) line. In general the break-even distance illustrated in Fig. 1.1 depends on various aspects, such as right of way (the required width of the corridor around the HVDC power line is almost half of the space required for High Voltage Alternative Current (HVAC) systems), the transmission medium (cable or overhead lines), the type of substation (HVAC, thyristor based HVDC, VSC-HVDC) and environmental aspects (generally in disfavour of AC systems). For a thyristor HVDC system, the break-even distance using overhead lines is between 500km and 800km [4]. For cabled systems, the break-even distance is much lower, generally between 40km and 80km. The total losses for HVDC are more important than for HVAC for low distances, since the efficiency of the HVDC converter cannot match the efficiency of the transformer in an AC system. On the other side, line losses are smaller for HVDC.

Figure 1.1: Break-even distance of HVDC versus HVAC [5]

### 1.2.2 Distribution

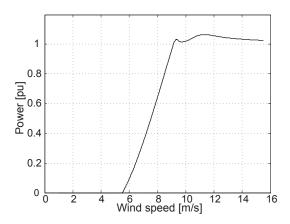

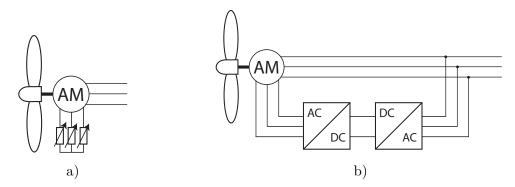

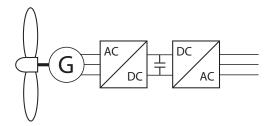

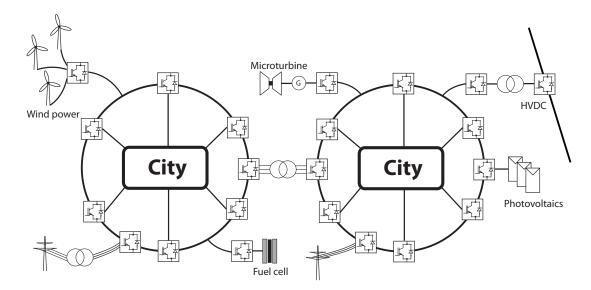

The way energy is produced is about to change from a centralised to a more distributed production [6]. These distributed generators include many DC output based technologies, such as Photovoltaic (PV), fuel cells and even micro- and wind turbines often have a DC intermediate circuit.

First investigations in the field of Medium Voltage Direct Current (MVDC) or Low Voltage Direct Current (LVDC) distribution concepts have been proposed within dedicated

contexts like feeding of large Computer Server Farms. In this approach, multiple, decentralised sources are considered, but also back-up power like classical Uninterruptible Power Supply (UPS). However, the cascade of multiple classic AC/DC and DC/AC conversions can lead to poor energy efficiency [7]. The use of bulky Low Frequency (LF) electromagnetic transformers furthermore requires a lot of raw material.

Storage technologies are to play an important role in the future grid due to the stochastic production of the renewable energy. Battery based storage or even electrical vehicles could be used in the future to support the electricity network. These storage technologies are based on DC and will most probably be used in the distribution level.

On the side of the loads, many domestic devices such as computers, lighting and sometimes even washing machines require a supply with DC power.

#### 1.2.3 Actual State

The crucial element to either DC or AC grids is the voltage transformation devices. In an AC system, the transformers can easily adapt the voltage to a higher level for energy transport or reduce it to meet the load requirements. Conventionally the High Voltage (HV), Medium Voltage (MV) and Low Voltage (LV) networks are interfaced with multiple low frequency electromagnetic transformers. Voltage conversion for DC is yet not so simple and requires the use of power electronics, also called power electronic or DC transformer. The efficiency of conventional distribution transformer is generally higher than 98%. In order to match the efficiency of an AC system, the DC transformer should obtain at least the same efficiency.

Another decisive element in a distribution and transmission network is the protection. AC circuit breakers are available for all power levels and normally extinguish a short-circuit current after 10-100ms, taking advantage of the natural zero crossing in an AC network. Today, the strongest argument against a DC based transmission system is the fact that present circuit breaker technology is not available for high powers. Since the natural zero crossing in DC does not exist, active semiconductor devices that turn off the current have to be used. The technology for DC circuit breaker is not yet as mature as for AC, many circuit breakers have been proposed [8,9], but not yet commercialised.

## 1.3 Objectives

When classical voltage transformation devices reach their optimal design and the limits of their capacities, new aspects from decentralised generation using DC voltage levels are expected to influence the general concept of power exchange between generators and consumers.

On the base of the previously given reflections and arguments, the proposal of a study is made for a MVDC energy collection and distribution grid. Indispensable voltage shift stages based on Medium Frequency (MF) power electronic transformations will be studied, where a large potential for secure, flexible and efficient power flow exists. New power electronic converter concepts are expected to become attractive solutions against the sensible aspect of the short-circuit behaviour of classical DC links and lines.

In particular the following points will be analysed in this thesis:

- DC collection networks and their properties and advantages

- New means of bidirectional interface converters between HV, MV, and LV

- Controllability and voltage boosting capacity of converters with important voltage step-up ratios is analysed

- Practical work will validate the proposed concepts

### 1.4 Outline

This work is organised in two parts and 9 chapters.

The first part is dedicated to DC collection and distribution grids, and illustrates the advantages of a DC system:

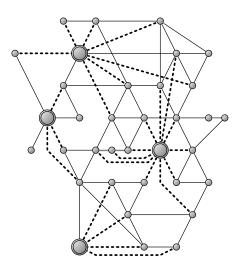

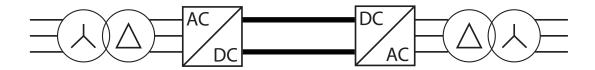

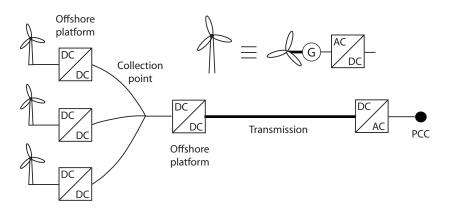

- In chapter 2, DC grids are compared to AC grids regarding efficiency and power transport capability. Three application fields are presented, where a DC grid could be employed. An AC and DC load flow is performed for each of the three collection and distribution grids and the losses are compared.

- Chapter 3 identifies the requirements to realise such DC networks and analyses possible converter candidates for the voltage adaptation. It has been found that the common drawback of the state of the art converters lies in the protection.

In the second part a converter topology, capable of coping with the short-comings of the conventional converter topologies regarding protection is presented:

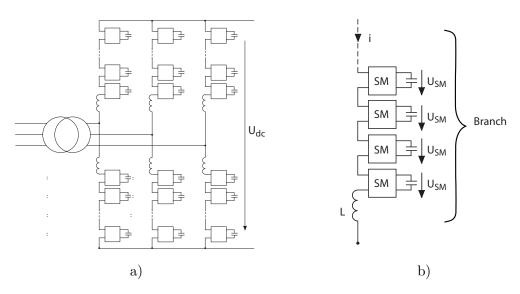

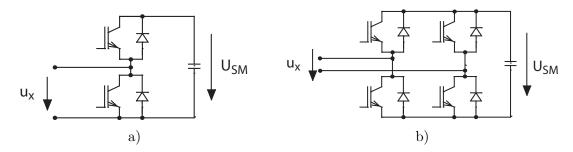

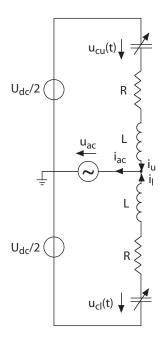

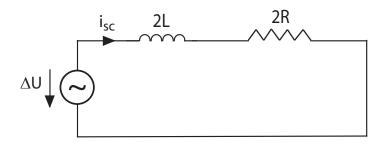

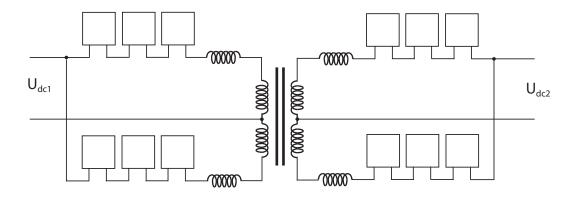

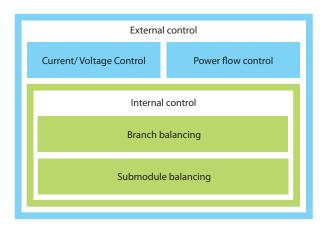

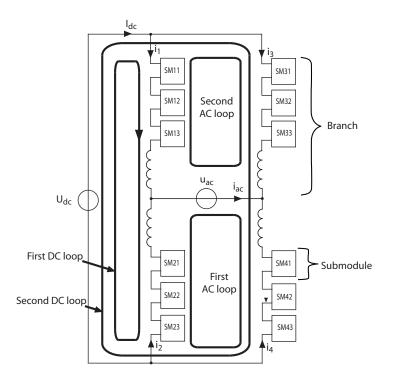

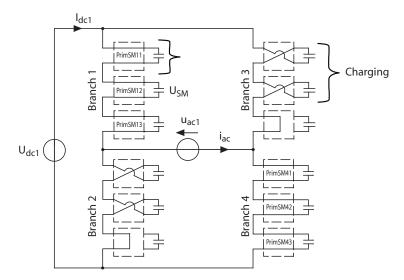

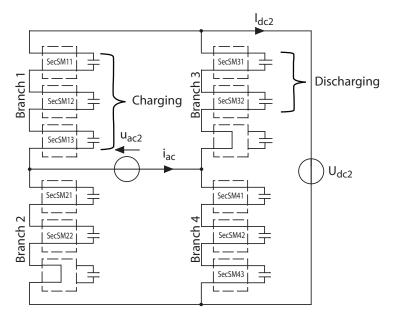

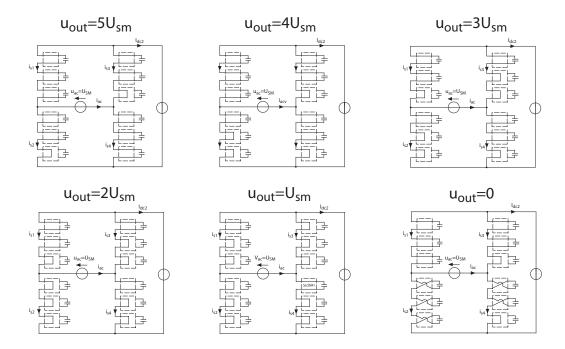

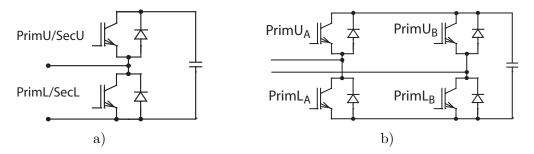

• Chapter 4 introduces the Modular Multilevel Converter (MMC), which is a part of the proposed DC/DC converter structure. The possible modulation methods are described and a mathematical model is established. The internal control methods are depicted and the component sizing is tackled.

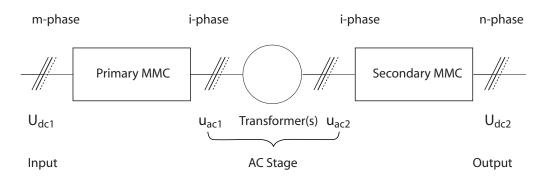

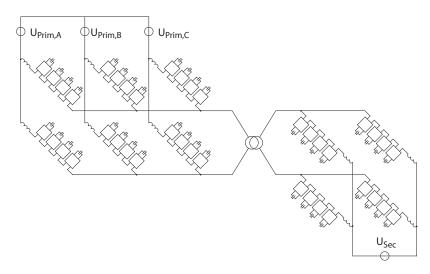

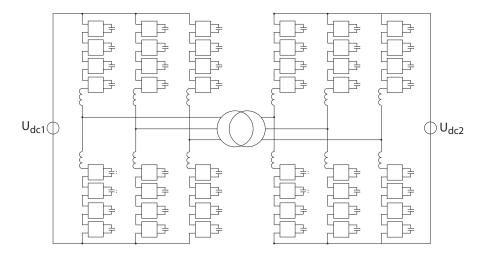

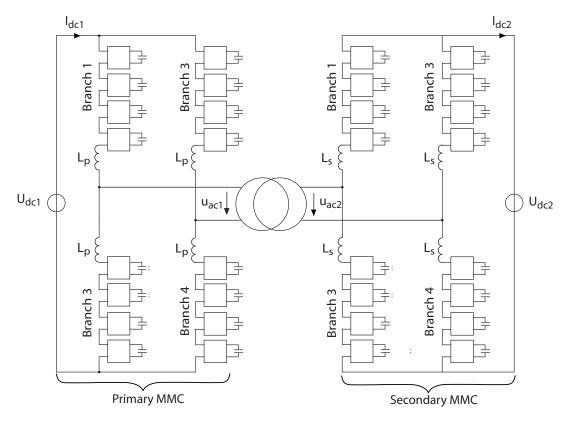

- In chapter 5, the modular DC/DC structure is presented. The mathematical model for this particular structure is derived and a formal parameter design is proposed.

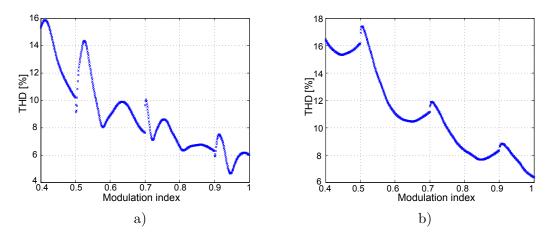

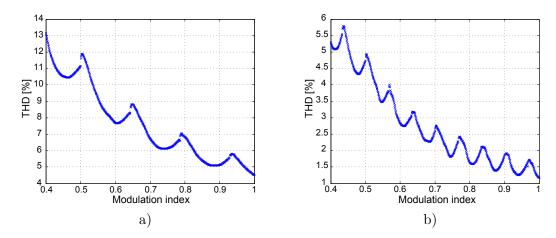

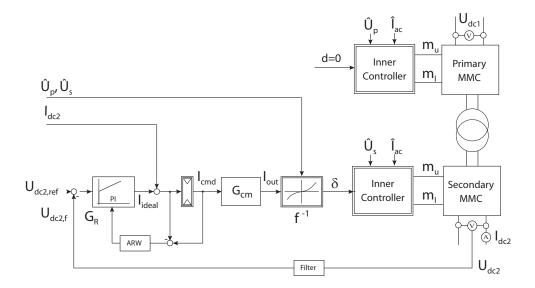

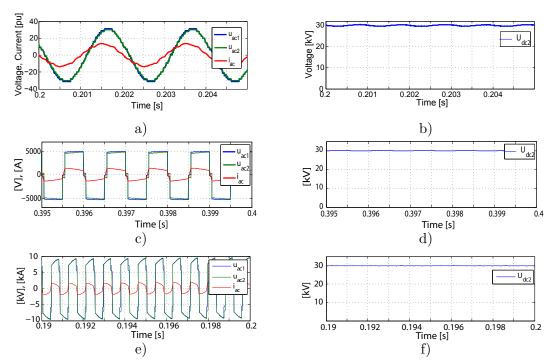

- Chapter 6 is the main contribution of the thesis, which explains the converter operation. Section 6.1 focuses on the multilevel modulation method applied to the DC/DC converter. Two fundamental switching frequency modulation methods are compared in terms of harmonic performance. The strategies for the internal and external control are detailed. Simulation results are shown and a start-up strategy is proposed.

An alternative modulation method based on a two-level modulation is shown in section 6.2. This method can achieve very high voltage elevation factors without using the transformer as voltage elevation device. Again the internal and external control is explained. Simulation results confirm the theoretical developments. The description of the start-up strategy completes this chapter.

The protection issues of DC networks are approached in section 6.3. The proposed structure is compared to a state of the art DC/DC converter for different faults.

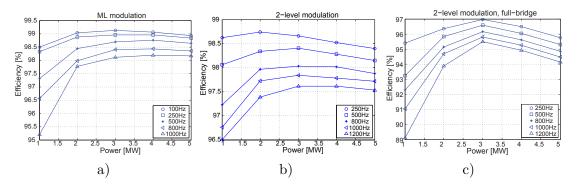

- In chapter 7, the efficiency of the topology is analysed. In section 7.1, a short description of the transformer design procedure is given and finally different designs are compared in terms of weight and loss distribution.

Section 7.2 focuses on the losses created by the semiconductors. First the utilised evaluation method is described and then the different modulation methods are compared in terms of losses for a particular case.

- The laboratory prototype is depicted in chapter 8. Results are obtained for both the multilevel and two-level modulation.

- Finally, chapter 9 gives the main conclusions and contributions of this thesis. The achieved objectives are discussed and future work will be pointed out.

# 2 DC Grid Applications and Case Studies

## 2.1 Efficiency of DC Distribution Systems

The efficiency and the power transport capability of MV networks will be investigated in this section. The efficiency of the producing or consuming units will not be considered, since efficiencies of converters depend very much on the actual stand of technology.

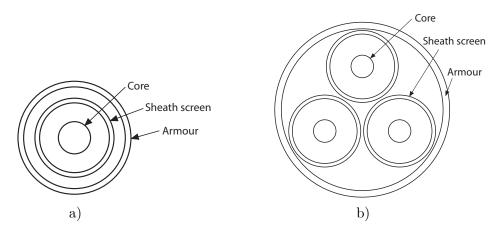

For this study only cable networks will be analysed. Both for offshore and onshore wind farms the collection network are compulsory undersea or in the ground. For solar plants, isolation favours the use of cables instead of open conductors. As far as the MV networks of cities is concerned, power transport is mostly done underground. Cables for AC systems are either single or three-core cables, depicted in Fig. 2.1.

Figure 2.1: a) Single-core cable b) Three-core cables

Typically XLPE-insulated cables are used for isolation, therefore they have been chosen for the following analysis. The considered cables have a layer of heavy armour on the outside to give added strength both for laying and for protecting against mechanical damage. The electromagnetic effects between the layers within the cable need to be

considered carefully when developing impedance models. Cables behave differently for AC than for DC, several effects have to be taken into consideration, which will be explained in the following.

#### 2.1.1 Cable Parameters

A cable is determined by four parameters: resistance, inductance, capacitance and conductance, which can be influenced by various effects.

### Cable Resistance

The line resistance  $R_{dc}$  is determined by the following formula

$$R_{dc} = \frac{\rho l}{A} \tag{2.1}$$

where  $\rho$  is the resistivity of the conductor, l is the cable length and A the cross-sectional area. The current in the conductor is equally distributed only for DC currents.

The Temperature Effect The resistivity of a conductor varies linearly with the temperature over the normal range of operation, given in the following equation.

$$R_{th} = R_{dc} \left( 1 + \alpha (T - T_0) \right) \tag{2.2}$$

where  $\alpha$  stands for the temperature coefficient of the material. T is the temperature in Kelvin and  $T_0$  is the initial temperature.

The Skin Effect The non-uniform current distribution in conductors carrying alternative current is due to the skin effect. With higher frequency the current density is increased near the surface, since the conductor centre will be enveloped by a greater magnetic field. In Fig. 2.2 the skin effect in a single conductor is depicted, the darker the region, the higher the current density.

The skin effect makes the effective resistance of a cable depended on the frequency. The problem is one-dimensional in cylindrical coordinates and depends only on the radius  $\rho$ .

Figure 2.2: Skin effect

Using the Maxwell equations a relation for the current density can be found in (2.3) [11].

$$\frac{1}{\rho} \frac{d}{d\rho} \left( \rho \frac{d\underline{J}_z(\rho)}{d\rho} \right) - j\omega\mu\sigma\underline{J}_z(\rho) \cong 0$$

(2.3)

The solution of this equation is a  $J_0$ -type Bessel function of order 0. The current distribution within the conductor is characterised by the skin depth, defined in (2.4).  $\mu$  is the conductivity of the conductor in [S/m].

$$\delta = \sqrt{2/\omega\mu\sigma} \tag{2.4}$$

Below this depth the current density decays to  $1/e \approx 0.37$  of the current density at the surface  $J_0$ .  $\mu = \mu_0 \mu_r$  is the absolute magnetic permeability of the conductor,  $\mu_0$  is the permeability of free space  $(4\pi 10^{-7} NA^{-2})$  and  $\mu_r$  is the relative permeability of the conductor (for a copper conductor  $\mu_r = 1$ ).

The relation (2.4) can be simplified, considering that the equivalent current conducting space is a hollow tube, with a thickness of  $\delta_s$  carrying direct current [12].  $R'_{ac}$  is the effective resistance for the AC system.

$$R'_{ac} = \frac{1}{\sigma_r \pi \delta_s (2r - \delta_s)} \tag{2.5}$$

This approximation is only valid for cables with pronounced skin effect  $(r \gg \delta_s)$ .

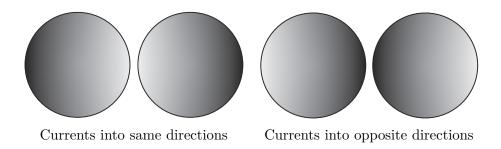

The Proximity Effect The proximity effect is often ignored when treating cable impedance models. It occurs when two conductors are situated closely together and their

magnetic fields are influencing each other. The current is not equally distributed on the surface and can either be on the outer side of the conductor (current in the same direction) or the inner side of the conductor (current in opposite direction). Fig. 2.3 displays this effect.

Figure 2.3: Proximity effect on two conductors

It has been shown in [11] that the proximity effect for single-core cables can be ignored, but not for three-core cables. For single-core cables only the skin effect has to be taken into account; for three-core cable, both, skin and proximity effect need to be taken into account. For calculating the proximity effect of three-core cables which are used for offshore energy collection, knowledge of the cable geometry is fundamental. The shielding and the layer arrangements can have an important impact on whether the proximity effect is influential or not. Since the proper determination of the proximity effect will exceed the frame of this thesis, it will only be referred to the development in [11].

Empirical Approach to Skin and Proximity Effect A somewhat more empiric approach is given in [13]. Skin and proximity effect are summarised to a factor  $y_{skin}$  and  $y_{proximity}$  depending on the frequency which is multiplied with the DC resistance.

$$R_{ac} = R_{dc}(1 + y_{skin} + y_{proximity}) (2.6)$$

The skin effect factor is given in (2.7) for single or multi-core conductors.

$$y_{skin} = \frac{x_s^4}{192 + x_s^4} \tag{2.7}$$

The proximity effect for a single-core cable can be described as follows:

$$y_{proximity} = 2.9 \frac{x_p^4}{192 + 0.8x_p^4} \frac{d_c^2}{S^2}$$

(2.8)

The proximity effect for a three-core cable can be described as follows:

$$y_{proximity} = \frac{x_p^4}{192 + 0.8x_p^4} \frac{d_c^2}{S^2} \left( 0.312 \frac{d_c^2}{S^2} + \frac{1.18}{\frac{x_p^4}{192 + 0.8x_p^4} + 0.27} \right)$$

(2.9)

where

- $x_s^2 = 8\pi f 10^{-7} \frac{k_s}{R_{dc}}$

- $x_p^2 = 8\pi f 10^{-7} \frac{k_p}{R_{dc}}$

- $k_s$ : Factor determined by conductor construction. 1 for circular, stranded compacted and sectored conductor.

- f: Frequency [Hz]

- $k_p$ : Factor determined by conductor construction ( $k_p = 1$  for circular, stranded and sectored conductors,  $k_p = 0.8$  if the conductor is dried and impregnated)

- $d_c$ : Diameter of conductor [mm]

- $R_{dc}$ : DC resistance at operating temperature T

- S: Spacing between conductor centres [mm]

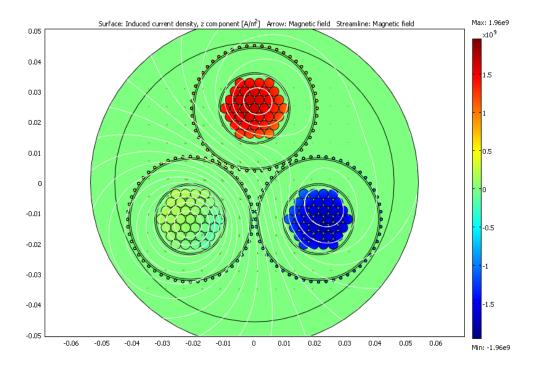

Generally for a 50Hz power network, the increase of the AC resistance is about 2%. Fig. 2.4 shows the proximity and the skin on a three-core cable used in a three phase system.

**Stranded Conductors** Since the strands within a cable are twisted, the DC resistance is not corresponding exactly to the cables length times the distributed resistance, but is about 1% higher [14].

Figure 2.4: Proximity and skin effect on a three-core cable (Nexans  $300mm^2$ )

#### Cable Inductance

A rather easy evaluation of the cable inductances can be found by applying the "mean geometric distance"  $g_{ij}$  between two conductors i and j and the "mean geometric radius"  $g_{ii}$  introduced by Maxwell [15].

The mutual inductance per unit length of a conductor can so be defined [16].

$$M'_{ij} = \frac{\mu_0}{2\pi} \ln \frac{g_{in}g_{jn}}{g_{ij}g_{nn}} \tag{2.10}$$

The self inductance is defined by

$$M'_{ii} = \frac{\mu_0}{2\pi} \ln \frac{g_{in}^2}{g_{ii}g_{nn}} \tag{2.11}$$

**Three-Core Cable** The symmetric structure of the three-core, three-phase cable allows to introduce the cyclic inductance  $L'_i = M'_{ii} - M'_{ij}$ . This is only valid for systems that respect the equation  $i_1 + i_2 + i_3 = 0$  and for which the mutual inductance  $M'_{ij}$  is

identical for the three phases. The cyclic inductance  $L'_i$  per unit length of this cable, depicted in Fig. 2.1 is given in (2.12).

$$L_i' = \frac{\mu_0}{2\pi} \left( \ln \frac{2 * D_{12}}{d} + \frac{1}{4} \right) \tag{2.12}$$

where

- $\mu_0$ : permeability of free space

- $D_{12}$ : centre to centre distance of two conductors

- d: conductor diameter

## Cable Capacitance

Capacitance is the ability to store electrical energy in a dielectric media due to a potential difference between two conductors. A capacitive effect can take place between the conductor and the sea and soil, as well as with the armouring and sheathing. In contrast to overhead lines, where reactive power is consumed, cabled conductors are producing reactive power because the cable capacitance is much higher. This capacitance has several important impacts on system design and operation. For an AC system, the capacitive reactive power produced in the line has an impact on the reactive power balance of the feeder and the whole distribution system. The large charging current of cable networks may also hinder the operation of MV network circuit breakers even in a lightly loaded system [17]. As the total length of the MV feeder system is known, it is possible to evaluate the requirements for reactive power compensation and earth fault current compensation and/or the earthing impedance.

For a DC transmission system, a capacitive cabled line provides can be exploited to reduce the size of the DC capacitor bank required for providing DC voltage stability and for filtering of the switching noise [11]. (2.13) indicates the capacitance per unit length C' for a cable [18].

$$C' = \frac{2\pi\epsilon_0\epsilon}{\ln\left(\frac{D}{d}\right)} \tag{2.13}$$

- $\epsilon_0 = \frac{10^{-9}}{36\pi} \frac{F}{m}$ : permittivity of free space

- $\epsilon$ : relative dielectric constant of the insulation (2.4 for XLPE)

- D: outer diameter including insulation

- d: inner diameter without insulation

## Equivalent Model for the Cable

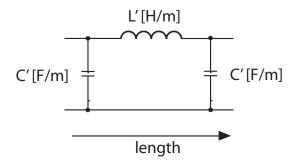

With the parameters given above an equivalent model for the cable can be established. For this work the equivalent  $\pi$ -model is selected, depicted in Fig. 2.5.

Figure 2.5:  $\pi$ -model of the power cable

# 2.1.2 Current Carrying Capacity

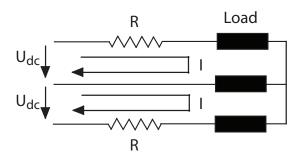

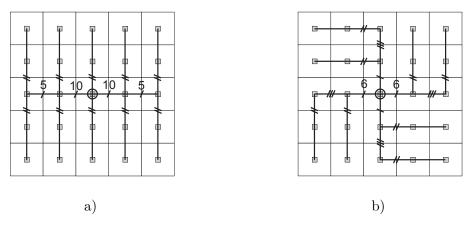

In an AC network, much more attention is allocated to the line reactance and often the line resistance is neglected. However, for DC systems the line reactance is non-existent which leads to a much higher power transport capability [19]. To have a mean of comparison, cables with the same characteristics are going to be used for AC and DC, i.e. a three phase cable is used for AC without a neutral conductor. For the DC system, the same cable is used in a bipolar way with a positive, a neutral and a negative pole such as depicted in Fig. 2.6. The central conductor is the neutral and for a balanced system there should not be any current in this conductor.

Figure 2.6: Three line DC model

## Limitation of Power Flow due to the Resistive Losses

The maximum current in a conductor is determined by the maximum operating temperature. The temperature in a conductor increases due to the ohmic losses in the conductor. The maximal current for a given cable for either AC or DC transmission is found by determining and comparing the conduction losses for both cases. The losses for a three phase AC system or DC system are given in (2.15).  $R_{ac,90^{\circ}\text{C}}$  respectively  $R_{dc,90^{\circ}\text{C}}$  is the equivalent line resistance of the AC respectively DC system at 90 °C.

$$\Delta P_{ac,3} = 3R_{ac,90} \circ_{\rm C} I_{ac,3}^2 \tag{2.14}$$

$$\Delta P_{dc} = 2R_{dc,90^{\circ}\text{C}}I_{dc}^2 \tag{2.15}$$

Working at the limit of operation for both AC and DC systems results in equal losses  $\Delta P_{AC,3} = \Delta P_{DC} = \Delta P_{max}$ ). From this assumption the ratio of the AC and DC current can be determined. [20] gives a more thorough analysis of the losses of three phase cable dependent on the temperature.

$$\frac{I_{dc}}{I_{ac,3}} = \sqrt{\frac{3}{2} \frac{R_{ac,90}}{R_{dc,90}}} \approx \sqrt{\frac{3}{2}}$$

(2.16)

In order to simplify the above equation, the skin and proximity effect are neglected (around 3% only) and the AC resistance is supposed to be equal to the DC resistance.

Since the three phase cable is used in a bipolar way (see Fig. 2.6), the maximum DC voltage is twice the phase-neutral voltage of the three phase cable.

$$U_{dc} = 2\sqrt{\frac{2}{3}}U_{ac,3} \tag{2.17}$$

The power transport for AC and for DC is depicted in (2.18) and (2.19).

$$P_{ac,3} = \sqrt{3}I_{ac,3}U_{ac,3}\cos\phi \tag{2.18}$$

$$P_{dc} = I_{dc}U_{dc} \tag{2.19}$$

With the help of (2.16), (2.17), (2.18) and (2.19), the ratio of AC and DC power transport

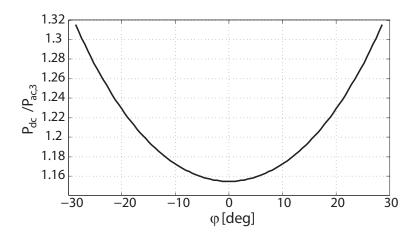

can be determined in (2.20). Fig. 2.7 illustrates the power transport capability dependent on the phase angle. However, one needs to take into account that this calculation does not consider the reactive energy needs of the cable, which can demand a certain value for  $\cos \phi$ . This will be analysed further in the following.

$$\frac{P_{dc}}{P_{ac,3}} = \frac{2}{\sqrt{3}\cos\phi} \tag{2.20}$$

Figure 2.7: Ratio of AC and DC power transport

## Limitation of Power Flow due to the Reactive Power

**DC Power Transport** The transported power for a DC system can be expressed as the difference between input power and cable losses. R' is the metric resistance of the cable in  $\Omega/m$  and l is the length of the cable.

$$P_{dc} = U_{dc}I_{dc} - 2I_{dc}^2R'l (2.21)$$

(2.21) is valid for a three line system, such as depicted in Fig. 2.6.

AC Power Transport Electrical lines for AC transmission can only be used within certain limits. For example, the phase difference between two points should not exceed a given angle, defined by the cable parameters and the transmitted power, since the maximum voltage and current should be respected. The active power transported by a three-phase AC system is limited not only by the resistive losses, but also by the reactive

losses, since the reactive current in a line produces also resistive losses.

The transported complex apparent power can be described as the difference of input power and losses.

$$\underline{S}_{ac} = 3U_p I_l^* - (P_{losses} + jQ_{losses}) = P_{ac} + jQ_{ac}$$

(2.22)

with

$$P_{losses} = 3R'lI_l^2 (2.23)$$

$$Q_{losses} = 3\omega L' l l_l^2 - 3\omega C' l \frac{U_p^2 + U_q^2}{2}$$

(2.24)

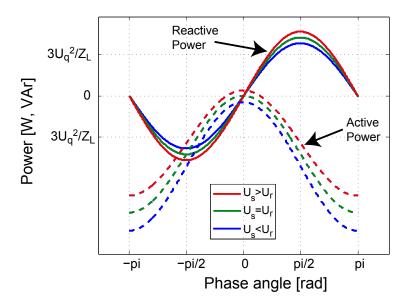

Considering a  $\pi$ -section model of a transmission line, represented in Fig. 2.5, the power transfer from the sending port (s) to the receiving port (r) is expressed in (2.26).

$$P_{sr} = \frac{3|U_s|^2}{|Z_l|} \left( \cos(\phi_l) - \frac{|U_r|}{|U_s|} \cos(\theta_{sr} - \phi_l) \right)$$

(2.25)

$$Q_{sr} = \frac{3|U_s|^2}{|Z_l|} \left( \sin(\phi_l) + \frac{|U_r|}{|U_s|} \sin(\theta_{sr} - \phi_l) \right) + 3U_q^2 B_t / 2$$

(2.26)

In the equations derived above, the equivalent  $\pi$ -model has been used for the long transmission line, for which the parameters  $Z_l$  and  $\phi_l$  are given in the following equation.

$$\underline{Z}_l = R'l + j\omega L'l = R_l + jX_l \tag{2.27}$$

$$\phi_l = \arctan \frac{\omega L'}{R'} \tag{2.28}$$

$$\underline{B}_t = j\omega C'l \tag{2.29}$$

$\theta_{SR}$  = Phase shift between the voltages at both ends

Fig. 2.8 explains the needed compensation of reactive power. The more active power is transported, the more reactive power must be injected to keep the voltages at the extremities constant. Often the loads consume reactive power, which must be transported in addition.

A line or a network can be operated trying to keep all the voltages constant. This means

Figure 2.8: Transportable AC power in a power cable

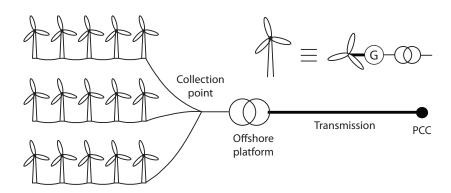

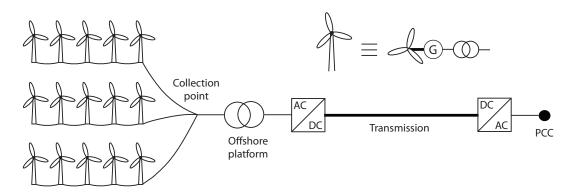

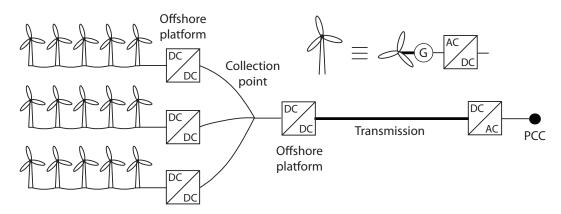

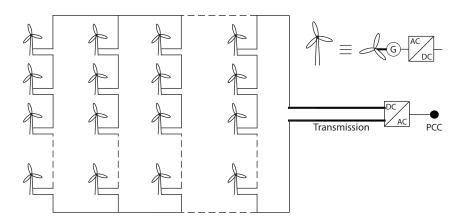

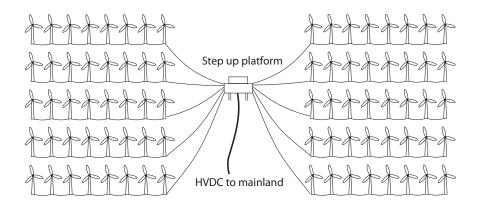

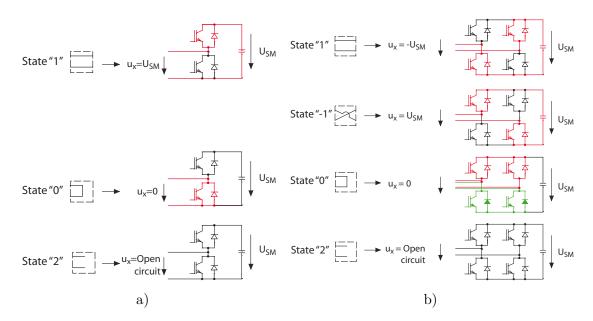

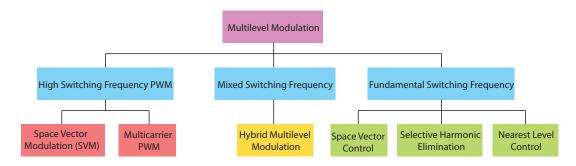

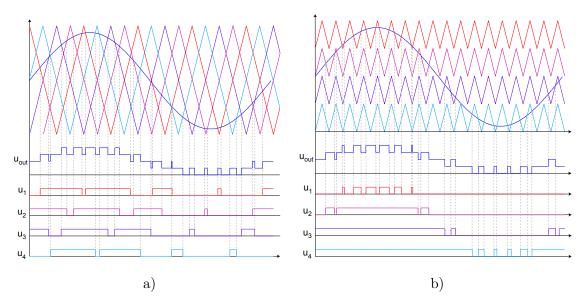

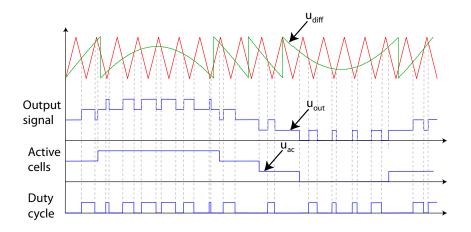

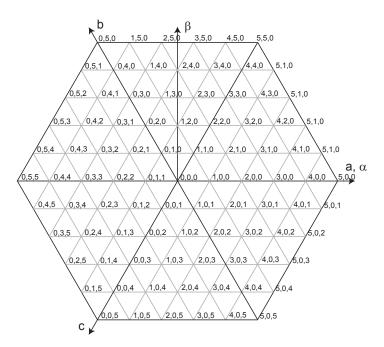

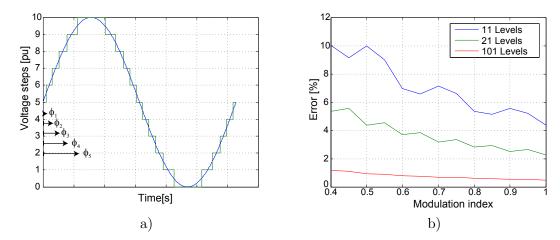

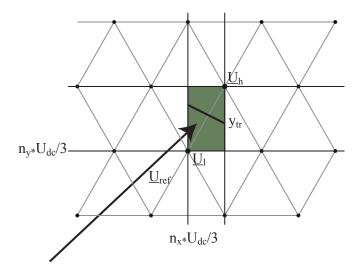

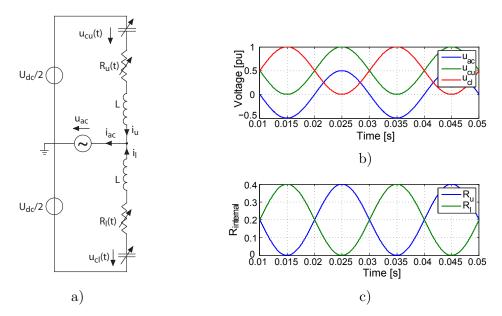

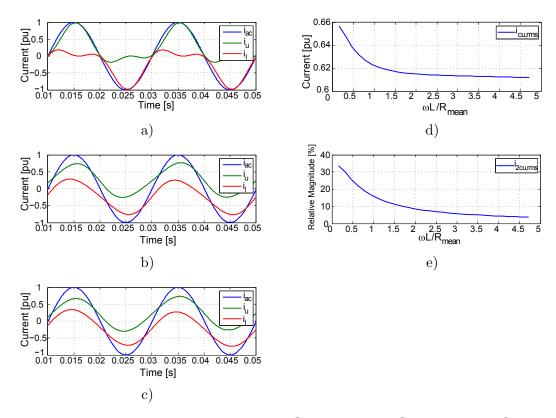

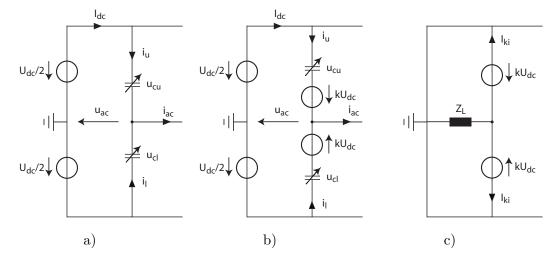

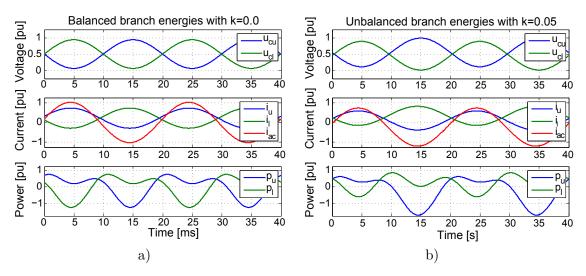

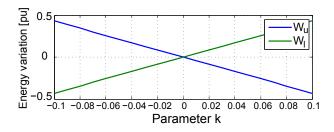

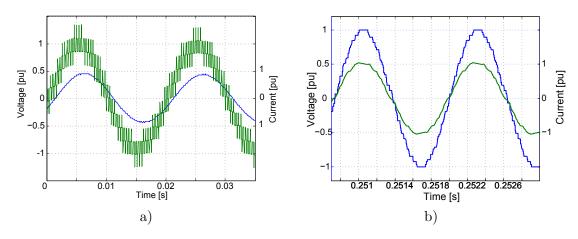

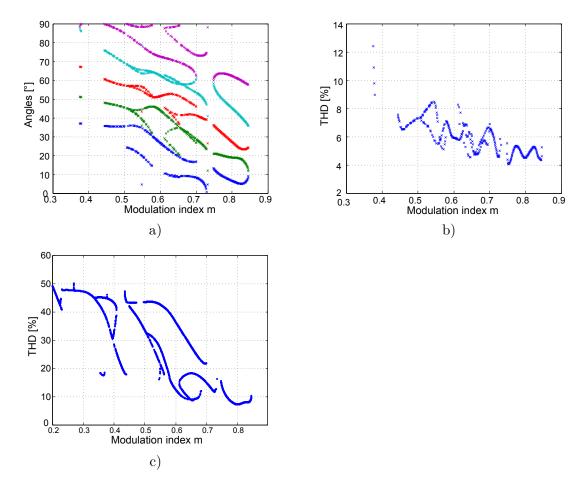

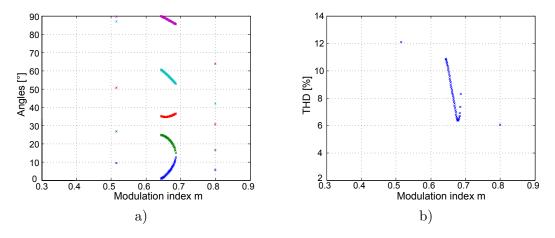

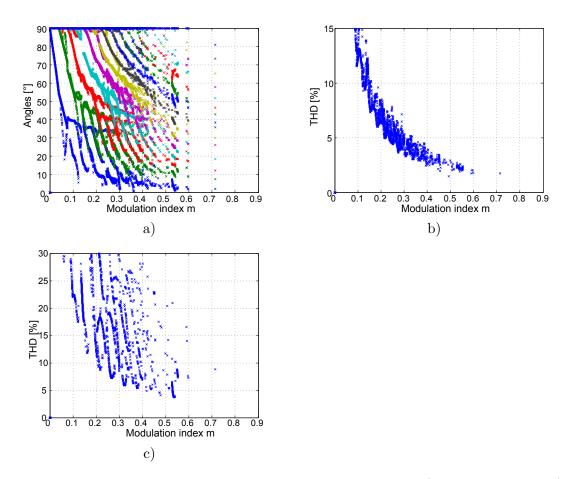

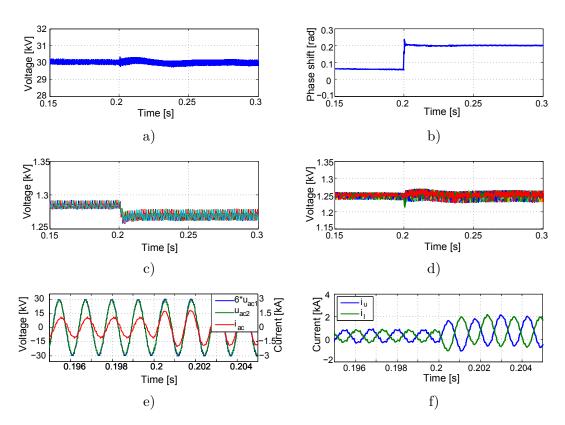

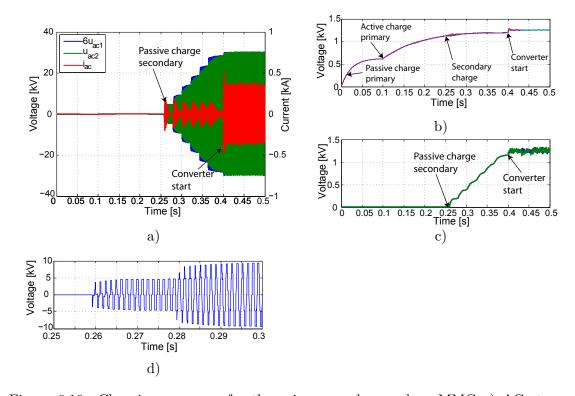

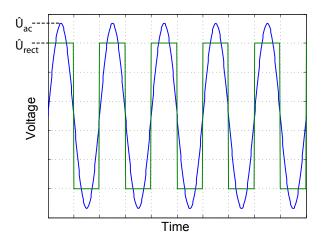

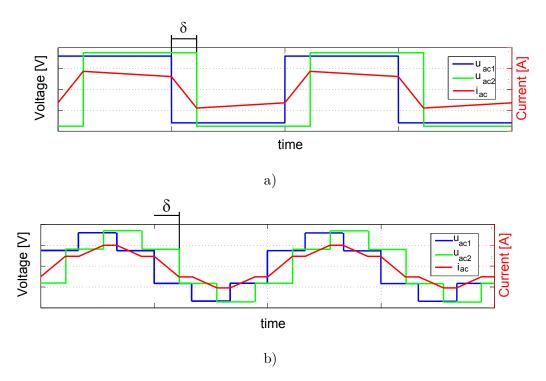

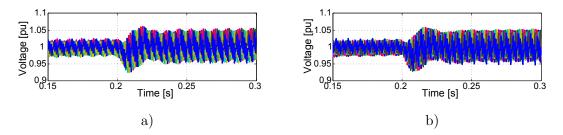

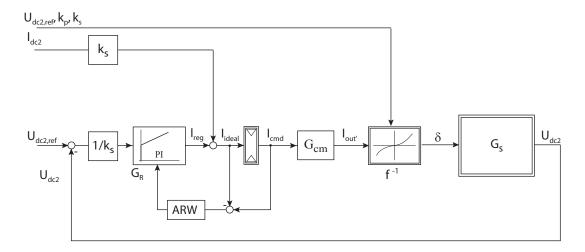

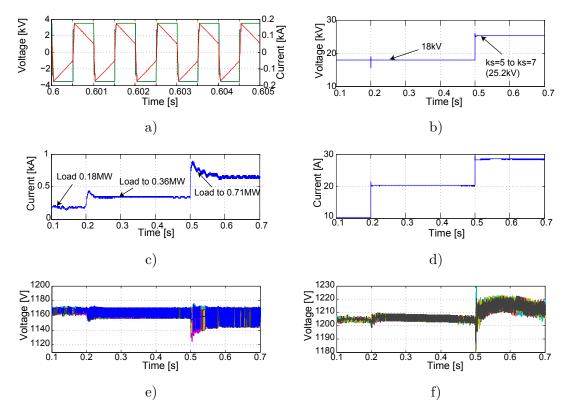

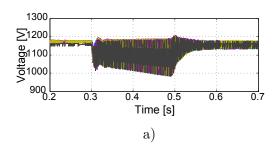

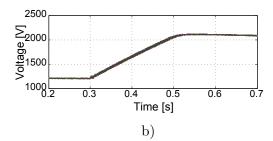

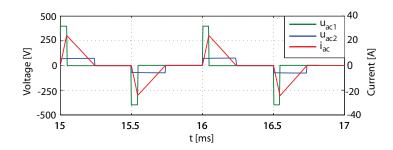

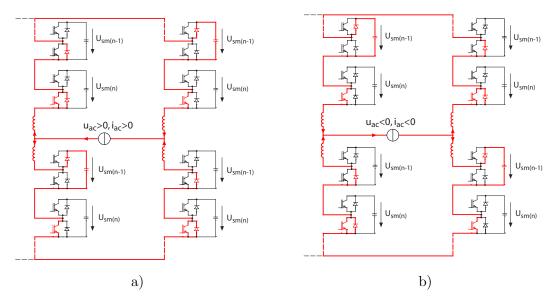

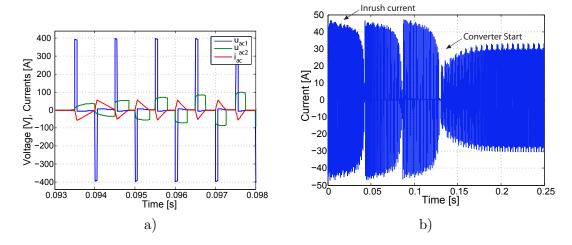

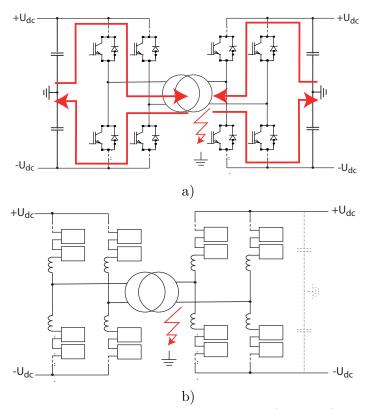

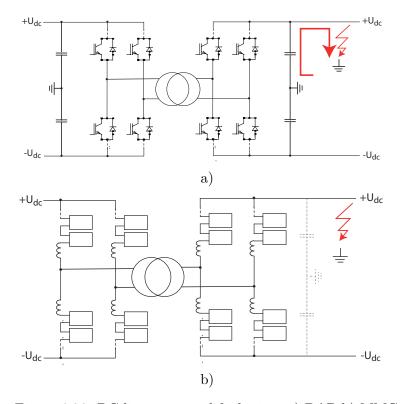

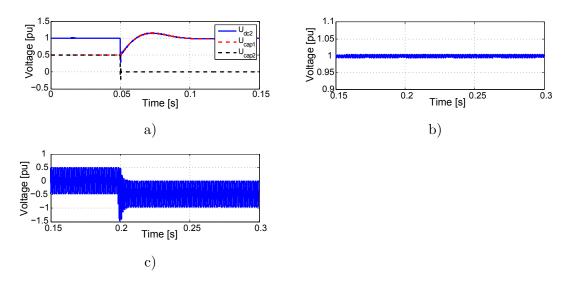

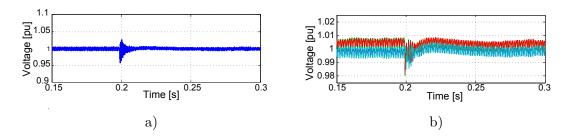

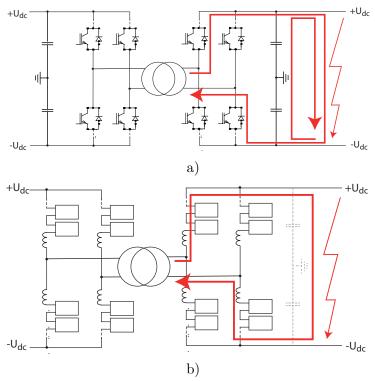

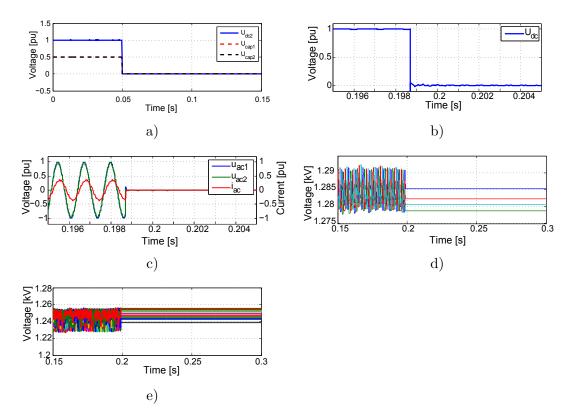

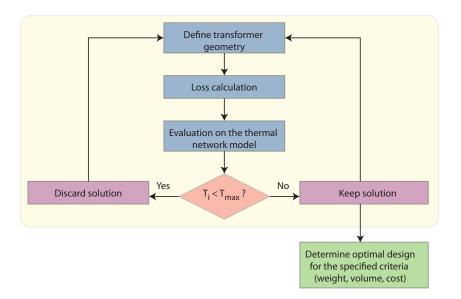

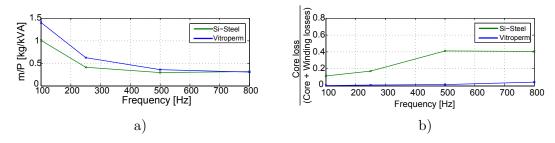

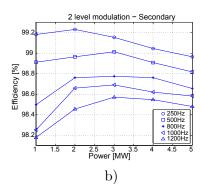

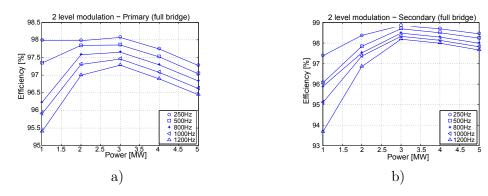

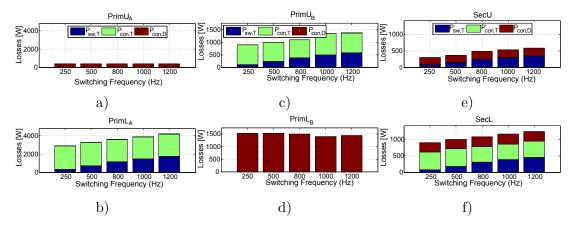

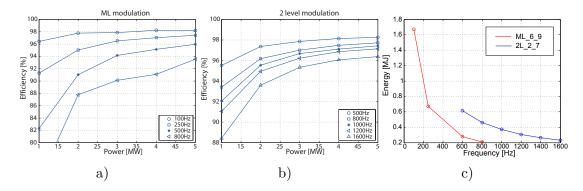

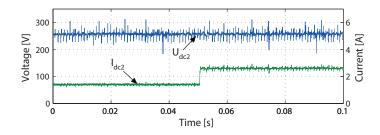

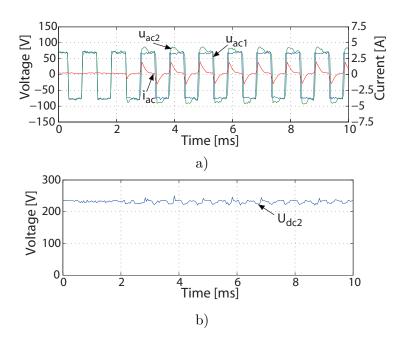

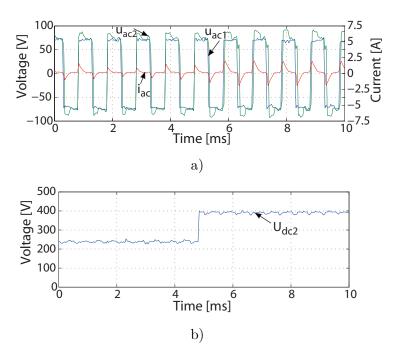

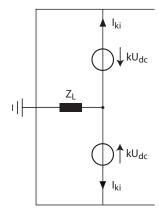

that somehow reactive power needs to be introduced to compensate the voltage drop. If the receiving end is not consuming any reactive power, so we can set  $Q_{ac} = 0$ . This implicates that the reactive power consumption of the line needs to be compensated by the input. The reactive power for the voltage compensation flows into the opposite direction of the active power flow.