# Formalizing and Verifying Transactional Memories

THÈSE Nº 4541 (2009)

PRÉSENTÉE LE 7 AVRIL 2010 À LA FACULTE INFORMATIQUE ET COMMUNICATIONS LABORATOIRE DE MODÈLES ET THÉORIE DE CALCULS PROGRAMME DOCTORAL EN INFORMATIQUE, COMMUNICATIONS ET INFORMATION

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Vasu Singh

acceptée sur proposition du jury:

Prof. B. Faltings, président du jury Prof. T. Henzinger, directeur de thèse Prof. R. Alur, rapporteur Prof. H. Attiya, rapporteur Prof. R. Guerraoui, rapporteur

# Abstract

Transactional memory (TM) has shown potential to simplify the task of writing concurrent programs. TM shifts the burden of managing concurrency from the programmer to the TM algorithm. The correctness of TM algorithms is generally proved manually. The goal of this thesis is to provide the mathematical and software tools to automatically verify TM algorithms under realistic memory models.

Our first contribution is to develop a mathematical framework to capture the behavior of TM algorithms and the required correctness properties. We consider the safety property of opacity and the liveness properties of obstruction freedom and livelock freedom. We build a specification language of opacity. We build a framework to express hardware relaxed memory models. We develop a new high-level language, Relaxed Memory Language (RML), for expressing concurrent algorithms with a hardware-level atomicity of instructions, whose semantics is parametrized by various relaxed memory models. We express TM algorithms like TL2, DSTM, and McRT STM in our framework.

The verification of TM algorithms is difficult because of the unbounded number, length, and delay of concurrent transactions and the unbounded size of the memory. The second contribution of the thesis is to identify structural properties of TM algorithms which allow us to reduce the unbounded verification problem to a language-inclusion check between two finite state systems. We show that common TM algorithms satisfy these structural properties.

The third contribution of the thesis is our tool FOIL for model checking TM algorithms. FOIL takes as input the RML description of a TM algorithm and the description of a memory model. FOIL uses the operational semantics of RML to compute the language of the TM algorithm for two threads and two variables. FOIL then checks whether the language of the TM algorithm is included in the specification language of opacity. FOIL automatically determines the locations of fences, which if inserted, ensure the correctness of the TM algorithm under the given memory model. We use FOIL to verify DSTM, TL2, and McRT STM under the memory models of sequential consistency, total store order, partial store order, and relaxed memory order.

**Keywords:** Concurrency, Transactional memories, Semantics, Specification, Software verification, Model checking, Relaxed memory models.

# Résumé

Les Mémoires Transactionnelles (MT) ont démontré un grand potentiel pour simplifier l'écriture de programmes concurrents. Les MT évitent aux programmeurs de se préoccuper de la concurrence, qui est gérée au niveau des algorithmes de MT elles-mêmes. La correction des algorithmes de MT est généralement prouvée manuellement. Le but de cette thèse est de donner des outils à la fois mathématiques et logiciels pour vérifier par *model checking* les algorithmes de MT supposant un modèle de mémoire faible.

Notre première contribution est de développer des outils mathématiques pour exprimer le comportement des algorithmes de MT et les propriétés de correction requises. Nous nous intéressons à la fois à des propriétés de sûreté, comme l'opacité, et de vivacité, comme la non-obstruction et l'abscence de *livelock*. De plus, nous construisons un outil logiciel pour exprimer les modèles mémoires matériels dits faibles. Nous développons un nouveau langage de haut niveau, RML, pour exprimer les algorithmes concurrents avec un niveau matériel d'atomicité des instructions, et dont la sémantique est paramétrée par de nombreux modèles mémoires faibles. Nous exprimons les algorithmes MT comme TL2, DSTM et McRT SRT dans notre nouveau langage, RML.

La vérification des algorithmes de MT est difficile à cause du nombre illimité de transactions concurrentes, de la durée et des délais non-bornés d'une transactions et de la taille non-bornée de la mémoire. La deuxième contribution de cette thèse est d'identifier les propriétés des algorithmes MT qui permettent de réduire le problème de vérification d'un modèle infini au problème d'inclusion de langage de deux machines d'états finies. Nous montrons que les algorithmes de MT usuels satisfont ces propriétés.

La troisième contribution de cette thèse est notre outil FOIL pour la vérification par *model checking* des algorithmes de MT. FOIL prend comme entrée la description RML d'un algorithme de MT et le description du modèle mémoire. FOIL utilise la sémantique opérationnelle de RML pour calculer le langage de l'algorithme de MT pour deux fils d'exécution et deux variables. FOIL contrôle ensuite si le langage de l'algorithme de MT est inclus ou non dans le langage de la spécification. FOIL détermine automatiquement les emplacements des barrières, qui, si elles sont insérées, assure la correction de l'algorithme de MT dans le modèle mémoire donné. Nous utilisons FOIL pour

vérifier les algorithmes DSTM, TL2 et McRT STM dans des modèles mémoires à cohérence séquentielle, ordre total des écritures, ordre partiel des écritures et ordre mémoire affaibli.

**Mots clés :** Concurrence, mémoire transactionnelle, sémantique, spécification, vérification de logiciels, model checking, modèles mémoires faibles.

# Acknowledgments

Today, the achievement that I am most proud of is that I had Tom as the supervisor for my PhD. I was completely new to the field of verification and theoretical computer science when I started working with Tom. It was Tom's simple way of doing profound research and his devotion to his students that made me comfortable in my doctoral studies over time. Tom taught me the importance of being precise and formal in my ideas. Tom improved my writing skills beyond recognition. Moreover, getting to know Tom as the kind and wonderful person he is, was a great pleasure.

I have been fortunate to have Rachid as a co-author for my publications. He always encouraged me to put in the best effort and target the top conferences in the field. Rachid taught me how to present new ideas in research to others. I also thank the thesis reviewers, Hagit and Rajeev, for taking the time to read my thesis and being a part of the jury.

I take this opportunity to thank my family for the many things that I, in childhood, assumed came with a family; but after growing up, realized that I was fortunate to have those things. The love and affection of my mother made my childhood so memorable. She taught me how to make the best effort and expect the least returns. My father taught me many important things, of which I find two things hard not to mention. One is adjustment to any circumstances in life, and another is the value of time. These things made my life simpler and my work more efficient. I wonder if any father devotes so much time and energy to his children. I have also been lucky to have an elder brother and an elder sister. My brother, eight years elder to me, enjoyed teaching me engineering mechanics while I was in secondary school. Although I understood just a part of what he taught, I thank him for developing in me an ability to grasp new knowledge faster. I am also thankful to my brother's family (my sister-in-law, my niece, and my nephew) for their patience during the time I could not visit them for the last 2 years. My elder sister helped me with my school homework, and taught me new and interesting things throughout my childhood. It took me years to learn to live without her. I am grateful to her family (my brother-in-law, and my two nieces) for keeping me so close to their hearts even when I have been so distant. Without my wife, I would not have been able to finish my doctorate with this peace and balance of mind. She always stood by me and adjusted herself with my deadlines and travel plans. I also express gratitude to my parents-in-law and my sister-in-law for their support, love, and affection.

I extend my gratitude to Dirk, Grégory, Maria, Nir and all other colleagues for keeping EPFL a place I loved to work at. I thank Dirk for boosting my confidence in my early days of working in the field of verification. I cannot thank Sylvie enough for all her administrative help, including the phone calls on my behalf when my modest French vocabulary was insufficient. I thank Fabien for the flawless and powerful IT infrastructure setup.

Last but not the least, I thank the Swiss National Science Foundation and EPFL for supporting my doctoral studies. I spent five great years at EPFL. The resources and the work environment provided at EPFL are certainly among the best in the world. I enjoyed living in the beautiful city of Lausanne. The serene views of Lac Léman from the shores in St. Sulpice are unforgettable. I felt proud to be a part of Switzerland during my stay. The Swiss impressed me with the importance they give to safety, quality, and preserving the environment. I loved the efficiency of the unmatched Swiss public transport, which I thoroughly used to visit the farthest and the prettiest corners of the country. To Amma, Appa, and Tina

# Contents

| Abstract                                                                                 | i    |

|------------------------------------------------------------------------------------------|------|

| Résumé                                                                                   | iii  |

| Contents                                                                                 | ix   |

| List of Figures                                                                          | xii  |

| List of Tables                                                                           | xiii |

| List of Algorithms                                                                       | xiv  |

| 1 Introduction                                                                           | 1    |

| 1.1 Parallel Programming                                                                 | 2    |

| 1.2 Transactional Memories                                                               | 2    |

| 1.3 TM Implementations                                                                   | 3    |

| 1.4 Correctness in TM                                                                    |      |

| 1.4.1 Safety                                                                             | 4    |

| 1.4.2 Liveness                                                                           |      |

| 1.5 Relaxed Memory Models                                                                |      |

| 1.6 Problem Statement                                                                    |      |

| 1.6.1 Challenges $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |      |

| 1.6.2 Our approach                                                                       |      |

| 1.7 Generalizing the Notion of Opacity                                                   |      |

| 1.8 Related Work                                                                         |      |

| 1.8.1 Formalisms for transactional memories                                              |      |

| 1.8.2 Formalisms for relaxed memory models                                               |      |

| 1.8.3 Verification tools                                                                 |      |

| 1.9 Organization of the Thesis                                                           |      |

| 2 A Preliminary Formalism                                                                | 15   |

| 2.1 Transactional Programs                                                               | 15   |

| 2.2 Transactional Memories                                                               | 16   |

| 2.2.1 Histories                                                                          | 16   |

|   |            | 2.2.2            | Transactions                                    | 16              |

|---|------------|------------------|-------------------------------------------------|-----------------|

|   |            | 2.2.3            | Safety in TM                                    | 17              |

|   |            | 2.2.4            | Liveness in TM                                  | 18              |

|   | 2.3        | TM S             | pecifications                                   | 18              |

|   |            | 2.3.1            | Construction of TM specifications               | 19              |

|   |            | 2.3.2            | A nondeterministic TM specification for opacity | 20              |

|   |            | 2.3.3            | A deterministic TM specification for opacity    | 24              |

|   | 2.4        | ТМ А             | lgorithms                                       | 27              |

|   |            | 2.4.1            | The Simple language                             | 28              |

|   |            | 2.4.2            | Language of a TM algorithm                      | 29              |

|   |            | 2.4.3            | The transition system of a TM algorithm         | 30              |

|   | 2.5        | Exam             | ples of TM Algorithms                           | 31              |

|   |            | 2.5.1            | Sequential TM                                   | 31              |

|   |            | 2.5.2            | Two phase locking TM                            | 32              |

|   |            | 2.5.3            | Transactional locking II                        | 32              |

|   |            | 2.5.4            | DSTM                                            | 34              |

|   |            |                  |                                                 |                 |

| 3 |            |                  | ry Verification                                 | <b>37</b>       |

|   | 3.1        |                  | l Checking Safety                               | 38              |

|   |            | 3.1.1            | Obtaining a suitable transition system          | 38              |

|   |            | 3.1.2            | Results                                         | 38              |

|   |            | 3.1.3            | Ordering in TL2                                 | 39              |

|   | 3.2        |                  | Checking Liveness                               | 40              |

|   | 3.3        |                  | ding the Verification Results                   | 41              |

|   |            | 3.3.1            | Properties of TM algorithms                     | 41              |

|   |            | 3.3.2            | Checking properties of example TM algorithms    | 42              |

|   |            | 3.3.3            | Structural properties of TM                     | 43              |

|   |            | 3.3.4            | The reduction theorem                           | 45              |

|   | 3.4        |                  | ting the Liveness Verification Problem          | 46              |

|   |            | 3.4.1            | Discussion                                      | 46              |

| 4 | <b>m</b> 1 | <b>D</b>         | -11                                             | 40              |

| 4 | 4.1        | Form             |                                                 | 49              |

|   | 4.1        | 4.1.1            | ework                                           | 49<br>49        |

|   |            |                  | Memory instructions                             | $\frac{49}{50}$ |

|   |            | 4.1.2            | Memory models                                   | $50 \\ 51$      |

|   |            | $4.1.3 \\ 4.1.4$ | Histories                                       | $51 \\ 51$      |

|   |            | 4.1.4<br>4.1.5   |                                                 | $51 \\ 52$      |

|   | 4.9        |                  | Discussion on opacity                           | $\frac{52}{53}$ |

|   | 4.2        | 4.2.1            | pecifications for Opacity                       | $53 \\ 54$      |

|   |            | 4.2.1<br>4.2.2   | A nondeterministic TM specification             | $54 \\ 62$      |

|   | 4.3        |                  | A deterministic TM specification                | 02<br>65        |

|   | 4.3        |                  | ed Memory Language                              | 66<br>66        |

|   |            | 4.3.1            | Syntax                                          |                 |

|   |            | 4.3.2            | Semantics                                       | 66<br>71        |

|   |            | 4.3.3            | Example execution in RML                        | 71              |

|              | 4.4           | TM Algorithms in <b>RML</b>                  | 72       |

|--------------|---------------|----------------------------------------------|----------|

| <b>5</b>     | The           | Verification                                 | 77       |

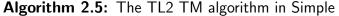

|              | 5.1           | The FOIL Tool                                | 77       |

|              | 5.2           | Results                                      | 78       |

|              |               | 5.2.1 Sequential consistency                 | 78       |

|              |               | 5.2.2 Relaxed memory models                  | 78       |

|              |               | 5.2.3 Analysis                               | 79       |

|              |               | 5.2.4 Model checking liveness                | 80       |

|              | 5.3           | Implementation Details                       | 80       |

|              |               | 5.3.1 Generating the state space             | 80       |

|              |               | 5.3.2 Finding a counterexample               | 82       |

|              |               | 5.3.3 Counterexample analysis                | 82       |

|              | 5.4           | Structural Properties                        | 83       |

| 6            | Para          | ametrized Opacity                            | 85       |

| U            | 6.1           | Preliminaries                                | 88       |

|              | 6.2           | Parametrized Opacity                         | 90       |

|              | 0.2           | 6.2.1 Memory models                          | 90       |

|              |               | 6.2.2   Examples of memory models            | 92       |

|              |               | 6.2.3 Parametrized opacity                   | 92<br>95 |

|              | 6.3           | TM Implementations                           | 95<br>96 |

|              | 6.4           |                                              | 90<br>99 |

|              | 0.4           | Achieving Parametrized Opacity               | 99<br>99 |

|              |               | r                                            |          |

|              | 0 5           | 6.4.2 Instrumented TM implementations        | 106      |

|              | 6.5           | Discussion                                   | 109      |

|              |               | 6.5.1 Impact on practical TM implementations | 109      |

|              |               | 6.5.2 Weaker notions of correctness          | 110      |

| 7            | Con           | clusion                                      | 113      |

|              | 7.1           | Summary                                      | 113      |

|              | 7.2           | In Retrospect: Lessons Learned               | 114      |

|              | 7.3           | Future Directions                            | 115      |

| $\mathbf{A}$ | $\mathbf{TM}$ | Specifications for Opacity Without Rollbacks | 117      |

|              | A.1           | A Nondeterministic TM Specification          | 117      |

|              | A.2           | A Deterministic TM specification             | 122      |

| Bi           | bliog         | raphy                                        | 127      |

# **List of Figures**

| 1.1<br>1.2<br>1.3<br>1.4 | Examples of programs with transactions                                                                                                                                           | $5 \\ 7 \\ 8 \\ 11$ |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 2.1<br>2.2<br>2.3        | Cases disallowed by the nondeterministic TM specification for opacity<br>Analysis for creating a deterministic TM specification for opacity<br>The syntax of the language Simple | 24<br>25<br>28      |

| 4.1                      | Cases disallowed by the nondeterministic TM specification for fine-                                                                                                              |                     |

|                          | grained opacity                                                                                                                                                                  | 59                  |

| 4.2                      | The syntax of the language $RML$                                                                                                                                                 | 66                  |

| 4.3                      | An example of an RML program                                                                                                                                                     | 71                  |

| 5.1                      | A schematic of FOIL                                                                                                                                                              | 77                  |

| 6.1                      | Motivating examples for the definition of parametrized opacity                                                                                                                   | 86                  |

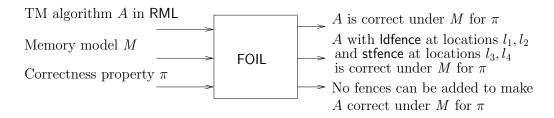

| 6.2                      | Examples of histories and sequential histories                                                                                                                                   | 90                  |

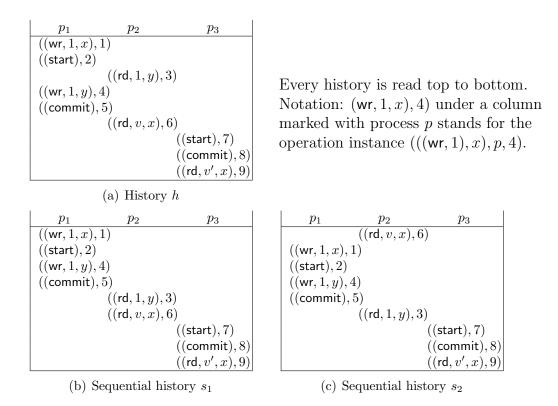

| 6.3                      | An example of a trace and corresponding histories                                                                                                                                | 96                  |

| 6.4                      | The trace $r$ constructed in Theorem 1, Case 1                                                                                                                                   | 100                 |

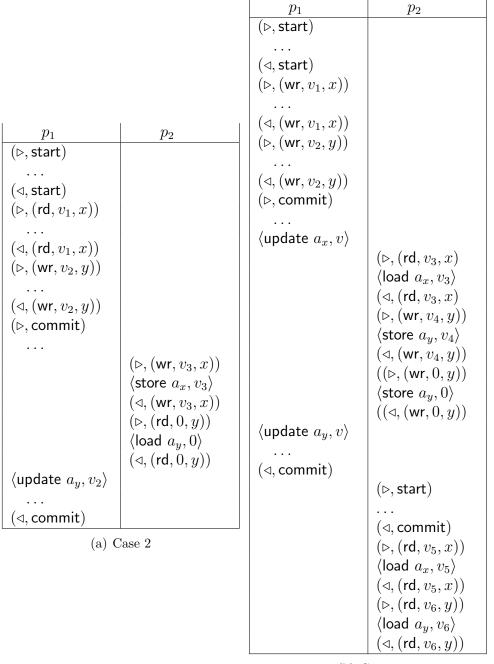

| 6.5                      | Traces $r$ constructed in Theorem 1, Case 2 and 3 $\ldots \ldots \ldots$                                                                                                         | 101                 |

| 6.6                      | The trace $r$ constructed in Theorem 2 $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                            | 104                 |

| 6.7                      | A global lock based TM implementation                                                                                                                                            | 105                 |

| 6.8                      | Optimizations allowed by relaxed memory models                                                                                                                                   | 109                 |

|                          |                                                                                                                                                                                  |                     |

# **List of Tables**

| 3.1 | The results of checking opacity of TM algorithms with a coarse abstraction            | 39 |

|-----|---------------------------------------------------------------------------------------|----|

| 3.2 | The results of verifying liveness properties in TM algorithms at a coarse abstraction | 41 |

| 4.1 | The definitions needed in the semantics of $RML$                                      | 67 |

| 5.1 | The results of checking opacity of TM algorithms under sequential consistency         | 78 |

| 5.2 | The results of checking opacity of TM algorithms under relaxed memory models          | 79 |

# List of Algorithms

| 2.1 | The nondeterministic TM specification for opacity                    | 21  |

|-----|----------------------------------------------------------------------|-----|

| 2.2 | The deterministic TM specification for opacity                       | 26  |

| 2.3 | The sequential TM algorithm in Simple                                | 32  |

| 2.4 | The two-phase locking TM algorithm in Simple                         | 33  |

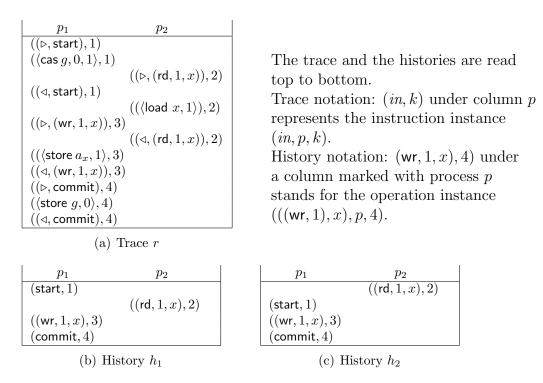

| 2.5 | The TL2 TM algorithm in Simple                                       | 34  |

| 2.6 | The DSTM algorithm in Simple                                         | 35  |

| 4.1 | The nondeterministic TM specification for fine grained opacity       | 55  |

| 4.2 | The deterministic TM specification for fine grained opacity          | 62  |

| 4.3 | The TL2 algorithm in $RML$                                           | 73  |

| 4.4 | The DSTM algorithm in RML                                            | 74  |

| 4.5 | The McRT-STM algorithm in RML                                        | 75  |

| 5.1 | Obtaining the transition system of a TM algorithm                    | 81  |

| 5.2 | Obtaining a counterexample to opacity on-the-fly                     | 81  |

| A.1 | The nondeterministic TM specification for fine grained opacity with- |     |

|     | out rollbacks                                                        | 118 |

| A.2 | The deterministic TM specification for fine grained opacity without  |     |

|     | rollbacks                                                            | 123 |

|     |                                                                      |     |

# Introduction

Over the last fifty years, the transistor density on a chip has doubled every two years. This phenomenon is widely known as the Moore's law [Moo65]. The exponential increase in transistor density has also resulted in an exponential increase in microprocessor clock rates, memory capacity, and similar capabilities of digital electronic devices. Moore's law is expected to continue to hold in the near future. However, higher clock rates have been accompanied by a much higher power consumption and heat dissipation, as these are cubic functions of the clock rate [FH05]. Around five years ago, the microprocessor clock rate hit the heat wall: the heat dissipation would damage the processor on increasing the clock rate further. Since then, the clock rates of a microprocessor have not scaled proportionately with the transistor density. This, in turn, led to the saturation of the performance of a uniprocessor. An alternative to increase the computation power proportionately with the transistor density is to build multiple processor cores in a single chip, where the cores run at lower clock rates. Lower clock rates result in lower power consumption and lower heat dissipation. Moreover, lower clock rates reduce the design complexity of a microprocessor.

However, to exponentially scale up the speed of a program using a multicore, it becomes crucial to exploit the computation power of all cores simultaneously. This requires the program to be *parallel*. A parallel program is one written to exploit the potential of a parallel computing resource like a multiprocessor or a cluster of processors. The research in parallel programs has been driven by high performance computing for the last few decades. However, the use of parallel programming has been limited to expert programmers. To achieve the full potential offered by multicore processors, we require suitable programming infrastructures and tools that make parallel programming accessible to mainstream programmers.

# 1.1 Parallel Programming

Parallel programming poses several challenges to the programmer. First of all, a programmer needs to identify computations that can be executed simultaneously. Secondly, a parallel program often requires concurrent access to underlying shared data. To prevent inconsistencies due to concurrent accesses, a parallel program requires precise synchronization. The performance of a parallel program depends on how the program handles concurrency. Concurrency makes parallel programs hard to write, and even harder to verify. Conventionally, concurrency relies on blocking synchronization primitives like locks and semaphores. These synchronization primitives often pose a trade-off between performance and programming effort. While coarse-grained locking is easy to reason about and prove correct, it does not often harness the computation power of a multicore efficiently. On the other hand, fine-grained locking yields an efficient program, but is a challenge to use correctly. Errors in using these synchronization techniques can result in unexpected data races, deadlocks, and livelocks. Moreover, concurrency leads to behaviors that are exponential in the number of threads, which makes errors hard to find or reproduce.

Other means of managing concurrency in parallel programs include nonblocking synchronization. Non-blocking algorithms use hardware provided atomic read-modify-write operations, and avoid the problems associated with locks or semaphores. However, non-blocking algorithms are extremely hard to design and to prove correct.

These problems with the current mechanisms to handle synchronization lead us to the question: can we provide a programming paradigm that ensures correctness of a parallel program, and at the same time, yields good performance. Transactional memory (TM) is one proposal that holds high potential to serve this requirement.

## 1.2 Transactional Memories

The idea of TM is inspired by the notion of database transactions. Transactional memory was first introduced by Herlihy and Moss [HM93] in multiprocessor design. Later Shavit and Touitou [ST95] introduced software transactional memory (STM), a software-based variant of the concept.

The basic notion of the execution of a TM is a transaction: a sequence of memory instructions that satisfies the following three properties: atomicity, isolation, and consistency. Atomicity ensures that either all or none of the effects of a transaction are visible. Isolation ensures that the intermediate state of a transaction is never visible to other transactions. Consistency ensures that the memory remains in a consistent state before a transaction starts, and after a transaction is over. TM are based on optimistic concurrency. That is, they allow speculative execution of transactions. If a transaction commits, all its effects are visible to other transactions. If a transaction aborts, none of the effects are visible, and the transaction may be retried. An extensive overview of TM can be found in Larus et al. [LR07].

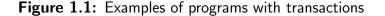

A decade after TM was invented, Harris and Fraser [HF03] proposed that the notion of a transaction can be used as a language level construct for synchronization in parallel programs. The runtime uses a TM implementation to execute a block of code, marked as atomic, as a transaction. This gave TM the potential to serve as an important paradigm to handle concurrency in parallel programs. Examples of programs with atomic blocks are shown in Figure 1.1. TM alleviates the difficulties of parallel programming. Although a programmer still needs to identify the parallelizable components in a program, a TM guarantees that these components are executed in parallel correctly, and with good performance.

## **1.3 TM Implementations**

The success of transactional memories as a programming paradigm is evident from the plethora of TM implementations available today. TM have been implemented in hardware, software, and as a hybrid of hardware and software.

#### Hardware TM

TM was initially proposed by Herlihy and Moss [HM93] as a hardware mechanism. Most hardware TM (HTM) [MBM<sup>+</sup>06, HWC<sup>+</sup>04] rely on a modification to the cache coherence protocol to achieve atomicity of transactions. Proposals to exploit HTM [RG02] to implement conventional lock based critical sections also exist. HTM offer good performance, but suffer from the following drawbacks. Firstly, HTM require architectural changes to hardware and require the TM algorithm to be embedded in hardware. This makes HTM an expensive and inflexible option. Secondly, most HTM only support bounded transactions that can fit the on-chip resources. Although proposals [AAK<sup>+</sup>05, RHL05] exist in the literature to avoid this limitation, the design complexity of these proposals is significant.

#### Software TM

The limitations of HTM make STM a compelling choice to implement TM. Although the first STM was proposed by Shavit et al. [ST95] in 1995, STM gained popularity in 2003, when Herlihy et al. [HLMS03] proposed DSTM, and Harris et al. [HF03] proposed to use TM to provide transactions as a language level construct for synchronization in parallel programs. Since then, many STM [HLMS03, DSS06, SATH<sup>+</sup>06, FH07, MM07, RFF06] have been proposed. Software provides the flexibility to design and test new sophisticated TM algorithms. So, unlike HTM, STM widely differ in their protocols, and make an interesting verification problem. However, STM do not perform as well as HTM due to runtime overhead and bookkeeping in software.

#### Hybrid TM

Research has also focused on hybrid approaches [DFL<sup>+</sup>06, KCH<sup>+</sup>06], where transactions are first tried in the hardware component. If the transaction exhausts the resources available, it is retried in software. Thus, hybrid TM aims to provide the benefits of both HTM and STM. Sun's Rock processor [DLMN09], the first commercial processor with hardware support for transactions, is designed to be a hybrid TM.

Apart from the infrastructure of implementation, TM can also be classified on the basis of conflict detection and version management in their algorithms. Two transactions are in conflict if they access the same data, and at least one of the transactions writes. As TM rely on speculative execution, transactions are prone to conflict with each other. The conflict detection protocol varies in different TM algorithms. While some TM algorithms detect conflicts as soon as they happen, other TM algorithms detect conflicts when transactions commit.

As a running transaction has a possibility to abort, different versions of the data have to be managed at the same time: one version for recording the changes made to the data by the transaction, another to hold the original value of the data. Different TM algorithms differ in the way they manage the versions. A *deferred update* TM algorithm creates a local copy of all data written in a transaction, and uses this local copy to update the global data at the time of commit. On the other hand, a *direct update* TM algorithm updates the global data during the execution of a transaction and maintains a local copy of the original data to restore the global data upon an abort. A deferred update TM algorithm is also known as lazy update or redo log TM algorithm. A direct update TM algorithm is also known as eager update or undo log TM algorithm.

## 1.4 Correctness in TM

As a TM algorithm promises proper synchronization in a parallel program to the programmer, correctness is an important issue in TM algorithms. A TM algorithm is correct if it ensures correctness for all programs. Precisely because a TM algorithm encapsulates the difficulty of handling concurrency, the potential of subtle errors is enormous. This makes verification of TM algorithms an important candidate for formal methods. We now look at the safety and liveness properties expected in TM algorithms.

#### 1.4.1 Safety

The correctness properties in TM build upon the correctness notions of database transactions. The most common correctness requirement in databases is serializability [Pap79] which requires that committed transactions appear to

| $\begin{array}{c} \text{Thread 1} \\ \hline atomic \{ \\ x := 1 \\ x := 2 \\ \} \end{array}$ | Thread 2<br>$atomic \{$<br>r := x<br>$\}$ | $\begin{array}{c} \mbox{Thread 1} \\ \hline atomic \{ \\ x := 1 \\ x := 2 \\ \} \\ atomic \{ \\ y := 2 \\ \} \\ \end{array}$ | Thread 2<br>$atomic \{$<br>z := x - y<br>$\}$ | Thread 1<br>atomic {<br>x := 1<br>y := 1<br>} | Thread 2<br>atomic {<br>$r_1 := x$<br>$r_2 := y$<br>$r_3 := 1/(r_1 - r_2 - 1)$<br>} |

|----------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------|

| (a) Can                                                                                      | r = 1?                                    | (b) Ca                                                                                                                       | an $z < 0$ ?                                  | (c) Can threa                                 | d 2 perform a division by 0?                                                        |

initially x = y = z = 0 in every case

be sequential. Strict serializability further requires that the order of nonoverlapping transactions is preserved. However, it was observed [DSS06, HLMS03] that strict serializability is not sufficient for memory transactions. It is important that even aborted transactions do not observe an inconsistent state of the memory, as this could lead to unexpected side effects like infinite loops or array bound violations. This has led a strong notion of correctness in TM, referred to as *opacity* [GK08]. Opacity requires that all transactions appear to execute sequentially. This prevents aborting transactions from reading inconsistent values. Most of the TM implementations [HLMS03, DSS06, SATH<sup>+</sup>06, FH07, MM07] indeed claim to satisfy opacity.

Figure 1.1 illustrates the three safety properties: serializability, strict serializability, and opacity. In Figure 1.1(a), thread 2 cannot observe the value of x as 1 under the correctness properties of serializability, strict serializability, and opacity. This is because all three correctness properties require the basic principle of isolation and atomicity of transactions. Consider Figure 1.1(b). Strict serializability and opacity require that if thread 2 observes the value of y as 2, then thread 2 observes the value of x as 2. That is, strict serializability and opacity require that the effect of transactions is visible in the order the transactions appear. Consider Figure 1.1(c). As serializability and strict serializability do not pose any restrictions on aborted transactions, it is possible that an aborted transaction views an inconsistent state by reading x as 1 and y as 0. Note that this might result in a division by zero by an aborting transaction which might crash the whole program. Opacity requires that even aborting transactions view consistent state. Thus, a division by zero error is not possible if the TM satisfies opacity.

#### 1.4.2 Liveness

Early TM algorithms provided nonblocking progress guarantees. Below, we discuss liveness properties that provide nonblocking progress guarantees:

- The weakest nonblocking progress guarantee is known as obstruction freedom. A TM implementation is *obstruction free* if every transaction is guaranteed to commit as long as no other transaction makes a step. Note that obstruction freedom does not guarantee whether any transaction will commit if more than one transaction take steps. In other words, a TM implementation may livelock even if it is obstruction free.

- A TM implementation is *livelock free* if some transaction is guaranteed to commit in a finite number of steps. Livelock freedom implies obstruction freedom. But, a TM implementation that is livelock free does not guarantee that every transaction will commit.

- A TM implementation is *wait free* if every transaction is guaranteed to commit in a finite number of steps. Wait freedom implies livelock freedom.

The most efficient TM implementations today rely on locks. Thus, they fail to guarantee even obstruction freedom, the weakest non-blocking progress guarantee. Weaker progress guarantees [GK09] have also been defined in the framework of TM implementations.

# 1.5 Relaxed Memory Models

The correctness of a program depends on the infrastructure on which it runs. The same holds for TM algorithms. To ensure correctness, it is important to understand the behavior of TM algorithms on commercial processors. Processors, for reasons of performance, do not guarantee that the instructions in a program are executed in program order. Rather, processors specify a memory model [AG96] that specifies the set of allowed behaviors of memory accesses.

For example, the memory model *sequential consistency* specifies that a multiprocessor executes the instructions of a thread in program order. On the other hand, the memory model *total store order* specifies that a multiprocessor may relax the order of a store followed by a load to a different address, by delaying stores using a store buffer. In principle, a memory model offers a tradeoff between transparency to the programmer and flexibility to the hardware to optimize performance. Sequential consistency is the most stringent memory model, and thus the most intuitive to the programmer. But, most of the available multiprocessors do not support sequential consistency for reasons of performance.

The problem of synchronization in parallel programs becomes harder under relaxed memory models: apart from the interleavings of different threads, one needs to consider the possible reorderings of instructions within each thread. To illustrate the point, we give some examples of memory models. We give a parallel program and describe the outcomes under different relaxed memory models.

| Exampl | es of | memory | models |

|--------|-------|--------|--------|

|--------|-------|--------|--------|

| Initially : $x_1 =$                                                                         | $y_1 = x_2 = y_2 = 0$                                                                       |                                                                                                                                        |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Thread 1                                                                                    | Thread 2                                                                                    | $O_1: r_1 = 1, r_2 = 1, r_3 = 1, r_4 = 1$                                                                                              |

| $\begin{array}{l} x_1 := 1 \\ y_1 := 1 \\ r_1 := y_2 \\ r_3 := x_2 \\ x_1 := 2 \end{array}$ | $\begin{array}{l} x_2 := 1 \\ y_2 := 1 \\ r_2 := y_1 \\ r_4 := x_1 \\ x_2 := 2 \end{array}$ | $O_2 : r_1 = 0, r_2 = 0, r_3 = 0, r_4 = 0$<br>$O_3 : r_1 = 1, r_2 = 1, r_3 = 0, r_4 = 0$<br>$O_4 : r_1 = 1, r_2 = 1, r_3 = 2, r_4 = 2$ |

Figure 1.2: The outcomes of a parallel program under different memory models

- Sequential consistency (SC) does not allow any pair of instructions to be reordered.

- Total store order (TSO) relaxes the order of a store followed by a load to a different address. But, the order of stores cannot be changed. TSO allows a load that follows a store to the same address to be eliminated.

- *Partial store order (PSO)* is similar to TSO, but further relaxes the order of stores.

- *Relaxed memory order (RMO)* relaxes the order of instructions even more than PSO, by allowing to reorder all memory instructions to different addresses.

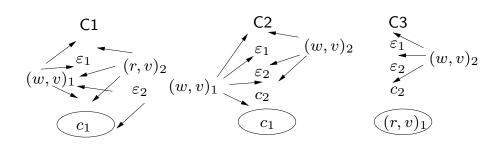

Figure 1.2 illustrates a parallel program with two threads that distinguishes between the different memory models in terms of the possible outcomes. Outcome  $O_1$  is allowed by SC, while other outcomes are not. Outcomes  $O_1$  and  $O_2$  are allowed by TSO. Outcomes  $O_1, O_2$ , and  $O_3$  are allowed by PSO. All outcomes  $O_1, O_2, O_3$ , and  $O_4$  are allowed by RMO.

Although most commercial multiprocessors use a relaxed memory model, TM algorithms published in the literature assume sequentially consistent behavior. The relaxations introduce a scope of errors when TM algorithms are executed on relaxed memory models. Typically, TM designers use *fences* to ensure a strict ordering of memory operations. As fences hurt performance, TM designers want to use fences only when necessary for correctness.

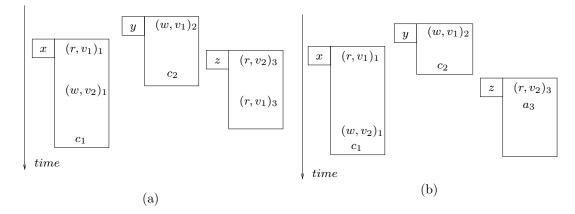

To illustrate the point, we consider the code fragments of the commit and the read procedures of a typical timestamp-based TM like TL2 [DSS06] in Figure 1.3. Assume that at the start of a transaction,  $t_1$  and  $t_2$  are set to the global timestamp *ts*. The commit procedure updates the timestamp *ts* before it updates the variables to be written. The read procedure first reads the timestamp, followed by the read of the variable, followed by a second read of the timestamp. The read is successful only if the two timestamps are equal. A

| txCommit : | update global timestamp $ts$<br>for each variable $v$ in write set<br>update value of $v$ | txRead: | $\begin{array}{l} \dots \\ t_1 := ts \\ \textbf{if}  (t_1 \neq t_2) \textbf{ then} \\ \text{read value of } v \\ t_2 := ts \end{array}$ | abort |

|------------|-------------------------------------------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------|-------|

|            |                                                                                           |         | if $(t_1 \neq t_2)$ then                                                                                                                | abort |

Figure 1.3: Sample code fragments of commit and read procedures of a TM

crucial question is, given the memory model, which fences are required to keep the STM correct. On a memory model like sequential consistency [Lam79] or total store order [WG94], the code fragment in Figure 1.3 is correct without fences. On the other hand, on memory models that relax store order, like partial store order [WG94], we need to add a *store fence* after the timestamp update in the commit procedure. For even more relaxed memory models that may swap independent loads, like relaxed memory order [WG94], as well as the Java memory model [MPA05], we need more fences, namely, *load fences* in the read procedure. But the question is how many? Do we need to ensure that the read of v is between the two reads of ts, and thus put two fences? The answer is no. To ensure correctness, we just need one fence and guarantee that the second read of ts comes after the read of v.

# 1.6 Problem Statement

This thesis develops a formalism and a verification tool to answer the question: does a TM algorithm ensure a given safety or liveness property on a given memory model? If not, can the TM algorithm use fences to ensure the property under the memory model?

## 1.6.1 Challenges

This problem translates into three main challenges as described below.

#### Formalization

Although TM have been built and implemented since almost two decades, there is little work in the direction of formalizing the properties of TM. The challenge lies in mapping a given transactional program, as written by a programmer, to the set of instruction sequences (called histories) as issued by a TM on the processors with a given relaxed memory model. This requires to take into account, the state of each transaction in the TM, the interaction between different transactions, and the behavior of the scheduler. Intuitively, a TM algorithm is correct if for all transactional programs, all histories produced by the TM are correct.

#### **Correctness specification**

We consider opacity as our safety correctness criterion. While opacity has been formally defined, verification requires to check whether a history satisfies opacity or not. Thus, we need to build a specification that captures the set of all histories that satisfy opacity. We find it non-trivial to build a specification that can be used to efficiently verify TM algorithms.

#### Verification

The formal framework and the correctness specification lay the groundwork for verification. However, there remain two challenges in verification. First of all, with an unbounded number of threads and variables, the state space of a TM algorithm is unbounded. So, we need to either reduce the problem to a finite number of threads and variables, or use infinite state verification. Secondly, even with a small number of threads and variables, there is a high level of non-determinism due to multiple threads and the relaxed memory model. Building an automated tool to capture state spaces of such magnitude is challenging.

#### 1.6.2 Our approach

We tackle the above challenges in two steps. In the first step, we ignore the challenges posed by hardware level atomicity and relaxed memory models. We assume atomicity of a coarse grained alphabet of instructions. This step aims to provide an intuition of the verification technique without delving into the complications introduced by real hardware. We develop a formalism for TM algorithms and correctness properties of TM. We obtain a transition system corresponding to a TM algorithm. The set of histories produced by the TM algorithm corresponds to the language of the transition system. At first, we restrict ourselves to checking the correctness of a TM algorithm with a finite number of threads and variables. To do this, we first describe the correctness property as a finite state specification, and then check that the language of the TM algorithm is included in the specification. We build nondeterministic and deterministic transition systems (specifications) corresponding to the safety property of opacity. It is easy to show that the nondeterministic specification is indeed the set of all correct histories. But, to check that the language of the TM algorithm is included in the nondeterministic specification, we would need to determinize the specification. The large size of the nondeterministic specification makes determinization infeasible. Instead, we manually create a deterministic specification for the correctness property and use automated tools to establish the equivalence of nondeterministic and deterministic specifications. The deterministic specification allows us to easily check the correctness of a TM algorithm. We reduce the problem of verification of TM algorithms with an unbounded number of threads and variables, to verifying TM algorithms with two threads and two variables. This reduction relies on structural properties of TM algorithms. We express two phase locking, TL2, and DSTM in our framework, and show that these TM algorithms indeed satisfy the structural properties. Then, we prove opacity of the TM algorithms by checking that the language of the TM algorithms is contained in that of the deterministic TM specification. We also verify the liveness properties of TM algorithms. The first step indeed solves the verification problem at an abstraction.

In the second step, we address the complications in verification introduced by modeling TM algorithms at the level of atomicity provided by hardware, under relaxed memory models. We build a formalism for relaxed memory models. We express memory models as a function of hardware memory instructions, that is, loads and stores to 32 bit words. We describe various relaxed memory models, such as total store order (TSO), partial store order (PSO), and relaxed memory order (RMO) in our formalism. The reason for choosing these memory models is to capture different levels of relaxations allowed by different multiprocessors. Then, we build a new language, Relaxed Memory Language (RML), with a hardware-level of atomicity, whose semantics is parametrized by a relaxed memory model. We describe different TM algorithms in RML. We develop a new tool FOIL<sup>1</sup> to verify the safety and liveness of three different TM algorithms under different memory models. While we choose opacity as the safety criterion, using FOIL we can also verify other safety properties such as strict serializability that can be specified in our formalism. FOIL proves the opacity of the considered TM algorithms under sequential consistency and TSO. As the original TM algorithms have no fences, FOIL generates counterexamples to opacity for the TM algorithms under further relaxed memory models (PSO and RMO), and automatically inserts fences within the RML description of the TM algorithms that are required (depending upon the memory model) to ensure opacity. We observe that FOIL inserts fences in a pragmatic manner, as all fences it inserts match those in the manually optimized official implementations of the considered TM algorithms. Our verification leads to an interesting observation that many TM algorithms are sensitive to the order of loads and stores, but neither to the order of a store followed by a load, nor to store buffering. In other words, all TM algorithms we consider are opaque under TSO without any fences.

# **1.7** Generalizing the Notion of Opacity

The verification technique built in this thesis checks correctness of pure transactional programs. This technique would suffice if a program could execute all operations on shared data within transactions, and apply non-transactional operations only to thread-local data. In practice, however, not all operations on shared data can be wrapped in transactions. For example, a programmer may wish to make shared data local to a thread, operate non-transactionally

<sup>&</sup>lt;sup>1</sup>Foil is a fencing weapon. Our tool inserts fences in the TM algorithm to make the TM algorithm correct.

| Thread 1                           | Thread 2              |

|------------------------------------|-----------------------|

| $atomic \{ x := 1 \\ y := 1 \\ \}$ | $r_1 := x$ $r_2 := y$ |

**Figure 1.4:** Can  $r_1 = 1$  and  $r_2 = 0$ ? It depends on the memory model (initially x = y = 0).

upon it for a while, and make it shared again [MBS<sup>+</sup>08, SMDS07]. It is thus not surprising to see a large body of research dedicated to exploring the various models of interaction between transactions and non-transactional code [ABHI08, DS09, GMP06, SMDS07, MBL06, MG08], and building TM implementations based on those models [SMAT<sup>+</sup>07, MBS<sup>+</sup>08].

The interaction between transactions and non-transactional operations has been defined using a notion of strong atomicity [MBL06, LR07] in the literature. The intuition behind strong atomicity is that transactions execute atomically with respect to other transactions and non-transactional operations. Unfortunately, strong atomicity has not been formally defined. This has led to multiple interpretations [SDMS08]. Consider, for example, the execution depicted in Figure 1.4 (adapted from Grossman et al. [GMP06]). The transaction executed by thread 1 updates variables x and y. Thread 2 reads the variables x and y non-transactionally. Is it possible that thread 2 reads x as 0 and y as 1? According to the definition by Martin et al. [MBL06], strong atomicity allows this result. But, according to the definition of strong atomicity by Larus et al. [LR07], this result is not allowed. The ambiguity in this definition can be attributed to an implicit assumption on the interaction between non-transactional operations, which in turn, depends upon the underlying memory model [AG96]. While Martin et al. [MBL06] assume a relaxed memory model that allows to reorder independent reads (for example, RMO [WG94]), Larus et al. [LR07] assume a sequentially consistent memory model.

We claim that while a TM can be implemented in a way to ensure opacity for transactions, there is little one can do (on a given platform or run-time environment) to change the underlying memory model. Hence, it is desirable to define opacity *parametrized* by a memory model. This thesis provides a general formal framework for describing the interactions between transactions and nontransactional operations. We consider opacity as a correctness condition for transactions, and parametrize it by a memory model.

### **1.8 Related Work**

This thesis builds upon and improves the existing formalisms for TM and relaxed memory models. Moreover, this thesis presents a new verification tool for TM algorithms. We describe some existing related work in these directions.

#### **1.8.1** Formalisms for transactional memories

While a lot of work has been carried out in the direction of developing fast and efficient transactional memories, there is limited research in the direction of formalizing correctness properties of TM. Scott [Sco06] was the first to provide a formal semantics for STM. However, his correctness criterion requires the order of commits to be preserved. Most of the popular STM algorithms, for example TL2 [DSS06], do not preserve the order of conflicts. Guerraoui and Kapalka [GK08] define opacity to precisely capture the safety aspect of STM and highlighted the subtle differences with database transactions.

The interaction of transactions with non-transactional operations has been widely studied. The study was pioneered by Grossman et al. [GMP06], where the authors raised several issues that need to be tackled in order to create TM implementations that handle non-transactional operations properly. The authors express the correctness property using sample executions, and thus the property lacks a formal specification. Work by Scott et al. [SDMS08] focuses on providing a set of rules that should hold irrespective of the memory model. This work is restricted to memory models that do not allow out-of-thin-air values. Menon et al. [MBS<sup>+</sup>08] define correctness by mapping transactions to critical sections, thus providing an intuitive definition of single global lock atomicity. Type systems and operational semantics for transactional programs with non-transactional accesses have been proposed by Abadi et al. [ABHI08] and Grossman et al. [MG08]. We provide a formal specification of the correctness property in the presence of relaxed memory models.

#### 1.8.2 Formalisms for relaxed memory models

Adve et al. [AG96] provide a detailed description of hardware relaxed memory models. Language level memory models have been developed for Java [MPA05] and C++ [BA08]. Various formalisms for memory models have been proposed in the literature [BP09, BMS08, GHS09, SJMvP07, SSN<sup>+</sup>09]. Most of these formalisms provide an axiomatic definition of memory models. Architectural manuals [WG94, Sit02] also describe memory models in an axiomatic style. Operational semantics of relaxed memory models were developed by Petri et al. [BP09]. Their formalism captures write-to-read/write reordering used in memory models like TSO and PSO. Moreover, the formalism allows thread creation. However, it cannot express read-to-read/write relaxations found in memory models like RMO. Verification based on axiomatic memory model specifications relies on constraint solving (like SAT solvers) to validate execution traces. As our tool is based on explicit state model checking, we find it more intuitive to define an operational semantics of relaxed memory models. Our operational semantics handles write-to-read/write and read-to-read/write relaxations, but cannot handle thread creation.

For the definition of parametrized opacity, we use an axiomatic definition of memory models. Most of the existing formalisms for memory models are tailored to capture the intricacies of specific memory models. We build a general formalism, with the focus on classification of memory models on the basis of reordering of instructions they allow.

#### **1.8.3** Verification tools

Many tools for verification have been built in the last several years. Model checkers like BLAST [BHJM07] and SLAM [BR02] verify properties of sequential programs. Model checkers like Zing [AQR<sup>+</sup>04], SPIN [Hol97], KISS [QW04], and CHESS [QR05, MQB<sup>+</sup>08] are developed for verification of concurrent programs. These tools are built to detect races in concurrent programs. However, TM algorithms, by design, often consist of benign races. Moreover, these tools assume a sequentially consistent memory model, and miss out a whole range of interleavings that arise due to the reorderings of the instructions of a thread allowed by a relaxed memory model. Verification of concurrent data types has been attempted with theorem proving [CGLM06, VHHS06]. These methods require a manual tedious proof construction, and assume sequential consistency.

Dynamic tools [FF09, EQT07, FFY08, FF04] for verifying atomicity and race freedom in concurrent programs have also been built. Manovit et al. [MHC<sup>+</sup>06] used testing to find errors in TM implementations. Elmas et al. [ETQ05] have built tools for runtime verification of concurrent data types. The motivation for dynamic tools is to check the correctness of a computation at runtime, and throw an exception in case of error. Dynamic tools can find errors in a TM algorithm only when the TM algorithm is used to execute a transactional program. Dynamic tools cannot be used to establish the correctness of a TM algorithm, that is, to check whether the TM algorithm is correct for all programs. However, as static analysis is tricky for real TM implementations, we believe that dynamic tools can be useful to check correctness properties of TM implementations at runtime. Instead of the data race specification, the specification of opacity constructed in this thesis could be used.

Burckhardt et al. [BAM06, BAM07] developed CheckFence, a static verification tool for concurrent C programs under relaxed memory models. The tool requires as input a bounded test program (a finite sequence of operations) for a concurrent data type and uses a SAT solver to check the consistency and report if any fences are required. However, CheckFence cannot automatically introduce fences. We use the structural properties of TM, which allow us to consider a maximal program on two threads and two variables in order to generalize the result to all programs with any number of threads and variables. We model the correctness problem as a relation between transition systems. Moreover, our tool, FOIL, automatically inserts fences. Padua et al. [LP01, FLM03] developed mechanisms to ensure sequential consistency under relaxed memory models. However, conservatively putting fences into TM implementations to guarantee sequential consistency would badly hurt TM performance. TM programmers put fences only where necessary. Gopalakrishnan et al. [GYS04] developed a verification tool for checking memory orderings for small programs.

Recent work has addressed verification in the context of transactional memories. Tasiran [Tas08] verified the correctness of the Bartok STM. The author manually proves the correctness of the Bartok STM algorithm, and uses assertions in the Bartok STM implementation to ensure that the implementation refines the algorithm. This work is orthogonal to ours, as we focus on automated techniques to prove the correctness of TM algorithms. Cohen et al. [CPZ08] model checked STM applied to programs with a small number of threads and variables, against the strong correctness property of Scott [Sco06]. Further, they studied safety properties in situations where transactional code has to interact with non-transactional accesses.

## 1.9 Organization of the Thesis

Chapter 2 presents a preliminary formalism of TM algorithms, and specifications for opacity. The chapter presents a language Simple, followed by examples of TM algorithms in the language. Chapter 3 presents results of model checking safety and liveness of TM algorithms for a finite number of threads and variables. Then, the chapter presents structural properties of TM algorithms that extend the verification results to an arbitrary number of threads and variables. These two chapters simplify and extend the formalism and the verification technique we presented at PLDI 2008 [GHJS08] and CONCUR 2008 [GHS08].

Chapter 4 builds upon the preliminary formalism. It presents a formalism and examples of memory models. The chapter presents the syntax and operational semantics of our language RML, followed by examples of different TM algorithms expressed in RML. Chapter 5 presents our tool FOIL to verify opacity of different TM algorithms under different relaxed memory models. Then, we show that the structural properties of TM algorithms hold at this low level of atomicity. These two chapters are based on our work presented at CAV 2009 [GHS09]. Chapter 6 extends the notion of opacity to mixed transactional code by introducing parametrized opacity. Chapter 7 concludes the thesis and discusses directions for future work.

# 2

# **A** Preliminary Formalism

The motivation of the preliminary formalism is to explain our verification technique for TM algorithms without the complications introduced by hardware level atomicity and relaxed memory models. Our preliminary approach tackles the problem of verifying TM algorithms at a level of abstraction by making certain assumptions. We assume a level of atomicity higher than that provided by the hardware. We assume that the instructions of a thread execute in program order. We restrict our verification to deferred update TM algorithms, that is, to TM algorithms which update global memory on a commit. Moreover, we assume that all writes are committed atomically.

## 2.1 Transactional Programs

Let  $V = \{1, ..., k\}$  be a set of transactional variables. Let  $T = \{1, ..., n\}$  be a set of threads. Let the set C of transactional commands be  $(\{txrd, txwr\} \times V) \cup \{txend\}$ . These commands correspond to a read or write of a transactional variable, and to the end of a transaction.

Depending upon the underlying TM, the execution of these commands may correspond to a sequence of instructions in our abstraction. For example, a read of a transactional variable may require to check the consistency of the variable by first reading a version number. Similarly, a transaction end may require to validate the variables read, followed by copying many variables from a thread-local buffer to global memory. Moreover, the semantics of the txwr and the txend commands depend on the underlying TM. For example, a (txwr, v) command does not alter the value of v in a deferred update TM, whereas it does in a direct update TM. On the other hand, an txend command may alter transactional variables in a deferred update TM, and not in a direct update TM. In this chapter, we assume that a (txwr, v) command does not alter the value of v globally, which restricts the verification technique to deferred update TM algorithms.

We consider transactional programs as our basic sequential unit of computation. We express transactional programs as infinite binary trees on transactional commands, which makes the representation independent of specific control flow statements, such as exceptions for handling aborts of transactions. Our definition restricts us to purely transactional code, as every command is part of some transaction. For every command of a thread, we define two successor commands, one if the command is successfully executed, and another if the command fails due to an abort of the transaction. Note that this definition allows us to capture different retry mechanisms of TM, e.g., retry the same transaction until it succeeds, or try another transaction after an abort. We use a set of transactional programs to define a multithreaded transactional program. A transactional program  $\theta$  is an infinite binary tree  $\theta : \mathbb{B}^* \to C$ . Let  $\Theta$  be the set of all transactional programs. A *(multithreaded)* transactional program  $prog: T \to \Theta$  is a function from the set of threads to the set of transactional programs. Let *Progs* be the set of all multithreaded transactional programs.

# 2.2 Transactional Memories

We characterize a TM by the sequences of memory instructions the TM can produce. We call a sequence of instructions a *history*.

#### 2.2.1 Histories

In order to reason about the correctness of TM, the history must contain, apart from the sequence of memory instructions that capture the reads and writes of transactional variables in the program, the information of when transactions finish. This is because the correctness of a TM depends on the sequence of reads and writes issued to transactional variables and the boundaries where the transactions finish. Let the set In of instructions be ({read, write}  $\times V$ ). Let  $\hat{In}$  be  $In \cup {\text{commit, abort}}$ .

Let  $\hat{Op} = \hat{In} \times T$  be the set of *operations*. A history  $h \in \hat{Op}^*$  is a finite sequence of operations. We characterize a TM by the set of finite and infinite histories it produces. Formally, a transactional memory (TM)  $\Gamma$  is a prefix-closed subset of  $\hat{Op}^* \cup \hat{Op}^{\omega}$ .

#### 2.2.2 Transactions

Given a history  $h \in \hat{Op}^*$ , we define the *thread projection*  $h|_t$  of h on thread  $t \in T$  as the subsequence of h consisting of all operations op in h such that  $op \in \hat{In} \times \{t\}$ . Given a thread projection  $h|_t = op_0 \dots op_m$  of a history h on thread t, an operation  $op_i$  is finishing in  $h|_t$  if  $op_i$  is a commit or an abort.

An operation  $op_i$  is *initiating in*  $h|_t$  if  $op_i$  is the first operation in  $h|_t$ , or the previous operation  $op_{i-1}$  is a finishing operation.

Given a thread projection  $h|_t$  of a history h on thread t, a consecutive subsequence  $x = op_0 \dots op_m$  of  $h|_t$  is a transaction of thread t in h if (i)  $op_0$ is initiating in  $h|_t$ , and (ii)  $op_m$  is either finishing in  $h|_t$ , or  $op_m$  is the last operation in  $h|_t$ , and (iii) no other operation in x is finishing in  $h|_t$ . The transaction x is committing in h if  $op_m$  is a commit. The transaction x is *aborting* in h if  $op_m$  is an abort. Otherwise, the transaction x is *unfinished* in h. We say that a transaction x is finished in h if x is committing or aborting in h. Given a history h and two transactions x and y in h (possibly of different threads), we say that x precedes y in h, written as  $x <_h y$ , if the last operation of x occurs before the first operation of y in h. A history h is sequential if for every pair x, y of transactions in h, either  $x <_h y$  or  $y <_h x$ .

#### 2.2.3 Safety in TM

We consider the safety property, opacity, for transactional memories. Opacity builds upon the safety property of strict serializability. Strict serializability [Pap79] requires that the order of conflicting statements from committing transactions is preserved, and the order of non-overlapping transactions is preserved. Opacity [GK08], in addition to strict serializability, requires that even aborting transactions do not read inconsistent values. The motivation behind the stricter requirement for aborting transactions in opacity is that in TM, inconsistent reads may have unexpected side effects, like infinite loops, or array bound violations. Although we restrict our attention to read and write operations, the notion of opacity has been extended to arbitrary operations.

An operation  $op_1$  of transaction x and an operation  $op_2$  of transaction y(where x is different from y) conflict in a history h if (i)  $op_1$  is a read of some variable v, and  $op_2$  is a commit of a transaction that writes to v, or (ii)  $op_1$  and  $op_2$  are both commits of transactions that write to some variable v. Note that this notion of conflict corresponds to the deferred update semantics [LR07] in transactional memories, where the writes of a transaction are made global upon the commit. A history  $h = op_0 \dots op_m$  is strictly equivalent to a history h' if (i) for every thread  $t \in T$ , we have  $h|_t = h'|_t$ , and (ii) for every pair  $op_i, op_j$  of operations in h, if  $op_i$  and  $op_j$  conflict and i < j, then  $op_i$  occurs before  $op_j$  in h', and (iii) for every pair x, y of transactions in h, where x is a committing or an aborting transaction, if  $x <_h y$ , then it is not the case that  $y <_{h'} x$ .

We define the safety property opacity  $\pi \subseteq \hat{Op}^*$  as the set of histories hsuch that there exists a sequential history h', where h' is strictly equivalent to h. Although we do not use the property of strict serializability, we define it to illustrate the formalism. We define a function  $com : \hat{Op}^* \to \hat{Op}^*$  such that for all histories  $h \in \hat{Op}^*$ , the history com(h) is the subsequence of h which consists of every operation in h that is a part of a committing transaction. We define the safety property strict serializability  $\pi_{ss} \subseteq \hat{Op}^*$  as the set of histories h such that there exists a sequential history h', where h' is strictly equivalent to com(h). We note that  $\pi \subseteq \pi_{ss}$ , that is, if a history is opaque, then it is strictly serializable.

#### 2.2.4 Liveness in TM

We formalize two different notions of liveness, obstruction freedom and livelock freedom, as discussed in the TM literature. A third notion, wait freedom [Her91], implies livelock freedom. Since we will show that none of our TM examples satisfy livelock freedom, they do not satisfy wait freedom either.

We consider infinite histories in  $\hat{Op}^{\omega}$ . An infinite history  $\bar{h} \in \hat{Op}^{\omega}$  is obstruction free [HLM03] if for all threads t, if the history  $\bar{h}$  has an infinite number of aborts of t, then either  $\bar{h}$  has an infinite number of commits of t, or there are infinitely many operations of some thread  $u \neq t$ . Formally,  $\hat{h}$  is obstruction free if  $\bigwedge_{t \in T} (\Box \Diamond (abort, t) \to \Box \Diamond ((commit, t) \lor \bigvee_{in \in \hat{In}, u \in T \setminus \{t\}} (in, u)))$ , where the temporal operation  $\Box$  denotes 'always' and the temporal operation  $\Diamond$  denotes 'eventually'. Obstruction freedom is a Streett condition [Str82].

An infinite history  $\bar{h} \in \hat{Op}^{\omega}$  is *livelock free* (often referred to as lock-free [HLM03, FH07]) if the history has an infinite number of commits, or there is a thread t such that t has infinitely many operations and finitely many aborts in  $\hat{h}$ . Formally,  $\hat{h}$  is *livelock free* if  $\Box \Diamond (\bigvee_{t \in T} (\mathsf{commit}, t)) \lor \bigvee_{t \in T} (\Box \Diamond (\bigvee_{in \in In} (c, t)) \land \Diamond \Box \neg (\mathsf{abort}, t))$ . Note that livelock freedom implies obstruction freedom.

We say that  $\Gamma$  ensures (n, k) opacity if for every finite history h in  $\Gamma$  such that h has at most n threads and at most k variables, we have  $h \in \pi$ . Moreover,  $\Gamma$  ensures opacity if  $\Gamma$  ensures (n, k) opacity for all n and k. A TM  $\Gamma$ ensures (n, k) obstruction freedom (resp. (n, k) livelock freedom) if every infinite history  $\bar{h} \in \Gamma$  such that  $\bar{h}$  has at most n threads and at most k variables is obstruction free (resp. livelock free). Moreover,  $\Gamma$  ensures obstruction freedom (resp. livelock freedom) if  $\Gamma$  ensures (n, k) obstruction freedom (resp. (n, k)livelock freedom) for all n and k.

## 2.3 TM Specifications

We capture safety properties of TM using TM specifications. We use the set of instructions as the alphabet of the TM specification. We also allow a special  $\varepsilon$  instruction in the alphabet, which we use in nondeterministic TM specifications. As we see later, the  $\varepsilon$  instruction marks the serialization point of a transaction in a nondeterministic specification.

A TM specification Spec on an alphabet  $\hat{In}$  is a 3-tuple  $\langle Q, q_{init}, \delta \rangle$ , where Q is a set of states,  $q_{init}$  is the initial state, and  $\delta \subseteq Q \times ((\hat{In} \cup \{\varepsilon\}) \times T) \times Q$  is a transition relation. A sequence  $r_0 \ldots r_m$  in  $((\hat{In} \cup \{\varepsilon\}) \times T)^*$  is a run of the TM specification if there exist states  $q_0 \ldots q_{m+1}$  in Q such that  $q_0 = q_{init}$ , and for all i such that  $0 \leq i \leq m$ , we have  $(q_i, r_i, q_{i+1}) \in \delta$ . A history  $h = op_0 \ldots op_k$

corresponds to a run  $r_0 \ldots r_m$  if h is the longest subsequence of operations in  $\hat{O}p$  in  $r_0 \ldots r_m$ .