## BIO-INSPIRED CELLULAR MACHINES: TOWARDS A NEW ELECTRONIC PAPER ARCHITECTURE

THÈSE Nº 3933 (2007)

PRÉSENTÉE LE 7 DÉCEMBRE 2007 À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS Groupe Sanchez SECTION D'INFORMATIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

## Fabien VANNEL

Ingénieur en Electronique et Electrotechnique, Ecole supérieure d'Ingénieurs (ESIEE), Paris, France et de nationalité française

acceptée sur proposition du jury:

Prof. C. Petitpierre, président du jury Prof. E. Sanchez, Prof. D. Mange, directeurs de thèse Prof. G. De Micheli, rapporteur Dr W. Hammer, rapporteur Prof. G. Tempesti, rapporteur

A ma grand-mère.

# Version abrégée

L'informatique est une invention très récente, vieille de quelques décennies seulement. Même si les prémices du calcul automatisé sont bien plus anciens (W. Schickard construisit la première calculatrice mécanique en 1623), il faudra attendre l'invention du transistor par W. Shockley, J. Bardeen et W. Brattain en 1947 pour propulser les calculateurs hors des laboratoire et observer l'omniprésence des systèmes informatiques dans le quotidien de chaque être humain.

Les ordinateurs ne se contentent plus d'être des systèmes très performants, capables d'exécuter des milliards d'opérations par seconde, mais envahissent notre monde en se glissant dans les moindres recoins de notre environnement. De la montre à quartz à l'ordinateur de bureau, en passant par la clé de voiture, le téléphone portable, la télévision, ou la carte de crédit, les microprocesseurs sont omniprésents; il est fort probable qu'ils seront encore plus nombreux demain, et qu'ils pourront se nicher dans nos vêtements ou notre journal.

La recherche incessante de systèmes de plus en plus puissants, plus robustes, plus intelligents, ne passe pas uniquement par l'amélioration des technologies de fabrication des puces électroniques, mais également par la recherche de nouvelles architectures informatiques. Pour atteindre ces objectifs une des voies de recherche est la bioinspiration. La nature est fascinante pour l'ingénieur: quoi de plus intelligent, adaptatif, évolutif et robuste qu'un être vivant? D'une simple cellule possédant son plan de construction sous forme d'ADN va se développer un être multi-cellulaire complet. Ces particularités de la nature ont souvent été étudiées et mimées afin de concevoir des systèmes artificiels adaptatifs, robustes et insensibles aux défaillances. Le modèle POE résume les trois grandes sources de la bio-inspiration: l'évolution des espèces (P: phylogenèse), le développement par division et différenciation d'un être multicellulaire (O: ontogenèse) et l'apprentissage par interaction avec l'environnement (E: épigenèse).

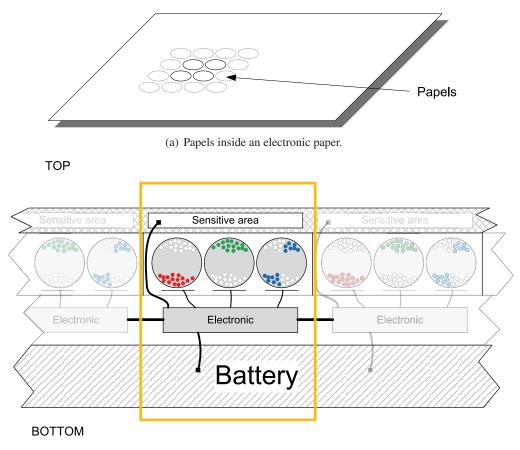

Cette thèse se propose d'approfondir l'étude de l'axe ontogenétique du modèle POE, grâce à l'étude de trois machines informatiques cellulaires tout à fait originales dont l'élément de base satisfait les six caractéristiques suivantes: (1) il est reconfigurable, (2) de complexité minimale, (3) présent en grand nombre, (4) interconnecté avec ses voisins de façon locale, (5) disposant d'un système d'affichage et (6) d'un capteur permettant une interaction minimale.

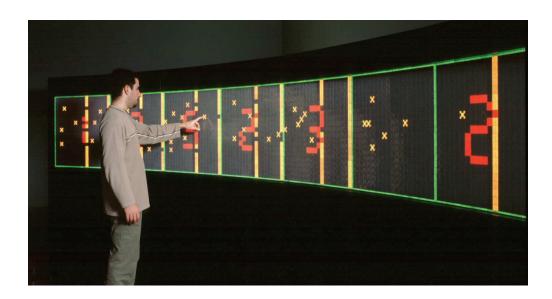

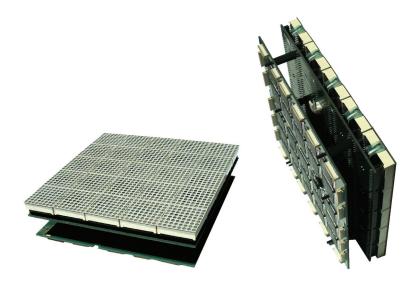

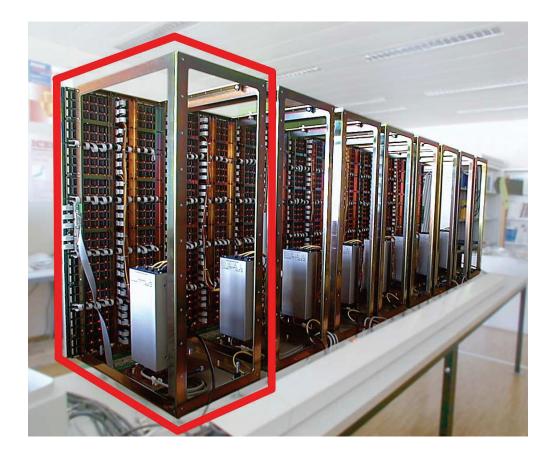

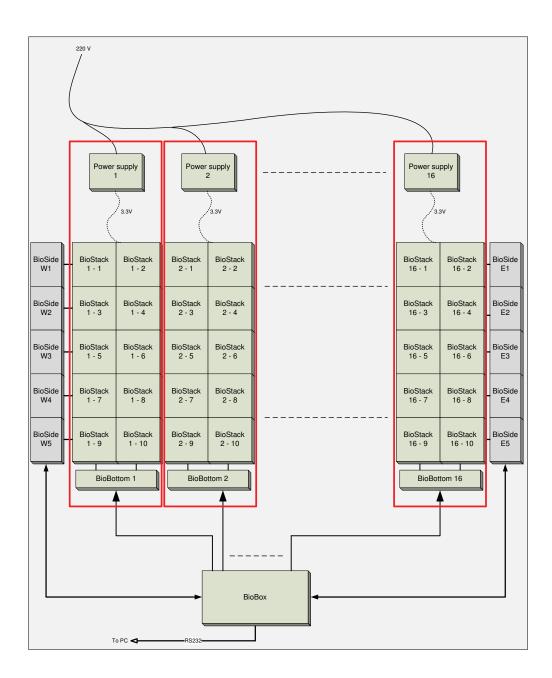

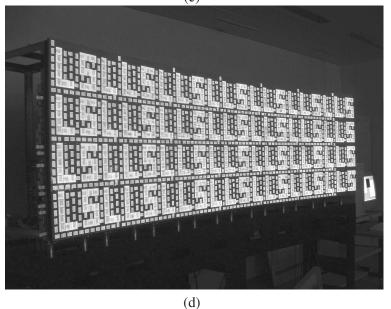

Le BioWall, qui est notre première réalisation, est constitué d'une surface de 4'000 éléments de base ou molécules, aptes à réaliser tous les systèmes cellulaires compor-

tant au plus  $160\times25$  éléments.

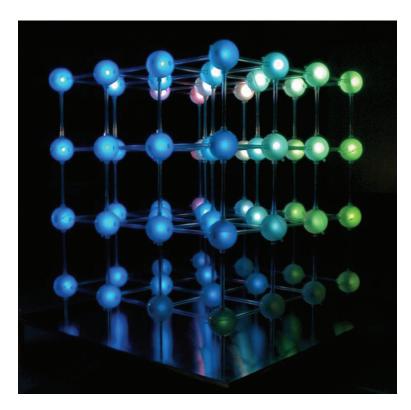

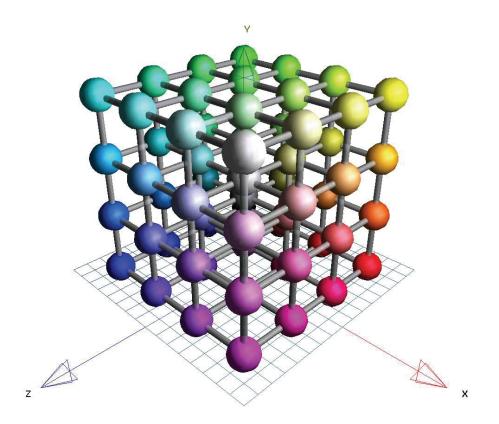

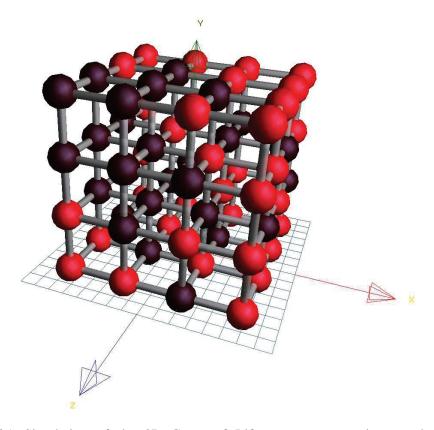

La seconde réalisation, le BioCube, transpose l'architecture à deux dimensions du BioWall dans un espace à trois dimensions, limitée à  $4 \times 4 \times 4 = 64$  éléments de base ou sphères, cherche à préfigurer un ordinateur tridimensionnel construit à partir des nanotechnologies.

Quant à la troisième machine, le BioTissue, elle reprend les hypothèses du BioWall tout en poussant ses performances aux limites des techniques actuelles tout en lui ajoutant les atouts d'un système autonome.

La convergence de ces trois réalisations, étudiées dans le contexte des technologies émergentes, nous amène à définir et proposer l'architecture informatique de l'ordinateur du futur: le tissu ou papier électronique.

**Mot-clés:** système bio-inspiré, ordinateur cellulaire, système reconfigurable, conception électronique, architecture des ordinateurs, Embryonique, tolérance aux pannes, FPGA, nanotechnologies, papier électronique.

# Abstract

Information technology has only been around for about fifty years. Although the beginnings of automatic calculation date from as early as the  $17^{th}$  century (W. Schickard built the first mechanical calculator in 1623), it took the invention of the transistor by W. Shockley, J. Bardeen and W. Brattain in 1947 to catapult calculators out of the laboratory and produce the omnipresence of information and communication systems in today's world.

Computers not only boast very high performance, capable of carrying out billions of operations per second, they are taking over our world, working their way into every last corner of our environment. Microprocessors are in everything, from the quartz watch to the PC via the mobile phone, the television and the credit card. Their continuing spread is very probable, and they will even be able to get into our clothes and newspapers.

The incessant search for increasingly powerful, robust and intelligent systems is not only based on the improvement of technologies for the manufacture of electronic chips, but also on finding new computer architectures. One important source of inspiration for the research of new architectures is the biological world. Nature is fascinating for an engineer: what could be more robust, intelligent and able to adapt and evolve than a living organism? Out of a simple cell, equipped with its own blueprint in the form of DNA, develops a complete multi-cellular organism. The characteristics of the natural world have often been studied and imitated in the design of adaptive, robust and fault-tolerant artificial systems. The POE model resumes the three major sources of bio-inspiration: the evolution of species (P: phylogeny), the development of a multi-cellular organism by division and differentiation (O: ontogeny) and learning by interaction with the environment (E: epigenesis).

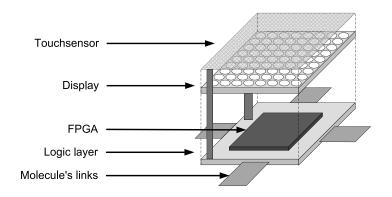

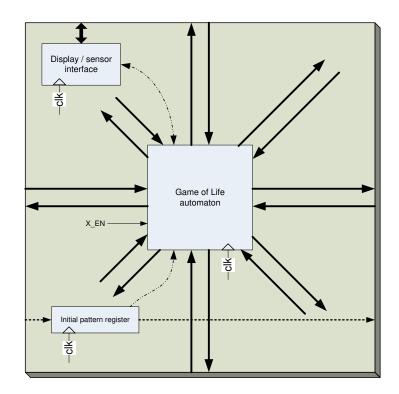

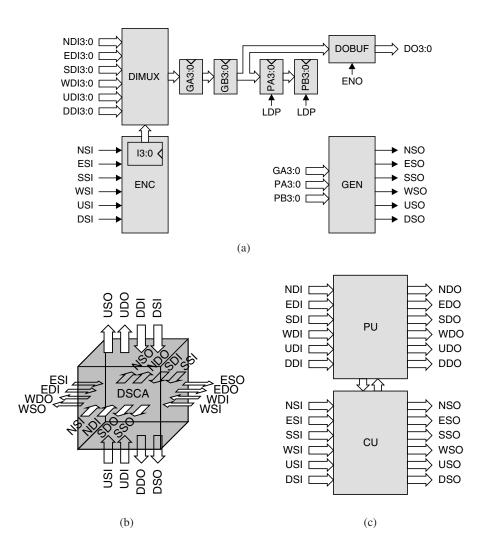

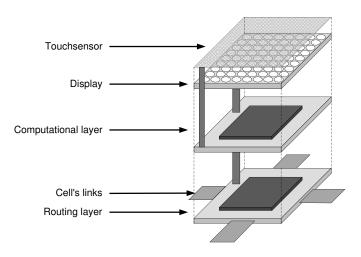

This thesis aims to contribute to the ontogenetic branch of the POE model, through the study of three completely original cellular machines for which the basic element respects the six following characteristics: it is (1) reconfigurable, (2) of minimal complexity, (3) present in large numbers, (4) interconnected locally with its neighboring elements, (5) equipped with a display capacity and (6) with sensor allowing minimal interaction.

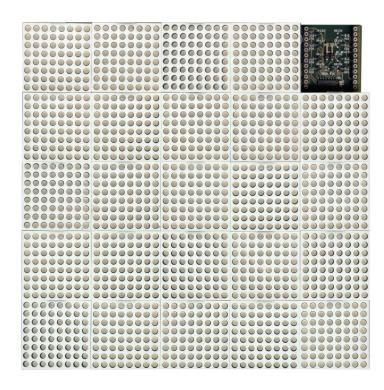

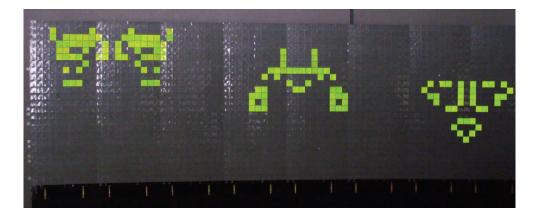

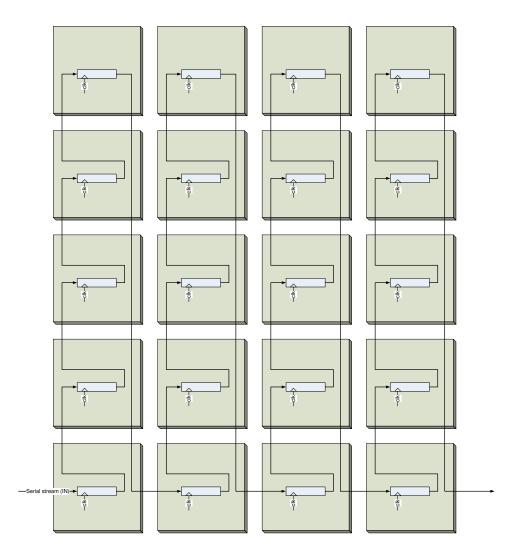

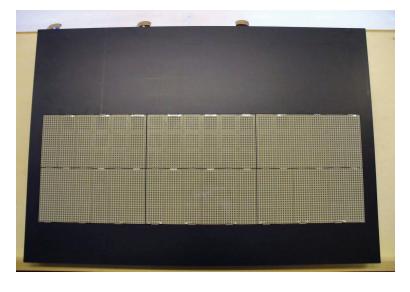

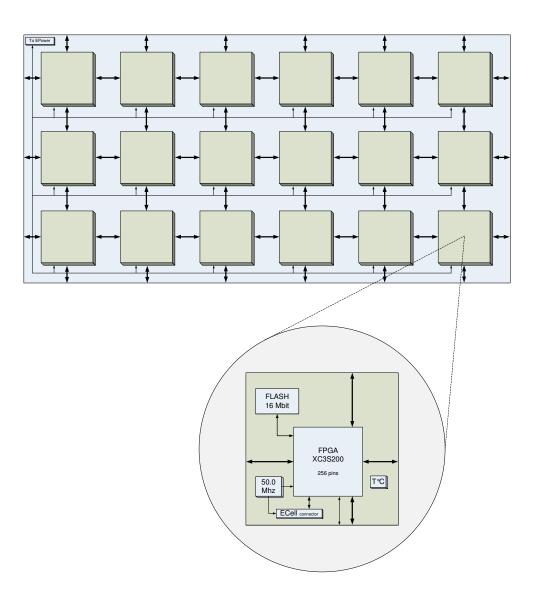

Our first realization, the BioWall, is made up of a surface of 4,000 basic elements or molecules, capable of creating all cellular systems with a maximum of  $160 \times 25$  elements.

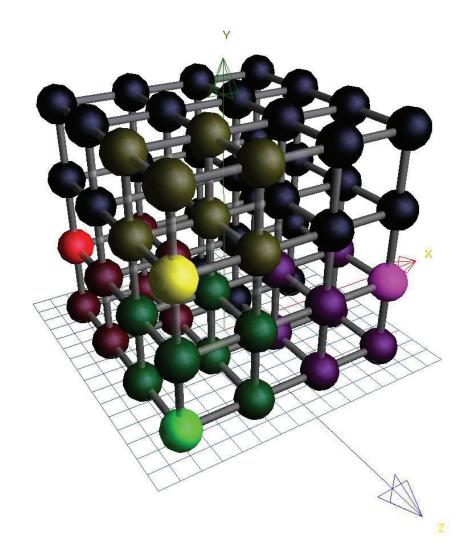

The second realization, the BioCube, transposes the two-dimensional architecture

of the BioWall into a two-dimensional space, limited to  $4 \times 4 \times 4 = 64$  basic elements or spheres. It prefigures a three-dimensional computer built using nanotechnologies.

The third machine, named BioTissue, uses the same hypothesis as the BioWall while pushing its performance to the limits of current technical possibilities and offering the benefits of an autonomous system.

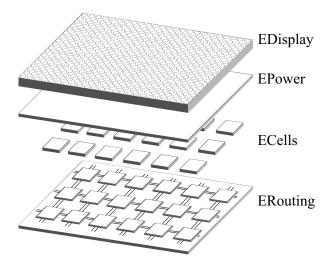

The convergence of these three realizations, studied in the context of emerging technologies, has allowed us to propose and define the computer architecture of the future: the electronic paper.

**Keywords:** bio-inspired hardware, cellular computing, reconfigurable computing, electronic design, computer architecture, Embryonics, fault tolerance, FPGA, nanotechnologies, electronic paper.

## Chapter

## Introduction

HAT would the words *computer* or *computer science* have meant for our grandparents? Probably an inconceivable revolution. For younger people, these concepts are part of the fabric of our world. In less than 50 years, the invention of the transistor has projected the computer from the laboratories to the public place, where it is now found everywhere: watches, mobile phones, music players, cars, credit cards...

Computing needs are evolving towards faster microprocessors and the conquest of new targets and applications. The newspaper becoming a computer [92], and the integration of processors in clothes [79] are just two examples. Computers are also becoming smaller and thinner - less noticeable - but increasing by present in our everyday world.

#### **1.1** Bio-inspired cellular computing

Up to now, the main research in computing has focused on increasing the computational performance of microprocessors. This has been achieved mainly through reducing the size of etching silicon technologies making it possible to increase the operating frequency of the microprocessors. Recently, the demands for ever increasing computing power have been addressed by designing architectures capable of exploiting parallelism at the instruction level through hardware mechanisms such as super-scalar execution. However, all these approaches seem to have reached their practical limits, mainly due to issues related to design complexity and cost-effectiveness.

The current trend in computer design seems to favor a switch to coarser-grain parallelization, typically at the thread level. In other words, high computational power is achieved not by a single very fast and very complex microprocessor, but through the parallel operation of several on-chip processors, each executing a single thread. This kind of approach is currently implemented commercially through multi-core processors and in the research community through the *Multi-processors Systems On Chip* (MPSoCs) term, which is itself largely based on the *Network On Chip* (NoC) paradigm [34, 33].

Extrapolating this trend to take into account the vast amount of on-chip hardware resources that will be available in the next few decades (either through further shrink-

age of silicon fabrication processes or by the introduction of molecular-scale devices), together with the predicted features of such devices (i.e. the impossibility of global synchronization), this approach comes to resemble another computational paradigm, commonly known as *cellular computing*.

Loosely based on the observation that biological organisms are in fact highly complex structures, which function thanks to the parallel operation of vast numbers of relatively simple elements (the cells), this paradigm tries to draw an analogy between multi-cellular organisms and multi-processor systems. At the root of this analogy is the observation that organisms, in addition to being completely asynchronous, are built through a bottom-up self-assembly process and do not require the specification of a complete layout.

The existing interpretations and implementations of this paradigm are extremely varied, ranging from theoretical studies [115, 118] to commercial realizations (notably, the *Cell* CPU [97, 98] jointly developed by IBM<sup>®</sup>, Sony<sup>®</sup> and Toshiba<sup>®</sup>), through wetware-based systems [9], OS-based mechanisms [49] and amorphous computing approaches [2].

Depending on the authors, the *cells* may comprise different levels of complexity ranging from very simple, locally-connected, logic elements to high-performance computing units endowed with memory and complex network capabilities. However, in every case, the basic idea of two-dimensional systems composed of relatively simple connected elements, remains.

#### 1.2 Thesis goal

The objective of this thesis is to study different systems based on a cellular architecture. From the simplest architecture, which can nonetheless do complex computation thanks to its huge size, to the most complex cellular system able to challenge today's computer performances, this thesis will discuss how cellular systems can been applied to solve various problems, and be included in future computing systems. Moreover, newcomer technologies like molecular electronics, or nanoelectronics, will probably be made up of regular arrays interconnected together locally [130]. This thesis will study an algorithm able to configure a cellular network of any size, and which includes fault tolerance capabilities. Our final goal is to propose an architecture which could be used for manufacturing a product of the future: electronic paper.

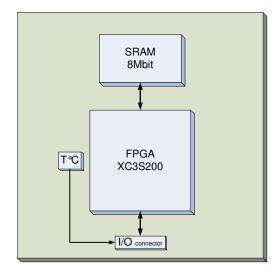

It has long been a practice of our research laboratory to attempt to physically realize, in hardware, systems in order to verify their properties and to analyze their efficiency. Considering the complexity of this kind of systems, prototyping in hardware requires vast amounts of reconfigurable resources, which for this project take the form of Field Programmable Gate Array (FPGA) components, as specified in this thesis. Our realizations are all based on a recurrent basic topology: each cell of our cellular machines is endowed with at least the following three key components: a reconfigurable computing unit, a display element and an external sensor allowing users to interact with the cell.

#### **1.3** Thesis organization

This thesis is divided into 10 chapters. Chapters 3 to 8 present our three realizations. The presentation of each of the three realizations is structured in the same way: a first chapter describes the hardware machine, and a second chapter focuses on applications.

Chapter 2 provides a rather general overview of the world of computer hardware. It summarizes the evolution of the computer from its birth to the current models, and makes some predictions concerning its future. We also outlined the evolution of technologies and of computer hardware architectures. As the focus for the past several decades has been on speeding up processing by miniaturization, we will discuss some new research topics like nanotechnologies for technology improvements, and cellular computing for architecture improvements.

#### 1.3.1 Three biologically-inspired machines

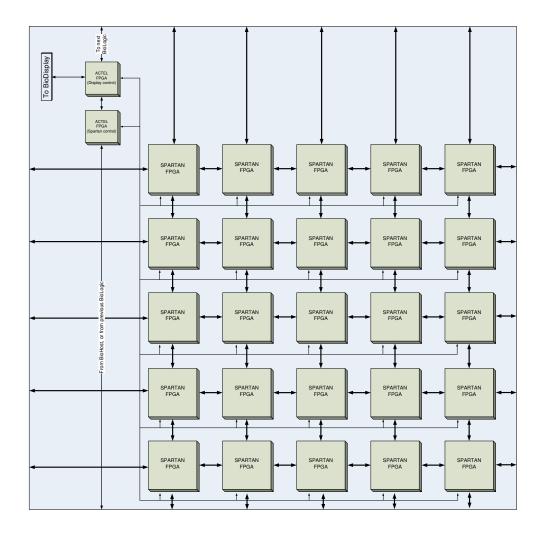

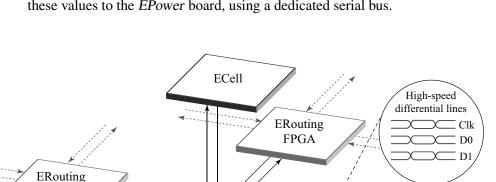

The next chapters describe the three bio-inspired machines developed during this thesis. They are all based on a same common cellular architecture, where several identical units are interconnected using a mesh-network topology. At the heart of each of our units, is an FPGA, which allows several experiments to be easily conducted thanks to its reconfigurable properties and computing performance.

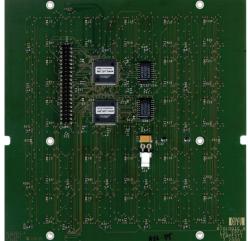

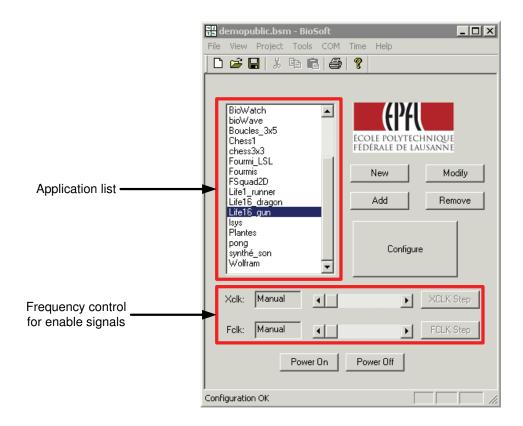

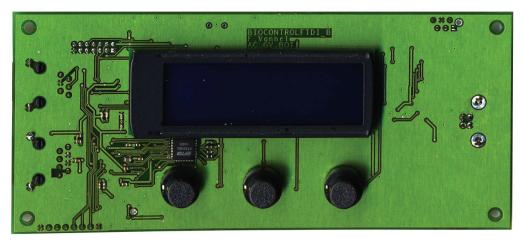

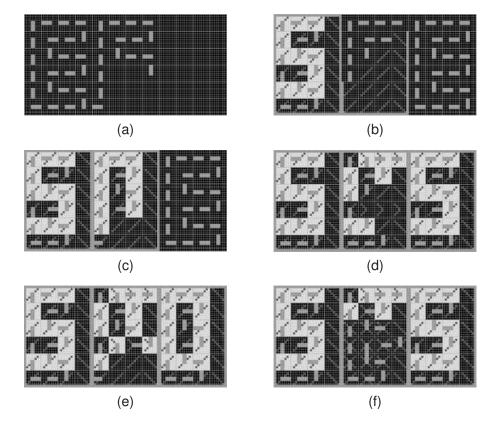

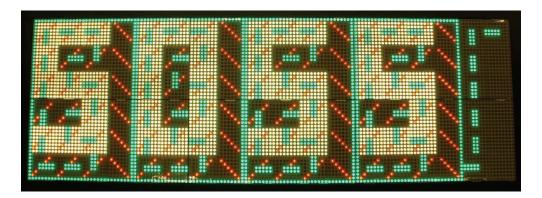

Chapter 3 deals with our first invention: the BioWall. This bio-inspired electronic tissue was firstly developed to study and test the ontogenetic model described in the Embryonics project in hardware. The BioWall is made of 4'000 identical molecules and is also the largest of the three realizations in terms of size. The results obtained from this machine are very promising, but the BioWall needs some additional features and improvements in order to supply the autonomy needed to accomplish our final goal: the electronic paper.

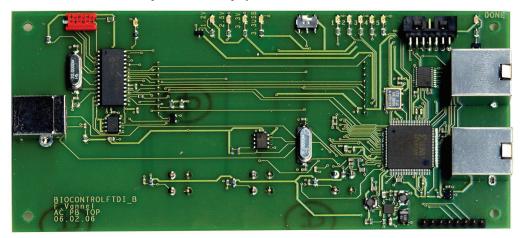

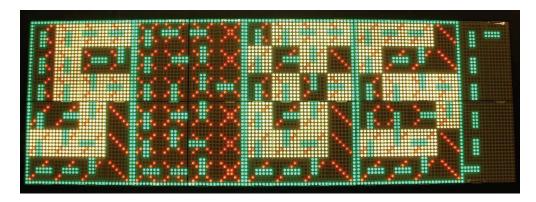

Chapter 5 extends the concept of the BioWall from a wall in 2D to a cube in 3D. This second invention, called the BioCube, proposes an architecture that could be used with promising circuits of the future based on nanotechnologies. Several improvements towards autonomy have been added to this cellular system.

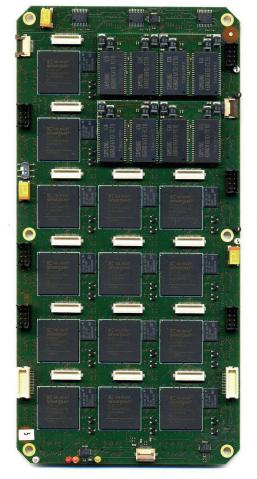

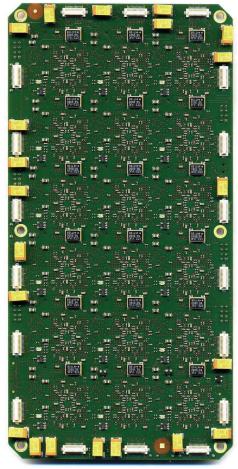

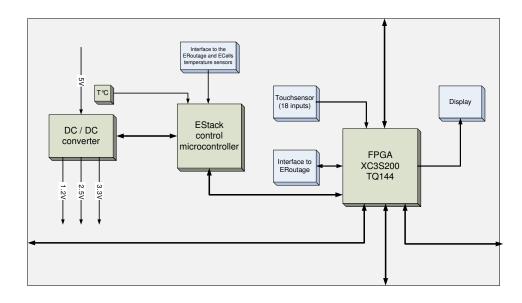

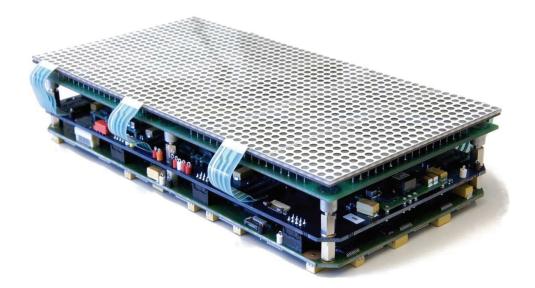

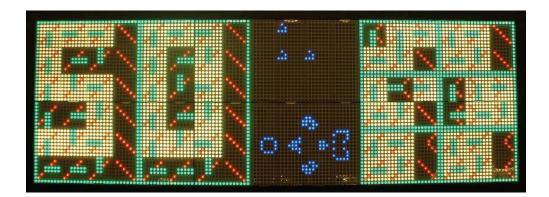

Chapter 7 presents our final realization: the BioTissue. It is the outcome of our current research in terms of systems conceived in hardware. This tablet, still based on a cellular architecture, similar to the BioWall global structure, is fully autonomous and can run several different applications at the same time. Its structure is a precursor of tomorrow's electronic paper architecture.

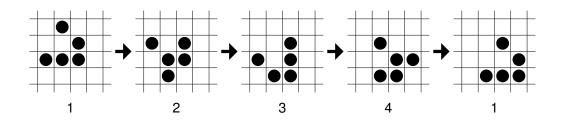

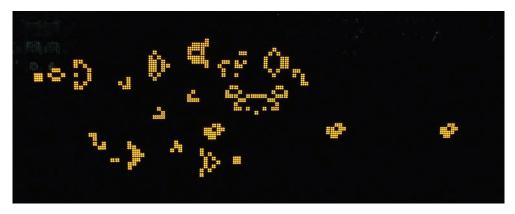

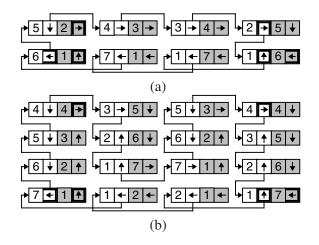

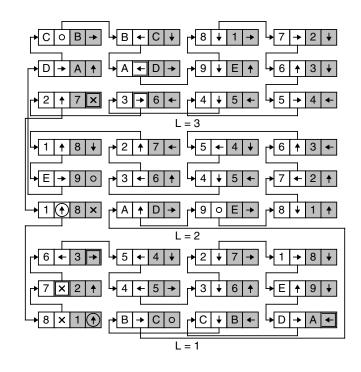

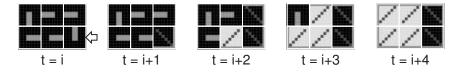

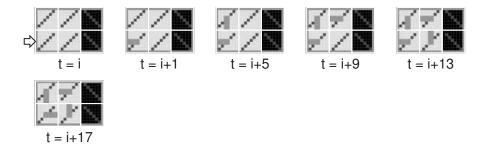

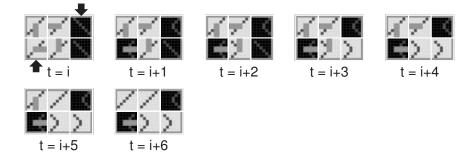

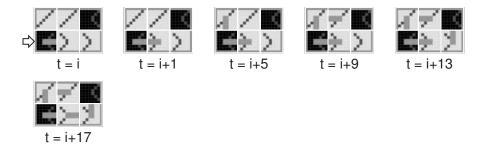

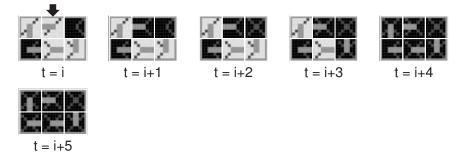

#### **1.3.2** Two common applications

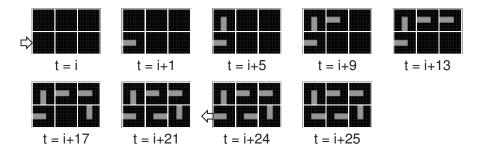

For the purpose of comparing our three architectures, we developed two different applications, that were both implemented in the three different machines. The first application, the Game of Life, will be a useful tool for comparing the performance of each machine and a good example to show how to develop an application on the three systems. The second application, the Tom Thumb replicating loop, is a perfectly dedicated application, which is used for investigating the bio-inspired capabilities of each machine. Improvements to this application are added in each new implementation (depending on the resources of each machine) and the final version implemented onto the BioTissue is the current result of our research on this topic.

Chapter 4 describes these two applications running onto the BioWall, chapter 6 does the same for the BioCube, and chapter 8 shows the evolution of these applications running on the BioTissue.

#### The Game of Life

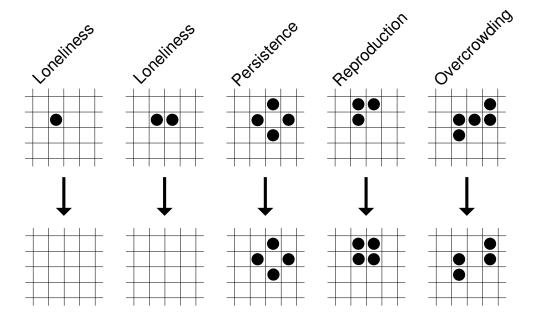

Our first application is a simple Cellular Automata (CA): John Conway's Game of Life [47]. It is probably the best known CA. Chapter 4 will present the principles of this automaton. We chose this application for several reasons:

- This simple automaton is easy to implement on our three realizations.

- Since it is a cellular automaton, it is well suited to our cellular architectures which are perfectly adapted for parallel computation.

- The biological aspects found in this automaton match the bio-inspired quality of our research. "Because of Life's analogies with the rise, fall and alterations of a society of living organisms, it belongs to a growing class of what are called 'simulation games' (games that resemble real life processes)" [47].

- From these simple, local rules, some astoundingly complex global behaviors have been observed and developed, and a tissue with a huge number of automaton cells allows the Game of Life to be programmed to perform computations. Indeed, it is a universal computer [101]. The perfect example of its universality is the implementation of the Turing machine [105].

- Another capacity of this automaton is the self-reproduction of organisms [14], which is part of our research topic.

This application will be tailored to the three systems.

#### Self-replicating loop

The second application is a novel self-replicating loop endowed with universal construction properties, perfectly suited to the regular cellular structure of our systems. The goal of this application is to perform configuration, cloning, cicatrization and regeneration mechanisms through a single process inspired from the biological world.

Self-replicating and self-repairing machines could be used in the development of new physical architectures where defects and failures are common. This is not the case with our current silicon technologies, but could soon be used with the development of molecular electronics where manufacturing defects may be present in many parts of the component. This application proposes a new methodology for configuring a regular network of computational units, even if some units are defective. Our research focuses on a 2D and a 3D network topologies. The cicatrization and regeneration mechanisms have only been added in the last version of our application, i.e. the application running on the BioTissue, as the latter is complex enough to support these processes.

#### **1.3.3** The electronic paper

The final chapter before the conclusion is a summary of our three machines and a proposal for a novel architecture, the electronic paper. Chapter 9 focuses on a possible future system, which would allow computing power to invade our newspapers and our clothes. Our research could be adapted for products like electronic paper. In this chapter, we will discuss how our cellular architectures could be perfectly suited for this kind of product, and for the manufacturing processes of these tissues. Primarily the research done on the BioTissue but also the research on the BioCube will help us to define an architecture specially suited for an electronic tissue, which will hopefully become common after some years once the appropriate manufacturing technologies are be ready.

Chapter 10 resumes our work and gives some ideas for future researches based on our thesis work.

#### **1.4 Contributions**

The following major contributions were important in the realization of this thesis work:

#### 1.4.1 BioWall

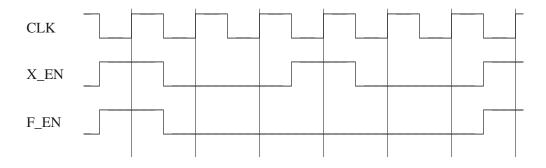

The BioWall was a huge and time consuming realization which involved many researchers of the Logic Systems Laboratory (LSL). As one of the major developers of this machine, I proposed and developed several features for the control and the configuration of this wall: FPGA configuration process, clocking and synchronization of the FPGAs, system supervising, interfaces with external modules (remote control, audio, video). In addition to the hardware side of this machine, important work was done to simplify the implementation of the applications described in chapter 4; many reusable Intellectual Property (IP) cores have been developed for the SPARTAN<sup>®</sup> FPGA. The study and implementation of the applications running on this wall was conducted in collaboration with the BioWall LSL team.

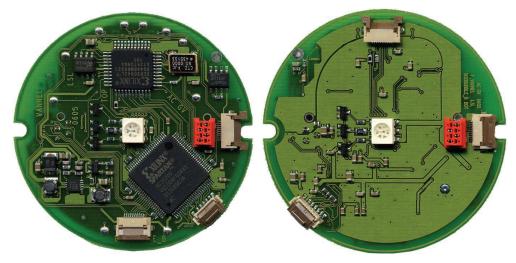

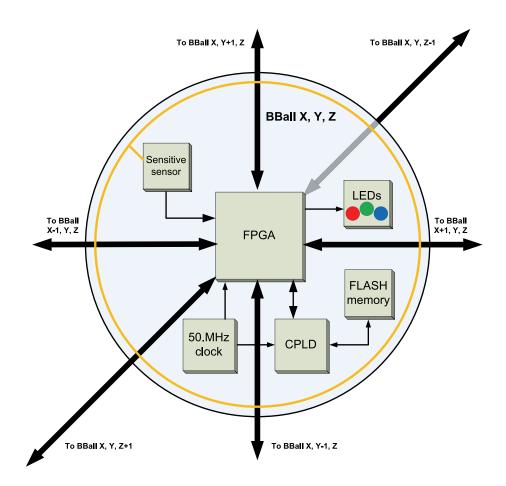

#### 1.4.2 BioCube

The BioCube is an evolution of the BioWall architecture towards the third dimension. Since the dimensions of this new machine are smaller than those of the BioWall, and although it is just as complex or more, I found myself nearly alone to define and build this new system. The definition of the new architecture, the development of the hardware devices and all stages of testing the prototypes were accomplished by myself. The analysis of the capabilities and performance of this machine was carried out via the development of applications as seen in chapter 6. The research concerning the 3D Tom Thumb loop was a collaborative work with researchers of the LSL.

#### 1.4.3 BioTissue

The BioTissue architecture is a novel proposal inspired by the BioWall architecture, but completely revisited to match the new needs I specified to create a powerful,

autonomous cellular machine whose performance is closer to that of an actual Personal Computer (PC) than to a dedicated cellular research tool. Research done on the BioTissue before its construction has always been in connection with the idea of defining and building a machine the architecture of which could fit the needs of a possible electronic paper machine of the future. As well as defining the whole architecture of the BioTissue, I built the machine. The need for an operating system led me to imagine and to implement the  $\mu$ OS application. The help of the LSL researchers was needed to update the Tom Thumb algorithm to create the eSOS application described in chapter 8.

#### 1.4.4 Electronic paper

This thesis would not be complete if we didn't look ahead and find a common future for our three cellular machines. The predicted electronic newspaper product [96], which will be similar to the current paper version, led us to propose an architecture based on our research, which could match the new printing fabrication process of electronic components, while being perfectly adapted to any flat computer like the electronic paper.

# Chapter 2

# The computer through the ages

HE twenty century was a fascinating era with many memorable developments. Since then planes have developed from the first prototype made of wood to the huge Airbus A380, able to carry more than 500 passengers and automobiles have colonized the city. Another evolution, or maybe revolution, happened in less than half a century: the invention of the semiconductor and the democratization of its main application, the computer. In a few decades the computer went from a huge, expensive and slow machine dedicated to a single simple task, to incredibly powerful computers, small, inexpensive, interactive, multitasking, present in each family, and connected all together via the Internet.

This chapter will focus on the computer's history from its first prototype to the current omnipresent machines, and will make some predictions for its future evolution. This subject could fill a book, or even an encyclopedia, let alone a chapter. Studying the history of computers since the first prototype to the current powerful microprocessors is not the aim of this chapter, which will only give some major points which will help understand the research contained in this thesis paper.

Section 2.1 presents a short overview of the main events in the history of the computer and more particularly its main component, the microprocessor. Section 2.2 presents the current microprocessor architectures, and the different components allowing computation. The last section 2.3 is consecrated to our vision for improving microprocessor performance, such as new research into materials, or the introduction of bio-inspired architectures.

#### 2.1 The birth of the computer

Originally, the term "computer" did not refer to a computing machine, but referred to a person who performed numerical calculations [50]. Such a human computer often worked with the aid of mechanical calculating devices like abacus, slide rules or astrolabes.

#### 2.1.1 The first computing machine

If a computing machine is a device able to input data, compute it and produce a result, then the first computing machine is the *Antikythera mechanism* [109, 35] dating from around 80 BC, designed to calculate astronomical positions. Nothing so complex was subsequently developed before the beginning of the 17<sup>th</sup> century, when Wilhelm Schickard conceived the first calculating machine able to accomplish addition, subtraction, multiplication and division [123]. At the same time, Gottfried Leibniz published an article describing the principles of binary arithmetic, the basis of our modern computing numeral system. Two centuries later, George Boole published in 1854 a landmark paper detailing a logic system that would become known as Boolean algebra. The next step toward the implementation of Boolean algebra was performed by Claude Shannon in 1937, who used electronic relays and switches to include binary arithmetic in hardware, the basis of modern computing and practical digital circuit design.

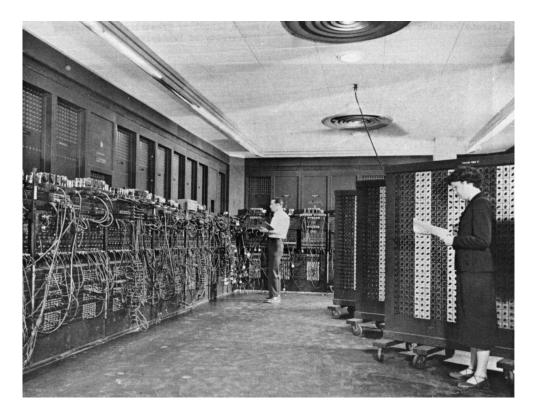

During the first half of the  $20^{th}$  century, several machines were built, mainly for military purposes. The Electronic Numerical Integrator And Computer (ENIAC) [109], the construction of which started in 1943, was the first large-scale, electronic, digital computer capable of being reprogrammed (by rewiring the machine) to solve a full range of computing problems. Physically, ENIAC (Fig. 2.1) was a massive machine of 27 tons, roughly sized  $30m \times 2.4m \times 0.9m$ , and consuming 150 kW of power. This computer was built with 17,468 vacuum tubes, 7,200 crystal diodes, 1,500 relays, 70,000 resistors, 10,000 capacitors and around 5 million hand-soldered joints. Data to process were input using a punched card reader, while a punched card perforator wrote the results. The ENIAC machine could perform 385 multiplication operations per second, but needed to be partially rewired to update its program. Two years after the start of ENIAC, in 1945, John von Neumann, while he was working on the development of the Electronic Discrete Variable Automatic Computer (EDVAC), presented a paper describing the complete design of a stored-program computer, the architecture of which, named "von Neumann architecture", is still used nowadays.

Most of these machines were made of vacuum tubes, which had a notable disadvantage, specially when used in huge number: they tended to leak, and the metal that emitted electrons burned out. Moreover, tubes were big and required so much power that big machines were too large and took too much energy to run. These problems led scientists and engineers to think of other ways to perform the tubes' tasks by looking at how one might control electrons in solid materials, like metals and semiconductors.

#### 2.1.2 The invention of the transistor

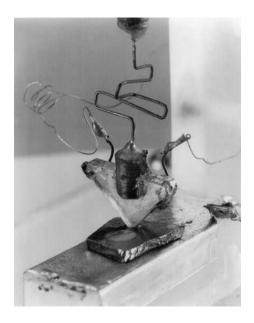

In 1947, John Bardeen and Walter Brattain, working at Bell Telephone Laboratories under the direction of William Shockley, were trying to understand the nature of the electrons at the interface between a metal and a semiconductor, when they realized that by putting two point contacts very close to each other, they could get similar results as a three-electrode tube. They had just invented the first "point contact" transistor. (Fig. 2.2)

Their first application was to build a few of these transistors and to connect them with some other components in order to develop an audio amplifier. This device was

Figure 2.1: The ENIAC machine.

shown to chief executives at Bell Telephone Company, who were very impressed by the fact that it did not need time to warm up before use (unlike the heaters in vacuum tube circuits). The importance of this new technology was immediately realized and this invention was the spark that ignited a huge research effort in solid state electronics. William Shockley developed an improved version of this "point contact" transistor, the junction transistor, which was built on thin slices of different types of semiconductor material pressed together. The junction transistor was easier to understand theoretically, and could be manufactured more reliably. The amazing thing about the invention of this "point contact" transistor is that the first patent for the field-effect transistor principle was registered in Germany in 1928 by the physicist Julius Edgar Lilienfeld. Unfortunately, Lilienfeld did not publish any research articles about his device, and his work was ignored by industry.

For many years, transistors were manufactured as individual electronic components and replaced vacuum tubes in computers. Electronic circuits could be made more complex, with more transistors, switching faster than tubes and consuming much less power. However, it did not take a long time before the limits of this construction technique were reached. Circuits based on transistors became too large and too difficult to assemble since there were too many electronic components to deal with. Global computer performance was limited because the time taken for electric signals to propagate over a long distance could not be reduced any further. To make the circuits even faster, one needed to pack the transistors closer and closer together.

Figure 2.2: The first point contact transistor developed by J. Bardeen and W. Brattain. Paper clips and razor blades were used to make the device.

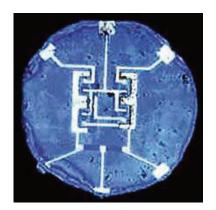

#### 2.1.3 The integrated circuit

In 1958 and 1959, Jack Kilby at Texas Instruments and Robert Noyce at Fairchild Semiconductor, came up, almost simultaneously, with a solution to the problem of packaging a large number of components, and the Integrated Circuit (IC) was born (Fig. 2.3). Instead of making and assembling transistors one-by-one, several transistors could be manufactured at the same time, in the same piece of semiconductor. Not only transistors, but other electric components such as resistors, capacitors and diodes could be realized by the same process into the same material. The first IC contained only around a dozen transistors. Since this time the number of transistors inside an IC has continuously increased, along with the complexity and performance of computers build upon these ICs.

Nowadays, ICs still use the same principle as the concepts developed by J. Kilby [65] and R. Noyce [89]. The structure is still two dimensional and only differs in the substrate used, where silicon has mainly replaced germanium.

#### **2.1.4** From the microprocessor to the Personal Computer (PC)

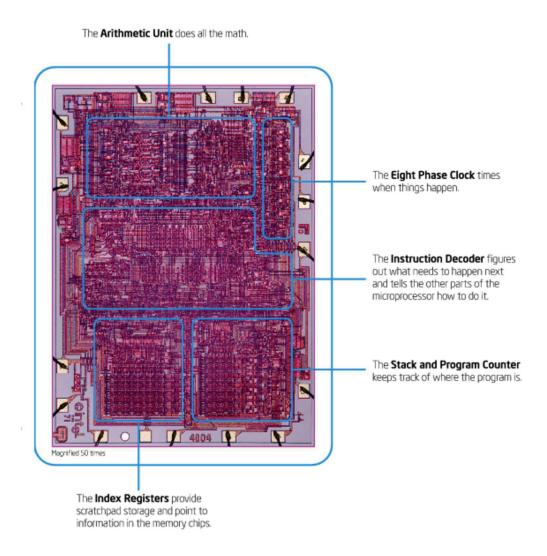

For years, new ICs were built for each new product. The methodology was the same; IC manufacturers got the specifications from their customer and designed a circuit able to compute the customer's needs. The story [17] of the invention of the first microprocessor starts with Busicom, a Japanese company specializing in hand-held calculators, which asked Intel<sup>®</sup> to produce a line of products with different capabilities, each with different advanced mathematical functions, aimed at a different market segment. Instead of manufacturing the multiple requested ICs, Intel<sup>®</sup> focused on looking for a way to design fewer chips with more general capabilities. In 1971, Intel<sup>®</sup> were able to

Figure 2.3: The first IC developed by R. Noyce.

offer Busicom a logic chip that incorporated more of the concepts of a general purpose computer, and which could be used for many other applications besides calculators. The first microprocessor was born: the Intel<sup>®</sup> 4004. With the addition of three other dedicated ICs, a simple microprogrammable computer was built. The other chips contained Read-Only Memory (ROM), Random Access Memory (RAM), and a chip to handle output functions. Together, these ICs constituted a computer as powerful as the ENIAC machine described on page 8. After this, several new more powerful models were designed and sold as general purpose microprocessors. Different products could use the same microprocessors, only software running on these microprocessors was different.

During the following decade, several computers based on microprocessors were built and sold by different companies. Software development become more and more important since it allowed the specialization of each computer to a dedicated task and made it possible to switch between programs easily. In 1981, IBM<sup>®</sup> brought out its first low-cost single-user computer that they dubbed a Personal Computer (PC). This machine came with a monochrome screen, a keyboard and an Operating System (OS). Different kinds of software, for word processing, accounting, spreadsheets and games was developed and sold for use with this kind of machine.

From the time of the first PC, relentless technological advances and innovation have put powerful PCs at the center of daily activities for people worldwide, with more than one billion computers connected to Internet in 2007. The PC has changed the way people communicate, retrieve information, go shopping, and entertain themselves.

#### 2.2 Today's computers

The first Intel<sup>®</sup> microprocessor, the 4004, was a simple 4-bit model made of 2'300 transistors, which worked at a maximum frequency of 108 KHz. Nowadays, microprocessors are 100'000 times more complex than the 4004. They are built with 64-bit architectures, are made of millions of transistors, and have a core frequency of around 3 GHz. Today, microprocessors are available in a wide range of types, architectures, performance and also price. They range from tiny microprocessors costing less than one US dollar and suited for embedded systems requiring low processing performance,

Figure 2.4: The first Intel<sup>®</sup> 4004 microprocessor. Source: Intel<sup>®</sup>.

like watches, to extremely powerful models designed for the fastest computers, but which are enormously power hungry and cost more than a thousand US dollars.

Until very recently, the main research on microprocessors has focused on increasing computational performance. The major factor for performing this task has mainly been through reducing the size of etching silicon technologies, resulting in reduction of the transistor size from 10  $\mu m$  for the Intel<sup>®</sup> 4004 to 0.065  $\mu m$  or 65 nm for the latest microprocessor currently on the market. A higher number of transistors can consequently fit onto the same surface, resulting in higher speeds. Another major key to these performance increases comes from the evolution of the microprocessors architecture.

#### 2.2.1 Microprocessor architecture

From the first microprocessor, which was based on a very simple architecture with a 4-bit Arithmetic Logic Unit (ALU), to the 64-bit microprocessors available today, the principle of operation is still the same: microprocessors execute a sequence of stored instructions, or programs, sequentially to compute information coming from memory or a peripheral, and write the result in memory or send it to a device. To perform this task several microprocessor architectures have been developed over the past few decades, and several architecture models are in use today.

#### Single core

Since speed was the main limitation to technological developments, improvements were made by looking for methods to compute a higher quantity of data during each cycle. Complex Instruction Set Computers (CISCs) and Reduced Instruction Set Computers (RISCs) are two different Central Processing Unit (CPU) architectures which coexist for a long time. Whereas CISC based machines are mainly used in extremely fast and high performance PCs, RISC microprocessors are succeeding in performing the same tasks, at a reduced frequency. RISC architectures are thus often used in tiny or embedded microprocessors working at low power. Several other architectures, theoretically extremely powerful, such as Very Long Instruction Word (VLIW) and Explicitly Parallel Instruction Computing (EPIC) have been invented, but they are not widely used since the development of software for these kinds of CPUs is more complex and thus only used on few highly specialized computers. Aside from the internal CPU structure, several improvements have been made to performance through the addition of cache memory inside the microprocessor chip. Descriptions of all these architectures can be found in several books [91, 53]. Since our thesis work uses several RISC based microprocessors, we describe below some specifications of this architecture.

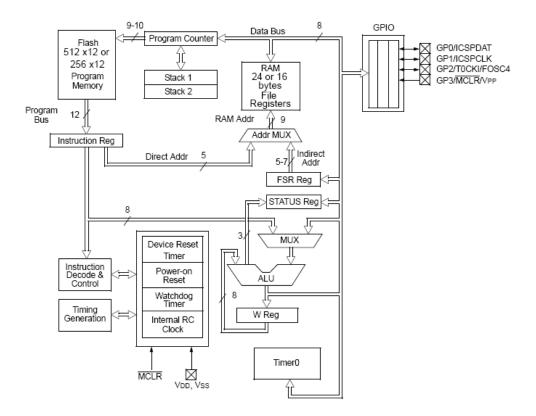

The Reduced Instruction Set Computer (RISC), is a CPU design philosophy that favors an instruction set reduced both in size and complexity of addressing modes, in order to enable easier implementation, greater instruction level parallelism, and more efficient compilers. Our example in figure 2.5 is a simple 8-bit microcontroller<sup>1</sup> based on a Harvard architecture, which is a computer design model, in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architectures where program and data are fetched on the same bus. Separating program and data memory also allows instructions to be sized differently. The Microchip<sup>®</sup> PIC10F20x uses, for example, an 8-bit wide data word, and a 12-bit wide instruction, making it possible to have the whole instruction in a single word. The advantage of a RISC structure is the possibility, by using a pipeline, to execute an instruction at each cycle with the exception of program branches, which could need more than one cycle in some cases.

Recently, the ever-increasing demand of computing power has been met by de-

<sup>&</sup>lt;sup>1</sup>The difference between a Microcontroller unit (MCU) and a microprocessor resides in the additional features included in the same package. An MCU is built upon a microprocessor with embedded memory, and peripherals allowing direct reading and writing on Input/Output (I/O), or including specific communication buses, timers, display drivers...

Figure 2.5: Diagram of the Microchip<sup>®</sup> RISC PIC10F20x microcontroller based on a Harvard architecture. Source: [57]

signing architectures capable of exploiting parallelism at the instruction level through hardware mechanisms such as VLIW super-scalar architecture. However, as previously mentioned, all these approaches have reached their practical limits, mainly due to issues related to design complexity and cost-effectiveness.

#### **Multi-cores**

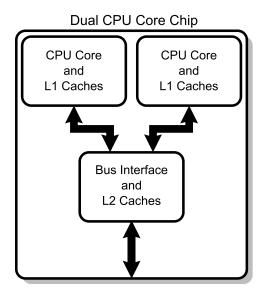

For the past few years, a new trend in computer design has favored another methodology to parallelize computations. Rather than using a unique single very fast and very complex microprocessor, parallelism has been reached by the introduction of multicore microprocessors. A multi-core microprocessor combines into a single physical package, two or more independent single CPUs similar to the one described in the previous paragraph (Fig. 2.6). Each core has its own cache memory and can share a single coherent cache at the highest on-device cache level (e.g. L2 in figure 2.6). The processors also share the same interconnection with the rest of the system. Such architecture with two cores allows concurrent execution of two threads.

Some years after the first dual-core microprocessors, new developments are moving towards processors with quad-, eight- or more cores. Research done on *Multiprocessors Systems On Chip* (MPSoCs), and *Network On Chip* (NoC) systems [34,

Figure 2.6: Diagram of a dual core microprocessor, with CPU-local Level 1 caches, and a shared, on-die Level 2 cache.

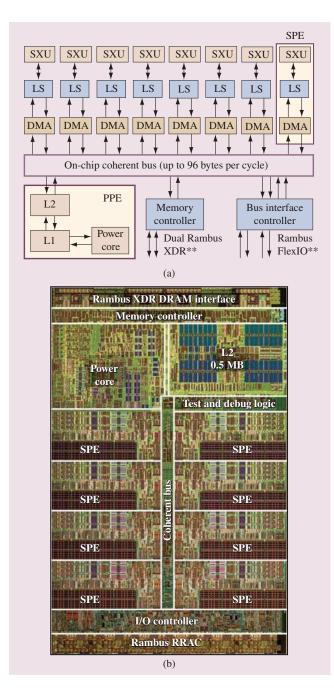

33] have, for example, been used for the development of the *Cell* processor [61, 97, 98] jointly developed by IBM<sup>®</sup>, Sony<sup>®</sup> and Toshiba<sup>®</sup>, which include up to eight identical cores (Fig. 2.7). The multi-core structure is currently used for PC microprocessors (with several dual- or quad-core CPUs), or in game consoles, which require highly powerful CPUs (the *Cell* multi-core microprocessor is used in the Sony<sup>®</sup> PS3). The general trend in this domain will be from multi-core to many-core where the number of independent cores will increase to large numbers of tens or even hundreds, thus allowing as many threads as the number of cores present in the microprocessor to be executed in parallel. The Intel<sup>®</sup> Tera-scale research project [54] tried to study how by varying the mix of functional elements (with experiment up to 100 cores), the Tera-scale architecture can allow designers to create multiple implementations that match specific market needs.

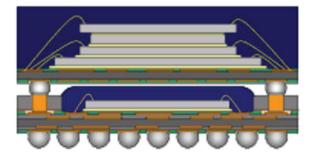

Since all cores are identical, and rather than manufacturing new chips for each new multi-core configuration, a new packaging method, based on 3D stacking, allows each individual core to be stacked in the same package.

#### **3D** electronics

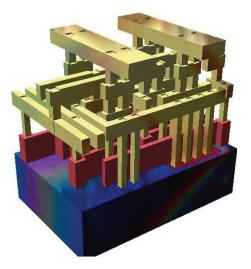

Figure 2.8 represents the rendering of a small Complementary Metal-Oxide-Semiconductor (CMOS) standard cell with three layers of metal. Even if the construction seems to be in 3D, we call this kind of circuit a 2D component, since all the transistors are on the silicon substrate plane (represented in blue in the figure). The definition of 3D integrated circuit would have been to be able to place transistors inside or on top of this metal web [52]. A solution based on a laser recrystallization process has been proposed in 1983 [64]. However, at this time, the additional costs for having several transistors layers was not justified, and this technique has never been used.

Figure 2.7: (a) Cell microprocessor block diagram and (b) die photo. The first generation Cell processor contains a Power Processor Element (PPE) with a Power core, first- and second-level caches (L1 and L2), eight Synergistic Processor Elements (SPEs) each containing a Direct Memory Access (DMA) unit, a Local Store memory (LS) and execution units (SXUs), and memory and bus interface controllers, all interconnected by a coherent on-chip bus. Source: [61] Today, huge silicon surfaces are needed to meet the need for memory components with enormous capacities. The solution for having a large amount of memory within a small package has been reached through stacking several wafer layers in the same package [110]. Several low-cost methods have been developed, and are mainly used by memory chip manufacturers.

A System in Package (SiP) is a number of integrated circuits enclosed in a single package or module. The chips constituting the SiP are stacked vertically inside the package (Fig. 2.9). They are internally connected by fine wires that are buried in the package. A SiP can contain up to 50 silicon dies. Despite its benefits, this technique decreases the yield of fabrication since any defective chip in the package will result in a non-functional packaged integrated circuit, even if all other modules in that same package are functional. Other methods less expensive and simpler to implement exist, like the Stacked Package-Chip Size Package (SP-CSP) stacking where each die is connected to the others using classic bonding technology (Fig. 2.10).

Figure 2.8: CMOS small standard cell with three layers of metal layers. For visual purposes, the dielectric has been removed. The yellow structures are metal interconnections, with the vertical pillars being contacts. The red structures are polysilicon gates, and the blue at the bottom is the crystalline silicon bulk.

Currently SiP are mainly used by memory manufacturers, but are also used for dedicated components used in cellphones, where telecommunication circuits lay over a microprocessor in the same package. The recent developments in multi-core microprocessors are starting to use these technique. Intel<sup>®</sup> for example includes two identical dual-core processors in the same package to produce its quad-core microprocessor.

#### 2.2.2 Components

Nowadays, three approaches are most often used to perform a computing task. The first one consists in building a dedicated component, commonly named Application-

Figure 2.9: Two individual ICs at the bottom-right and a stacked chip made of 19 layers of these ICs. Source: [58]

Figure 2.10: Cross-sectional schematic of SP-CSP. Source: [62]

Specific Integrated Circuit (ASIC), which will be suited for this specific task. The second method is to use a microprocessor, which has the advantage of being able to execute many other different tasks, but the disadvantage of not being as powerful an ASIC since its architecture allows it to processes only sequential programs. The third approach is to use a Field Programmable Gate Array (FPGA), which combines the advantages of both microprocessors and ASICs.

Table 2.1 summarizes the advantages and disadvantages of these three families, which will be described in the next paragraphs.

#### ASIC

An Application-Specific Integrated Circuit (ASIC) is an integrated circuit (IC) customized for a particular use, rather than for a general use. The design of an ASIC leaves for engineers the liberty to design the circuit according to their specifications. The engineer can specify the exhaustive features of the chip and optimize the functionality of the circuit, or the power consumption. It is possible to distinguish semicustom integrated circuits, where only logic gates blocks are placed and routed, and full-custom circuits, where even the characteristics of each transistor can be specified.

Nowadays many components libraries are available for the designer, who can buy

|                             | ASIC | Microprocessor | FPGA |

|-----------------------------|------|----------------|------|

| Performance <sup>a</sup>    | +    | +              | 0    |

| Parallelism                 | +    | 0              | +    |

| General use                 | -    | +              | +    |

| Reconfigurability           | -    | +              | +    |

| Component cost <sup>b</sup> | +    | 0              | -    |

| Development costs           | -    | +              | 0    |

| Development time            | -    | +              | 0    |

<sup>a</sup>In terms of clock speed.

<sup>b</sup>Indication based on high volume.

Table 2.1: Comparison of microprocessor, ASIC and FPGA technologies.("-" means disadvantage "0" neutral and "+" advantage).

specific blocks, also called Intellectual Property (IP) modules. An IP can be for example a MP3 audio decoder, a memory module, an encryption system.... Since production costs are very high, particular care should be taken with verification. The whole circuit should be simulated to avoid errors, which are expensive and can cause big delays to the project. To simplify the conception, designers most often use System-On-Chip (SoC) [5] methodologies, which allow several modules to be designed in parallel, optimized, tested, and integrated together into the same circuit.

#### Microprocessors

The best example of an ASIC full custom design is the PC microprocessor, where the end goal is high frequency. Microprocessors are the most commonly used components, perfectly suited for computing. Their sequential programming helps to easily develop programs. The microprocessor family includes microprocessors from the well-known PC microprocessor, extremely powerful and fast, to the tiny microprocessor of your watch, which is slow and low power. MCUs and Digital Signal Processors (DSPs) are the perfect example of ICs that include one microprocessor and additional features, like memory, I/O interfaces, bus controllers, analog interfaces, display controllers in the same package... The MCU model is often chosen based on the peripherals and memory resources of the component, more than on the microprocessor features.

#### FPGA

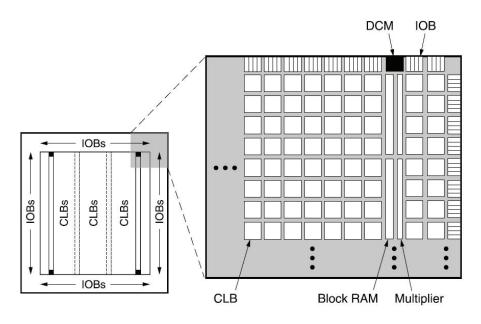

A field-programmable gate array is a semiconductor device containing programmable logic components called "logic blocks", or CLB, and programmable interconnections (Fig. 2.11). Logic blocks can be programmed to perform the function of basic logic gates such as AND, XOR, or more complex combinational functions such as decoders or simple mathematical functions. In most FPGAs, the logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memories. A hierarchy of programmable connections allows logic blocks to be interconnected as needed by the system designer, somewhat like a one-chip programmable breadboard.

Figure 2.11: SPARTAN<sup>®</sup> 3 Family Architecture. Source: [142]

Logic blocks and connections can be programmed by the customer or designer, after the FPGA is manufactured, to implement any logical function.

FPGAs are usually slower than their Application-Specific Integrated Circuit (ASIC) counterparts, as they handle a more complex design, and draw more power. But their advantages include a shorter time to market, ability to be re-programmed, and low development costs. The main difference between programming a standard microprocessor chip and an FPGA are into the program. Microprocessor involves the specification of a sequence of actions, or instructions, while FPGA involves a configuration of the machine itself, often at the gate level.

The FPGAs have the main advantage of being able to fulfill the same role as a MCU since they can embed microprocessor softcores in their configuration. Then, once the FPGA is configured, its microprocessor can be programmed to execute a sequential program. Advantages over MCU solution can reside in the possibility to integrate specific customs periphericals.

After the prototyping and test phases, it is still possible to migrate the developed design into a fixed version that more resembles to an ASIC [42].

#### **2.3** The future of the computer

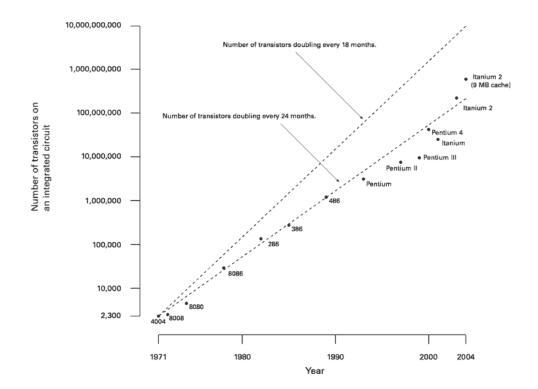

In 1965, a researcher named Gordon E. Moore made the empirical observation that the number of transistors on an integrated circuit doubles every 24 months: "The complexity for minimum component costs has increased at a rate of roughly a factor of two per year ... Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years. That means by 1975, the number of components per integrated circuit for

minimum cost will be 65,000. I believe that such a large circuit can be built on a single wafer." [82]

Figure 2.12: Moore's law: growth of transistor counts for Intel<sup>®</sup> processors.

This prediction was made a few years after the realization of the first IC; 40 years later, Moore's law is still correct [30]. Figure 2.12 shows the evolution of the number of transistors for Intel<sup>®</sup> microprocessors, with a line representing the prediction of Moore's law. Many factors are linked to the evolution of transistor number: the size decrease, the power consumption decrease, the price decrease, the frequency increase of a transistor. The observation of the evolution of all these factors also matches the prediction of Moore's law. Another factor is correlated with this law: the price of an IC foundry, which is, for a current brand new factory, about one billion US Dollars. Moore's law has been applied to several electronic domains, and states for example that RAM storage capacity increases at the same rate as microprocessor performance.

Currently, PC microprocessors are fabricated using a 65nm process. The next generation will be 45nm and will start to be commercially produced at the end of 2007 [31]. Research for building the next generation foundry, which will be 32nm, is on the way. In some years, silicon process technologies will approach the physical limits of the atomic structure. The semiconductor industry's roadmap identifies a near future where current CMOS technology will no longer be adequate, since scaling the transistor down to atomic size will become ineffective and very costly [59]. This could happen in less than a decade. Will it be the end of Moore's law? [41]

#### 2.3.1 Nanotechnology and future architectures

Because of the need for ever better systems, and more powerful PCs with new features, it seems that the evolution of the computer will continue, at least until the singularity has been reached [68]. Predictions place this date prior to the end of our century, which mean that up to this date, new technologies need to be developed by humans. However, the CMOS silicon will reach its manufacturing limits before the ultimate computer [138] targeting the singularity is developed. Thus, new technologies such as nanotechnology<sup>2</sup> [103, 95, 43] will have to take over the current CMOS silicon technology. In 1959 Richard Feynman introduced this field of research in his well-known statement: "There is plenty of room at the bottom" [44]. He stated that from the point of view of physics there are not in principle any obstacles for implementing devices at the atomic level. Nowadays it is evident that nanotechnology has grown into a multidisciplinary field, drawing from chemistry, biology, computer science and mechanical engineering [112].

However, there is a lack of consensus on what type of technology and computing architecture will take over. Several research direction, all based on nanotechnology, are already on the go. Among them, the most probable break through technology successor to the current silicon technology are:

- **Nanoelectronics**, the main elements of which are constituted of nanotubes or nanowires. Nanotubes are predicted as replacements for transistors, whereas nanowires will be able to link together components at the nanometer scale.

- **Molecular electronics** aims to ultimately miniaturize logic circuits using single molecules which will act as electronic switches and storages elements [26, 135, 134].

- **Quantum computing** breaks the classic paradigm by introducing *qubits* in place of bits. Physical quantic phenomena will help solve problems exponentially faster than our classical methods [138, 24].

- **DNA computing** allows to computation to be carried out directly on molecules. All operations are performed using specific Deoxyribonucleic Acid (DNA) strands. Its main advantages reside in its massively parallel computing strength [19]. Unfortunately, the reliability of the computational process with the amount of DNA that must be supplied is not verifiable.

- **Membrane computing** is another biological field, where computations are performed inside a region defined by a membrane structure. Membranes can evolve and dissolve themselves to allow the next operations to be performed [130]. Although the formal approach to membrane computing is completely described in theory, no implementation exists yet.

<sup>&</sup>lt;sup>2</sup>Nanotechnology definition (Dr. Mike Roco, National Science and Technology Council, February 2000): "research and technology development at the atomic, molecular or macromolecular levels, in the length scale of approximately 1–100 nanometer range, to provide a fundamental understanding of phenomena and materials at the nanoscale and to create and use structures, devices and systems that have novel properties and functions because of their small and/or intermediate size."

Based on current results, nanoelectronics will probably be the first breakthrough technology ready for manufacturing a future microprocessor generation. However this new revolution will not be ready for a huge production before a decade.

In parallel to these attempts to produce a mature substitute for the CMOS silicon technology, researchers are working on many other fields. Among these fields, we can mention the research for new microprocessor architectures, which may increase processor performance, using massive parallelism similar to biological cellular structure for example.

The future of the computer lies not only in increasing performance, but also the arrival of the pervasive computing, where computation capabilities are less crucial than size, or physical structure. One of the current research domains involves the realization of thousands of identical autonomous microcomputers which could be scattered in fields or included in wall paint in the aim of gathering specific information and communicating it to a user through an auto-organized network. The Smart Dust project is a perfect example of such a project, the aim of which is to build such a system in a cubic millimeter [137].

Processors are also looking to conquer new applications like the newspaper [67]. This kind of application does not require powerful system, but needs the integration of CMOS technology into new materials like flexible polymers.

The following paragraphs will be focus on two of the most promising new paradigms: nanoelectronics and bio-inspiration.

#### 2.3.2 Nanoelectronics and nano-computer

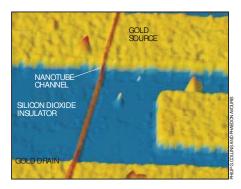

The ultimate operating limit of the silicon transistor may be around 10 nm, or about 30 atoms long. Since it will be crucial to find alternative technologies that can further shrink computing devices, the most promising candidates are nanotubes and nanowires. Carbon nanotubes (Fig. 2.13) are cylindrical carbon molecules with novel properties that make them potentially useful in a wide variety of applications and especially in the nanoelectronics domain. A nanotube is a seamless cylinder with a diameter of around a nanometer and whose length-to-diameter ratio exceeds 10,000. Depending on its structure, a nanotube can have semiconductor properties (Fig. 2.13), or behave like a metallic element, giving it electric conductive abilities. Nanotubes

Figure 2.13: Representation of a twisted carbon nanotube, which behaves like a semiconductor. Source: [27]

differ from the current materials used in the electronic field in several novel properties, and especially in their capacity to carry high currents. As a comparison, the current density estimated for a nanotube is around 1 billion amps per square centimeter, whereas copper wires burn out at about 1 million  $\frac{A}{cm^2}$ . Researchers have succeeded in building transistor components using nanotubes [27] (Fig. 2.14), and designing a microprocessor using nanotubes could become a reality in some years [12].

Figure 2.14: Nanotube used in an experimental field-effect transistor. Source: [27]

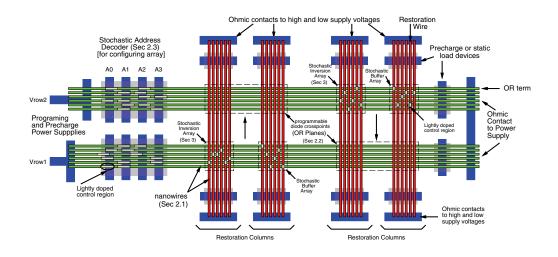

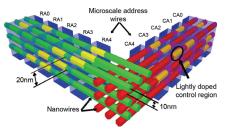

For example, André Dehon has specialized his research in the development of nanoelectronic architectures toward the development of Programmable Logic Array (PLA) [36]. Figure 2.15 shows an example of a PLA structure able to realize combinational functions: the first step toward FPGAs built with carbon nanotubes and nanowires. In the nanoelectronic world, the construction of 3D structures will be much easier than with CMOS silicon technologies. Thus, creation of 3D chips could be considered once the technology is mature (Fig 2.16).

Figure 2.15: Example of a nanowire PLA structure. Source: [36]

Relative sizes and number of wires not shown to scale.

Figure 2.16: Details of a 3D Nanowire PLA. Source: [48]

#### 2.3.3 Bio-inspiration

The evolution of technology is the product of human imagination. We have been able to create some really impressive and powerful systems, like the one discussed in this thesis: the microprocessor. Developing and manufacturing microprocessors is extremely expensive. The cost for building and equipping a cleanroom is currently near to a billion US dollars. Moreover, the latest PC microprocessors are certainly very powerful, but they need a lot of power, and thus need to be cooled.

On the other hand, Nature has found incredibly good solutions for building extremely small and complex living systems, moreover at an incredibly low cost and low power consumption. The human brain, for example, is able to perform extremely complex operations like object recognition. The biggest computers, the size of which is many times greater than a human brain, are not yet able to perform this task, and are limited to the recognition of some pre-learned objects.

Rather than trying to improve our current technologies by miniaturizing the transistor size, it could be interesting to look at how Nature has created the living world, and thus try to find some ideas that might be used for designing or manufacturing microprocessors. If we look closer, a living creature is composed of cells, the number of which may vary from one for a bacterium, to hundred trillion for a human being. Each cell has in common the construction map of the whole organism, the DNA. The human cell, sizing about  $10\mu m$ , is able to self-replicate in a few minutes, with its 3 billion DNA pairs perfectly copied. The most spectacular aspect of this process may be that this transformation requires little energy and occurs at normal temperature and pressure (unlike the IC process which needs strong acids, high temperatures and pressures and a dust free atmosphere).

It is thus very interesting to copy Nature in our research. The aim is not to use natural processes and add them to our microprocessor design, but to try to take inspiration from them and find applications where they could be used. Bio-inspiration is not a new concept and has already been introduced into computer science [78], but several research fields could still benefit from this approach to find new developments.

#### The POE model

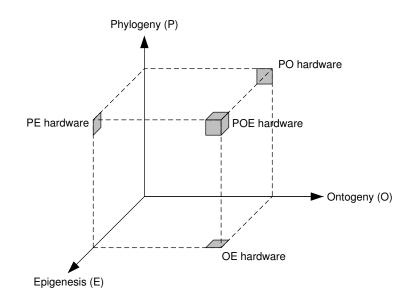

Bio-inspiration encompasses a lot of different areas. To help researchers to define their bio-inspiration domain, a classification model has been proposed, the POE model [119,

111]. If we consider life on Earth since its very beginning, then the following three levels of organization can be distinguished [119, 111]:

- **Phylogeny:** The first level concerns the temporal evolution of the genetic program, the hallmark of which is the evolution of species, or phylogeny. The multiplication of living organisms is based upon the reproduction of the program, subject to an extremely low error rate at the individual level, so as to ensure that the identity of the offspring remains practically unchanged. Mutation (asexual reproduction) or mutation along with recombination (sexual reproduction) give rise to the emergence of new organisms. The phylogenetic mechanisms are fundamentally non-deterministic, with the mutation and recombination rate providing a major source of diversity. This diversity is vital for the survival of living species, for their continuous adaptation to a changing environment, and for the appearance of new species.

- **Ontogeny:** Upon the appearance of multicellular organisms, a second level of biological organization manifests itself. The successive divisions of the mother cell, the zygote, with each newly formed cell possessing a copy of the original genome, is followed by a specialization of the daughter cells in accordance with their surroundings, i.e., their position within the ensemble. This latter phase is known as cellular differentiation. Ontogeny is thus the developmental process of a multicellular organism. This process is essentially deterministic: an error in a single base within the genome can provoke an ontogenetic sequence which results in notable, possibly lethal, malformations.

- Epigenesis: The ontogenetic program is limited in the amount of information that can be stored, thereby rendering the complete specification of the organism impossible. A well-known example is that of the human brain with some  $10^{10}$  neurones and  $10^{14}$  connections: far too large a number to be completely specified in the four-character genome of length approximately  $3 \times 10^9$ . Therefore, upon reaching a certain level of complexity, there must emerge a different process that permits the individual to integrate the vast quantity of interactions with the outside world. This process is known as epigenesis, and primarily includes the nervous system, the immune system, and the endocrine system. These systems are characterized by the possession of a basic structure that is entirely defined by the genome (the innate part), which is then subjected to modification through lifetime interactions of the individual with the environment (the acquired part). The epigenetic processes can be loosely grouped under the heading of *learning* systems.

In analogy to nature, the space of bio-inspired hardware systems can be partitioned along these three axes: *phylogeny*, *ontogeny*, and *epigenesis*, giving rise to the POE model. Combinations of these components over these three axes give new possibilities for research fields (Fig. 2.17).

The following list gives the computer applications and implementations of these three axis and their combinations:

• P: If in life, phylogeny principally concerns the genetic evolution of species,

Figure 2.17: The tri-dimensional representation of the POE model

then in the engineering world this corresponds mainly to the panel of evolutionary algorithms, genetic algorithms and evolvable hardware [55, 112].

- O: The *ontogenetic* axis involves the development of a single individual from its own genetic material, essentially without environmental interactions. It involves multi-cellular organization, cellular division and differentiation from the mother cell to the daughter cells. Each daughter cell possesses a copy of the original genome. Our thesis research will be mainly based on this axis of inspiration.

- E: The *epigenetic* axis involves learning through environmental interactions that take place after formation of the individual. Artificial neural networks are the most common illustration of *epigenesis* [63].

- **PO**: The combination of the *phylogeny* and *ontogeny* axes exhibits the evolution of cellular structures, and the creation of self-reproducing and self-healing evolvable hardware. The Morphogenetic Evolutionary System is an example of such a PO plane [108].

- **PE**: An example of the PE plane is evolutionary artificial neural networks, where evolution allows adaptation of the network structure, the synaptic weights and/or learning rules [144].

- **OE**: This plane combines ontogenetic mechanisms (self-replication, self-repair) with epigenetic learning (neural network). The combination gives self-reproducing and self-healing learning hardware systems.

- **POE**: This space comprises systems that exhibit characteristics pertaining to all three axes, like a hardware system that exhibits learning, evolutionary diversity and a multi-cellular array [111, 120]. The POETIC project concluded the realization of IC able to support these three axes [84].

From a technological point of view we observed that many bio-inspired realizations are based on programmable circuits like FPGAs.

Of these three bio-inspired research axes, we will focus on *ontogeny* in the next paragraph, with the presentation of an original bio-inspired research project developed by the Logic Systems Laboratory (LSL) team: the Embryonics project.

#### The Embryonics project

In the previous paragraph we mentioned the powerful characteristics of the human being, whose hundred trillion of cells execute their genome, divide and replicate ceaselessly from conception to the death of the individual. Faults are rare and, in the majority of cases, successfully detected and repaired. This remarkable process relies on the structure of the DNA for its complexity and its precision. The Embryonics<sup>3</sup> project [75, 76, 78] is inspired by the basic processes of molecular biology and by the embryonic development of living beings. By adopting certain features of cellular organization, and by transposing them to the two-dimensional world of integrated circuits on silicon, the Embryonics project shows that properties unique to the living world, such as self-replication and self-repair, can also be applied to Integrated Circuits (ICs), and proposes a novel robust architecture to fulfill these objectives.

Almost every living being, with the notable exceptions of viruses and bacteria, share the same basic principles for their organization. The incredible complexity present in organisms is based on multi-cellular organization where cells having a limited function are able to behave on very complex ways by assembling themselves into specific structures and operating in parallel.

Each cell can be considered as universal since each contains the whole of the organism's genetic material, the genome. The Embryonics project is based on the same structure and features the three fundamental features of an organism:

- 1. **Multicellular organization** divides the organism into a finite number of cells, each charged with a unique function (neuron, muscle, intestine,...). The same organism can contain multiple cells of the same kind.

- 2. **Cellular division** is the process whereby each cell (beginning with the first cell or zygote) generates one or two daughter cells. During this division, all of the genetic material of the mother cell, the genome, is copied into the daughter cell(s).

- 3. Cellular differentiation defines the role of each cell of the organism, that is, its particular function (neuron, muscle, intestine,...). This specialization of the cell is obtained through the expression of part of the genome, consisting of one or more genes, and depends essentially on the physical position of the cell in the organism

When a minor (wound) or major (loss of an organ) trauma occurs, living organisms are thus potentially capable of self-repair (i.e. cicatrization) or self-replication (i.e. cloning or budding). The main goal of the Embryonics project is the implementation of the above three features of living organisms in an integrated circuit in silicon, in order to obtain the properties of self-repair and self-replication.

<sup>&</sup>lt;sup>3</sup>For embryonic electronics

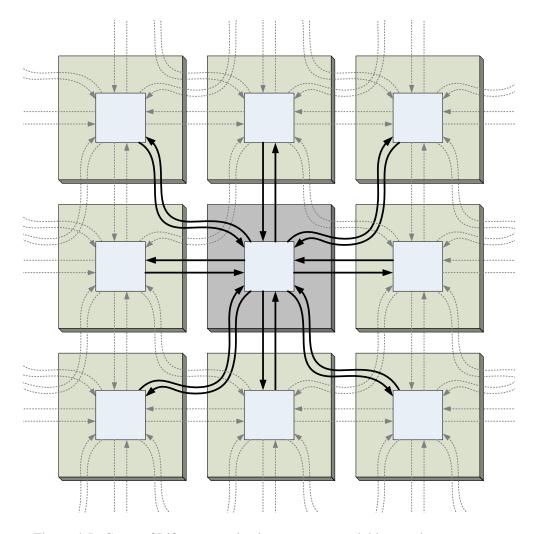

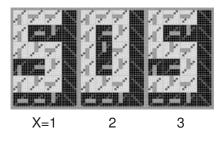

**Multicellular organization** The Embryonics project is based on a regular two dimensional grid, similar to the silicon process possibility, but different from the living world where cells are organized on a three dimensional structure.

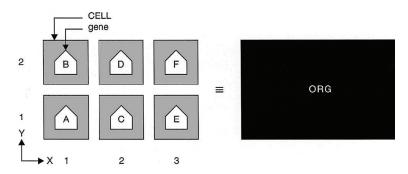

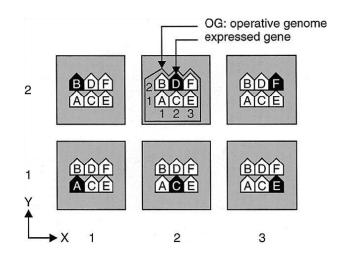

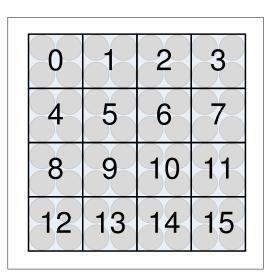

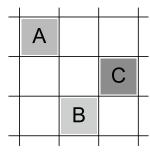

The artificial organism is divided by the multicellular organization into a finite number of cells; each cell realizes a unique function, defined by a subprogram called the gene of the cell, which is part of the genome (Fig. 2.18). The same organism can contain multiple cells expressing the same gene. However, the state and values computed by each cell are independent from the other cells.

Figure 2.18: Multicellular organization of a 6-cell organism expressing 6 different genes.

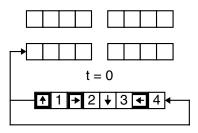

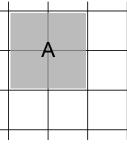

**Cellular differentiation** The operative genome (OG) is the program containing all the genes of an artificial organism, where each gene (A to F) is a subprogram characterized by a set of instructions and by the cell's position (coordinates X,Y=1,1 to X,Y=3,2).

When each cell contains the entire operative genome (Fig. 2.19), depending on its position in the array, i.e., its place within the organism, each cell can interpret the operative genome and extract then execute the gene which defines its function.

In summary, storing the whole operative genome in each cell makes the cell universal: it can execute any one of the genes of the operative genome and thus implement *cellular differentiation*.

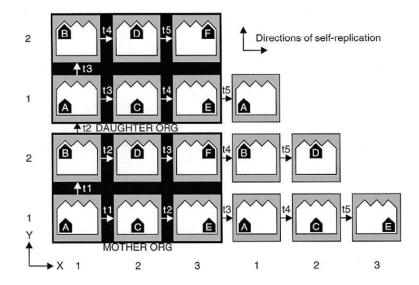

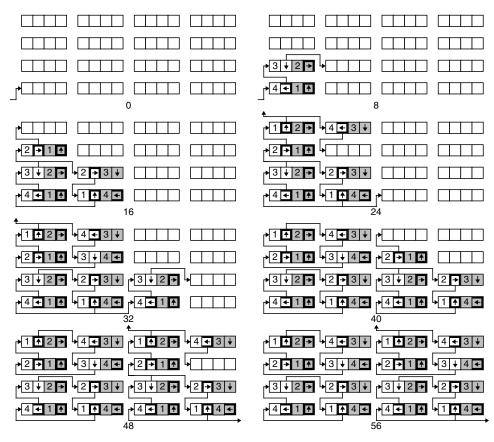

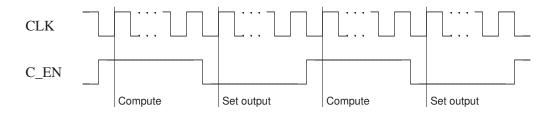

In our artificial organism, any cell CELL[X,Y] continuously computes its coordinate X by incrementing the coordinate WX of its neighbor immediately to the west. Likewise, it continuously computes its coordinate Y by incrementing the coordinate SX of its neighbor immediately to the south. At startup, the first cell, at the bottom left of the organism, is arbitrarily defined as having the coordinates X,Y=1,1, and holds the one and only copy of the operative genome OG. After time t1, the genome of the zygote (*mother* cell) is copied into the neighboring (*daughter*) cells to the east (CELL[2,1]) and to the north (CELL[1,2]). This process of cellular division continues until the six cells of the organism are completely programmed (in our example, the farthest cell is programmed after time t3).

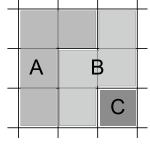

**The self-replication of organisms** The *self-replication* or cloning of the organism, i.e., the production of an exact copy of the original, can be performed if empty cells exist on the silicon circuit (at least six in our organism example) and if the calculation

Figure 2.19: Cellular differentiation of the organism with the operative genome and its expressed gene depending on the coordinates.

of the coordinates produces a cycle  $X = 1 \rightarrow 2 \rightarrow 3 \rightarrow 1 \dots$  and  $Y = 1 \rightarrow 2 \rightarrow 1 \dots$ in figure 2.20, implying X = (WX + 1) modulo 3 and Y = (SY + 1) modulo 2.

When both conditions are present, a copy of the *mother* organism will be produced and one or many *daughter* organisms will populate the IC silicon surface.

Figure 2.20: Self-replication of a six-cell organism in a limited homogeneous array of  $6 \times 4$  cells (situation after 5 cellular divisions).

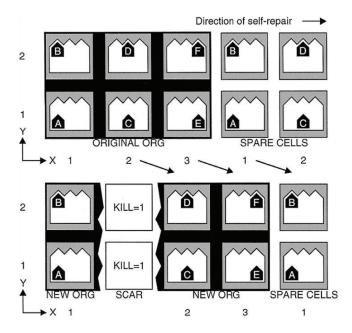

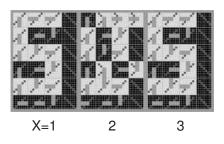

**The self-repair of organisms** In order to implement the *self-repair* of the organism, two columns of spare cells have been added to the right of the original organism (Fig. 2.21). The existence of a fault is detected by a KILL signal, which is produced in each cell by a built-in self-test mechanism. The state KILL=1 identifies the faulty cell,

and the entire column to which the faulty cell belongs is considered faulty and is deactivated (column X=2 in figure. 2.21). All the functions (X coordinate and gene) of the cells at the right of the column X=1 are shifted by one column to the right. Obviously, this process requires as many spare columns to the right of the array as there are faulty cells or columns to repair (two spare columns, tolerating two successive faulty cells, in the example of figure. 2.21). It also implies that the cell needs to be able to bypass the faulty column and to divert to the right all the required signals (such as the operative genome and the coordinate, as well as the data buses).

Figure 2.21: Self-repair of a 6-cell organism with four spare cells and a faulty column.

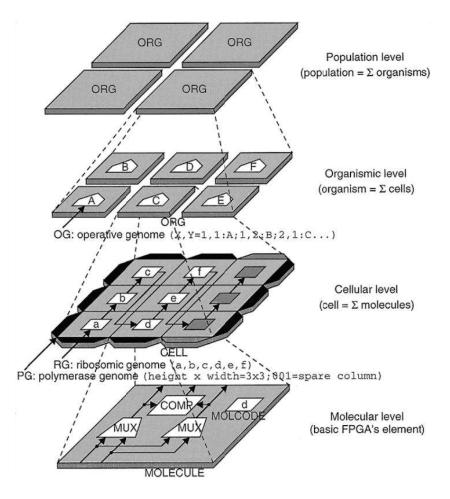

**The Embryonics Landscape** In each cell of every living being, the genome is translated sequentially by a chemical processor, the *ribosome*, to create the proteins needed for the organism's survival. The ribosome itself consists of molecules, whose description is an important part of the genome.

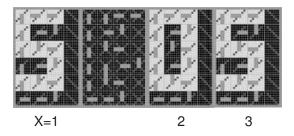

In the Embryonics project each cell is a small processor that sequentially executes the instructions of the artificial genome, the operative genome OG.

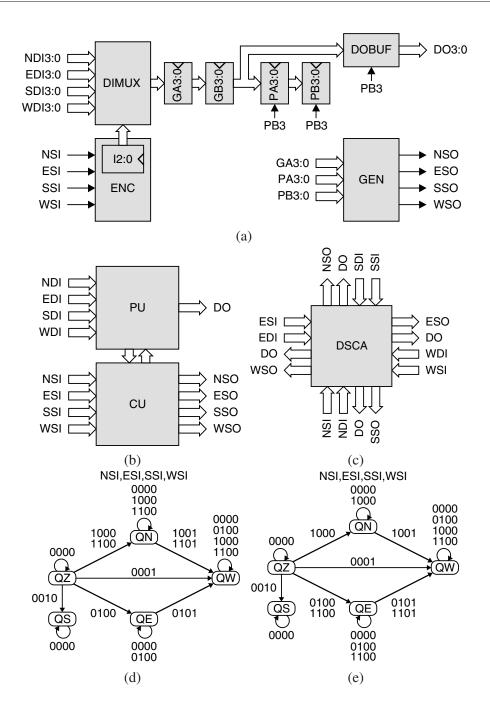

The need to realize organisms of varying degrees of complexity has led us to design an artificial cell characterized by a flexible architecture, that is itself configurable. The Embryonics project could therefore be implemented using previously described FPGA components. Each element of this FPGA (consisting essentially of a buffer and a multiplexer associated with a programmable connection network) is then equivalent to a molecule, and an appropriate number of these artificial molecules allows the creation of application specific processors, i.e. cells.

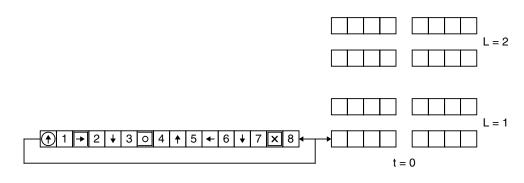

As a result of this new definition, the final architecture of the Embryonics project is based on the following four hierarchical levels of organization, described from the bottom up (Fig. 2.22):

Figure 2.22: The Embryonics landscape: a four level hierarchy.

- The basic primitive of the system is the molecule, the FPGA element, consisting essentially of a buffer and a multiplexer associated with a programmable connection network. The multiplexer is duplicated to allow the detection of faults. The logic function of each molecule is defined by its molecular code or MOL-CODE.

- A cell is made up of a finite set of molecules: essentially a processor with the associated memory. In a first programming step of the FPGA, the *polymerase genome* PG defines the topology of the cell, that is, its width, height, and the presence and positions of columns of spare molecules. In a second step, the *ribosomic genome* RG defines the logic function of each molecule by assigning its molecular code or MOLCODE.

- An organism, an application specific multiprocessor system is made up of a finite set of cells. In a third and last programming step, the operative genome OG is copied into the memory of each cell to define the particular application executed by the organism, for example the electronic watch, the random number generator,...

• The organism can itself self-replicate, giving rise to a *population* of identical organisms, the highest level of our hierarchy.

Since fault-tolerance is a recurrent topic in the Very-Large-Scale Integration (VLSI) industrial world [70, 29], the Embryonics project provided an illustration of the use of bio-inspiration to solve a specific problem. Even if the results of this project are not currently used in the industry as, for example, inside FPGA's architectures, the Embryonics project is a perfect example of an ontogenetic hardware [117] whose results can stimulate new kinds of research and future applications [129, 22, 77].

# 2.4 Towards cellular machines

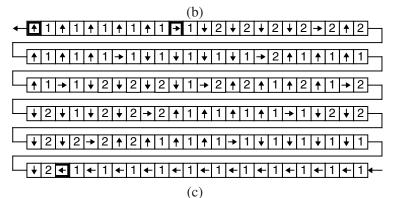

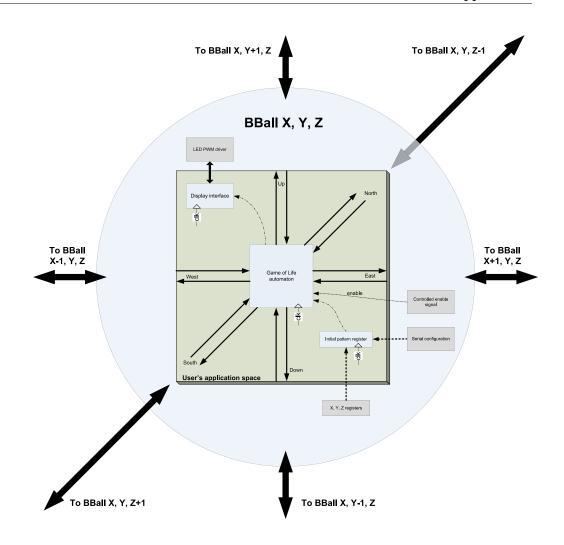

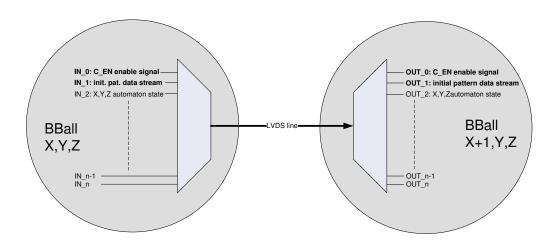

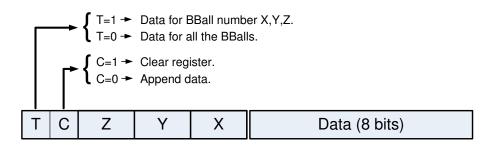

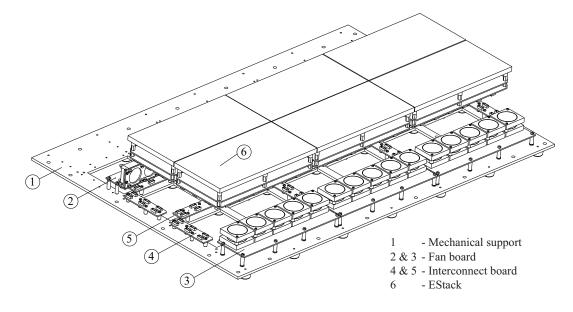

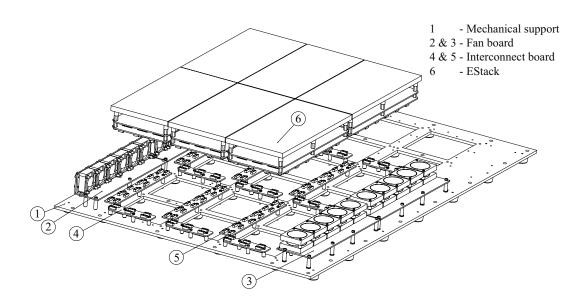

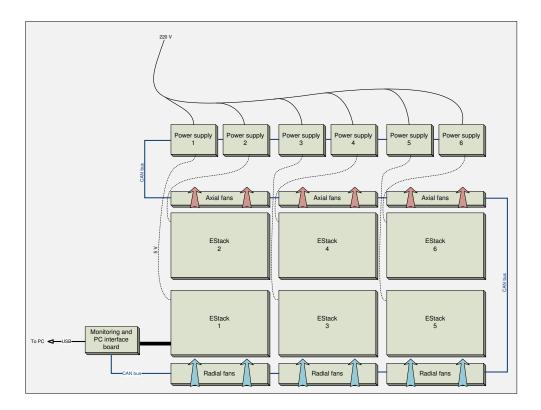

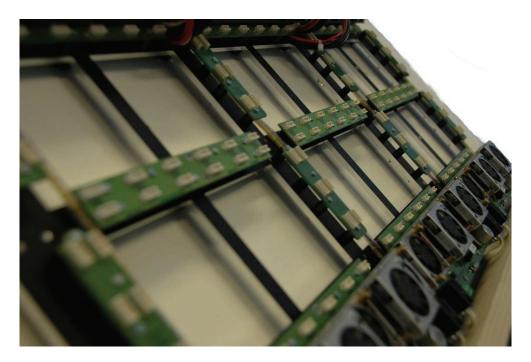

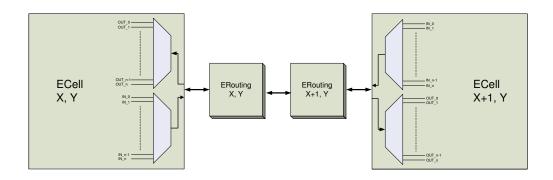

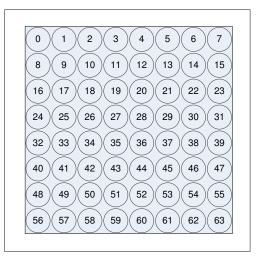

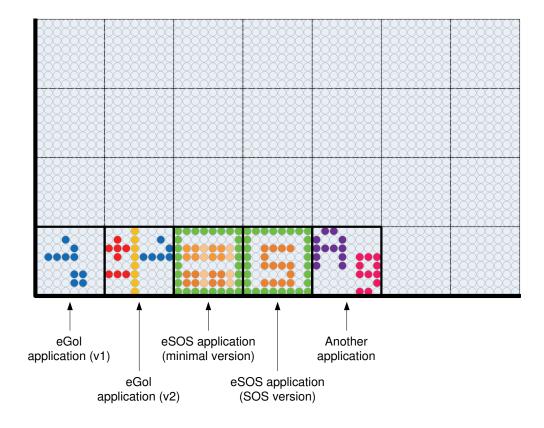

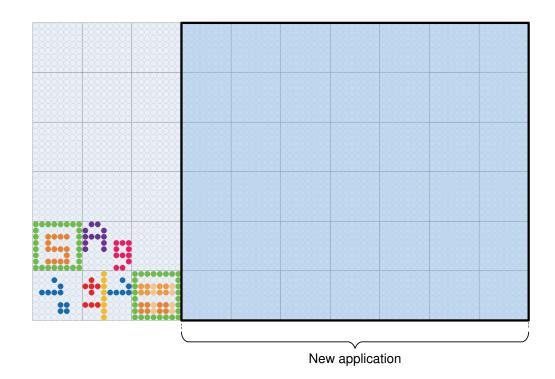

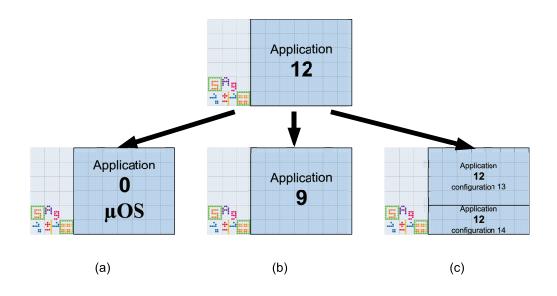

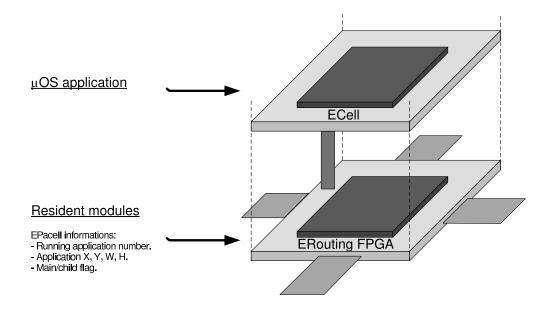

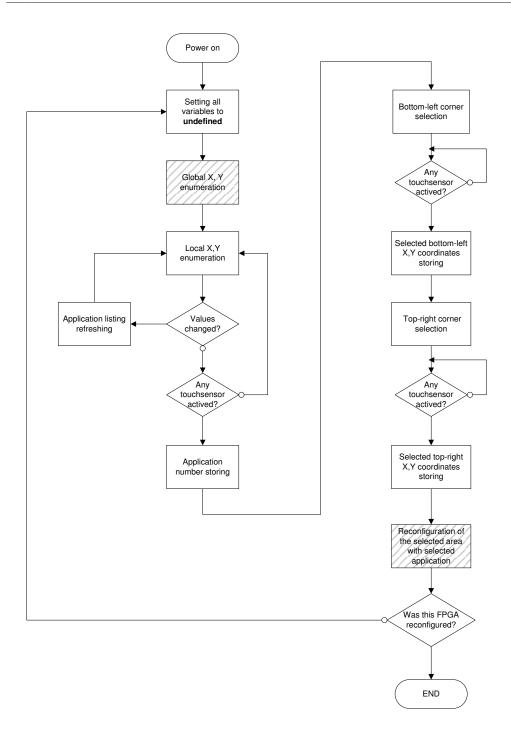

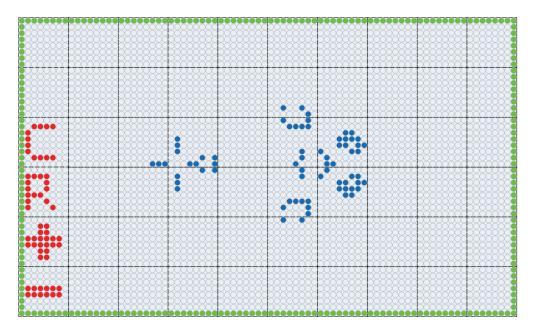

In the space of a few decades, computers have produced a revolution in the industrial domain. From a small number of machines and only few researchers in the computer domain in the 1960's, computing has developed to the extent that millions of people now own a PC and several microprocessors embedded in everyday tools like watches, music players, automobiles... At the same time, the number of researchers around the world working in the computer sciences area has to be one of the most rapidly expanding communities. In a few decades, the CMOS silicon technology has been invented and has practically reached its apogee. Substitutes, like nanoelectronic components, or the quantum computer will soon be a reality.