# HYBRID CONTINUOUS-DISCRETE-TIME MULTI-BIT DELTA-SIGMA A/D CONVERTERS WITH AUTO-RANGING ALGORITHM

### THÈSE Nº 3912 (2008)

PRÉSENTÉE LE 22 FÉVRIER 2008

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

Laboratoire d'électronique générale 1

SECTION DE GÉNIE ÉLECTRIQUE ET ÉLECTRONIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

# Sergio PESENTI

ingénieur en microtechnique diplômé EPF et de nationalités italienne et suisse, originaire de Corsier-sur-Vevey (VD)

acceptée sur proposition du jury:

Prof. J. R. Mosig, président du jury Prof. M. Kayal , directeur de thèse P. Clement, rapporteur Prof. W. Redman-White, rapporteur Prof. J.-Ph. Thiran, rapporteur

Je dédie cette thèse à ma tendre et merveilleuse épouse, Francesca.

# Remerciements

Je souhaiterais avant tout remercier Maher Kayal et Patrick Clément pour m'avoir donné l'opportunité de travailler sur ce projet de thèse et, plus particulièrement, pour m'avoir soutenu et encouragé dans les moments les plus difficiles. Leur confiance m'a permis de donner le meilleur de moi-même dans des conditions parfois défavorables. Je tiens à leur exprimer toute ma reconnaissance quant à leurs efforts de titan - le plus souvent cachés et silencieux - pour faire aboutir ce projet. Leurs compétences techniques ainsi que leurs qualités humaines font de Maher et de Patrick des personnes d'exception.

Je remercie très chaleureusement toutes les personnes avec qui j'ai partagé le bureau 331 du Laboratoire d'Electronique Générale pendant près de cinq longues années:

Danica Stefanovic, avec qui j'ai étroitement collaboré et avec laquelle je continue à travailler à ce jour. Brillante, exigeante et passionnée, elle a su apporter l'optimisme quant tout me semblait converger vers un inéluctable désastre.

Louis Harik, qui a également contribué à la réalisation de ce travail. Il est pour moi un modèle de patience et de modestie.

Nicolas Schlumpf et Cédric Bassin, mes premiers collègues de bureau. Ils excellent dans l'électronique autant que dans l'art de l'humour, deux disciplines indispensables dans notre métier.

Jari Curty et Patrice Beaud, visiteurs inconditionnels du bureau. Leurs connaissances techniques et philosophiques n'ont cessé de m'impressionner, autant que leur maîtrise de l'outil informatique.

Mes remerciements s'adressent aussi aux incontournables piliers du laboratoire que sont **Joseph Guzzardi**, **Isabelle Buzzi**, **Marie Halm** et **Danielle Gallay**. Je veux également exprimer une immense reconnaissance à tous mes autres amis et collègues. Je m'estime heureux d'avoir croisé sur mon chemin autant de personnes formidables qui, avec leurs

paroles d'encouragement et de soutien, m'ont fait oublier les personnes qui sont leur exact opposé.

Pour terminer, j'aimerais exprimer ma plus profonde gratitude à mes parents, **Margherita** et **Daniele Pesenti**, pour leur confiance en moi, sans compromis et sans limites, et à mon épouse **Francesca Catalano** qui, à elle seule, donne un sens à tout ce que j'accomplis.

# **Abstract**

In wireless portable applications, a large part of the signal processing is performed in the digital domain. Digital circuits show many advantages. The power consumption and fabrication costs are low even for high levels of complexity. A well established and highly automated design flow allows one to benefit from the constant progress in CMOS technologies. Moreover, digital circuits offer robust and programmable signal processing means and need no external components. Hence, the trend in consumer electronics is to further reduce the part of analog signal processing in the receiver chain of wireless transceivers. Consequently, analog-to-digital converters with higher resolutions and bandwidths are constantly required. The ultimate goal is the direct digitization of radio frequency signals, where the conversion would be performed immediately after the front -end amplifier.

$\Delta\Sigma$ -modulation-based converters have proved to be the most suitable to achieve the required performance. Switched-capacitor implementations have been widely used over the last two decades. However, recent publications and books have shown that continuous-time architectures can achieve the same performance with lower power consumption. Most designs found throughout the literature use a single- or few-bit internal quantizer with a high-order modulation. As a result, in order to achieve the resolutions and bandwidths required today, the sampling frequency must exceed 100MHz. This approach leads to non-negligible power consumption in the clock generation. Moreover, the presence of such fast squared signals is not suitable for a system-on-chip comprising radio frequency receivers.

In this thesis we propose a low-power strategy relying on a large number of internal levels rather than on a high sampling frequency or modulation order. Besides, a hybrid continuous-discrete-time approach is used to take advantage of the accuracy of switched-capacitor circuits and the low power consumption of continuous-time implementation. The sensitivity to clock jitter brought about by the continuous-time stage is reduced by the use of a large number of levels. An auto-ranging algorithm is de-

veloped in this thesis to overcome the limitation of a large-size quantizer under low-voltage supply. Finally, the strategy is applied to a design example addressing typical specifications for a Bluetooth receiver with direct conversion.

**Keywords:** analog-to-digital conversion, delta-sigma modulation, multibit, quantization noise, hybrid architecture, continuous-time, discrete-time, full clock-cycle sampling, double-sampling, digital calibration, autoranging algorithm, tracking quantizer, dynamic element matching, spectral shaping, tree-structured encoder, segmented DAC, Bluetooth, WCDMA, GSM, EDGE, comparator, CMOS technology, fully-differential amplifier, transconductance amplifier.

# Résumé

Dans les applications portables de communication sans-fil, une grande partie du traitement du signal est exécutée de manière numérique. Les circuits numériques présentent plusieurs avantages. Même pour un haut degré de complexité, la consommation d'énergie ainsi que les coûts de fabrication sont faibles. Le processus de conception est bien établi avec un haut degré d'automatisation permettant de tirer profit du progrès constant des technologies CMOS. En outre, les circuits numériques offrent un traitement du signal robuste et programmable et ne nécessitent aucun composant externe. La tendance pour le marché grand public est donc de réduire encore plus la partie analogique dans les chaînes de réception de systèmes sans fil. En conséquence, des convertisseurs avec des résolutions et des bandes passantes toujours plus élevées sont nécessaires. Le but ultime est la numérisation directe du signal radio, où la conversion serait faite après amplification du signal fournit par l'antenne.

Les convertisseurs basés sur la modulation  $\Delta\Sigma$ se trouvent être les plus appropriés pour atteindre les performances requises. Les implémentations à capacités commutées ont été très utilisées ces deux dernières décennies. Cependant, de récentes publications ont montré que les architectures à temps continu pouvaient atteindre les mêmes performances avec une consommation réduite. La plupart des réalisations présentées dans les publications font usage d'un quantificateur interne à deux ou à un nombre restreint de niveaux et une modulation d'ordre élevé. Par conséquent, pour atteindre les résolutions et bandes passantes demandées de nos jours, la fréquence d'échantillonnage dépasse la centaine de mégahertz. Cette approche amène à une consommation non négligeable du générateur d'horloge. En outre, la présence de signaux carrés d'une telle rapidité est à éviter sur un système intégré de grande taille qui comprend des récepteurs radio.

Dans cette thèse, nous proposons une stratégie à faible consommation qui compte sur un grand nombre de niveaux internes plutôt que sur une haute fréquence d'échantillonnage et un ordre de modulation élevé. De plus, une approche hybride à temps continu et discret est employée

afin de profiter de la précision des circuits à capacités commutées et de la faible consommation des circuits à temps continu. La sensibilité à la gigue du signal d'horloge, introduite par le traitement à temps continu, se voit diminuée par l'utilisation d'un nombre élevé de niveaux internes. Un algorithme d'ajustement automatique d'amplitude est développé dans cette thèse afin de gommer l'inconvénient d'un quantificateur de grande taille travaillant sous basse tension d'alimentation. Pour terminer, la stratégie est appliquée à un exemple de conception visant les spécifications typiques d'un récepteur Bluetooth à conversion directe.

**Mots-clés:** conversion analogique-numérique, modulation delta-sigma, multibit, bruit de quantification, architecture hybride, temps continu, temps discret, échantillonnage sur deux demi périodes, double échantillonnage, calibration numérique, algorithme d'ajustement automatique d'amplitude, quantificateur, appariement dynamique, mise en forme spectrale, encodeur à structure en arbre, CAN segmenté, Bluetooth, WCDMA, GSM, EDGE, comparateur, technologie CMOS, amplificateur différentiel symétrique, amplificateur à transconductance.

# **Contents**

| C | onte | nts         |                               | хi |  |  |  |

|---|------|-------------|-------------------------------|----|--|--|--|

| 1 | Intr | ntroduction |                               |    |  |  |  |

|   | 1.1  | Motiv       | ation                         | 1  |  |  |  |

|   | 1.2  | Intent      | ion of the this work          | 2  |  |  |  |

|   | 1.3  | Hybrid      | d multi-bit modulators        | 2  |  |  |  |

|   | 1.4  | Orgar       | nization of the dissertation  | 3  |  |  |  |

| 2 | Del  | ta-Sig      | gma ADC from the ground       | 5  |  |  |  |

|   | 2.1  | From        | analog to digital             | 5  |  |  |  |

|   |      | 2.1.1       | Sampling                      | 5  |  |  |  |

|   |      | 2.1.2       | Quantization                  | 8  |  |  |  |

|   |      | 2.1.3       | Over-sampling                 | 12 |  |  |  |

|   |      | 2.1.4       | Spectral shaping              | 14 |  |  |  |

|   |      | 2.1.5       | Digital decimation            | 19 |  |  |  |

|   | 2.2  | Perfo       | rmance calculations           | 23 |  |  |  |

|   |      | 2.2.1       | Linear model                  | 23 |  |  |  |

|   |      | 2.2.2       | Modulator general description | 24 |  |  |  |

|   |      | 2.2.3       | Dynamic range                 | 25 |  |  |  |

|   |      | 2.2.4       | Resolution                    | 27 |  |  |  |

|   |      | 2.2.5       | Simulations                   | 31 |  |  |  |

|   |      | 2.2.6       | Aggressive pole placement     | 34 |  |  |  |

|   |      | 2.2.7       | Optimal zero placement        | 36 |  |  |  |

|   | 2.3  | Circui      | it imperfections              | 38 |  |  |  |

|   |      | 2.3.1       | Removal of quantization noise | 38 |  |  |  |

|   |     | 2.3.2  | Circuit noise                                       | 39 |

|---|-----|--------|-----------------------------------------------------|----|

|   |     | 2.3.3  | Clock jitter                                        | 40 |

|   |     | 2.3.4  | Component mismatch                                  | 41 |

|   |     | 2.3.5  | Harmonic distortion                                 | 42 |

|   | 2.4 | Archit | ecture classification                               | 44 |

|   |     | 2.4.1  | Single- and multi-bit                               | 44 |

|   |     | 2.4.2  | Low-, high- and band-pass                           | 46 |

|   |     | 2.4.3  | Single and multi-feedback path                      | 46 |

|   |     | 2.4.4  | Single and multi-stage                              | 48 |

|   | 2.5 | Concl  | usions                                              | 50 |

| 3 | Lov | v-pow  | ver strategy                                        | 51 |

|   | 3.1 | Strate | gy outline                                          | 51 |

|   |     | 3.1.1  | Continuous-time implementations                     | 51 |

|   |     | 3.1.2  | Multi-bit feedback                                  | 52 |

|   |     | 3.1.3  | Optimal DEM segmentation                            | 53 |

|   |     | 3.1.4  | Auto-ranging algorithms                             | 55 |

|   |     | 3.1.5  | Hybrid architecture                                 | 56 |

|   |     | 3.1.6  | Continuous-to-discrete domain interface             | 57 |

|   |     | 3.1.7  | Summary                                             | 58 |

|   | 3.2 | Anti-a | liasing property                                    | 60 |

|   |     | 3.2.1  | Signal processing of the continuous-time modulator  | 60 |

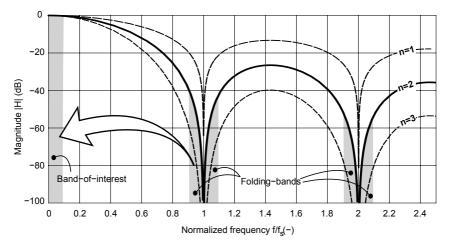

|   |     | 3.2.2  | Input signal spectrum folding                       | 62 |

|   | 3.3 | Clock  | jitter issue                                        | 64 |

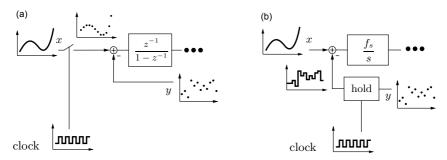

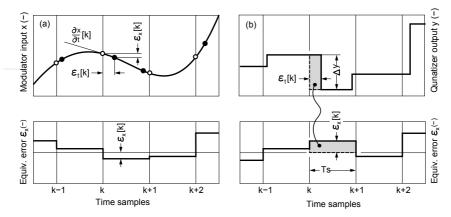

|   |     | 3.3.1  | Discrete- and continuous-time mechanisms            | 64 |

|   |     | 3.3.2  | Analytical expression of the jitter transfer factor | 68 |

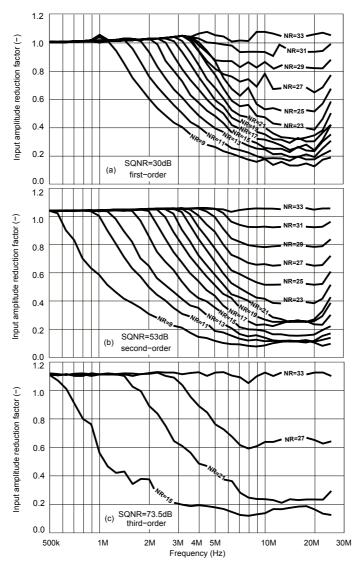

|   |     | 3.3.3  | Resolution degradation                              | 71 |

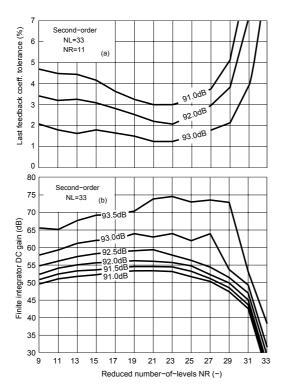

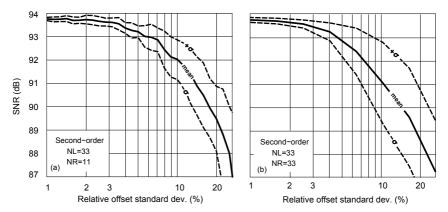

|   | 3.4 | Accur  | acy of coefficients                                 | 76 |

|   | 3.5 | Samp   | ling capacitor mismatch                             | 79 |

|   | 3.6 | Concl  | usions                                              | 84 |

| CONTENTS | xi |  |  |

|----------|----|--|--|

|          |    |  |  |

| 4.1   |        | vations                                   |

|-------|--------|-------------------------------------------|

|       | 4.1.1  | Slow and fast components                  |

|       | 4.1.2  | Exploiting the phenomenon                 |

|       | 4.1.3  | Auto-ranging technique                    |

| 4.2   | Princi | ple in detail                             |

|       | 4.2.1  | Last integrator reuse for signal shifting |

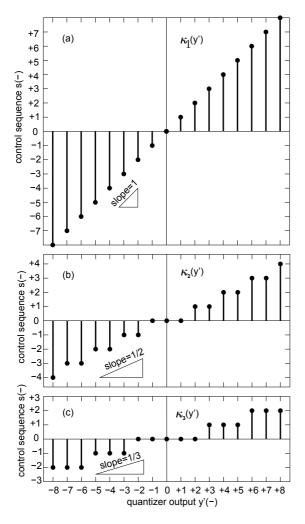

|       | 4.2.2  | Control function                          |

|       | 4.2.3  | Implementation constraints                |

|       | 4.2.4  | Number of step changes                    |

| 4.3   | Realiz | ation and limitations                     |

|       | 4.3.1  | Simulations                               |

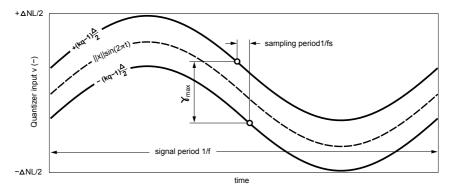

|       | 4.3.2  | Input signal constraints                  |

|       | 4.3.3  | Sensitivity to circuit imperfections      |

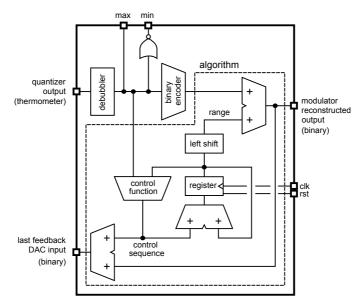

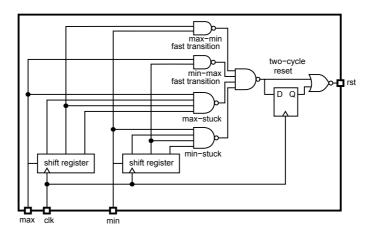

|       | 4.3.4  | Hardware implementation                   |

| 4.4   | Optim  | ization                                   |

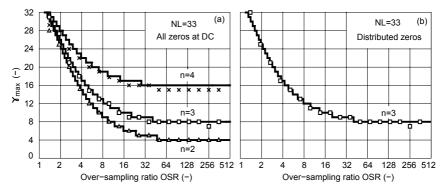

|       | 4.4.1  | Reduced number of quantization levels     |

|       | 4.4.2  | Reduction factor                          |

|       | 4.4.3  | Extendability                             |

| 4.5   | Concl  | usions                                    |

| 5 Mis | matcl  | n shaping optimizations                   |

| 5.1   | Dynar  | nic element matching                      |

| 5.2   | Tree-s | structured architectures                  |

|       | 5.2.1  | Spectral shaping                          |

|       | 5.2.2  | Higher-order spectral shaping             |

| 5.3   | Optim  | ization                                   |

|       | 5.3.1  | DAC segmentation                          |

|       | 5.3.2  | Synthesis automation                      |

|       | 5.3.3  | Standard segmentation                     |

|       | 3.0.0  |                                           |

| 6 | Des        | sign e  | xample                                      | 133 |

|---|------------|---------|---------------------------------------------|-----|

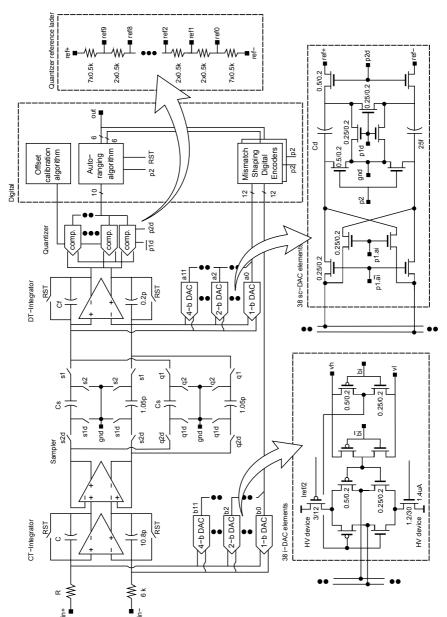

|   | 6.1        | Modul   | lator design                                | 133 |

|   |            | 6.1.1   | Targeted specifications and topology choice | 133 |

|   |            | 6.1.2   | Circuit description                         | 134 |

|   | 6.2        | Syste   | m Design                                    | 137 |

|   |            | 6.2.1   | Signal processing of the circuit            | 137 |

|   |            | 6.2.2   | Design equations                            | 139 |

|   |            | 6.2.3   | Design procedure                            | 142 |

|   |            | 6.2.4   | Noise considerations                        | 144 |

|   | 6.3        | Desig   | n of the amplifiers                         | 147 |

|   |            | 6.3.1   | Behavioral models                           | 147 |

|   |            | 6.3.2   | Continuous-time amplifier                   | 148 |

|   |            | 6.3.3   | Switched capacitor devices                  | 150 |

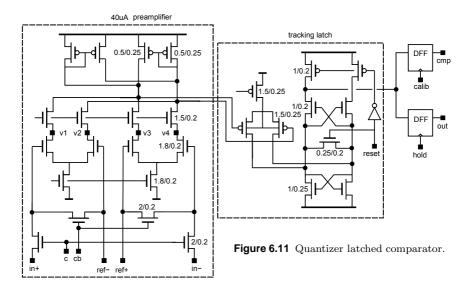

|   | 6.4        | Quant   | izer design                                 | 154 |

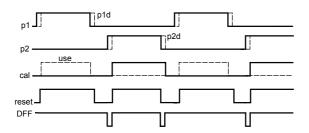

|   |            | 6.4.1   | Comparator                                  | 154 |

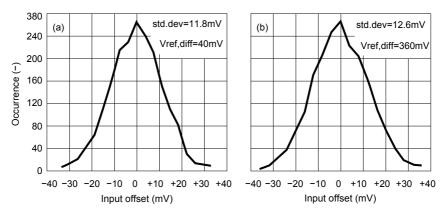

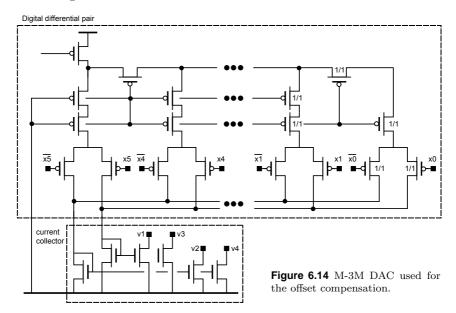

|   |            | 6.4.2   | Offset compensation circuit                 | 156 |

|   |            | 6.4.3   | Residual offset                             | 158 |

|   | 6.5        | Final o | circuit                                     | 161 |

|   |            | 6.5.1   | Benchmarking                                | 164 |

|   | 6.6        | Concl   | usions                                      | 167 |

| _ | 0          |         |                                             | 400 |

| 7 |            | nclusi  |                                             | 169 |

|   | 7.1        |         | s outlook                                   |     |

|   | 7.2        |         | contributions                               |     |

|   | 7.3        | Future  | e perspectives                              | 172 |

| Α | Mat        | thema   | tical definitions and proofs                | 175 |

|   | <b>A.1</b> | Defini  | tion of the norms                           | 175 |

|   | A.2        | The 1-  | norm of a z transfer-function               | 176 |

|   | A.3        | The 2-  | norm of a z transfer-function               | 177 |

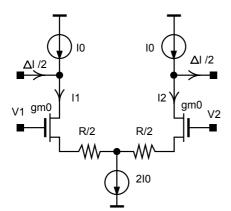

|   | A.4        | Differe | ential pair model                           | 178 |

| CONTENTS | xv |

|----------|----|

|          |    |

| В   | Veri  | log-A codes                             | 183 |

|-----|-------|-----------------------------------------|-----|

|     | B.1   | Transconductance behavioral model       | 183 |

| С   | MA    | ΓHEMATICA codes                         | 185 |

|     | C.1   | Synthesis functions                     | 185 |

|     | C.2   | Extraction and display of the solutions | 186 |

| D   | MA    | TLAB codes                              | 189 |

|     | D.1   | Modulators with auto-ranging            | 189 |

|     | D.2   | Mismatch shaping encoder                | 193 |

| Bi  | blio  | graphy                                  | 195 |

| Lis | st of | Figures                                 | 203 |

| Lis | st of | Tables                                  | 213 |

| Lis | st of | publications                            | 217 |

# Chapter 1 Introduction

#### 1.1 Motivation

In wireless portable applications, a large part of the signal processing is performed in the digital domain. Digital circuits show many advantages. The power consumption and fabrication costs are low even for high levels of complexity. A well established and highly automated design flow allows one to benefit from the constant progress in CMOS technologies. Moreover, digital circuits offer robust and programmable signal processing means and need no external components. Hence, the trend in consumer electronics is to further reduce the part of analog signal processing in the receiver chain of wireless transceivers. Consequently, Analog-to-Digital Converters (ADC) with higher resolutions and bandwidths are constantly required. According to [Raz96], the ultimate goal is the direct digitization of Radio Frequency (RF) signals, where the conversion would be performed immediately after the front-end Low-Noise Amplifier (LNA).

$\Delta\Sigma$ -modulation-based converters have proved to be the most suitable to achieve the required performance [Jes01, GWT02]. Discrete-Time (DT) Switched-Capacitor (SC) implementations have been widely used over the last two decades. However, recent publications [Kap03, YS04, AL02] and books [CS00, BH01, KvR06, OG06, Sho95, Yan02] have shown that Continuous-Time (CT) architectures can achieve the same performance with lower power consumption. Besides, CT modulators present an inherent anti-aliasing property, relaxing the specifications of the analog low pass filter placed in front of the ADC. Most designs found throughout the literature use a single- or few-bit internal quantizer with a high-order modulation. As a result, in order to achieve the resolutions and bandwidths

required today, the sampling frequency must exceed 100MHz. This approach leads to non-negligible power consumption in the Phase-Locked Loop (PLL) generating the clock signals. Moreover, the presence of such fast squared signals is not suitable for a System-on-Chip (SoC) comprising RF receivers.

#### 1.2 Intention of the this work

The objective of this thesis is to propose a low-power strategy relying on a large internal Number-of-Levels (NL) rather than on a high sampling frequency  $(f_s)$  or modulation order (n). Besides, a hybrid continuous-discrete-time approach is used to take advantage of the accuracy of SC circuits and the low power consumption of continuous-time implementations. The intention of this work is to provide designers with an optimization methodology.

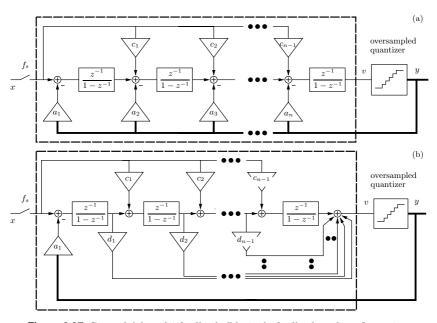

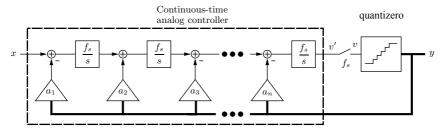

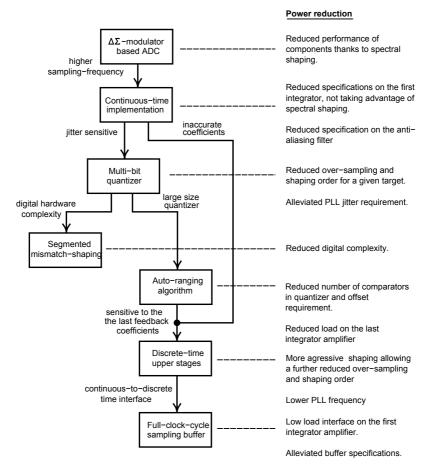

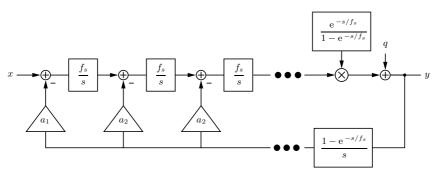

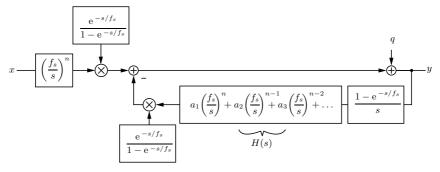

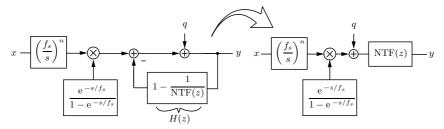

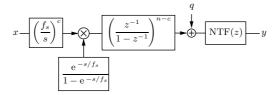

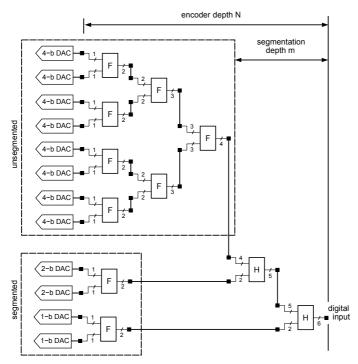

# 1.3 Hybrid multi-bit modulators

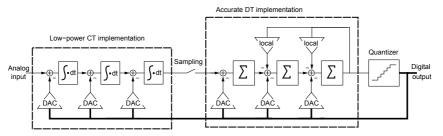

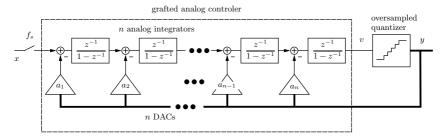

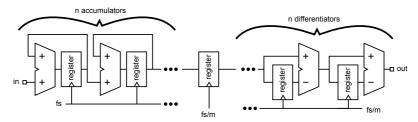

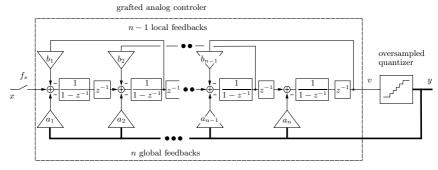

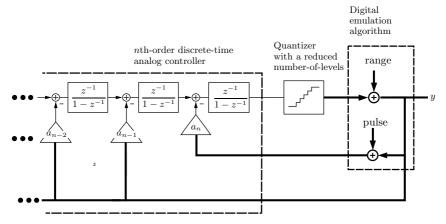

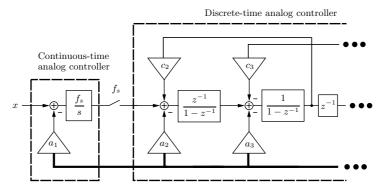

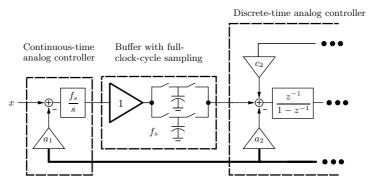

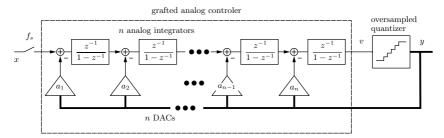

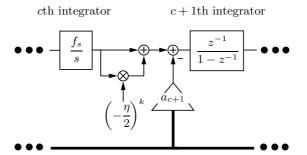

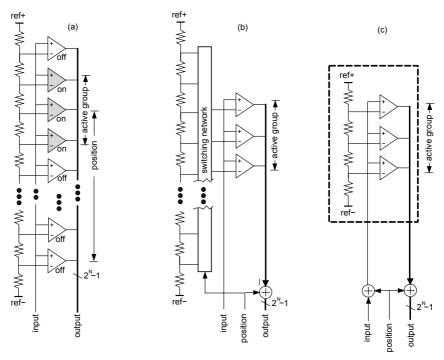

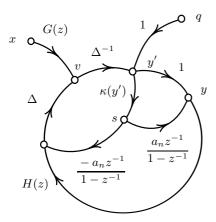

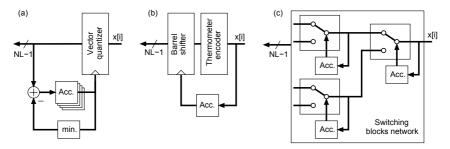

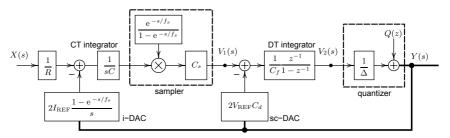

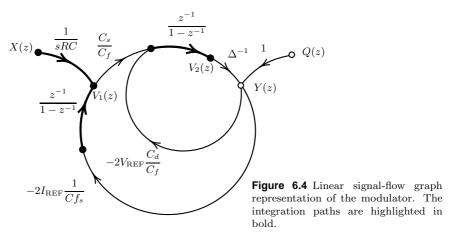

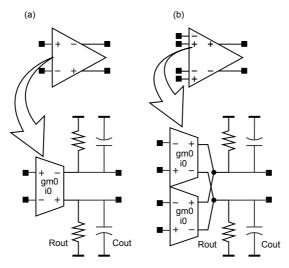

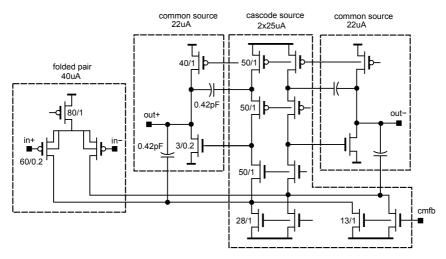

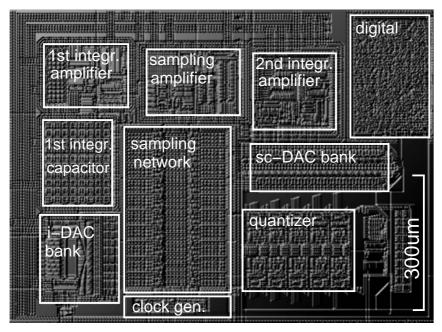

In the general case, a  $\Delta\Sigma$  modulator consists of an NL-level quantizer and an nth-order analog filter providing spectral shaping of the quantization noise. The analog filter is set up with n successive integration stages. From the second to the last one, each successive stage takes advantage of an additional order of the spectral shaping. As a consequence, the power consumption of the modulator is generally dominated by its first stage. Hence, having the first stage as a CT integrator enables a significant amount of power saving. On the other hand, keeping the upper stages as DT integrators allows one to take advantage of the accuracy of SC circuits coefficients. The modulator still takes partial advantage of inherent antialiasing filtering. Figure 1.1 shows an illustrative example of such a hybrid architecture.

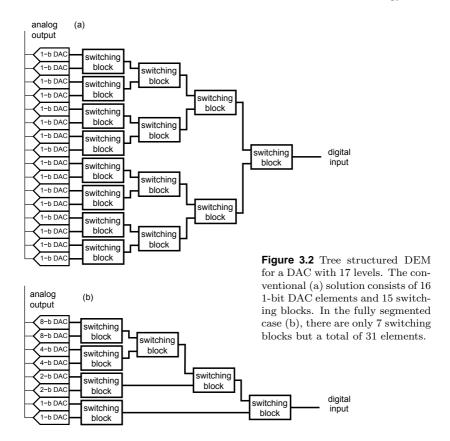

Multi-bit hybrid architectures were proposed by [MCL<sup>+</sup>05, KRSC05] for audio applications and by [RLS<sup>+</sup>03] for communication systems. In this thesis, we suggest of further increasing the number of levels. An auto-ranging algorithm is developed to overcome the limitation of a large-size quantizer with a low voltage supply. The complexity of the Dynamic Element Matching (DEM) is addressed by an appropriate segmentation

Introduction 3

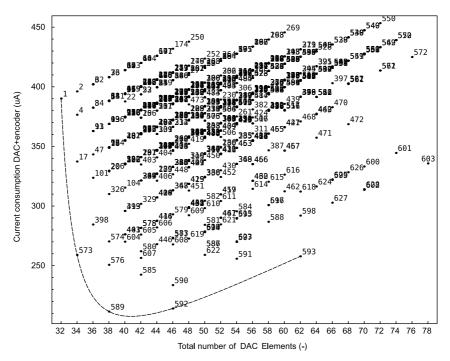

**Figure 1.1** Illustrative example of the hybrid architecture.

of the DACs as proposed by [FSW<sup>+</sup>02, Gal97]. A synthesis algorithm is developed to evaluate all the possible segmentations.

# 1.4 Organization of the dissertation

The thesis starts by a didactic review of the  $\Delta\Sigma$ -modulation signal processing, then presents the low-power strategy and its relevant aspects, and ends with a design example.

Chapter 2 introduces the  $\Delta\Sigma$ modulation for analog-to-digital conversion. The fundamental aspects of the signal processing are covered as well as the methods used for performance estimation. An accurate analytical expression of the expected resolution is derived for the general case of a multi-bit single-stage modulator. The impact of the most relevant circuit imperfections is shown. The chapter ends with an overview of the well-known architectures and variants commonly used nowadays.

**Chapter 3** proposes the low-power strategy which consists of an optimal combination of different techniques. Relevant aspects of the techniques used are covered. The sensitivity to clock jitter is studied in detail and used as a main optimization criterion.

**Chapter 4** explains the principle of the auto-ranging algorithm. The main limitations of the technique are analyzed, taking into account the implementation constraints. An analytical expression of the efficiency of the

algorithm is developed and used for optimization. The extendability to different applications is demonstrated.

**Chapter 5** discusses the optimization of the DEM. The segmented treestructured architecture is introduced. Different shaping algorithms are provided as well as a synthesis method. An analytical expression of the power consumption is given.

**Chapter 6** presents a design example addressing the specifications for a BLUETOOTH receiver with direct conversion. The modulator equations are derived, giving a general design procedure. The design of the amplifiers and the quantizer is outlined. The digital calibration of the comparators offset is analyzed. The chapter ends with a comparison with other published works.

**Chapter 7** gives the final conclusions and summarizes the main contributions of the thesis. Suggestions for further development and analyses are made.

# Chapter

2

# **Delta-Sigma ADC from the ground**

The purpose of this chapter is to cover the fundamental aspects of  $\Delta\Sigma$  analog-to-digital conversion. It considers the basics of signal processing up to the main issues known today. It also introduces the definitions commonly used and makes the link between the analytical models and the reality of implementation. The first section enables the non-expert reader to rapidly understand how a low-resolution quantizer can become a high-resolution converter by subsequently over-sampling, grafting a control system and filtering. The detailed calculations of the expected performance are given in the second section. The third section introduces the main circuit imperfections that would potentially reduce the expected performances. Finally, the last section gives a broad view of the most classic architectures known today.

# 2.1 From analog to digital

## 2.1.1 Sampling

The first task in analog-to-digital conversion consists in providing samples of the analog signal equally apart in time by the sampling period  $T_s$ . This process of going from the continuous-time to the discrete-time domain is called sampling. We define the sampling frequency as  $f_s = 1/T_s$ . After sampling, there is no any signal faster than half of the sampling frequency, also referred to as the Nyquist frequency.

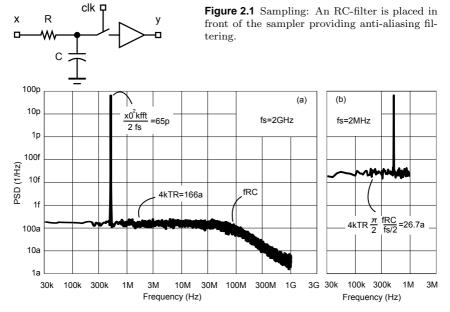

Figure 2.1 shows a low-pass filter followed by an ideal sampler. Code 2.1 and 2.2 simulate the sampling of a single-tone and the additional filtered

resistor white Gaussian noise, whose Power Spectral Density (PSD) is given by:

$$\mathscr{P}_N(f) = 4kTR. (2.1)$$

As shown in Figure 2.2(a), when the noise is sampled at a frequency higher than the filter cut-off frequency  $f_{RC}$ , no aliasing occurs and the output spectrum contains the tone and the filtered thermal noise. In contrast, Figure 2.2(b) shows that if the bandwidth of the noise is higher than the Nyquist rate, the noise unavoidably folds back and its level increases. As treated in detail in many textbooks [Raz01, JM97], the noise floor is multiplied by  $\pi/2$  and the ratio between the cut-off and Nyquist frequencies.

$$\mathscr{P}_N(f) = 4kTR \cdot \frac{\pi}{2} \cdot \frac{2f_{RC}}{f_s} \,. \tag{2.2}$$

Figure 2.2 Sampling process: Simulations performed with 50 average points and  $2^{18}$  FFT bins. A 1mV tone at 500kHz together with a 10kΩ resistor thermal noise are sampled at a frequency of 2GHz (a) and 2MHz (b). The filter cut-off is set at 100MHz.

**Code 2.1** MATLAB code for the sampling process: **avr** and **kfft** control the averaging number and the FFT number of bins. The down-sampling factor is set by **down**, whereas **f0**, **fs** and **fRC** are respectively the tone, sampling and filter cut-off frequencies.

```

avr=50; waste=1024; down=1024;

kfft=2^18;k=kfft*avr+2*waste;

%sim. parameters

f0=500e3;fs=2e9;

%signal/sampling freg.

f0=fs*round(kfft*f0/fs)/(kfft); %integer nbr.of period

fRC=100e6;

%filter cut-off freq.

v0=1.0e-3;

%signal amplitude

%sqrt(4kTR fs/2))

n0=4.07e-4;

noise = n0*randn(k,1);

signal = v0*(sin(2*pi*f0*(1:k)'/fs));

v=signal+noise;

RCfilter=(1-exp(-2*pi*fRC/fs))*exp(-(2*pi*fRC/fs)*(0:2^10)');

v filtered =filter(RCfilter,1,v);

v down =v filtered(1:down:k);

```

Code 2.2 MATLAB for power spectral density esitmation.

```

%%%%% power spectral density of the filtered signal %%%%%%%

y=v_filtered;

psd = zeros(kfft, 1);

for j=0:avr-1

psd=psd+...

abs(fft(y(waste+1+j*kfft:waste+(j+1)*kfft))).^2/kfft/fs*2;

end

psd=psd(1:kfft/2+1)/avr;f=(0:fs/kfft:fs/2);loglog(f,psd);

%%%%% power spectral density of the down-sampled signal %%%%

kfft=kfft/down;fs=fs/down;waste=waste/down;

y=v_down;

psd = zeros(kfft, 1);

for j=0:avr-1

psd=psd+...

abs(fft(y(waste+1+j*kfft:waste+(j+1)*kfft))).^2/kfft/fs*2;

end

psd=psd(1:kfft/2+1)/avr;f=(0:fs/kfft:fs/2);loglog(f,psd);

```

With the circuit described in Figure 2.1 the cut-off is given as  $2\pi RC$ . As a well-known result, commonly referred to as the kT/C-noise, the noise

floor becomes independent of the resistor size:

$$\mathscr{P}_N(f) = \frac{kT}{C} \cdot \frac{2}{f_s} \,. \tag{2.3}$$

All these considerations reveal that the process of sampling itself already degrades the quality of the signal, even before its conversion into a digital representation. Furthermore, it gives good reasons to place an anti-aliasing filter in front of an ADC to avoid the folding of any signal or noise present at frequencies higher than the Nyquist rate

The experiment of Code 2.1 introduces a few important features of spectral estimations. First of all, it is important to appropriately round the number of periods of the tone in the simulation in order to avoid spectral spreading. Secondly, in the presence of random signals, averaging is essential to reveal the continuous shapes hidden by important variations. A power-of-two is suitable choice for the number of samples to avoid an artificial zero padding by the *Fast Fourier Transform* (FFT) algorithm. Finally, in order to provide a representation of the single side-band PSD, the absolute value of the FFT is squared, normalized by the number-of-bins  $k_{\rm FFT}$  and by the sampling frequency [IIO2, HvV99]:

$$PSD[k] = \frac{2|FFT[k]|^2}{f_s k_{FFT}} \quad \forall k \in \{0, \dots, k_{FFT}/2\}.$$

(2.4)

#### 2.1.2 Quantization

The second task of the conversion consists in providing samples with an amplitude rounded to the closest value of a finite set of so-called *levels*. This process of going from the continuous-amplitude to the discrete-amplitude is called *quantization*.

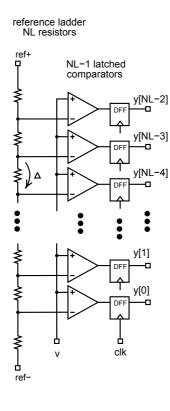

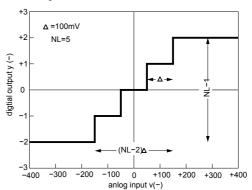

This task is performed by a quantizer, also called flash ADC, which is the core of any analog-to-digital conversion circuit. Figure 2.3 describes a quantizer with NL levels. In some architectures, such as successive approximation, single-bit  $\Delta\Sigma$  or pipeline converters, NL can go down to two, requiring only one comparator.

Figure 2.3 A quantizer with NL levels consists of a bank of (NL-1) comparators, providing a quantization in amplitude, and (NL-1) Data-Flip-Flops (DFF), providing the quantization in time. The (NL-1) voltage thresholds, separated by steps of  $\Delta$ , are usually generated by a resistive ladder with NL resistors. The (NL-1) outputs of the data-flip-flops form an integer number, represented by a thermometer code.

Figure 2.4 Mid-thread 5-level quantizer transfer characteristic described by Equation (2.5). The vertical parts correspond to the voltage thresholds and the horizontal parts to the possible output levels.

Figure 2.4 shows the transfer characteristic from the analog input v to the digital output y, which in all cases can be described by

$$y = \begin{cases} \operatorname{sign}(v)(\operatorname{NL} - 1)/2, & \text{if } |v| \ge \operatorname{NL}\Delta/2, \\ \operatorname{round}(v/\Delta), & \text{if } \operatorname{NL} \text{ is odd}, \\ \operatorname{floor}(v/\Delta) + 1/2, & \text{otherwise}. \end{cases}$$

(2.5)

Whether the Number-of-Levels NL is even or odd, the quantizer has a mid-rise or mid-thread transfer characteristic. NL is often chosen as a power-of-two because the quantizer output can be further encoded in a binary representation with the minimum Number-of-bits N, where  $NL=2^{N}$ .

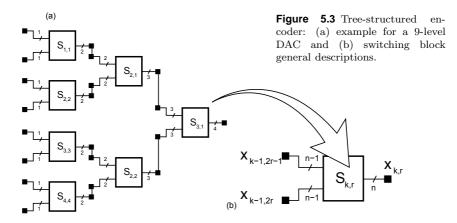

Alternatively, choosing NL as a power-of-two plus one allows encoding in the so-called *extra-LSB* representation, as is necessary for the use of a tree-structured mismatch shaping encoder, as discussed in Chapter 5. In such a case, NL is odd and the number of comparators is even. In this thesis only quantizers with power-of-two plus one levels are considered.

**Code 2.3** MATLAB for the quantization process: The tone amplitude v0 is set at the maximum allowed, namely at half of NL. The quantization error q is extracted to determine its statistical distribution. The power spectral density is evaluated as already described in Code 2.1. For the sake of simplicity, an odd-NL quantizer with steps equal to one is considered.

```

avr=20;kfft=2^11;k=kfft*avr;

%sim. parameters

NL=2^5+1;

%Number-of-Levels

v0=NL/2;

%signal amplitude

f0=200e3;fs=32e6;

%signal/sampling freq.

f0=fs*round(kfft*f0/fs)/(kfft); %integer nbr.of period

v = v0*(sin(2*pi*f0*(1:k)'/fs));

y = zeros(k, 1);

for i=1:k

if (abs(v(i)) >= NL/2)

y(i) = sign(v(i)) * (NL-1)/2;

else

y(i) = round(v(i));

end

end

%quantization noise extraction

q=y-v;

```

**Code 2.4** Additional MATLAB code for dithering: The tone amplitude is reduced by **extra** to prevent over-loading as the necessary dithering amplitude **d0** is quite high

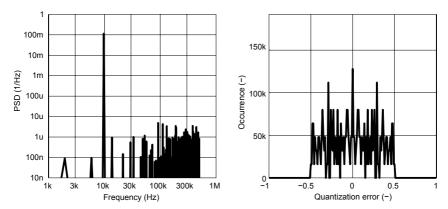

Code 2.3 is a simulation of the quantization process applied to a single tone. The results in Figure 2.5 show an output PSD that is nothing but

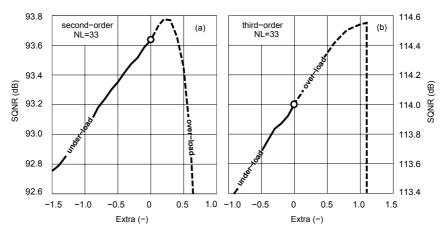

**Figure 2.5** Quantization process: Simulation performed with 2000 averages, NL=33, extra=-1.5, single-tone at 10kHz and sampling frequencies  $f_s$ =1MHz.

Figure 2.6 Dithered quantization: Simulation performed with 2000 averages, NL=33, extra=-1.5, Gaussian dithering of 0.5, single-tone at 10kHz and sampling frequencies  $f_s$ =1MHz.

a sum of harmonics because of the deterministic nature of the quantization process. In the second experiment, with the modification proposed in Code 2.4, a Gaussian *dithering* signal is artificially added at the input and removed at the output. The quantization becomes a random process. According to Figure 2.6, the output PSD is white and the statistical dis-

tribution is uniformly distributed between  $\pm 1/2$ . In real cases, the signal to be converted is quite random and no dithering is usually required.

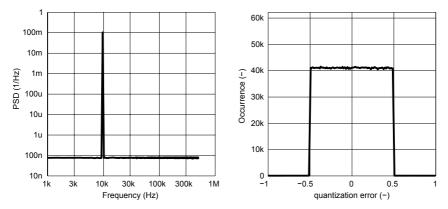

This observation leads to the so-called linear approximation where the highly non-linear behavior of Equation (2.5) is modeled as a gain of  $1/\Delta$ . Any error from that linear characteristic generated by the quantization process is considered an additional random noise. As highlighted in Figure 2.7, this approximation holds as long as the input stays within  $\pm NL\Delta/2$ , namely as long as errors are bounded and random. If we exceed this range, the quantizer overloads and, as shown in Figure 2.8, with a sinusoidal input, harmonic distortion is generated.

Figure **2.7** A mid-thread 5-level quantizer: The real transfer characteristic shown as a dashed line. The linear model consists in separating the characteristic in a gain of  $1/\Delta$  and a quantization error q bounded by  $\pm 1/2$ . Beyond the range of  $\pm NL\Delta/2$  the quantizer is overloaded and the linear model no longer holds.

The subject of quantization noise is only outlined here to give an insight. The subject is handled analytically at greater length in [Gra90, Gal94, Gal93].

#### 2.1.3 Over-sampling

Today it is hard to find applications requiring quantizers with a number of bits less than 10, meaning 1024 levels. Building a quantizer with such a

**Figure 2.8** Overloaded quantizer: 2000 averages, NL=33, extra=0, Gaussian dithering of 0.5, in-band single-tone at 10kHz, sampling frequencies fs=1MHz.

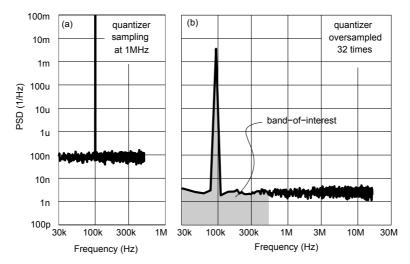

large NL is impractical. But, as explained in more detail in the next section, the quantization noise level is inversely proportional to the sampling frequency. We can therefore choose to sample the signal faster.

Let us suppose that the input signal frequency never exceeds a certain  $band\text{-}of\text{-}interest\ f_b$ . If  $f_s$  equals twice  $f_b$ , the quantizer is said to operate at the Nyquist-rate, whereas if  $f_s$  is higher we talk about over-sampling. We commonly define the  $Over\text{-}Sampling\ Ratio\ OSR$  as how much faster the signal is sampled with respect to the Nyquist rate.

$$OSR = \frac{f_s}{2f_b} . (2.6)$$

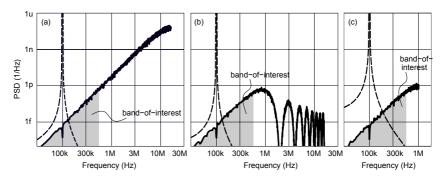

Figure 2.9 highlights how the 33-level example studied previously, over-sampled 32 times, sees its quantization level dropping. In addition to lowering the quantization noise PSD, over-sampling provides a frequency space able to contain unwanted signals that would be removed afterwards. Signals appearing either inside or outside the band-of-interest are usually referred to as the *in-band* and *out-of-band* signals respectively.

**Figure 2.9** Over-sampled quantizer: Simulation results of Code 2.3 with avr=20, NL=33, extra=-1.5,  $d_0$ =0.5. As the sampling frequencies goes from (a)1MHz to (b)32 MHz, the quantization noise, integrated over the band of interest, here from 0 to 500kHz, drops by the same factor. Meanwhile, the area under the in-band tone at 100kHz remains unchanged.

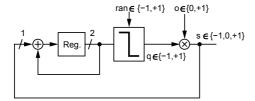

#### 2.1.4 Spectral shaping

$\Delta\Sigma$ -modulation consists in grafting an analog error control system onto an over-sampled quantizer. The digital quantizer output is converted by DACs and re-injected before the quantizer, so creating one or more feedback loops. Unlike the quantizer, a DAC does not introduce any quantization error and is therefore represented by a linear gain as in Figure 2.10.

A nth-order modulator is a cascade of n integrators whose purpose is to provide a strong negative reaction at low frequencies. This forces the quantizer output to be an accurate replica of the analog input at low frequencies. This process is commonly referred to as  $spectral\ noise\ shaping$  and its mathematical description is analyzed in detail in the next section.

Figure 2.10 describes a conventional nth-order  $\Delta\Sigma$ -modulator implemented by Code 2.5.

**Figure 2.10**  $\Delta\Sigma$ -modulation: Conventional *n*th-order architecture.

#### **Code 2.5** MATLAB code for an *n*th-order $\Delta\Sigma$ -modulator.

```

8888888888 parameters 8888888888888888888888888888888888

coeff=[1 3 3];

n=length(coeff);

x0 = (NL - 2^n + 1 - 2) / 2;

dit = d0*randn(k+n+1,1);

sig = zeros(k, n+1);

out = zeros(k,1);

x=x0*(sin(2*pi*f0*(1:k)'/fs));

sig(:,1) = x + dit(n+1:k+n);

for i=n+1:k

for r=1:n

sig(i, r+1) = sig(i-1, r+1) - coeff(r) * out(i-1) + sig(i-1, r);

if (abs(sig(i,n+1)) >= NL/2)

out (i) = sign (sig (i, n+1)) * (NL-1)/2;

else

out(i) = round(sig(i, n+1));

end

end

out=out-dit(1:k);

%dither remotion

```

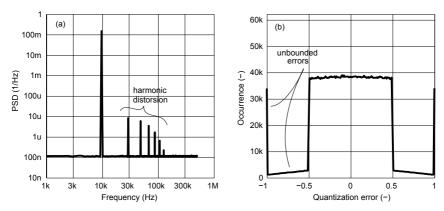

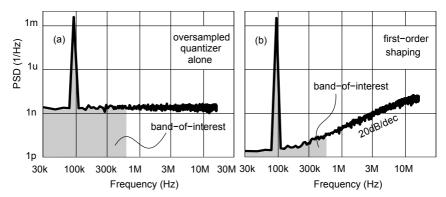

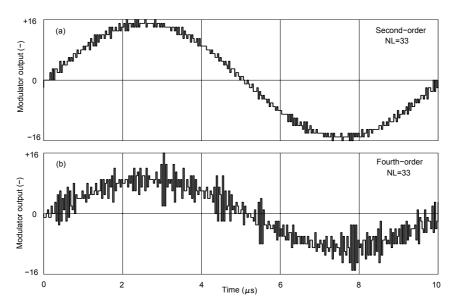

Figure 2.11 shows the quantizer output with a first-order control system. Compared to the over-sampled quantizer alone, the quantization noise level droped around DC. In contrast, the input tone remained unchanged. The control system provided what we call *spectral shaping*. As for the simple over-sampled case, we consider our input signals are within a certain band-of-interest.

Figure 2.11 Spectral shaping: Simulation results of (a) Code 2.3 and (b) Code 2.5 with avr=20,NL=33,extra=-1.5,  $d_0=0.5$ ,  $f_s=32$ MHz. The shaping provides a 3-decade attenuation of the quantization level at low frequencies. Meanwhile, the area under the in-band tone at 100kHz remains unchanged.

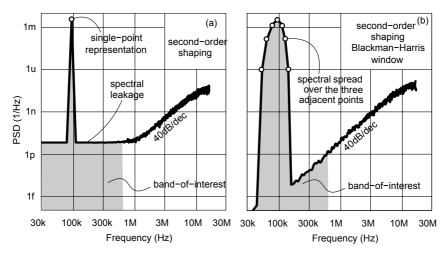

Figure 2.12 shows the quantizer output with a second-order control system. At first sight, the second-order shaping does not bring any benefit with respect to the first-order shown previously. In reality, the quantization noise floor goes further down but this is hidden by a phenomenon called *spectral leakage*.

Fourier analysis supposes that the data go from minus infinity to plus infinity and are perfectly periodic. To this extent what we did is equivalent to multiplying these samples by a finite rectangular window. As a result, the spectrum of the data, periodic and of infinite length, convolves with the spectrum of the window. Hence, the spectrum of the rectangular window is a sinc function and therefore has so-called *side-lobes* which make any point of the data spectrum *leak* on the other frequencies. Well-known textbooks like [OSB99, HvV99], where the subject is studied in detail, propose other windows with reduced side-lobes but increased speed of the spectrum. The *Blackman-Harris* window provides an interesting trade-off. Figure 2.12(b) shows the same second-order modulator output with the proposed modification of Code 2.6 including the windowing of the samples. The tone is now represented by about five dominant points and the side-lobes are low enough to reveal the drop of quantization noise level.

Figure 2.12 Second-order spectral shaping: 20 averages, NL=33, extra=-1.5, Gaussian dithering of 0.5, in-band single-tone at 100kHz, sampling frequencies  $f_s$ =1MHz and 32MHz.

$\textbf{Code 2.6} \ \ \text{Modification of the MATLAB code for PSD estimation with Blackman-Harris window}$

```

w=blackmanharris(kfft);

w=w/mean(w);

psd=zeros(kfft, 1);

for j=0:avr-1

y=w.*out(1+j*kfft:(j+1)*kfft);

psd=psd+abs(fft(y)).^2/kfft/fs;

end

psd=psd(1:kfft/2+1)/avr;

```

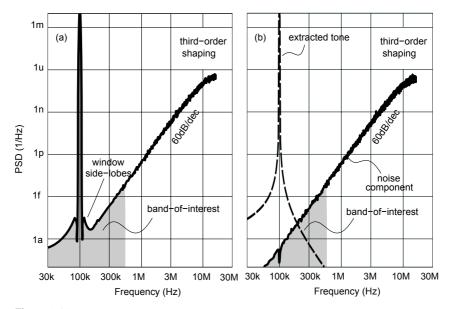

As we increase either n or NL, the tone representation in the PSD moves up and the side-lobes around the tone emerge from the noise. As highlighted by the third-order case in Figure 2.13, it becomes harder to make a clear distinction between the tone and the noise contributions.

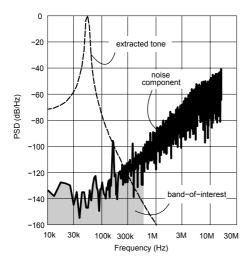

Another way of proceeding, practiced in particular by [FSW<sup>+</sup>02], consists in extracting the tone from the samples using the best root-mean-square method. Then both the tone and the noise PSD are evaluated separately. Distinction between the tone and the noise is now guaranteed and a narrow spectrum window, like the Blackman-Harris, is therefore not

Figure 2.13 Third-order spectral shaping: 20 averages, NL=33, no extra, no dithering, in-band single-tone at  $100 \mathrm{kHz}$ , sampling frequencies 32 MHz.

necessary. Only the side-lobes are to be considered to avoid leakage. We can also remove the period synchronization, since an integer number of periods is not essential. Code 2.7 encompasses the modifications of PSD estimation.

${\bf Code~2.7}$  Modification of MATLAB code for PSD estimation with signal extraction method.

```

y_s=(A(1).*s+A(2).*c);

y_n=y-y_s;

psd_n=psd_n+abs(fft(y_n)).^2/kfft/fs;

psd_s=psd_s+abs(fft(y_s)).^2/kfft/fs;

end

psd_s=psd_s(1:kfft/2+1)/avr;

psd_n=psd_n(1:kfft/2+1)/avr;

```

A Hann window is used. Ideal sine-wave and cosine-wave vectors  $s_i$  and  $c_i$  are generated. Their amplitudes,  $s_0$  and  $c_0$ , are found by minimizing the root-mean-square errors with respect to the sample vector  $y_i$ :

$$\frac{\partial}{\partial s_0, c_0} \sum_{i=1}^k (y_i - s_0 s_i - c_0 c_i)^2 = 0.$$

(2.7)

which lead to the following solution:

$$\begin{bmatrix} s_0 \\ c_0 \end{bmatrix} = \begin{bmatrix} +\sum s_i^2 & +\sum s_i c_i \\ -\sum s_i c_i & +\sum c_i^2 \end{bmatrix}^{-1} \begin{bmatrix} +\sum y_i s_i \\ -\sum y_i c_i \end{bmatrix} . \tag{2.8}$$

Note that in this last example no dithering is used. In fact, as the order is higher, the length of any output pattern that would repeat periodically becomes extremely large.

### 2.1.5 Digital decimation

As mentioned earlier, the digital quantizer output goes through a filter, ideally removing everything outside the band, and is re-sampled at the Nyquist rate. Such a process is called *decimation*. The design of the digital filter depends strongly on the application, more specifically on what we expect as out-of-band unwanted signals. In most cases, the decimation is done in two stages. Each of them consists of an anti-aliasing filter followed by a down-sampler. Because a linear phase response is often required and stability must be guaranteed, Finite Impulse-Response (FIR) filters with symmetric coefficients are used almost exclusively.

The first-stage performs a rough filtering and down-samples at twice the Nyquist rate. It consists of a cascade of n identical m-tap FIR filters. Because all the m coefficients are equal to one, this is called an nth-order comb-filter. The transfer function  $H_c(z)$  of the filter becomes a geometric series and can therefore be rewritten as follows:

$$H_c(z) = (1 + z^{-1} + z^{-2} + z^{-3} + \dots + z^{-m})^n = \left(\frac{1 - z^{-m}}{1 - z^{-1}}\right)^n$$

(2.9)

Therefore, as described in Figure 2.14, a comb-filter can be realized with n accumulators, operating at  $f_s$ , and n differentiators operating at  $f_s/m$ .

Figure 2.14 First-stage decimation filter made of n cascaded accumulators and n differentiators.

According to [Bra91], it is sufficient to chose a filter order n equal to the order of the modulator plus one. Figure 2.15 show the first-stage decimation process applied to a second-order modulator.

**Figure 2.15** First-stage decimation: (a) 33-level second-order modulator output sampled at 32MHz and comb filter output before (b) and after down-sampling (c) at 2MHz. A band of 500KHz is considered.

Code 2.8 provides the necessary additional procedure for this experiment. Figure 2.15(b) highlights the comb filter shaping with its notches at multiples of 2MHz. Figure 2.15(c) shows the PSD after down-sampling at 2MHz. The spectrum around the notches folds back to DC. Nevertheless, the attenuation around the notches prevents the noise floor increasing.

Code 2.8 MATLAB code for the first-stage decimation filter.

```

x=out mod;

out comb=zeros(k,1);

acc1=zeros(k,1);acc2=zeros(k,1);acc3=zeros(k,1);

dif1=zeros(k,1); dif2=zeros(k,1); dif3=zeros(k,1);

out=zeros(k,1);

for i=17:k

acc1(i) = acc1(i-1) + x(i-1);

acc2(i) = acc2(i-1) + acc1(i-1);

acc3(i) = acc3(i-1) + acc2(i-1);

dif1(i) = acc3(i) - acc3(i-16);

dif2(i)=dif1(i)-dif1(i-16);

out comb(i) = dif2(i) - dif2(i-16);

end

out comb=out comb/16^3;

out comb down=out comb(1:16:k);

x=out comb down;

```

The second-stage of decimation consists of a sharper filter, usually implemented as a half-band filter, performing the remaining down-sampling factor of two. A half-band filter is a symmetric (m/2+1)-tap FIR filter, where the order m is even and all odd coefficient are chosen to be zero, except the middle one. Its transfer function  $H_h(z)$  can be written as

$$H_h(z) = \begin{cases} c_1 z^{-1} + c_3 z^{-3} + \dots + c_{m/2} z^{-m/2} + \dots \\ c_0 z^{-0} + c_2 z^{-2} + \dots + c_{m/2} z^{-m/2} + \dots \\ \dots + c_3 z^{-m+3} + c_1 z^{-m+1} , & \text{if } \frac{m}{2} \text{ is even }, \\ \dots + c_2 z^{-m+2} + c_0 z^{-m} . & \text{if } \frac{m}{2} \text{ is odd }. \end{cases}$$

$$(2.10)$$

Depending on the application, a high-order FIR filter is required to remove unwanted signals, as well as quantization noise, that would fold back to the band-of-interest when down-sampling. A poly-phase half-band filter allows the number of operations to be drastically reduced compared

to conventional FIR filters. Nevertheless, such an architecture can only perform a decimation by two.

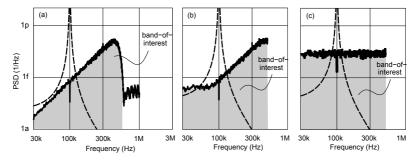

Figure 2.16 shows the second-stage decimation process simulated with Code 2.9.

**Figure 2.16** Second-stage decimation: Half-band FIR filter output before (a) and after down-sampling (b) at 1MHz. (c) PSD of a Nyquist-rate 32k-level quantizer.

## Code 2.9 MATLAB code for the second-stage decimation filter.

Figure 2.16(b) shows the filter output after down-sampling. The PSD highlights the aliasing of the spectrum around  $f_s/2$  which folds back to DC. Figure 2.16(c) shows the PSD of a Nyquist-rate quantizer with a large number-of-levels. The areas under the band-of-interest in Figures 2.16 and 2.15 are all the same. The 33-level analog modulator,

together with digital filters, is comparable to a 32k-level Nyquist-rate quantizer.

Another filter, operating at the Nyquist rate, is usually added to compensate for the droop of the signal transfer function inside the band-of-interest brought about by the preceding filter stages.

Since the complexity of the stages progressively increseases up as the sampling frequency decreases, this set-up is efficient in terms of area and power consumption. Moreover, filtering and down-sampling are often combined. The digital filter is part of the complete analog-to-digital conversion process. One of the interesting aspects of  $\Delta\Sigma$ -modulation-based converters is that they are realized with half analog circuitry and half digital hardware. The latter takes benefits from the constant progress in CMOS technologies. Its contribution to power consumption and die area therefore becomes negligible. Furthermore, the digital section is usually synthesized from a formal description, in a Hardware Description Language (HDL), so allowing jumping from one technology to the other without redesigning the whole filter.

## 2.2 Performance calculations

## 2.2.1 Linear model

In the previous section we saw that the quantization process described by Equation (2.5), under certain conditions, is equivalent to a linear gain of  $1/\Delta$  and an additional random signal q, called the *quantization noise*. The quantizer can therefore be represented as in Figure 2.17.

**Figure 2.17** Quantization: Linear signal flow graph representation where, q is white noise uniformly distributed between  $\pm 1/2$ .

According to the observation made in Section 2.1.2, the probability density function of the quantization noise  $p_q(x)$  has a uniform distribution

bounded by  $\pm 1/2$ :

$$p_q(x) = \begin{cases} 1, & \text{if } -1/2 < x < +1/2, \\ 0, & \text{otherwise}. \end{cases}$$

(2.11)

The variance of such a distribution<sup>1</sup> is well-known as:

$$\sigma_q^2 = \int_{-\infty}^{+\infty} p_q(x) x^2 dx = \frac{1}{12} . \tag{2.12}$$

Additionally, the power spectral density of the quantization noise  $\mathcal{P}_q(f)$  is constant. With the hypothesis that the quantization noise is stationary and according to Rayleigh's energy theorem we can write:

$$\sigma_q^2 = \int_{-\infty}^{+\infty} \mathscr{P}_q(f) df = \mathscr{P}_q(f) f_s. \qquad (2.13)$$

We can finally claim that the quantization noise power spectrum is of the form

$$\mathscr{P}_{q}(f) = \begin{cases} \frac{1}{12f_{s}}, & \text{if } -f_{s}/2 < f < +f_{s}/2, \\ 0, & \text{otherwise}. \end{cases}$$

(2.14)

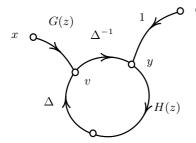

## 2.2.2 Modulator general description

Any single-stage  $\Delta\Sigma$ -modulator could be described by the linear Signal Flow-Graph (SFG) shown in Figure 2.18. As considered from the beginning of this chapter, nodes x and y represent the modulator analog input and digital output, whereas node v is the input of the quantizer.

We apply the quantizer linear approximation discussed previously. The quantizer is therefore modeled as a gain of  $\Delta^{-1}$  with an additional white noise source q, uniformly distributed between  $\pm 1/2$ . By applying Mason's gain formula [MZ60], we can calculate the expression of frequency response Y(z) and V(z) as functions of the sources X(z) and Q(z):

<sup>&</sup>lt;sup>1</sup>Many textbooks refer the quantization noise to the quantizer input. In such a case, the random variable q is uniform to within  $\pm \Delta/2$  and the variance is equal to  $\Delta^2/12$

Figure 2.18 General linear Signal Flow Graph representation of the single-stage modulator: The quantizer is represented by a gain of  $\Delta^{-1}$  and an additional random source q. In contrast, the DACs do not introduce errors and are simply modeled as a gain of  $\Delta$ .

$$Y(z) = \underbrace{\frac{G(z) \cdot \Delta^{-1}}{1 - H(z)}}_{\text{=STF}(z)} X(z) + \underbrace{\frac{1}{1 - H(z)}}_{\text{=NTF}(z)} Q(z) , \qquad (2.15)$$

$$V(z) = \underbrace{\frac{G(z)}{1 - H(z)}}_{=\Delta \cdot \text{STF}(z)} X(z) + \underbrace{\frac{H(z) \cdot \Delta}{1 - H(z)}}_{=\Delta \cdot (\text{NTF}(z) - 1)} Q(z) . \tag{2.16}$$

Equation (2.15) provides the common definition of the Signal Transfer Function (STF) and the Noise Transfer Function (NTF).

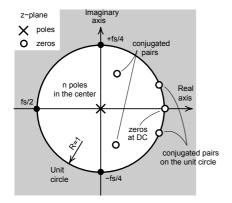

## 2.2.3 Dynamic range

Let us consider as a hypothesis the classic nth-order architecture with a flat STF(z), which simply consists of an n-delay function, and an NTF(z)with n poles at the center of the z-plane, and n zeros  $z_i$  at frequencies  $f_i$ , that are either real or complex conjugated pairs:

$$STF(z) = \Delta^{-1}z^{-n} , \qquad (2.17)$$

$$STF(z) = \Delta^{-1} z^{-n} , \qquad (2.17)$$

$$NTF(z) = \prod_{i=1}^{n} (1 - z_i z^{-1}) , \qquad (2.18)$$

where

$$z = e^{j2\pi f/f_s} , \qquad (2.19)$$

$$z_i = e^{j2\pi f_i/f_s + \sigma_i}. (2.20)$$

Figure 2.19 Poles and zeros: representation in the complex z-plane. Stability is guaranteed if all the poles are within the unit circle. Here all the n poles are placed at the center providing the maximum stability. The zeros appear either on the real axis or in complex conjugated pairs.

In such conditions, with the additional constraint that  $\text{Re}[z_i] \geq 0$ ,  $\forall z_i$ , referring to Equation (2.16), the highest possible value of v is given by:

$$||y||_{\infty} = \underbrace{||STF(z)||_{1}}_{=k_{x}\Delta^{-1}} \cdot ||x||_{\infty} + \underbrace{||NTF(z)||_{1}}_{=k_{x}} \cdot ||q||_{\infty} , \qquad (2.21)$$

$$\|v\|_{\infty} = \underbrace{\|\operatorname{STF}(z)\|_{1} \cdot \Delta}_{=k_{x}} \cdot \|x\|_{\infty} + \underbrace{\|\operatorname{NTF}(z) - 1\|_{1}}_{=k_{q} - 1} \cdot \Delta \cdot \|q\|_{\infty} . \quad (2.22)$$

Let us call the quantities  $k_x$  and  $k_q$  signal and noise range factors respectively. The initial hypotheses of Equation (2.17) imply that  $k_x$  is always unity. According to the definitions and proofs provided in Appendix A.1 and A.2, we can write that:

$$k_x = 1 (2.23)$$

$$k_q = \prod_{i=1}^n (1 + z_i) \ . \tag{2.24}$$

For the specific case where all the zeros are placed at DC, these relationships become

$$k_x = 1 (2.25)$$

$$k_q = 2^n . (2.26)$$

Let us assume that the modulator is at the limit of overloading. The quantization errors are still uniformly distributed between  $\pm 1/2$  and we can write:

$$||q||_{\infty} < \frac{1}{2}$$

(2.27)

$$||v||_{\infty} < \frac{1}{2}\Delta(NL) \tag{2.28}$$

The definition of v claims that the quantizer never overloads, which implies that q never exceeds  $\pm 1/2$ . Once all these conditions are met, we can rewrite Equation (2.22) to optain that

$$||x||_{\infty} < \frac{1}{2}\Delta \left(NL - k_q + 1\right)$$

, (2.29)

which provides the maximum input signal the modulator can sustain without overloading, also referred to as the *full-scale* amplitude. It is interesting to note that NL cannot be smaller than kq-1 and that this limitation increases with the modulator order. For this reason, the non-overload dynamic range is limited by the equation:

$$NL = 2^n - 1. (2.30)$$

With a single comparator quantizer NL = 2 and with any order n > 1 the modulator is overloaded for an NTF=  $(1 - z^{-1})^n$ .

Figure 2.20 illustrates how a high-order modulator is limited. More room is required for quantization noise than for the signal itself. From Equation (2.21) we find the range of the digital output to be right at the limit of the maximum deliverable by the quantizer:

$$||y||_{\infty} < \frac{1}{2}(NL+1)$$

. (2.31)

### 2.2.4 Resolution

Let us consider now an *n*th-order modulator, such as described by Equations (2.18) and (2.17), with all its zeros at DC, namely  $z_i = 1$ ,  $\forall z_i$ . A full-scale tone applied at the input appears at the output with a total power

$$P_{x,y} = \frac{\|x\|_{\infty}^{2}}{2} |STF(f)|^{2} = \frac{1}{8} (NL - 2^{n} + 1)^{2} .$$

(2.32)

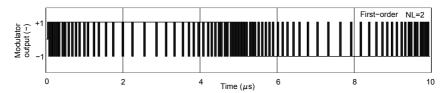

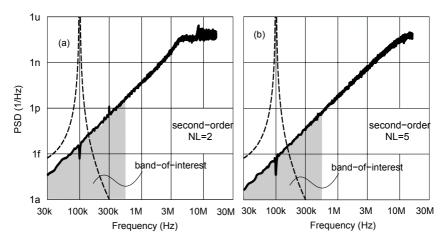

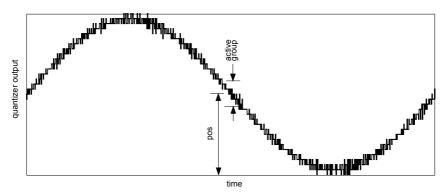

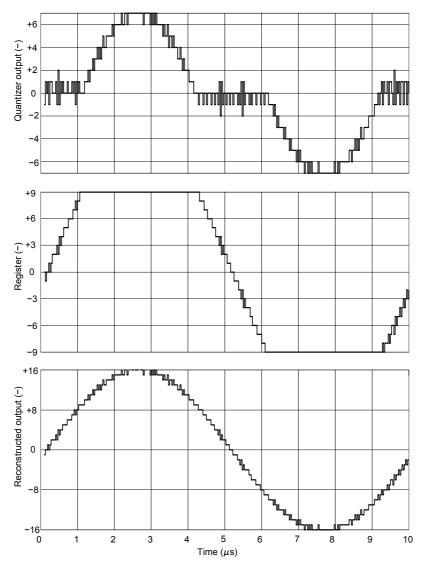

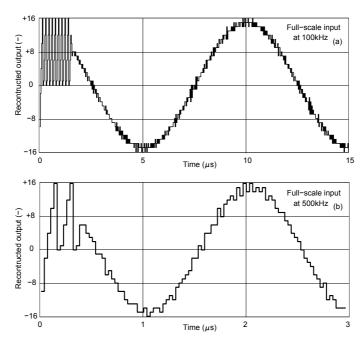

**Figure 2.20** Digital output of a second (a) and a fourth-order (b) modulator with a 33-level quantizer. A clear distinction can be made between the fast quantization noise at 32MHz and the slow 100kHz-tone input.

However, the quantization noise q undergoes the NTF before reaching the output. As shown in the previous section, the modulator output passes through different digital filters and is down-sampled to  $2f_b$ . For this reason, supposing ideal infinitely sharp filtering, only the quantization noise integrated over that band-of-interest is to be considered:

$$P_{q,y} = \int_{-f_b}^{f_b} \mathscr{P}_Q(f) df = 2 \frac{1}{12f_s} \int_{0}^{f_b} |\text{NTF}(f)|^2 df . \qquad (2.33)$$

As mentioned earlier, the Over-Sampling Ratio (OSR) is defined as:

$$OSR = \frac{f_s}{2f_b} . (2.34)$$

Assuming the OSR  $\gg 1$ , namely  $f_s \gg f_b$ , the NTF can be simplified by

removing the high-order terms in its Taylor expansion.

$$|\text{NTF}(f)|^{2} = \left| (1 - z^{-1})^{n} \right|_{z=e^{j2\pi f/f_{s}}}^{2} = \cdots \qquad (2.35)$$

$$\cdots = \left| \left( -j\frac{2\pi f}{f_{s}} - \frac{2\pi^{2} f^{2}}{f_{s}^{2}} + j\frac{4\pi^{3} f^{3}}{3f_{s}^{3}} + \cdots \right)^{n} \right|^{2} \cong \left( \frac{2\pi f}{f_{s}} \right)^{2n}.$$

The high-over-sampling assumption simplifies the calculation of  $P_{q,y}$ :

$$P_{q,y} \cong \frac{2}{12f_s} \int_0^{f_b} (2\pi f/f_s)^{2n} df = \frac{1}{12\pi} \left(\frac{\pi}{\text{OSR}}\right)^{2n+1} / (2n+1) .$$

(2.36)

We finally calculate the *Signal-to-Quantization Noise Ratio* and find the general relationship:

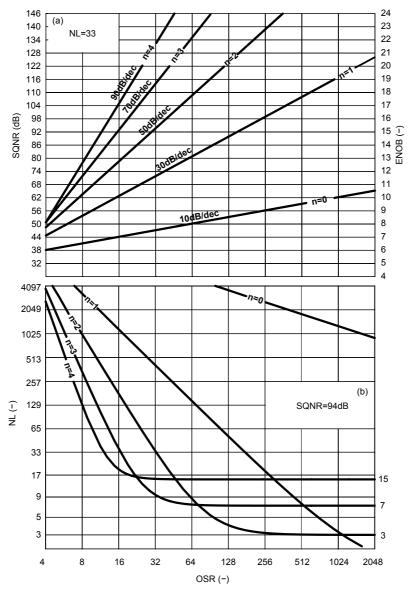

$$SQNR_{max} = \frac{P_{x,y}}{P_{q,y}} = \frac{3}{2} \pi (NL - 2^n + 1)^2 (2n + 1) \left(\frac{OSR}{\pi}\right)^{2n+1}.$$

(2.37)

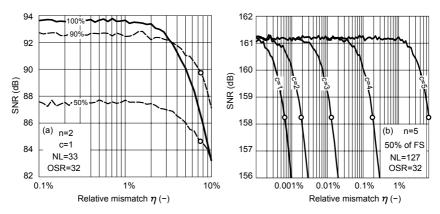

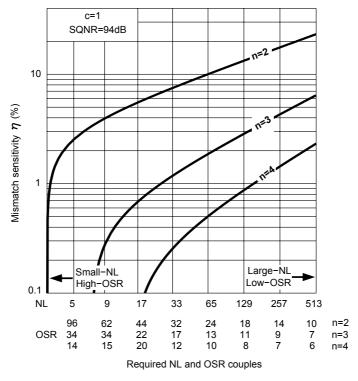

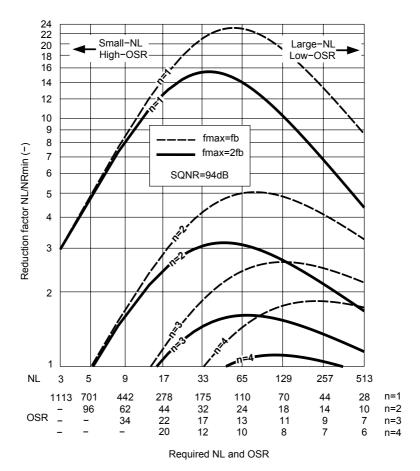

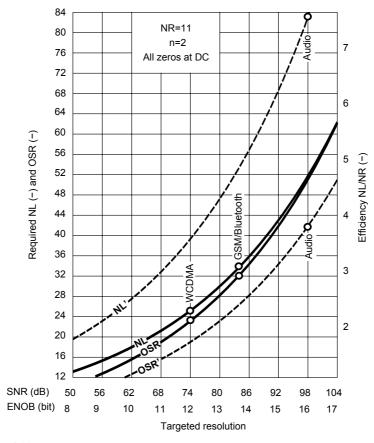

This relationship is evaluated in Figure 2.21(a) for different cases of modulator order. As an alternative, Figure 2.21(b) shows the equation inverted so as to find the quantizer size for a targeted  $SQNR_{max}$ :

$$NL = 2^{n} - 1 + \sqrt{\frac{2\pi SQNR}{3(2n+1)} \left(\frac{\pi}{OSR}\right)^{2n+1}}.$$

(2.38)

Similarly, the expression for the SQNR can be inverted so as to find the required OSR as a function of the other parameters:

OSR =

$$\pi \sqrt[2n+1]{\frac{2 \text{ SQNR}}{3\pi (\text{NL} - 2^n + 1)^2 (2n + 1)}}$$

. (2.39)

In the case of non-over-sampled quantizer alone, referred to as a Nyquist-rate quantizer, n=0, OSR=1 and we get:

$$SQNR_{max} = \frac{3}{2}NL^2. \qquad (2.40)$$

Figure 2.21 Equation (2.37): (a) achievable SQNR for a given NL=33 and (b) required NL for a given SQNR=94dB.

As mentioned in the previous section, we can define the *number-of-bits* N, also referred to as the *resolution*

$$N = \frac{\log NL}{\log 2}.$$

(2.41)

By combining the last two equations we find the relationship between the SQNR and an the equivalent N-bit quantizer resolution, commonly called *Effective Number-of-Bits* ENOB.

$$ENOB = \frac{SQNR_{dB} - 1.76}{6.02}$$

(2.42)

The left and right scales in Figure 2.21(a) provide this direct relationship between the ENOB and the SQNR. In a real implementation, the distortion generated by the circuit itself and by other sources of noise degrades the SNQR. The latter becomes the *Signal-to-Noise plus Distortion Ratio* SNDR. This last relationship therefore provides a way of evaluating an equivalent resolution in terms of the number of bits.

### 2.2.5 Simulations

Given the power spectral density, extracted according to the methods described in Section 2.1.4, the expected resolution is determined as the ratio of the total signal and noise power within the band-of-interest. As proposed by the additional Code 2.10, the total powers are evaluated by summing the noise and extracted power spectral densities along the band.

$\textbf{Code 2.10}\,$  Additional MATLAB code for SNR calculation with the signal extraction method.

```

f1=0; f2=500e3;

kf1=round(f1/fs*kfft)+1;

kf2=round(f2/fs*kfft)+1;

SNR=10*log10(sum(psd_s(kf1:kf2))/sum(psd_n(kf1:kf2)))

```

Alternatively, the conventional evaluation of the SNR is given by  $\operatorname{Code} 2.11$ .

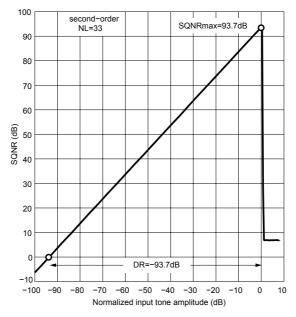

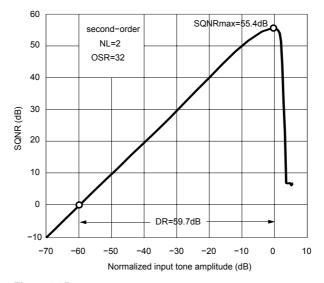

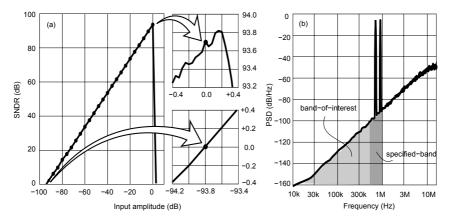

The SNR is usually evaluated for different input signal amplitude providing the so-called *Dynamic-Range Plot* (DR-Plot). Figure 2.22 shows

Code 2.11 Additional MATLAB code for SNR calculation with direct evaluation.

```

f1=0; f2=500e3;

kf1=round(f1/fs*kfft)+1;

kf2=round(f2/fs*kfft)+1;

kf0=round(f0/fs*kfft)+1;

SNR=10*log10(sum(psd(kf0-3:kf0+3))/sum(psd([kf1:kf0-4,kf0+4:kf2])));

```

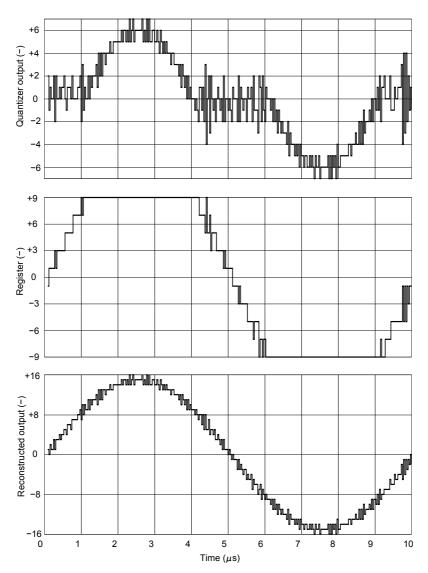

**Figure 2.22** Dynamic range plot around the under- and over-load regions for a second- and third-order modulator. To optain such a smooth plot, 1000 averaging points are required and a small 0.05 dithering signal for the second-order modulator.

the DR-Plot for a 33-level second-order modulator. As expected, the SNR grows monotonically from zero up to  $\mathrm{SQNR}_{\mathrm{max}}$  with a slope of 10dB per decade. For some architecture or in the presence of circuit imperfections, the DR-Plot may present a deviation from the ideal form. To make things clear, we commonly define the *Dynamic Range* as the input amplitude

**Figure 2.23** Dynamic range plot around under-over-load region for a second- and third-order modulator. To obtain such a smooth plot 1000 averaging points are required and a small 0.05 dithering signal for the second-order modulator.

**Figure 2.24** Quantization noise in the overload region for a second-order modulator with extra=0.2.

range for which the SNR goes from zero to its maximum, usually referred to as the *Peak*-SNR. In the ideal case DR and SNR are the same.

For input amplitudes higher than the range determined by Equation (2.29) the quantizer overloads. The modulator cannot be considered as a linear system anymore. The feedback loops small-signal gain is periodically deactivated and the system tends to work as a cascade of n integrators in open-loop. Since such a system is unstable, increasing the amplitude leads to further instability. For this reason, the SNR drops abruptly. Figure 2.23 highlights the transition from an under-load situation, through an over-load region, before reaching a completely unstable

condition.

Figure 2.24 shows the quantization errors under over-load conditions. The errors remain within  $\pm 0.5$  with periodical exceptions when the input signal is either high or low, thus generating harmonics and additional noise. The behavior within this region is hard to predict since the modulator cannot be modeled anymore as a linear system. In a conservative design we try to avoid the overload region. Nevertheless, the third-order case in Figure 2.23(b) reveals a longer overload region because of a larger  $k_q$  which can be exploited for higher-order cases.

## 2.2.6 Aggressive pole placement

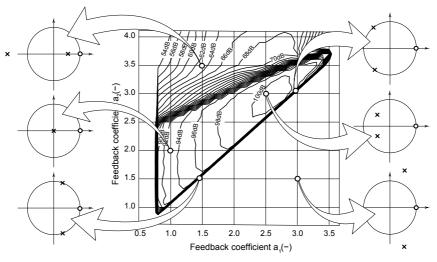

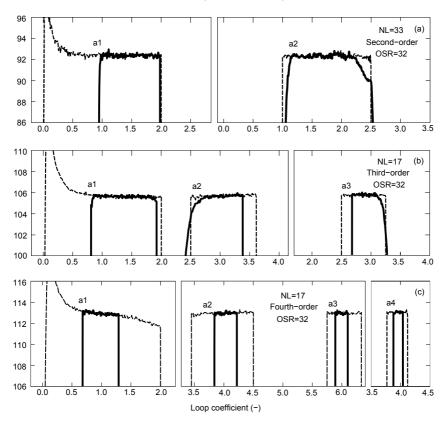

Figure 2.25 Maximum achievable SQNR of a 33-level second-order modulator with an OSR of 32 as a function of the global feedback coefficients  $a_1$  and  $a_2$ . The resulting position of the poles and zeros for few relevant case are depicted on the sides. The experiment is performed with at input signal at 100kHz for a sampling frequency of 32MHz.

The poles are responsible [HvV99] for the rising peaks, even to infinity, of the frequency response. Any real pole, or conjugated complex pair of poles, inside the unity circle provides a damped impulse response. In contrast, the poles outside the circle provide an impulse response which

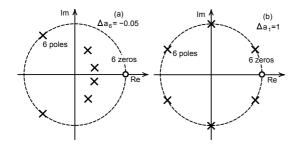

grows unbounded. The position of the poles, shared by both the NTF and the STF, is determined by global feedback coefficients  $a_i$ . As already mentioned in Section 2.2.3, we chose throughout this thesis to place the poles at the center of the z-plane. This provides the system with the best robustness in terms of stability [Oga95, Lon95], the center of z-plane being the farthest point from the unity circle.

The performance of the spectral shaping in a  $\Delta\Sigma$ -modulator is essentially determined by the zeros. The poles may nevertheless increase the integrated quantization noise if they are placed close to the band-of-interest. Figure 2.25 show the maximum achievable SQNR as a function of the global feedback coefficients. Paradoxically, an appropriate placement of the poles allows an improvement of the SQNR by 6dB with respect to the conservative case where the poles are at the center.

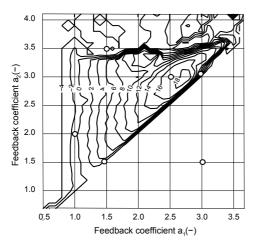

**Figure 2.26** Parameter extra as a function of the global feedback coefficients  $a_1$  and  $a_2$  for the case of Figure 2.25.

This improvement is due to an increase in dynamic range. In this experiment, for each set of coefficients, a dynamic range plot is performed to find the maximum input amplitude, sometimes also over-loading the quantizer. Figure 2.26 depicts the parameter extra for each set of feedback coefficients. This parameter is defined as the additional number-of-levels with respect to the over-load limit for the simple case with all the poles in the center.

The Figure 2.25 shows that the maximum of 100dB is reached when  $\{a_1, a_2\} = \{2.5, 3\}$ . The case with  $\{1.5, 3.5\}$  is unstable but provided an

SQNR of 63dB. The saturation of the quantizer limiting the unstable behavior caused the modulator to operate as a highly non-linear system.

Designing an NTF with optimal placed poles is risky and is usually referred to as aggressive noise shaping in contrast to a conservative noise shaping. Furthermore, to have a flat STF, feed-forward paths are required to compensate for the rise provided by the poles.

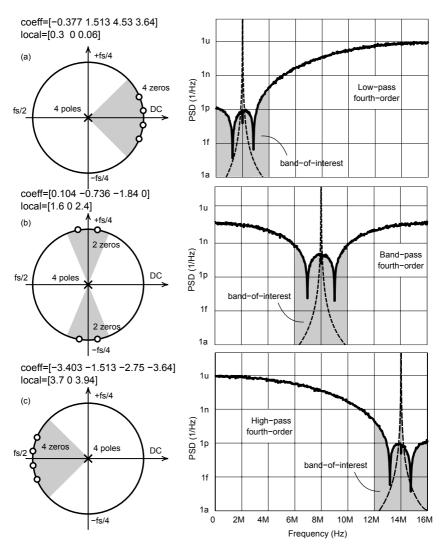

## 2.2.7 Optimal zero placement

So far we have considered the NTF of modulators with zeros placed at DC. The general case studied in Section 2.2.3 started with the hypothesis, in Equation (2.18), that zeros are either real or complex conjugated pairs. To be able to control the zeros, additional *local* feedback paths are necessary. By local feedback, we mean feedback loops not comprising the quantizer. The generic architecture, described in Figure 2.27 and implemented by the additional Code 2.12, forces the zeros to be placed on the unit circle.

Figure 2.27  $\Delta\Sigma$ -modulation: Additional local feedbacks  $b_i$  controlling the zeros of the NTF.

**Code 2.12** Additional MATLAB code for local feedback paths. The vectors **coeff** and **local** provide the list  $a_i$  and  $b_i$  coefficients respectively.

The zeros are responsible [HvV99] for peaks of the frequency responses falling even to zero. Any real zero, or conjugated complex pair of zeros, on the unity circle provides a notch in the frequency response. The zeros that are not on the circle provide only a light drop. Without local feedback loops, all the n zeros are automatically placed at DC.

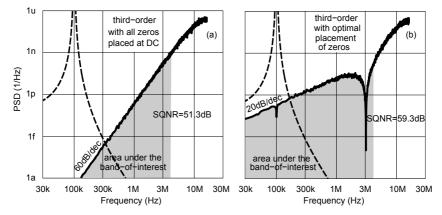

**Figure 2.28** 33-level third-order modulator sampling at 32 MHz with a band-of-interest from 0 to 4MHz. All the poles are placed at the center of the z-plane. In (a) all the zeros are at DC. In (b) one zero is placed at DC and a complex conjugated pair at 3MHz. The coefficient and local feedback vectors are respectively [1 2.64 2.64] and [0 0.36].

Placing zeros on the unit circle gives the NTF with deep drops at specific frequencies. According to [ST05], an optimal placement can provide important resolution improvements. Table 2.1 gives the frequency positions of the zeros, with respect to the band of interest, allowing calculation of the local coefficients  $b_i$ . The global coefficient values  $a_i$  are set in a *Pascal triangle* configuration. Because the local coefficients influence the location of the poles, correction terms are added to keep them at the center of the z-plane.

**Table 2.1** Feedback coefficients to place the poles at the center of the unity circle, optimal zero placement on the unity circle according to [ST05]. The nominal values of the global coefficients  $a_i$  are in bold to highlight the *Pascal triangle* configuration.

| n | $(b_1,b_2,\ldots,b_{n-1})^{\mathrm{T}}$                                                                                  | $(a_1,a_2,\ldots,a_n)^{\mathrm{T}}$                                                                                                                           | impr.(dB) |

|---|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1 | [-]                                                                                                                      | [1]                                                                                                                                                           | 0         |

| 2 | $\left[ 2 - 2\cos(\frac{0.77\pi}{\text{OSR}}) \right]$                                                                   | $\left[ egin{array}{c} 1-b_1 \ 2-b_1 \end{array}  ight]$                                                                                                      | 3.5       |

|   | $\left[\begin{array}{c}0\\2-2\cos(\frac{0.58\pi}{\mathrm{OSR}})\end{array}\right]$                                       | $\begin{bmatrix} 3 - b_1 \end{bmatrix}$                                                                                                                       | 8         |

| 4 | $\begin{bmatrix} 2 - 2\cos(\frac{0.34\pi}{\text{OSR}}) \\ 0 \\ 2 - 2\cos(\frac{0.86\pi}{\text{OSR}}) \end{bmatrix}$      | $\begin{bmatrix} 1 - b_1^3 + 5b_1^2 - 6b_1 \\ 4 - b_1^3 + 6b_1^2 - 10b_1 \\ 6 + b_1^2 - 5b_1 - b_2 \\ 4 - b_1 - b_2 \end{bmatrix}$                            | 13        |

| 5 | $\begin{bmatrix} 2 - 2\cos(\frac{0.54\pi}{\text{OSR}}) \\ 0 \\ 2 - 2\cos(\frac{0.91\pi}{\text{OSR}}) \\ 0 \end{bmatrix}$ | $\begin{bmatrix} 1 \\ 5 - b_1^3 + 6b_1^2 + b_2b_1 - 10b_1 \\ 10 - b_1^3 + 7b_1^2 + 2b_2b_1 - 15b_1 \\ 10 + b_1^2 - 6b_1 - b_2 \\ 5 - b_1 - b_2 \end{bmatrix}$ | 18        |

# 2.3 Circuit imperfections

## 2.3.1 Removal of quantization noise

We usually make a clear distinction between the quantization noise and errors provided by circuit imperfections such as thermal noise and component mismatches. The former can be seen as a system limitation imposed by design. The quantization noise often hides these imperfections. The study of their impact on the resolution becomes easier if we selectively remove quantization noise from the modulator output sequence in simulations. As implemented by Code 2.13, the difference between the output and the input of the quantizer gives the quantization errors. These errors

go through an imitation of the NTF before being subtracted from the modulator output.

Code 2.13 Additional MATLAB code for quantization noise removal. The filter function imitate a second-order with all the poles at the center of the z-plane an all the zeros at DC.

```

...

q(i)=out(i)-sig(i,n+1); %get quantization errors

end

out=out-filter([1 -2 1],[1],q); %removal

...

```

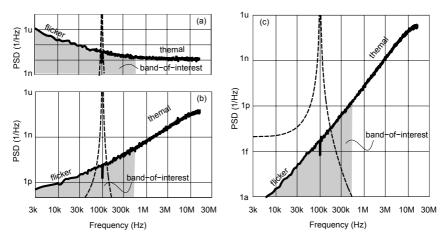

## 2.3.2 Circuit noise

The simplest model of circuit noise consists of a white Gaussian variable, accounting for thermal noise, and an additional 1/f-power law component, accounting for the so-called *flicker*-noise which is particularly important in CMOS transistors. Code 2.14 generates such a noise sequence with an IIR filter. The generation of colored noise is treated at great length in [Kas95].

$\textbf{Code 2.14}\ \mathrm{MATLAB}\ \mathrm{code}$  for the generation of circuit noise with white and  $1/\mathrm{f}\text{-power}$  law components.

```

pink=zeros(1,1000);

pink(1)=1;

for m=2:1000

pink(m)=(m-2.5)*pink(m-1)/(m-1);

end

noise=filter(1,pink,0.1*randn(k,1))+0.5*randn(k,1)

```

Figure 2.29 shows the output of a conventional second-order modulator in the presence of noise. The quantization errors are removed. A colored noise is introduced at different nodes of the system, at the modulator input, after the first integrator and before the quantizer. The results illustrate how the circuit errors, here circuit noise, benefit from the modulator spectral shaping. As a consequence, the errors due to the imperfections of the first components in the processing chain, like the input signal, undergo the STF before reaching the modulator output. It is not possible distinguish these errors form the wanted signal. As shown in

Figure 2.29(a), the colored noise appears at the output without attenuation or spectral shaping. Hence these errors usually limit the resolution of the modulator.

In contrast, the errors introduced after the kth integrator are spectrally shaped with a kth-order high-pass transfer function. In particular, as revealed in Figure 2.29(c), the errors occurring at the input of the quantizer, like the quantization noise, undergo the NTF.

**Figure 2.29** Second-order 33-level modulator with circuit noise injected at the input (a), after the first integrator (b) and before the quantizer (c). The quantization noise is removed.

## 2.3.3 Clock jitter

The modification proposed in Code 2.15 introduces the effect of an imperfect sampling clock signal. The sampling period is now randomly distributed around  $1/f_s$  using a Gaussian variable whose spectrum is white.

${\bf Code~2.15}$  Modification of the MATLAB code of the signal generation to introduce the clock jitter.

```

x=x0*(sin(2*pi*f0*(0.1*randn(k,1)+(1:k)')/fs));

```

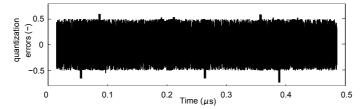

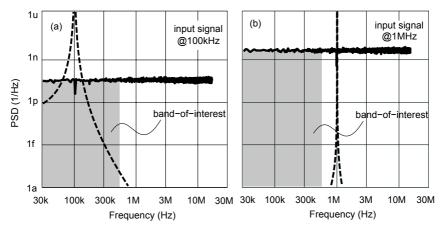

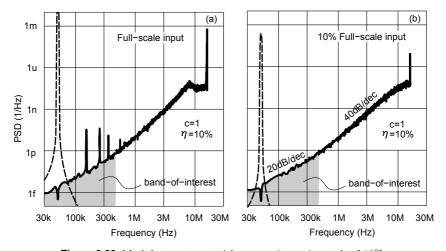

This imperfection is called *clock jitter*. Figure 2.30 show how the presence of a high-amplitude high-frequency turns the clock jitter into a noise

**Figure 2.30** Output power spectral density of a second-order 33-level modulator, whose sampling is affected by clock jitter, with a full-scale input tone at 100kHz (a) and 1MHz (b). The quantization noise is removed.

signal. The clock jitter is analyzed in detail in the next chapter, showing the different transfer mechanisms for the continuous- and discrete-time modulators.

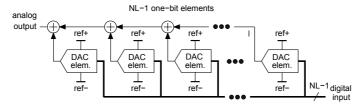

## 2.3.4 Component mismatch

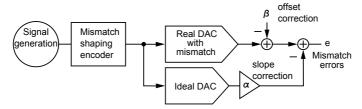

A multi-bit  $\Delta\Sigma$ -modulator requires an ADC and, for each node fed back from the digital output, a DAC. In a conventional implementation, these blocks are realized as a bank of NL comparators for the ADC, and as a bank of NL one-weight elements for the DAC. Among the major benefits of integrated circuits, we find that identical components close to each other are well matched. Nevertheless, the matching properties are highly dependent on the size of the components. But increasing their size also increases the distance between the components therefore reducing the matching properties. As a result, the matching properties are limited by the technology.

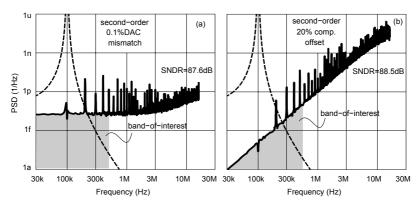

The mismatches between the components of the ADC and DAC affect their input-output transfer characteristic which is, in an ideal situation, a perfect staircase function. The DAC element mismatch changes the height of levels and the comparators offset changes the thresholds. These changes in the characteristic cause harmonic distortion. Figure 2.31 shows the modulator output in the presence of mismatch. The quantization noise is completely removed. Since the harmonic distortion occurs in the  $\Delta\Sigma$ -modulator loop, the harmonic tones generated also fold parts of the quantization noise.

**Figure 2.31** Output power spectral density of a second-order 33-level modulator with DAC elements mismatch (a) and ADC comparator offset (b).

As highlighted in Figure 2.31, the errors brought about by the ADC are shaped contrary to the errors of the first DAC. A similar degradation of SNR is produced with 0.1% and 20% of mismatch, in the DAC and ADC respectively. This illustrates once again how the spectral shaping of the modulator itself allows relaxing the circuit imperfection of components placed at the end of the signal processing chain, like the quantizer in this case.

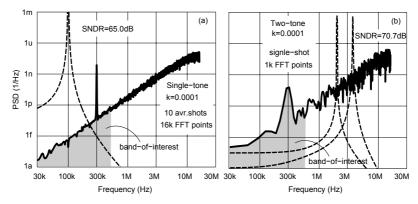

### 2.3.5 Harmonic distortion

A non-linear behavior in the system gives rise to harmonic distortion. As a didactic model, let us consider the simple function  $f(x) = x + kx^3$  and a single-tone input signal. When this function is applied directly at the input of the modulator, an additional sinewave at three times the tone frequency appears with an amplitude of 3k/4. As highlighted in Figure 2.32(a), the additional sinewave is an unwanted signal and brings

about a degradation of the SNR. As already mentionned earlier, in such a case, we use the *Signal-to-Noise plus Distortion Ratio* (SNDR) to determine the resolution. In order to take into account the distortion in simulations, the test tone needs to be set at a rather low frequency with respect to the band-of-interest. Consequently, the number of clock cycles to simulate can be quite large. This might be impractical in complex circuit level simulations.

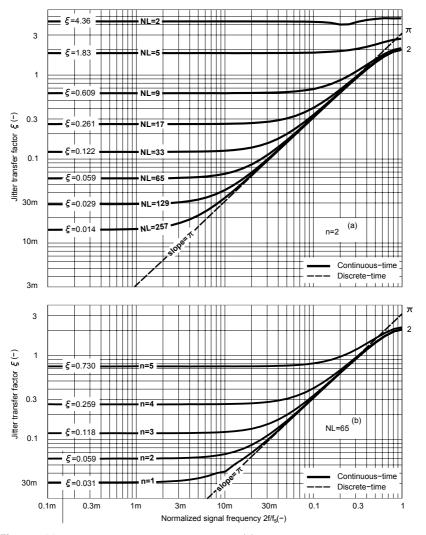

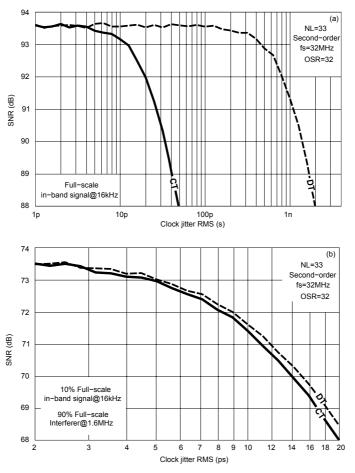

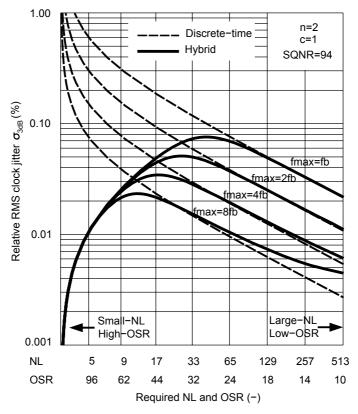

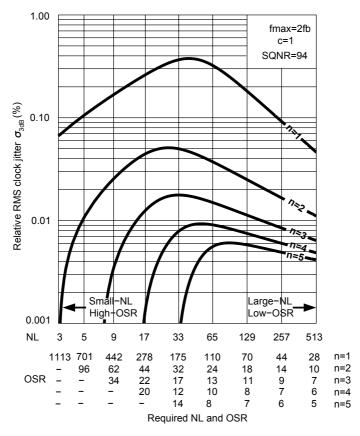

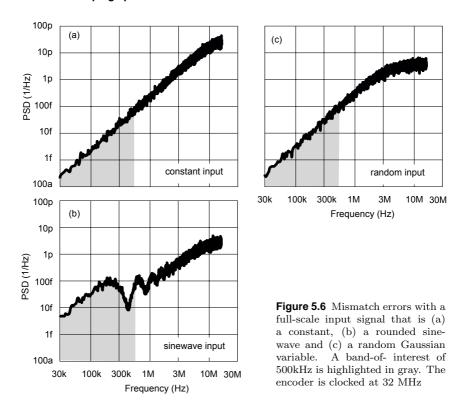

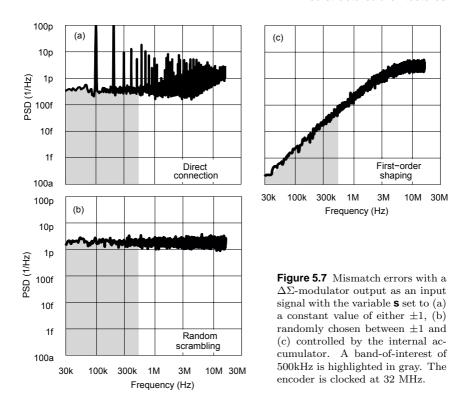

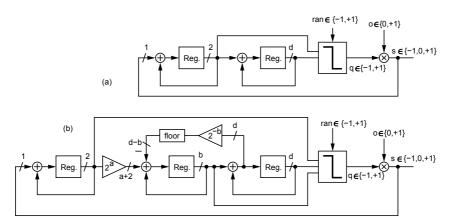

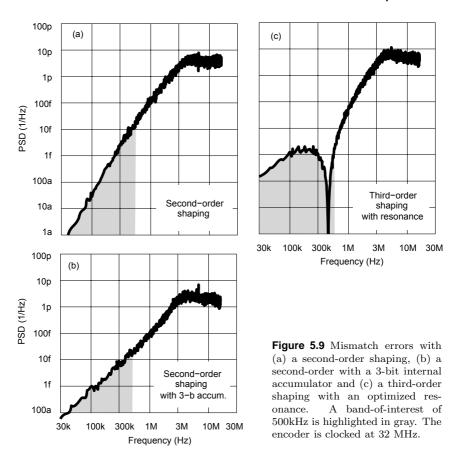

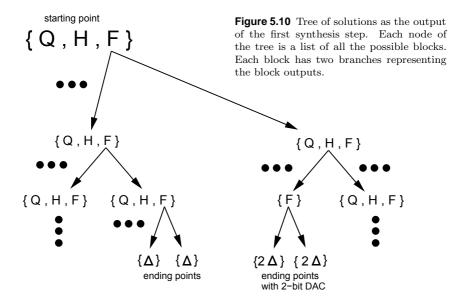

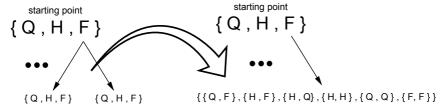

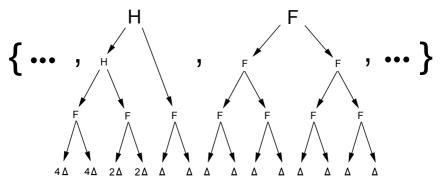

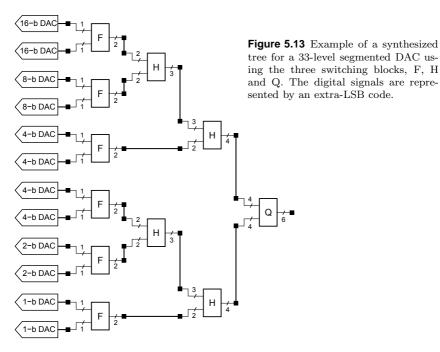

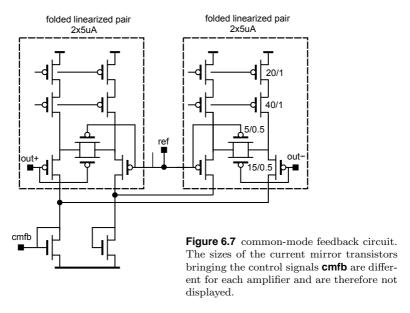

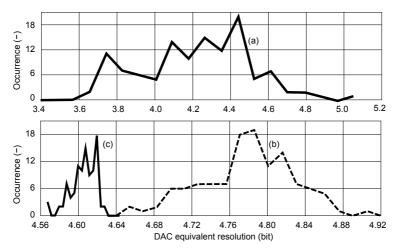

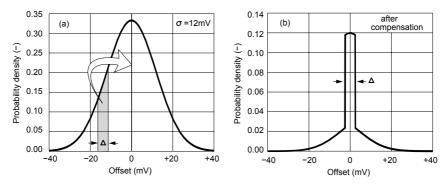

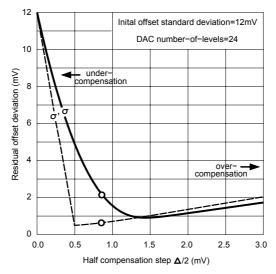

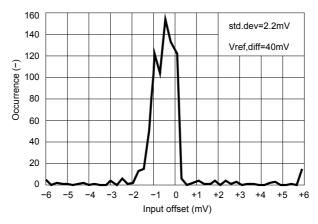

**Figure 2.32** Simulation of distorsion in a second-order 33-level modulator with a full-scale low-frequency single-tone (a) and two half-scale high-frequency tones (b). A 500kHz bandwidth is considered.