# ABOVE-IC RF MEMS DEVICES FOR COMMUNICATION APPLICATIONS

#### THÈSE N° 3778 (2007)

PRÉSENTÉE LE 13 AVRIL 2007

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

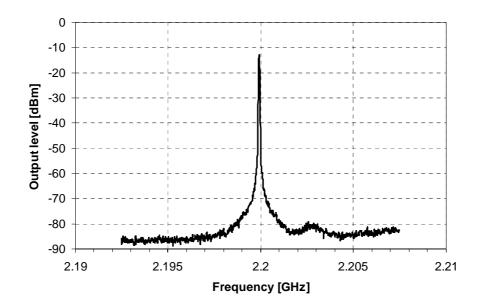

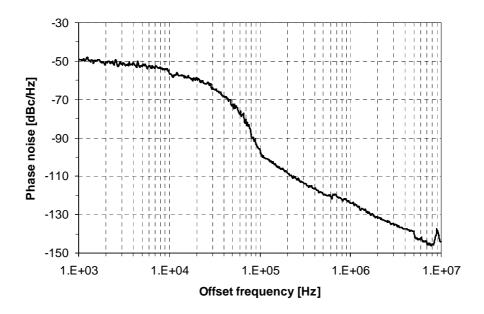

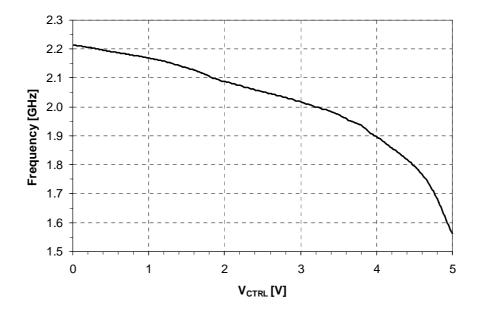

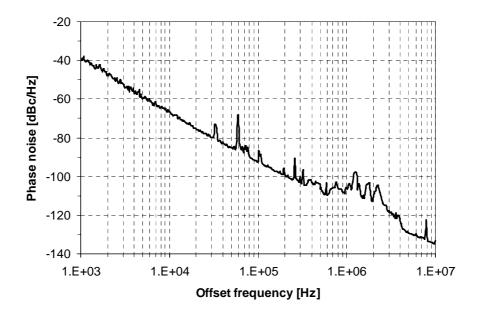

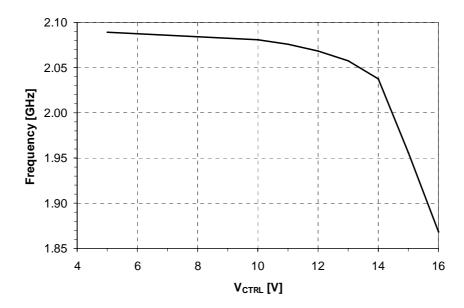

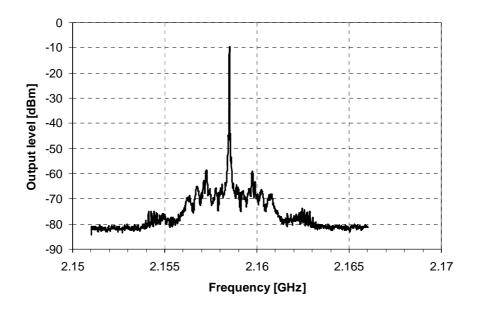

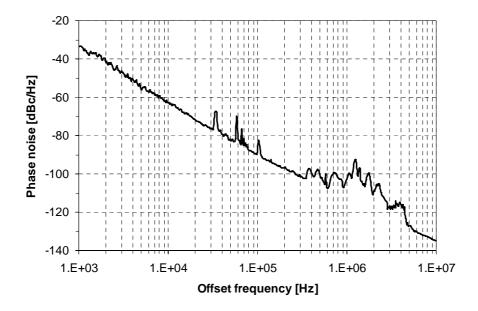

Laboratoire d'électronique générale

SECTION DE GÉNIE ÉLECTRIQUE ET ÉLECTRONIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

#### Raphaël FRITSCHI

ingénieur en microtechnique diplômé EPF de nationalité suisse et originaire de Teufenthal (AG)

acceptée sur proposition du jury:

Prof. M. A. Ionescu, Dr Ph. Flückiger, directeurs de thèse Prof. N. de Rooij, rapporteur Prof. G. Fedder, rapporteur Prof. R. Plana, rapporteur

Science is like sex: sometimes something useful comes out, but that is not the reason we are doing it.

Richard P. Feynman

### **Contents**

| Abstract                                                                | xi   |

|-------------------------------------------------------------------------|------|

| Version abrégée                                                         | xiii |

| Chapter 1 Introduction                                                  | 1    |

| 1.1 MOTIVATION AND SCOPE OF THE THESIS                                  |      |

| 1.2 Organization of this thesis                                         |      |

| Chapter 2 Metal surface micromachining process                          | 7    |

| 2.1 Introduction to silicon micromachining techniques                   |      |

| 2.1.1 History of micromachining                                         | 9    |

| 2.1.2 Surface micromachining                                            |      |

| 2.1.2.1 Basic idea                                                      |      |

| 2.1.2.2 Stiction                                                        | 10   |

| 2.1.2.3 Sacrificial layer materials                                     |      |

| 2.2 THIN FILM SILICON AS A SACRIFICIAL LAYER FOR SURFACE MICROMACHINING | 12   |

| 2.2.1 Isotropic dry etching of silicon                                  | 12   |

| 2.2.1.1 Plasma-free etching in gas phase                                |      |

| 2.2.1.2 Plasma etching                                                  | 12   |

| 2.2.2 Process optimization for SF <sub>6</sub> plasma releasing         | 14   |

| 2.2.2.1 Inductively coupled plasma (ICP) etching equipment              | 14   |

| 2.2.2.2 Design of experiment                                            | 15   |

| 2.2.2.3 Influence of the different parameters                           | 17   |

| 2.2.2.4 Optimized parameters                                            | 25   |

| 2.2.2.5 Releasing of aluminum membranes                                 |      |

| 2.2.3 Comparison with state-of-the-art dry releasing processes          |      |

| 2.3 METAL SURFACE MICROMACHINING FOR ABOVE-IC RF MEMS APPLICATIONS      |      |

| 2.3.1 Choice of materials                                               |      |

| 2.3.1.1 CMOS post-process compatibility                                 |      |

| 2.3.1.2 Structural material                                             |      |

| 2.3.1.3 Silicon sacrificial layer deposition technique                  |      |

| 2.3.1.4 Summary of chosen materials                                     |      |

| 2.3.2 Successive improvements in the fabrication process steps          | 29   |

| 2.3.2.1 Patterning of the a-Si sacrificial layer                        |      |

| 2.3.2.2 Residual stress control in sputtered a-Si sacrificial layer     |      |

| 2.3.2.3 Metal 1-to-Metal 2 via                                          |      |

| 2.3.2.4 CMP planarization of the sacrificial layer                      |      |

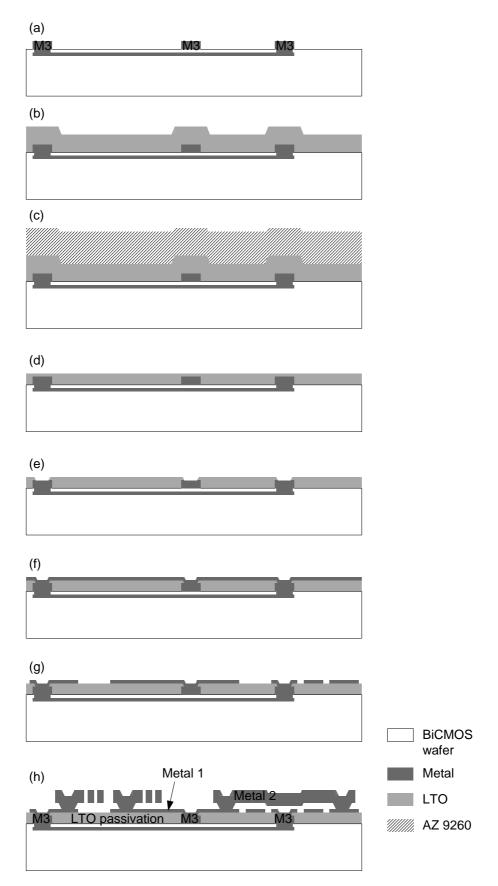

| 2.3.3 Final process flow                                                |      |

| 2.3.4 Characterization of sputtered Al-Si (1%) alloy                    |      |

| 2.3.4.1 Electrical properties extraction                                | 38   |

| 2.      | 3.4.2 Mechanical properties extraction                                                             | 39  |

|---------|----------------------------------------------------------------------------------------------------|-----|

| 2.      | 3.4.3 Summary of sputtered Al-Si (1%) properties                                                   | 42  |

| 2.4     | CONCLUSIONS                                                                                        | 42  |

| Chapter | 3 MEMS tunable capacitors                                                                          | 43  |

| 3.1     | STATE-OF-THE-ART                                                                                   |     |

| 3.1.    |                                                                                                    |     |

| 3.1.2   |                                                                                                    |     |

| 3.1     |                                                                                                    |     |

| 3.      | 1.3.1 Electrostatic actuation                                                                      |     |

| 3.      | 1.3.2 Electro-thermal actuation                                                                    | 51  |

| 3.      | 1.3.3 Piezoelectric actuation                                                                      | 52  |

| 3.1.4   | $\epsilon$                                                                                         |     |

| 3.      | 1.4.1 Electrostatic actuation                                                                      | 53  |

| 3.1.:   | $\mathcal{F}$                                                                                      |     |

| 3.      | 1.5.1 Movable dielectrics                                                                          |     |

|         | 1.5.2 Voltage-tunable ferroelectric thin films                                                     |     |

| 3.1.0   | J                                                                                                  |     |

| 3.2     | SINGLE-AIR-GAP ARCHITECTURE                                                                        |     |

| 3.2.    | 3 - 1 - 1 - 1 - 1 - 2 - 3 - 3 - 3 - 3 - 3 - 3 - 3 - 3 - 3                                          |     |

|         | 2.1.1 Pull-in effect                                                                               |     |

|         | 2.1.2 Release voltage                                                                              |     |

|         | 2.1.3 Equivalent spring constant                                                                   |     |

|         | 2.1.4 Summary of electromechanical design                                                          |     |

| 3.2.2   |                                                                                                    |     |

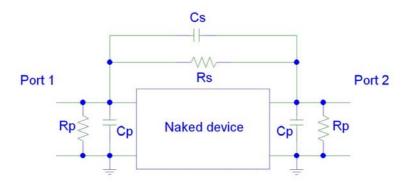

|         | 2.2.1 Equivalent circuit model                                                                     |     |

| 3.2     |                                                                                                    |     |

|         | 2.3.1 S-parameter measurements                                                                     |     |

| 3.3     | 2.3.2 Thermal characterization  Double-air-gap architecture for extended capacitance tuning range. |     |

| 3.3.    |                                                                                                    |     |

|         | 3.1.1 Tuning range                                                                                 |     |

|         | 3.1.2 Summary of electromechanical design                                                          |     |

| 3.3.2   |                                                                                                    |     |

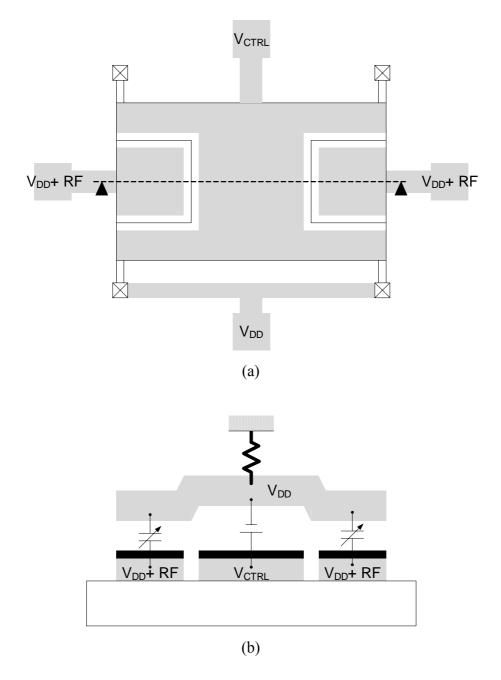

|         | 3.2.1 Biasing configuration                                                                        |     |

|         | 3.2.2 Equivalent circuit model                                                                     |     |

| 3.3.    |                                                                                                    |     |

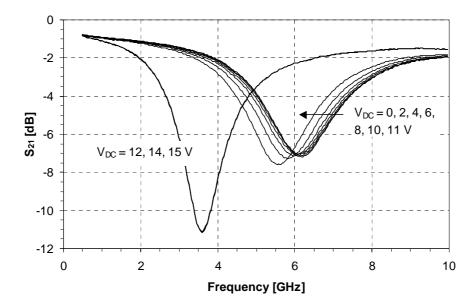

|         | 3.3.1 S-parameter measurements                                                                     |     |

| 3.4     | WAFER-LEVEL PACKAGING                                                                              |     |

| 3.4.    |                                                                                                    |     |

| 3.4.2   | 1 1                                                                                                |     |

| 3.5     | CONCLUSIONS                                                                                        |     |

| Chanter | 4 Voltage-controlled oscillators (VCOs)                                                            | 91  |

| 4 1     | Introduction                                                                                       |     |

| 4.1.    |                                                                                                    | 93  |

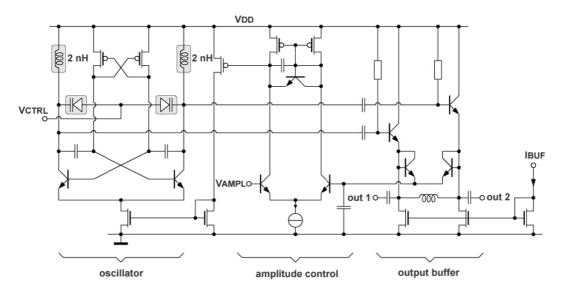

| 4 2     | DESCRIPTION OF THE INTEGRATED CIRCUIT                                                              |     |

| 4.2.    |                                                                                                    |     |

| 4.2.    |                                                                                                    |     |

|         | VCO WITH STANDARD DIODE VARICAPS                                                                   |     |

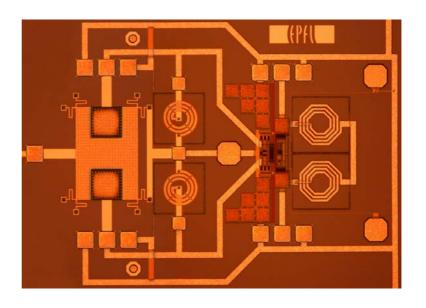

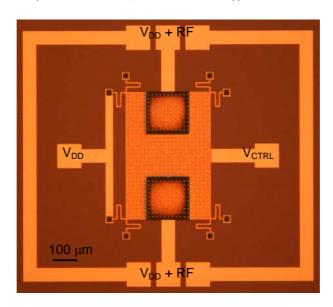

|         | Lavout                                                                                             | 101 |

| 4.3.      |                                                                                                          |     |

|-----------|----------------------------------------------------------------------------------------------------------|-----|

| 4.3       |                                                                                                          |     |

| 4.4       |                                                                                                          |     |

| 4.4.      | J .                                                                                                      |     |

| 4.4.      |                                                                                                          |     |

| 4.5       |                                                                                                          |     |

| 4.5.      | 1 1 1                                                                                                    |     |

|           | 5.1.1 Realization                                                                                        |     |

|           | 5.1.2 RF design                                                                                          |     |

|           | 5.1.3 Characterization                                                                                   |     |

| 4.5.      |                                                                                                          |     |

| 4.5       |                                                                                                          |     |

| 4.5.4     | $\mathcal{C}$ 1 1                                                                                        |     |

|           | 5.4.1 Principle                                                                                          |     |

|           | 5.4.2 Design                                                                                             |     |

| 4.5.:     | · J · · · · · · · · · · · · · · · · · ·                                                                  |     |

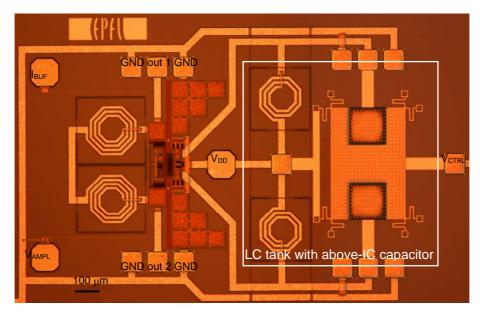

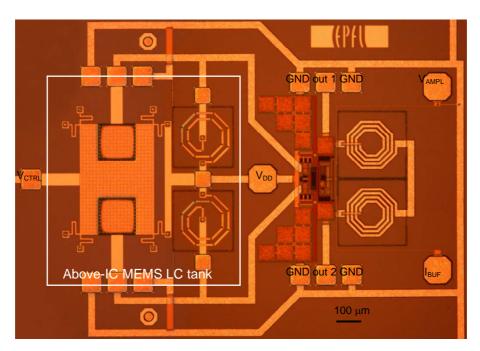

|           | 5.5.1 VCO with X-FAB inductors and above-IC MEMS tunable capacitor 5.5.2 VCO with above-IC MEMS LC tank  |     |

| 4.5.0     |                                                                                                          |     |

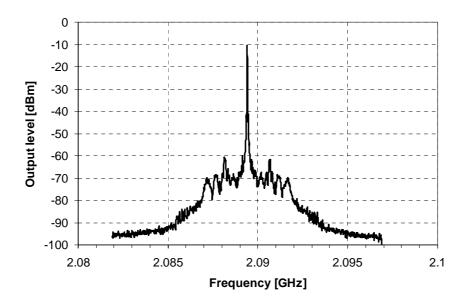

|           | 6 Characterization                                                                                       |     |

|           | 5.6.2 VCO with A-FAB inductors and above-IC MEMS tundole capacitor  5.6.2 VCO with above-IC MEMS LC tank |     |

| 4.6       | SUMMARY OF THE PHASE NOISE PERFORMANCE OF THE DIFFERENT VCOs                                             |     |

| 4.7       | INFLUENCE OF THE POST-PROCESSING ON BICMOS PERFORMANCE                                                   |     |

| 4.7.      |                                                                                                          |     |

| 4.7.      | •                                                                                                        |     |

| 4.8       | Conclusions                                                                                              |     |

|           |                                                                                                          |     |

|           | 5 Capacitive switches and application to V-TTDLs                                                         |     |

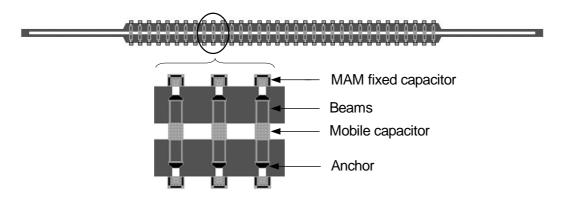

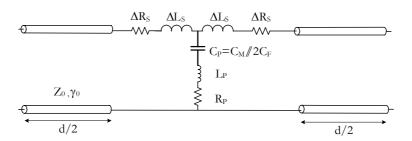

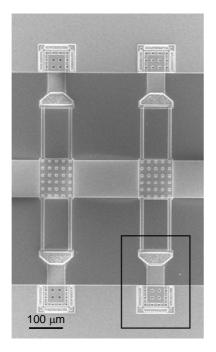

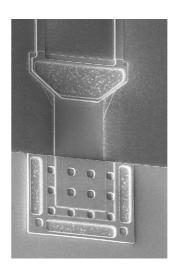

| 5.1       | COPLANAR WAVEGUIDE (CPW) MEMS SHUNT CAPACITIVE SWITCHES                                                  |     |

| 5.1.      |                                                                                                          |     |

| 5.1.2     | 1                                                                                                        |     |

| 5.1       | ~                                                                                                        |     |

| 5.1.4     | r                                                                                                        |     |

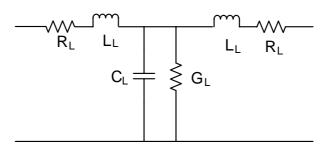

| 5.2       | APPLICATION TO VARIABLE TRUE-TIME DELAY LINES (V-TTDLS)                                                  |     |

| 5.2.      |                                                                                                          |     |

| 5.2.      |                                                                                                          |     |

| 5.2.      | 1                                                                                                        |     |

| 5.3       | Conclusions                                                                                              | 142 |

| Chapter   | 6 Suspended-gate MOSFET (SG-MOSFET)                                                                      | 143 |

| 6.1       | Introduction                                                                                             | 145 |

| 6.2       | ARCHITECTURE AND PRINCIPLE.                                                                              | 145 |

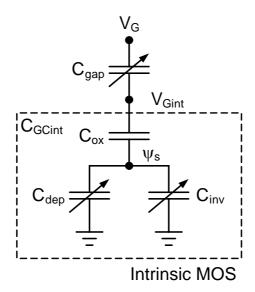

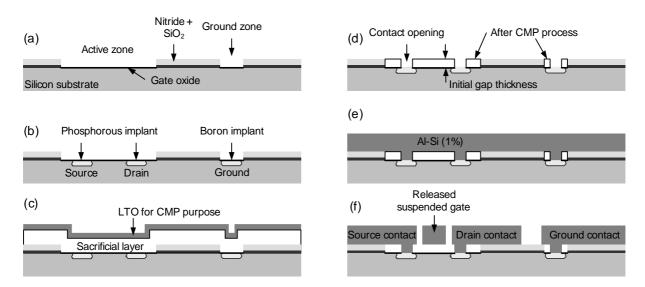

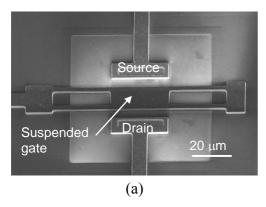

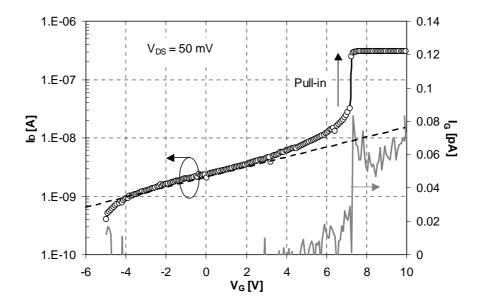

| 6.3       | UNIFIED ANALYTICAL DC MODEL                                                                              | 146 |

| 6.4       | FABRICATION PROCESS.                                                                                     | 149 |

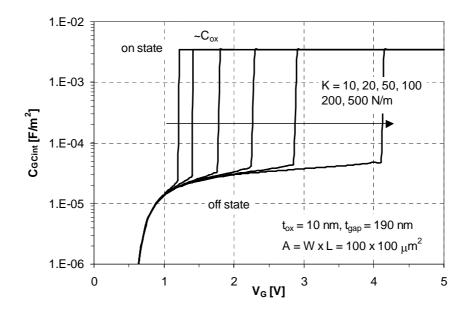

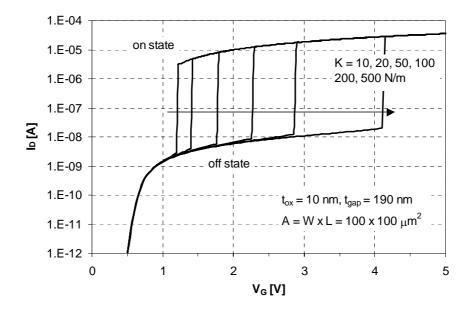

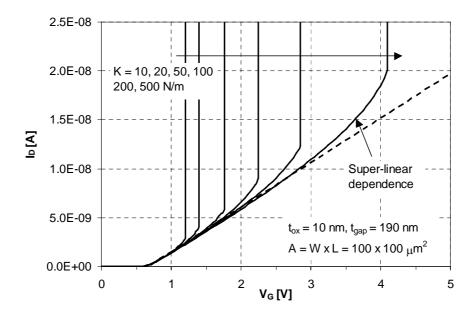

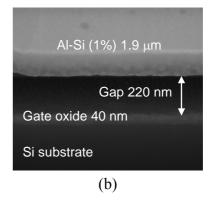

| 6.5       | Experimental results                                                                                     |     |

| 6.6       | CONCLUSIONS                                                                                              | 153 |

| Chapter   | 7 Summary and outlook                                                                                    | 155 |

| 7.1       | SUMMARY OF MAIN ACHIEVEMENTS                                                                             |     |

| 7.1       | OUTLOOK                                                                                                  |     |

|           | es                                                                                                       |     |

| TOTAL CIT | ~ij ••••••••••••••••••••••••••••••••••••                                                                 | ±37 |

#### x CONTENTS

| Acknowledgments  | 171 |

|------------------|-----|

| Curriculum vitae | 173 |

| Publications     | 175 |

#### **Abstract**

Wireless communications are showing an explosive growth in emerging consumer and military applications of radiofrequency (RF), microwave, and millimeter-wave circuits and systems. Applications include wireless personal connectivity (Bluetooth), wireless local area networks (WLAN), mobile communication systems (GSM, GPRS, UMTS, CDMA), satellite communications and automotive electronics.

Future cell phones and ground communication systems as well as communication satellites will require more and more sophisticated technologies. The increasing demand for size and weight reduction, cost savings, low power consumption, increased frequency and higher functionality and reconfigurability as part of multiband and multistandard operation is necessitating the use of highly integrated RF front-end circuits. Chip scaling has made a major contribution to this goal, but today a situation has been reached where the presence of numerous *off-chip* passive RF components imposes a critical bottleneck to further integration and miniaturization of wireless transceivers.

Microelectromechanical systems (MEMS) technology is a rapidly emerging enabling technology that is intended to replace the discrete passives by their integrated counterparts.

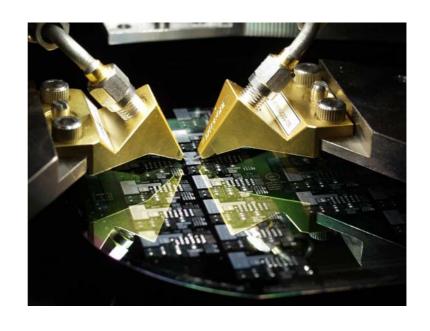

In this thesis, an original metal surface micromachining process, which is compatible with CMOS post-processing, for *above-IC integration* of RF MEMS tunable capacitors and suspended inductors is presented.

A detailed study on  $SF_6$  inductively coupled plasma (ICP) releasing has been performed in order to ascertain the optimal process parameters. This study has emphasized the fact that temperature plays an important role in this process by limiting silicon dioxide etching. Moreover, the optimized recipe has been found to be independent of the sacrificial layer used (amorphous or polycrystalline silicon) and its thickness. Using this recipe, 15.6  $\mu$ m/min Si underetch rate with high Si: SiO<sub>2</sub> selectivity (> 20000: 1) has been obtained.

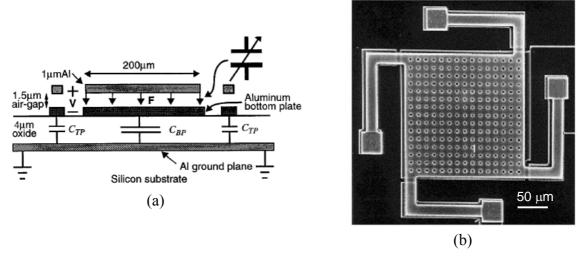

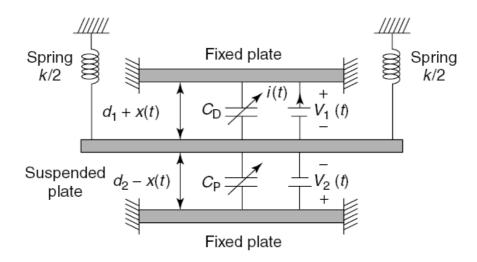

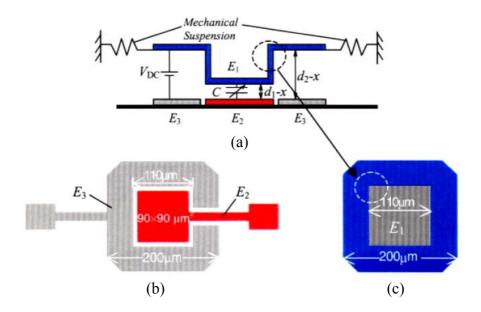

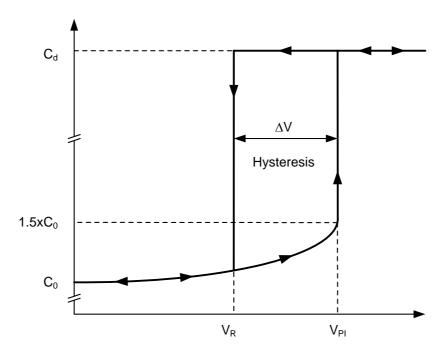

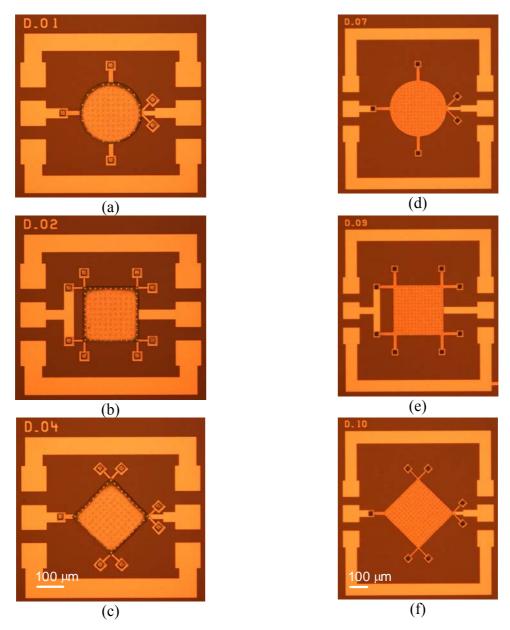

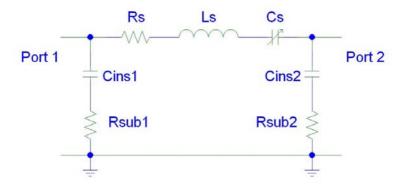

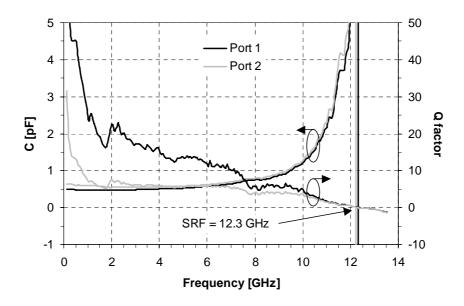

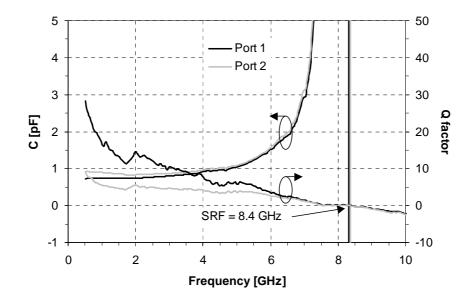

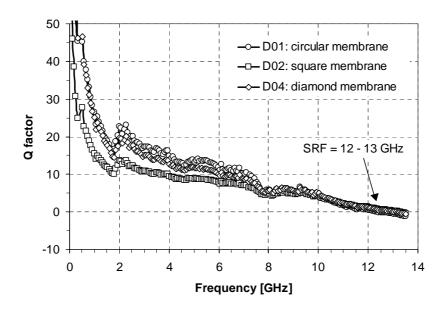

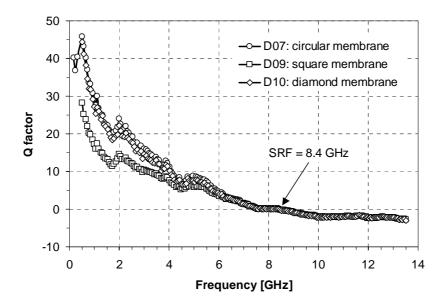

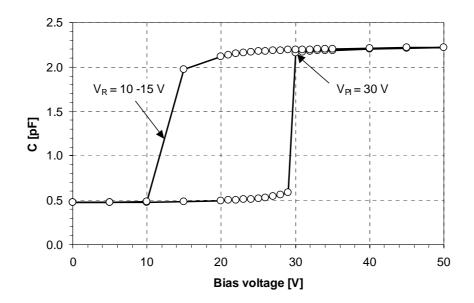

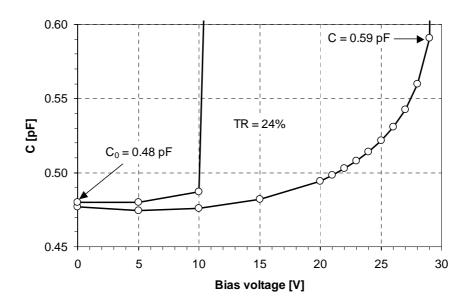

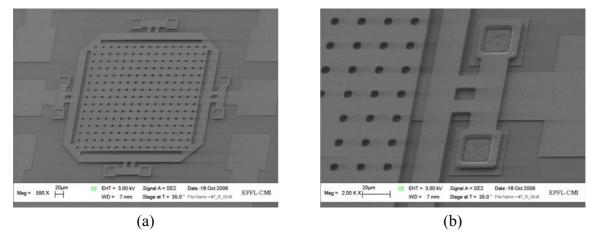

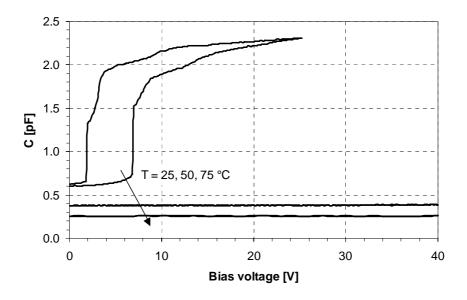

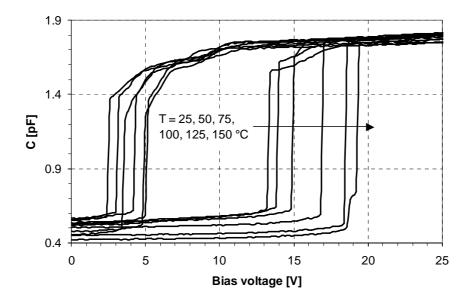

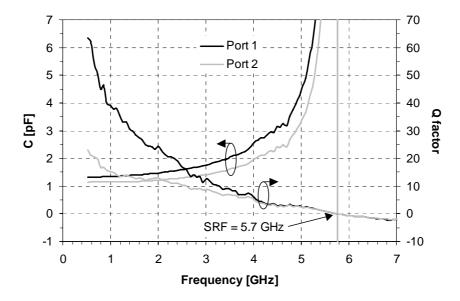

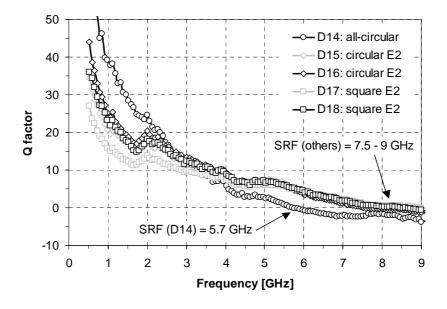

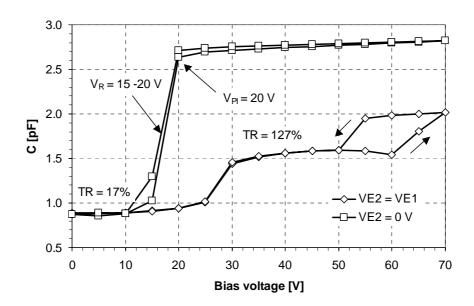

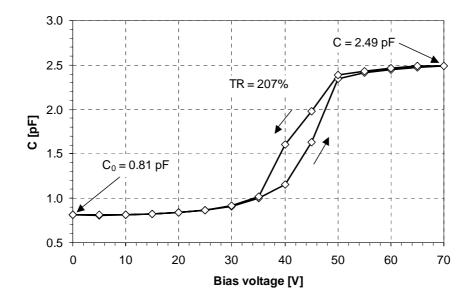

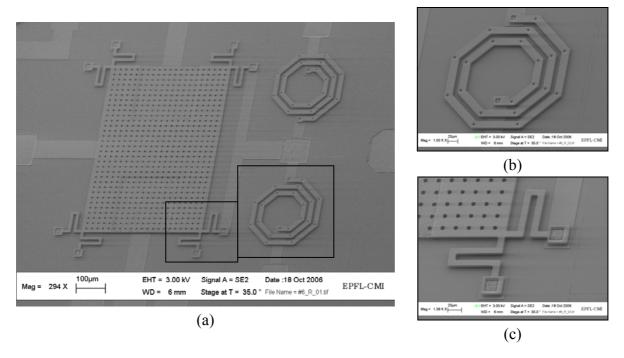

Single-air-gap and double-air-gap parallel-plate MEMS tunable capacitors have been designed, fabricated and characterized in the pF range, from 1 MHz to 13.5 GHz. It has been shown that an optimized design of the suspended membrane and direct symmetrical current feed at both ports can significantly improve the quality factor and increase the self-resonant frequency, pushing it to 12 GHz and beyond. The maximum capacitance tuning range obtained for a single-air-gap capacitor is 29% for a bias voltage of 20 V. The maximum capacitance tuning range obtained for a double-air-gap capacitor is 207% for a bias voltage of 70 V.

#### xii Abstract

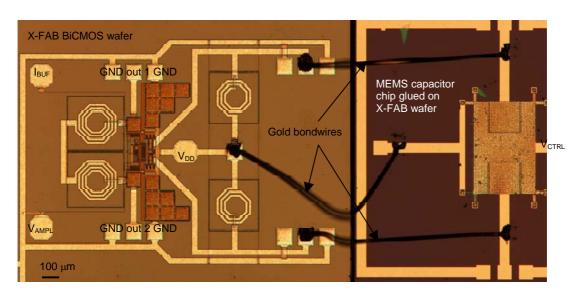

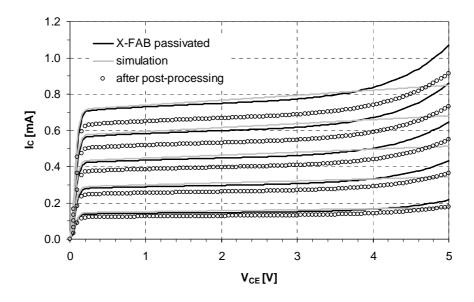

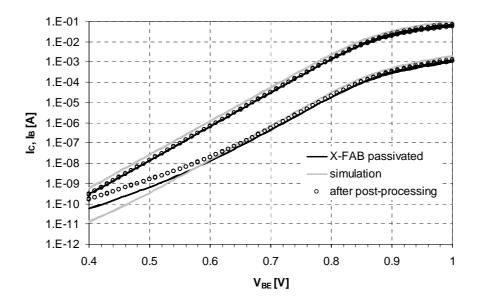

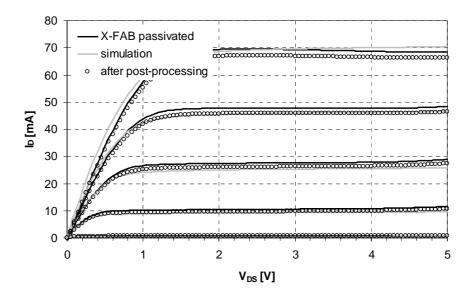

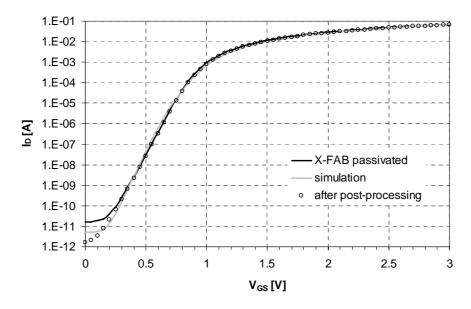

The post-processing of X-FAB BiCMOS wafers has been successfully demonstrated to fabricate monolithically integrated VCOs with above-IC MEMS LC tank. Comparing a suspended inductor and the X-FAB inductor with the same design, it has been shown that increasing the thickness of the spiral from 2.3 to 4  $\mu$ m and having the spiral suspended 3  $\mu$ m above the passivation layers lead to an improvement factor of 2 for the peak quality factor and a shift of the self-resonant frequency beyond 15 GHz. No significant variation on bipolar and MOS transistors characteristics due to the post-processing has been observed and we conclude that the variation due to post-processing is in the same range as the wafer-to-wafer variation.

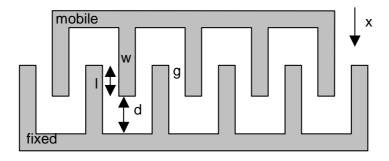

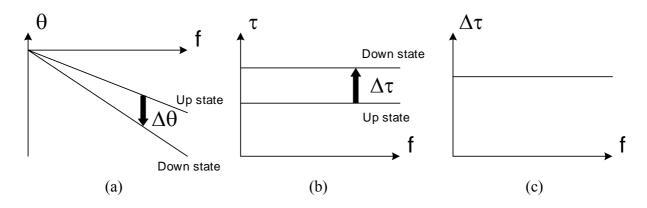

Based on our metal surface micromachining process, coplanar waveguide (CPW) MEMS shunt capacitive switches and variable true-time delay lines (V-TTDLs) have been designed, fabricated and characterized in the 1 - 20 GHz range.

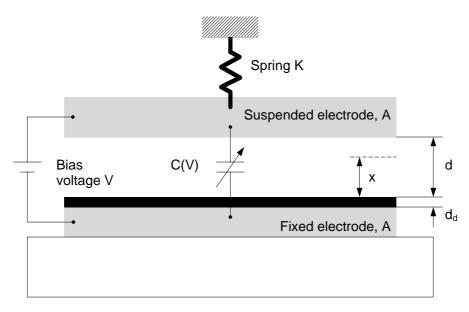

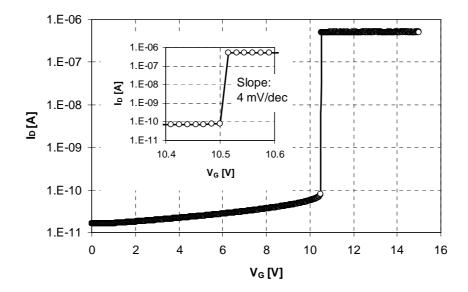

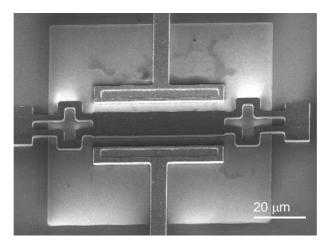

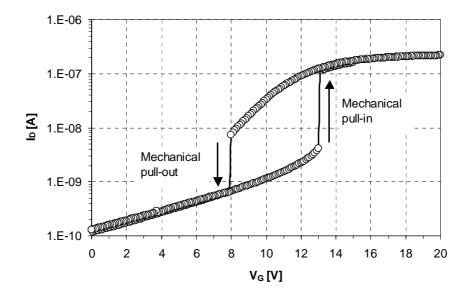

A novel MEMS device architecture: the SG-MOSFET, which combines a solid-state MOS transistor and a metal suspended gate has been proposed as DC current switch. The corresponding fabrication process using polysilicon as a sacrificial layer has been developed to release metal gate suspended over gate oxide by  $SF_6$  plasma. Very abrupt current switches have been demonstrated with subthreshold slope better than 10 mV/decade (better than the theoretical solid-state bulk or SOI MOSFET limit of 60 mV/decade) and ultra-low gate leakage (less than 0.001 pA/ $\mu$ m<sup>2</sup>) due to the air-gap.

#### Keywords:

MEMS tunable capacitors, above-IC integration, metal surface micromachining process, VCOs with above-IC MEMS LC tank, capacitive switches, variable true-time delay lines (V-TTDLs), suspended-gate MOSFET.

#### Version abrégée

Les communications sans fil ont montré une croissance explosive dans les applications grand public et militaires pour des circuits et systèmes radiofréquence (RF), micro-ondes et ondes millimétriques. Ces applications comprennent les objets de communication sans fil personnels (Bluetooth), les réseaux de communication locaux (WLAN), les systèmes de communication mobile (GSM, GPRS, UMTS, CDMA), les communications par satellites et l'électronique pour l'industrie automobile.

Les téléphones mobiles du futur, les systèmes de communication terrestres, aussi bien que satellitaires nécessiteront une technologie de plus en plus sophistiquée. La demande croissante pour la réduction de taille, de poids et de coût, la faible consommation, la fréquence croissante et l'augmentation de la fonctionnalité et de la reconfigurabilité requiert l'utilisation de circuits RF *front-end* à haute densité d'intégration. La réduction de taille des puces électroniques a beaucoup contribué à cette fin, cependant de nos jours, la présence de nombreux composants RF passifs hors-puce ont amené à une limite d'intégration et de miniaturisation pour les émetteurs/récepteurs sans fil.

La technologie MEMS (microsystèmes électromécaniques) est une technologie émergente, sensée remplacer les éléments passifs discrets par des dispositifs intégrés.

Dans cette thèse, un procédé de fabrication par micro-usinage de surface de couches minces métalliques, compatible avec les procédés CMOS, est proposé pour l'intégration monolithique de condensateurs variables MEMS et de bobines suspendues.

Une étude détaillée sur la libération de microstructures par plasma  $SF_6$  ICP a été menée dans le but de définir les paramètres de procédé idéaux. Cette étude a mis à jour le fait que la température joue un rôle important dans ce procédé, en limitant la gravure de l'oxyde de silicium. La recette de gravure optimisée est indépendante de la couche sacrificielle utilisée (silicium amorphe ou polycristallin) et de son épaisseur. En utilisant cette recette, une vitesse de sous-gravure du silicium de  $15.6~\mu m/min$  avec une sélectivité élevée par rapport au  $SiO_2$  (> 20000: 1) a été obtenue.

Des condensateurs variables MEMS à plaques parallèles et simple/double espacement ont été *designés*, fabriqués et caractérisés dans la gamme du pF, de 1 MHz à 13.5 GHz. Il a été démontré qu'un design optimisé de la membrane suspendue et une polarisation en courant directe et symétrique à chaque port permet d'améliorer significativement le facteur de qualité et de repousser la fréquence de résonance au-delà de 12 GHz. Le taux d'accordabilité maximal de la capacité obtenu pour un condensateur à simple espacement est de 29% pour

une polarisation de 20 V. Pour un condensateur à double espacement, ce taux passe à 207% pour une polarisation de 70 V.

Le *post-processing* de plaques X-FAB BiCMOS pour l'intégration monolithique d'oscillateurs contrôlés en tension (VCOs) à circuit résonant MEMS LC *above-IC* a été démontré avec succès. En comparant une bobine suspendue et une bobine X-FAB ayant le même design, il a été montré que le fait d'augmenter l'épaisseur de la spirale de 2.3 à 4 µm et d'avoir la spirale suspendue 3 µm au-dessus des couches de passivation du circuit permet de doubler le maximum du facteur de qualité et de déplacer la fréquence de résonance au-delà de 15 GHz. Aucune détérioration significative des caractéristiques MOS et bipolaire n'a été observée malgré le *post-processing*. Il a été conclu que l'influence du *post-processing* est du même ordre de grandeur que la variation de plaque à plaque.

Sur la base du procédé de fabrication par micro-usinage de surface de couches minces métalliques, des commutateurs capacitifs montés sur guide d'onde coplanaire et des lignes à retard variables (V-TTDLs) ont été *designés*, fabriqués et caractérisés dans la gamme de 1 à 20 GHz.

Une nouvelle architecture de dispositif MEMS: le transistor MOS à grille suspendue (SG-MOSFET) a été proposée comme commutateur de courant DC. Cette architecture combine un transistor MOS et une grille métallique suspendue. Le procédé de fabrication correspondant utilisant le polysilicium comme couche sacrificielle a été développé pour la libération par plasma SF<sub>6</sub> de la grille métallique suspendue sur l'oxyde de grille. Des commutateurs de courant DC avec une pente sous-seuil plus faible que 10 mV/décade (surpassant la valeur théorique limite de 60 mV/décade pour le transistor MOS) et de très bas courants de fuite dans la grille (<  $0.001 \text{ pA}/\mu\text{m}^2$ ) ont été démontrés.

#### Mots-clés:

Condensateurs variables MEMS, intégration monolithique *above-IC*, procédé de fabrication par micro-usinage de surface de couches minces métalliques, oscillateurs contrôlés en tension (VCOs) à circuit résonant MEMS LC *above-IC*, commutateurs capacitifs, lignes à retard variables (V-TTDLs), transistor MOS à grille suspendue.

# Chapter 1 Introduction

Wireless communications are showing an explosive growth in emerging consumer and military applications of radiofrequency (RF), microwave, and millimeter-wave circuits and systems. Applications include wireless personal connectivity (Bluetooth), wireless local area networks (WLAN), mobile communication systems (GSM, GPRS, UMTS, CDMA), satellite communications and automotive electronics.

Future cell phones and ground communication systems as well as communication satellites will require more and more sophisticated technologies. The increasing demand for size and weight reduction, cost savings, low power consumption, increased frequency and higher functionality and reconfigurability as part of multiband and multistandard operation is necessitating the use of highly integrated RF front-end circuits. Chip scaling has contributed a lot to this goal, but today a situation has been reached where the presence of numerous *off-chip* (or discrete) passive RF components such as high-Q inductors, ceramic and SAW filters, quartz-crystal reference resonators, diode varicaps and GaAs PIN diode or FET switches imposes a critical bottleneck against further integration and miniaturization of wireless transceivers [1, 2].

Microelectromechanical systems (MEMS) technology is a rapidly emerging enabling technology that can replace the discrete passives by their integrated counterparts. RF MEMS components that are currently under development in laboratories around the world include switches, high-Q voltage-tunable capacitors, high-Q micromachined inductors, thin film bulk acoustic resonators (FBARs), transmission line resonators, micromechanical resonators and filters and micromachined antennas [3-5].

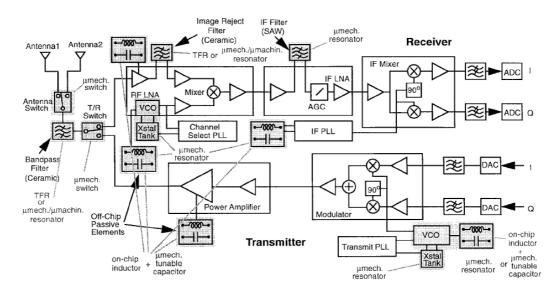

RF MEMS can be used for switching, frequency selection in RF and IF filter stages, tuning and matching in RF front-end in wireless transceivers (Figure 1.1), and further, in switched-line phase shifters used in radar systems.

Figure 1.1 System-level schematic detailing the front-end design for a typical wireless transceiver. The off-chip high-Q passive components targeted for replacement with micromechanical versions (suggestions in lighter ink) are indicated by shading. From [1].

#### 4 Introduction

The integration of MEMS can either be achieved by hybrid or monolithic approach, leading to a system-in-package (SiP) or a system-on-chip (SoC) solution, respectively.

In SiP, passive and active components are integrated at the package level using technologies like low-temperature co-fired ceramic (LTCC) technology [6, 7] or multi-layer thin-film multi-chip module (MCM-D) technology [8].

In SoC, the MEMS devices are directly fabricated on IC wafers. Several approaches have be reported. The first one is based on post-CMOS fabrication steps for releasing micromechanical structures made of stack of oxide, aluminum and poly-Si layers [9, 10]. The second approach is called *above-IC integration* and involves a complete surface micromachining process on top of ICs. This has already been applied to monolithically integrate RF MEMS switches [11, 12] and thin-film bulk acoustic resonators (FBAR) [13] with ICs. In the third one, called *in-IC integration*, the micromechanical structures are fabricated in parallel at the same level as the transistors, the thin silicon-on-insulator (SOI) layer playing the structural role. With this approach thin-SOI NEMS accelerometers have been built [14]. The fourth one is called *MEMS-first* approach. The micromachined structures are fabricated on SOI wafers and vacuum-encapsulated in epitaxially-sealed (epitaxially-grown polycrystalline and single-crystal silicon) chambers buried under the wafer surface and then CMOS process can be performed on single-crystal silicon [15, 16].

In order to follow the electronic system demands on scaling, performance and functionality, 3D integration is gaining more and more interest. This is particularly the case of 3D stacked SoC [17, 18] which allows the heterogeneous integration of different optimized technologies, such as silicon, compound semiconductors and other substrates, MEMS and integrated passive devices, with 3D interconnects to meet the specifications for radio, analog, logic, memory, etc. and reach the desired performance levels and circuit density.

#### 1.1 MOTIVATION AND SCOPE OF THE THESIS

The starting point of this thesis was to develop RF MEMS passives (with main focus on capacitors) integrable with advanced CMOS RF ICs. Then emerged the idea of using thin film silicon as a sacrificial layer for low-temperature surface micromachining and hence release the micromechanical structures by SF<sub>6</sub> plasma.

Based on that, a surface micromachining process has been developed with two main constraints. First, the fabrication process should be compatible with CMOS post-processing and second, it aims at fabricating radiofrequency (RF) MEMS electrostatically-actuated capacitive membrane-based devices for *above-IC integration*.

Two European projects, WIDE-RF "Innovative MEMS Devices for Wideband Reconfigurable RF Microsystems" (IST-2001-33286) and integrated project MIMOSA "Microsystems Platform for Mobile Services and Applications" (IST-2002-507045), have been the driving forces of the work presented in this thesis.

In particular, the choice of MEMS tunable capacitors and capacitive switches as targeted devices has led to two circuit demonstrators: voltage-controlled oscillators (VCOs) and variable true-time delay lines (V-TTDLs). Both involve a strong collaboration with colleagues

in our lab and in the Laboratory of Electromagnetism and Acoustics (EPFL-LEMA), respectively.

The initial idea also helped a lot in developing the novel suspended-gate MOSFET (SG-MOSFET) architecture.

#### 1.2 ORGANIZATION OF THIS THESIS

This introduction is the first of seven chapters included in this thesis manuscript.

Chapter 2 begins with an introduction to silicon micromachining techniques with more emphasis on surface micromachining. It describes a study on SF<sub>6</sub> inductively coupled plasma (ICP) releasing for silicon thin film sacrificial layer. It details the chronological improvements that have been brought to the fabrication process based on the SF<sub>6</sub> plasma releasing, leading to a metal surface micromachining process compatible with CMOS post-processing for above-IC integration of radiofrequency (RF) MEMS devices. It also presents the extraction of the electrical and mechanical properties of the sputtered Al-Si (1%) alloy used.

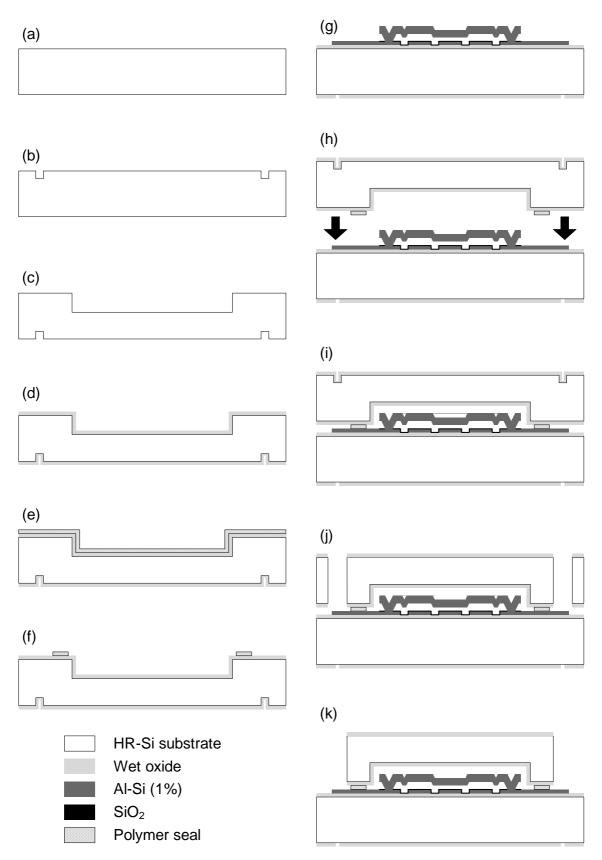

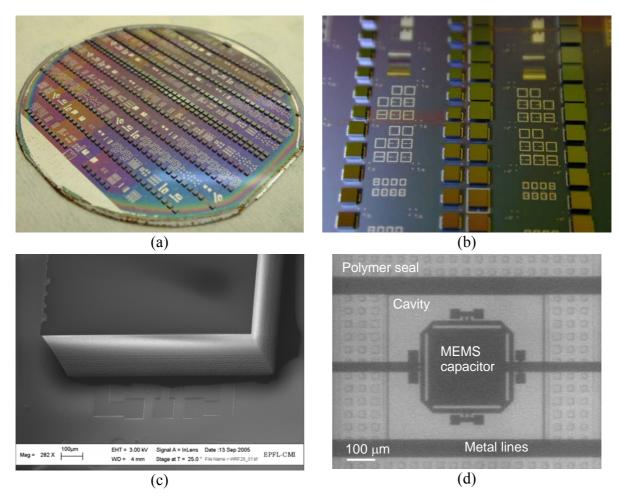

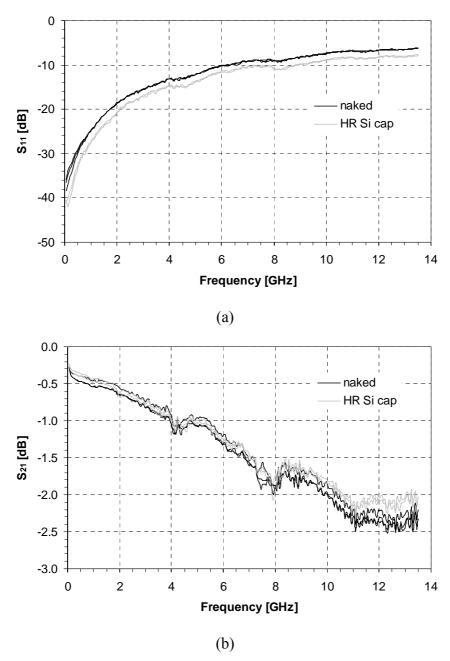

Chapter 3 contains a review of MEMS tunable capacitors classifying them according to their tuning principle, such as gap tuning, area tuning and relative permittivity tuning. Then it describes two architectures of electrostatic gap-tuning capacitors based on the metal surface micromachining process described in chapter 2: the standard single-air-gap parallel-plate structure and the double-air-gap architecture for extended capacitance tuning range. The electromechanical and RF designs as well as the RF, electromechanical and thermal characterizations are presented. Finally, a wafer-level packaging technique and its effect on RF performance is described.

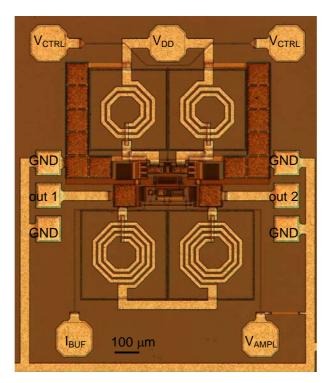

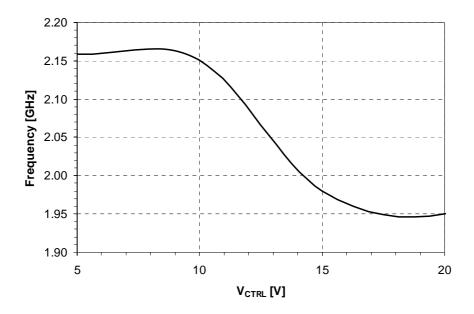

Chapter 4 focuses on voltage-controlled oscillators (VCOs) designed in X-FAB 0.6-µm BiCMOS process. Different realizations of the LC tank are presented and characterized. First with standard diode varicaps and then with wire-bonded MEMS tunable capacitor. The realization and characterization of suspended planar spiral inductors fabricated by surface micromachining and the post-processing of BiCMOS wafers are then described as preliminary steps in realizing the VCO demonstrator with above-IC MEMS LC tank. The third realization involves X-FAB spiral inductors and above-IC *two-in-one* double-air-gap capacitor. The last one is a VCO with above-IC MEMS LC tank. The influence of the post-processing on BiCMOS performance is evaluated by measuring the effect on bipolar and MOS transistors characteristics.

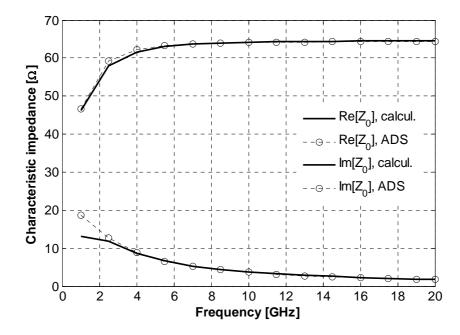

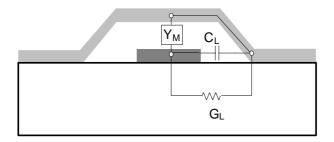

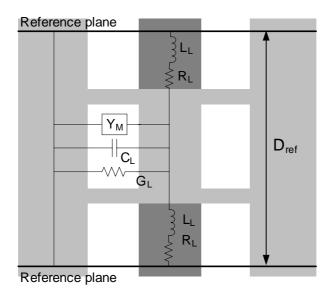

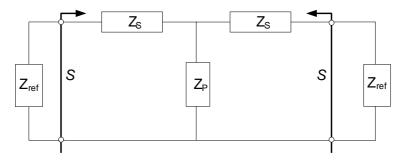

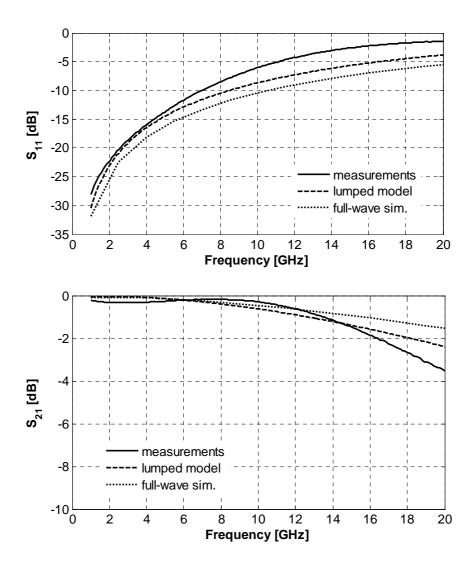

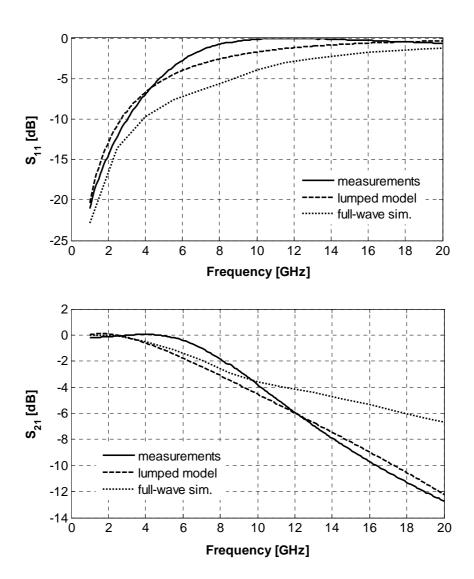

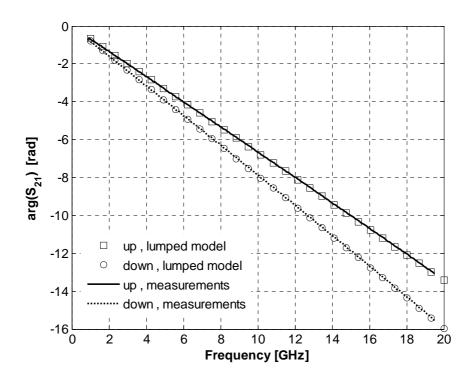

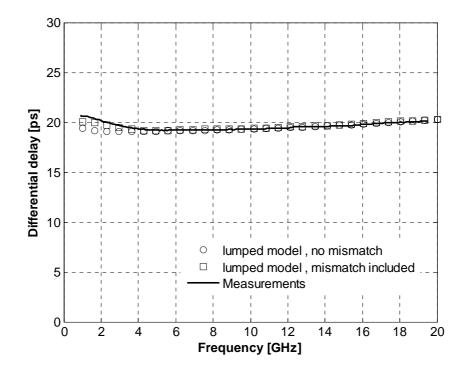

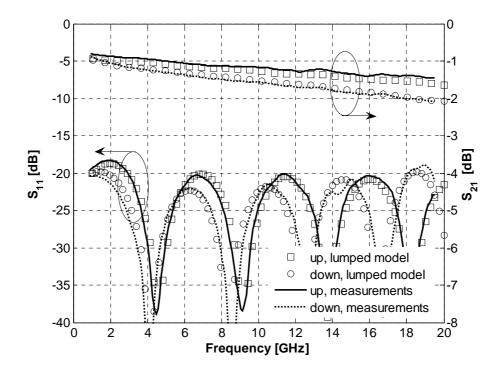

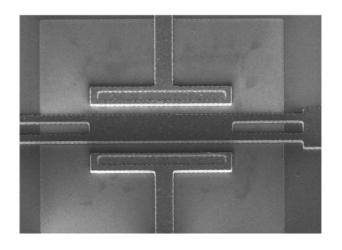

In chapter 5, the fabrication process is used to build coplanar waveguide (CPW) MEMS shunt capacitive switches. A lumped-element circuit model is presented and compared to EM full-wave simulation and measurements. In the second part of this chapter, these switches are used as distributed loading capacitors in variable true-time delay lines (V-TTDLs).

Chapter 6 deals with a novel MEMS device architecture: the suspended-gate MOSFET (SG-MOSFET), which combines a solid-state MOS transistor and a metal suspended gate. A unified analytical model is developed and used to investigate main electrostatic characteristics. In the fabrication process, polysilicon is used as a sacrificial layer for releasing the metal gate. Finally, its potential application as DC current switch is proposed.

#### 6 Introduction

Chapter 7 is a summary of the work presented in this thesis and gives a short outlook on possible and interesting future research activities in the field of above-IC RF MEMS devices for communication applications.

# Chapter 2 Metal surface micromachining process

# 2.1 INTRODUCTION TO SILICON MICROMACHINING TECHNIQUES

#### 2.1.1 History of micromachining

There has been activity in silicon-based micromachining since the early 1960's, when the integrated circuit (IC) technology was developed. Photolithography is used to define patterns that are subsequently *selectively* etched in chemical processing steps to define the geometries of thin films deposited on the substrate. This sequence of steps is repeated to produce electronic integrated circuits and this is known as the *planar* process developed in the 1960's [19-21].

Two basic methods have evolved from this process to fabricate micromechanical structures, which we call now *microelectromechanical systems* (MEMS). One method builds the mechanical parts by anisotropically etching the bulk silicon substrate, it is therefore called *bulk micromachining* [22]. A second technique uses deposited films to make the mechanical parts extending above the surface of the silicon substrate; this technique is called *surface micromachining*. To make a mechanical part from the deposited layer material, an underlying *sacrificial layer* is *selectively* etched, thus releasing the element except where it is anchored to the substrate.

The surface micromachining concept was demonstrated in the mid-1960's by Nathanson *et al.* at Westinghouse Research Laboratory using a freestanding gold cantilever beam as *resonant gate* for a field-effect transistor (FET) [23]. In the early 1980's, Howe and Muller at the University of California, Berkeley, first fabricated polycrystalline silicon (poly-Si) microstructures using a silicon dioxide sacrificial layer [24, 25]. Unlike the resonant-gate transistor work on metal structures, poly-Si surface micromachining was quickly recognized as a promising technology and employed at both academic and industrial laboratories. The review paper by Petersen in 1982 [26] helped in gaining a larger acceptance of micromachined silicon as a structural material. Since then, many new surface micromachining techniques have been developed, leading to a great variety of possible structural and sacrificial layer systems.

#### 2.1.2 Surface micromachining

#### 2.1.2.1 Basic idea

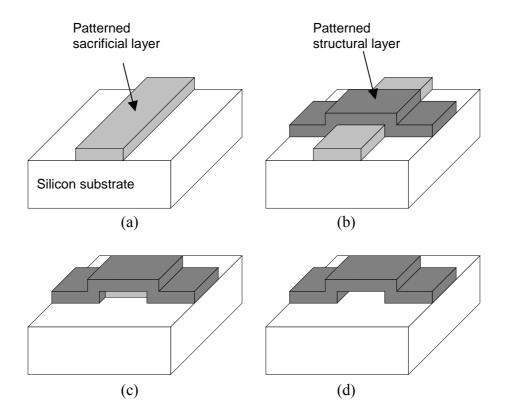

The basic idea of surface micromachining is illustrated by the fabrication steps described in Figure 2.1. The first step is the deposition and patterning of the sacrificial layer. This is followed by the deposition and patterning of the structural layer. Next, the sacrificial layer is selectively etched. The last steps, rinsing and drying procedures, depend on the sacrificial layer etching technique being employed.

Figure 2.1 Basic process scheme of surface micromachining: (a) deposition and patterning of the sacrificial layer, (b) deposition and patterning of the structural layer, (c) sacrificial layer selective etching, (d) rinsing and drying procedures (if needed). Adapted from [20].

#### 2.1.2.2 Stiction

Stiction of thin films occurs after releasing with wet chemical etchants. Two different mechanisms play a role in stiction [27]. First, a temporary physical contact between surface micromachined structures and the substrate is induced by capillary forces during drying of the rinse liquid. After this, permanent attachment is caused by van der Waals forces and hydrogen bridges which are induced by the small separation distance during this contact.

Several methods have been investigated to prevent or reduce stiction. The released structures can be freeze-dried using isopropyl alcohol (IPA) and cyclohexane [28], dried with a supercritical CO<sub>2</sub> technique [29] or dried by coating the released microstructures with hydrophobic self-assembled monolayer (SAM) films prior to removal from aqueous stage [30]. Another method is to temporary increase the mechanical stiffness of the structure. It has been demonstrated for SiO<sub>2</sub> sacrificial layer. A portion of the oxide layer can be substituted by a spun-on polymer spacer after a partial etch of the oxide. After completion of the sacrificial etching, the polymer spacer prevents collapse during evaporative drying. Last, an isotropic oxygen plasma etches the polymer to release the structure [31].

Released-induced stiction can also be completely avoided by using plasma or gas phase etching techniques (see next paragraph and section 2.2).

#### 2.1.2.3 Sacrificial layer materials

Three types of sacrificial layer materials are briefly described.

#### Silicon dioxide sacrificial layer

Since the early 1980's, silicon dioxide sacrificial layer [32] have been widely used notably in combination with poly-Si [24, 25] or poly-SiGe [33] structural layer. As polycrystalline silicon is typically deposited using gas-phase decomposition of silane (SiH<sub>4</sub>) in a low pressure chemical vapor deposition (LPCVD) furnace at about 600 °C, it is not compatible with other sacrificial materials.

Silicon dioxide can be deposited by several techniques such as LPCVD or plasma enhanced CVD (PECVD) using silane or tetraethosiloxane (for tetraethyl orthosilicate (TEOS) oxide) as reactant gas.  $SiO_2$  layers are isotropically etched in wet hydrofluoric (HF) acid solutions (such as HF/H<sub>2</sub>0, buffered HF (BHF), or HNO<sub>3</sub>/HF mixtures) or by HF vapor phase etching (VPE) [34]. All these solutions exhibit very poor selectivity to aluminum. Selective releasing of aluminum MEMS has been demonstrated by using *Pad-etch* solution, which is a mixture of ammonium fluoride (NH<sub>4</sub>F), acetic acid (CH<sub>3</sub>COOH), ethylene glycol (C<sub>2</sub>H<sub>6</sub>O<sub>2</sub>) and water [32].

By repeating the basic sacrificial oxide and structural polysilicon fabrication steps, one can build extremely complex structures. Examples are the Sandia Ultra-planar, Multi-level MEMS Technology 5 (SUMMiT V) fabrication process [35] and the Multi-User MEMS Processes (MUMPs) [36].

#### Polymer sacrificial layer

Polymer sacrificial layers such as polyimide can be isotropically etch in oxygen plasma in barrel reactors. Polyimide has a glass transition temperature comprised between 290 and 400 °C (depending of the series [37]) and hence has been used for releasing materials deposited at low temperature such as physical vapor deposited (PVD) metals [38-40] and sputtered silicon [41, 42].

Another example of polymer sacrificial layer is polystyrene [43]. With this method, SU-8 microstructures have been released by dissolving polystyrene in toluene.

#### Metal sacrificial layer

The use of metal sacrificial layer has been reported in combination of other metals as structural layer, for example in [44] where copper is selectively wet etched on substrates with Ni-Fe alloy (Permalloy) and gold.

IC standard aluminum metallization can also be used as a sacrificial layer for releasing dielectrics microstructures [45].

## 2.2 THIN FILM SILICON AS A SACRIFICIAL LAYER FOR SURFACE MICROMACHINING

In the previous section, it has been clearly shown that a dry releasing step can eliminate the release-induced stiction problem and therefore leads to an increased yield for the overall MEMS process.

Based on EPFL-CMI experience on deep anisotropic silicon etching with high etch rate and commercially available high-density ICP etch equipments, we have investigated the use of silicon thin film as sacrificial layer for surface micromachining.

#### 2.2.1 Isotropic dry etching of silicon

Silicon can be etched in fluorine- and chlorine-based plasma or gas phase etching [46]. Chlorine-based plasma is not relevant for releasing because the etching is not spontaneous. It is only used for anisotropic etching.

#### 2.2.1.1 Plasma-free etching in gas phase

For plasma-free dry etching, the etch gases must provide both the elements that form the desorbable products and strong oxidizing agents. These demands are satisfied by halogen compounds [47]: noble gas fluorides, such as XeF<sub>2</sub>, and halogen fluorides, such as ClF<sub>3</sub> [48] and BrF<sub>3</sub> [49, 50].

Among them, xenon difluoride has been extensively investigated [51-59]. XeF<sub>2</sub> has the capability at room temperature to spontaneously etch silicon at significant rates without requiring a plasma to generate reactive species. Practically, the process is a pulsed etching: the duration of the etch is controlled by the number of cycles. A cycle consists of exposing the wafer to XeF<sub>2</sub> at its room temperature equilibrium pressure, followed by pumping down the chamber. The etch rate has been reported to be extremely load-dependent [52] and the limiting step in the etching process appears to be the supply of fluorine atoms to the reaction site [53]. XeF<sub>2</sub> alone does not etch silicon dioxide and nitride, but can etch these dielectrics in presence of ion or electron bombardment and under UV irradiation. This may help to explain why fluorine atoms are non selective in standard plasma processes [54]. Commercial XeF<sub>2</sub> etchers are now available [60]. Moreover, as XeF<sub>2</sub> etching is a room temperature process, it can be used to release polymer microstructures.

#### 2.2.1.2 Plasma etching

Sulfur hexafluoride (SF<sub>6</sub>) is the preferred plasma etchant for isotropic etch of silicon [61]. It has been widely used in deep anisotropic silicon etching in conjunction with a passivation gas, like  $C_4F_8$ , in the so-called Bosch process [62], or  $O_2$ , in the cryogenic process [63].

The basic chemical reactions that occur in  $SF_6$  plasma are as following [64]:

Dissociation

$$e^{-} + SF_{6} \rightarrow SF_{5} + F + e^{-}$$

(2.1)

$e^{-} + SF_{5} \rightarrow SF_{4} + F + e^{-}$  (2.2)

$e^{-} + SF_{4} \rightarrow SF_{3} + F + e^{-}$  (2.3)

Ionization  $e^{-} + SF_{6} \rightarrow SF_{5}^{+} + F + 2 e^{-}$  (2.4)

$e^{-} + SF_{6} \rightarrow SF_{3}^{+} + F_{2} + F + e^{-}$  (2.5)

$e^{-} + SF_{4} \rightarrow SF_{3}^{+} + F + e^{-}$  (2.6)

Attachment  $e^{-} + SF_{6} \rightarrow SF_{5}^{-} + F$  (2.7)

$e^{-} + SF_{4} \rightarrow SF_{3}^{-} + F$  (2.8)

$e^{-} + SF_{4} \rightarrow SF_{3}^{+} + F + 2 e^{-}$  (2.9)

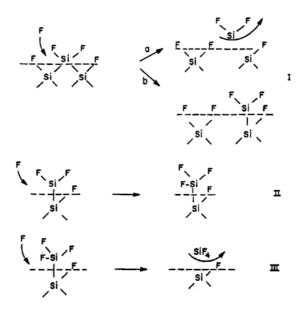

When silicon is exposed to atomic fluorine, it quickly forms a fluorinated *crust* that extends about 5 monolayers into the bulk. Evidence suggests that F atoms penetrate the top of this layer and attack subsurface Si-Si bonds, releasing silicon in the form of two gaseous desorption products: a free radical SiF<sub>2</sub> and the stable volatile product SiF<sub>4</sub> (Figure 2.2) [46].

Figure 2.2 Mechanism of silicon etching by fluorine. Reaction results in the formation of gaseous  $SiF_2$  (Ia) and bound fluorosilicon radicals (Ib) that are fluorinated further to form higher  $SiF_x$  products. From [46].

SF<sub>6</sub> isotropic etch has been also used as a post-CMOS fabrication step for releasing micromechanical structures made of stack of oxide, aluminum and poly-Si layers [65, 66].

#### 2.2.2 Process optimization for SF<sub>6</sub> plasma releasing

Both sputtered amorphous and LPCVD polycrystalline silicon thin films are investigated in this study because they are directly linked to two different applications of interest. Sputtered amorphous silicon (a-Si) is an interesting candidate for use as sacrificial layer in aluminum membrane-based MEMS devices such as MEMS tunable capacitors (see section 2.3 and chapter 3) and capacitive switches (see chapter 5), while LPCVD polycrystalline silicon (poly-Si) is of interest in the suspended-gate MOSFET (SG-MOSFET) (see chapter 6).

The key challenge was to improve the releasing step by obtaining a high aspect ratio (i.e. length-to-thickness ratio), a maximal etch rate of the Si sacrificial layer and a high selectivity to silicon dioxide.

The experiments have been performed in a high-density ICP etcher (Alcatel 601E, now Adixen AMS 200DSE) taking advantage of the independent control of radicals, ion flux and chuck temperature. Etching was performed using pure sulfur hexafluoride (SF<sub>6</sub>), which is commonly used to achieve deep anisotropic silicon etching with high etch rate, high uniformity ( $\pm$  5%) and high Si: SiO<sub>2</sub> selectivity (more than 150: 1). However, by increasing chemical etching and limiting physical etching, underetching of thin silicon layer with high selectivity to SiO<sub>2</sub> can also be performed in ICP etcher.

#### 2.2.2.1 Inductively coupled plasma (ICP) etching equipment

The Alcatel 601E machine belongs to a new generation of dry etching equipment with high performance, thanks to the combination of the latest technologies:

- ICP type plasma (inductively coupled plasma);

- Substrate holder which can be biased and temperature controlled (cryogenic and tunable from room temperature down to -170 °C);

- Powerful pumping systems which lead to high secondary vacuum and the possibility of working with high gas flow rates while maintaining low pressure.

Compared to reactors with capacitive coupling (commonly named RIE: reactive ion etching), this type of machine has the following advantages:

- The possibility of biasing the substrate holder independently of inductive plasma creation;

- The generation of low pressure (0.5 to 10 Pa) high density (10<sup>10</sup> to 10<sup>12</sup> cm<sup>-3</sup>) plasma without sputtering of the reactor walls.

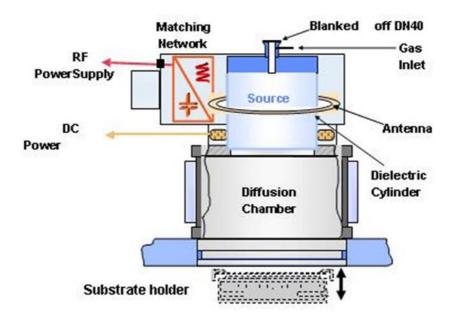

The Alcatel 601E reactor consists of the ICP source, the diffusion chamber, the cryogenic substrate holder, the pumping system and the gas inlet (Figure 2.3).

The ICP source is composed of an antenna connected to a RF generator and wrapped around a dielectric (alumina) cylinder. The RF generator energy is inductively coupled to the plasma. The alternative current (13.56 MHz) in the antenna induces an electromagnetic field inside the alumina cylinder and primary, sufficiently mobile, electrons can acquire energy (heavy ions cannot follow the electromagnetic field oscillations). These energetic electrons generate ions/electrons pairs by inelastic collisions with neutrals. A DC coil, 12 V biased, also surrounds the alumina cylinder and generates a magnetic field to confine the plasma and limit electrons losses on the walls.

The diffusion chamber is placed between the ICP source and the substrate holder and plays the role of a buffer zone to increase plasma uniformity. A permanent magnetic field is generated by magnets to limit losses at the walls and maintain plasma density.

The cryogenic substrate holder temperature can be controlled between -170 °C and room temperature by combining a liquid nitrogen circulation and discrete resistances, whose supply is controlled by a PID regulator. The wafer is fixed by mechanical clamping and the energy transfer between the substrate holder and the wafer is made by an helium film, whose pressure is adjustable. The substrate holder can be biased by a RF generator (13.56 MHz or pulsed low frequency), which allows to control the mean energy of ions during etching.

Figure 2.3 Synoptic view of the Alcatel 601E (now Adixen AMS 200DSE) ICP etching equipment.

Two Alcatel 601E etchers have been used to extend the available range of process parameters: the one at EPFL-CMI, and the other at GREMI lab in Orléans, France.

#### 2.2.2.2 Design of experiment

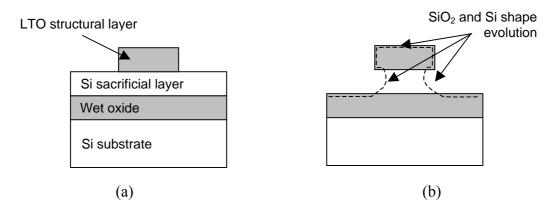

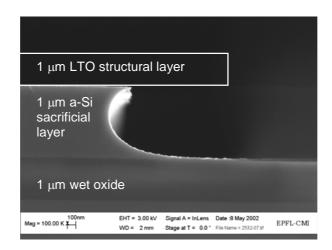

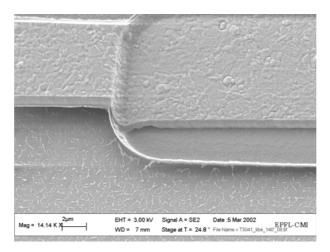

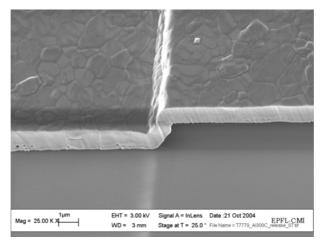

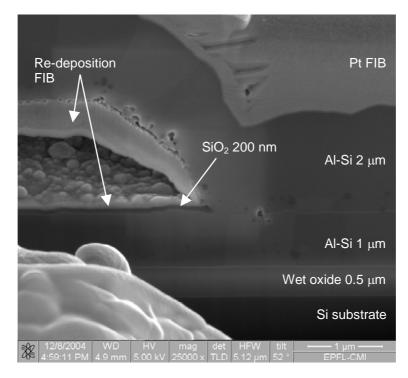

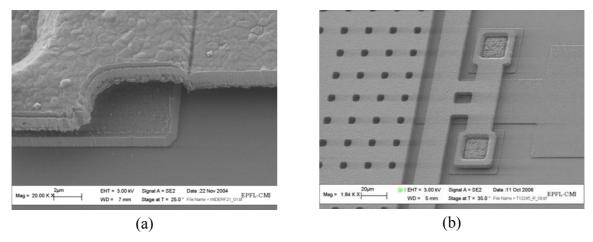

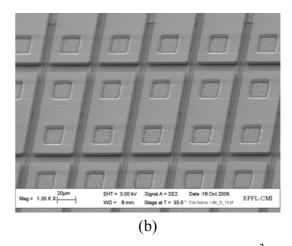

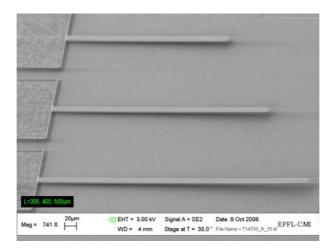

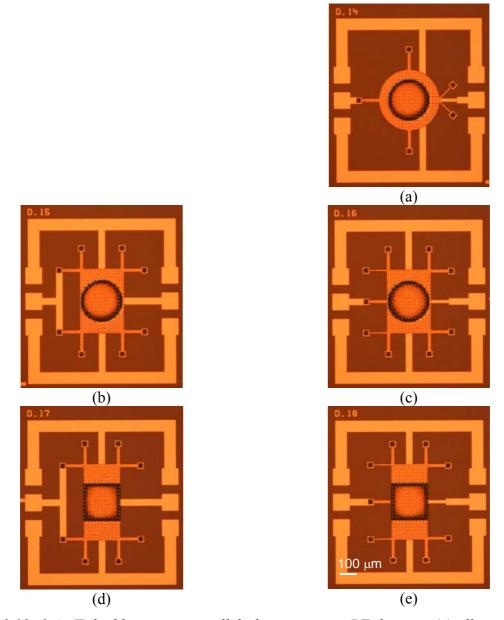

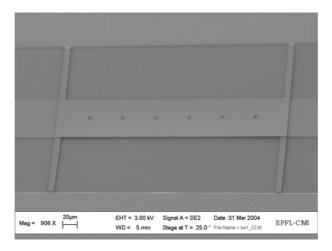

To investigate sacrificial layer etching, simple test structures have been designed: squares, square openings, trenches, circles and crosses, whose lateral dimensions are 2, 5, 10, 20, 50, 100, 200 and 500  $\mu$ m. The structures are made of a 1  $\mu$ m-thick transparent LTO (low temperature oxide) LPCVD silicon dioxide layer is used as structural material, so that we can easily measure the underetch length with a conventional optical microscope. The thicknesses of the sacrificial layers were 0.5, 1, 2 and 3  $\mu$ m and 200, 300 nm for sputtered amorphous and LPCVD polycrystalline silicon thin films, respectively (Figures 2.4, 2.5 and 2.6). Silicon dioxide thickness has been measured beside the membrane using a spectro-reflectometer (Nanospec AFT 6100).

Figure 2.4 Cross section illustrations of (a) the test structures: LTO LPCVD  $SiO_2$  structural layer and a-Si or poly-Si sacrificial layer and (b) the evolution of Si underetch and  $SiO_2$  shapes during  $SF_6$  releasing (dashed line).

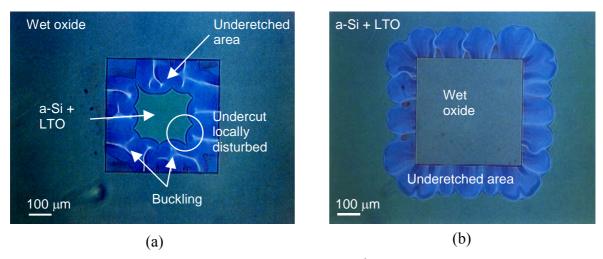

Figure 2.5 Optical microphotographs of  $500 \times 500 \mu m^2$  square (a) and square opening (b) in LTO structural layer. Induced stress between released and non released parts causes LTO membrane to buckle and locally disturbs the a-Si undercut (serrated shape).

Figure 2.6 SEM cross section view with the profile of 1  $\mu$ m-thick a-Si sacrificial layer during SF<sub>6</sub> releasing. The 1  $\mu$ m-thick LTO structural layer has been removed and is schematically represented for clarity (thickness is not at scale).

Based on the etching recipes used at EPFL-CMI prior to this work for 1  $\mu$ m-thick a-Si and 400 nm-thick poly-Si sacrificial layers (Table 2.1) and on the capabilities of the two Alcatel 601E ICP etchers available, the experimental plasma parameters have been determined (Table 2.2).

Table 2.1 Etching recipes used at EPFL-CMI prior to this work for 2 µm-thick a-Si and 400 nm-thick poly-Si sacrificial layers. These recipes were the basis for determining the experimental plasma parameters (Table 2.2).

| Sacrificial layer                  |         |         |

|------------------------------------|---------|---------|

| material                           | a-Si    | poly-Si |

| thickness [µm]                     | 2       | 0.4     |

| Plasma settings                    |         |         |

| ICP source power [W]               | 1500    | 1500    |

| bias power [W]                     | 0       | 0       |

| SF <sub>6</sub> flow rate [sccm]   | 200     | 200     |

| pressure [Pa]                      | 3       | 18      |

| chuck temperature [°C]             | 20      | 20      |

| Releasing features                 |         |         |

| Si underetch rate [µm/min]         | 1.9     | 0.3     |

| SiO <sub>2</sub> etch rate [Å/min] | 12.6    | 1.7     |

| Si: SiO <sub>2</sub> selectivity   | 1500: 1 | 1750: 1 |

Table 2.2 Experimental plasma parameters. Central parameters are highlighted in bold.

| Experimental plasma parameters   |                                      |

|----------------------------------|--------------------------------------|

| ICP source power [W]             | 1000, <b>1500</b> , 2000, 2500, 3000 |

| Bias power [W]                   | 0                                    |

| SF <sub>6</sub> flow rate [sccm] | 100, <b>300</b> , 500, 700, 900      |

| Pressure [Pa]                    | 3, 5, <b>10</b> , 15, 18             |

| Chuck temperature [°C]           | -110, -40, -20, 0, <b>20</b> , 40    |

#### 2.2.2.3 Influence of the different parameters

In the following, we present a detailed experimental study to determine the influence of the most relevant etching parameters: (i) process time, (ii)  $SF_6$  flow rate, (iii) pressure, (iv) ICP source power, (v) chuck temperature, as well as design and sacrificial layer parameters: (vi) opening feature size of the structures, (vii) silicon sacrificial layer thickness, (vii) a-Si deposition temperature.

Subsequently, their impact on the: (i) silicon underetch rate, (ii) silicon dioxide etch rate, and (iii) Si: SiO<sub>2</sub> selectivity are reported. Finally, the SiO<sub>2</sub> thickness under membranes is also measured.

To evaluate the influence of the parameters separately, each experiment has the central parameters (Table 2.2) as starting point and one parameter is varied.

#### Process time and $SF_6$ flow rate

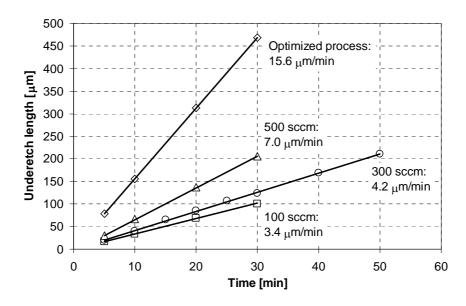

The releasing using a 1  $\mu$ m a-Si sacrificial layer was carried out up to 450  $\mu$ m underetch length resulting in a very uniform etch rate that can be as high as 15  $\mu$ m/min (Figure 2.7). SF<sub>6</sub> flow rate is increased (100, 300 and 500 sccm) and leads to an increase in the number of fluorine radicals available in chemical reaction resulting in higher etch rate of silicon. Underetch rate increases rapidly with SF<sub>6</sub> flow rate (from 3 to 7  $\mu$ m/min) but remains linear with process time. Contrary to deep anisotropic etching where etch rate decreases with depth, underetch rate of thin silicon layer is constant over a large length. This implies that the reactant flux in extremely thin gaps is sufficient to (1) enhance chemical reaction and (2) evacuate volatile products.

Figure 2.7 Underetch length of 1  $\mu$ m a-Si sacrificial layer vs. time for different processes with increased SF<sub>6</sub> flow rate and for the optimized process (Table 2.7).

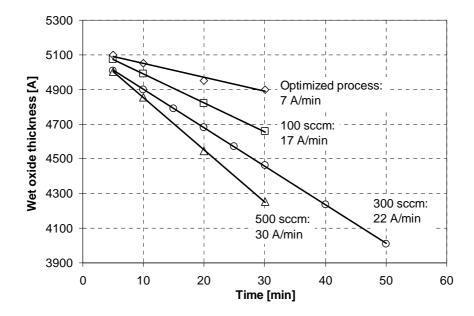

Figure 2.8 depicts oxide thickness beside membranes as a function of process time for different processes. Increased  $SF_6$  flow rates lead to an increased chemical reaction with silicon dioxide.

After plasma optimization, very high Si underetch rate and high selectivity on  $SiO_2$  were performed (Optimized process, see Table 2.7). Fluorine reaction with silicon dioxide is frozen by lowering chuck temperature at -110 °C.

Figure 2.8 Wet oxide thickness vs. time for different processes with increased  $SF_6$  flow rate and for the optimized process (Table 2.7).

Table 2.3 Si underetch and  $SiO_2$  etch rates and  $Si: SiO_2$  selectivity for different  $SF_6$  flow rates and the optimized process (Table 2.7).

| SF <sub>6</sub> flow rate [sccm]   | 100     | 300     | 500     | Optimized  |

|------------------------------------|---------|---------|---------|------------|

|                                    |         |         |         | process    |

| Si underetch rate [µm/min]         | 3.4     | 4.2     | 7.0     | 15.6       |

| SiO <sub>2</sub> etch rate [Å/min] | 17      | 22      | 30      | 7          |

| Si: SiO <sub>2</sub> selectivity   | 2000: 1 | 1900: 1 | 2300: 1 | > 20000: 1 |

#### **Pressure**

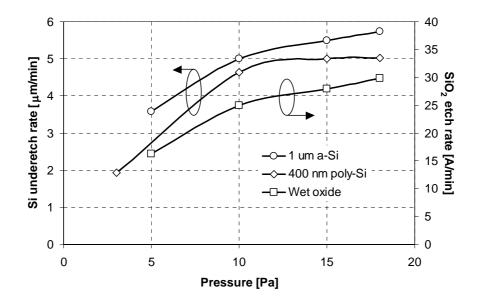

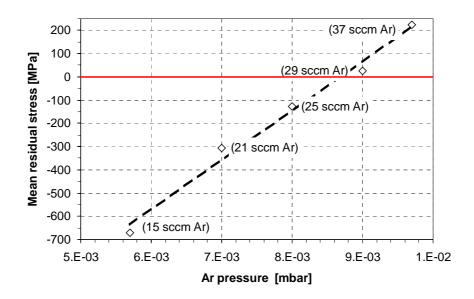

Process pressure has a significant impact on the results of plasma etching. It has a large influence on plasma features such as the reactive species density, ions flux, sheath potential, energy of ions reaching the surface and chemical kinetics. Higher pressure leads to increase the number of fluorine radicals available in chemical reaction resulting in higher etch rate of silicon. The release etchings are performed at 20 °C with a source power of 1500 W and a SF<sub>6</sub> flow rate of 300 sccm by changing the process pressure in the range of 3 - 18 Pa. It can be seen in Figure 2.9 that a-Si, poly-Si and SiO<sub>2</sub> etch rates increase as a function of reactor pressure with a threshold around 10 Pa. This is probably due to the chemical reaction saturation; indeed, silicon underetch rate cannot increase indefinitely and is limited by reactant products. However, higher pressure also increases the ions/neutrals collision, thereby reducing ions directionality and ions energy. This may explain the SiO<sub>2</sub> etch rate reduction observed around 10 Pa.

Figure 2.9 Si sacrificial layer underetch rate and SiO<sub>2</sub> etch rate vs. pressure.

Table 2.4 Si underetch and  $SiO_2$  etch rates and Si:  $SiO_2$  selectivity for different pressures.

| Pressure [Pa]                         | 3    | 5       | 10      | 15      | 18      |

|---------------------------------------|------|---------|---------|---------|---------|

| a-Si underetch rate [µm/min]          | N.A. | 3.6     | 5.0     | 5.5     | 5.7     |

| poly-Si underetch rate [µm/min]       | 1.9  | N.A.    | 4.6     | 5.0     | 5.0     |

| SiO <sub>2</sub> etch rate [Å/min]    | N.A. | 16      | 25      | 28      | 30      |

| a-Si: SiO <sub>2</sub> selectivity    | N.A. | 2200: 1 | 2000: 1 | 1960: 1 | 1900: 1 |

| poly-Si: SiO <sub>2</sub> selectivity | N.A. | N.A.    | 1840: 1 | 1780: 1 | 1670: 1 |

#### ICP source power

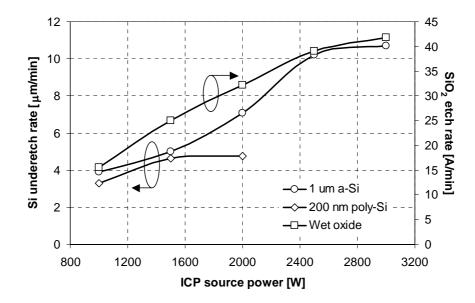

Increasing ICP source power extends the electron energy distribution function (EEDF) and therefore, a larger number of electrons with high energy are available for dissociation and ionization. Evolution of sacrificial layer and silicon dioxide etch rates is shown in Figure 2.10. It can be seen that increasing ICP source power increases  $SiO_2$  and sacrificial layer etch rate. A threshold is observed around 1500 W for the 200 nm poly-Si sacrificial layer and around 2500 W for the 1  $\mu$ m a-Si sacrificial layer. This is due to the saturation of reactant species, which depends on thickness of the sacrificial layer and source power. In fact four fluorine atoms react with one silicon atom to form  $SiF_4$  molecule, which is a volatile product at room temperature,  $SiF_4$  molecules are then desorpted from the surface and pumped away.

Figure 2.10 Si sacrificial layer underetch rate and SiO<sub>2</sub> etch rate vs. ICP source power.

Table 2.5 Si underetch and  $SiO_2$  etch rates and  $Si: SiO_2$  selectivity for different ICP source power.

| ICP source power [W]                  | 1000    | 1500    | 2000    | 2500    | 3000    |

|---------------------------------------|---------|---------|---------|---------|---------|

| a-Si underetch rate [µm/min]          | 3.9     | 5.0     | 7.0     | 10.2    | 10.7    |

| poly-Si underetch rate [µm/min]       | 3.3     | 4.6     | 4.8     | N.A.    | N.A.    |

| SiO <sub>2</sub> etch rate [Å/min]    | 16      | 25      | 32      | 39      | 42      |

| a-Si: SiO <sub>2</sub> selectivity    | 2440: 1 | 2000: 1 | 2190: 1 | 2610: 1 | 2550: 1 |

| poly-Si: SiO <sub>2</sub> selectivity | 2060: 1 | 2200: 1 | 1500: 1 | N.A.    | N.A.    |

#### **Temperature**

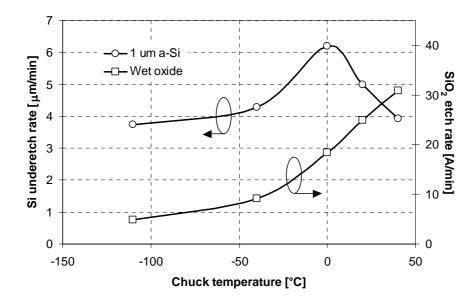

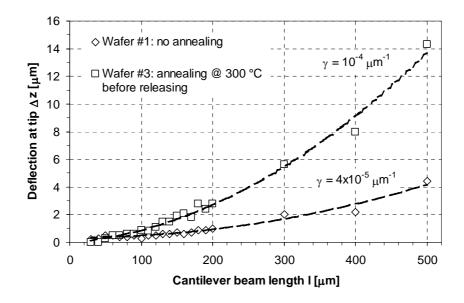

The chuck temperature is controllable and influences underetch rate and Si: SiO<sub>2</sub> selectivity. The influence of temperature on the etch process, with an experimental range of -110 °C up to 40 °C for 30 min etch duration, is shown in Figure 2.11. It should be noted that chuck temperature during etching plays a crucial role in reducing silicon dioxide etch rate, while silicon underetch rate appears to have a maximum peak close to 0 °C. This is important for suspended-gate MOSFET (see chapter 6), where a high quality gate oxide should remain after releasing. By decreasing the temperature, we show that the silicon dioxide etch rate is significantly reduced without significantly affecting the releasing. These results show clearly that SiO<sub>2</sub> reaction with fluorine was suppressed by lowering chuck temperature. A maximum peak around 0 °C was observed for both sacrificial layers (a-Si and poly-Si). The reason for the high etch rate at 0 °C is not well understood at the present time. A significant dependence of underetch rate with chuck temperature is not unexpected since the etch rate depends on sticking probabilities of the species and often changes with surface temperature. The advantage of cryogenic cooling is seen in the selectivity with respect to silicon dioxide. Temperature is an independent parameter, which affects silicon dioxide etch rate without

decreasing Si underetching too much. The chuck temperature is therefore a crucial parameter and special attention must be paid to this when releasing silicon sacrificial layer.

Figure 2.11 1  $\mu$ m a-Si sacrificial layer underetch rate and SiO<sub>2</sub> etch rate vs. chuck temperature.

Table 2.6 Si underetch and  $SiO_2$  etch rates and  $Si: SiO_2$  selectivity for different chuck temperature.

| Chuck temperature [°C]             | -110    | -40     | 0       | 20      | 40      |

|------------------------------------|---------|---------|---------|---------|---------|

| Si underetch rate [µm/min]         | 3.8     | 4.3     | 6.2     | 5.0     | 3.9     |

| SiO <sub>2</sub> etch rate [Å/min] | 5       | 9       | 18      | 25      | 31      |

| Si: SiO <sub>2</sub> selectivity   | 7600: 1 | 4780: 1 | 3440: 1 | 2000: 1 | 1250: 1 |

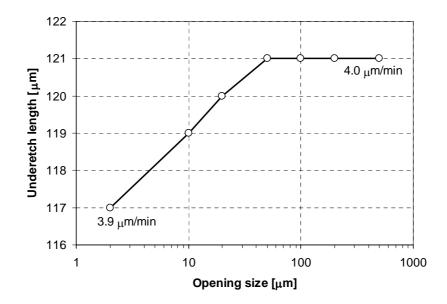

#### Feature size

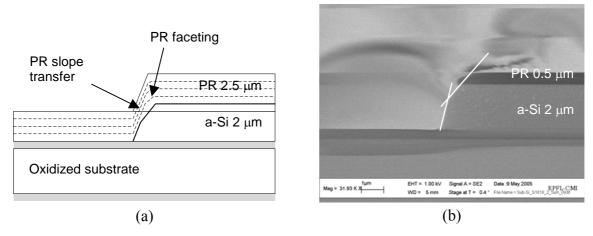

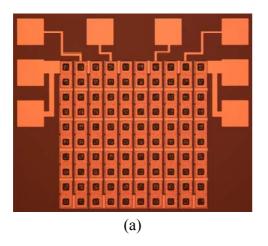

Test cells have been designed to study the releasing with the opening area of etching. It consists of trenches with opening sizes from 2  $\mu$ m to 500  $\mu$ m. Figure 2.12 shows the relationship between etch rate and opening size. The etch duration is 30 min, source power, bias power, pressure, SF<sub>6</sub> flow rate and chuck temperature are respectively 1500 W, 0 W, 10 Pa, 300 sccm and 20 °C. Feature size of the structure has been found to have little influence on underetch rate: 4.0  $\mu$ m/min for 500  $\mu$ m opening size and 3.9  $\mu$ m/min for 2  $\mu$ m opening size (i.e. a decrease of less than 3%). Experimental results show also that no aspect ratio dependent etching (ARDE) effect occurs in lateral etching of silicon unlike deep RIE etching. Taking advantage of this last remark, large metal membrane-based MEMS devices can be designed with 5 x 5  $\mu$ m<sup>2</sup> etch holes to reduce the releasing process time.

Figure 2.12 Underetch length of 1 µm a-Si sacrificial layer vs. opening size after 30 min of etching with the room temperature optimized process (Table 2.7).

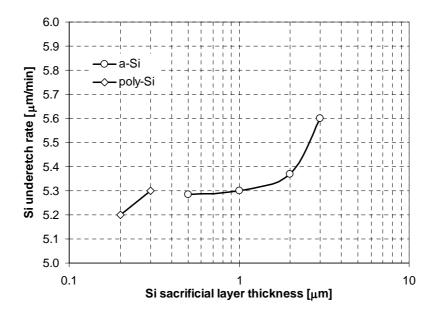

#### Silicon sacrificial layer thickness

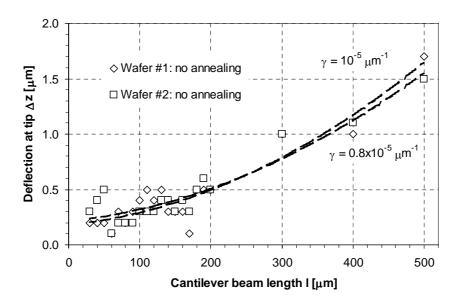

Si underetch rate was investigated for different sacrificial layer thicknesses and is shown in Figure 2.13. Si underetch rate is only varies of 7% over more than one decade of sacrificial layer thickness (3 µm to 200 nm). This late remark is important for MEMS tunable capacitors, where double air-gaps, hence two different sacrificial layer thicknesses, are needed (see section 3.3). In addition, this process is very efficient in releasing very thin poly-Si sacrificial layer as required for suspended-gate MOSFETs (see chapter 6) and to release thick a-Si sacrificial layer as required for tunable capacitors and capacitive switches.

Figure 2.13 Si underetch rate vs. sacrificial layer thickness for a-Si and poly-Si. Si underetch rate only varies by 7% over more than one decade of sacrificial layer thickness (3 µm to 200 nm).

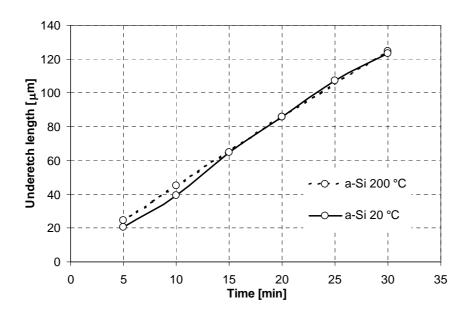

#### a-Si deposition temperature

Substrate temperature influences the film adhesion on the wafer, surface smoothness and microstructure of the deposited layer. Therefore we decided to study underetching of 1  $\mu$ m a-Si sacrificial layers deposited at 20 and 200 °C. We show that substrate temperature during deposition has no influence on the a-Si underetch rate (Figure 2.14).

Figure 2.14 Underetch length of 1  $\mu$ m a-Si sacrificial layer deposited at 20 and 200 °C vs. time.

#### Silicon dioxide thickness under membranes

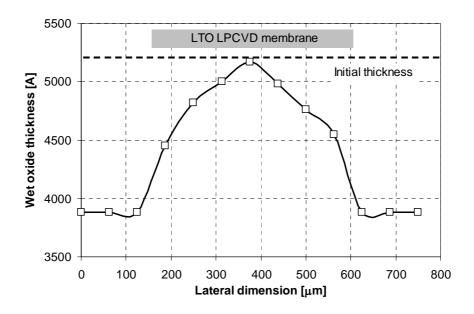

To better understand silicon dioxide etching under a membrane, a 450 x 450  $\mu$ m<sup>2</sup> membrane has been removed to access the wet oxide layer and its thickness has been measured using a spectro-reflectometer. A typical silicon dioxide profile under the released membrane is shown in Figure 2.15. We show that SiO<sub>2</sub> etch rate depends on exposure time to plasma since the etch rate under membrane is constant (16 Å/min) and on ions flux since etch rate is higher beside membrane (22 Å/min).

Figure 2.15 Wet oxide profile under a 450 x 450  $\mu$ m<sup>2</sup> membrane. The membrane is schematically represented for clarity (thickness is not at scale).

#### 2.2.2.4 Optimized parameters

Based on the previous study, several recipes have been investigated in order to optimize the process parameters. This study emphasizes the fact that temperature plays an important role in this process by limiting silicon dioxide etching. Moreover, the optimized recipe has been found to be independent of the sacrificial layer used (a-Si or poly-Si) or its thickness. SF<sub>6</sub> flow rate, pressure and ICP source power were set to 500 sccm, 18 Pa and 3000 W, respectively, and chuck temperature was lowered to -110 °C. Using this recipe, 15.6  $\mu$ m/min Si underetch rate with very high Si: SiO<sub>2</sub> selectivity (> 20000: 1) has been obtained (Table 2.7).

In practice, we will not use this cryogenic process for releasing our aluminum membrane-based MEMS devices. If it was the case, we should have considered the effect of releasing at low temperature on stress, knowing that the structures will operate at room temperature or higher temperature. The room temperature optimized process (Table 2.7) exhibits Si underetch rate of 4.2  $\mu$ m/min with high Si: SiO<sub>2</sub> selectivity (1900: 1) which is sufficient for releasing large membranes (few hundreds of  $\mu$ m) with etch holes in a reasonable time of 10 - 15 minutes.

| Table 2.7   | Optimized      | and ro  | om tem    | perature  | optimized    | process   | parameters   | and         | respective    |

|-------------|----------------|---------|-----------|-----------|--------------|-----------|--------------|-------------|---------------|

| releasing j | features for a | a 1 µm- | thick spi | uttered a | -Si sacrific | ial layer | deposited at | <i>20</i> ° | $^{\circ}C$ . |

|                                    | Optimized process | Room T optimized |

|------------------------------------|-------------------|------------------|

|                                    |                   | process          |

| Plasma settings                    |                   |                  |

| ICP source power [W]               | 3000              | 1500             |

| bias power [W]                     | 0                 | 0                |

| SF <sub>6</sub> flow rate [sccm]   | 900               | 300              |

| pressure [Pa]                      | 18                | 10               |

| chuck temperature [°C]             | -110              | 20               |

| Releasing features                 |                   |                  |

| Si underetch rate [µm/min]         | 15.6              | 4.2              |

| SiO <sub>2</sub> etch rate [Å/min] | 7                 | 22               |

| Si: SiO <sub>2</sub> selectivity   | > 20000: 1        | 1900: 1          |

#### 2.2.2.5 Releasing of aluminum membranes

Fluorine chemistry does not etch aluminum because the AlF<sub>3</sub> etch product has a very low vapor pressure [67, 68], compared to AlCl<sub>3</sub> etch product (vapor pressure of 7x10<sup>-5</sup> Torr at 25 °C) obtained when etching aluminum with chlorine chemistry.

Figure 2.16 Vapor pressure of AlF<sub>3</sub>, AlCl<sub>3</sub> and AlBr<sub>3</sub> vs. temperature. From [68].

We have observed that, during aluminum membranes releasing, the Si underetch rate saturates rapidly to a value of about 2  $\mu$ m/min instead of a constant 4.2  $\mu$ m/min for the room temperature optimized process (Table 2.7). The reason could be an AlF<sub>3</sub> passivation of the etch front.

#### 2.2.3 Comparison with state-of-the-art dry releasing processes

Table 2.4 gives a comparison between the results we have obtained with the  $SF_6$  optimized and room temperature optimized processes (Table 2.7) and the state-of-the-art dry releasing processes.  $SF_6$  plasma has been chosen because it exhibits much higher etch rate than  $O_2$  plasma and HF vapor phase etching and moreover it presents a high selectivity to  $SiO_2$  and aluminum.

Table 2.8 Comparison between the results we have obtained with the  $SF_6$  optimized and room temperature optimized processes (Table 2.7) and the state-of-the-art dry releasing processes.

| Process                         | Sacrificial layer | Underetch rate | Selectivity to |

|---------------------------------|-------------------|----------------|----------------|

|                                 | material          | [µm/min]       | $SiO_2$        |

| SF <sub>6</sub> ICP plasma      | a-Si and poly-Si  | 15.6           | > 20000: 1     |

| Optimized process               |                   |                |                |

| SF <sub>6</sub> ICP plasma      | a-Si and poly-Si  | 4.2            | 1900: 1        |

| Room T optimized                |                   |                |                |

| process                         |                   |                |                |

| SF <sub>6</sub> ICP plasma [65] | bulk Si           | 4.5            | N.A.           |

| XeF <sub>2</sub> gas phase [60] | Si                | 2-4            | > 1000: 1      |

| BrF <sub>3</sub> gas phase [49] | Si                | 1-14           | > 3000: 1      |

| O <sub>2</sub> plasma *         | polyimide         | ~ 1            | very high      |

|                                 | PI26xx [37]       |                |                |

| HF vapor phase [69]             | thermal oxide     | 0.07-0.1       | -              |

<sup>(\*</sup> at EPFL-CMI, Tepla300 microwave plasma stripper, barrel reactor)

### 2.3 METAL SURFACE MICROMACHINING FOR ABOVE-IC RF MEMS APPLICATIONS

#### 2.3.1 Choice of materials

The development of a new surface micromachining process requires the choice of different materials: sacrificial and structural layer and insulating layers. The choice is dictated by on the one hand the functionality of the MEMS devices and associated applications and on the other hand by the clean room process available.

The process presented in this section is intended to be compatible with CMOS post-processing for *above-IC integration* in order to fabricate radiofrequency (RF) MEMS devices. These devices are mainly electrostatically-actuated capacitive membrane-based devices (see following chapters).

#### 2.3.1.1 CMOS post-process compatibility

In order to make integrated devices, the steps used to fabricate the micromechanical structures must not adversely impact the underlying circuitry.

High temperatures, plasma or X-ray damage, electrostatic discharge (ESD), metal diffusion into silicon, contamination, or physical etching of the CMOS must all be avoided.

Among these, temperature is the main concern in above-IC approach since the underlying circuitry is completely passivated by multiple dielectric layers except for some areas of the top interconnect metallization layer, where we want an electrical contact between the circuitry and the post-processed devices. High temperatures must be avoided since the aluminum metallization in standard CMOS melts at 660 °C. However, the metallization will fail at the junctions well before that temperature is reached. As a practical limit, the maximum post-process temperature on CMOS wafers with Al interconnects is generally considered to be 450 °C [70]. However Sedky *et al.* have shown that 0.35 µm CMOS technology can withstand annealing temperatures up to 525 °C for 90 min [71].

This rules out the deposition of many LPCVD films, such as LPCVD poly-Si and silicon nitride, which typically takes place at temperatures in excess of 575 °C, for structural and insulating layers but leaves place for metals and sputtered silicon [41, 42].

X-ray damage, a by-product of e-beam evaporation and, to a lesser extent, plasma processes, is also a concern. The X-rays ionize atoms in the gate region resulting in shifts in the threshold voltage of the affected transistors [72]. For these reasons it is advisable to avoid e-beam evaporation when integrating microstructures with circuits.

Circuits are commonly protected against ESD.

Metals such as copper, silver and gold heavily diffuse into silicon at low temperature and are not tolerated in standard CMOS fabrication.

Contamination by alkali atoms is a concern during etching of silicon in KOH solutions. The  $K^+$  ions are mobile in oxide and can shift threshold voltages if they reach the gate.

#### 2.3.1.2 Structural material

The choice of structural material for RF MEMS is a compromise between electrical and mechanical properties and process limitations.

RF MEMS need highly conductive materials in order to reduce series resistive losses. This rules out LPCVD poly-Si and poly-SiGe, even if heavily doped, and also sputtered silicon. The four most conductive metals are Ag, Cu, Au, and Al (Table 2.9).

| Table 2.9 | Electrical | l resistivity f | or t | bulk metal | s at | room i | temperature | [73 | 7. |

|-----------|------------|-----------------|------|------------|------|--------|-------------|-----|----|

|           |            |                 |      |            |      |        |             |     |    |

| Material | Electrical resistivity        |

|----------|-------------------------------|

|          | $[10^{-8} \Omega \mathrm{m}]$ |

| Ag<br>Cu | 1.6                           |

| Cu       | 1.7                           |

| Au       | 2.2                           |

| Al       | 2.7                           |

Among them, silver is the best electrical conductor but is uncommon in surface micromachining. Copper is replacing aluminum as interconnect material (Cu-damascene process) in advanced CMOS technologies and also as material for high-Q micromachined inductors but requires diffusion barrier layers. Gold is the preferred conductor for transmission lines in monolithic microwave ICs (MMICs).

These three materials (Ag, Cu, Au) can be patterned by wet etching but cannot be plasma etched. Moreover they are not allowed in some clean room equipment at EPFL-CMI, as they may contaminate other on-going processes.

Aluminum and aluminum alloys with small amounts (few percents) of Cu and / or Si have been widely investigated in IC technology as interconnect material [70] but also in MEMS processes [38, 74, 75].

#### 2.3.1.3 Silicon sacrificial layer deposition technique

Amorphous silicon (a-Si) thin films can be deposited at low temperature (< 300 °C) by PECVD [76] or sputtering.

Some PECVD tests were performed in Alcatel 601D PECVD system using pure silane (SiH<sub>4</sub>) and argon as dilution gas. The a-Si deposited layers exhibited poor quality and a thickness uniformity of more than 10%.

The first a-Si sputtered films were deposited by RF sputtering in the Balzers BAS450 single chamber multi-target magnetron sputtering system. Results shown a low deposition rate of 8 nm/min but a good thickness uniformity of 4%.

a-Si depositions are currently made by DC sputtering using a boron-doped target (5 - 30 m $\Omega$ cm) in the Pfeiffer Vacuum Spider 600 high vacuum magnetron sputter cluster system. The obtained deposition rate is 100 nm/min with a thickness uniformity in the same range as the BAS450 system.

#### 2.3.1.4 Summary of chosen materials

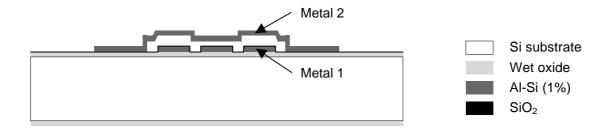

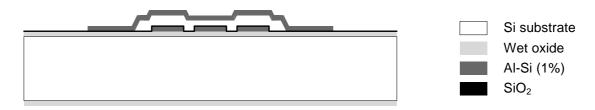

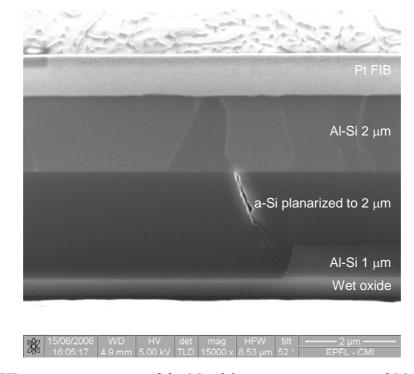

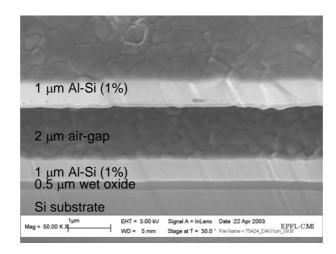

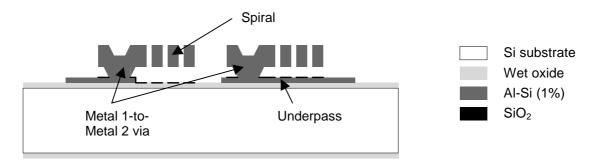

Sputtered aluminum alloy with 1% of silicon (Al-Si (1%)) was chosen for the structural material. Due to the unavailability of a PECVD system for depositing insulating layers at low temperature, the SiO<sub>2</sub> layer covering the aluminum bottom electrodes of the devices was also sputtered. This means that all the physical layers are deposited in the Spider 600 system.

Table 2.10 Summary of the materials used in the metal surface micromachining process developed for above-IC RF MEMS applications. All of them are sputter-deposited in Spider 600 system.

| Layer       | Material     |

|-------------|--------------|

| Structural  | Al-Si (1%)   |

| Insulating  | ${ m SiO_2}$ |

| Sacrificial | a-Si         |

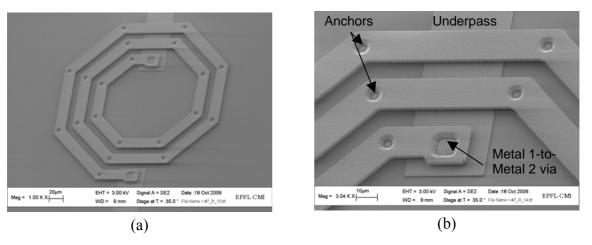

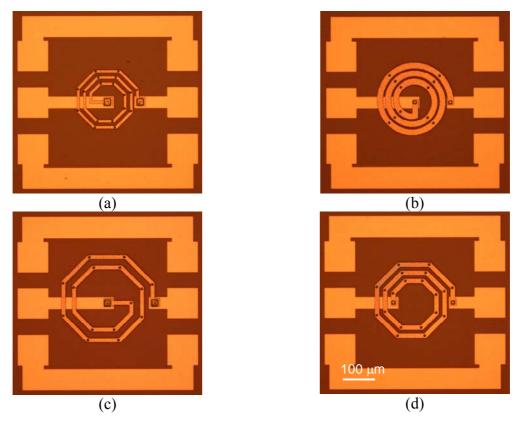

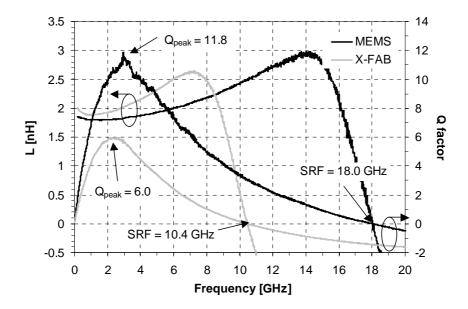

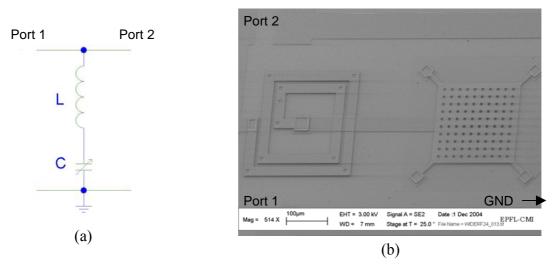

#### 2.3.2 Successive improvements in the fabrication process steps