# UNIFYING SOFTWARE AND HARDWARE OF MULTITHREADED RECONFIGURABLE APPLICATIONS WITHIN OPERATING SYSTEM PROCESSES

THÈSE Nº 3626 (2006)

PRÉSENTÉE LE 22 SEPTEMBRE 2006 À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS Laboratoire d'architecture de processeurs SECTION D'INFORMATIQUE

# ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

# Miljan VULETIĆ

Ingénieur diplômé de l'Université de Belgrade, Yougoslavie de nationalité serbe et monténégrine

acceptée sur proposition du jury:

Prof. E. Sanchez, président du jury Prof. P. lenne, directeur de thèse Prof. D. Andrews, rapporteur Prof. G. Brebner, rapporteur Prof. W. Zwaenepoel, rapporteur

Marici i Slobodanu

#### Acknowledgements

First of all, I wish to express my sincere thanks to my advisor, Paolo, for his counsel, guidelines, and help that he provided during all these years I spent at EPFL. We had many cheerful discussions that sprang the ideas presented in this thesis and latenight (or early-morning) paper submissions that eventually resulted in publications (well, most of them). Apart from being a great thesis advisor, Paolo was a steady companion for a pint of ale and a handful of conversation, after long working days at conferences and meetings. These rare relaxing moments I really appreciate.

Special thanks are due to David Andrews and Gordon Brebner, both of them being the members of my thesis committee. The discussions I had with them helped in evaluating my work within the research community and, at the same time, in answering some challenging related questions. I would also like to thank Willy Zwaenepoel for his participation in the thesis committee and Eduardo Sanchez for presiding the thesis committee and for giving inspiring counsels on reconfigurable computing.

I extend my thanks to Laura Pozzi, who offered valuable help while I was focusing my research topics, and to Nuria Pazos Escudero, who gave useful remarks while I was finishing the thesis writing. Jean-Luc Beuchat, at the very beginning, and Walter Stechele and his group, at the very end, helped in applying the ideas presented in the thesis to real-world problems of software and hardware interfacing. I acknowledge and appreciate the hard work of the students that I followed, whose semester, internship, and diploma projects fostered the practical proof of my thesis.

Of all wonderful moments spent at the Processor Architecture Laboratory (LAP), I will most surely remember the outdoor activities (barbecues, hiking, and skiing) and friendly chats (of rather nontechnical content), fulfilled with laughter and enthusiasm of former and current LAP members. I would like to thank them all for these good moments.

Although hard work is the essence of a PhD student being, it was not just everything. My friends from Lausanne and all over (luckily, there are many to be recognised, whereas mentioning all of them would be error prone) showed me different and pretty successful ways (not to confuse with beer and wine) how to stop thinking about computer engineering. I admire their friendly attitude and social initiative, even if I was difficult to persuade for leaving my research duties (except on a sunny day with powder snow or for an important match of E2050 or Fusion Forte football teams).

While my parents, Marica and Slobodan, and my sister, Jelena, were everlasting origin of long-haul care, "Made-in-Serbia" warmth, and family love, for which I am grateful and I will forever reciprocate, my wife, Chantal, was neverending source of short-haul encouragement, thorough understanding, and stellar love. She brightened my Lausanne sky like the most glittering and beloved star of Earendil, and to her go all my love and gratitude. \_\_\_\_\_

#### Abstract

Novel reconfigurable System-on-Chip (SoC) devices offer combining software with application-specific hardware accelerators to speed up applications. However, by mixing user software and user hardware, principal programming abstractions and system-software commodities are usually lost, since hardware accelerators (1) do not have execution context—it is typically the programmer who is supposed to provide it, for each accelerator, (2) do not have virtual memory abstraction—it is again programmer who shall communicate data from user software space to user hardware, even if it is usually burdensome (or sometimes impossible!), (3) cannot invoke system services (e.g., to allocate memory, open files, communicate), and (4) are not easily portable—they depend mostly on system-level interfacing, although they logically belong to the application level.

We introduce a unified *Operating System* (OS) process for codesigned reconfigurable applications that provides (1) unified memory abstraction for software and hardware application parts, (2) execution transfers from software to hardware and vice versa, thus enabling hardware accelerators to use systems services and callback other software and hardware functions, and (3) multithreaded execution of multiple software and hardware threads. The unified OS process ensures portability of codesigned applications, by providing standardised means of interfacing.

Having just-another abstraction layer usually affects performance: we show that the runtime optimisations in the system layer supporting the unified OS process can minimise the performance loss and even outperform typical approaches. The unified OS process also fosters unrestricted automated synthesis of software to hardware, thus allowing unlimited migration of application components. We demonstrate the advantages of the unified OS process in practice, for Linux systems running on Xilinx Virtex-II Pro and Altera Excalibur reconfigurable devices.

**Keywords:** HW/SW Codesign, Hardware Accelerators, OS Support, Virtual Memory, Execution Context for Codesigned Applications, Reconfigurable Computing.

#### Résumé

Les systèmes intégrés sur puce ("Systems-on-Chip") reconfigurables offrent la possibilité d'accélérer des applications en combinant du logiciel avec des accélérateurs spécifiques implémentés en matériel. Cependant, la combinaison du logiciel utilisateur avec le matériel utilisateur ne permet plus de bénéficier des abstractions principales de programmation et des facilités d'utilisation du système d'exploitation. En effet, les accélérateurs d'applications implémentés en matériel : (1) n'ont pas de contexte d'exécution (c'est au programmeur d'assurer ce contexte pour chaque accélérateur) ; (2) ne peuvent pas profiter de la mémoire virtuelle (c'est à nouveau le programmeur qui doit transférer les données depuis l'espace de mémoire utilisateur à l'espace de mémoire matériel, même si c'est pénible voire même impossible, selon les cas!) ; (3) ne peuvent pas appeler les services du système d'exploitation; et (4) ne sont pas facilement portable (ils dépendent des interfaces du système, même s'ils appartiennent sémantiquement au niveau d'application).

Pour les applications conçues en logiciel et en matériel reconfigurable, nous proposons un concept de processus du système d'exploitation *unifié*. Ce concept permet : (1) l'abstraction de mémoire unifiant les parties de l'application logicielles et matérielles ; (2) les transferts d'exécution du logiciel vers le matériel et viceversa, afin que les accélérateurs matériels puissent appeler les services systèmes et d'autres fonctions logicielles ou matérielles ; et (3) l'exécution de plusieurs processus légers (*"multithreaded execution"*) en logiciel et en matériel. De plus, l'utilisation du processus du système d'exploitation unifié assure la portabilité des applications conçues partiellement en logiciel et en matériel, offrant ainsi des moyens standard d'interfaçage.

En général, le fait d'introduire une nouvelle couche d'abstraction influence significativement la performance des applications: contrairement à cette attente, nous montrons que les optimisations en cours d'exécution effectuées dans la couche du système contenant le processus unifié permettent de minimiser la perte de performance et même, dans certain cas, de dépasser les approches typiques. De plus, le processus unifié rend possible la synthèse automatique et sans restriction du logiciel jusqu'au matériel ; c'est-à-dire, il est possible de migrer sans restriction les composants de l'application du logiciel vers le matériel ou inversement. Nous démontrons par des cas pratiques les avantages du processus unifié mentionnés ci-dessus sur un système Linux s'exécutant sur deux plateformes reconfigurables.

Les mots-clés: Accélérateurs en Matériel, Contexte d'Exécution des Applications Conçues en Logiciel et en Matériel, Ordinateurs Reconfigurable.

# Contents

| 1        | Intr | roduction                                           | 1         |

|----------|------|-----------------------------------------------------|-----------|

|          | 1.1  | User Applications and OS Processes                  | 1         |

|          | 1.2  | Codesigned Applications in Software-centric Systems | 3         |

|          | 1.3  | Seamless Interfacing of Software and Hardware       | 5         |

|          | 1.4  | Thesis Organisation                                 | 6         |

| <b>2</b> | Mis  | sing Abstractions for Codesigned Applications       | 9         |

|          | 2.1  | Process Model of Computation                        | 9         |

|          | 2.2  | Typical Architectures: Accessing Memory             | 11        |

|          | 2.3  | Typical Architectures: Callbacks to Software        | 14        |

|          | 2.4  | Typical Architectures: Multithreading               | 15        |

|          | 2.5  |                                                     | 18        |

| 3        | Sta  | te of the Art                                       | <b>23</b> |

|          | 3.1  | Memory Wrappers and Subsystems                      | 23        |

|          | 3.2  | Reconfigurable Computing                            | 24        |

|          |      | 3.2.1 Reconfigurable Accelerator Integration        | 25        |

|          |      | 3.2.2 Parallel Execution                            | 26        |

|          |      | 3.2.3 Managing FPGA Resources                       | 29        |

|          | 3.3  | Hardware and Software Interfacing                   | 29        |

|          | 3.4  | -                                                   | 32        |

|          | 3.5  |                                                     | 32        |

| 4        | Vir  | tual Memory for Hardware Accelerators               | 35        |

|          | 4.1  | System Architecture                                 | 35        |

|          | 4.2  | Hardware Interface to Virtual Memory                | 36        |

|          | 4.3  | OS Extensions for Virtual Memory                    | 38        |

|          | 4.4  | Dynamic Optimisations in Abstraction Layer          | 40        |

|          |      | 4.4.1 Motivation                                    | 41        |

|          |      | 4.4.2 Hardware and Software Extensions              | 42        |

| <b>5</b> | Uni  | fied Memory Performance and Overheads               | 45        |

|          | 5.1  | Performance Metric for Heterogeneous Computing      | 45        |

|          | 5.2  | Overhead Analysis                                   | 47        |

|              | 5.3             | Experimental Results                             |

|--------------|-----------------|--------------------------------------------------|

|              |                 | 5.3.1 Typical Data Sizes                         |

|              |                 | 5.3.2 Small Input Data                           |

|              |                 | 5.3.3 Different Number of Memory Pages           |

|              |                 | 5.3.4 Area Overhead                              |

|              |                 | 5.3.5 Results Summary                            |

| 6            | $\mathbf{Svs}$  | tem Support for Execution Transfers 61           |

|              | 6.1             | Callbacks to Software                            |

|              | 6.2             | Kernel Mediation for Callbacks                   |

|              | 6.3             | Enabling Unrestricted Automated Synthesis        |

|              |                 | 6.3.1 Synthesis Flow                             |

|              |                 | 6.3.2 Virtual Machine Integration                |

|              |                 | 6.3.3 Experiments                                |

|              |                 | 6.3.4 Summary                                    |

| 7            | Tra             | nsparent Software and Hardware Multithreading 73 |

| •            | 7.1             | Extending a Multithreaded Programming Paradigm   |

|              | 7.2             | Support for Extended Multithreading              |

|              | 1.2             | 7.2.1         WMU Extensions         7.5         |

|              |                 | 7.2.2       VMW Manager Extensions       77      |

|              | 7.3             | Multithreading Case Study                        |

|              | 1.0             | 7.3.1 Multithreaded Execution                    |

|              |                 | 7.3.2 Multiple Memory Ports                      |

| 8            | Cor             | clusions 85                                      |

| 0            | 8.1             | Obtained Results   86                            |

|              | 8.2             | Implications                                     |

|              | 8.3             | Future Research Directions    88                 |

|              |                 |                                                  |

| Α            | WN              | IU Interface91                                   |

|              | A.1             | Hardware Interface                               |

|              | A.2             | Parameter Exchange                               |

|              | A.3             | Internal Structure                               |

| в            | $\overline{VM}$ | W System Call 97                                 |

|              | B.1             | VMW Programming                                  |

|              | B.2             | Parameter Exchange                               |

| $\mathbf{C}$ | Rec             | onfigurable SoC Platforms 101                    |

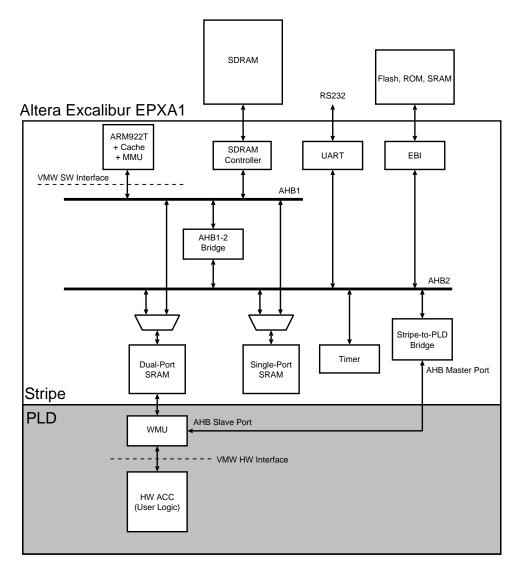

|              | C.1             | Altera Excalibur Platform                        |

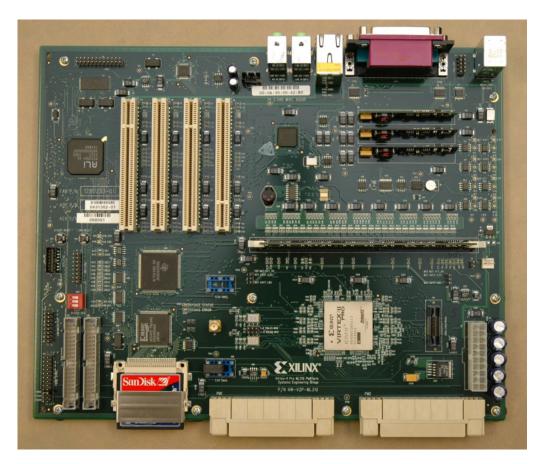

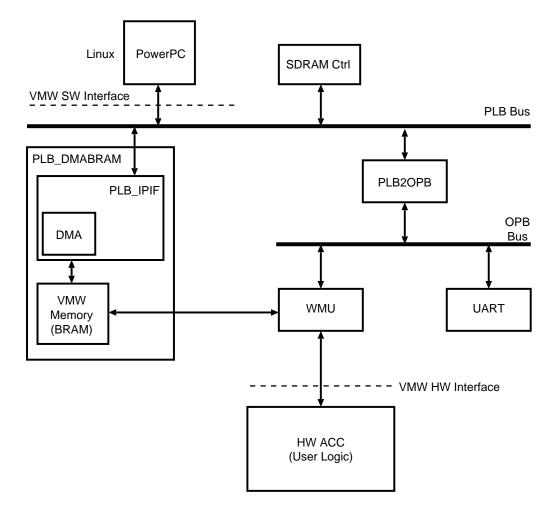

|              | C.2             | Xilinx Virtex-II Pro Platform                    |

| D            | Apr             | olications 109                                   |

|              |                 | IDEA Accelerator Design                          |

|              |                 | Contrast Engine Design                           |

| $\mathbf{E}$         | E CPD Calculation |                                                                                          | 115 |

|----------------------|-------------------|------------------------------------------------------------------------------------------|-----|

|                      | E.1               | CPD from Control-Flow Graphs                                                             | 115 |

|                      | E.2               | Hardware Execution Time                                                                  | 117 |

|                      | E.3               | Critical Section Speedup                                                                 | 119 |

| F                    | F.1               | EG4 Hardware Reference         Virtual Socket Framework         Virtual Memory Extension |     |

| Bibliography 124     |                   |                                                                                          | 124 |

| Curriculum Vitae 137 |                   |                                                                                          | 137 |

# **List of Figures**

| 1.1  | User software and system software running on system hardware            | 2  |

|------|-------------------------------------------------------------------------|----|

| 1.2  | Memory space of mixed software and hardware process                     | 4  |

| 1.3  | Levels of abstraction in a software-centric system                      | 5  |

| 1.4  | User software and user hardware as peers                                | 6  |

| 2.1  | Process model of computation: a stored-program computer                 | 10 |

| 2.2  | Blending temporal and spatial ways of computation                       | 10 |

| 2.3  | Typical hardware accelerator accessing local memory                     | 11 |

| 2.4  | Programming for the IDEA cryptography application                       | 12 |

| 2.5  | Typical hardware accelerator accessing main memory                      | 13 |

| 2.6  | Programming for the contrast enhancement application                    | 14 |

| 2.7  | Execution timelines of typical hardware accelerators                    | 15 |

| 2.8  | Servicing hardware accelerator callbacks to software                    | 16 |

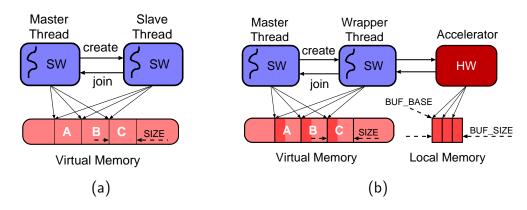

| 2.9  | Multithreaded code for software-only and hardware accelerator ver-      |    |

|      | sion of codesigned application                                          | 17 |

| 2.10 | Multithreading memory perspective for software-only and hardware        |    |

|      | accelerator version of the codesigned application                       | 18 |

|      | A heterogeneous-code unified-memory computer                            | 18 |

| 2.12 | Hardware accelerator capable of accessing virtual memory of user        |    |

|      | process through WMU                                                     | 19 |

|      | Programming with a virtual-memory-enabled hardware accelerator          | 20 |

| 2.14 | Platform-dependent and portable VHDL-like code                          | 20 |

| 3.1  | Specialised CPU extended with reconfigurable functional unit $\ldots$ . | 25 |

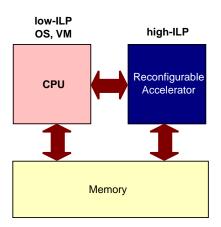

| 3.2  | CPU used in tandem with coprocessor-like reconfigurable accelerator     | 26 |

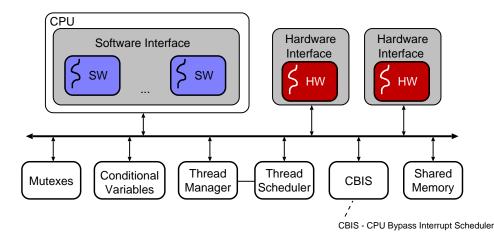

| 3.3  | System using <i>hthreads</i> for codesigned applications                | 27 |

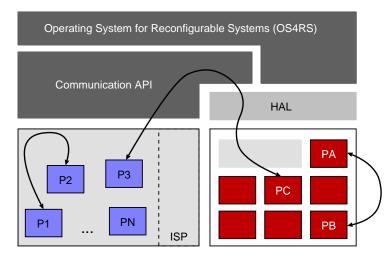

| 3.4  | Inter-task communication in the OS4RS system                            | 27 |

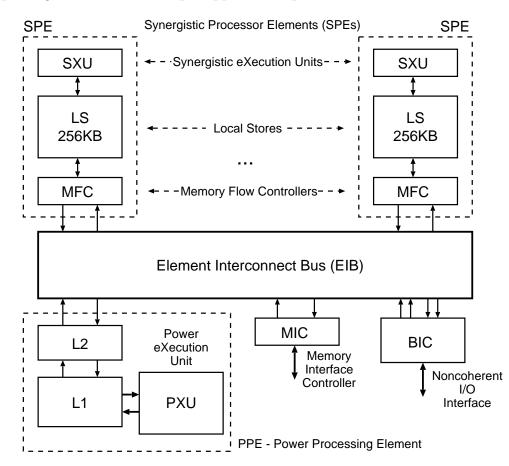

| 3.5  | Block diagram of the Cell processor                                     | 28 |

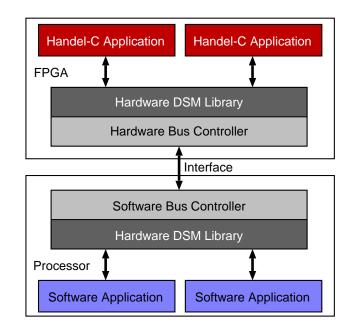

| 3.6  | Data streaming manager (DSM) for portable codesign                      | 30 |

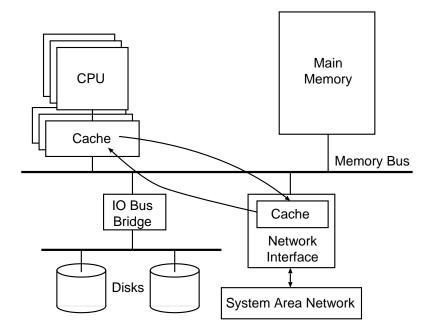

| 3.7  | Network interface with cache on memory bus                              | 31 |

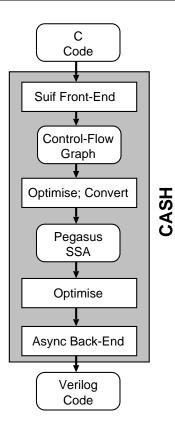

| 3.8  | Compiler for Application-Specific Hardware (CASH)                       | 33 |

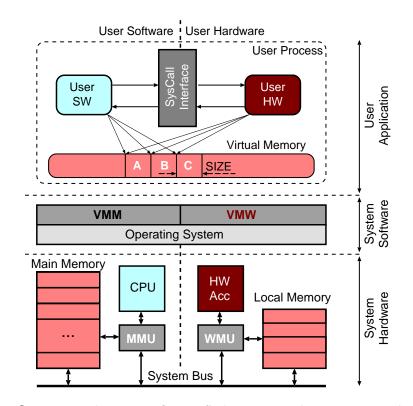

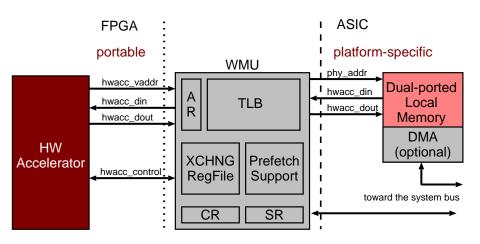

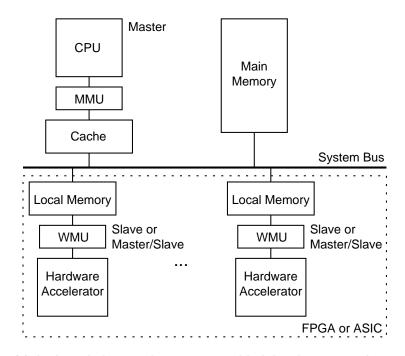

| 4.1  | Support architecture for unified memory abstraction                     | 36 |

| 4.2          | WMU structure and WMU interface to user hardware, local memory,            | 37              |  |

|--------------|----------------------------------------------------------------------------|-----------------|--|

| 4.3          | Calling the IDEA hardware accelerator through the <i>sys_hwacc</i> system  |                 |  |

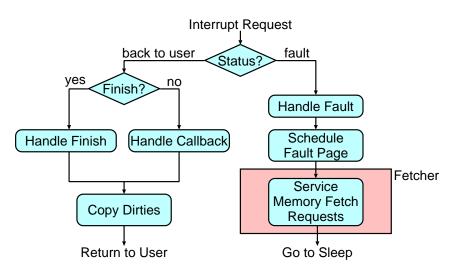

| 4 4          |                                                                            | 39              |  |

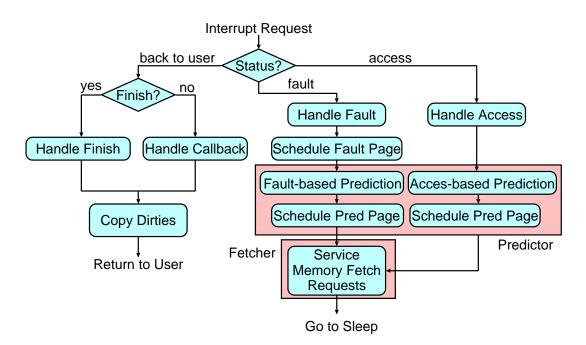

| 4.4<br>4 5   | Basic VMW interrupt handler                                                | $\frac{39}{41}$ |  |

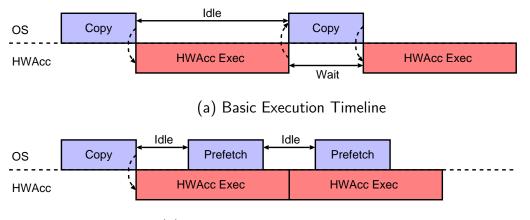

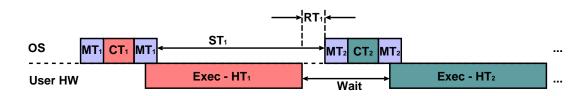

| $4.5 \\ 4.6$ | Execution timeline of virtual-memory-enabled hardware accelerator .        | $41 \\ 42$      |  |

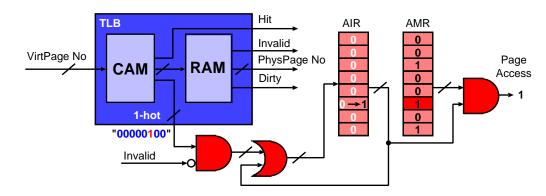

| 4.0<br>4.7   | Page access detection in the WMU                                           | $\frac{42}{43}$ |  |

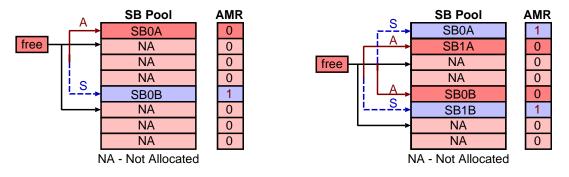

| 4.7          | Stream Buffer (SB) allocation and the AMR                                  | 43<br>43        |  |

| 5.1          | The operating system activities related to the hardware accelerator        |                 |  |

|              | execution                                                                  | 48              |  |

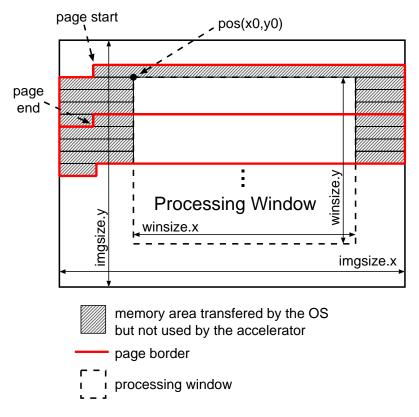

| 5.2          | Memory layout of an image                                                  | 50              |  |

| 5.3          | The operating system activities related to the hardware accelerator        |                 |  |

|              | execution                                                                  | 50              |  |

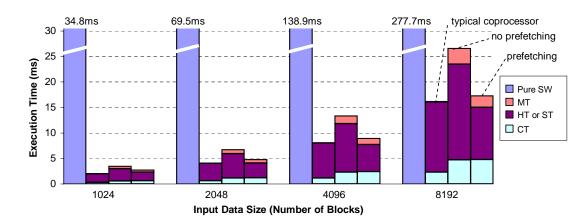

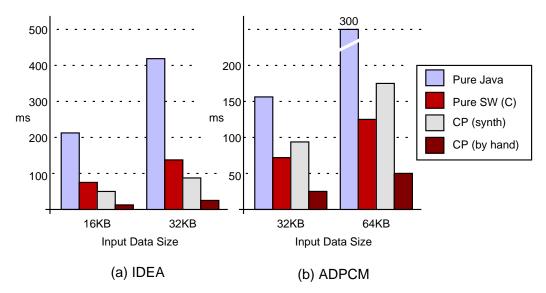

| 5.4          | IDEA execution times                                                       | 52              |  |

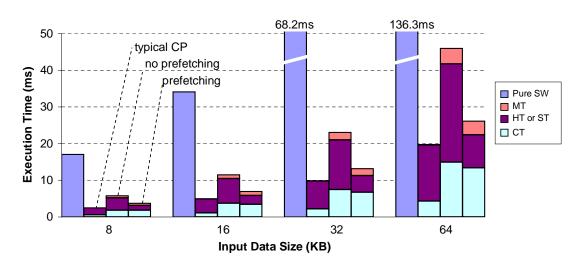

| 5.5          | ADPCM decoder execution times                                              | 52              |  |

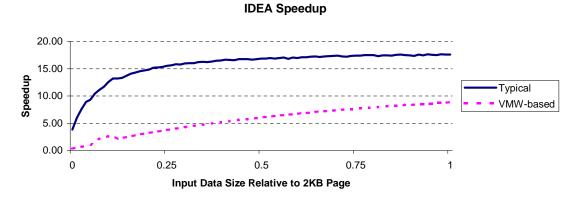

| 5.6          | Speedup for small input data sizes                                         | 55              |  |

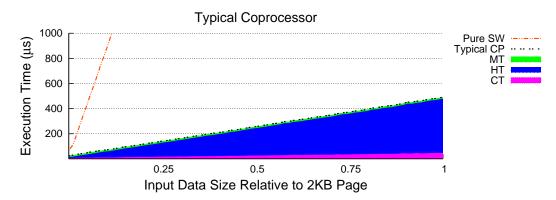

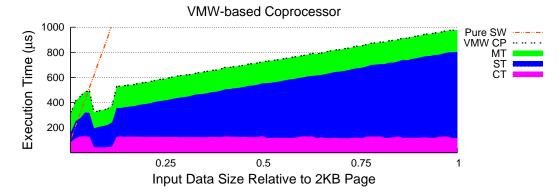

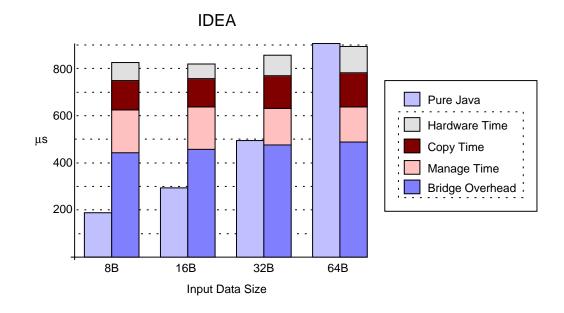

| 5.7          | Typical accelerator execution times for small input data sizes             | 55              |  |

| 5.8          | VMW-based accelerator execution times for small input data sizes $\ . \ .$ | 56              |  |

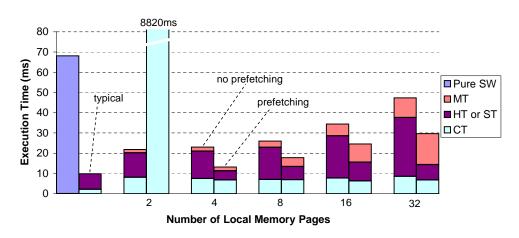

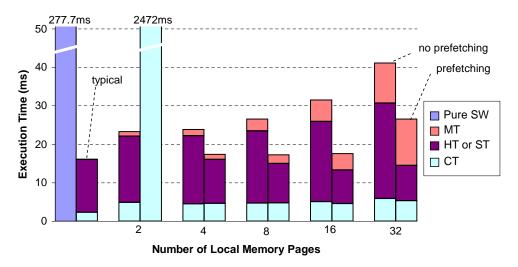

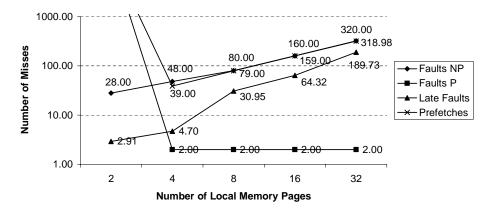

| 5.9          | ADPCM decoder performance for different number of VMW pages                | 57              |  |

| 5.10         | IDEA execution times for different number of local memory pages            | 57              |  |

| 5.11         | 1 0                                                                        | 58              |  |

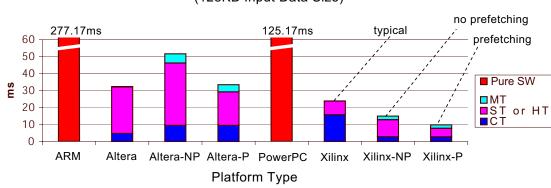

| 5.12         | Two different platforms run the same application                           | 59              |  |

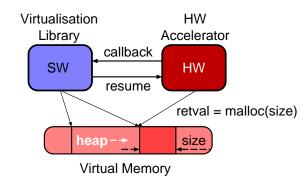

| 6.1          | $Memory \ allocation \ callback  . \ . \ . \ . \ . \ . \ . \ . \ . \ .$    | 62              |  |

| 6.2          | Supporting <i>malloc</i> callback                                          | 62              |  |

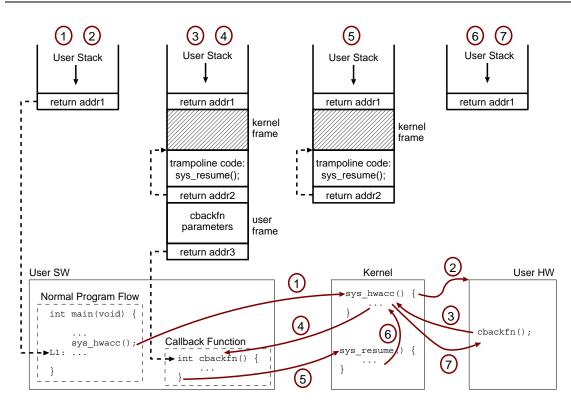

| 6.3          | Kernel mediation for hardware accelerators calling back software           | 64              |  |

| 6.4          | Handling memory transfers for hardware accelerators                        | 66              |  |

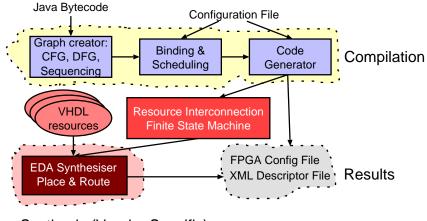

| 6.5          | Automated unrestricted synthesis flow                                      | 67              |  |

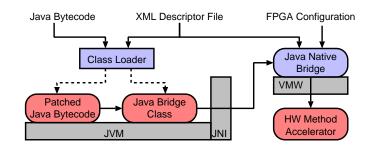

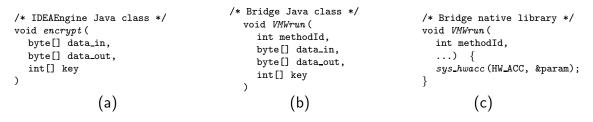

| 6.6          | Execution steps for an accelerator run from Java program                   | 68              |  |

| 6.7          | Invoking hardware accelerators from a Java application                     | 69              |  |

| 6.8          | Execution times of synthesised accelerators                                | 70              |  |

| 6.9          | Invocation overhead for small data sizes                                   | 71              |  |

| 7.1          | Multithreaded virtual-memory-enabled hardware accelerators                 | 74              |  |

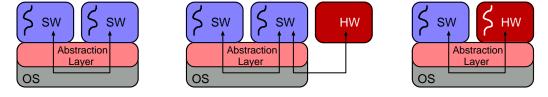

| 7.2          | Standard, wrapper-based, and extended multithreading of user soft-         |                 |  |

|              | ware and user hardware                                                     | 74              |  |

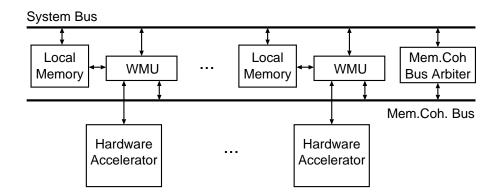

| 7.3          | Memory coherence support for multiple hardware accelerators                | 75              |  |

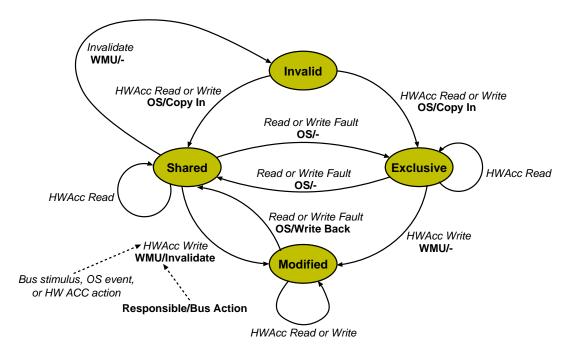

| 7.4          | State diagram for page-level memory coherence protocol                     | 76              |  |

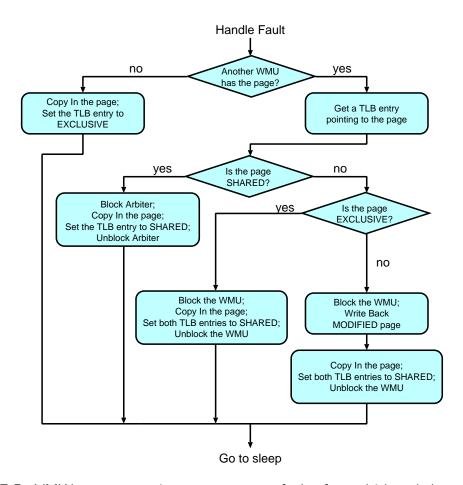

| 7.5          | VMW manager actions on a memory fault of a multithreaded accel-            |                 |  |

|              | erator                                                                     | 78              |  |

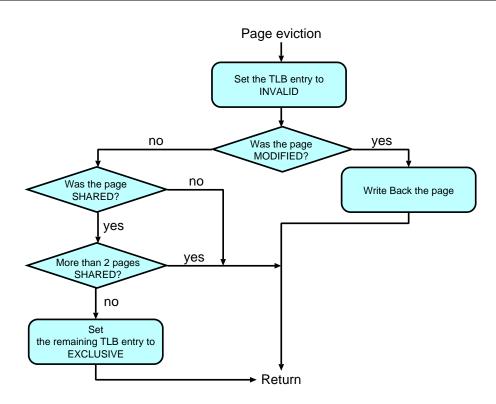

| 7.6          | VMW manager actions on evicting a page from the local memory               | 79              |  |

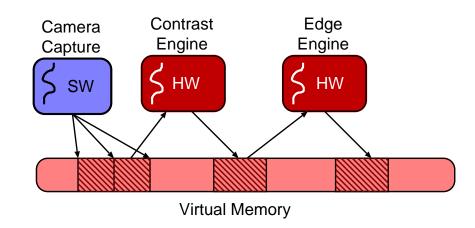

| 7.7          | Producer/consumer chain of threads for edge detection                      | 80              |  |

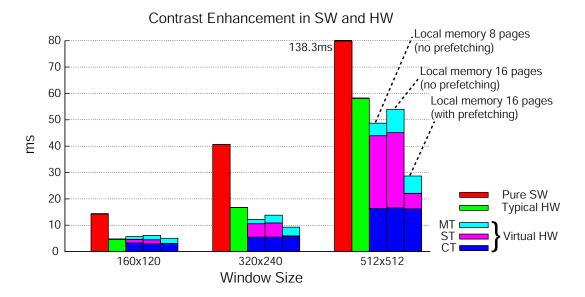

| 7.8          | Execution times of contrast-enhancement application                        | 80              |  |

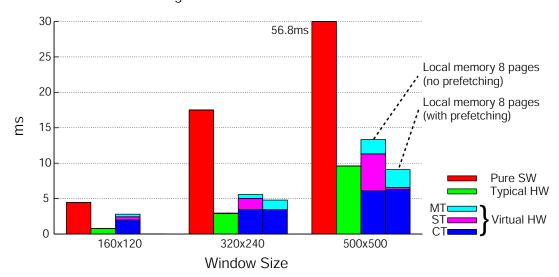

| 7.9          | Execution times of edge-detection application                              | 81              |  |

xii

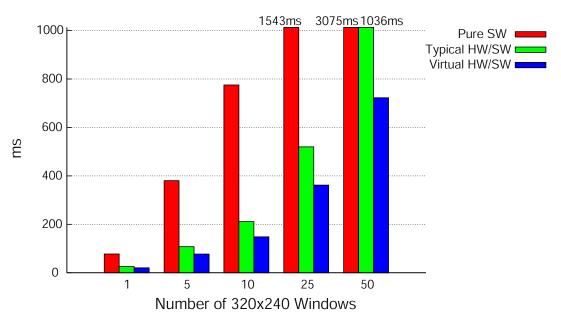

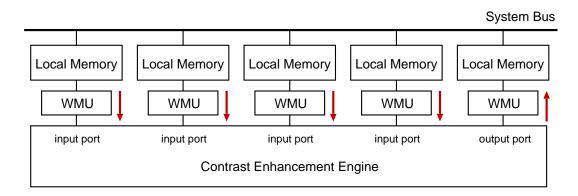

|                                        | Execution times for multithreaded image processing application 82<br>Contrast enhancement engine with multiple memory ports 83                                                                                       |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

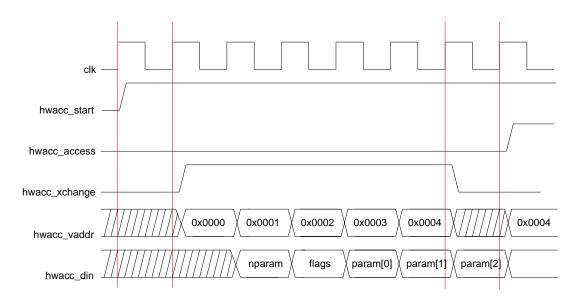

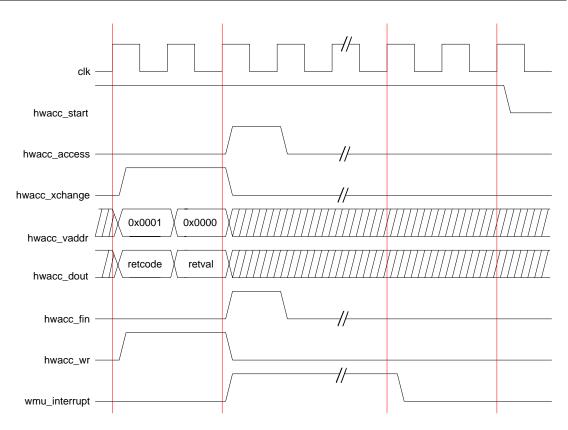

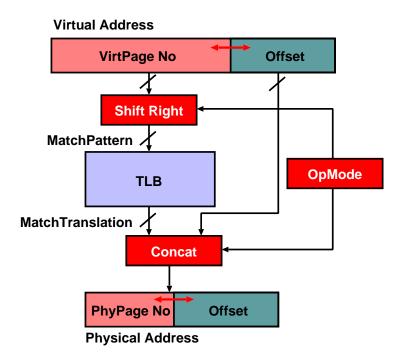

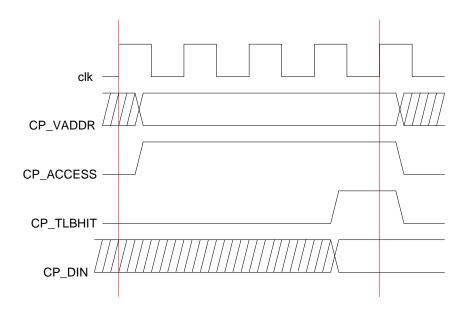

| A.1<br>A.2<br>A.3<br>A.4               | VHDL code of the WMU interface for hardware accelerators92Timing diagram showing the accelerator start up93Timing diagram showing the accelerator completion94WMU address translation and multiple operation modes95 |

| B.1<br>B.2                             | Invoking hardware accelerator through system call interface 98<br>The parameter exchange structure                                                                                                                   |

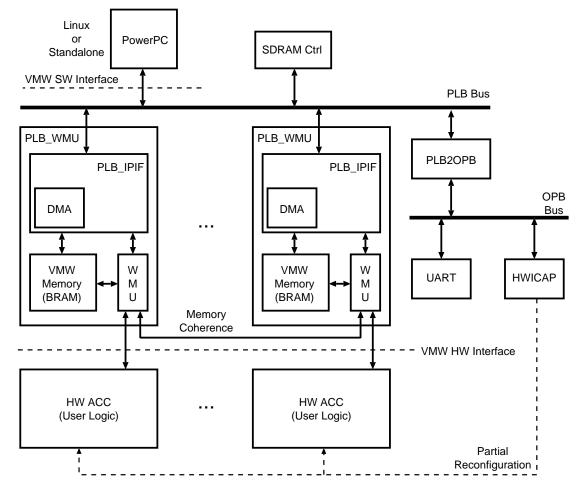

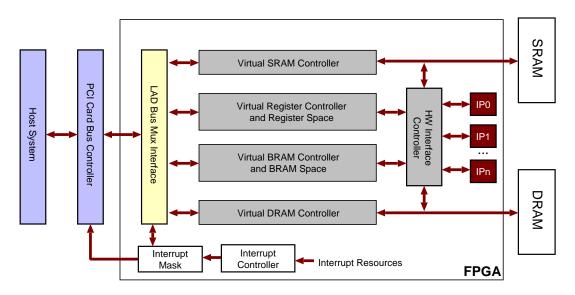

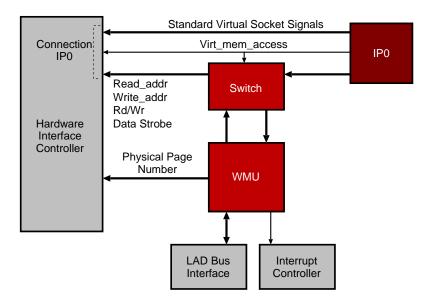

| C.1<br>C.2<br>C.3<br>C.4<br>C.5<br>C.6 | RokEPXA board102WMU integration within Altera device103The accelerator read access104Xilinx ML310 board105WMU integration within Xilinx device106Xilinx platform for multithreading107                               |

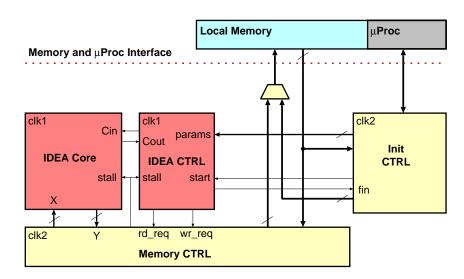

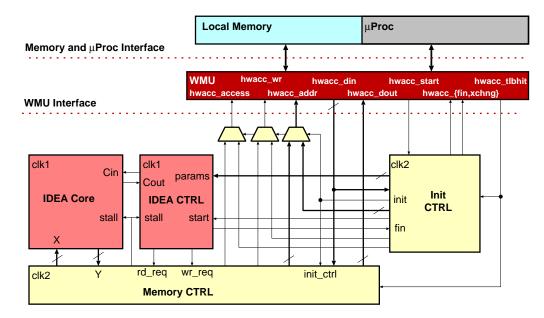

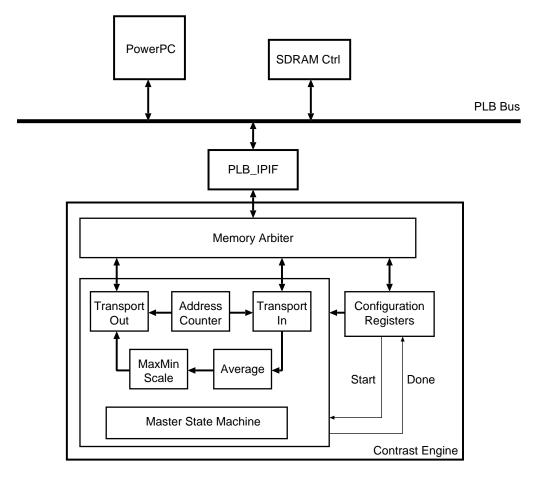

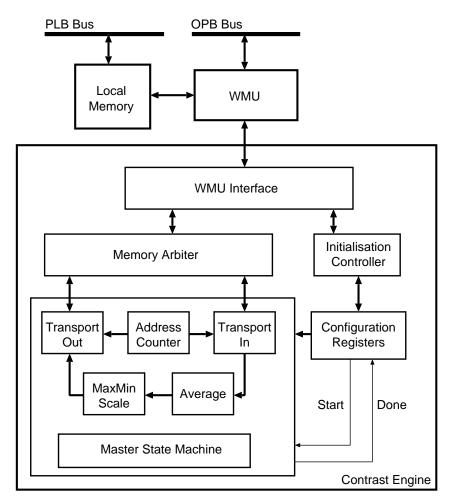

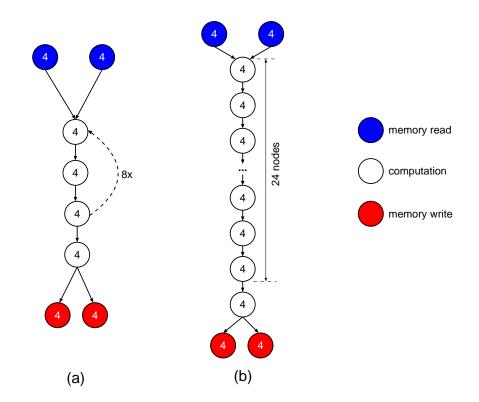

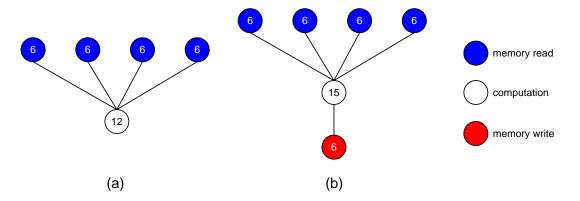

| D.1<br>D.2<br>D.3<br>D.4               | Typical IDEA accelerator accessing local memory                                                                                                                                                                      |

| E.1<br>E.2                             | Control-flow graph of the IDEA hardware accelerator                                                                                                                                                                  |

| F.1<br>F.2<br>F.3                      | Wildcard II reconfigurable PC Card122Virtual Socket framework123Virtual memory for Virtual Socket framework124                                                                                                       |

# Chapter

# Introduction

'The time has come,' the Walrus said,

'To talk of many things:

Of shoes—and ships—and sealing-wax—

Of cabbages—and kings—

And why the sea is boiling hot—

And whether pigs have wings.'

—Lewis Carroll, Through the Lookinglass

THIS thesis shows that an Operating System (OS) providing a unified process context for running codesigned hardware and software applications can (1) simplify software and hardware interfacing, (2) support advanced programming paradigms, and (3) enable runtime optimisations and unrestricted automated synthesis; all these benefits can be achieved for an affordable cost. In this introduction, we first recall major abstractions that system software provides to software-only user applications; then, we introduce our contribution, through the discussion on the lack of such abstractions for codesigned applications; finally, we present the organisation of the thesis.

## 1.1 User Applications and OS Processes

User applications are rarely run bare on the underlying system hardware. An abstraction layer created through system software provides the execution environment, eases programming, increases portability, improves security, and releases application programmers from managing and sharing system hardware resources (i.e., processors, memories, mass storage devices, input/output peripherals) [110, 116]. Such abstraction is to date either missing or incomplete for codesigned hardware and software applications. This thesis proposes a solution providing the unified and complete abstraction for codesigned applications.

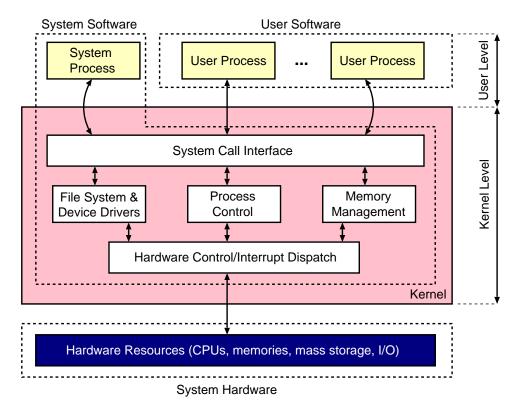

A process (or a task) is one of the basic concepts in the OS design: it represents an instance of a running user program [12, 116, 117]. Multiple processes can coexist and run in a computer system at the same time; they can share physical resources based on the OS services but still be screened from each other. Figure 1.1 shows several

system and user processes (software-only) running upon a Unix-like OS [13]. In the figure, we distinguish the following categories: *system hardware*, *system software*, and *user software*.

**Figure 1.1:** User software and system software running on system hardware. System software completely screens user software from system hardware.

System hardware represents hardware components of a computer system. The system hardware may comprise different resource types: computational resources (*Central Processing Units*—CPUs), memory resources (including mass storage devices), communication resources (human-computer interfaces, network interfaces), etc.

System software is responsible for controlling, integrating, and managing the individual hardware components of a computer system [126]. It runs on a CPU either as a *kernel* (i.e., software layer wrapping hardware components of the system [110, 116], running in a privileged mode of the CPU execution [4, 81, 105, 107]) or as a system process (running in an unprivileged mode of the CPU execution).

User software represents a user application, written and compiled by computer system users; it always runs on the CPU in user mode of execution; its use of system resources is restricted and managed by system software. The user software runs in the abstract context of an OS process and uses hardware resources exclusively through system services. The OS system call interface completely hides interfacing particularities and protects the system hardware from end users.

While running within the context of a process, user applications benefit from the virtual memory abstraction. Thanks to the system software support, any user program has an illusion of having the whole machine for itself: the process context comprises its own memory address space and the machine state. Wherever the code and data physically reside, user applications see the image of the linear address space; there is no notion of the physical memory capacity and organisation. Beside standardising the runtime environment, the OS process provides user applications with dynamic memory management facilities, through stack and heap mechanisms [104].

The benefits of user programs using system services are multiple: (1) parallelism even on uniprocessor systems—if a process is blocked in a system call waiting on an event, other processes can use the CPU for computation, (2) portability across different platforms—if architecturally different computer systems support the same system call interface, one should be able to port simply application code just by recompiling, (3) abstracted access to hardware—there is no need to know particular characteristics of hardware devices, (4) optimised resource sharing—the system software can optimise the resource usage based on the process behaviour. Although the overall performance of the system shown in Figure 1.1 is often suboptimal, the benefits of the abstraction are overwhelming.

# 1.2 Codesigned Applications in Software-centric Systems

We call codesigned hardware and software applications the applications that have some of their parts running on CPUs and the rest running in specialised hardware (i.e., hardware specifically designed to speed up and parallelise the execution of performance demanding tasks). Codesigned applications blend two models of computation [38]: (1) temporal computation (scarce hardware resources such as ALUs, shifters, multipliers are reused in time by the instruction sequence being executed); (2) spatial computation (where abundant hardware resources are wired and deployed in space—silicon area—to fit more closely the nature of the application, thus maximising the processing parallelism). Standard processors (especially those intended for embedded applications—typically smaller and slower than cutting-edge CPUs but more power efficient) are often extended with application-specific hardware accelerators [51, 58, 128] to achieve performance goals and meet power constraints. The approach becomes widely used, especially with recent developments in designing versatile Systems-on-Chip (SoC), the market growth of consumer appliances, and Field Programmable Gate Arrays (FPGAs) [3, 130] coming of age.

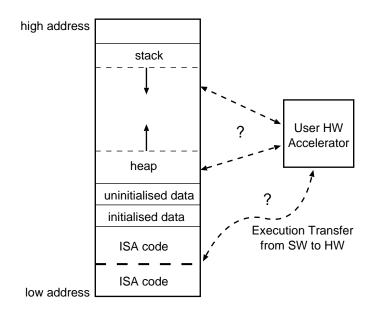

By extending the CPU with the application-specific hardware, codesigned applications consist of heterogeneous code: (a) the software part consisting of CPU instructions—typically generated by a compiler from a specification (program) written in a high-level programming language, and (b) the hardware part consisting of hardwired logic or FPGA configuration [38, 133]—typically generated by a synthesiser from a specification (description) written in a *Hardware Description Language* (HDL). Figure 1.2 shows a heterogeneous-code user program executing within the context of an OS process. The process executes on the CPU and, at one point

**Figure 1.2:** Memory space of mixed software and hardware process. Hardware accelerator does not belong to the context of the software process: it neither shares memory abstraction with software nor it uses standardised means of execution transfers.

in time, transfers the execution to the hardware accelerator; when the accelerator finishes the computation, it returns back the control to the software part. The hardware part of the code does not belong to the process context; there is neither virtual memory support, nor standardised means of hardware invocation—software programmers and hardware designers have to solve the interfacing for a particular architecture they use. This thesis addresses the problem of *user hardware* missing the abstractions that are already available to user software.

User hardware—application specific hardware accelerators running on behalf of user software—is semantically linked to a particular user application, since software and hardware parts of the application exhibit jointly some specified functionality and operate on the same data. We may think of FPGAs as a system-level resource available for implementing both user hardware (the FPGA is a computational resource for application-specific accelerators programmed with configuration in place of the ISA—Instruction Set Architecture—code) and system hardware (the FPGA is a control-building resource for system devices such as peripheral controllers).

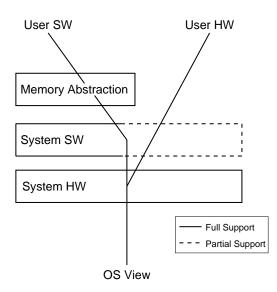

The Y-chart in Figure 1.3 shows the different levels of abstraction—provided and managed by the OS—visible to software and hardware parts of a traditional codesigned application running in a software-centric system. User software does not recognise user hardware as its peer. Abstraction levels (such as virtual memory and system-service interface) typically available to user software do not exist for user hardware.

The missing abstraction imposes limits on: (1) interfacing hardware and software parts of codesigned applications—while writing user software and while designing user hardware, software programmers and hardware designers have to be aware of specific interfacing details; (2) available programming paradigms—advanced programming concepts such as multithreading assume unified memory space and sys-

**Figure 1.3:** Levels of abstraction for traditional codesigned applications in a softwarecentric system. User hardware misses system abstractions available to user software.

tem-enforced memory consistency; (3) portability of codesigned applications across different platforms—it is burdensome for programmers to preserve their hardwareagnostic, high-level programming approaches, and it is challenging for hardware designers to write accelerators that can run across different platforms, without any change in the HDL code; (4) user hardware ability to use results of system services if there is no memory abstraction present, this is either cumbersome or even impossible (as an example, we can think of dynamic memory allocation). The thesis proposes a solution to remove the imposed limits.

### 1.3 Seamless Interfacing of Software and Hardware

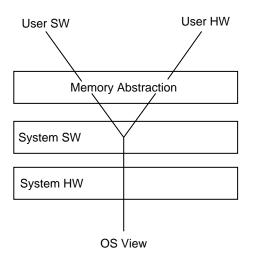

Our goal is to provide the missing abstractions for user hardware and bring user software and user hardware to the same conceptual level. We propose a unified process context for heterogeneous-code programs (consisting of user software and user hardware) to achieve transparent software and hardware interfacing and their seamless integration. In this way, by delegating platform-specific tasks to a system-level virtualisation layer, we also increase the portability of codesigned applications. The virtualisation layer provides unified memory abstraction for software and hardware processes and hides platform details from users as much as general-purpose computers do. It consists of an OS extension relying on a system hardware extension that provides (1) unified virtual memory, (2) execution transfers from software to hardware and vice versa (such that user hardware becomes able to callback software and use system services), and (3) multithreaded execution, for user software and hardware accelerators running within the same OS process. The presence of the virtualisation layer brings platform-agnostic interfacing and enables (1) dynamic optimisations of codesigned applications, and (2) unrestricted automated synthesis from high-level programming languages.

**Figure 1.4:** User software and user hardware as peers in a proposed system supporting codesigned applications. User hardware can run together with user software in the same execution context.

In contrast to Figure 1.3, Figure 1.4 shows the unified abstraction levels that we introduce visible by both user software and user hardware components of codesigned applications. We delegate the system specific tasks to the OS, which makes possible to extend the incomplete or missing abstraction layers from Figure 1.3 to the full boxes in Figure 1.4. The extended abstraction minimises the programmer and designer efforts, when interfacing user software and user hardware of codesigned applications. It also enables simultaneous execution of user hardware and user software within the same OS process. Although the introduction of an additional abstraction usually brings overheads, we show how its presence can be turned into additional advantages. More importantly, the advantages are achieved without any user intervention. Similar things happen in an OS, where system software screens the user from a number of runtime optimisations [12, 117].

# 1.4 Thesis Organisation

Our contribution, starting from a simple idea of unifying the execution context for software and hardware parts of codesigned applications, provides the first general evaluation of this concept in practice—on real reconfigurable systems. We show that—even with the overheads of our mixed software-and-hardware approach having unified memory for user software and user hardware is beneficial, in the terms of simplified hardware design and software programming, while the advantageous performance of spatial execution is only moderately affected. When building future systems for codesigned applications, designers can immediately rely on our results and our overhead analysis.

In Chapter 2, we illustrate problems of hardware and software interfacing to motivate our contribution. In Chapter 3, we present the state-of-the-art and discuss related hardware and software interfacing approaches, already-proposed OS-based extensions for reconfigurable applications, and existing portability solutions that in-

| what                | where     |

|---------------------|-----------|

| unified memory      | Chapter 4 |

| execution transfers | Chapter 6 |

| multithreading      | Chapter 7 |

**Table 1.1:** Our principal contributions and the corresponding chapters.

crease platform independence for codesigned applications. In the following chapters, we discuss different aspects of our contribution.

Table 1.1 summarises our principal contributions, by showing *what we add* (the first column) to form unified OS processes for running codesigned applications and *where we describe* (the second column) the corresponding implementation. Our contribution (marked in Table 1.1 by the numbers of the corresponding chapters— Chapter 4, 6, and 7) provides to OS processes running codesigned applications the abstractions, services, and programming paradigms already available to software-only processes.

We show an implementation of the unified virtual memory for mixed software and hardware processes in Chapter 4; there, we also explain the extensions of our implementation that enable dynamic, runtime optimisations to improve performance transparently to the end user—the virtual memory abstraction we propose not only introduces overheads but also brings additional advantages. We introduce a performance metric for heterogeneous computing in Chapter 5; afterwards, we perform experimental measurements on reconfigurable SoC platforms to show and discuss advantages and limited overheads of our unified memory scheme. In Chapter 6, we introduce the OS extensions supporting user hardware callbacks to user software hardware becomes capable of invoking system calls directly; then, we show how these extensions, together with the unified memory abstraction, enable unrestricted automated synthesis of hardware accelerators from high-level programming languages. Having unified memory abstraction between software and hardware is essential for supporting multithreaded programming paradigm. In Chapter 7, we extend the virtualisation layer to support multithreading for codesigned applications. Finally, we conclude the thesis in Chapter 8 and give directions for future work.

# Chapter 2

# Missing Abstractions for Codesigned Applications

Wovon man nicht sprechen kann, darüber muß man schweigen.

What we cannot speak of, we must pass over in silence. —Ludwig Wittgenstein, *Tractatus Logico-Philosophicus*

IN this chapter, we motivate the introduction of a unified process context for running codesigned applications by showing hardware and software interfacing problems in the case of typical existing architectures. The unified process abstraction that we introduce releases software programmers and hardware designers from interfacing problems. We discuss the system requirements to support this abstraction.

# 2.1 Process Model of Computation

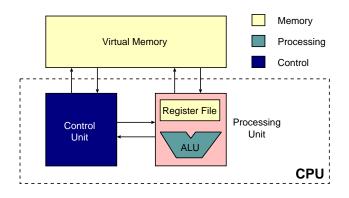

An OS process—in most of its implementations—provides to a user program running within its context a model of computation based on the *random-access machine* [102]—an abstract machine definition from theoretical computer science. The model features a CPU (with separate control and processing units) interconnected to a random-access memory (as shown in Figure 2.1). The CPU executes a program (a sequence of instructions) and operates on data. The program and the data are all stored in the random-access memory. The computation performed by the CPU from Figure 2.1—in its simplest implementation—is purely temporal [38]: hardware resources (such as ALUs) are reused in time by the instruction sequence being executed.

As Figure 2.1 shows, the process model provides a unique, virtual memory address space. The architectural improvements of the physical underlying machine (such as memory hierarchy, multiple issue, pipelined and out-of-order execution [56]) are typically hidden from ordinary users; at most, only system software and compilers—especially in the case of VLIW machines [41]—are concerned. A memory manager component of the system software (e.g., the *Virtual Memory*)

**Figure 2.1:** Process model of computation: a stored-program computer. The control unit fetches and executes the program stored in the random access memory. The program operates on data also stored in the same memory.

*Manager*—VMM—of the OS) provides the virtual memory abstraction, no matter what is the organisation of the underlying physical memory.

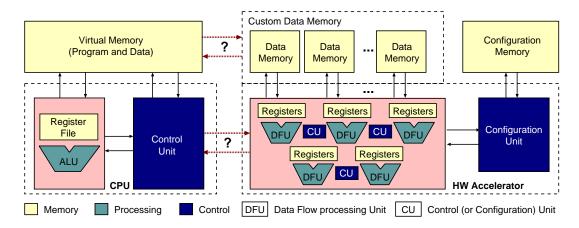

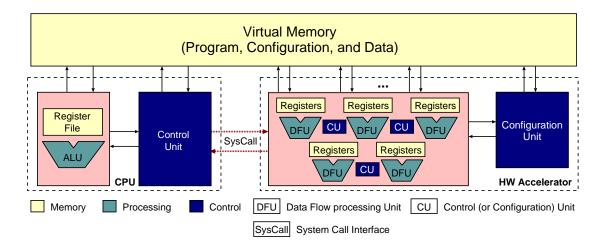

Figure 2.2 depicts the temporal computation machine from Figure 2.1 extended with a spatial computation engine—an application-specific hardware accelerator. In contrast to the CPU from Figure 2.1, we can notice the following differences: (1) the hardware accelerator employs custom processing units (*Data-Flow processing Units*—DFUs) deployed in space and tailored to fit as much as possible a specific application data-flow; (2) there is no centralised register file in the hardware accelerator but the data local to the computation are stored in distributed registers corresponding to the data-flow; (3) the number and the size of memory ports are custom to the application; (4) there is no centralised control, it is rather distributed across the accelerator; (5) the configuration (in the case of reconfigurable hardware accelerators) or hardwired logic gates (in the case of ASIC hardware accelerators) determine the behaviour of the accelerator, not the sequence of programming instructions.

**Figure 2.2:** Blending temporal and spatial ways of computation. The hardware accelerator performs application-specific computation. There is no common address space between software and hardware. Furthermore, there is no standardised way of execution transfers.

Although the machine from Figure 2.2 may run a given application faster than the temporal machine from Figure 2.1, we notice that the virtual memory abstraction and the neat programming environment have disappeared: (1) user software and user hardware do not share the memory address space—it is typically on the application programmer to arrange the communication and data transfers; (2) there is no standardised way of execution transfer—it is again on the application programmer to explicitly control the hardware accelerator; (3) system services are only partially available to user hardware—programmers may use software wrappers to call system services on behalf of the user hardware. In the following sections, we illustrate the software programming and hardware design issues for typical existing architectures running codesigned applications [17, 72, 112].

## 2.2 Typical Architectures: Accessing Memory

Having disjoint memory address spaces for user software and user hardware exposes data communication to users; it is the task of software programmers and hardware designers to arrange memory transfers from software to hardware address spaces and vice versa. In this section, we show typical arrangements for hardware accelerator accesses to the memory.

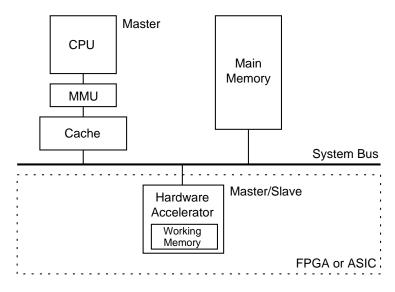

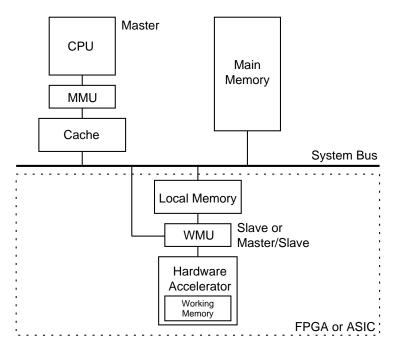

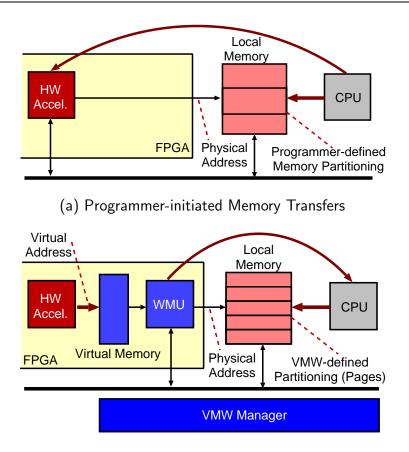

**Figure 2.3:** Typical hardware accelerator accessing local memory. While user software has an ideal image of the memory provided by virtual memory mechanisms, user hardware generates physical addresses of the local memory. It is the task of the programmer to arrange the communication between user software and user hardware.

Figure 2.3 shows a possible implementation of the machine from Figure 2.2: the hardware accelerator (user hardware) directly accesses a local on-chip memory to perform the computation. The user software, running on the CPU, has a perfect, linear image of the memory provided by the virtual memory manager of the OS [116]. For speeding up the execution, a system hardware unit called *Memory Management Unit* (MMU), and often integrated within the CPU [56] supports the translation of

virtual memory addresses. In contrast to the user software, the user hardware is directly interfaced to the system hardware and generates physical memory addresses for fast accesses to the local memory. The programmer controls the accelerator and accesses its local memory through a memory mapped region (this assumes using the *mmap* system call of the OS).

|                                        | /* HW accelerator version accessing local memory */                                                    |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|

|                                        | <pre>idea_block *buff =     mmap(0, sizeof(idea_block), LMEM_PHYADDR);</pre>                           |

| <pre>/* Software-only version */</pre> | <br>data_chunk = LMEM_SIZE / 2;                                                                        |

| <pre>idea_block A[n64], B[n64];</pre>  | <pre>while (data_ptr &lt; n64 * sizeof(idea_block)) {     memcpy(buf, A + data_ptr, data_chunk);</pre> |

| <br>idea_cipher_sw(A, B, n64);<br>     | <pre>IDEA_CTRL_REG = START;<br/>while(*IDEA_STATUS_REG != FINISH);<br/>IDEA_STATUS_REG = INIT;</pre>   |

|                                        | <pre>memcpy(B + data_pt, buf + data_chunk, data_chunk); data_ptr += data_chunk;</pre>                  |

|                                        | }                                                                                                      |

| (a)                                    | (b)                                                                                                    |

**Figure 2.4:** Programming for the IDEA cryptography application: software-only version (a) and HW accelerator version (b). Software-only case is neat and clean. The presence of the hardware accelerator demands programmer activities for controlling the accelerator, partitioning the data, and scheduling data transfers.

If the memory size is limited, the programmer is responsible for partitioning the data and scheduling the data transfers. Figure 2.4 compares programming of the IDEA cryptography application [82] for its software-only and codesigned implementations. The software-only version (in Figure 2.4a) just invokes the encryption function by passing the pointers to the input and output IDEA blocks. On the other side, using the hardware accelerator (in Figure 2.4b) demands partitioning the data to fit the local memory, transferring the data explicitly from the main memory to the local memory and the other way around, and iterating until the computation is finished. Although it is not a difficult task, it is quite burdensome and demands programmer's knowledge of the hardware memory access pattern. In principle, the local memory serves as a software managed cache or scratchpad [113].

Figure 2.5 shows another approach with a hardware accelerator capable of initiating master transactions on the system bus and directly accessing the main memory. The user software is responsible for controlling the accelerator and passing the physical addresses of a fixed memory region, previously reserved by the OS. Since user hardware generates physical addresses of the main memory, an erroneously-designed or malicious accelerator may cause nondeterministic behaviour and crashes of the whole system.

With the assumption that a large amount of the physical memory is available (which may not be always true, especially in the embedded applications), the programming is made simpler (as Figure 2.6b shows for an image processing application [15]) and closer to the pure software (shown in Figure 2.6a); there is no more need to partition and copy data iteratively. However, single accesses to the main

**Figure 2.5:** Typical hardware accelerator accessing main memory. While user software has an ideal image of the memory provided by virtual memory mechanisms, user hardware generates physical addresses of the main memory. It is the task of the programmer and hardware designer to arrange the communication properly.

memory are rather expensive. To overcome this drawback, the hardware designer has to manage and implement burst accesses to the main memory, which imposes creating buffers and local memory management on the hardware side: the programmer's burden from Figure 2.4b has not disappeared but *is just shifted to the hardware designer*; instead of managing the memory in user software, it becomes the task of user hardware. In the case of applications that exhibit multiple input and output data streams (as is the case with the contrast enhancement application from Figure 2.6b—four input images and one output image), the hardware designer would have to manage the corresponding number of input and output data buffers—filled and emptied by burst transfers—and synchronise them with the accelerator.

Our contribution liberates software programmers and hardware designers from burdensome memory transfers. We delegate the memory interfacing tasks to system software and system hardware. Chapter 4 explains a novel system architecture providing unified memory abstraction for user software and user hardware.

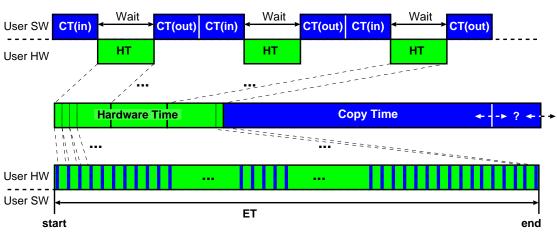

**Performance Analysis.** Figure 2.7 sketches possible execution timelines of the two presented typical approaches for a given application. The overall *Execution* Time (ET) of the approach with the local memory is the sum of the Copy Time (CT) and pure Hardware execution Time (HT). The overall execution time (ET) of the approach with the main memory consists of hardware executions interleaved (or partially overlapped if bursts are supported) with master memory accesses. If we assume identical computation cores of the hardware accelerators, the pure hardware execution time is the same: the overall performance figure depends on the effectiveness of memory transfers.

It is debatable which of the two approaches is better. A programmer responsible for data transfers to the local memory can overlap computation with data transfers (by dividing the local memory in two halves—the first processed by the hardware and

/\* HW accelerator version

```

accessing main memory */

/* Software-only version */

unsigned char *resimg =

mmap(0, imgsize, RES_PHYADDR);

unsigned char outimg[imgsize],

unsigned char *inpimg[i] =

inpimg[4][imgsize];

mmap(0, winsize,INPi_PHYADDR);

\verb|contrast\_enhancement\_sw||

memcpy(inpimg[i], cam_out[frame_i], winsize);

(outimg, inpimg, winsize, imgsize);

CONTRAST_CTRL_REG = START;

while (*CONTRAST STATUS REG != FINISH):

CONTRAST_STATUS_REG = INIT;

memcpy(outing, resimg, winsize);

(a)

(b)

```

**Figure 2.6:** Programming for the contrast enhancement application: software-only version (a) and HW accelerator version (b). Software-only case is neat and clean. The presence of the hardware accelerator demands controlling the accelerator and using *mmap()* system call.

the second used for copying) or use a DMA (although this would mean descending from the user-level to system programming) to speed up the process. A hardware designer responsible for memory accesses to the main memory can use burst accesses and hardware-managed buffers to improve the performance. Whichever of the two approaches an application architect chooses, the memory management tasks, which are normally delegated to the system, burden the user-level software and hardware: pushing the management of the memory hierarchy from the programmer toward the virtual memory manager and the cache controller is the analogous assignment of the general computer architecture.

## 2.3 Typical Architectures: Callbacks to Software

There are some cases in which hardware accelerators may want to call back software. For example, hardware may request software to invoke a system call, service an exception, demand an external computation, display the accelerator status, or send a message to some other application part (Chapter 6 shows callbacks to software required for mapping high-level languages to hardware).

Programmers and designers wanting to support hardware callbacks to software encounter two principal difficulties: (1) writing additional code to service callbacks is necessary, and (2) parameter passing conventions are not standardised but rather chosen in an *ad-hoc* manner. The additional obstacle is the lack of the unified memory between software and hardware: if there is no memory abstraction present, some software return values can be completely useless to hardware (we can take malloc() function as an example).

While the runtime environment implements a *calling sequence*—the sequence of instructions and data arrangements necessary to perform a function call [2]—for software-only applications (usually through stack management), no such arrangement exists for codesigned applications; the programmer has to write the code that

Hardware Accelerator Accessing Local Memory

Hardware Accelerator Accessing Main Memory

**Figure 2.7:** Execution timelines of typical hardware accelerators. The execution time of the typical hardware accelerator accessing local memory consists of memory transfer intervals (in user software) and hardware execution intervals (in user hardware). The execution time of the typical hardware accelerator accessing main memory consists of interleaved short memory-access intervals (using system bus transactions) and hardware executions intervals. If one assumes the same computation cores, summing up hardware intervals for both accelerators gives the same amount of time spent in hardware execution. What matters to the overall performance is the effectiveness of memory accesses.

supports parameter exchange and hardware callbacks to software. Figure 2.8 shows an example code servicing multiple callback requests generated by a hardware accelerator. After launching the accelerator, the program loops until the FINISH signal arrives. Depending on a callback identification (FPCOMP\_ID for a floating point computation, MSEND\_ID for sending a message) received from the hardware, the programmer prepares invocation parameters and calls the appropriate software function. Once the function returns, the programmer passes the return value supposedly non-void—to the accelerator and resumes its execution. The nonexistent memory abstraction brings additional complexity (similarly to what Figure 2.4b shows) to the code.

Our contribution shifts the parameter passing and function invocation tasks from the user to the system. With the execution transfers supported by the OS and assuming a unified memory abstraction, hardware accelerators become capable of using any system service or function from the standard library. Chapter 6 demonstrates how an OS can provide transparent execution transfers for hardware accelerators invoking software functions, be it system services or library calls.

# 2.4 Typical Architectures: Multithreading

The lack of unified memory and system-level support for codesigned applications narrows available programming paradigms. For example, running multithreaded

```

/* Typical HW accelerator calling back software */

HWACC CTRL REG = START:

while (*HWACC_STATUS_REG != FINISH) {

switch(*HWACC_CBACK_ID) {

case FPCOMP_ID: ...

fpcomp (p1,p2); ...

HWACC_CTRL_REG = RESUME;

break;

case MSEND_ID: ...

msend(p1)); ...

HWACC_CTRL_REG = RESUME;

break;

default:

... printf("Unknown callback ID."); ...

break;

}

}

. . .

```

**Figure 2.8:** Servicing hardware accelerator callbacks to software. The programmer has to examine the callback identifier and, then, to dispatch the execution toward the corresponding function.

codesigned applications (in software-centric systems) demands additional activities on the programmer side to perform memory transfers and enforce memory consistency.

Figure 2.9a shows a simple program computing the sum of two vectors, using a POSIX-like [88] thread management. In the master thread, the programmer declares the vector pointers and the identifier of the slave thread function, initialises the vectors, and creates the slave thread by invoking the thread creation function (*thread\_create*). Thread creation is similar to a function call, except that the caller and the callee continue their execution simultaneously (from the programmer's perspective) and perform their work in parallel. After doing some work simultaneously, the master eventually synchronises with the slave through the join primitive (i.e., it waits until the slave returns). The two threads share the virtual memory address space and they use the same memory pointers. Once the computation is finished, the master thread can immediately access the results through its pointer to the result vector C.

The fact that the threads share the same virtual memory address space (as Figure 2.10a indicates) is one of the crucial concepts of multithreading: the threads share the same memory, while having separate execution stacks.

We suppose now that the designer decides to move the vector-addition slave thread to hardware execution. Similarly to what we have seen in Section 2.2, without system-level support for threads executed in hardware, the programmer needs to take explicit care of the communication between the application software and hardware components. The master thread is unchanged, while a wrapper thread is now needed in order to control and transfer data to the hardware accelerator which is now responsible for the computation (Figure 2.9b shows a solution for integration of the hardware accelerator, using a software wrapper thread). The wrapper thread initialises the accelerator, copies data to the accelerator local memory, and launches

```

/* Master Thread */

void main() {

int *A, *B, *C;

int n;

int thr_id;

read(A, n);

read(B. n):

/* Master Thread */

thr_id = thread_create(add_vectors, A, B, C, n);

void main() {

do_some_work_meanwhile();

int *A, *B, *C;

thread_join(thr_id);

int n;

int thr_id;

}

read(A, n);

/* Wrapper Thread */

read(B, n);

void add_vect(int *A, int *B, int *C, int n) {

thr_id = thread_create

int d_chunk = BUF_SIZE / 3;

(add_vect, A, B, C, n);

int *d_ptr = 0;

/* initialise accelerator */

do_some_work_meanwhile():

thread_join(thr_id);

write(HWACC_CTRL, INIT);

. . .

while (d_ptr < n) {

}

copy(A + d_ptr, BUF_BASE, d_chunk);

/* Slave Thread */

copy(B + d_ptr, BUF_BASE + d_chunk, d_chunk);

void add_vect(int *A, int *B, int *C, int n) {

/* launch accelerator */

int i;

write(HWACC_CTRL, ADD_VECT);

for(i = 0; i < n; i++)</pre>

while () {

C[i] = A[i] + B[i];

if (read(HWACC_STATUS) == FINISHED) {

copy (BUF_BASE + 2*d_chunk,

}

}

C + d_ptr, d_chunk);

break;

} else {

do_some_work_meanwhile();

}

}

d_ptr += d_chunk;

} ...

}

(a)

(b)

```

**Figure 2.9:** Multithreaded code for software-only (a) and hardware accelerator version (b) of codesigned application. In the software-only case, the threads use the same memory pointers. In the codesigned case, the programmer has to write a wrapper.

the computation. Since the input data does not necessarily fit to the local memory of the accelerator, the wrapper iteratively copies data back and forth, until all the data are processed. The hardware accelerator and the software threads do not share the same memory address space (as Figure 2.10b shows).

For a codesigned application with multiple threads in hardware, the programmer has to create a wrapper thread per hardware accelerator. Changing the HDL code of a hardware accelerator and its memory access pattern may require changes in the wrapper thread—the interfacing details burden software programmers and hardware designers.

Our contribution enables wrapper-free and access-pattern-independent multithreaded execution of user software and user hardware. Chapter 7 presents the system-level extensions to enforce memory consistency and support synchronisation, thus enabling multithreaded programming paradigm for codesigned applications.

**Figure 2.10:** Multithreading memory perspective for software-only (a) and hardware accelerator (b) version of the codesigned application. In the software-only case, the threads share the same memory. In the case with the hardware accelerator, software and hardware address spaces are separate.

# 2.5 Unified Process Context for Codesigned Applications

To overcome the interfacing burdens and to enable user hardware invoking system services and software functions, we propose a system-supported, unified process context for machines that combine temporal and spatial models of computation (as Figure 2.11 shows). Having unified processes for codesigned applications simplifies the interfacing, memory communication, and execution transfers between user software and user hardware, thus allowing seamless integration of software and hardware application parts. The introduced high-level abstraction does not mean abandoning the performance benefits of application-specific execution and custom-memory architectures (as we will show later in this thesis).

**Figure 2.11:** A heterogeneous-code unified-memory computer. The CPU executes the ISA code and performs temporal computation; the hardware accelerator performs spatial computation. Both share unified memory abstraction (where program, configuration, and data are stored) and use the system support for execution transfers between software and hardware application parts.

We propose making hardware accelerators capable of (1) accessing virtual memory and sharing the address space with software to enable transparent memory communication and screen user software and user hardware from the interfacing details, and (2) implementing a common calling sequence with software to support transparent execution transfers and user hardware callbacks to user software.

**Figure 2.12:** Hardware accelerator capable of accessing virtual memory of user process through *user hardWare memory Management Unit* (WMU), in a similar way as user software does through MMUs.

Figure 2.12 shows an architecture that allows an application-specific hardware accelerator to run in the process context of their peer software. Not only the unified process can simplify hardware and software interfacing but it can allow hardware accelerators to benefit—*transparently and without any need for user intervention*—from spatial and temporal locality of memory accesses (a well-known and largely-exploited concept from general-purpose computing).

Assuming the system-level support for unified processes, programming such a system is straightforward. In the programming presented in Figure 2.13, whatever the size of the data to process, the programmer can just pass the data pointers (A and B) and the number of blocks to encrypt (n64) to the hardware accelerator. There is no need to partition the data and schedule the transfers, as was the case for the typical approach shown in Figure 2.4b. It is the responsibility of system software and system hardware, as it is the case in the general-purpose computing systems.

On the hardware side, having the virtual memory abstraction allows the hardware designer to write HDL code independent of the memory size and location. It is the task of the system to ensure that the requested data is brought to the local memory acting as a cache. There is no need for either burst accesses or explicit buffering. The action is completely invisible for the hardware designer and, again, /\* Virtual memory-enabled hardware version \*/

idea\_block A[n64], B[n64];

...

idea\_cipher\_hw(A, B, n64);

**Figure 2.13:** Programming for the IDEA cryptography application with a virtualmemory-enabled hardware accelerator. The accelerator is capable of accessing the data to process through the virtual memory pointers to the user address space.

it is on the system to perform it transparently. In a similar manner, the memory hierarchy in general-purpose systems is managed transparently to the end user (e.g., cache block transfers and virtual address translations).

Figure 2.14 compares excerpts of a VHDL-like code for both the typical and the virtual-memory-enabled IDEA hardware accelerators. While writing the code for the typical hardware accelerator, the hardware designer has to (1) use physical addresses of the local memory, (2) be aware of the memory size, and (3) arrange the memory partitioning in accordance with the programmer. The code is inherently platform dependent. While writing the code for the virtual-memory-enabled hardware accelerator, the hardware designer does not care about these tasks. The accelerator generates virtual memory addresses and the system provides translation and synchronisation: the user code becomes portable.

```

-- Initialisation with runtime-dependent

-- Initialisation

-- virtual memory pointers

-- with platform-dependent addresses

ptr_a <= A;

ptr_a <= LMEM_BASE;</pre>

ptr_b <= B;</pre>

ptr_b <= LMEM_BASE + LMEM_SIZE/2;</pre>

i := 0;

- Computation

-- Computation

cucle 1:

cycle 1:

-- partition of A[]

-- object A[]

LMEM_PHYADDR <= ptr_a;

VMEM_VIRTADDR <= ptr_a;</pre>

LMEM_ACCESS <= '1':

VMEM_ACCESS <= '1';</pre>

LMEM_WR <= '0';

VMEM_WR <= '0';

cycle 2:

cycle 2:

reg_a <= DATAIN;</pre>

reg_a <= DATAIN;

cycle 3:

cucle 3:

reg_b := IDEA(reg_a);

reg_b := IDEA (reg_a);

-- an element in a partition of B[]

-- any element in B[]

LMEM_PHYADDR <= ptr_b;

VMEM_VIRTADDR <= ptr_b;</pre>

DATAOUT <= reg_b;

DATAOUT <= reg_b;

LMEM_ACCESS <= '1';

VMEM ACCESS <= '1':

LMEM_WR <= '1';

VMEM_WR <= '1';

ptr_{a,b} <= ptr_{a,b} + 1;

ptr_{a,b},i <= ptr_{a,b},i + 1;

if (ptr_b = LMEM_BASE + LMEM_SIZE) then

if (i = n64) then

-- finished for a data chunk

-- finished for the entire vectors

partial_finish;

finish:

else

else

cycle 1:

cycle 1;

end if;

end if:

(a)

(b)

```

**Figure 2.14:** Platform-dependent (a) and portable (b) VHDL-like code of the hardware accelerator. The platform dependent code reflects the limited size of the local memory and uses physical memory addresses. The portable code uses virtual memory addresses with no notion where the data actually reside.

**System Requirements.** To achieve our goal of having unified process context for codesigned applications, we need (1) system hardware support for user hardware invocation, virtual address translation, and memory coherence enforcement, and (2) system software support for steering these activities and enabling the interoperation with user software. In general-purpose computer systems, memory management units (MMUs) and cache controllers [33, 56] represent the system hardware responsible for virtual address translation and transparent and coherent memory hierarchy. The OS kernel, in turn, represents the system software responsible for managing the hardware and for providing the process model of computation to user software. It is the responsibility of system designers to decide how to partition—between system software and system hardware—the task of providing the process and memory abstractions. Researchers have explored different approaches [95], many of them being demonstrated in practice [1, 16, 74].

We choose a mixed software and hardware scheme that employs (1) a hardware translation engine (the user hardWare memory Management Unit—WMU—from Figure 2.12) and (2) an OS extension. The scheme slightly trades off performance for applicability to a wide range of reconfigurable SoCs; there are no hardware requirements regarding the system-bus capability to support memory coherence. Our approach is not limited to reconfigurable SoCs, although we primarily target these devices in our case studies. Following the state-of-the-art (in Chapter 3), we present details of our architecture, and demonstrate its prevailing benefits and limited drawbacks in Chapters 4, 5, 6, and 7. We also show that performance is not significantly affected, despite the inherent overhead of our scheme.

# Chapter 3

# State of the Art

Grâce à l'art, au lieu de voir un seul monde, le nôtre, nous le voyons se multiplier et autant qu'il y a d'artistes originaux, autant nous avons de mondes à notre disposition, plus différents les uns des autres que ceux qui roulent dans l'infini, et bien des siècles après qu'est éteint le foyer dont il émanait, qu'il s'appelât Rembrandt ou Ver Meer, nous envoient encore leur rayon spécial.

—Marcel Proust, Le Temps Retrouvé

BOTH research and industry have tackled a large number of issues from hardware and software codesign, bus wrappers and memory subsystems for embedded computing, programming paradigms and OS-support for reconfigurable computing, and general hardware and software interfacing. In this chapter, we present the state-of-the-art and distinguish our contribution from related works.

We first show in Section 3.1 how our research relates to industry standardisation efforts for providing IP-level design reuse and portability, and to research on memory wrappers and memory subsystems for embedded computing. Then, in Section 3.2, we compare our work to major approaches of reconfigurable computing for extending standard CPUs with application-specific hardware accelerators. In the same section we also discuss related work on parallel programming paradigms for reconfigurable computing, and we present the status of the research on OSs for reconfigurable computing. In Section 3.3, we show existing approaches also offering portable and seamless interfacing between software and hardware. Section 3.4 presents related work that motivated our user-transparent dynamic optimisation technique. Finally, Section 3.5 compares existing work on high-level synthesis with our unrestricted automated approach.

## 3.1 Memory Wrappers and Subsystems

The increasing need for IP-reuse and component-based system design motivates abundant industrial and research activities regarding memory abstractions and communication interfaces. On the industry side, many standardisation efforts have facilitated interconnecting IP blocks that come from different sources. For example, AMBA [8] and CoreConnect [59] are some well-known industry standards for onchip bus interconnections. Going one step further, the *Virtual Component Interface*  (VCI) is a standard [71] that separates bus-specific interfacing logic from the internal functionality of IP blocks; in this way, it hides the details of the underlying bus interface from the IP designer. On the research side, many researchers have addressed memory wrappers and transparent bus interconnections. For example, Lyonnard et al. [78] and Gharsalli et al. [49] propose automatic generation of application-specific interfaces and memory wrappers for IP designs. Similarly, Lee and Bergmann [69] introduce an interfacing layer that automates connecting IP designs to a wide variety of interface architectures. The main originality of our idea, with respect to the standardisation efforts and wrapper-related works, is not in the abstraction of the memory interface details (signals, protocols, etc.) between generic producers and consumers, but in the dynamic allocation of the interfacing memory, buffer, or communication ports between a processor and a hardware accelerator—that is the implication of the OS in the process.

Extensive literature exists on the design and allocation of application-specific memory systems, typically for ASIC end SoC designs (e.g., Catthoor et al. [28] discuss methodologies for custom memory management, while Panda, Dutt, and Nicolau [91] survey different memory issues for SoCs). In most cases, the existing approaches are compiler-based static techniques consisting of (1) design methodologies for customising the ASIC memory hierarchy for specific applications and (2) software transformations to exploit better a given memory hierarchy. The latter techniques are independent from the actual interface we handle, and their proficient use can enhance the design of hardware accelerators, including virtual-memoryenabled ones. In contrast to well-established static techniques, a few works have a dynamic flavour. For example, the work of Leeman et al. [70] on refining dynamic memory management for embedded systems is fully complementary to our approach. Since our system layer—providing the unified memory for software and hardware—is dynamic in its nature, one could consider using Leeman's methodology to improve the dynamic behaviour of our memory allocation process.

In the area of memory systems for reconfigurable computing, Herz et al. [57] have studied the generation of optimal access patterns for coprocessors within SoC architectures; their focus is not in abstraction from architectural details and portability, as it is the case in this thesis. Although we only use simple access patterns for validation, hardware designers can use any access pattern in conjunction with the unified memory. In this way, their address generation techniques are complementary to our work.

### 3.2 Reconfigurable Computing

In this section, we first relate our architecture with two major architectural approaches in reconfigurable computing that blend temporal and spatial computation. Then, we compare our approach to parallel execution in reconfigurable SoCs with recent developments in multithreading for reconfigurable applications. Finally, we survey existing OS extensions—complementary to ours—that address system software support for reconfigurable applications.

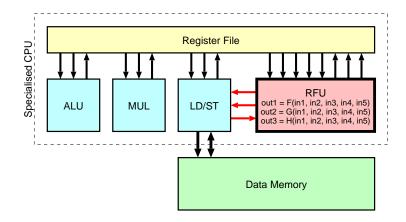

**Figure 3.1:** Specialised CPU extended with *Reconfigurable Functional Unit* (RFU). The RFU implements a special instruction built by collapsing multiple ISA instructions into the complex one.

#### 3.2.1 Reconfigurable Accelerator Integration

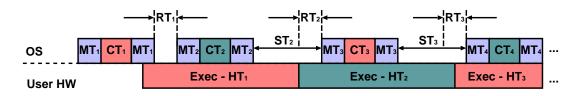

Two of the most common approaches that mix temporal computation within a CPU and spatial computation within reconfigurable hardware are: (1) fine-grained, specialising the CPU data-path with an application-specific reconfigurable functional unit (RFU in Figure 3.1); and (2) coarse-grained, specialising the application execution off the CPU, with an application-specific reconfigurable accelerator (acting like a coprocessor in Figure 3.2).