## INVESTIGATION AND CONTROL OF A HYBRID ASYMMETRIC MULTI-LEVEL INVERTER FOR MEDIUM-VOLTAGE APPLICATIONS

THÈSE Nº 2846 (2003)

PRÉSENTÉE À LA FACULTÉ SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

Institut des sciences de l'énergie

SECTION D'ÉLECTRICITÉ

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES TECHNIQUES

PAR

### Martin VEENSTRA

Master of Science in Electrical Engineering, Delft University of Technology, Pays-Bas et de nationalité néerlandaise

acceptée sur proposition du jury:

Prof. A.-Ch. Rufer, directeur de thèse Prof. R. Lorenz, rapporteur Dr T. Meynard, rapporteur Prof. J.-J. Simond, rapporteur Dr P. Steimer, rapporteur

> Lausanne, EPFL 2003

# Preface

In the final phase of my studies at Delft University of Technology, I performed 4 months practical work at ABB Corporate Research, which led to my employment as a Research Engineer in the same company immediately after my graduation in 1995. During the following 3 years, I gained a lot of industrial experience from my colleagues and the variety of projects we worked on, all in the field of high-power drives for traction or industrial applications. A job rotation at ABB Industry resulted in the proposal for an industrial Ph.D. research topic, which I eagerly accepted.

This dissertation has been carried out in the years 1998 through 2003 during my employment as Assistant-Doctorant under Prof. Alfred Rufer, director of the Laboratoire d'Électronique Industrielle at the École Polytechnique Fédérale de Lausanne. The topic of this thesis is a collaboration with ABB Industry as industrial partner.

I sincerely thank Prof. Alfred Rufer for accepting me as doctoral student. His strict confidence, availability and full support throughout the whole period of my research work, towards me personally and in managing the laboratory as a whole, together with his openness to new ideas, created the nutritious environment in which the obtained results could grow.

Special thanks go to Dr. Peter Steimer of ABB Industry for supporting this research project. His proposal of the subject and financial contribution were the basis for this dissertation, and our fruitful collaboration resulted in a patent.

I wish to thank the President of the Board of Examiners Prof. Juan Mosig and its Members Prof. Alfred Rufer, Prof. Jean-Jaques Simond, Prof. Robert Lorenz, Dr. Peter Steimer and Dr. Thierry Meynard for their valuable participation in the exam.

My thanks are equally addressed to all the members of the Laboratoire d'Électronique Industrielle for their support and the pleasant atmosphere they create in the lab. The administrative and technical assistance of Fabienne Vionnet, Roberto Zoia and Yves Birbaum form a great and appreciated relief in the daily work. Special thanks go to Sébastien Mariéthoz for our exhaustive and instructive discussions on a wide range of technical topics and the fruitful collaboration in the realization of hardware for our laboratory prototypes. I also wish to thank Dr. Philippe Barrade for reading the manuscript and commenting it with valuable remarks in an incredibly short time.

Finally, I address my sincere thanks to my parents and my friends, whether living around the corner or hundreds of kilometers away. Their constant support and their encouragement in difficult moments has been an important contribution in the realization of this work. Their presence for writing, talking or undertaking social activities and mountain tours gave me the energy to finish this project as it is.

> September 2003, Martin Veenstra

# Abstract

Power-electronic inverters are becoming popular for various industrial drives applications. In recent years also high-power and medium-voltage drive applications have been installed. However, the existing solutions suffer from some important drawbacks.

Hybrid asymmetric multi-level inverters promise significant improvements for medium-voltage applications. This dissertation investigates such a hybrid inverter. To simplify the topology, some inverter parts are deprived of their feeding from the net and can only supply reactive power. The non-supplied intermediate-circuit capacitor voltages are inherently unstable and require a suitable control method for converter operation, preferably without influence on the load. Apart from normal operation, also converter start-up is an issue to consider, for which it is desirable to limit additional equipment.

In this dissertation, we investigate the behaviour of this new inverter, and develop methods to obtain its reliable operation for the considered applications. These methods include modulation, voltage stabilization and start-up. We establish suitable models for their foundation.

The principle achievement of this work is the development of a control method to stabilize a multitude of capacitor voltages which have no equilibrium state. Power balancing is performed by varying the common-mode output voltage, using a non-linear model-predictive controller. This method, which is new to power electronics, is applied to our hybrid asymmetric nine-level inverter driving an asynchronous motor. Computer simulations and measurements on an experimental drive system demonstrate stable behaviour in steady-state and during transients over the whole operating range. The obtained results prove the possible implementation of such a complex control algorithm for fast real-time operation.

As second important accomplishment, this thesis proposes a start-up method that charges the non-supplied intermediate-circuit capacitors in parallel with the supplied ones, without additional equipment. Measurements show its successful application in the investigated drive system.

# Résumé

Les onduleurs de l'électronique de puissance gagnent en popularité pour diverses applications d'entraînements industriels. Au cours des dernières années, des applications moyenne tension de forte puissance ont également été installées. Cependant, les solutions existantes souffrent de certains inconvénients majeurs.

Les onduleurs multiniveaux asymmétriques hybrides promettent des améliorations considérables pour les applications moyenne tension. Cette thèse examine un tel onduleur hybride. Afin de simplifier la topologie, certaines parties de l'onduleur sont privées de leur alimentation réseau, et ne peuvent fournir que de la puissance réactive. Les tensions des condensateurs aux circuits-intermédiaires non-alimentés sont instables et requièrent une méthode de contrôle adéquate afin de permettre le fonctionnement du convertisseur, de préférence sans influence sur la charge. Indépendament du fonctionnement normal, le démarrage du convertisseur est également un sujet à étudier, pour lequel on souhaite limiter les équipements supplémentaires.

Dans cette thèse, nous étudions le comportement de ce nouvel onduleur, et nous développons des méthodes afin d'obtenir un fonctionnement fiable pour les applications envisagées. Ces méthodes incluent la modulation, la stabilisation des tensions et le démarrage. Nous établissons des modèles appropriés pour leur fondement.

Le résultat principal de ce travail est le développement d'une méthode de réglage pour stabiliser une multitude de tensions de condensateur n'ayant pas d'état d'équilibre. L'équilibrage des puissances est effectué par la variation de la composante homopolaire des tensions de sortie, en utilisant un régulateur prédictif non-linéaire. Cette méthode, qui est nouvelle dans le domaine de l'électronique de puissance, est appliquée à notre onduleur neuf-niveaux asymmétrique hybride entraînant un moteur asynchrone. Des simulations sur ordinateur ainsi que des mesures sur un système d'entraînement expérimental démontrent un comportement stable sur toute la plage de fonctionnement, aussi bien en régime stationnaire qu'en régime transitoire. Les résultats obtenus prouvent l'implémantation possible en temps réel rapide d'un algorithme fort complexe.

Comme deuxième résultat important, cette thèse propose une méthode de démarrage qui pré-charge les condensateurs aux circuits-intermédiaires nonalimentés en parallèle avec ceux alimentés, sans équipement supplémentaire. Des mesures montrent sa mise en oeuvre réussie sur le système d'entraînement étudié.

# Zusammenfassung

Leistungselektronische Umrichter gewinnen an Beliebtheit für verschiedenste industrielle Antriebe. In den letzten Jahren wurden ebenfalls Hochleistungsund Mittelspannungsantriebe installiert. Die bestehenden Lösungen leiden jedoch unter einige wichtige Nachteile.

Hybride asymmetrische Mehrstufenumrichter versprechen wichtige Verbesserungen für Mittelspannungsanwendungen. Diese Dissertation untersucht einen solchen Hybridumrichter. Um den Leistungsteil zu vereinfachen werden einige Umrichterteile von ihren Netzspeisungen beraubt, weswegen sie nur noch Blindleistung liefern können. Die Spannungen der nichtgespiesenen Zwischenkreiskondensatoren sind unstabil und verlangen ein geeignetes Regelungsverfahren für den Umrichterbetrieb, vorzugsweise ohne Einfluss auf die Last. Neben dem Normalbetrieb ist auch der Aufstart des Umrichters ein wichtiges Thema, wofür zusätzliche Ausrüstung beschränkt werden sollte.

In dieser Dissertation untersuchen wir das Verhalten dieses neuen Umrichters und entwickeln ein Verfahren zwecks Ermöglichung seines zuverlässigen Betriebs für die betrachteten Anwendungen. Diese Verfahren beinhalten Modulierung, Spannungsstabilisierung und Aufstart. Wir leiten geeignete Modelle zu deren Fundierung her.

Das wichtigste ergebnis dieser Arbeit ist die Entwicklung eines Regelungsverfahrens zwecks Stabilisierung einer Mehrzahl von Kondensatorspannungen die keinen Gleichgewichtszustand haben. Der Leistungsausgleich wird erreicht durch variieren der Homopolarspannungskomponente am Umrichterausgang, unter Verwendung eines nichtlinearen Vorhersagereglers. Dieses Verfahren, das neu ist in der Leistungselektronik, wird auf unserem hybriden asymmetrischen Neunstufenumrichter angewand, der einen Asynchronmotor antreibt. Computersimulationen und Messungen an einem experimentellen Antriebssystem demonstrieren ein stabiles Verhalten im ganzen Drehzahlbereich, sowohl im stationären wie im transienten Betrieb. Die erzielten Ergebnisse beweisen die mögliche Implementierung solch ein komplexes Regelverfahren für schnellen Echtzeitbetrieb. Als zweites wichtiges Ergebnis schlägt diese Abhandlung ein Aufstartverfahren vor, das die nichtgespiesenen Zwischenkreiskondensatorspannungen parallel zu den gespiesenen auflädt, ohne zusätzliche Ausrüstung. Messungen zeigen seine erfolgreiche Anwendung auf das untersuchte Antriebssystem.

# Contents

| Pr       | refac               | е             |                                         | iii |  |  |  |

|----------|---------------------|---------------|-----------------------------------------|-----|--|--|--|

| Al       | bstra               | $\mathbf{ct}$ |                                         | v   |  |  |  |

| Ré       | ésum                | é             |                                         | vii |  |  |  |

| Zι       | ısam                | menfa         | ssung                                   | ix  |  |  |  |

| Co       | onter               | nts           |                                         | xi  |  |  |  |

| 1        | Intr                | oducti        | ion                                     | 1   |  |  |  |

|          | 1.1                 | Asym          | metric and Hybrid Multi-Level Inverters | 1   |  |  |  |

|          | 1.2                 | Subje         | ct of the Dissertation                  | 2   |  |  |  |

|          | 1.3                 | Outlin        | ne of the Dissertation                  | 3   |  |  |  |

| <b>2</b> | Power-Part Topology |               |                                         |     |  |  |  |

|          | 2.1                 | Multi-        | Level Inverters                         | 7   |  |  |  |

|          |                     | 2.1.1         | Symmetric Multi-Level Inverters         | 8   |  |  |  |

|          |                     | 2.1.2         | Asymmetric Multi-Level Inverters        | 11  |  |  |  |

|          | 2.2                 | Mediu         | um-Voltage Drives                       | 14  |  |  |  |

|          |                     | 2.2.1         | Series-Connected H-Bridges Inverter     | 14  |  |  |  |

|          |                     | 2.2.2         | Neutral-Point Clamped Inverter          | 15  |  |  |  |

|          | 2.3                 | Hybrid        | d Inverter                              | 17  |  |  |  |

|          |                     | 2.3.1         | Topology Synthesis                      | 17  |  |  |  |

|          |                     | 2.3.2         | Properties                              | 19  |  |  |  |

|          |                     | 2.3.3         | Variants                                | 21  |  |  |  |

| 3        | Pul                 | se-Wio        | lth Modulation                          | 23  |  |  |  |

|          | 3.1                 | Two-L         | evel PWM Strategies                     | 24  |  |  |  |

|          |                     | 3.1.1         | Basic Principle                         | 24  |  |  |  |

|   |                   | 3.1.2                                                                                                                                      | Variants                                                      | 25                                                                                            |  |  |  |  |  |

|---|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|--|

|   | 3.2               | Multi-I                                                                                                                                    | Level PWM Strategies                                          | 26                                                                                            |  |  |  |  |  |

|   |                   |                                                                                                                                            |                                                               | 27                                                                                            |  |  |  |  |  |

|   |                   |                                                                                                                                            | -                                                             | 27                                                                                            |  |  |  |  |  |

|   |                   |                                                                                                                                            |                                                               | 29                                                                                            |  |  |  |  |  |

|   |                   |                                                                                                                                            |                                                               | 31                                                                                            |  |  |  |  |  |

|   | 3.3               | Varving                                                                                                                                    |                                                               | $\overline{32}$                                                                               |  |  |  |  |  |

|   |                   |                                                                                                                                            |                                                               | 33                                                                                            |  |  |  |  |  |

|   |                   |                                                                                                                                            | 1                                                             | 34                                                                                            |  |  |  |  |  |

| 4 | Cor               |                                                                                                                                            |                                                               | 37                                                                                            |  |  |  |  |  |

|   | 4.1               | Proper                                                                                                                                     | ties of Signal Modes                                          | 37                                                                                            |  |  |  |  |  |

|   |                   | 4.1.1                                                                                                                                      | Common Mode                                                   | 38                                                                                            |  |  |  |  |  |

|   |                   | 4.1.2                                                                                                                                      | Differential Mode                                             | 39                                                                                            |  |  |  |  |  |

|   | 4.2               | Transfe                                                                                                                                    | orming Three-Phase Quantities                                 | 39                                                                                            |  |  |  |  |  |

|   |                   | 4.2.1                                                                                                                                      | Separate Transforms                                           | 39                                                                                            |  |  |  |  |  |

|   |                   | 4.2.2                                                                                                                                      | Combined Transforms                                           | 40                                                                                            |  |  |  |  |  |

|   |                   | 4.2.3                                                                                                                                      | Application to Inverter States                                | 42                                                                                            |  |  |  |  |  |

|   |                   | 4.2.4                                                                                                                                      | Application to PWM Signals                                    | 44                                                                                            |  |  |  |  |  |

|   | 4.3               | Varying                                                                                                                                    | g Common Mode at Fixed Differential Mode                      | 48                                                                                            |  |  |  |  |  |

| 5 | Inv               | Inverter Modeling 53                                                                                                                       |                                                               |                                                                                               |  |  |  |  |  |

|   | 5.1               |                                                                                                                                            |                                                               | 53                                                                                            |  |  |  |  |  |

|   |                   |                                                                                                                                            |                                                               | ۳.4                                                                                           |  |  |  |  |  |

|   |                   |                                                                                                                                            |                                                               | 54                                                                                            |  |  |  |  |  |

|   |                   | 5.1.2                                                                                                                                      | PWM-Controlled Average Model                                  | $\frac{54}{55}$                                                                               |  |  |  |  |  |

|   | 5.2               | 5.1.2<br>PWM-0                                                                                                                             | PWM-Controlled Average Model       Controlled Hybrid Inverter | -                                                                                             |  |  |  |  |  |

|   | 5.2               | 5.1.2<br>PWM-0                                                                                                                             | PWM-Controlled Average Model       Controlled Hybrid Inverter | 55                                                                                            |  |  |  |  |  |

|   | 5.2               | 5.1.2<br>PWM-0<br>5.2.1                                                                                                                    | PWM-Controlled Average Model                                  | 55<br>56                                                                                      |  |  |  |  |  |

|   | 5.2               | 5.1.2<br>PWM-0<br>5.2.1<br>5.2.2                                                                                                           | PWM-Controlled Average Model                                  | 55<br>56<br>57                                                                                |  |  |  |  |  |

|   | 5.2<br>5.3        | 5.1.2<br>PWM-0<br>5.2.1<br>5.2.2<br>5.2.3                                                                                                  | PWM-Controlled Average Model                                  | 55<br>56<br>57<br>59                                                                          |  |  |  |  |  |

|   |                   | 5.1.2<br>PWM-0<br>5.2.1<br>5.2.2<br>5.2.3<br>Influence                                                                                     | PWM-Controlled Average Model                                  | 55<br>56<br>57<br>59<br>60                                                                    |  |  |  |  |  |

|   |                   | 5.1.2<br>PWM-0<br>5.2.1<br>5.2.2<br>5.2.3<br>Influeno<br>5.3.1                                                                             | PWM-Controlled Average Model                                  | 55<br>56<br>57<br>59<br>60<br>63                                                              |  |  |  |  |  |

| 6 | 5.3               | 5.1.2<br>PWM-0<br>5.2.1<br>5.2.2<br>5.2.3<br>Influen<br>5.3.1<br>5.3.2<br>Dacitor-                                                         | PWM-Controlled Average Model                                  | 555<br>56<br>57<br>59<br>60<br>63<br>63                                                       |  |  |  |  |  |

| 6 | 5.3               | 5.1.2<br>PWM-0<br>5.2.1<br>5.2.2<br>5.2.3<br>Influeno<br>5.3.1<br>5.3.2<br>Dacitor-<br>Control                                             | PWM-Controlled Average Model                                  | 555<br>56<br>57<br>59<br>60<br>63<br>63<br>65<br>73<br>73                                     |  |  |  |  |  |

| 6 | 5.3<br>Cap        | 5.1.2<br>PWM-0<br>5.2.1<br>5.2.2<br>5.2.3<br>Influeno<br>5.3.1<br>5.3.2<br>Pacitor-<br>Control<br>6.1.1                                    | PWM-Controlled Average Model                                  | 555<br>56<br>57<br>59<br>60<br>63<br>63<br>63<br>65<br>73<br>73<br>73                         |  |  |  |  |  |

| 6 | 5.3<br>Cap<br>6.1 | 5.1.2<br>PWM-0<br>5.2.1<br>5.2.2<br>5.2.3<br>Influend<br>5.3.1<br>5.3.2<br>Deacitor-<br>Control<br>6.1.1<br>6.1.2                          | PWM-Controlled Average Model                                  | 55<br>56<br>57<br>59<br>60<br>63<br>63<br>65<br>73<br>73<br>74<br>75                          |  |  |  |  |  |

| 6 | 5.3<br>Cap        | 5.1.2<br>PWM-0<br>5.2.1<br>5.2.2<br>5.2.3<br>Influen<br>5.3.1<br>5.3.2<br><b>Dacitor-</b><br>Control<br>6.1.1<br>6.1.2<br>Model-           | PWM-Controlled Average Model                                  | 555<br>56<br>57<br>59<br>60<br>63<br>63<br>63<br>65<br>73<br>73<br>73                         |  |  |  |  |  |

| 6 | 5.3<br>Cap<br>6.1 | 5.1.2<br>PWM-0<br>5.2.1<br>5.2.2<br>5.2.3<br>Influent<br>5.3.1<br>5.3.2<br><b>Dacitor-</b><br>Control<br>6.1.1<br>6.1.2<br>Model-<br>6.2.1 | PWM-Controlled Average Model                                  | 555<br>556<br>577<br>590<br>603<br>633<br>635<br>635<br>73<br>737<br>747<br>757<br>776<br>777 |  |  |  |  |  |

| 6 | 5.3<br>Cap<br>6.1 | 5.1.2<br>PWM-0<br>5.2.1<br>5.2.2<br>5.2.3<br>Influent<br>5.3.1<br>5.3.2<br><b>Dacitor-</b><br>Control<br>6.1.1<br>6.1.2<br>Model-<br>6.2.1 | PWM-Controlled Average Model                                  | 55<br>56<br>57<br>59<br>60<br>63<br>63<br>63<br>65<br>73<br>73<br>73<br>74<br>75<br>76        |  |  |  |  |  |

|                                   | 6.3                        | MPC for Capacitor Voltage Stabilization | 80  |  |  |  |  |  |  |  |  |

|-----------------------------------|----------------------------|-----------------------------------------|-----|--|--|--|--|--|--|--|--|

|                                   |                            | 6.3.1 System Model                      | 80  |  |  |  |  |  |  |  |  |

|                                   |                            | 6.3.2 State Prediction                  | 82  |  |  |  |  |  |  |  |  |

|                                   |                            | 6.3.3 Control Problem and Cost Function | 84  |  |  |  |  |  |  |  |  |

|                                   |                            | 6.3.4 Problem Optimization              | 85  |  |  |  |  |  |  |  |  |

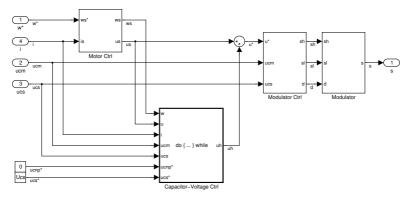

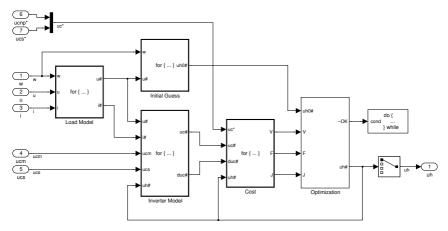

| 7                                 | Implementation and Results |                                         |     |  |  |  |  |  |  |  |  |

|                                   | 7.1                        | System Design                           | 89  |  |  |  |  |  |  |  |  |

|                                   |                            | 7.1.1 Voltage Levels                    | 90  |  |  |  |  |  |  |  |  |

|                                   |                            | 7.1.2 Switching Frequency               | 91  |  |  |  |  |  |  |  |  |

|                                   |                            | 7.1.3 Intermediate-Circuit Capacitors   | 91  |  |  |  |  |  |  |  |  |

|                                   |                            | 7.1.4 Control                           | 94  |  |  |  |  |  |  |  |  |

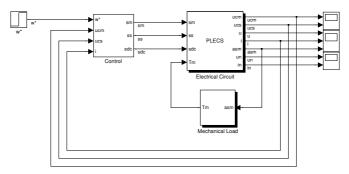

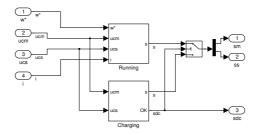

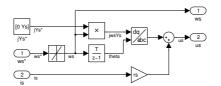

|                                   | 7.2                        | Simulation Model                        | 99  |  |  |  |  |  |  |  |  |

|                                   |                            | 7.2.1 Implementation                    | 100 |  |  |  |  |  |  |  |  |

|                                   |                            | 7.2.2 Results                           | 101 |  |  |  |  |  |  |  |  |

|                                   | 7.3                        | Laboratory Prototype                    | 102 |  |  |  |  |  |  |  |  |

|                                   |                            | 7.3.1 Implementation                    | 104 |  |  |  |  |  |  |  |  |

|                                   |                            | 7.3.2 Results                           | 108 |  |  |  |  |  |  |  |  |

| 8                                 | Pre-Charge Method          |                                         |     |  |  |  |  |  |  |  |  |

|                                   | 8.1                        | Principle                               | 117 |  |  |  |  |  |  |  |  |

|                                   | 8.2                        | Implementation and Results              | 119 |  |  |  |  |  |  |  |  |

| 9                                 | Conclusion                 |                                         |     |  |  |  |  |  |  |  |  |

|                                   | 9.1                        | Topology                                | 123 |  |  |  |  |  |  |  |  |

|                                   | 9.2                        | Obtained Results                        | 124 |  |  |  |  |  |  |  |  |

|                                   | 9.3                        | Recommendations                         | 125 |  |  |  |  |  |  |  |  |

| $\mathbf{A}$                      | Jaco                       | Jacobian-Matrix Calculation             |     |  |  |  |  |  |  |  |  |

| Bibliography                      |                            |                                         |     |  |  |  |  |  |  |  |  |

| List of Figures<br>List of Tables |                            |                                         |     |  |  |  |  |  |  |  |  |

|                                   |                            |                                         |     |  |  |  |  |  |  |  |  |

| Curriculum Vitae                  |                            |                                         |     |  |  |  |  |  |  |  |  |

xiv

## Chapter 1

# Introduction

Power-electronic inverters are becoming popular for various industrial drives applications. In recent years also high-power and medium-voltage drive applications have been installed [1, 2]. To overcome the limited semiconductor voltage and current ratings, some kind of series and/or parallel connection will be necessary. Due to their ability to synthesize waveforms with a better harmonic spectrum and attain higher voltages, multi-level inverters are receiving increasing attention in the past few years [3–6]. However, the increasing number of devices tends to reduce the overall reliability and efficiency of the power converter. On the other hand, solutions with a low number of devices either need a rather large and expensive LC output filter to limit the motorwinding insulation stress, or can only be used with motors that do withstand such stress.

## 1.1 Asymmetric and Hybrid Multi-Level Inverters

Asymmetric multi-level inverters use different intermediate-circuit capacitor voltages in various parts of the inverter. By addition and subtraction of these voltages, more different output-voltage levels can be generated with the same number of components, compared to a symmetric multi-level inverter [7–9]. Higher output quality can be obtained with smaller circuit and control complexity, and output filters can be remarkably shrunk or even eliminated.

The various parts of an asymmetric multi-level inverter execute different functions in the power conversion. Equipped with several different semiconductor devices, a hybrid converter exploits their individual advantages and strengths [10–13]. The main power is supplied with high reliability and low losses by one device, the output harmonic content is reduced by an other. By using state-of-the-art semiconductor devices, this can lead to a better overall design for medium-voltage drives.

In order to further simplify the power part and increase the efficiency of such a converter, we can remove some of the power supplies and let those parts of the converter supply only reactive power [14–16]. We obtain a very interesting solution in terms of power quality, efficiency, reliability and cost.

However, the resulting system is unstable, and without control the nonsupplied intermediate-circuit capacitor voltages will quickly run away from their nominal values. An appropriate converter control method is needed to stabilize those voltages, preferably without deteriorating the output voltage. In general, this can not be done instantaneously by lack of an equilibrium state, but only on an average in time. Apart from normal operation, also the precharging of the non-supplied intermediate-circuit capacitors upon converter start-up is an issue to consider.

### **1.2** Subject of the Dissertation

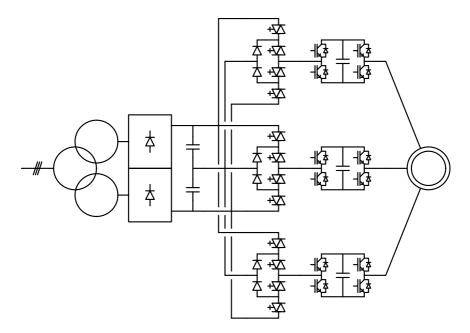

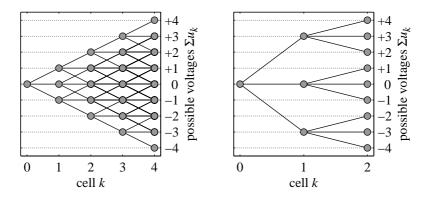

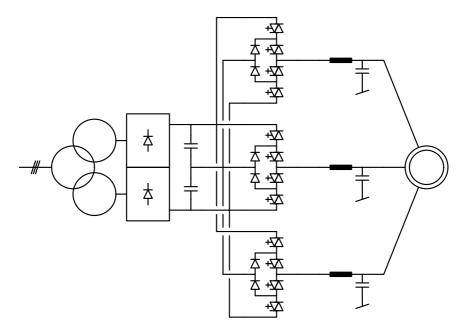

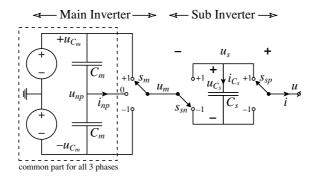

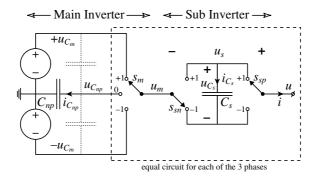

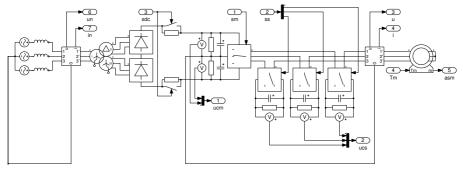

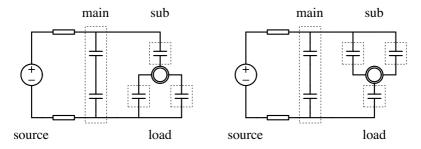

This dissertation investigates a hybrid asymmetric multi-level inverter which promises significant improvements for medium-voltage drives. It consists of a three-phase three-level IGCT inverter (main inverter), with a two-phase two-level IGBT inverter (sub inverter) in series with each phase (see Figure 1.1) [14–16]. Integrated gate-commutated thyristors (IGCT) with a high voltage-blocking capability are used to provide the main power with high reliability and low losses [17–19], insulated-gate bipolar transistors (IGBT) with a higher switching-frequency capability are used to reduce the output harmonic content. We will use a ratio of 3 between the intermediate-circuit capacitor voltages of the main and the sub inverter to obtain a maximum of output-voltage levels. By addition and subtraction of these voltages, nine different output-voltage levels can be generated.

The main inverter is fed from the net by a twelve-pulse transformer and diode rectifier. As an alternative, a back-to-back configuration with a second hybrid inverter, serving as active rectifier, is possible as well [14].

To keep the power part simple and the efficiency high, the sub inverters have *no* feeding from the net. They can only supply reactive power, which *must* be assured by appropriate converter control. Moreover, also the main-inverter neutral-point, which lacks supply by a power source too, must be kept balanced.

To avoid additional cost and reduced reliability, additional pre-charging

Figure 1.1: Circuit diagram of the hybrid inverter in a medium-voltage drive application. The three sub-inverter intermediate circuits are *not* supplied by a power source.

equipment should be kept minimal. The main inverter can be pre-charged in a usual way, using a set of pre-charge resistors along with a bypass switch on the AC or the DC side of the transformer and rectifiers. Pre-charging of the sub inverters can not be accomplished in such a manner. It is, however, desirable to avoid additional equipment and to dispose of an other method to perform this task.

The main goals of this dissertation are a thorough understanding of the behaviour of this new inverter, and the development of methods to obtain its reliable operation for the considered applications. The principle topics to be studied are described in the following section.

## 1.3 Outline of the Dissertation

In Chapter 2, we will take a brief look at existing inverter topologies and new research fields. We will discuss the main advantages and disadvantages of those solutions. Based on this, the power-part topology of a hybrid asymmetric multi-level inverter for medium-voltage industrial drives will be synthesized. It promises to be a simple and reliable circuit with a good output quality and high efficiency.

Different modulation methods exist to generate appropriate output voltages with a voltage-source inverter. We will investigate the widely used and well-known pulse-width modulation (PWM) methods in Chapter 3. Many variants exist, especially for multi-level inverters. We will discuss some properties and choose a modulator for our hybrid asymmetric multi-level inverter.

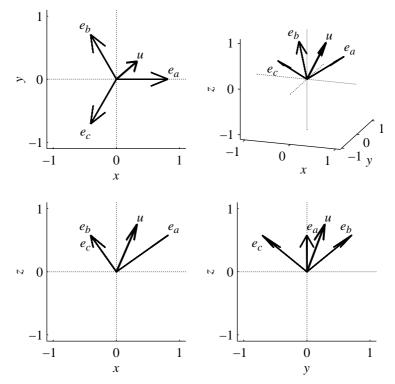

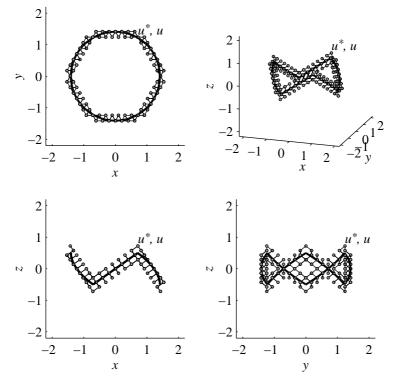

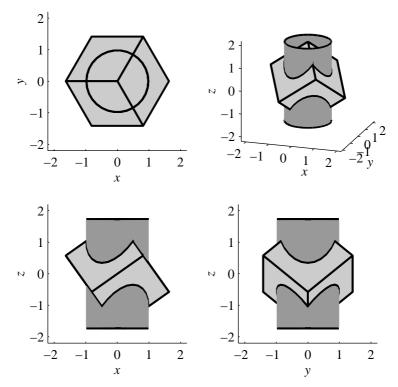

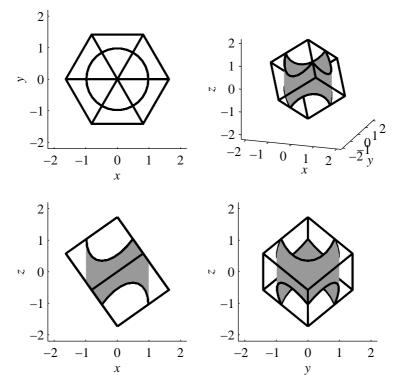

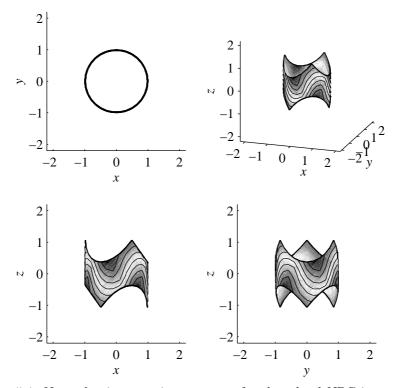

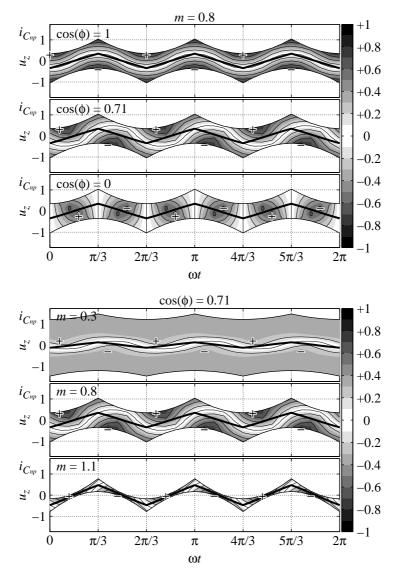

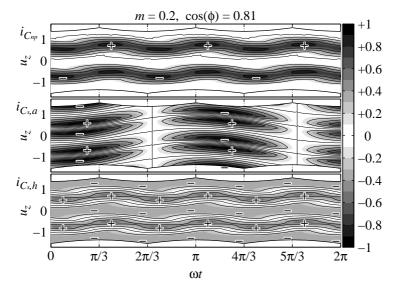

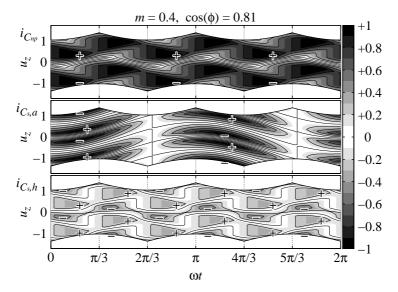

In Chapter 4, we will study the common mode and the differential mode of voltages and currents in three-phase power systems. As we will see in the following chapters, these aspects are of great importance to our system. We will define a transform matrix to change between phase quantities and their corresponding common and differential modes. As an illustration, we will apply the transform to some relevant signals of a nine-level inverter: the inverter output-states voltages, and the reference and output signals of its pulse-width modulator. Finally, for the purpose of our future control, we will investigate varying common mode at fixed differential mode.

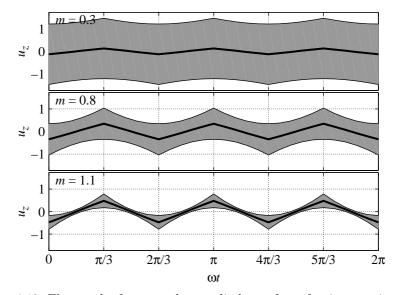

In order to properly control an inverter, we must thoroughly understand its behavior. Especially the switched-mode behavior of power-electronic inverters can make its modeling difficult. Chapter 5 starts with an exact description of ideal switches. Based on this, we will derive an approximate switch model under PWM control, neglecting the switching behavior and taking only average values over a switching interval into account. Using such switch models, we will construct a model of our hybrid asymmetric multi-level inverter. Especially the intermediate-circuit capacitor voltages will be of our interest, since we need a control algorithm to stabilize them. We will focus at the influence of the possible common-mode voltages, because—as we will learn in Chapter 6—this stabilization can be done by adding an appropriate common-mode component to the output voltage.

Since the main-inverter neutral point and the three sub-inverter intermediate circuits are not supplied by a power source, their capacitor voltages have to be stabilized by an appropriate control algorithm, preferably without deteriorating the output voltage. This system is unstable, and without control the non-supplied intermediate-circuit capacitor voltages will quickly run away from their nominal values. Chapter 6 describes methods to affect the capacitor voltages without influence on the load, and analyzes their properties. Based on these insights, we propose a strategy to accomplish the desired control. We will show how this strategy can be applied to stabilize the capacitor voltages in our hybrid inverter.

For the development of the models, methods and strategies proposed in the

previous chapters, extensive use of computer calculations and simulations has been employed. In order to validate the obtained results, a low-voltage laboratory prototype of a hybrid-inverter drive system has been built and tested. Chapter 7 describes the design of our hybrid inverter in a drive application. We will discuss its implementation in a simulation model, together with the obtained results. The realization of a laboratory prototype required adaptations in the controller design, which we will comment. The prototype has been subjected to extensive tests, whose results are presented and discussed.

In Chapter 8, we will propose a special pre-charge method for our hybrid inverter. The main inverter (NPC topology) is pre-charged in a usual way via a set of pre-charge resistors along with a bypass contactor, either on the AC or the DC side of the transformer and rectifiers. The sub-inverter intermediatecircuit capacitors are charged in parallel to and together with those of the main inverter, by exploiting certain inverter switching configurations. Measurements show its successful application in the proposed drive system.

## Chapter 2

# Power-Part Topology

Power-electronic inverters are becoming popular for various industrial drives applications. In recent years also high-power and medium-voltage drive applications have been installed [1, 2]. To overcome the limited semiconductor voltage and current ratings, some kind of series and/or parallel connection will be necessary. Due to their ability to synthesize waveforms with a better harmonic spectrum and attain higher voltages, multi-level inverters are receiving increasing attention in the past few years [3–6]. However, the increasing number of devices tends to reduce the overall reliability and efficiency of the power converter. On the other hand, solutions with a low number of devices either need a rather large and expensive LC output filter to limit the motorwinding insulation stress, or can only be used with motors that do withstand such stress.

In this chapter, we will take a brief look at existing inverter topologies and new research fields. We will discuss the main advantages and disadvantages of those solutions. Based on this, the power-part topology of a hybrid asymmetric multi-level inverter for medium-voltage industrial drives will be synthesized. It promises to be a simple and reliable circuit with a good output quality and high efficiency.

## 2.1 Multi-Level Inverters

In this section, we will discuss the most important multi-level inverter topologies and their properties. First, we will look at the well-known symmetric multi-level inverter topologies. Second, we will regard the emerging field of asymmetric multi-level inverters.

### 2.1.1 Symmetric Multi-Level Inverters

Multi-level inverters are known since several decades [3]. The well-known circuit topologies are:

- series-connected H-bridges inverter (SHB);

- neutral-points clamped inverter (NPC);

- imbricated-cells inverter (IC).

Their properties are briefly discussed in the following. A generalized multilevel topology, which combines the topologies of NPC and IC inverters, is described in [6].

Multi-level inverters are characterized by the number of different outputvoltage levels that can be generated by the inverter. Any inverter that generates more than two output-voltage levels is called a multi-level inverter. Although mostly an odd number of levels is chosen, even numbers are possible as well.

The classical solutions are called symmetric multi-level inverters, because they have the same voltage on each of the intermediate-circuit capacitors, and all the power semiconductors have to be capable to block this same voltage in their 'off' state. A value corresponding to the chosen technology is used. Series connection of components is needed where multiples of this voltage occur. This is the case for NPC and IC converters of more than three levels. As can be deduced from the generalized topology [6], series connection of equivalent diodes or capacitors is related to their clamping of multiple switches.

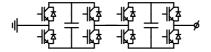

#### Series-Connected H-Bridges Inverter

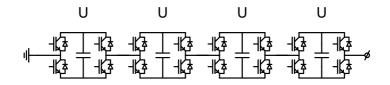

Figure 2.1 shows the circuit diagram of a 5-level series-connected H-bridges inverter [1,5,20,21]. For clarity, only one phase is drawn. The power semiconductors form H-bridges, which are connected in series. The number of active semiconductors is proportional to the number of levels.

Each H-bridge has its own intermediate-circuit capacitor, which are at different and varying potentials. As a consequence, the circuit needs an isolated

Figure 2.1: Phase circuit diagram of a 5-level SHB inverter.

power supply for each DC link. The number of intermediate-circuit capacitors, and thus of independent power supplies, is proportional to the number of levels.

The ground symbol shows a common (for all phases) reference point, where the phases are connected together. Each H-bridge can generate a positive, a negative or a zero voltage. The total output voltage is the sum of the individual H-bridge voltages. The possible output voltages are thus symmetric around zero, and zero voltage can be generated as well. The number of output-voltage level is therefore always odd.

The high number of isolated power supplies, using either low- or mediumfrequency transformers, tend to make the circuit rather complex. Since the converter consists basically of three independent single-phase converters, no (reactive) power can be directly exchanged between the phases. It must either be stored in the intermediate circuits—which increases their capacitor size—, or exchanged via active rectifiers and the transformer—which increases losses.

A similar converter is obtained by parallel connection of the H-bridges on their DC side and a series connection via independent transformer windings on their AC side [22,23]. In this case, a single power supply feeds the common DC link.

#### Neutral-Points Clamped Inverter

Figure 2.2 shows the circuit diagram of a 5-level neutral-points clamped inverter [4,24]. For clarity, only one phase is drawn. The power semiconductors are connected in series. The intermediate circuit is divided into several parts, whose so called neutral points can be connected to the output via the clamp-

Figure 2.2: Phase circuit diagram of a 5-level NPC inverter.

ing diodes. Series connection of clamping diodes is necessary, assumed they have the same voltage-blocking capability as the power semiconductors. The number of active semiconductors is proportional to the number of levels, the number of clamping diodes, however, is proportional to its square.

The intermediate-circuit capacitors are common for all phases. As a consequence, the circuit needs only one power supply for the total DC link. Moreover, (reactive) power can be freely exchanged between the phases without additional losses. The number of intermediate-circuit capacitors is proportional to the number of levels.

The ground symbol shows a common (for all phases) reference point in the middle of the DC link. The possible output voltages are thus symmetric around zero. In case the circuit has an even number of levels, and thus an odd number of intermediate-circuit capacitors, this reference point must be artificially constructed.

Component load is not equally distributed within the converter, both for the semiconductors and the capacitors, which complicates converter design. The stabilization of the capacitor voltages is problematic. Although a new approach proposes to overcome this problem [25], it rises new issues which limit its application.

#### **Imbricated-Cells Inverter**

Figure 2.3 shows the circuit diagram of a 5-level imbricated-cells inverter [26, 27]. For clarity, only one phase is drawn. The power semiconductors are connected in series. Their connection points are clamped by additional ca-

Figure 2.3: Phase circuit diagram of a 5-level IC inverter.

pacitors. Series connection of clamping capacitors is necessary, assumed they have the same voltage rating as the power semiconductors. The number of active semiconductors is proportional to the number of levels, the number of clamping capacitors, however, is proportional to its square.

The intermediate-circuit capacitors (not the clamping capacitors!) are common for all phases. As a consequence, the circuit needs only one power supply for the total DC link. Moreover, (reactive) power can be freely exchanged between the phases without additional losses. The number of intermediatecircuit capacitors is proportional to the number of levels.

The ground symbol shows a common (for all phases) reference point in the middle of the DC link. The possible output voltages are thus symmetric around zero. In case the circuit has an even number of levels, and thus an odd number of intermediate-circuit capacitors, this reference point must be artificially constructed.

The high number of clamping capacitors are rather voluminous and costly. Their voltage stabilization requires appropriate control and a high number of measurements.

The concept of the IC inverter has been further developed, resulting in the stacked multi-cell (SMC) inverter [28, 29]. It promises a reduction of the energy stored in the converter and thus of the clamping-capacitors size.

### 2.1.2 Asymmetric Multi-Level Inverters

In the past few years, the idea has risen to use different voltages on the various intermediate-circuit capacitors of a multi-level inverter. These inverters are called asymmetric multi-level inverters. Up to now, mainly asymmetric SHB inverters have been investigated [7–9, 12, 13, 16, 30–35], although the concept can be applied to other circuit topologies as well: NPC [33, 36], IC [37], and combinations of basic structures [9–11, 14–16].

Asymmetric multi-level inverters have exactly the same circuit topology as symmetric multi-level inverters. They differ only in the used capacitor voltages. The properties of asymmetric multi-level inverters are however quite different from those of their symmetric versions. Especially the number of output-voltage levels can be dramatically increased.

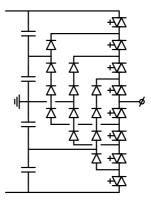

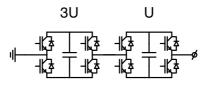

Instead of increasing the number of levels, one can also choose to reduce the number of cells. This is an interesting possibility to increase the reliability of a converter, while keeping the same output quality. As an example, we will compare a symmetric with an asymmetric nine-level inverter (Figure 2.4 and 2.5). The asymmetric version is only one possible solution out of several [8,9].

We will first take a look at the inverter states and the corresponding output voltages of both inverters. Based on this, we will briefly discus the voltage,

Figure 2.4: Phase circuit diagram of a symmetric 9-level SHB inverter.

Figure 2.5: Phase circuit diagram of an asymmetric 9-level SHB inverter.

power and switching frequency of the different cells.

#### **Inverter States and Output Voltages**

Each H-bridge cell has four possible switching states, of which two result in the same output voltage. The output voltages are 'plus the capacitor voltage', 'minus the capacitor voltage' and 'zero voltage' (two times). We will only take the three states with different output voltages into account, and forget about the internal redundancy for now. The voltage of the  $k^{\text{th}}$  cell  $u_k$  is thus

$$u_k = s_k u_{C_k} \quad \text{with } s_k \in \{-1, 0, +1\},$$

(2.1)

where  $s_k$  is the switching state and  $u_{C_k}$  is the capacitor voltage of this cell. After k cells in the inverter, we have the voltage  $u_{k0}$  relative to the reference point

$$u_{k0} = \sum_{i=1}^{k} u_i.$$

(2.2)

The phase output voltage is, of course, obtained by summing over all cells.

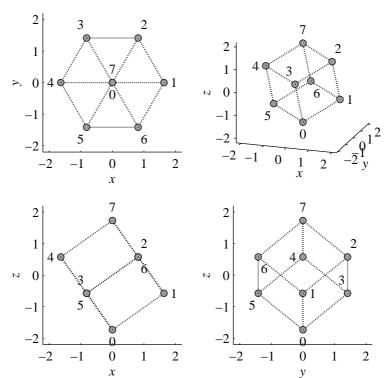

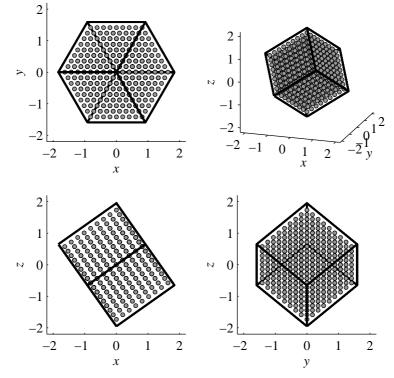

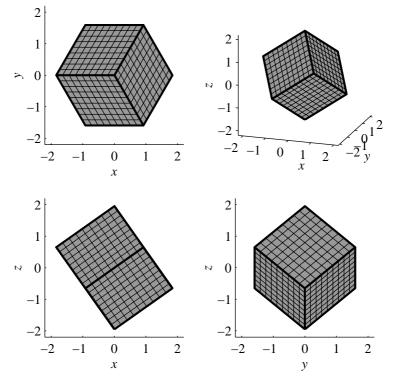

We can now construct a tree of possible cell and output voltages. We start at the reference point, which has zero voltage per definition. From this point, three branches are drawn, corresponding to the three possible voltages of the first cell. At each of these three values, we have the three possible voltages of the second cell. So at each point of the first cell, we draw the three branches

(a) Symmetric 9-level SHB inverter shown in Figure 2.4.

(b) Asymmetric 9-level SHB inverter shown in Figure 2.5.

Figure 2.6: Inverter states and output voltages (one phase) of two different 9-level SHB inverters.

of the second cell. And we go on in a similar manner until the last cell to complete the tree. Figure 2.6 shows such trees for our two inverters.

Each branch in the tree corresponds to a switching state of an H-bridge cell. So each path in the tree (a sequence of branches) corresponds to a switching state of the inverter. Different paths can result in the same output voltage. If so, the inverter has redundant switching states. As can be clearly seen in Figure 2.6(a), the symmetric solution has many redundant states. The presented asymmetric solution of Figure 2.6(b), however, has no redundant states.

#### Cell Voltage, Power and Switching Frequency

The cells in the symmetric inverter all have the same voltage. Normally, the controller is designed in such a way that the delivered active power and the switching frequency are the same as well. This is done by properly alternating the redundant states.

In the asymmetric inverter, the cells have different voltages. This also has consequences for the delivered power and the switching frequency [9, 15, 16]. 'Big cells', which have a big voltage, deliver mainly active power, and are operated with a low switching frequency. 'Small cells', which have a small voltage, deliver mainly reactive power, and are operated with a high switching frequency.

## 2.2 Medium-Voltage Drives

Power-electronic converters have been successfully implemented for mediumvoltage drive applications. The most important and widely-used solutions are:

- series-connected H-bridges inverter (SHB);

- neutral-point clamped inverter (NPC);

- current-source inverter (CSI);

- load-commutated inverter (LCI);

- cyclo converter (CC).

The first two solutions are multi-level voltage-source converters, both of which have been successfully implemented as standard products for medium-voltage industrial drives. Their aspects will be treated in more detail in this section. The other converters are current-source or direct converters. They will not be regarded in this dissertation.

### 2.2.1 Series-Connected H-Bridges Inverter

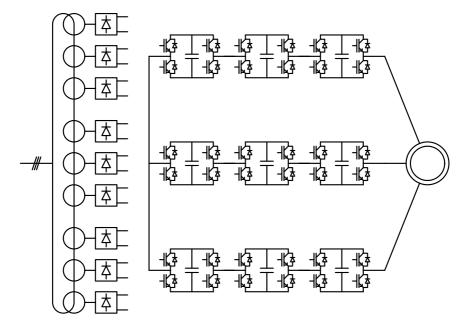

The series-connected H-bridges inverter is an emerging inverter for mediumvoltage drive applications [1,20]. A state-of-the-art realization with three cells per phase is shown in Figure 2.7, higher cell numbers are common though. An input transformer feeds each of the cells via its own three-phase winding and diode rectifier. To obtain a high pulse number at the primary side, secondary transformer windings in star, delta, zig-zag and combinations are used. The SHB inverter uses insulated-gate bipolar transistors (IGBT) with a low voltage-blocking but a high switching-frequency capability. IGBT require only rather simple gate drivers.

This inverter has excellent input-current and output-voltage waveforms. The output-voltage steps are steep but limited in magnitude. Therefore no output filter is needed even for retro-fit applications. Due to the small voltage steps of this inverter, also the common-mode voltage can be kept small enough to be of no further concern.

The drawback of this inverter is the high number of components for the rectifier, the inverter, as well as the control equipment, and the complexity of the input transformer. All this has a negative influence on the efficiency, reliability and cost of such a drive.

For applications where energy recuperation is desired, the diode rectifiers can be replaced by three-phase IGBT inverter bridges. This solution implies a different topology and control on the net and the motor side. A so called common DC bus application, where several inverters are connected to the same intermediate circuit, can not be realized.

Figure 2.7: Circuit diagram of an SHB inverter in a medium-voltage drive application.

### 2.2.2 Neutral-Point Clamped Inverter

The three-level neutral-point clamped inverter is a widely used inverter for medium-voltage drive applications [2, 14, 38, 39]. A state-of-the-art realization with output filter is shown in Figure 2.8. A twelve-pulse input transformer and diode rectifier feeds the common intermediate circuit (a higher pulse number is possible for special cases). The NPC inverter uses integrated gate-commutated thyristors (IGCT) with a high voltage-blocking but a low switching-frequency capability. IGCT are highly reliable components with rather low losses.

The NPC inverter has a simple circuit, but generates big and steep voltage steps which can damage the winding insulation of standard motors. For retrofit applications, where an existing motor is subsequently equipped with an inverter, an LC output filter is needed in order to smooth the inverter voltage. Such a filter is rather heavy and expensive. Since passive damping would cause too big losses, an active damping algorithm must be added to the controller. In case of a fault, self-excitation between motor and filter capacitors can occur. A special protection concept must prevent this and potential damage caused

Figure 2.8: Circuit diagram of an NPC inverter in a medium-voltage drive application.

by its increasing voltages.

As most power-electronic converters, also the NPC inverter generates a common-mode voltage. In order to keep it away from the motor, the LC filter star point is connected to the ground. As a result, the full common-mode voltage will be seen on the transformer side. To prevent big common-mode currents in case of long transformer cables (big parasitic capacities), a common-mode filter must be added to the circuit (e.g. in the intermediate circuit between rectifier and capacitors).

For applications where energy recuperation is desired, a simple back-toback connection of two inverters can be realized. The transformer and rectifier are thus replaced by a second NPC inverter with its LC filter. A so called common DC bus application, where several inverters are connected to the same intermediate circuit, is possible as well.

### 2.3 Hybrid Inverter

In the previous sections, we have regarded existing medium-voltage drives and the concept of asymmetric multi-level inverters. We have briefly discussed their main properties. In this section, we will combine the advantages of those different solutions and synthesize the power-part topology of a hybrid asymmetric multi-level inverter for medium-voltage industrial drives. It promises to be a simple and reliable circuit with a good output quality and high efficiency.

### 2.3.1 Topology Synthesis

As we have seen in the previous section, two multi-level inverter topologies have been successfully implemented as standard products for medium-voltage industrial drives: the SHB and the three-level NPC inverter.

In spite of their success, both topologies suffer from a principle drawback: the trade-off between power quality—both on the grid and the motor side and circuit complexity—which translates in efficiency, reliability and cost. The SHB inverter has excellent input-current and output-voltage waveforms, at the cost of a complex input transformer and a high number of semiconductor devices, along with their control equipment. The NPC inverter, on the other hand, has a simple circuit, but needs a large LC output filter to drive standard motors.

This trade-off can be tackled by using an asymmetric multi-level inverter. Applying this approach to the SHB topology allows to reduce the number of H-bridge cells while maintaining the number of output-voltage levels. However, the need for a, although somewhat simplified, complex input transformer remains.

As a consequence of choosing an asymmetric multi-level inverter, also the power semiconductors have to be capable to block these different cell voltages in their 'off' state. If we have cell voltages with a ratio of 3 or even more, it is not recommended to use the same power semiconductors all over the inverter. It is better to use different elements which suit the different requirements best [9–16, 33, 34].

On the one hand, 'big cells', which have a big voltage, deliver mainly active power, and are operated with a low switching frequency. These are ideal operating conditions for IGCT, which are very reliable elements providing a high blocking voltage together with low on-state losses [17–19].

On the other hand, 'small cells', which have a small voltage, deliver mainly reactive power, and are operated with a high switching frequency. These are ideal operating conditions for IGBT, which allow higher switching frequencies and have good performance at lower voltages.

Figure 2.9: Phase circuit diagram of a hybrid asymmetric 9-level SHB inverter, combining two power-semiconductor technologies.

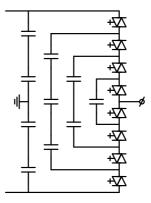

Figure 2.10: Phase circuit diagram of a hybrid asymmetric 9-level NPC/SHB inverter, reducing the feeding complexity.

By combining IGBT and IGCT in a hybrid asymmetric SHB inverter, we take advantage of their individual qualities and strength [12, 13, 34]. We call it a hybrid inverter because it unites two power-semiconductor technologies. The resulting topology is shown in Figure 2.9.

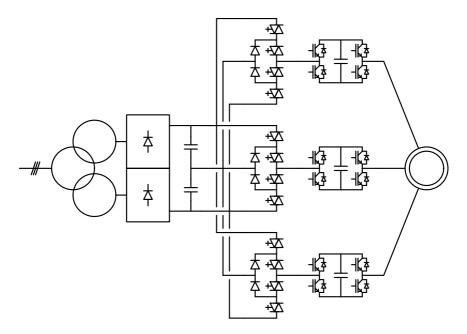

In this topology, the problem of the complex feeding of the cells remains. So we will look for a solution to improve this. As we have seen, the H-bridge cells generate three different voltages each. But a three-level inverter would do the same! So, instead of using three H-bridges (one for each output phase), we can use one three-phase three-level inverter [10,11]. This works, of course, only for those cells which are directly connected to each other (the 'big cells'), and not for the floating ones (the 'small cells'). The NPC inverter has only one common intermediate circuit for all three phases, instead of separate ones for each H-bridge it replaces. This leads to a further simplification of the feeding transformer and rectifiers. The resulting topology, which combines the SHB with the NPC inverter, is shown in Figure 2.10.

In this topology, we have reduced the feeding to one 'big' DC link, which is common for all three phases, and three floating 'small' DC links. But we have seen that 'big cells' deliver mainly active power, whereas 'small cells' deliver mainly reactive power. This rises the idea to remove the feeding of the latter completely and let them produce reactive power only [14–16]. By eliminating those power supplies, we considerably reduce the complexity of the feeding transformer and rectifiers: only that of the NPC inverter remains. This reduces the inverter cost and increases its reliability. At the same time, converter efficiency is increased by elimination of related power-supply losses.

However, ensuring zero active power for the non-supplied cells is not an easy task. This is required to keep their capacitor voltages stabilized. We will see how this can be achieved by an appropriate inverter control method in the following chapters.

Figure 2.11 shows the resulting circuit diagram of our hybrid asymmetric multi-level inverter for medium-voltage drive applications [14–16]. It consists of a three-phase three-level IGCT inverter (main inverter), with a two-phase two-level IGBT inverter (sub inverter) in series with each phase. IGCT with a high voltage-blocking capability are used to provide the main power with high reliability and low losses, IGBT with a higher switching-frequency capability are used to reduce the output harmonic content. We will use a ratio of 3 between the capacitor voltages of the main and the sub inverter to obtain a maximum of output-voltage levels. By addition and subtraction of these voltages, nine different output-voltage levels can be generated.

#### 2.3.2 Properties

The power-part topology of our hybrid asymmetric nine-level inverter for medium-voltage drive applications is a merger of the well-known IGCT NPC inverter, the well-known IGBT SHB inverter, and the new concept of asymmetric multi-level inverters. The power is supplied from the net by an input transformer and twelve pulse rectifier (higher pulse number in special cases). The robust IGCT NPC inverter delivers the active power with a poor waveform but low losses. The series-connected IGBT H-bridge cells improve the output quality to a nine-level waveform. The whole circuit remains very efficient, simple and reliable.

The output-voltage steps are steep but limited in magnitude. Therefore no output filter is needed even for retro-fit applications. Due to the small voltage steps of this inverter, also the high-frequency common-mode voltage is small enough to be of no further concern.

For applications where energy recuperation is desired, a simple back-toback connection of two inverters can be realized. The transformer and rectifier are thus replaced by a second hybrid inverter [14]. A so called common DC bus application, where several inverters are connected to the same intermediate circuit, is possible as well.

The main problem of this inverter lies in the control part. Since there is no

Figure 2.11: Circuit diagram of a hybrid asymmetric nine-level inverter in a medium-voltage drive application. The three sub-inverter intermediate circuits are *not* supplied by a power source.

feeding of the three floating H-bridge cells, we need a control method to keep their capacitor voltages stable. At the same time, this control method must assure a stable neutral-point voltage of the NPC inverter part as well.

Ensuring zero active power for the non-supplied cells is not an easy task. The resulting system is unstable, and without control the non-supplied intermediate-circuit capacitor voltages will quickly run away from their nominal values. An appropriate converter control method is needed to stabilize those voltages, preferably without deteriorating the output voltage. In general, this can not be done instantaneously by lack of an equilibrium state, but only on an average in time.

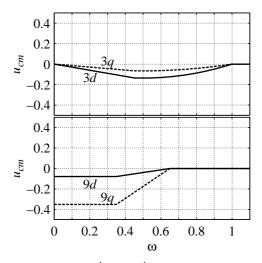

As we will see in the following chapters, we can solve this problem by adding a common-mode voltage to the output (3<sup>rd</sup>, 9<sup>th</sup> or 15<sup>th</sup> harmonic). The amplitude and the absolute frequency of this common-mode voltage will always stay small enough not to harm the driven motor. The additional common-mode voltage will be very small around the nominal operating point (output voltage and frequency). This especially means that an eventual line-side inverter will never need and generate big common-mode voltages.

Apart from normal operation, also the pre-charging of the intermediatecircuit capacitors is an issue to consider. To avoid additional cost and reduced reliability, additional equipment should be kept minimal. Usually a set of precharge resistors along with a bypass contactor on the AC or the DC side of the transformer and rectifiers is used. This enables to benefit from the anyhow existing feeding circuit. The solution on the AC side is more economical for multiple independent DC links (e.g. SHB), the one on the DC side is attractive in case of a single intermediate circuit (e.g. NPC).

Pre-charging of the sub inverters in our hybrid topology can not be accomplished in such a manner. However, additional equipment is not required, by charging their intermediate-circuit capacitors in parallel to and together with those of the main inverter. The latter is pre-charged in a usual way. The switching configuration used for this purpose is explained in Chapter 8.

### 2.3.3 Variants

The proposed power-part topology of our hybrid asymmetric nine-level inverter is not the only viable solution. Within the same concept, other variants are possible as well. Some of these possibilities are given in the following, which can be used alone or in combination. This dissertation does not further study their properties, but its theory can be extended and applied to them as well.

Instead of using a ratio of 3 between the capacitor voltages of the main and the sub inverter, we can choose a ratio of 2 as well.<sup>1</sup> In this case, we obtain a seven-level inverter with some redundant states. These redundancies can be used either to reduce the switching frequency of the semiconductor components, or to influence the capacitor loading of the floating H-bridge cells [9, 15, 16].

As in general concepts for symmetric and asymmetric multi-level inverters, we can of course increase the number of floating cells per phase beyond one. They can have all the same or (partly) different capacitor voltages, and (partial) feeding is possible as well [9–11, 15, 16]. A higher number of outputvoltage levels can be obtained, with or without redundant states. However, an increasing number of non-fed intermediate-circuit capacitors will increase control complexity and might limit the operating range.

The floating cells are not limited to two-level H-bridges, but can be more complex structures as well [9, 35]. Mainly three-level or combined two/three-level H-bridges are of practical interest [10, 11, 15]. Similarly, the main inverter

<sup>&</sup>lt;sup>1</sup>With a ratio of 1, the multi-level inverter is symmetric [40]. With ratios of 1, 2 or 3, the multi-level inverter has a uniform step (voltage difference between two adjacent output-voltage levels); its step is non-uniform with other values [9].

is not limited to a three-level NPC topology. As an alternative, the classical two-level inverter is of practical interest as well [9–11, 15, 16].

## Chapter 3

# **Pulse-Width Modulation**

Voltage-source inverters—two-level and multi-level—have a finite number of possible output voltages. For most applications, especially motor drives and net inverters, sinusoidal output voltages are desired. Different modulation methods exist to generate appropriate output voltages, taking the inverter limitations and required output quality into account.

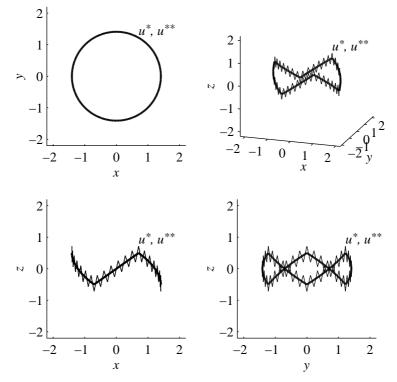

In this chapter, we will investigate the widely used and well-known pulsewidth modulation (PWM) methods [41–46]. Many variants exist, especially for multi-level inverters [9,47–52]. We will discuss some properties and choose a modulator for our hybrid asymmetric multi-level inverter.

In the following sections, we will define all inverter voltages relative to the (equivalent) intermediate-circuit midpoint. For all inverters—two-level or multi-level—the minimum value of the output phase voltage will be normalized equal to -1, and the maximum value equal to +1. For two-level inverters only those two output states exist. Multi-level inverters have additional states in between, which are usually equally distributed between those limits. With an equal distribution, the multi-level inverter has a uniform step (voltage difference between two adjacent output-voltage levels); its step is non-uniform with other values [9].

We will define the modulation index as the ratio of the fundamental phasevoltage amplitude and the maximum inverter phase output voltage. With the normalized inverter voltages defined above, the modulation index equals the fundamental phase-voltage amplitude.

## 3.1 Two-Level PWM Strategies

Two-level pulse-width modulation is well-known and widely used in power electronics. We will explain its principle and variants in this section.

#### 3.1.1 Basic Principle

Within a switching interval  $t_s$ , an average output voltage  $\bar{u}$  is generated by switching the two output-state voltages  $u_1$  and  $u_2$  for appropriate times  $t_1$  and  $t_2$ :

$$t_1 u_1 + t_2 u_2 = t_s \bar{u}, \quad \text{with } t_1 + t_2 = t_s.$$

(3.1)

We can solve this equation with respect to the switching times:

$$t_1 = \frac{\bar{u} - u_2}{u_1 - u_2} t_s, \quad t_2 = \frac{\bar{u} - u_1}{u_2 - u_1} t_s.$$

(3.2)

We see a linear relationship between the switching times  $t_k$  and the average output voltage  $\bar{u}$ .

The previous equations can also be written in terms of the duty cycles  $d_k$ , which are the conduction times  $t_k$  relative to the switching interval  $t_s$ :

$$d_k = \frac{t_k}{t_s}, \quad k = 1, 2;$$

(3.3)

$$d_1u_1 + d_2u_2 = \bar{u}, \text{ with } d_1 + d_2 = 1;$$

(3.4)

$$d_1 = \frac{u - u_2}{u_1 - u_2}, \quad d_2 = \frac{u - u_1}{u_2 - u_1}.$$

(3.5)

From (3.5), we see that the duty cycles can also be interpreted as normalized average voltages. The duty cycle  $d_2$  corresponds to the average voltage  $\bar{u}$  for the mapping  $[u_1, u_2] \rightarrow [0, 1]$ .

For practical realization, we must determine the switching moments, when we switch from one output state to the other. We can either calculate the switching times according to (3.2) and use a timer to detect the switching moments. Or we can use the linearity of (3.2) and compare the desired output voltage with a linear ramp signal in each switching interval, as illustrated in Figure 3.1.

The ramp can either be raising or falling, in both cases the higher outputvoltage level is chosen if the desired voltage is bigger than the ramp, and the lower output-voltage level is chosen if the desired voltage is smaller than the ramp. The raising and/or falling ramps of all the consecutive switching intervals form the carrier signal of the pulse-width modulation method.

Figure 3.1: Determining the PWM switching moment, where we switch the output voltage u between the two output-states voltages  $u_1$  and  $u_2$ , by comparing the (desired) average output voltage  $\bar{u}$  (or a duty cycle  $d_k$ ) with a linear ramp signal c in a switching interval  $t_s$ . This diagram corresponds to (3.2), (3.3) and (3.5), as can be seen by checking congruent triangles.

#### 3.1.2 Variants

Based on this principle, there are several different ways to generate the modulation signals for an inverter [41–46]. But they can all be represented by similar graphical diagrams: a reference signal is compared to a carrier signal, and the output state is chosen according to which of the two signals is the biggest. It is especially mentioned here again, that also methods which only use calculated switching times, like the well-known space-vector PWM, have a corresponding graphical representation [42–46].

The main differences are in the choice of the carrier and reference signals. The possibilities are listed below.

- The carrier is usually a symmetrical triangular signal, but a saw tooth, or even irregular mixtures, can be used as well. The symmetrical signal produces less harmonics [41].

- If the inverter has several branches (H-bridge, three-phase inverter), a reference signal for each branch (phase) is needed. For each reference either the same carrier or phase-shifted carriers can be used. The same carrier is normally chosen, because it produces less harmonics in the branch-to-branch (phase-to-phase) voltages [41].

- In the case of multiple phases (branches), a common signal can be added to each of their references. This does not change the phase-to-phase

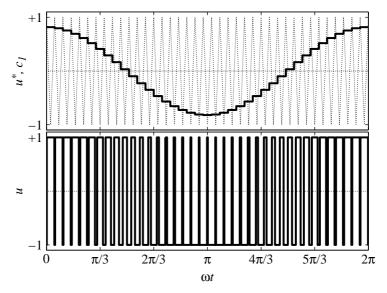

Figure 3.2: Reference signal  $u^*$ , triangular carrier  $c_1$  and output voltage u of a two-level inverter.

(branch-to-branch) reference signal, but does change the modulation pattern. It can of course only be done if the mid or star point of the load is not connected. This is often used to optimize the switching pattern with respect to generated harmonics or device switching frequency [43–46].

• The reference signals can be continuous or sampled synchronously to the carrier signal [52, 53]. The latter method generally produces less current harmonics [52]. Since digital controllers are used anyway nowadays and it is of no use to have a controller which is much faster than the modulator, this method is the preferred choice. Having the whole controller sampled this way also has the advantage of eliminating the switching-frequency content in the current measurements [53].

An example of a two-level pulse-width modulation is given in Figure 3.2.

## 3.2 Multi-Level PWM Strategies

Multi-level pulse-width modulation is an extension of the two-level PWM principles. We will discuss its variants in this section.

#### 3.2.1 Basic Principle

As for the two-level PWM, an average output voltage  $\bar{u}$  is generated by switching several (or even all) of the output-state voltages  $u_{1...n}$  for appropriate times within a switching interval  $t_s$  [25]. Normally, only the two closest states with voltages directly below and above the desired output voltage are used. The adjacent output-states voltages form modulation bands. Modulating only within such bands requires the fewest switching actions and produces the smallest harmonic content [52].

As for the two-level PWM, we can use carrier signals to determine the switching moments. Similarly to Figure 3.1, we will need one carrier per modulation band (pair of adjacent output-states voltages). For an inverter with n phase output levels, we have n-1 modulation bands, and we thus need n-1 carrier signals [51].

#### 3.2.2 Variants

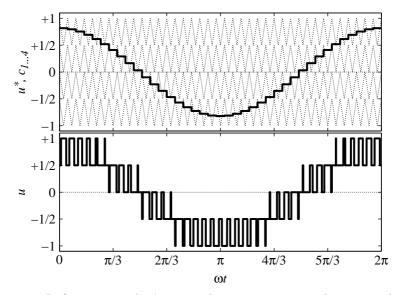

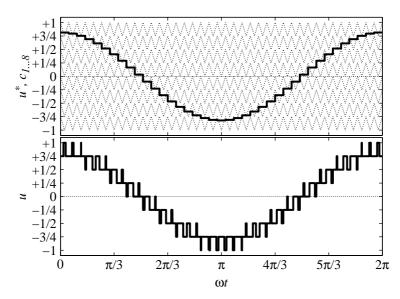

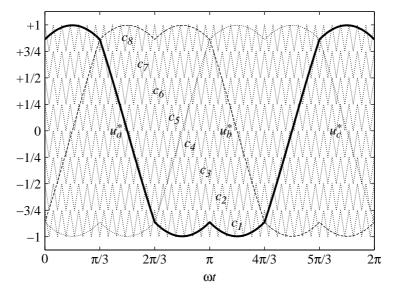

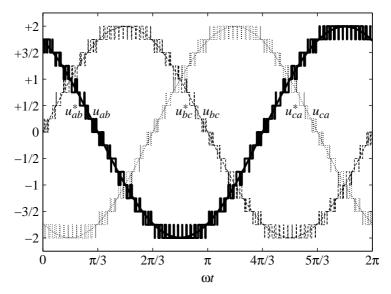

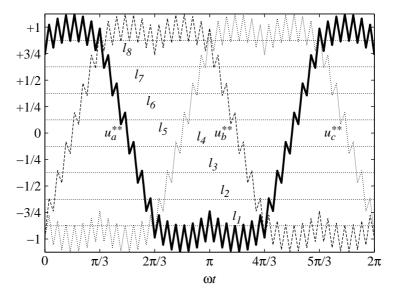

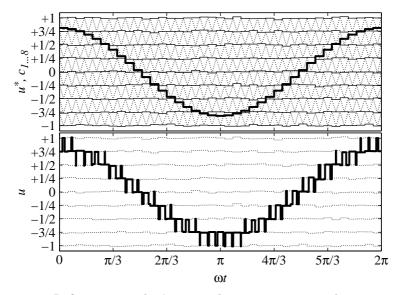

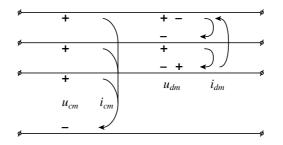

As for the two-level PWM, there are several different ways to generate the modulation signals. Additional to the possibilities listed in Section 3.1, the multiple carrier signals can have some phase shifts relative to each other [48, 49, 51, 52], or carriers with different waveforms can be used [50, 52]. The most used arrangements are equal triangular signals, which are either in-phase or alternated opposite-phase. Examples of a five- and a nine-level pulse-width modulation are given in Figure 3.3 and 3.4, where equal and in-phase carrier waveforms are used.

Carrier arrangements other than in adjacent-voltage modulation bands exist as well, such as the often used arrangement with horizontally distributed triangular signals (with a magnitude which reaches from the lowest (-1) to the highest (+1) state voltage) [48]. Actually, this method generates exactly the same output voltage as the alternated opposite-phase one, since the carrier line segments cover each other exactly.

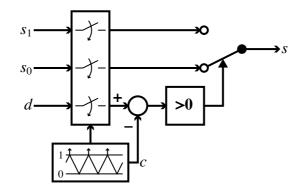

Depending on the hardware realization of the multi-level inverter (seriesconnected H-bridges SHB, neutral-points clamped NPC, imbricated cells IC,  $\ldots$ ), a control function is needed to associate the output state command to the individual switch commands. This function should also handle possible redundant states, for example by cycling through them. For certain hardware/modulator combinations a direct relation between the carrier signals and the individual switch commands exists (NPC with vertically distributed carriers, SHB and IC with horizontally distributed carriers) and therefore no additional function is needed. These combinations are often used in multi-level applications [4, 5, 20, 23, 26].

Figure 3.3: Reference signal  $u^*$ , triangular carriers  $c_{1...4}$  and output voltage u of a five-level inverter.

Figure 3.4: Reference signal  $u^*$ , triangular carriers  $c_{1...8}$  and output voltage u of a nine-level inverter.

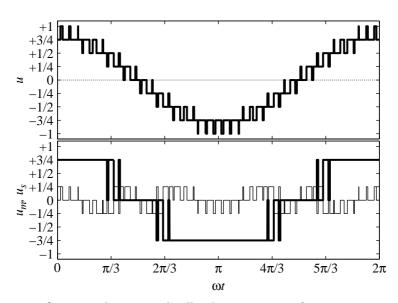

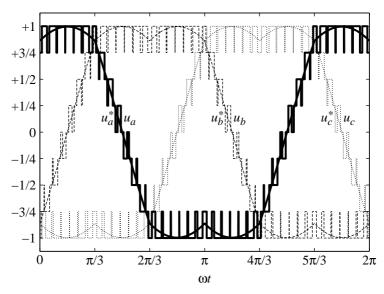

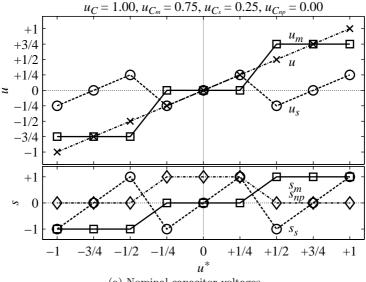

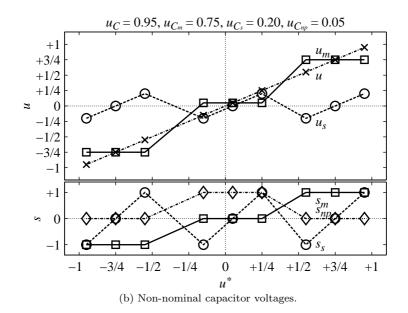

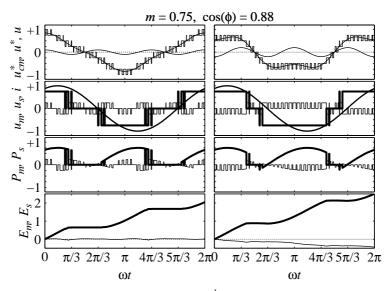

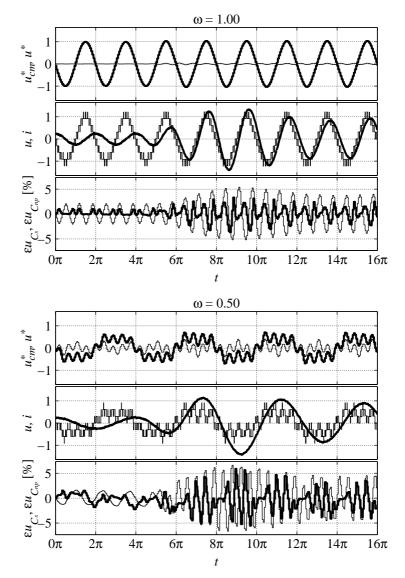

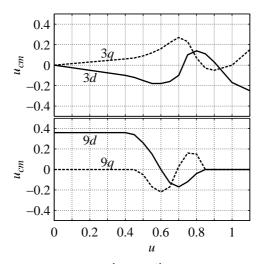

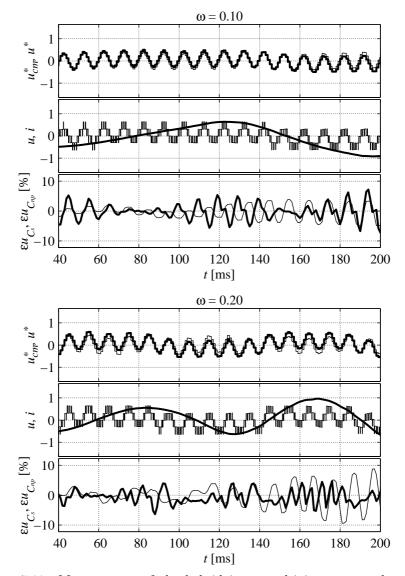

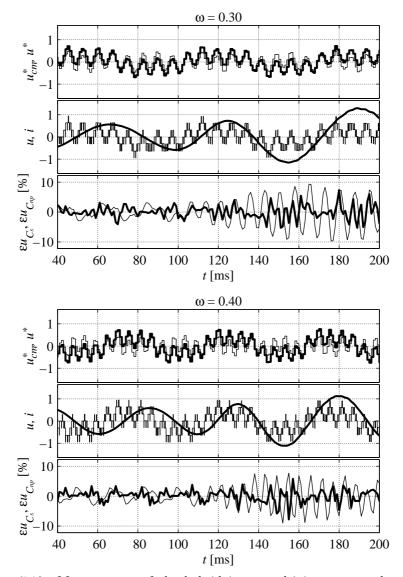

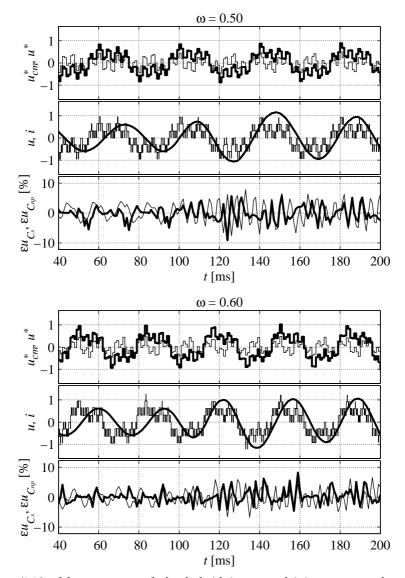

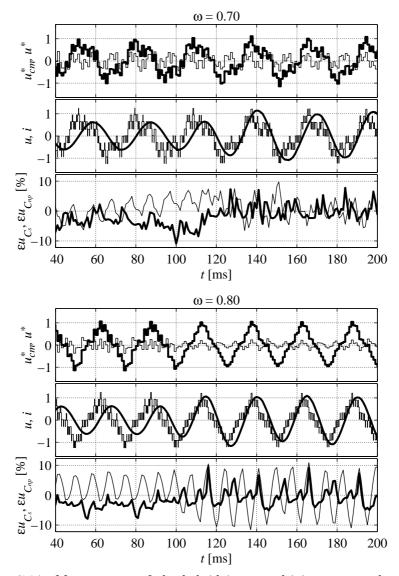

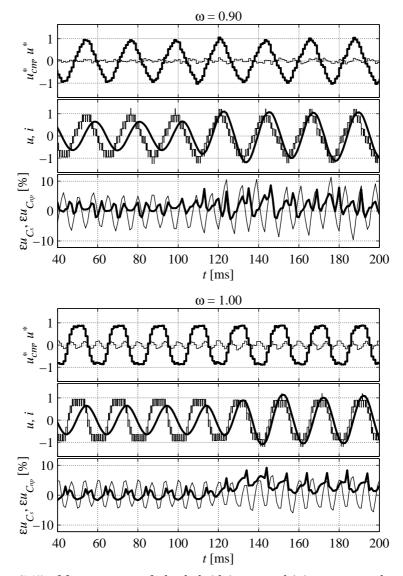

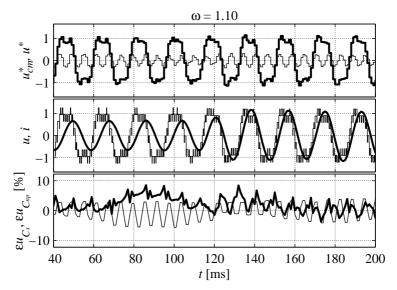

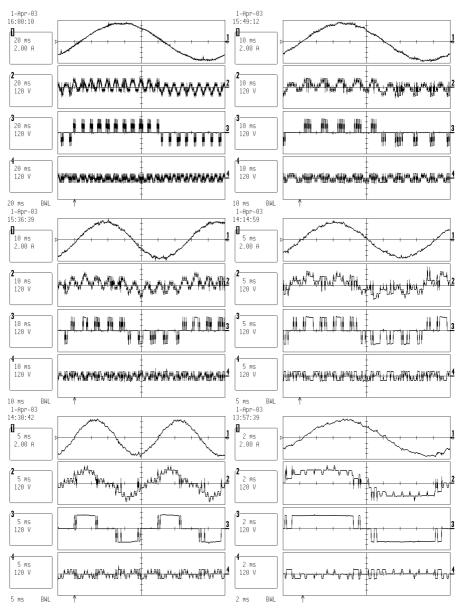

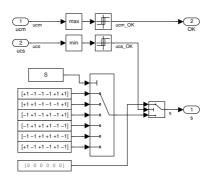

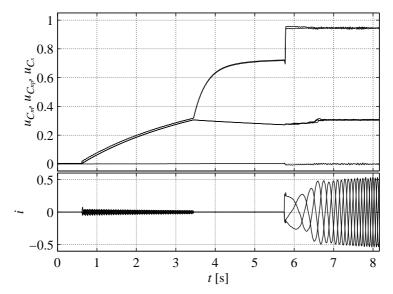

Figure 3.5: Output voltage u and cell voltages  $u_m$ ,  $u_s$  of an asymmetric ninelevel inverter.