## LOAD SHARING FOR MULTIPROCESSOR NETWORK NODES

### THÈSE N° 2725 (2003)

PRÉSENTÉE À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS

SECTION DES SYSTÈMES DE COMMUNICATION

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES TECHNIQUES

#### **PAR**

#### Lukas KENCL

Master en Informatique, Charles University, Prague, République Tchèque et de nationalité tchèque

acceptée sur proposition du jury:

Prof. J.-Y. Le Boudec, directeur de thèse Dr P. Droz, rapporteur Dr T. Przygienda, rapporteur Dr J. Rexford, rapporteur Prof. P. Thiran, rapporteur © Copyright by Lukas Kencl 2003 All Rights Reserved

# Abstract

This thesis discusses techniques for sharing the processing load among multiple processing units within systems that act as nodes in a data communications network.

Load-sharing techniques have been explored in the field of computer science for many years and their benefits are well known, including better utilization of processing capacity and enhanced system fault tolerance. We discuss deploying such methods in the specifics of the networking environment. We concentrate particularly on the data plane, or the data packet-processing tasks. After reviewing the main results in the fields of load sharing and multiprocessor networking systems architectures, we conduct a preparatory optimization study of a router system to gain better understanding of the optimization issues in a particular multiprocessor system.

The main contribution of this thesis, the adaptive load-sharing method, is presented next. We first formulate the optimization problem of mapping packets to processors. The goal is to minimize the likelihood of flow reordering, while respecting certain system constraints, such as the acceptable probability of a packet loss. As we show that the task is an  $\mathcal{NP}$ -complete problem, we propose a heuristic method that uses an adaptive hash-based mapping to assign packets to processors. We demonstrate its advantages and prove that the method adaptation policy possesses the key minimal disruption property with respect to the mapping. In other words, the adaptation results in a minimum number of flows being moved among processing units. Further on, the method is validated in an extensive set of simulations designed to imitate the networking environment.

Finally, two sample applications, an architecture of a multiprotocol router and an implementation of a server load balancer on a network processor demonstrate the applicability of the method.

# Zusammenfassung

Thema der vorliegenden Doktorarbeit sind Techniken zur Lastverteilung zwischen Prozessoren in Systemen, welche die Funktion von Netzwerkknoten in einem Datenkommunikationsnetz haben.

Techniken zur Lastverteilung werden in der Informatik schon seit vielen Jahren erforscht, und ihre Vorzüge, wie bessere Ausnutzung der Rechnerkapazität und eine grössere Fehlertoleranz des System, sind bestens bekannt. Die vorliegende Arbeit befasst sich mit der Anwendung dieser Methoden unter den spezifischen Bedingungen von Datennetzen. Hierbei liegt der Schwerpunkt der Betrachtung auf der Datenebene, bzw. auf der Verarbeitung von Datenpakten.

Nach einer Übersicht zu den wichtigsten Resultaten aus den Bereichen Lastverteilung und Architekturen von Multiprozessor-Netzwerksystemen wird eine erste Optimierungsstudie eines Router-Systems erarbeitet. Ziel ist hier die Erlangung eines tieferen Verständnisses der Optimierungsproblematik am Beispiel eines ausgewählten Multiprozessorsystems.

Anschliessend wird der Hauptbeitrag der vorliegenden Doktorarbeit, die Methode adaptiver Lastverteilung, vorgestellt. Zuerst wird das Optimierungsproblem für die Verteilung von Paketströmen auf Prozessoren formuliert. Ziel hierbei ist die Minimierung der akzeptablen Wahrscheinlichkeit einer ungewünschten Neuzuordnung eines Datenstromes bei Berücksichtigung bestimmter Systemvorgaben, wie z.B. der Wahrscheinlichkeit eines Paketverlustes. Da im folgenden gezeigt wird, dass diese Aufgabe ein  $\mathcal{NP}$ -vollständiges Problem ist, wird eine heuristische Methode vorgeschlagen, welche ein adaptives, hash-basiertes Verfahren für die Verteilung der Pakete auf die Prozessoren verwendet. Die Vorzüge dieser Methode werden aufgezeigt und

es wird bewiesen, dass das Adaptionsverfahren die grundlegende Eigenschaft minimaler, durch Neuzuordnung verursachter Paketstromunterbrechungen (minimal disruption property) besitzt. Damit verursacht der Adaptionsvorgang die Verschiebung einer lediglich minimalen Anzahl von Paketströmen zwischen den Prozessoren. Anschliessend wird die Methode in umfassenden Simulationen validiert. Dabei werden typische Einsatzbedingungen modelliert.

Die Anwendbarkeit der Methode wird anhand zweier Beispiele – der Architektur eines Multiprotokoll-Routers und der Netzwerkprozessor-Implementierung einer Lastverteilung für eine Serverfarm – unter Beweis gestellt.

To Jitka.

# Acknowledgments

First of all, it is a great pleasure to thank my advisor, Prof. Jean-Yves Le Boudec, who has provided me with excellent guidance throughout my Ph.D. research and has had enormous patience with me. I thank him for the many fruitful discussions and his vital contributions to this thesis.

I also thank the IBM Zurich Research Laboratory for providing me with a splendid working environment. It is a delight to work in a modern environment and with such competent and creative people. I am especially grateful to my manager, Patrick Droz, who has supported me throughout, helped me narrow the scope of the thesis by asking the right questions and made sure I had enough time and energy to finish it.

Furthermore, I thank my colleagues, namely Daniel Bauer, Ed Bowen, Robert Haas, Ton Engbersen, Laurent Frélechoux, Mitch Gusat, Andreas Herkersdorf, Ilias Iliadis, Andreas Kind, Bernard Metzler, Cyriel Minkenberg, Sean Rooney, Patricia Sagmeister, Jan Van Lunteren, Marcel Waldvogel and many others, for providing me with excellent comments and pointers to relevant publications and for creating a friendly working atmosphere. Special thanks go to my office mates, Sonja Buchegger and Roman Pletka, who not only spent endless time in scientific discussions with me, but were also enormous fun.

I also thank our visiting students, Bozidar Radunovic and Riccardo Russo, for their creative approach to the problems studied and their significant contributions to exploring the various subtopics of this work.

My sincere thanks to Lilli-Marie Pavka, Charlotte Bolliger and Urs Bitterli for helping me improve the quality of my publications enormously.

Last, but certainly not least, I thank my wife, Jitka. It is only by virtue of her love and sacrifice that I was able to finish this work. Being a wonderful wife and a caring mother, she has made the years spent working on this thesis fine and enjoyable. "However, how to distribute packets across parallel links while achieving load balance among the links and maintaining packet order in the same flow remains challenging."

H. Jonathan Chao, Next Generation Routers, September 2002.

# Contents

| $\mathbf{A}$ | Abstract        |         |                                           |    |  |

|--------------|-----------------|---------|-------------------------------------------|----|--|

| Ζι           | Zusammenfassung |         |                                           |    |  |

| A            | ckno            | wledgr  | nents                                     | ix |  |

| 1            | Inti            | roduct  | ion                                       | 1  |  |

|              | 1.1             | Optin   | nizing network nodes                      | 1  |  |

|              | 1.2             | Outlin  | ne                                        | 3  |  |

|              | 1.3             | Claim   | S                                         | 4  |  |

| <b>2</b>     | Sta             | te of t | he art                                    | 7  |  |

|              | 2.1             | Introd  | luction                                   | 7  |  |

|              | 2.2             | Load    | sharing and networking                    | 7  |  |

|              |                 | 2.2.1   | Load sharing in general                   | 7  |  |

|              |                 | 2.2.2   | Load sharing in networking                | 8  |  |

|              |                 | 2.2.3   | Robust hash routing                       | 10 |  |

|              | 2.3             | Route   | er architecture                           | 14 |  |

|              | 2.4             | Server  | r farms                                   | 18 |  |

|              |                 | 2.4.1   | Architectural demands                     | 18 |  |

|              |                 | 2.4.2   | Web caching and content delivery networks | 19 |  |

|              |                 | 2.4.3   | Server farm load balancing                | 20 |  |

|              | 2.5             | Concl   | usions                                    | 24 |  |

| 3 | Opt         | imizin | g router architecture                                         | 27 |

|---|-------------|--------|---------------------------------------------------------------|----|

|   | 3.1 Introdu |        | luction                                                       | 27 |

|   | 3.2         | Gener  | al distributed router architecture                            | 28 |

|   |             | 3.2.1  | Router model                                                  | 28 |

|   |             | 3.2.2  | LFE and MFE model                                             | 30 |

|   |             | 3.2.3  | Switch model                                                  | 33 |

|   |             | 3.2.4  | Time a packet spends within the system                        | 37 |

|   | 3.3         | Cost   | optimization                                                  | 37 |

|   |             | 3.3.1  | Forwarding engine cost                                        | 37 |

|   |             | 3.3.2  | Switch cost                                                   | 37 |

|   |             | 3.3.3  | Total system cost                                             | 39 |

|   |             | 3.3.4  | Optimization problem                                          | 39 |

|   | 3.4         | Nume   | rical results                                                 | 39 |

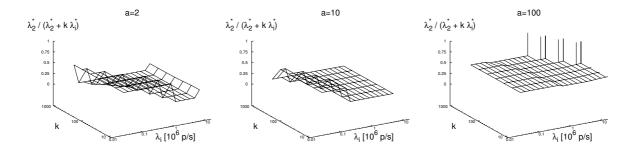

|   |             | 3.4.1  | Optimization                                                  | 39 |

|   |             | 3.4.2  | Total system cost                                             | 40 |

|   |             | 3.4.3  | Distribution of resources—LFEs, MFEs and switch capacity $$ . | 41 |

|   |             | 3.4.4  | Distribution of processing capacity—LFEs and MFEs             | 42 |

|   |             | 3.4.5  | Switch speed                                                  | 45 |

|   | 3.5         | Load   | sharing in a router                                           | 47 |

|   |             | 3.5.1  | Acceptable load sharing                                       | 47 |

|   |             | 3.5.2  | Other system requirements                                     | 48 |

|   | 3.6         | Concl  | usions                                                        | 49 |

| 4 | Ada         | ntive  | load sharing                                                  | 51 |

| • | 4.1         | -      | luction                                                       | 51 |

|   | 4.2         |        | ion and assumptions                                           | 52 |

|   | 4.3         |        | t-to-NPU mapping                                              | 54 |

|   | 4.4         |        | nization problem statement                                    | 57 |

|   | 4.5         | _      | tive load-sharing heuristic                                   | 59 |

|   | 2.0         | 4.5.1  | Adaptation algorithm                                          | 59 |

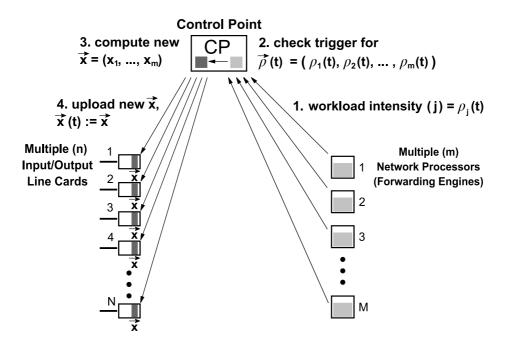

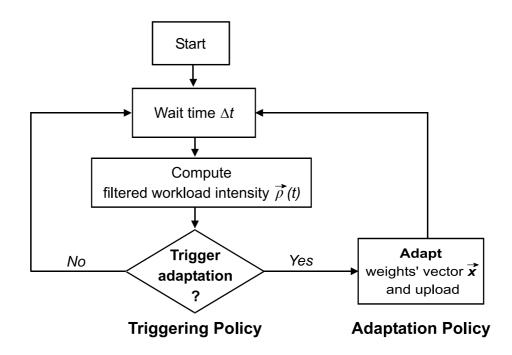

|   |             | 4.5.2  | Triggering policy                                             | 60 |

|   |             |        |                                                               |    |

|   |     | 4.5.3    | Minimal disruption                                            | 63  |

|---|-----|----------|---------------------------------------------------------------|-----|

|   |     | 4.5.4    | Adaptation policy                                             | 67  |

|   | 4.6 | Concl    | usions                                                        | 69  |

| 5 | Met | thod v   | alidation                                                     | 71  |

|   | 5.1 | Introd   | luction                                                       | 71  |

|   | 5.2 | Simple   | e simulator—proof of concept                                  | 72  |

|   |     | 5.2.1    | Potentially congested case                                    | 74  |

|   |     | 5.2.2    | Wrong initial weights case                                    | 76  |

|   | 5.3 | Realis   | tic traffic generation                                        | 76  |

|   | 5.4 | Route    | er system model                                               | 80  |

|   | 5.5 | Result   | ts                                                            | 81  |

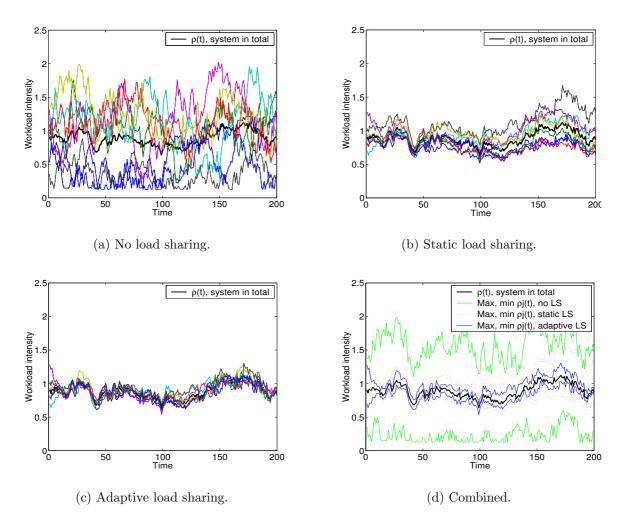

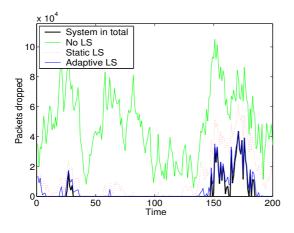

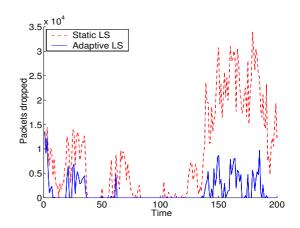

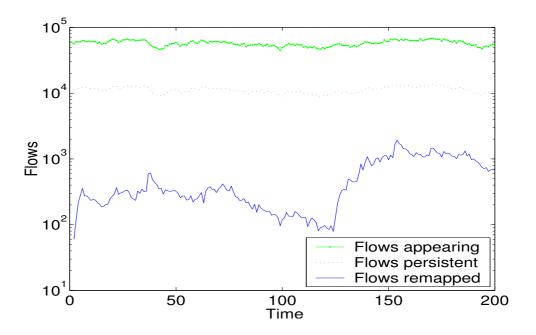

|   |     | 5.5.1    | Adaptive load sharing                                         | 81  |

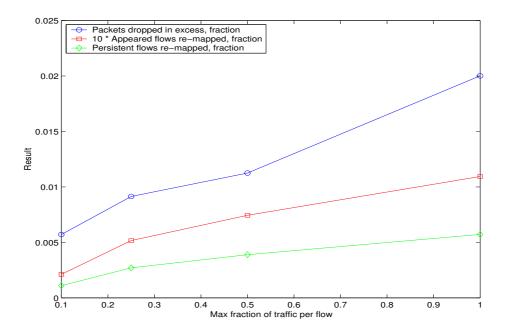

|   |     | 5.5.2    | Influence of maximal flow rate $\epsilon_f$                   | 86  |

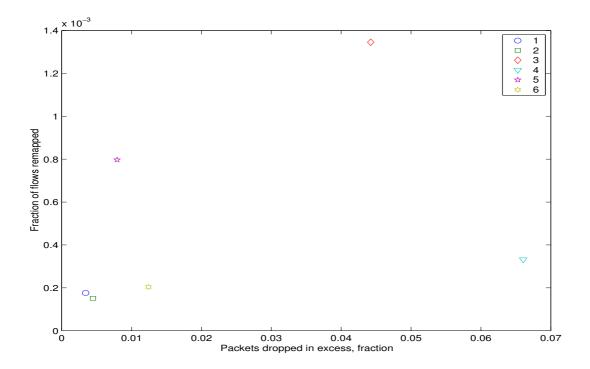

|   |     | 5.5.3    | Fractional factorial analysis of the load-sharing method $$   | 87  |

|   |     | 5.5.4    | Influence of the number of processors                         | 89  |

|   | 5.6 | Concl    | usions                                                        | 91  |

| 6 | App | olicatio | ons in networking systems                                     | 93  |

|   | 6.1 | Introd   | luction                                                       | 93  |

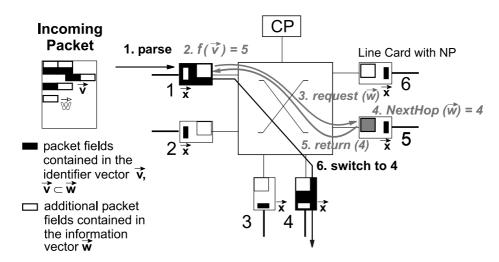

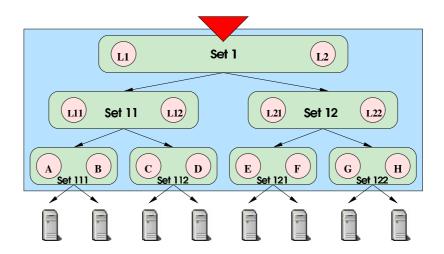

|   | 6.2 | Multip   | protocol router                                               | 94  |

|   |     | 6.2.1    | Router architecture                                           | 94  |

|   |     | 6.2.2    | Load indicator                                                | 96  |

|   |     | 6.2.3    | Pseudo-random function                                        | 96  |

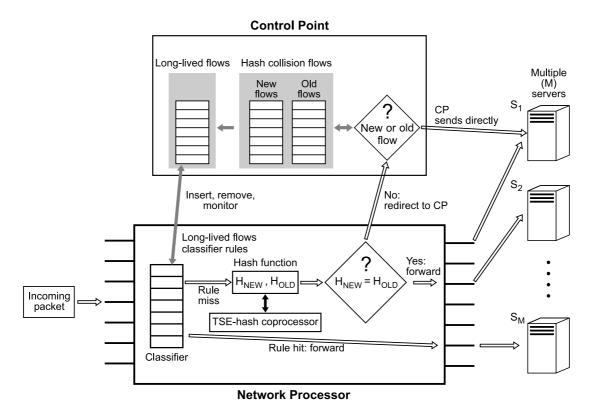

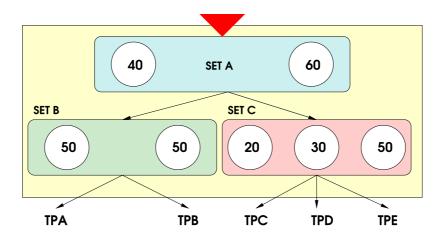

|   | 6.3 | Server   | c load balancer on a network processor                        | 100 |

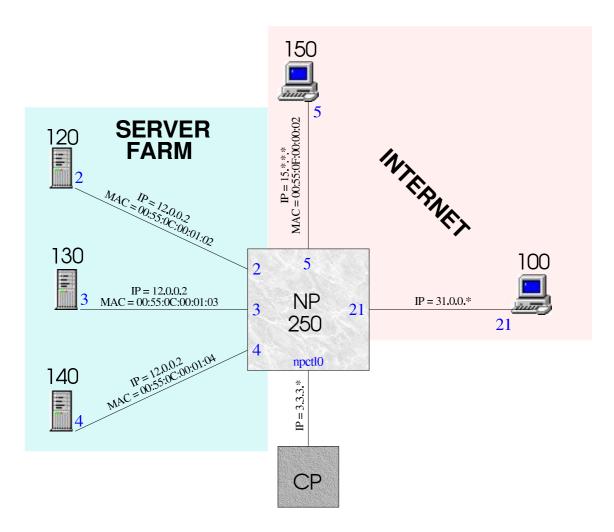

|   |     | 6.3.1    | Server farm topology                                          | 100 |

|   |     | 6.3.2    | Load Balancer on the PowerNP network processor—               |     |

|   |     |          | –general overview                                             | 103 |

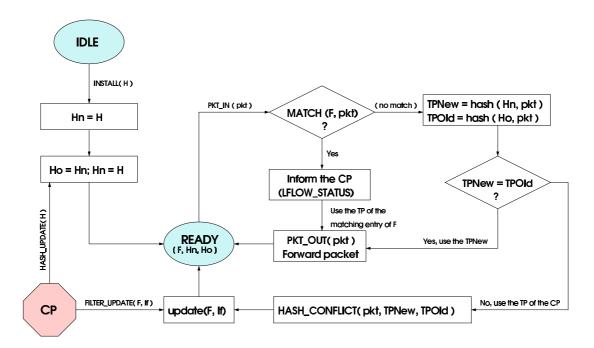

|   |     | 6.3.3    | Network processor data plane                                  | 105 |

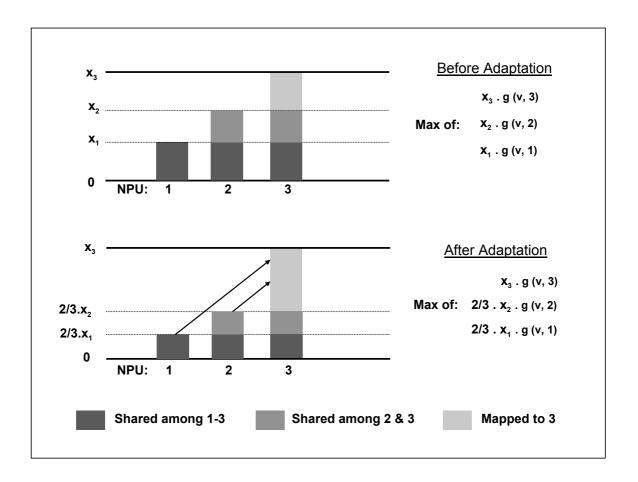

|   |     | 6.3.4    | HRW weights representation on the network processor $\dots$ . | 107 |

|   |     | 6.3.5    | HRW weights data structure                                    | 111 |

|   |     | 6.3.6    | Network processor data plane implementation                   | 118 |

|              | 6.4                                           | Conclusions        | 119 |  |

|--------------|-----------------------------------------------|--------------------|-----|--|

| 7            | Conclusions                                   |                    |     |  |

|              | 7.1                                           | Open issues        | 121 |  |

|              | 7.2                                           | Concluding remarks | 122 |  |

| Bibliography |                                               |                    |     |  |

| Α            | A List of publications and Curriculum Vitae 1 |                    |     |  |

# List of Tables

| 5.1 | Acceptable load sharing                                   | 83  |

|-----|-----------------------------------------------------------|-----|

| 5.2 | Flow remappings                                           | 85  |

| 5.3 | Fractional factorial analysis results                     | 87  |

| 5.4 | Effects of factors.                                       | 88  |

| 5.5 | Influence of the number of NPUs                           | 91  |

| 6.1 | Kernel IP routing table                                   | 101 |

| 6.2 | Kernel ARP table                                          | 102 |

| 6.3 | Results of the simulation using a flat data structure     | 114 |

| 6.4 | Results of two simulations on hierarchical data structure | 117 |

# List of Figures

| 2.1  | Mapping disruption problem                                                               | 11 |

|------|------------------------------------------------------------------------------------------|----|

| 2.2  | Robust hash routing minimizes the mapping disruption                                     | 13 |

| 2.3  | Distributed router architecture                                                          | 16 |

| 2.4  | Parallel router architecture                                                             | 17 |

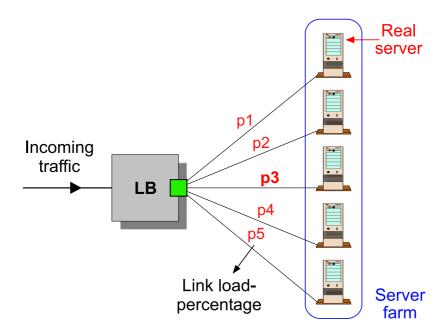

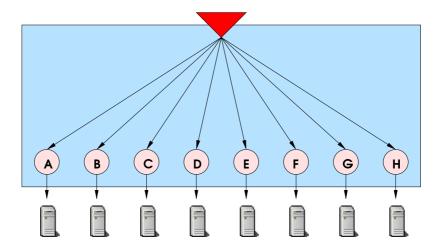

| 2.5  | Server load balancing topology                                                           | 20 |

| 3.1  | LFEs, switch and MFEs within the general distributed router archi-                       |    |

|      | tecture model                                                                            | 29 |

| 3.2  | ${\bf Model\ of\ the\ general\ distributed\ router\ architecture\ with\ multiple\ LFEs}$ |    |

|      | and MFEs                                                                                 | 30 |

| 3.3  | Traffic flows within the switch                                                          | 35 |

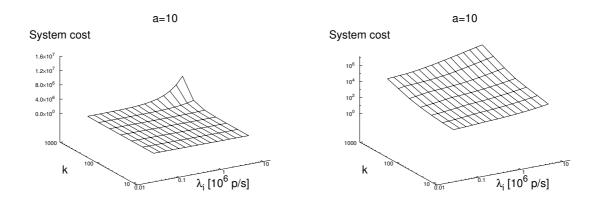

| 3.4  | Total system cost                                                                        | 41 |

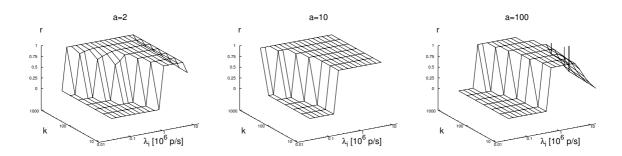

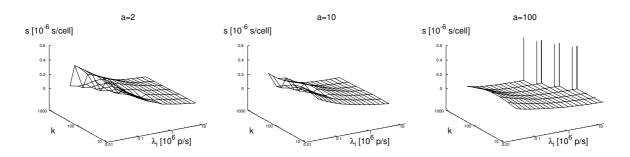

| 3.5  | Fraction of traffic enqueued at LFEs, $r$                                                | 42 |

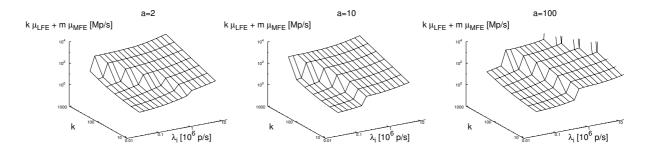

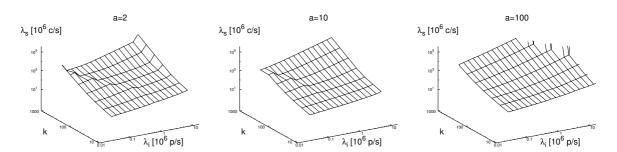

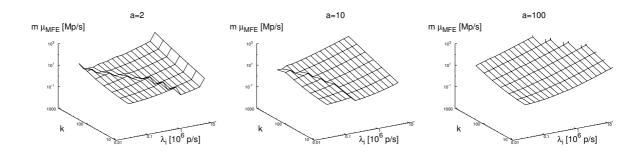

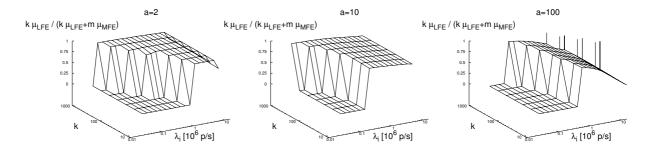

| 3.6  | Total processing power of the FEs                                                        | 43 |

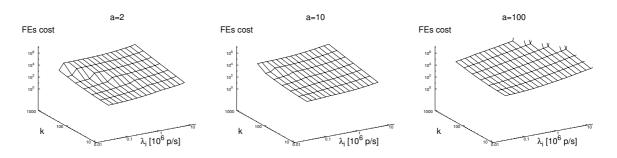

| 3.7  | Total cost of the FEs                                                                    | 43 |

| 3.8  | Switch saturation throughput                                                             | 43 |

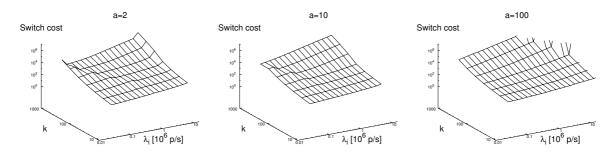

| 3.9  | Switch cost                                                                              | 44 |

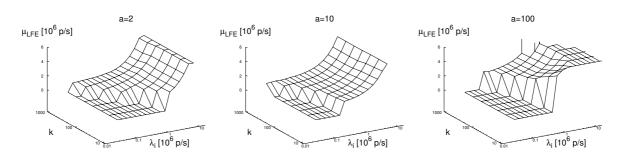

| 3.10 | Optimal processing power per individual LFE                                              | 44 |

| 3.11 | Total processing power of the LFEs (note that the graph was adjusted                     |    |

|      | for the reader's convenience in order to be able to depict the values                    |    |

|      | equal to 0, which would normally tend to negative infinity on a loga-                    |    |

|      | rithmic graph)                                                                           | 44 |

| 3.12 | Total processing power of the MFEs                                                       | 45 |

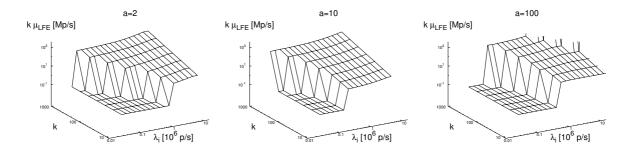

| 3.13 | Fraction of LFE processing power out of total system processing power.                   | 45 |

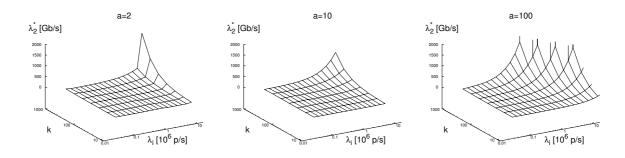

| 3.14 | Switch port transmission speed                                           | 46 |

|------|--------------------------------------------------------------------------|----|

| 3.15 | Traffic at the switch master port—the header passing overhead within     |    |

|      | the switch                                                               | 46 |

| 3.16 | Fraction of the header passing overhead out of the total switch traffic. | 46 |

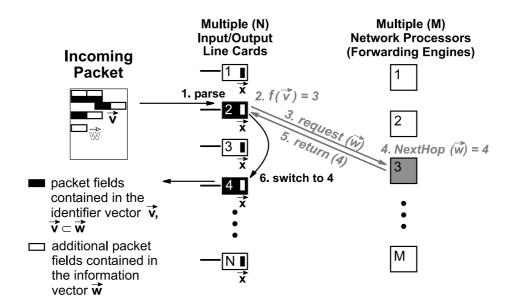

| 4.1  | Load-sharing scheme abstraction                                          | 55 |

| 4.2  | Load sharing with feedback                                               | 60 |

| 4.3  | Adaptation algorithm                                                     | 61 |

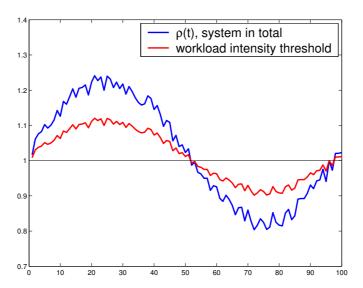

| 4.4  | Example of the dynamic workload intensity threshold as a function of     |    |

|      | a hypothetical filtered total system workload intensity                  | 62 |

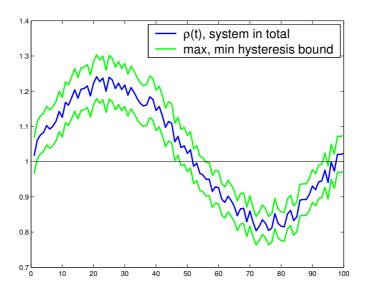

| 4.5  | Example of the hysteresis bound as a function of a hypothetical filtered |    |

|      | total system workload intensity                                          | 63 |

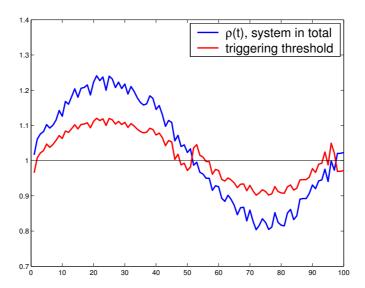

| 4.6  | Example of the triggering threshold as a function of a hypothetical      |    |

|      | filtered total system workload intensity                                 | 64 |

| 4.7  | Minimal disruption property of the adaptation                            | 68 |

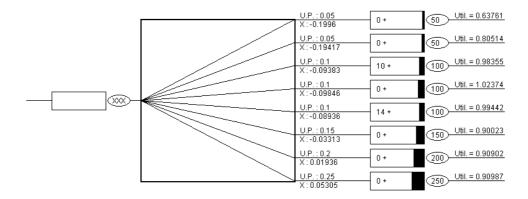

| 5.1  | The simple load-sharing system simulator                                 | 72 |

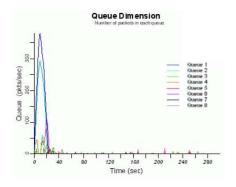

| 5.2  | Number of packets at the ingress queue                                   | 75 |

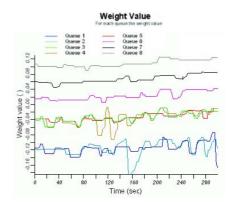

| 5.3  | Evolution of the weights' value                                          | 75 |

| 5.4  | Total number of packets queued in the output queues                      | 75 |

| 5.5  | System workload intensity                                                | 75 |

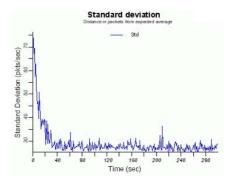

| 5.6  | Standard deviation                                                       | 75 |

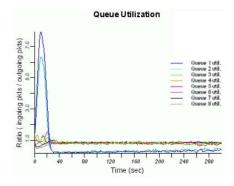

| 5.7  | Number of packets at the input queue                                     | 77 |

| 5.8  | The evolution of the weights' value                                      | 77 |

| 5.9  | Queue occupancy                                                          | 77 |

| 5.10 | Link workload intensity.                                                 | 77 |

| 5.11 | Standard deviation function                                              | 77 |

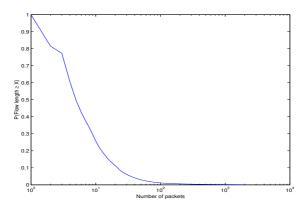

| 5.12 | Flow length cumulative distribution                                      | 78 |

| 5.13 | Per-processor workload intensity                                         | 82 |

| 5.14 | Packets dropped                                                          | 83 |

| 5.15 | Triggering and adaptation policy                                         | 84 |

| 5 16 | Flows re-manned                                                          | 25 |

| 5.17 | Influence of maximal per-flow fraction rate limit $\epsilon_f$         | 86  |

|------|------------------------------------------------------------------------|-----|

| 5.18 | Influence of the number of NPUs                                        | 90  |

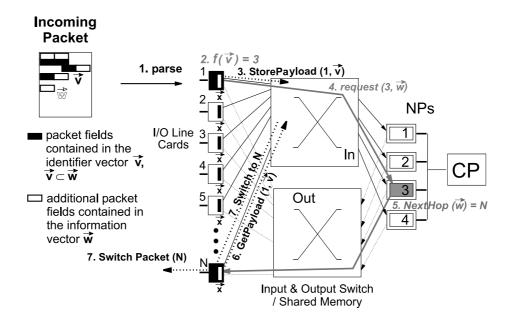

| 6.1  | Load sharing within a distributed multiprotocol router                 | 94  |

| 6.2  | Multiprotocol router, consisting of an input- and output switch/shared |     |

|      | memory and a pool of multiple NPUs, sharing the load of $N$ line cards | 95  |

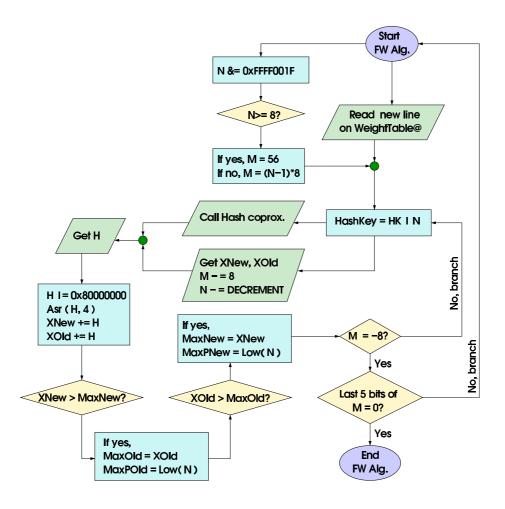

| 6.3  | Sample server farm topology                                            | 102 |

| 6.4  | Server load balancer on the PowerNP network processor                  | 104 |

| 6.5  | NP state diagram                                                       | 106 |

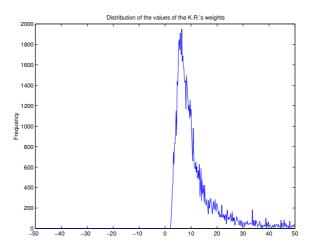

| 6.6  | Ross' weights distribution                                             | 109 |

| 6.7  | Russo's weights distribution                                           | 110 |

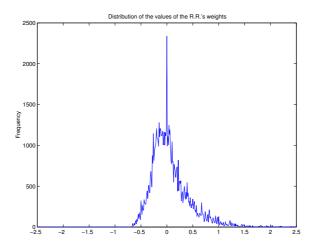

| 6.8  | HRW Mapping computation algorithm                                      | 112 |

| 6.9  | Flat data structure                                                    | 113 |

| 6.10 | Hierarchical data structure                                            | 115 |

| 6.11 | Topology for the hierarchical data structure simulations               | 117 |

# Chapter 1

## Introduction

## 1.1 Optimizing network nodes

With the ever-increasing transport capacity of links of complex data networks such as the Internet, it is the various processing nodes along the paths that the data traverses that are becoming the bottlenecks, preventing speedy and reliable data delivery.

As we are unable to raise the processing capacity of individual processors at an adequate rate, solutions on the device system level that aggregate capacities of multiple processors are increasingly being designed to support the growing data rates.

The functionality requirements for such network elements (routers, servers, server farms, proxies, caches, load balancers, firewalls) are becoming increasingly complex. With respect to networking, we typically distinguish between two kinds of functionalities associated with data communication:

- the *control plane* functionality, which exercises the overall control of the networking communication and the signaling among nodes, and

- the *data plane* functionality, which exercises the actual forwarding, processing, alterations or manipulations of data packets.

The work presented in this thesis concentrates on optimizing the *data plane* functionality of network elements, or, more specifically, optimizing the data plane functionality of network nodes that consist of *multiple processing units*.

The key contribution of this work is a method that optimizes the way the processing load is shared among the multiple processors, while respecting the specific constraints of the networking environment.

We assume that data for processing arrives over network links in the form of packets and that individual packets belonging to a specific connection between end hosts form a flow. Thus, traffic over each network link consists of packets belonging to various flows.

For several reasons, it is desirable that packets belonging to the same flow be processed by the same processor. Processing at different processors may result in packet reordering within a flow. Furthermore, a number of networking applications requires that packets from one flow be processed within some context—for example for reasons of policing or shaping, or in order to process subsequent requests from the same host. The information carried in each packet may require various amounts of processing power and the flows may consist of uneven amounts of packets. The method we present aims to fulfill the flow-preservation requirement while keeping the load on the multiple processors within some degree of balance. Furthermore, the decision where to process a packet is reached fast and without maintaining state information on the flows.

There are several factors that contribute to the difficulty of solving this task. There is high variation in network traffic patterns and they are not easily predictable. Furthermore, even if knowledge of the near future were available, the task of mapping various flows to processors and keeping the load balanced, while optimizing a system-wide function such as the amount of packets reordered, is  $\mathcal{NP}$ -Complete.

The advantages of deploying such a load-sharing method are manifold:

- It increases the total processing capacity of the system. The total load of the system is distributed over the processing elements in an optimal way and thus its processing capacity can be fully utilized;

- It increases the system flexibility. Addition or removal of processing capacity can be performed in a seamless manner with minimal disruption to the processing system;

1.2. OUTLINE 3

• Scalability. The method ensures that increasing the processing capacity of the system results in equivalent increase in processing performance of the system;

• Fault tolerance. A failure in one of the processing nodes is seamlessly hidden by others assuming its task (sharing its load).

There are many applications or systems in the networking area, for which deploying such a method is beneficial. We present two examples, a router and a server farm, but any system requiring that the packet processing load be spread over multiple processing units or destinations would benefit from the method.

The main contribution of this work is the presented load-sharing method. It is an *adaptive heuristic*: adaptive to cope with the varying traffic patterns, and a heuristic as it estimates the near-optimal solution within a very short time.

The method is hash-based, extending the robust hash routing method by Ross [50]. The fact that it is hash-based means that the mapping decision is achieved fast and that no state information on individual flows needs to be stored.

As the robust hash routing method leads to perfect load balancing over non-biased traffic patterns, we introduce the adaptive control loop to cope with the biased patterns. The key contribution of this work is the adaptation policy—we prove that the proposed adaptation policy possesses the minimal disruption property with respect to the flow-to-processor mapping—meaning that only a minimum amount of flows is moving among processors when the mapping is adjusted.

Furthermore, we present an extension of the method that shows how, by maintaining little state information, mapping disruption can be avoided altogether.

#### 1.2 Outline

In Chapter 2, we present an overview of the load-sharing methods in general and of the specific solutions to load-sharing problems encountered in networking. Furthermore, we review the state-of-the-art in the two domains considered for deployment of the load-sharing method, router architecture and server load balancing.

In Chapter 3, a preparatory study of a router architecture is presented, to provide a better understanding of the router design space and of the potential benefits of deploying a load-sharing method within a router.

The main contributions of this thesis are presented in Chapter 4. Here, the *adaptive load-sharing* method is described in detail and the *minimal disruption property* is proved by theoretical means.

In Chapter 5, a practical validation of the method is performed. First, a small, Java-based implementation is used as a proof of concept, and than a large, Matlabbased set of simulations to explore various parameters of the method over Internet-like generated traffic is carried out and discussed.

Real-world system applications of the method are discussed in Chapter 6. An existing implementation of a server farm load balancer on an IBM PowerNP network processor is described in detail, as well as potential implementations in a router system. Some method implementation issues, such as the optimal data structure for the mapping weights, are reviewed.

Finally, in Chapter 7, we offer some concluding remarks on the future applicability of the method and related open issues.

#### 1.3 Claims

- A new method for providing adaptive load sharing among multiple processing

units in a networked environment is presented. The method is hash-based, requires a minimum of state information to be maintained and leads to a minimum

of packet flow disruptions. The method comprises a flow-to-processor mapping

and an adaptive feedback mechanism;

- The minimal disruption property is proved by theoretical means;

- Model of a router equipped with the load-sharing method has been implemented in MATLAB;

- A traffic generator for generating realistic Internet traffic patterns has been

1.3. CLAIMS 5

implemented in MATLAB. The method has been tested extensively using the generated traffic;

- An extension of the method, which leads to zero flow disruption by adding a small amount of state information and duplicating the hash computation, has been developed;

- A prototype of the method has been implemented on the IBM PowerNP network processor to act as a Web server load balancer;

- A study of optimizing the router architecture has been conducted, concluding that parallelism and load sharing on the router data path are applicable and advantageous;

- Two patent applications have been submitted on the two versions of the loadsharing method.

# Chapter 2

# State of the art

#### 2.1 Introduction

In this chapter we are going to review the previous fundamental results in fields related to the topic of this thesis.

Load sharing or load balancing problems have been extensively studied in computer science for many years and there exists a number of works in this area. We present those that were crucial for our work and in the final part of the load sharing discussion we examine in detail the robust hash routing technique, which forms the basis of our optimized load-sharing method.

In the second and third sections of the chapter, we examine more closely previous works on the two classes of network nodes that we discuss in more detail throughout the thesis—multiprotocol routers and Web server farms.

## 2.2 Load sharing and networking

## 2.2.1 Load sharing in general

For a general survey of load-sharing algorithms, see [55]. A widely accepted taxonomy of load-sharing algorithms has been presented by Casavant and Kuhl [8].

Eager, Lazowska and Zahorjan [17] have studied specific adaptive load-sharing

policies, consisting of a transfer and a location policy. Their work shows that simple adaptive load-sharing policies yield significant performance improvements relative to the no load-sharing case and, at the same time, performance very close to complex adaptive policies. In addition, a threshold-based location policy is shown to bring substantial improvements over a random selection location policy.

The task of determining a processing unit on which a specific processing job should be executed so that a system-wide function is optimized has been shown to be  $\mathcal{NP}$ complete in general. El-Rewini, Ali and Lewis [19] provide an overview of the  $\mathcal{NP}$ completeness proofs for various instances of the problem and discuss some candidate heuristics for the solutions.

A heuristic, producing an answer which is not necessarily optimal, but is achieved in short time, is typically used. Such a global task scheduling heuristic usually takes some kind of dynamic processor workload information as input. The most effective representation of the workload index has been a topic of intensive research. Kunz [35] has demonstrated that a single, one-dimensional workload descriptor yields better results than more complex descriptors.

#### 2.2.2 Load sharing in networking

Load-sharing methods have recently been studied in relation to the task of distributing Internet traffic over multiple links or paths within the network [7], [6] [53]. Cao, Wang and Zegura evaluate in [7] the performance of various fast static hashing schemes, as well as of one adaptive, for splitting traffic among multiple links. The following static hash functions are studied:

1. Modulo over Destination Address

$$H(\cdot) = DestIP \mod N.$$

2. XOR Folding of Destination Address:

$$H(\cdot) = (D_1 \oplus D_2 \oplus D_3 \oplus D_4) \mod N$$

,

where  $D_i$  is the *i*-th octet of the destination IP address

3. XOR Folding of Source and Destination Addresses:

$$H(\cdot) = (S_1 \oplus S_2 \oplus S_3 \oplus S_4 + D_1 \oplus D_2 \oplus D_3 \oplus D_4) \mod N$$

where  $S_i$  and  $D_i$  are the *i*-th octets of the source and destination IP addresses, respectively.

4. Internet Checksum of the TCP 5-tuple (source and destination IP address, source and destination port, and protocol ID):

$$H(\cdot) = CheckSum(5 - tuple) \ mod \ N.$$

5. The 16-bit Cyclic Redundancy Check (CRC) function:

$$H(\cdot) = CRC16(5 - tuple) \mod N.$$

The study concludes that except for the CRC-based hash, other methods result in relatively poor traffic load-balancing.

Furthermore, the authors study an adaptive, table-based method, which, when adapted according to the monitored load, gives comparable performance as the CRC-based function, even when using the XOR folding as the primary indexing technique into the table. However, note that such method, as presented, requires to maintain considerable state information on the mapping of table bins. Furthermore, the adaptations may lead to significant disruptions in the mapping.

Basturk et al. [6] explore the possibilities of using the IP anycast routing to distribute traffic load among multiple paths or servers. Several load distribution techniques that pin packets from a particular flow to certain route are discussed. Four different disciplines for selecting the route are evaluated on real network traffic traces: round-robin, random, hash-based and least connections. An interesting finding with respect to the work presented in this thesis is that all the disciplines perform approximately equally well in the key metric of distributing the number of bytes transferred

among the multiple destinations.

Shaikh, Rexford and Shin [53] concentrate on the problem of mapping traffic flows onto multiple network paths in order to achieve better bandwidth utilization and routing stability. The method divides traffic flows into short-lived and long-lived and uses different mapping disciplines for each group, an adaptive one for the long-lived and a static one for the short-lived flows. It is demonstrated that for this problem, thanks to the particular length distribution of network flows, such a hybrid approach is beneficial over each method stand-alone, achieving better balance on one hand and saving on signalling overhead on the other. The study of flow length distribution in [53] has been inspirational for some of the experiments presented in Chapter 5.

Particular interest in load sharing has recently been raised in the areas of Web servers, Web caching and clustered digital libraries [5], [24], [50], [69].

#### 2.2.3 Robust hash routing

The robust hash routing (also known as Cache Array Routing Protocol (CARP)) distributed caching scheme, which uses the highest random weight (HRW) algorithm developed by Thaler and Ravishankar [62], and its more fine-grained, weighted version by Ross [50], is a popular choice for Web caches and is implemented in products offered by Microsoft [5]. This algorithm has become a foundation for our work.

The following example illustrates the general mapping disruption problem, the flaws of basic mapping functions and subsequently the advantages provided by the robust hash routing.

Let  $h(\cdot)$  be a hash function that maps the space of all n-bit binary numbers vectors  $\vec{v}$  to a hash space H. The hash space H is partitioned into N consecutive intervals, corresponding to N destinations for the mapped objects. Assume that a new destination is added to the N existing ones and thus there are now N+1 possible destinations. What fraction of objects do change their destination, if the same mapping (hash) function is still being used? Thaler and Ravishankar [62] refer to this fraction as the disruption coefficient.

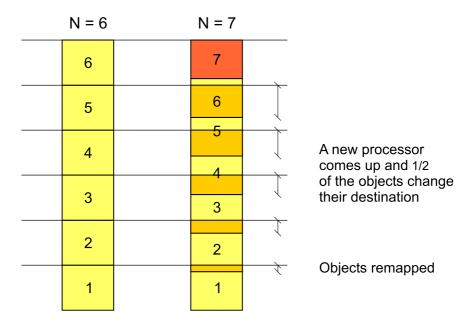

Figure 2.1: Mapping disruption problem

Initially, the hash space is divided into N sets as follows:

$$\left[0,\frac{1}{N}\right], \left[\frac{1}{N},\frac{2}{N}\right], \ldots, \left[\frac{N-1}{N},1\right].$$

If the hash function produces the score  $sc \in \left[\frac{j}{N}, \frac{j+1}{N}\right]$ , then destination j will be chosen. Suppose that all destinations are equally probable to be mapped to, meaning that the distribution of sc is uniform over the hash space H. Then, the hash space will be divided, upon the addition of the new destination, as follows (see Fig. 2.1):

$$\left[0, \frac{1}{N+1}\right], \left[\frac{1}{N+1}, \frac{2}{N+1}\right], \ldots, \left[\frac{N-1}{N+1}, \frac{N}{N+1}\right], \left[\frac{N}{N+1}, 1\right].$$

Only flows that belong to the following subsets have not changed their destination:

$$\left[0, \frac{1}{N+1}\right], \left[\frac{1}{N}, \frac{2}{N+1}\right], \left[\frac{2}{N}, \frac{3}{N+1}\right], \dots, \left[\frac{N-1}{N}, \frac{N}{N+1}\right].$$

The sum of these intervals represents the disruption coefficient:

$$\sum_{i=0}^{N-1} \frac{N-i}{N(N+1)} = \frac{1}{N(N+1)} \sum_{i=1}^{N} i = \frac{1}{2}.$$

This means that in this case 50% of the mapped objects have changed destination. Thaler and Ravishankar prove that the disruption coefficient ranges between 1/N and 1 for all mappings.

The robust hash routing is a mapping designed to avoid large disruption coefficient. With the robust hash routing [62], the object identifier  $\vec{v}$  and the destination index j are used together to generate a hash value or score. For every destination j, a score  $h(\vec{v}, j)$  is computed and the final destination chosen is the one with the maximum score:

$$f(\vec{v}) = j$$

$$\iff \qquad (2.1)$$

$$h(\vec{v}, j) = \max_{k \in [1, N]} h(\vec{v}, k).$$

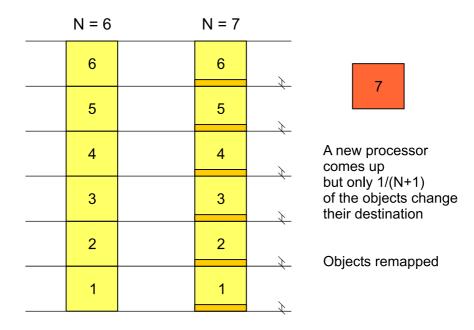

Thaler and Ravishankar [62] demonstrate that if a new destination is added, only a fraction of  $\frac{1}{N+1}$  of the objects is re-mapped (see Fig. 2.2), which is the minimum amount. Thus, we say that the HRW mapping possesses the *minimal disruption* property.

In the form above, the robust hash routing guarantees balancing of the mapped objects over the destinations, but only in case of homogenous size of the destinations. Ross [50] adds multiplicative weights into Eq. 2.2 to provide for heterogenous load distributions over destinations:

Figure 2.2: Robust hash routing minimizes the mapping disruption.

**Def. 1** *HRW Mapping* f. Let  $h(\vec{v},j)$  be a pseudo-random function  $h: V \times \{1,2,\ldots,m\} \to (0,1)$ , i.e., we assume  $h(\vec{v},j)$  to be a random variable in (0,1) with uniform distribution. The HRW mapping  $f(\vec{v})$  is then computed as follows:

$$f(\vec{v}) = j$$

$$\iff \qquad (2.2)$$

$$x_j \cdot h(\vec{v}, j) = \max_{k \in [1, N]} x_k \cdot h(\vec{v}, k)$$

where  $x_j \in \mathbb{R}^+$  is a weight multiplier assigned to each destination.

Ross [50] also introduces a formula for computing the weights  $x_i$ , depending on the target probability  $p_i$  of each destination:

**Theorem 1 (Ross)** Let  $p_1, \ldots, p_N$  be given target probabilities. Reorder the destinations so that  $p_1 \leq \ldots \leq p_N$ . Let

$$x_1 = \left(Np_1\right)^{1/N}$$

and let  $x_2, \ldots, x_N$  be calculated recursively as follows:

$$x_n = \left[ \frac{(N-n+1)(p_n - p_{n-1})}{\prod_{i=1}^{n-1} x_i} + x_{n-1}^{N-n+1} \right]^{\frac{1}{N-n+1}}.$$

(2.3)

Then the robust hash routing algorithm with multipliers  $x_1, \ldots, x_N$  will map the fraction  $p_n$  of incoming objects to the n-th destination,  $n = 1, \ldots, N$ .

To summarize, the HRW mapping possesses the following significant advantages over other hash-based load balancing schemes [50] [62]:

**Load balancing** The mapping provides load balancing over the request object space, even for the heterogeneous case. It allows to split the hashed objects into hash buckets of arbitrary size, as determined by predefined weights.

Minimal disruption In case of a processor failure, removal or addition, the number of request objects that are re-mapped to another destination is minimal.

#### 2.3 Router architecture

Latest developments in transmission technologies have led to an enormous increase in the amount of data transported over the links of the Internet. Such a rapid evolution places significant strain on the interconnecting equipment, primarily routers, to scale with the pace of the transmission speed increase. Recent works [21], [34] have provided a basis for the new generation of interconnecting devices by presenting the first gigabit and terabit router architectures. These works have built on new developments in the areas of switch architectures [20], [39] and fast lookup algorithms [14], [65], [44].

It is becoming increasingly difficult to satisfy the demands for router performance with a traditional centralized architecture [21]. In the case of multiple router inputs and high throughput, the single central processor is not able to cope with its processing task. In order to eliminate the packet processing bottleneck, *multiple* processing units, known as forwarding engines (FE), or, more sophisticated, network processors

(NPU), are typically deployed in contemporary routers. A router system thus consists of multiple processing units gathered around a switch element. Packet processing within such a system is essentially *distributed*. The previously centralized router devices are thus being replaced by routers of more effective architectures, distributed or parallel [10], [64], [11].

In principle, packet processing can either be carried out directly at router inputs, using local forwarding engines (LFE), or at remote master forwarding engines (MFE), reachable through the switch element. Both of these paradigms may be combined in one system. Given the performance demands, a single MFE may not be sufficient and thus MFEs are often grouped into pools of parallel MFEs. Critical related questions emerge—what are the best capacities, locations and schemes of cooperation of all the elements (switch, LFEs, MFEs) within a router system in order to satisfy given system performance demands, and what is the most economical alternative to satisfy those demands?

In the case of a distributed architecture [9], most of the packet processing load is performed by processors typically located directly at the router inputs. Such an architecture has the drawback of poor utilization because all the processors are hardly ever saturated, as the load is almost never evenly distributed over the inputs and does not always reach the nominal rate. Parallel router architectures [4], [23] are based on a pool of parallel processors, located remotely from the inputs, with all of the processors being able to perform the data path processing tasks. Packets may be buffered at the inputs, and relevant fields of the packet (for example, the packet header) are being sent to the pool for resolution. Such an architecture does not suffer from underutilization because loads of all the inputs are combined at the pool. Instead, the pool interconnect tends to become a major bottleneck. Another drawback is that if load balancing is performed over the pool, the load balancing device is a single point of failure for the entire router.

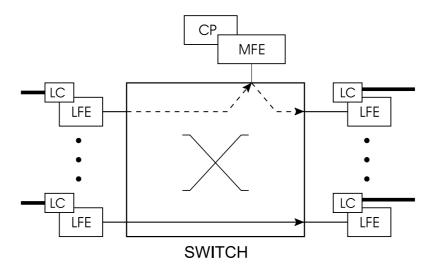

Two of the possible router architectures belonging to this space (albeit without considering the switch element), fully distributed and parallel, were examined and compared in [10]. In the fully distributed case (Fig. 2.3), each line card (LC) has a dedicated LFE attached. When a packet arrives at an LC, its LFE searches for

Figure 2.3: Distributed router architecture (LC: line card, LFE: local forwarding engine, MFE: master forwarding engine, CP: control point).

the appropriate route. If the route is found, the packet is immediately forwarded through the switch to the output LC. If an LFE is not able to determine the route (e.g. contains only a part of the routing table), or does not have enough processing power to handle all the arriving packets, it sends the packet header to the MFE, which contains a copy of the entire routing table and therefore is able to find the appropriate route. In general, as the MFE stores the entire routing table and should be able to assist all LCs, it is considerably more powerful than an LFE.

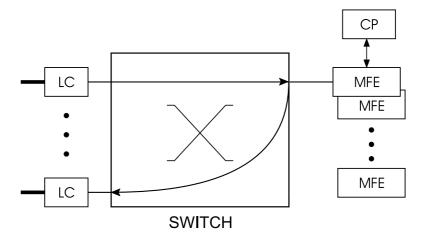

In the case of a parallel router architecture (Fig. 2.4), the router contains a pool of several high-performance MFEs that handle the router's entire workload. Any MFE can take on a new request as soon as it has processed the previous one. As long as the switch can handle the additional traffic, the total system processing power is considerably higher than in the case of a fully distributed system, but also the total system cost rises accordingly.

The content of the routing table is managed by the router control point (CP), which often resides in the same hardware unit as the MFE. The CP uploads the table to the FEs. As the CP is a processor dedicated to the control plane rather than to the data plane within router, it is not considered in the optimization, neither in [10],

Figure 2.4: Parallel router architecture (LC: line card, MFE: master forwarding engine, CP: control point).

nor in this work.

A simple framework for assessing the cost vs. performance ratio was applied in [10]. The cost and performance differences between a fully distributed and a parallel architecture, as well as the influence of various system parameters on the ratio, were studied. The optimizations were carried out by constraining the maximal packet-processing time and the maximal FE processing power while minimizing the total cost of the system.

The results of the optimization in [10] in the case of the distributed architecture indicate that as the cost ratio between MFE and LFE increases, it is more efficient to use the fully distributed architecture rather than a centralized one without LFEs. Similar behavior occurs when the fraction of packets an LFE unsuccessfully processes decreases. The parallel architecture is more expensive than the distributed one for the same workload, but it is scalable and thus able to handle a much higher workload.

Other designs [21], [51] seek to combine both approaches by containing remotely located (at a different switch port than the input line cards) network processors or forwarding engines, which serve a certain predefined set of inputs to carry out the packet processing tasks on packets arriving at a these inputs. Again, the traffic may not be evenly distributed over these sets, which leads to less efficient utilization.

Tantawy, Zitterbart and Koufopavlou [33] [61] have concentrated on exploring the possibilities of parallel implementations of the TCP/IP packet processing within routers. In these studies, functional decomposition of individual packet processing tasks has been determined and various possible forms of parallelism have been categorized: spatial parallelism, pipelining or concurrent operation.

In a study on future router architectures, Kumar, Lakhsman and Stilliadis [34] emphasize that due to the nature of networking transport protocols, it is often illegal, or at least extremely undesirable, to allow packet reordering within a packet flow. Although the widely used TCP protocol attempts to tackle this problem by correct reordering at the destination, reordering slows down data delivery, increases receiver buffer size and still may not prevent some undesirable retransmissions and subsequent network congestion. If packets from the same flow are to be processed by different processors, packet reordering can easily occur. Therefore, packets belonging to a particular flow should be processed by the same processor.

Dittman and Herkersdorf [16] present a hardware-based load balancer, designed for scaling the performance of network processors that handle the load at router interfaces. A single high-speed link can be balanced over multiple network processors of lower capacity. The load balancer uses an adaptive hash-table. Flows that exceed the capacity of a single processor are sprayed over multiple processors.

#### 2.4 Server farms

#### 2.4.1 Architectural demands

Connection speed, low latency, fault tolerance, and ease of management are the keywords for the contemporary web server architectures. As web sites handle everincreasing numbers of clients, the traditional solution, increasing the capacity of the servers, is becoming neither economically sound, nor scalable. Various techniques have been proposed and implemented in recent years in order to scale with the growth of the Internet. The solutions must continue to function appropriately even as they (or their context) evolve in size or volume. Flexible, easy-to-integrate products are required. Fault tolerance is a must, as the web sites must be able to operate not only under any traffic condition (including hostile traffic such as hacker attacks), but also in cases of unexpected internal problems (like software errors or hardware failures).

The typical contemporary solutions addressing the Web growth are server farm load balancing, Web caching and Content Delivery Networks (CDNs). Before reviewing the server farm load balancers in more detail, we provide a general overview of the other two solutions.

#### 2.4.2 Web caching and content delivery networks

#### Web caching

This technique employs local memories (caches) containing copies of the objects accessed most often (for example web pages). There are typically three ways to implement caching. With *Proxy Cache*, the internet browser is configured to first look for the resource directly in the cache. If the cache does not contain the object the web browser will contact the Web server. This approach is not generally used because it requires manual configuration. With *Transparent Caching*, the network automatically redirects the request to one or more caches through devices called cache re-directors. If a cache does not contain the required content, the request is redirected to the actual web server. Finally, with *Reverse Proxying*, the Web cache receives requests from the clients, proxies them to the Web server, and caches the response itself on its way back to the client. This means that when the request is repeated, the proxy server itself can provide static content from its cache.

#### Content delivery networks

Content Delivery Networks (CDNs) are private networks of geographically dispersed caching servers at the edge of the Internet. They bring content (like, for example, multimedia streaming) closer to the users and speed up its delivery. The CDNs

Figure 2.5: Server load balancing topology.

are an evolution of the caches. When the Web user clicks on a URL, the content-delivery network re-routes that user's request away from the site's original server to a cache server closer to the user. The three main techniques for the redirection are HTTP redirection, Internet Protocol (IP) redirection, and domain name system (DNS) redirection. In general, DNS redirection to the cache server is the most effective technique. The cache server determines what part of the content of the request exists in the cache, serves that content, and retrieves any non-cached content from the originating server. Any new content is also cached locally. Other than faster loading times, the process is generally transparent to the user, except that the URL served may be different from the one requested. CDN technologies are developed for example by Akamai [56] or Speedera [57].

## 2.4.3 Server farm load balancing

This is the most common technique of scaling a Web server capacity. As shown in Fig. 2.5 a pool of web servers, forming a server farm together, is connected to the Internet by a load balancer that acts as a front-end machine that intelligently directs

the clients (their TCP connections) to the servers according to the servers' capacities and status. This allows each server to operate more efficiently. The choice of the server falls into two basic categories: content unaware and content aware.

In the *content unaware* case there are no dedicated web servers for some specific protocols and thus all of them can process any kind of request. Every time the load balancer receives a request for a connection (SYN), it redirects the TCP connection to a server that will execute the TCP three-way handshake. The redirection is generally based on Layer 2, 3 or 4 information such as IP addresses or ports numbers.

In the *content aware* case, the load balancer is an end-point of the TCP connection, and can interpret the user's request through parsing the layer-7 information (i.e. the URL). The redirection happens after the TCP three-way handshake between the load balancer and the user. Each server may contain different contents or possess different levels of security. This solution is more flexible, but more demanding than the unaware case, considering that the load balancer must be able to parse layer-7 information spread over several packets.

It is typically required that the load-balancing solution is able to ensure *sticky* connections, that is, connections that are always redirected to the same server. Some applications require sticky connections, like, for example, filling of forms, shopping carts or bank transactions.

These particular connections are typically handled in three ways:

- The load balancer stores the pair [user ID, IP address] into a table. This solution does not work with the Network Address Translation (NAT), because for each new connection of the same user, there may be a new, dynamically assigned source IP address;

- The real server or the load balancer are able to distinguish a sticky-connection and send a cookie back to the user that is used next time to redirect the connection. This solution does not work with encrypted connections;

- The real server or the load balancer uses HTTP to redirect to the correct real server.

#### DNS-based server load balancing

A readily available software load balancer is the Berkeley Internet Name Daemon (BIND) [12], developed by the Internet Software Consortium (ISC). It resides in the primary web server and intercepts packets as they enter the web site. When a DNS request arrives, it uses the DNS Round Robin to select a particular IP address from a pool of addresses. The selection pointer selects the addresses in a round-robin fashion. This solution has numerous drawbacks:

- Even if the load balancer spreads the connections evenly, there is no relationship to the load of individual connections. Thus some servers might have to handle much more load than others.

- If the primary web server fails, the entire farm is disabled.

- No consideration about the type of content requested.

- Does not work well if session state must be maintained.

- Does not work well if the servers are of heterogenous capacity.

- With large server farms, DNS Round Robin is difficult to configure.

Shaikh, Tewari and Agrawal [54] conduct a study on the effectiveness of a DNS-based server selection. The authors identify as a significant drawback the fact that DNS-based schemes typically disable client-side caching of name resolution results, thus increasing the resolution overhead by up to two orders of magnitude.

#### Advanced load balancers

A large variety of more complex load balancers exist nowadays. We provide a brief overview of some of the commercially available products.

The Central Dispatch from Resonate [48] is a software-based server management solution. It employs port load balancing: after creating the additional server processes in the actual server cluster, Central Dispatch users simply specify the range of ports on the server to which incoming requests should be mapped. The incoming requests

are then forwarded to the most suitable server based on predefined scheduling policies. When port load balancing is configured, port selection at the server is performed, for example, in a round-robin manner; if one port does not respond, another port on the same machine is selected.

The Windows NT Load Balancer Service (WLBS) [41] from Microsoft is controlled by a distributed management software, which distributes the incoming load of IP requests across a cluster of multiple Windows nodes. The load-balancing scheme is based on the robust hash routing algorithm, described in Section 2.2.3, that incorporates the client IP address, its port number, or both, to determine which server responds. It is possible to specify a load percentage for each server. When changes occur, the load balancer starts a convergence process that automatically reconciles the changes in the cluster and transparently redistributes the incoming load.

IBM Network Dispatcher [24] is a software tool that routes TCP connections to multiple servers that share their workload, based on a monitored load metric. The algorithm contains an adaptive control loop, but it is required to maintain state information where each TCP connection has been mapped.

A dedicated load balancer is a configurable stand-alone appliance, which offers some router-like functionalities or is tightly integrated with an existing router system. Examples of such load balancer appliances are the Equalizer from Coyote Point Systems [60], BIG-IP LoadBalancer from F5 Networks and Cisco's Local Director.

The F5 Networks BIG-IP LoadBalancer 520 [22], is situated between the network and the server farm and automatically routes incoming queries to the most available server. It also provides support for heterogeneous server farms. The load balancer intercepts all data packets addressed to the site's IP address and distributes them to the appropriate server. The supported load-balancing algorithms are:

- Fastest—user connections are passed to the available server that responds the fastest;

- Round Robin—traffic is sent to the next available server in a predetermined sequence;

- Least Connections—the user is connected to the server with the least number of current connections;

- Ratio—assigns fractions to the server that best fits the request, according to a system that assigns weights for various factors, such as server capacity.

Local Director from Cisco Systems [59] is a connection manager appliance, tightly integrated with the Cisco routing and switching ("forwarding agent") products. When a forwarding agent receives a connection request, the request is forwarded to the manager (Local Director). The manager makes the load balancing decision and instructs the forwarding agent with the optimal destination. After destination selection, session data is forwarded directly to the destination without further manager participation. The load-balancing decisions can be based on various algorithms: application availability, server capacity, round robin, least connections, or Dynamic Feedback Protocol (DFP).

Another family of server load-balancing devices falls into the category of content smart switches and routers. These are standard switches or routers with some extra features enabled, including server load balancing. Examples are the suite of Alteon switches from Nortel Networks [42] or the Content Smart Switches and Routers from Cisco Systems [58]. Typically, they support load balancing over various entities, like servers, firewalls or multi-homed links. The server selection is based on server load and application response time, or the least connections or the round-robin algorithms.

# 2.5 Conclusions

In this chapter, we have reviewed the previous research and developments in the areas relevant to this thesis—in the load-sharing field and in the field of router architecture and of web server farm load balancing, as examples of multiprocessor systems within networks. In the load-sharing discussion, we have covered in depth the highest random weight (HRW) mapping algorithm, as it is a foundation for our adaptive load-sharing method presented in Chapter 4.

25

Some conclusions with respect to the topic of this thesis can be reached based on the works reviewed. Firstly, it is a clear trend, primarily for the reasons of scalability and fault tolerance, to equip network nodes with multiple processors. However, there are open questions as to what kind of architecture exploits such a multiprocessor system best.

Other findings show that it is non-trivial to design a hash-based, and thus fast, load-sharing method that would yield reasonable load balancing performance and yet not be computationally intensive. In the field of web servers, clearly the load-sharing techniques rely primarily on maintaining some form of state information about the connection mapping, regardless of the discipline used for the mapping establishment. This results in good load balancing performance, as the discipline can be periodically adapted, yet at a high cost of maintaining large amount of state information. It is the goal of this thesis to develop a method that preserves the advantages and overcomes the drawbacks of the techniques discussed.

# Chapter 3

# Optimizing router architecture

#### 3.1 Introduction

In this preparatory chapter, a model of an essentially distributed router is optimized from various perspectives, to obtain a more detailed understanding of the issues in the router architecture design space.

In the first part, we optimize the model from the perspective of the total cost of the entire system. The objective of the method is to serve as a general means for optimizing a router architecture with a given set of input constraints. The constraints are maximum line interface bandwidth, number of router line cards and maximum packet processing delay within the system.

To carry out the optimization on a realistic system model, the system model contains further constraints, which can be interpreted as technological limits, such as the maximum processing power of the forwarding engines (FEs) or the maximum switch port speed. The full set of constraints defines a space of feasible solutions over which the optimization is carried out. The optimization cost function is an aggregate of estimated market-based costs of the individual elements. The cost is expressed as a function of the technological parameters of each element.

The optimization output consists of variables describing the optimal architecture—the processing power of the local forwarding engines (LFEs) and of the main forwarding engines (MFEs), number of MFEs, switch port speed, and the distribution of

packet processing among LFEs and MFEs. Based on the results of the optimization, we reach some general conclusions about the most economical router architecture for a given set of constraints.

In the final section of this chapter, optimization in terms of maximizing the processing capacity while remaining within certain performance constraints is discussed. We define the term of acceptable load sharing and show how abiding by such principle routers may increase their processing capacity. Finally, some conclusions with respect to the applicability of load sharing within a router system are presented.

The chapter is organized as follows: Section 3.2 presents the router architecture model, and, in Section 3.3, the cost optimization problem is described in detail. In Section 3.4, results of the most interesting cost optimizations are discussed; Section 3.5 explores router optimization from the load-sharing point-of-view, and, finally, Section 3.6 contains some concluding remarks.

#### 3.2 General distributed router architecture

#### 3.2.1 Router model

A general model of an essentially distributed router architecture is optimized. Our model (see Fig. 3.1) contains a fixed number of LFEs (one per router input) of variable processing power (including null processing power, meaning that the LFEs are absent), a variable number of MFEs with variable processing power, and a switch of variable port speed. This work extends the model presented in [10] by a switch element and an LFE queuing and queue overload model. Furthermore, we present a hybrid, more general router architecture model, encompassing a large space of possible, in essence distributed, router architectures, including the centralized, fully distributed and parallel cases presented in [10].

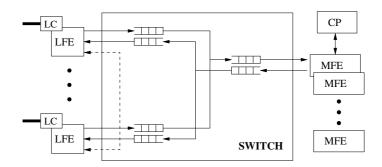

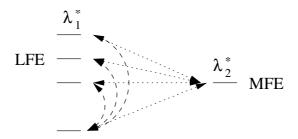

We consider a router having k LCs, with an LFE attached at every LC (see Fig. 3.1). A switch element interconnects all the LFEs and the pool of m parallel MFEs. All the possible sequences the processing of a packet may take—at an LFE, at an MFE, or at both processing units—are accounted for. A fraction  $r \in [0, 1]$  of the incoming

Figure 3.1: LFEs, switch and MFEs within the general distributed router architecture model.

traffic is processed locally at the LFEs; the fraction 1-r is diverted directly to the MFEs without being enqueued at the LFEs (see Fig. 3.2). Thus, if r=0, LFEs are not used at all and the router consists only of a pool of parallel MFEs and a switch. When r>1 the LFE may not be able to handle all the traffic destined for it locally, for various reasons, such as for being overloaded (see Section 3.2.2). Such traffic is sent to the MFEs as well, but only after passing through the LFE. Thus, if r=1, all the traffic is enqueued at the LFEs, yet a fraction that the LFEs will not be able to process will still subsequently be sent to the MFEs.

Arriving traffic is modelled as a Poisson process. The mean arrival rate at each input LC is  $\lambda_i$  packets per second (pps). The total router load is thus  $\lambda = k \lambda_i$ . The analysis carried out is a worst-case scenario, where we consider all the links to be fully loaded. In reality, workloads on different LCs are generally not uniform and may vary significantly over time. This implies that LFEs with a higher workload would forward more packets to the MFEs for processing than LFEs with a smaller workload, and one can imagine a feasible problem solution where for some periods of time, individual LFEs would be overloaded. We have experimented with nonuniform workload distributions on different LCs and the LFE overload, but the optimization results did not differ significantly from the uniform model. Nonuniform LC workloads are therefore not included in the model. The LFE model, as presented in Section 3.2.2, is applicable for the overload modelling, however the optimization never finds an overloaded LFE solution to be the optimal one.

Figure 3.2: Model of the general distributed router architecture with multiple LFEs and MFEs.

With respect to the optimization, parameters k and  $\lambda_i$  are a part of the optimization input, whereas values of r and m are a part of the output.

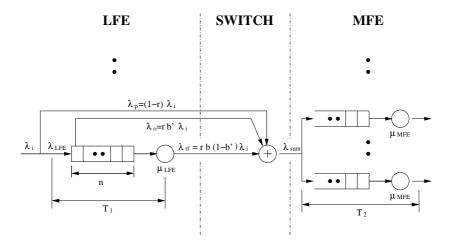

#### 3.2.2 LFE and MFE model

The processing power of an MFE is  $\mu_{\text{MFE}}$  pps, and that of an LFE is  $\mu_{\text{LFE}}$  pps. We use  $\mu_{\text{max}}$  as a bound on the maximum number of packets an FE can handle per second.

The possible scenarios of packet-processing distribution among LFEs and MFEs are depicted in Fig. 3.2. The fraction of traffic arriving at an LFE is  $\lambda_{\text{LFE}} = r\lambda_i$ . A fraction  $\lambda_p = (1 - r)\lambda_i$  is pre-scheduled directly for processing at the MFEs.

Regarding the packets sent for resolution through the switch to the MFEs, we assume that it is only the packet control information, i.e. the packet header, that travels through the switch (as in [27]). The packet payload is assumed to be buffered until a resolution of the packet processing task arrives from the MFE pool, again, travelling through the switch. Thus, in terms of number of packets, the amount travelling through the switch is the same, yet in terms of bits, only a fraction of the packet size makes the trip to the MFEs. In this work, the processing overhead and the memory size requirements for the packet header detachment, the payload buffering, and the packet reassembly are not considered.

Furthermore, we assume that a single LFE workload,  $\lambda_{\rm LFE}$ , can be greater than its processing power  $\mu_{\rm LFE}$ . The LFE queue size n is introduced as a parameter to model the LFE overload. When the LFE queue is full, a packet cannot be processed by the LFE and is forwarded to the MFE pool. Note that the overload traffic does not have a Poisson distribution because the probability that an LFE queue is full depends on the LFE load, but, for the sake of simplicity, we approximate it with a Poisson distribution as follows: the LFE queue is an M/M/1/n queue. Thus, the probability of a packet arriving at a full LFE queue is (see [31]):

$$b'(\lambda_{\rm LFE}) = P_n = \frac{1-\rho}{1-\rho^{n+1}}\rho^n, \qquad \rho = \lambda_{\rm LFE}/\mu_{\rm LFE}. \tag{3.1}$$

Thus, we assume the fraction of traffic  $\lambda_o = b' \lambda_{\text{LFE}} = r b' \lambda_i$  to be sent to the MFE pool due to LFE overload.

Furthermore, as in [10], even if a packet is being processed by an LFE, with a fixed probability b the LFE will not be able to find the packet next hop, and the packet is likewise forwarded to the MFE pool. Such packets account for route table misses, for example when the LFE acts only as a cache, storing a fraction of the routing table. We denote such a fraction of traffic as  $\lambda_{rf} = r b (1 - b') \lambda_i$ .

Finally, the fraction of traffic that actually does get resolved at the LFE and is forwarded directly to the outgoing switch port is  $\lambda_q = \lambda_i - (\lambda_p + \lambda_o + \lambda_{rf}) = r(1-b)(1-b')\lambda_i$ .

In Fig. 3.2 we observe that there are three possibilities for a packet to be queued. Either a packet is queued at an LFE and waits for time  $T_1$ , it is forwarded to the MFE and waits for  $T_2$ , or it is queued at both the LFE and the MFE owing to the LFE resolution failure.

Note that given the various paths the packet processing in the router can take, packets belonging to a particular flow may be reordered, which is highly undesirable [34]. In the interest of simplicity, we do not consider the additional processing overhead required to prevent reordering in this section.

#### LFE processing time

The average number of packets in a processor, the average workload arriving at the LFE queue, and the average LFE response time are

$$\overline{N}(\lambda_{\text{LFE}}) = \rho \times \frac{n\rho^{n+1} - (n+1)\rho^n + 1}{\rho^{n+2} - \rho^{n+1} - \rho + 1}$$

(3.2)

$$\lambda_a = \lambda_{\text{LFE}} * (1 - P_n) = \lambda_{\text{LFE}} * \frac{1 - \rho^n}{1 - \rho^{n+1}}$$

(3.3)

$$\overline{W}(\lambda_{\text{LFE}}) = \frac{\overline{N}(\lambda_{\text{LFE}})}{\lambda_a} = \frac{1}{\mu} \times \frac{1 - \rho^{n+1}}{1 - \rho^n} \times \frac{n\rho^{n+1} - (n+1)\rho^n + 1}{\rho^{n+2} - \rho^{n+1} - \rho + 1} . \tag{3.4}$$

Observing the behavior of a saturated LFE, we see from Eq. (3.4) that for higher n, the waiting time is longer. Therefore, a router with long LFE queues would be penalized with respect to the packet delay time compared to an equivalent router with smaller queues. On the other hand, a router with extremely small LFE queues (e.g. n=1) would have frequent queue overflows even on the nonsaturated LFEs, which would again penalize its performance. The queue length n thus has to be chosen carefully in order to achieve optimal performance. Ideally, n should be included in the optimization of the system parameters. Experimentally, though, we have found that changes in n do not have a very significant influence on the optimization in comparison to other factors, especially as the optimization never finds an overloaded LFE to be the optimal solution. Thus, to simplify the analysis, we use fixed n values. Note however that in reality, a queue of larger size would be necessary to handle bursty traffic, for which we do not account for in our model. Time  $T_1$  is simply the average response time  $\overline{W}(\lambda_{\text{LFE}})$ .

#### MFE pool processing time

The MFE pool queue is, as in [10], a simple infinite M/M/m queue, with the input workload representing the sum of non-processed packets from the LFEs, together with the pre-scheduled packets. As the part of workload sent for resolution to the MFE represents a sum of Poisson processes, the sum is a Poisson process as well. This

workload and the corresponding M/M/m queue waiting time are on average [31]:

$$\lambda_{\text{sum}} = k \left( \lambda_p + \lambda_o + \lambda_{rf} \right) \tag{3.5}$$

$$T_2 = \frac{1}{\mu_{\text{MFE}}} + \frac{\rho P_Q}{\lambda_{\text{sum}} (1 - \rho)}, \tag{3.6}$$

where

$$\rho = \frac{\lambda_{\text{sum}}}{m\mu_{\text{MFE}}} , \quad P_0 = \frac{1}{\sum_{j=0}^{m-1} \frac{(m\rho)^j}{j!} + \frac{(m\rho)^m}{m! (1-\rho)}} , \quad P_Q = \frac{P_0(m\rho)^m}{m! (1-\rho)} .$$

(3.7)

Considering the MFE pool an M/M/m queue may not necessarily be realistic, as we again do not account for the overhead to prevent packet reordering. Either a load balancing device in front of the pool, or packet re-sequencer at the exit of the pool would have to be in charge of maintaining the packet order. However, such mechanism may prevent the pool from acting as an M/M/m queue. For simplicity, we do not consider the devices and overhead required to ensure the packet sequence.

#### 3.2.3 Switch model

#### General input/output switch

The switch is characterized by two parameters—the switch port speed s and the number of input ports k. As k is an input to the optimization, s is the only parameter optimized by the method. The switch port speed is expressed in terms of transmission time per the fixed size switch cell, that is, in seconds per cell. The parameter s is constrained from below by the technological limit of  $s_{\min}$ ,  $s > s_{\min}$ , which means that a fixed-size switch cell cannot be transmitted at a switch port in less than  $s_{\min}$  seconds. To avoid confusion with the intensity indicators in packets per second, the intensity indicators in switch cells per second are denoted with \*, e.g.  $\lambda^*$  instead of  $\lambda$ .

We include the switch in our model by introducing the switch delay. In order to model the switch delay time, we consider a formula for an input/output-queued switch derived in [26] and [25]. In the interest of simplicity, we assume that the switch has infinitely large output queues, and that the number of inputs is large (i.e. greater than 16, [26]). In the case of a lower number of inputs, the performance of the switch is actually better than the formula depicts (as described in [30]), owing to lower contention, but in such a case the formula can still be used as a rough upper bound. Note that the head-of-line congestion at the input port considered in [26] and [25] has been eliminated in the latest switch architectures; however, in this work, we conform to this model in order to obtain a simple analytical formula for computing the switch delay.