UNIVERSIDADE DE LISBOA FACULDADE DE CIÊNCIAS DEPARTAMENTO DE INFORMÁTICA

## NETWORK CODING DATA PLANES WITH PROGRAMMABLE SWITCHES

**Diogo Figueiredo Pinto**

MESTRADO EM ENGENHARIA INFORMÁTICA

Especialização em Arquitectura, Sistemas e Redes de Computadores

Dissertação orientada por: Prof. Dr. Fernando Manuel Valente Ramos e co-orientada pela Prof.<sup>a</sup> Dra. Muriel Médard

2017

## Acknowledgments

I would like to begin with a special thanks to my advisors Professor Fernando Manuel Valente Ramos and Professor Muriel Médard, for all the patience, support and confidence throughout the last year.

A flimsy one to all my colleagues, for choosing not to use the 1.3.19 office during all the year, which allowed me to have all the peace, silence and concentration, in the world.

I am also thankful to the faculty's facilities, for providing me with microwaves to heat my delicious homemade meals.

Finally, a special one to Marlboro, for the marvelous cigarettes that helped me keep my mental sanity.

**FUNDING** This work was partially supported by the European Commission through project FP7 SEGRID (607109) and project H2020 SUPERCLOUD (643964), and by national funds of Fundação para a Ciência e a Tecnologia (FCT) through project UID/-CEC/00408/2013 (LaSIGE).

## Resumo

Atualmente, as redes de computadores seguem um paradigma tradicional de *store-and-forward*, ou seja, os dispositivos de rede fazem armazenamento, encaminhamento e/ou replicação de pacotes recebidos, sem os modificar. No virar do milénio, surgiu um artigo seminal [24], no qual foi demonstrado teoricamente que a *combinação* da informação proveniente de diversos pacotes, permite aumentar a capacidade de uma rede relativamente à capacidade máxima, alcançada por simples encaminhamento. Este resultado representou o nascimento de uma área promissora de investigação, conhecida como Codificação na Rede (*Network Coding*). A ideia é permitir que os nós intermédios da rede, possam aplicar uma função de codificação sobre o conteúdo dos pacotes antes do seu encaminhamento, proporcionando assim um novo paradigma de *store-code-forward*.

A família de técnicas tradicionais pode ser divida em duas categorias, com propósitos distintos. Codificação na Origem (*Source Coding*) com o objetivo de comprimir a informação enviada, e Codificação no Canal (*Channel Coding*) para compensar perdas e alteração de informação em canais ruidosos. Com codificação na rede, surge oportunidade para a definição de técnicas mais elaboradas e que visam outros propósitos. Deste modo, as técnicas de codificação tradicionais podem ser extendidas para além da codificação de pacotes em nós de origem, e da descodificação em nós de destino.

De um ponto de vista geral, a codificação na rede tem potencial para melhorar a taxa de transferência de informação na rede; aumentar a resiliência contra perda de pacotes, interrupção de canais e nós da rede; e aumentar a segurança contra ataques maliciosos que visam a captura, interpretação e modificação de pacotes.

Como técnica, a codificação na rede pode ser aplicada de dois modos distintos. Por um lado, sobre pacotes provenientes de um único fluxo de comunicação (*intraflow network coding*) e por outro, sobre múltiplos fluxos sem qualquer relação entre si (*interflow network coding*).

A título de exemplo, se considerarmos dois fluxos que chegam a um *switch* por dois canais distintos, mas que contestam o mesmo canal de saída, temos um gargalo na rede. Usando codificação na rede, o *switch* pode aplicar, bit a bit, o Ou-Exclusivo (XOR) sobre dois pacotes (um de cada fluxo) e encaminhar o resultado. A taxa de transferência é

melhorada, pois o *switch* necessita apenas de encaminhar um pacote codificado em vez de dois originais. É de salientar que, de forma a descodificar o pacote, o nó de destino tem de ter um dos pacotes originais usados na codificação.

Portanto, as vantagens da codificação na rede estão dependentes da topologia da rede, da própria função de codificação utilizada, e do modo como é aplicada.

Numa rede, um nó intermédio terá à partida acesso a vários pacotes. De forma a tirar máximo partido da técnica de codificação na rede, as funções de codificação utilizadas acabam por consistir num código linear (*Linear Network Coding*). A ideia é considerar todos os pacotes de uma mensagem a enviar (por exemplo, um ficheiro de texto, um vídeo, ou até um simples pedido HTTP) como um vetor de elementos de um dado campo finito. O tamanho de cada elemento, é dado pelo número de bits necessário para representar o maior valor desse campo. Se por exemplo o campo finito for 256, cada elemento terá 8 bits. A um vetor de elementos, damos o nome de símbolo.

Associado a cada símbolo transmitido na rede, existe um vetor de coeficientes, necessário para codificação e descodificação. O tamanho do vetor, é ditado pelo número de símbolos originais. Se a mensagem é divida em 5 símbolos, então o vetor tem tamanho 5.

Para codificar e criar um novo símbolo, o nó da rede começa por selecionar um novo vetor de coeficientes local. A função de codificação consiste numa combinação linear sobre um dado número de símbolos, utilizando o novo vetor local. O vetor do novo símbolo codificado é obtido da mesma forma. Sobre os vetores dos símbolos utilizados, é feita uma combinação linear utilizando o vetor local.

Para descodificar os símbolos originais, são necessários um número igual de símbolos codificados, linearmente independentes. De forma a que os símbolos codificados e recodificados na rede, sejam linearmente independentes, podem ser utilizados algoritmos de tempo polinomial [59], para estabelecer os vetores locais utilizados por cada nó intermédio da rede. De forma a simplificar o problema, os vetores locais podem ser aleatórios (*Random Linear Network Coding*). Se o campo finito for suficientemente grande, a probabilidade de obter símbolos codificados linearmente independentes chega perto dos 100%.

De forma a ter vetores mais reduzidos, tornando as operações mais simples, e permitindo uma descodificação gradual, os símbolos originais da mensagem podem ser organizados em gerações. Por cada geração, são gerados e injetados pela rede, símbolos codificados. Quando uma geração é descodificada, procede-se para a geração seguinte.

Repare-se que a função de codificação referida anteriormente, com base em XOR, é o caso base e mais simples de um código linear. Neste caso, o campo finito é de tamanho 2.

Apesar de ser um conceito relativamente simples, implementar e usar técnicas de codificação no plano de dados dos próprios dispositivos de rede é uma tarefa bastante complicada. Até mesmo quase impossível na maioria dos casos, visto que a *payload* dos pacotes é sujeita a alterações. O seu funcionamento baseia-se em protocolos fixos, que correm no próprio hardware de forma a maximizar o desempenho, o que torna difícil a tarefa de configurar e gerir uma rede para além das simples operações de encaminhamento de pacotes. Por este motivo, as implementações práticas de codificação na rede que têm vindo a surgir nos últimos anos, operam em redes *overlay*. Uma rede *overlay* reside logicamente na camada de aplicação, implicando que os dispositivos de rede propriamente ditos não são alterados.

O interesse crescente em operações mais complexas e exigentes na rede, mas condicionado pelo funcionamento rígido e fechado dos routers e switches tradicionais, motivou uma mudança de paradigma: de redes configuráveis para redes programáveis. A primeira instância de uma rede programável é conhecida como Rede Definida por Software (SDN). Numa rede SDN, o plano de controlo é separado do plano de dados, e reside num dispositivo à parte - um controlador logicamente centralizado. Utilizando a informação de pacotes provenientes do plano de dados dos *switches*, o controlador pode definir políticas de configuração mais flexíveis e instalar regras nas tabelas match-action dos mesmos. A comunicação entre os switches e o controlador está estandardizada, sendo utilizado um protocolo conhecido como OpenFlow. A limitação de switches e controladores Open-Flow está no processamento de pacotes, que continua a ser fixo. De facto, o OpenFlow atua sobre um conjunto fixo de protocolos. Além disso, a sequência de tabelas e ações de um switch Openflow também é fixa. Portanto, o OpenFlow não permite realmente definir nova funcionalidade no plano de dados de um switch. Apenas fornece um meio para o controlador tomar decisões e instalar regras nas tabelas *match-action*, dos mesmos. No âmbito de codificação na rede, este fator impossibilita a alteração da payload dos pacotes, e consequentemente a sua combinação.

No entanto, têm vindo a surgir recentemente *switches* programáveis, alguns até já em produção (por exemplo, Tofino da Barefoot Networks). Estes dispositivos permitem a programação e reprogramação do plano de dados, o que possibilita uma definição precisa e customizada do modo de processamento de pacotes. Com esta liberdade, a codificação na rede torna-se possível, no plano de dados.

Porém, a sua programação é baseada em interfaces de baixo nível, tornando-se um processo demorado e doloroso. Esta dificuldade, acrescida também às limitações descritas do *OpenFlow*, motivou a criação da linguagem de alto nível, P4.

A linguagem P4 permite definir cabeçalhos, *parsers* e a sequência de tabelas de *matchaction*, para qualquer dispositivo de rede compatível. As ações podem ser definidas utilizando um conjunto de primitivas básicas oferecidas pela linguagem. A linguagem P4 oferece três vantagens. Primeiro, não está dependente de protocolos e formatos de pacotes específicos, uma vez que a sua definição pode ser feita pelo programador. Segundo, per-

mite a reconfiguração do *switch* a qualquer momento. Terceiro, não depende do hardware subjacente, podendo ser escrita, da mesma forma, para qualquer dispositivo que tenha o compilador adequado.

O objetivo desta dissertação consiste no desenho, implementação e avaliação do primeiro *switch* capaz de realizar codificação no plano de dados, recorrendo à linguagem P4. Mais concretamente, a nossa solução consiste em dois *switches*: um que executa XOR (P4-XOR Switch), e outro que executa uma variante de *Random Linear Network Coding* (P4-RLNC Switch). Durante a implementação enfrentámos vários desafios, devido às peculiaridades da linguagem. Entre os principais fatores que dificultaram a implementação, está o facto de a linguagem ser declarativa, não permitindo a criação de estruturas de dados auxiliares em tempo de execução; e a impossibilidade de criar ciclos, essencial para repetir o mesmo processo de codificação sobre os vários elementos dos símbolos, no caso do P4-RLNC Switch.

Sendo um trabalho inovador, a avaliação focou-se essencialmente na funcionalidade dos dois *switches* concretizados. Adicionalmente, a performance do P4-XOR Switch também foi avaliada.

**Palavras-chave:** Redes definidas por Software, OpenFlow, Codificação na Rede, Comutadores Programáveis, P4

## Abstract

Network Coding (NC) is a technique that can be used to improve a network's throughput. In addition, it has significant potential to improve the security, manageability, resilience (to packet losses, link failures and node departures) and the support of quality of service, in both wired and wireless network environments. The idea is to allow intermediate nodes of the network (i.e. switches and/or routers) to mix the contents of incoming data packets before forwarding them. Something that, traditionally carried out at source nodes, is therefore extended to the network, creating an array of new options.

The difficulty of deploying NC on traditional switches lies in the impossibility to change or extend their operation with the requirements of this new paradigm. The devices are closed, the software and underlying hardware are vendor specific, and follow a fixed set of protocols and processing pipeline. This rigidity precludes NC in today's switches and routers.

Fortunately, programmable switches are beginning to emerge, with some already achieving production-levels and reaching the market (e.g., Barefoot Tofino). A new high-level language to program these switches has recently been proposed: P4. The P4 language allows the precise definition of how packets are processed in these programmable switches. Namely, it enables the definition of headers, parsers, match-action tables, and the processing pipeline itself. Therefore, by taking advantage of these constructs, P4 enables the deployment of NC, on the switch's data plane, for the first time.

In this dissertation, we design and implement two NC switches using the P4 language. Both switches employ Linear Network Coding (LNC). The main difference is that the first (P4-XOR Switch), simply performs the XOR of packets (i.e., a linear code with field size 2). The second (P4-RLNC Switch) is more generic, allowing larger field sizes. For this purpose it performs Random Linear Network Coding (RLNC), which is a random variant of LNC.

The evaluation was performed on Mininet (a network emulator) and focused on the functionality of both switches. Additionally, the performance of the P4-XOR Switch was tested as well. The main conclusion is that our implementations correctly perform the required operations allowing, for the first time, NC to be performed in real data planes. **Keywords:** Software-Defined Networking, OpenFlow, Network Coding, Programmable Switches, P4

# Contents

| List of Figures |         |                   |                                              |    |

|-----------------|---------|-------------------|----------------------------------------------|----|

| Li              | st of [ | <b>Fables</b>     |                                              | XV |

| 1               | Intr    | oductio           | n                                            | 1  |

|                 | 1.1     | Motiva            | ation                                        | 2  |

|                 | 1.2     | Goals             |                                              | 3  |

|                 | 1.3     | Contri            | butions                                      | 3  |

|                 | 1.4     | Struct            | ure of the document                          | 4  |

| 2               | Rela    | nted Wo           | ork                                          | 5  |

|                 | 2.1     | Netwo             | ork Coding - Overview                        | 5  |

|                 |         | 2.1.1             | Max-Flow Min-Cut Theorem                     | 6  |

|                 |         | 2.1.2             | Exclusive-OR Network Coding (XOR)            | 6  |

|                 |         | 2.1.3             | Linear Network Coding (LNC)                  | 7  |

|                 |         | 2.1.4             | Random Linear Network Coding (RLNC)          | 8  |

|                 |         | 2.1.5             | Other RLNC Schemes and Variants              | 10 |

|                 |         | 2.1.6             | Advantages and Use Cases                     | 11 |

|                 |         | 2.1.7             | Network Coding Applications                  | 13 |

|                 | 2.2     | and P4 - Overview | 16                                           |    |

|                 |         | 2.2.1             | Control Plane Programmability and SDN        | 16 |

|                 |         | 2.2.2             | OpenFlow, Switch Chips and Motivation for P4 | 18 |

|                 |         | 2.2.3             | Data Plane Programmability and P4            | 20 |

|                 |         | 2.2.4             | P4 Applications                              | 32 |

|   | 2.3  | Summ    | ary                    | . 33 |

|---|------|---------|------------------------|------|

| 3 | Desi | gn      |                        | 35   |

|   | 3.1  | Archite | ecture                 | . 36 |

|   | 3.2  | P4-XC   | DR Switch              | . 36 |

|   |      | 3.2.1   | Protocol Header Format | . 37 |

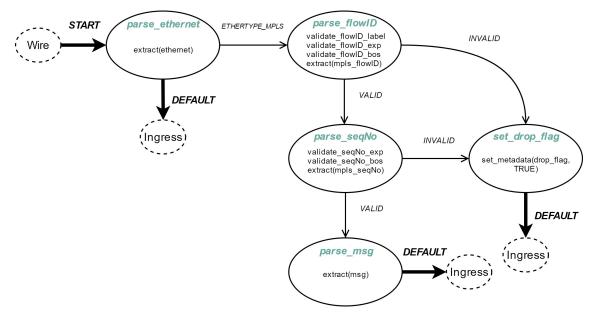

|   |      | 3.2.2   | Parse Graph            | . 38 |

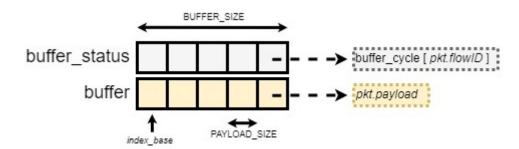

|   |      | 3.2.3   | Buffering Module       | . 39 |

|   |      | 3.2.4   | Coding Module          | . 40 |

|   |      | 3.2.5   | Forwarding Module      | . 40 |

|   |      | 3.2.6   | Operation              | . 41 |

|   | 3.3  | P4-RL   | NC Switch              | . 43 |

|   |      | 3.3.1   | Protocol Header Format | . 44 |

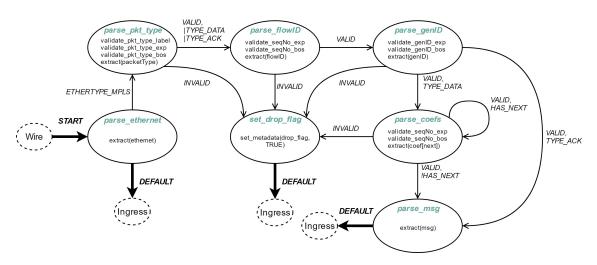

|   |      | 3.3.2   | Parse Graph            | . 45 |

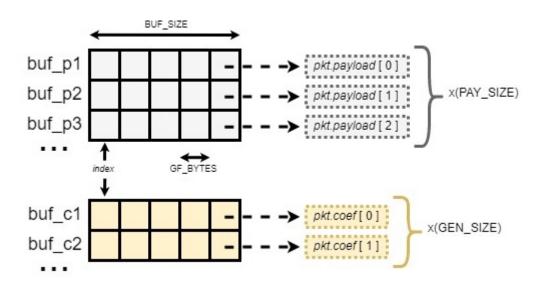

|   |      | 3.3.3   | Buffering Module       | . 46 |

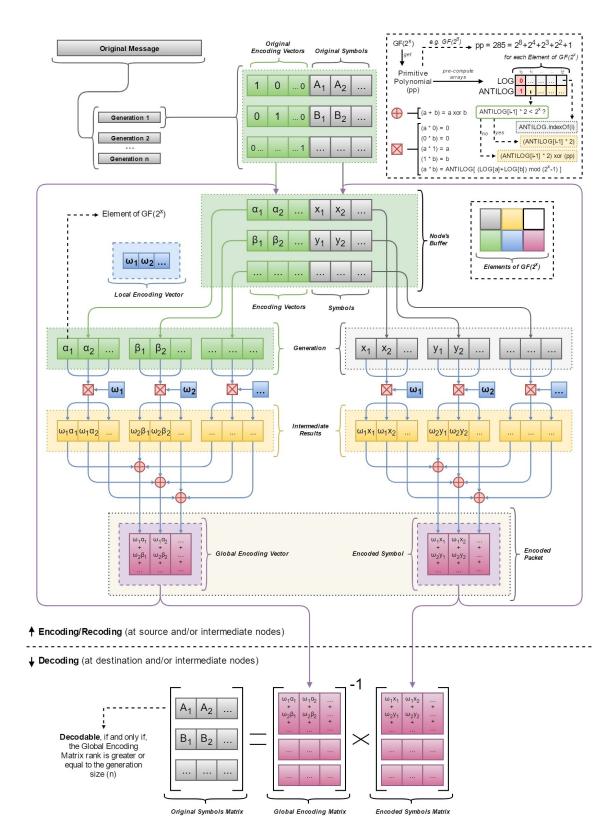

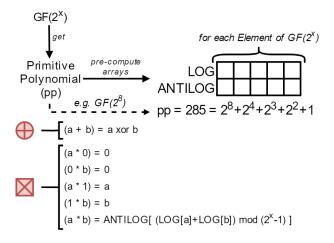

|   |      | 3.3.4   | Coding Module          | . 47 |

|   |      | 3.3.5   | Forwarding Module      | . 52 |

|   |      | 3.3.6   | Operation              | . 52 |

|   | 3.4  | Summ    | ary                    | . 55 |

|   |      |         |                        |      |

| 4 | Imp  | lementa | ation                  | 57   |

|   | 4.1  | Header  | r Definitions          | . 58 |

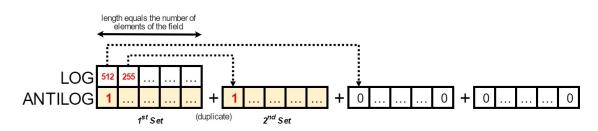

|   | 4.2  | Parser  | State Machines         | . 59 |

|   | 4.3  | P4-XC   | OR Switch              | . 61 |

|   |      | 4.3.1   | Buffering Module       | . 62 |

|   |      | 4.3.2   | Coding Module          | . 63 |

|   |      | 4.3.3   | Forwarding Module      | . 64 |

|   | 4.4  | P4-RL   | NC Switch              | . 65 |

|   |      | 4.4.1   | Buffering Module       | . 66 |

|   |      | 4.4.2   | Coding Module          | . 67 |

|    |             | 4.4.3    | Forwarding Module          | 73 |  |

|----|-------------|----------|----------------------------|----|--|

|    | 4.5         | Summ     | ary                        | 73 |  |

| 5  | Eval        | luation  |                            | 75 |  |

|    | 5.1         | Experi   | imental Setup              | 76 |  |

|    | 5.2         | Function | onality Tests              | 78 |  |

|    |             | 5.2.1    | P4-XOR Switch              | 78 |  |

|    |             | 5.2.2    | P4-RLNC Switch             | 82 |  |

|    | 5.3         | Perform  | mance of the P4-XOR Switch | 87 |  |

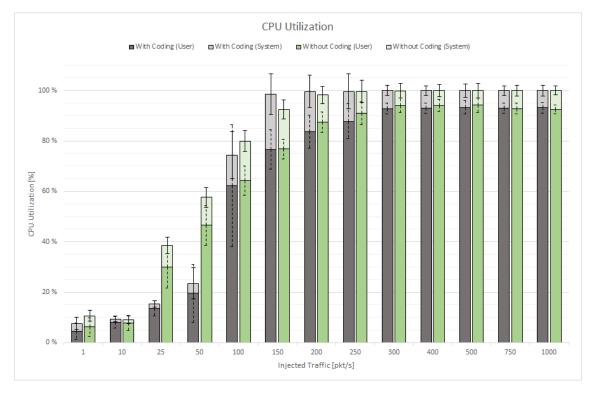

|    |             | 5.3.1    | CPU Utilization            | 88 |  |

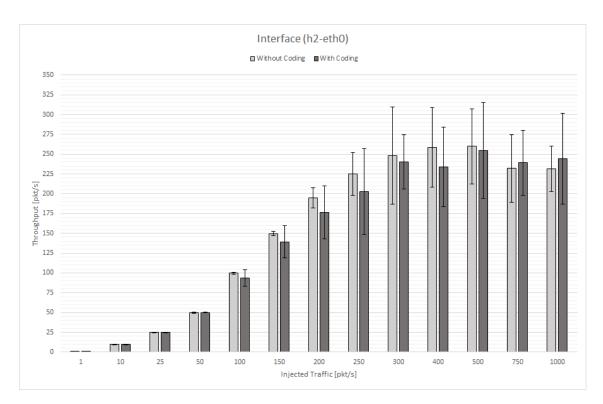

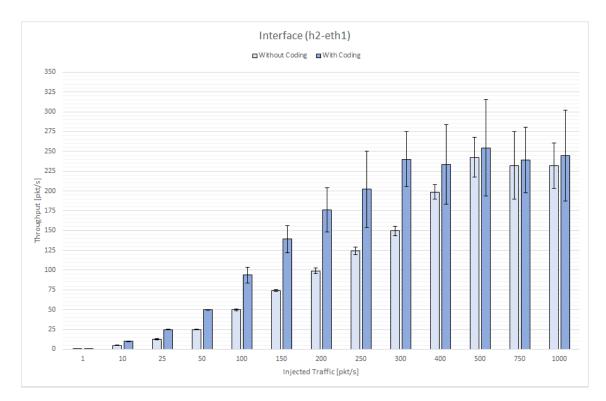

|    |             | 5.3.2    | Throughput                 | 89 |  |

|    | 5.4         | Summ     | ary                        | 93 |  |

| 6  | Con         | clusion  | & Future Work              | 95 |  |

| Gl | Glossary 97 |          |                            |    |  |

| Bi | bliogı      | raphy    |                            | 99 |  |

# **List of Figures**

| 2.1  | Traditional Butterfly Network                                        | 7  |

|------|----------------------------------------------------------------------|----|

| 2.2  | Random Linear Network Coding - Encoding.                             | 9  |

| 2.3  | Random Linear Network Coding - Decoding.                             | 9  |

| 2.4  | Example of SDN architecture.                                         | 18 |

| 2.5  | Abstract Forwarding Model                                            | 22 |

| 3.1  | Representation of the overlying architecture of the current solution | 36 |

| 3.2  | P4-XOR Switch's Protocol Header                                      | 37 |

| 3.3  | High-level representation of the P4-XOR Switch's parser              | 38 |

| 3.4  | P4-XOR Switch's Buffering Model.                                     | 39 |

| 3.5  | P4-RLNC Switch's Protocol Header.                                    | 44 |

| 3.6  | High-level representation of the P4-RLNC Switch's parser             | 45 |

| 3.7  | P4-RLNC Switch's Buffering Model.                                    | 46 |

| 3.8  | P4-RLNC Switch's Coding Model - Complete Overview                    | 48 |

| 3.9  | Arithmetic addition and multiplication over a galois field           | 50 |

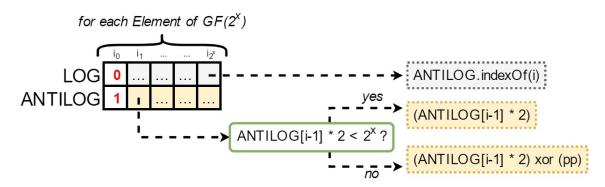

| 3.10 | LOG and ANTILOG table pre-computation.                               | 50 |

| 3.11 | LOG and ANTILOG table pre-computation - An improvement               | 51 |

| 3.12 | Modern variation of Fisher-Yates shuffle algorithm - An example      | 51 |

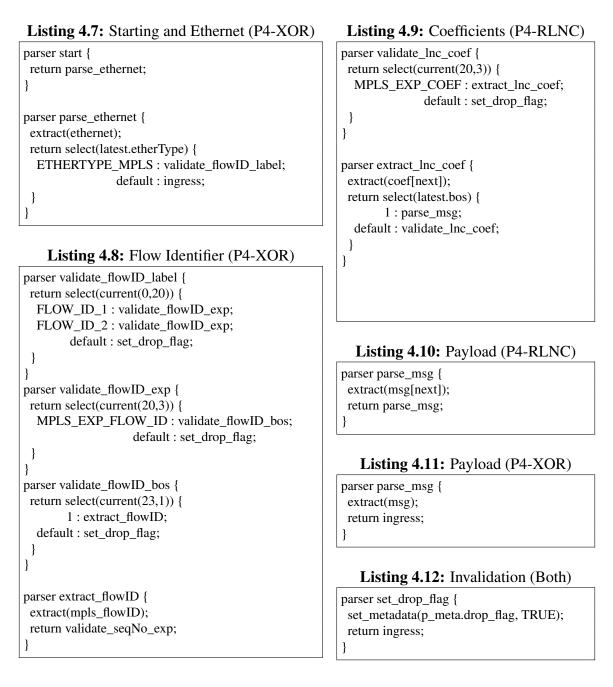

| 5.1  | Testing Environment's Network Topologies                             | 76 |

| 5.2  | Sending report of packet A - Source node h1, logical port 0          | 79 |

| 5.3  | Sending report of packet B - Source node h1, logical port 1          | 79 |

| 5.4  | Reception report of packet A - Destination node h2, logical port 0   | 80 |

| 5.5  | Reception report of packet AB - Destination node h2, logical port 1 | 80 |

|------|---------------------------------------------------------------------|----|

| 5.6  | Reception report of packet B - Destination node h3, logical port 0  | 81 |

| 5.7  | Reception report of packet AB - Destination node h3, logical port 1 | 81 |

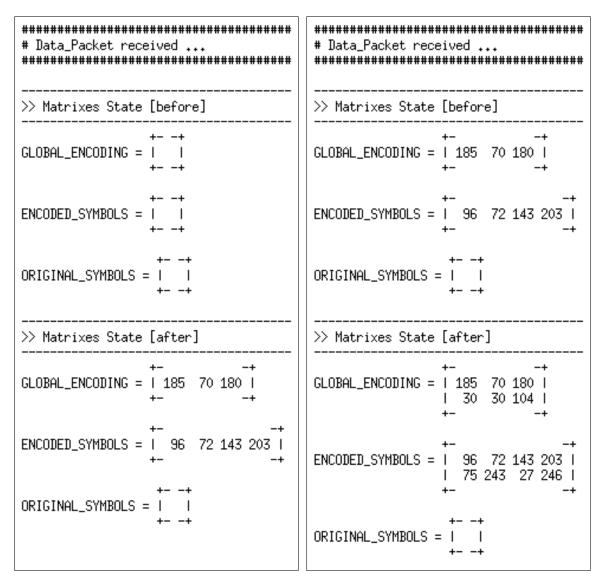

| 5.8  | Creation of a generation.                                           | 83 |

| 5.9  | Creation of the first DATA packet.                                  | 83 |

| 5.10 | Creation of the second DATA packet.                                 | 84 |

| 5.11 | Creation of the third DATA packet.                                  | 84 |

| 5.12 | Reception of the first recoded DATA packet                          | 85 |

| 5.13 | Reception of the second recoded DATA packet.                        | 85 |

| 5.14 | Reception of the third recoded DATA packet.                         | 86 |

| 5.15 | Measured CPU Utilization                                            | 89 |

| 5.16 | Measured Throughput on h2-eth0                                      | 91 |

| 5.17 | Measured Throughput on h2-eth1                                      | 91 |

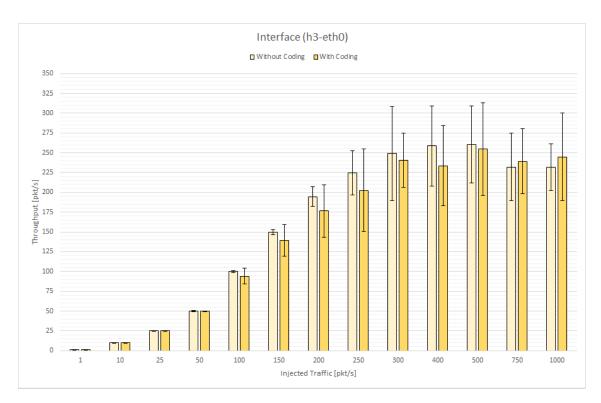

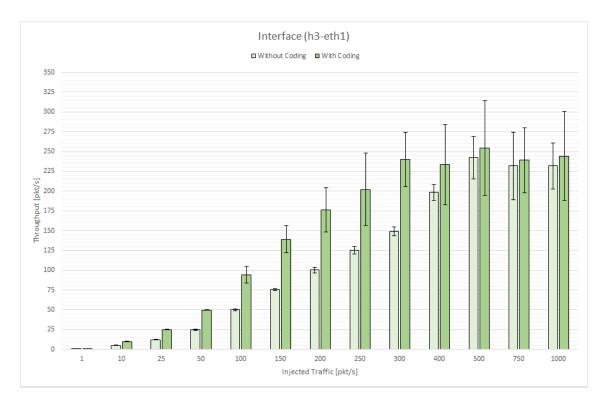

| 5.18 | Measured Throughput on h3-eth0                                      | 92 |

| 5.19 | Measured Throughput on h3-eth1                                      | 92 |

# **List of Tables**

| 5.1 | Expected Throughput on | Destination Nodes |  |  |  |  |  |  | 87 |

|-----|------------------------|-------------------|--|--|--|--|--|--|----|

|-----|------------------------|-------------------|--|--|--|--|--|--|----|

## **Chapter 1 – Introduction**

This chapter serves as an introduction for this dissertation. The motivation ( $\S$  1.1), goals ( $\S$  1.2) and contributions ( $\S$  1.3) are discussed here. Lastly, the remaining of the document is outlined ( $\S$  1.4).

In existing computer networks, packets are transmitted from source nodes to destination nodes through a chain of intermediate nodes, by a *store-and-forward* paradigm. In this paradigm, intermediate nodes simply store data packets from input links, and forward one or several copies to output links. Network Coding (NC) extends this paradigm to *store-code-forward*. Its premise is simple. Instead of simply store, replicate and/or forward incoming data packets, intermediate nodes are also allowed to mix the contents of several packets, by applying a coding function.

The encoding scheme can be designed in several different ways. It may be linear, nonlinear, random, static, convolutional, etc. However, derived from the characteristics of computer networks, the encoding scheme tends to be: linear and fixed (Linear Network Coding [62]), or linear and random (Random Linear Network Coding [47]).

Depending on the encoding scheme and on the network topology, the NC technique may provide several advantages. The main advantage is an increase of throughput, over traditional routing, specially in multicast scenarios. It may also improve security (e.g., to packet sniffing), manageability, resilience (to losses of specific packets, link failures and node departures) and quality of service.

Due to its potential and significant advances on the theoretical front, several practical applications emerged over the years, in different areas. This includes, content distribution systems [68], wireless networks [51], ad-hoc networks [39], storage networks [36], peer-to-peer networks [61], disruption-tolerant networks [63], among others.

However, its deployment has proved to be problematic, in practice. This is mainly due to the difficulty to change, extend or adapt the functionality of traditional switches. The incorporated switching chips have a fixed processing pipeline, which operates over a fixed set of protocols. Therefore, until now, practical implementations of NC tend to operate as overlay networks. An overlay network is logically located at the application layer (i.e., running in end-hosts), meaning that the underlying physical network devices are not

changed.

## **1.1 Motivation**

As already mentioned, NC is very advantageous, in theory. However, enabling it in today's networks can be, in practice, a big challenge as current switches do not offer the required flexibility. The processing pipelines are unnecessarily long and contain tables fixed in number, arrangement and size, which process a fixed set of headers. This makes it hard to add new protocols or change the existing ones. Therefore, NC is not possible in hardware switches.

However, computer networks are changing paradigm: from configurable to programmable. This change finally brings the opportunity to deploy NC at the network layer.

Software-Defined Networks (SDN) [56] are considered as the first instance of a programmable network. The idea is to enable control plane programmability, by physically decoupling the data plane from the control plane. This decoupling provides a logically centralized view over the network, which permits a more flexible and on-the-fly allocation of resources, like buffer management and dynamic routing. The communication between the control plane and data plane is standardized, in a protocol known as Open-Flow [69, 14]. However, SDN only addresses the exposition of the data plane, not its programming. Likewise, OpenFlow-compliant switches still operate over a fixed set of protocols, and a fixed processing pipeline of match-action tables. Moreover, the set of primitive instructions that may be used to define an action, is also fixed. In addition, the set of protocols, primitive instructions and processing pipeline do not contemplate modifications to the packet's payload. Therefore, OpenFlow alone does not allow the encoding of packets required for NC.

Nevertheless, it is true that several works leveraged on the OpenFlow capabilities to deploy NC. However, all of them required extensions and modifications to the OpenFlow protocol itself. For instance, in [72, 85] OpenFlow is extended with additional actions; and in [82, 57] it is integrated with the KODO library [73].

Fortunately, there has been recently, a great development of programmable switches. With their low-level interfaces, its easier to customize the processing pipeline of match-action tables, within the data plane. This means that, they are capable of running new user created protocols. The ability to program switches, and the restrictions of previous solutions (e.g., OpenFlow), served as motivation for the creation of high-level languages. Their objective is to ease the task of switch programming, and focus on expressiveness and portability.

The first high-level language, for switch programming, is known as P4 [26]. The P4 lan-

guage allows the definition of protocol headers, parsers, tables, actions and the processing pipeline itself. It is designed to be compiled to the underlying hardware. Many renowned companies are already starting to adopt P4 [17], and so it expected to become the standard for switch programming. In fact, P4 is already supported by the first programmable hardware switch: Barefoot Tofino [1].

Leveraging from the capabilities of programmable switches and languages such as P4, it is now possible to manipulate the payload of packets. Therefore, by using P4, we design and implement the first P4-compliant switch, capable of performing NC within the data plane itself.

#### **1.2 Goals**

The main goal of this dissertation is the design and implementation of a switch, capable of performing NC on the data plane. With that purpose, we use the recent and promising P4 language, which enables a custom and precise definition of the data plane of P4-compliant programmable switches. The target of our proposal is a P4-compliant software switch, provided by the P4 Consortium, known as Behavioral Model 2 (bmv2) [18]. This switch has been the target used in most related work, as in principle a program that runs in the bmv2 should run in any other target having the required compiler (e.g., Barefoot Tofino).

### **1.3** Contributions

The main contribution of this dissertation is the design and implementation of two NC data planes (P4-XOR Switch and P4-RLNC Switch), for P4-compliant switches, for the first time. As the names suggest, the P4-XOR Switch consists on Exclusive-OR Network Coding (XOR), and the P4-RLNC Switch on Random Linear Network Coding (RLNC). In order not to work just as a fixed code, but rather as a network protocol as well, we created and used a custom header stack, based on MPLS, to carry all encoding metadata. Besides the XOR and RLNC schemes, we also designed and implemented our own buffers, and forwarding rules. The implementation uses the P4-14 version of language, which is the most stable at this moment.

Finally, the evaluation of our solution was performed recurring to a network emulator with P4 support - Mininet. The evaluation includes functionality tests for both switches. Additionally, we also run performance tests, consisting of throughput and CPU utilization measurements, for the P4-XOR Switch, in the well-known butterfly topology. Our evaluation demonstrates both solutions to fulfill all requirements.

The result of this work is publicly available in our group's repository<sup>1</sup>. It includes the developed tools to automatically generate the P4 code of our switches; and the traffic generators, receptors and decoders, for testing purposes.

## **1.4** Structure of the document

This document is organized as follows. **Chapter 2** (§ 2) provides the background and related work on NC and P4. **Chapter 3** (§ 3) consists on the design of our NC solutions, using P4. **Chapter 4** (§ 4) details the implementation. **Chapter 5** (§ 5) presents the evaluation in terms of functionality and performance tests. **Chapter 6** (§ 6) finishes with a conclusion about the work done, and what may be done in the future.

<sup>&</sup>lt;sup>1</sup>https://github.com/netx-ulx/NC.p4

## **Chapter 2 – Related Work**

In this chapter, we overview the most important aspects, in the context of this dissertation, on Network Coding and the P4 language.

Network Coding (NC), as a technique, has a great potential to improve the overall performance of a network, over traditional routing. Specially, in a single-source multicast scenario. We start by specifying how the maximum multicast throughput is determined ( $\S$  2.1.1) which, unlike with routing, may always be achievable with a NC solution. We introduce Exclusive-OR Network Coding, to exemplify this result ( $\S$  2.1.2), and also because is one of the coding schemes we implemented. For the same reason, we describe Linear Network Coding ( $\S$  2.1.3) and Random Linear Network Coding ( $\S$  2.1.4). Then, we explore some of its variants ( $\S$  2.1.5), advantages and use cases ( $\S$  2.1.6). Finally, we finish with some practical applications of NC ( $\S$  2.1.7).

With the advent of programmable switches and of the P4 language, NC can be deployed on the data plane of a switch. We contextualize the motivation for the emergence of the language ( $\S$  2.2.1,  $\S$  2.2.2). Then briefly explain, in some detail, the language itself ( $\S$  2.2.3). We close the section, with applications that use P4 ( $\S$  2.2.4).

## 2.1 Network Coding - Overview

In today's existing packet computer networks such as the Internet, information is still delivered by routing packets from source to destination via intermediate nodes. It is the traditional store-and-forward design, i.e., intermediate nodes simply buffer received packets from input links and then relay or replicate them unmodified to output links. NC changes this design by allowing intermediate nodes to perform some computation, like applying a coding function or mix several packets before sending them to output links.

This mixing has been theoretically proven to maximize network throughput [24, 49, 54, 62]. For multicast, it can be done in a distributed manner with low complexity, and is robust to packet losses and network failures [46, 67]. It may also improve security and quality of service [81].

To perform NC, encoding and decoding schemes have to be employed on source, intermediate and/or destination nodes. There are several different schemes (with their own variations), but our main focus is on the most common: Exclusive-OR Network Coding (XOR), Linear Network Coding (LNC) and Random Linear Network Coding (RLNC).

#### 2.1.1 Max-Flow Min-Cut Theorem

The Max-Flow Min-Cut Theorem [24], firstly proven by Menger [70], states that the maximum multicast throughput of a network, per channel use, is bounded to the smallest edge cut separating the source and any of the destinations. This minimal cut represents the number of pairwise edge-disjoint paths from source to destination. Such a collection of pairwise-disjoint paths can be found using the Ford-Fulkerson algorithm [40].

In what concerns a unicast network, i.e., single source and destination nodes, the maximum throughput (equivalent to the smallest edge cut), per channel use, can be achieved simply with routing, by sending one packet along each of the edge-disjoint paths [71].

In the case of a multicast network, with a single source and a set of destination nodes, the maximum multicast throughput, per channel use, is not always achieved with routing [71]. However, it is achievable with NC [24]. Moreover, it is achievable with LNC, if the packet alphabet over a finite field is sufficiently large [62].

This is the main theorem of network multicasting. The next section provides a classical introductory example for this theorem and the concept of NC.

#### 2.1.2 Exclusive-OR Network Coding (XOR)

As the name suggests, in Exclusive-OR Network Coding (XOR) [24], the encoding and decoding schemes consist of a bit-wise addition, also referred as Exclusive-OR, or simply, XOR.

In XOR, source nodes transmit (n) original uncoded packets. Intermediate nodes perform encoding by applying a logical XOR on the incoming packets (from a single or multiple source/flow). Decoding is done at destination nodes. In order to decode, these nodes must previously receive and store (n - 1) original packets of the coded packet.

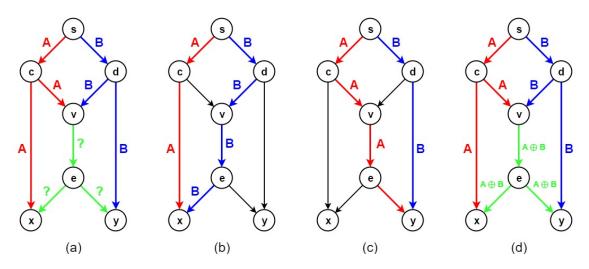

To illustrate the concept, let's consider a single source node S, and two destination nodes X and Y. Intermediate nodes C, D, E and V simply multicast incoming packets to the remaining ports. The source node S has two packets, A and B, which must be multicast to X and Y, at the highest rate possible. Also, each directed edge represents a network link, and can transmit only a single packet per time unit. From Figure 2.1 (a), if no coding is allowed, there is a "bottleneck" at the node V. Either the packet A or B is transmitted

**Figure 2.1:** Traditional Butterfly Network (a) Network bottleneck (b) Routing solution to X (c) Routing solution to Y (d) Network Coding solution.

through the outgoing link. To deliver both packets A and B, to both destinations X and Y, node V requires two time units. The first to transmit packet A, the second to transmit packet B, or vice-versa. This possible routing solution is illustrated in Figure 2.1 (b) and (c). From Figure 2.1 (d), if coding is allowed, by extending node's V functionality from *store-and-forward* to *store-encode-forward*, then it can perform a simple XOR on both packet A and B, and transmit the result. This allows to overcome the congestion of node V, as X obtains A and reconstruct B from  $A \oplus (A \oplus B) = B$  and Y obtains B and  $A = B \oplus (A \oplus B)$ , in a single time unit.

#### 2.1.3 Linear Network Coding (LNC)

In Linear Network Coding (LNC) [62], intermediate nodes transmit to output links, linear combinations of packets from input links. The coefficients of the combination are selected over a finite field F. In particular, the XOR scheme (§ 2.1.2) is the base case of a linear code, where the size of the finite field is just 2. From the literature, the LNC concept [32] can be formally defined as follows.

Consider a network with a single source s and a set of destinations T. Let h be the multicast capacity of the network, and  $x_1, \ldots, x_h$  the h packets to multicast from s to T, per unit of time. For each output link e from an intermediate node v, let y(e) denote its carried packet. The packet y(e) is a linear combination of packets y(e') from input links e' of node v, computed as  $y(e) = \sum_{e'} \beta_{e'} y(e')$ . The coefficients of this linear combination form a vector  $\beta_{(e)} = [\beta_{e'}(e)]$ , known as the local encoding vector on edge e. This vector's length equals the number of input links.

Consider  $y(e'_1), \ldots, y(e'_h)$  as the original  $x_1, \ldots, x_h$ . Then, the packet y(e) on any edge e in the network can be computed as a linear combination of the source packets  $x_1, \ldots, x_h$ ,

i.e.,  $y(e) = \sum_{i=1}^{h} g_i(e)x_i$ . The coefficients of this linear combination form a vector  $g(e) = [g_1(e), \ldots, g_h(e)]$ , known as the global encoding vector on edge e. The global encoding vector g(e) represents the packet y(e) in terms of the source packets  $x_1, \ldots, x_h$ . Concluding, the global encoding vectors can be computed recursively as  $g(e) = \sum_{e'} \beta_{e'}(e)g(e')$ , by using the coefficients of the local encoding vectors  $\beta(e)$ .

Supposing that a destination node  $t \in T$  receives the packets  $y(e_1), \ldots, y(e_h)$  on input links  $e_1, \ldots, e_h$ , they can be expressed in terms of the original packets as:

$$\begin{bmatrix} y(e_1) \\ \vdots \\ y(e_h) \end{bmatrix} = \begin{bmatrix} g_1(e_1) & \dots & g_h(e_1) \\ \vdots & \ddots & \vdots \\ g_1(e_h) & \dots & g_h(e_h) \end{bmatrix} \begin{bmatrix} x_1 \\ \vdots \\ x_h \end{bmatrix} = G_t \begin{bmatrix} x_1 \\ \vdots \\ x_h \end{bmatrix}$$

where the  $i_{th}$  row of the matrix  $G_t$  is the global encoding vector associated with edge  $e_i$  entering destination t. A network coding solution is found when the matrix  $G_t$  has full rank (in this case, h entries). The h original packets are then obtained by inverting the matrix  $G_t$  and applying the result to the previously received encoded packets.

Establishing the necessary local encoding vectors (for each node) to find a network coding solution is not trivial. Over the years, many algorithms appeared with that purpose. The first one was proposed by Li et al. [62], but the running time was exponential. The first polynomial time algorithm was proposed by Jaggi and Sander et al. [49]. Other polynomial time solutions are [43, 59]. As of today, the best algorithm is considered to be [59]. Koetter and Médard [54, 53] simplified the problem of finding these local encoding vectors, by alternatively giving an algebraic framework for LNC.

#### 2.1.4 Random Linear Network Coding (RLNC)

In Random Linear Network Coding (RLNC) [47], the local encoding vectors are simply chosen completely at random, over a large enough galois field (GF). If the field is sufficiently large, the resulting code will, with very high probability, achieve the maximum multicast rate for the considered network. The main advantage of RLNC is that the assignment of these vectors can be done in a decentralized way, without the need to run the polynomial time algorithms (as referred in § 2.1.3) to establish them over all network nodes a priori, during startup. This can be useful in practical applications [46, 28].

In this section, we describe, in a less formal and more practical way, the most standard RLNC [62, 47] strategy. There are several variants (§ 2.1.5).

In RLNC, a message (e.g., video, audio, etc) to be sent is broken into several chunks of equal length - each known as a "generation" of the original message. Each generation is further divided into "symbols", also of equal length each. The number of symbols

represents the generation size. Each symbol is further divided into elements of x bits, given the considered Galois Field  $(2^x)$ .

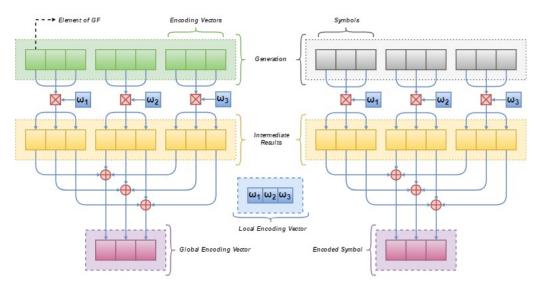

Figure 2.2: Random Linear Network Coding - Encoding.

Encoded symbols are obtained by performing linear combinations of all the original symbols of that generation. For each original symbol, a coefficient is randomly chosen over the considered Galois Field (GF). Then, each element of the given symbol is multiplied by this coefficient. Finally, each element composing the encoded symbol is the result of the addition of all the multiplications performed over the elements of each original symbol by the respective coefficient, of the same position (see Fig. 2.2).

The set of coefficients, used during the encoding process, is known as the local encoding vector. The set of local encoding vectors applied at each network node, from source to destination, forms the global encoding vector.

Figure 2.3: Random Linear Network Coding - Decoding.

To decode a generation, a number of linearly independent symbols, equal or greater than the generation size, and the respective global encoding vectors, is required. The symbols are placed on an Encoded Symbols Matrix (R) and the respective global encoding vectors on a Global Encoding Matrix (G), until the matrix G is square and has a rank equal to the generation size. The matrix with the original symbols (O) is obtained by solving  $O = G^{-1} \times R$ . The inverse of the matrix G is obtained with the Guass-Jordan elimination algorithm, which is a variant of Gaussian elimination (see Fig. 2.3).

#### 2.1.5 Other RLNC Schemes and Variants

As previously mentioned, there are several RLNC strategies. Depending on the use case, one strategy might be more adequate than another. Consequently, no strategy can be defined as the best. Below is a summary of the most well known and commonly used:

- Standard RLNC: For a given generation, all symbols are uniformly and randomly combined. Because the symbols are mixed as much as possible, this coding type is typically "dense" and computationally "heavy". As such, for a fairly efficient use, small field sizes are a requirement.

- **Sparse RLNC with uniform density** [38]: Same as the standard RLNC case, with the difference that some symbols of the given generation have a certain probability of being excluded during the encoding process. This is useful when the generation size is substantially high. As a result, the density of the code is reduced, without any downside, and the decoding performance is greatly increased.

- Sparse RLNC with fixed density [68]: Given the current generation, only a fixed number of symbols is used as input to the encoding process. If this fixed number of symbols equals the size of the generation, then it is the same as the standard RLNC. This strategy is useful if the decoder is able to provide feedback about the state of the decoding of the current generation, as the encoding/recoding processes can be adjusted accordingly to the current needs and, thus, provide a slight increase in performance.

- Seed-based RLNC [31]: Typically, the encoding vector is fully sent alongside the encoded symbol. To reduce this overhead, a random seed, able to generate the encoding vector, is sent instead. This strategy makes recoding more difficult and complex, even impossible in some cases. As such, this is used in scenarios where recoding is very little used, or not used at all.

- On-the-fly RLNC [35]: This scheme differs from the traditional block codes. Contrary to these, it is not necessary for all the data to be available before encoding/recoding/decoding can take place. Given the current generation, a symbol can be immediately encoded/recoded as soon as it is available. Decoding is similar. For each newly received symbol, the decoder immediately performs one additional decoding step and releases any resulting decoded symbols, if possible. This coding

strategy works well with low-delay services, such as VoIP, video streaming and messaging.

- **Perpetual RLNC** [44]: This is a sparse and well structured coding strategy. The non-zero coding coefficients, i.e., the coding coefficients associated to symbols used on the encoding/recoding process, have a specific location in the coding vector. The width of the non-zero subset of coefficients is analogous to the density of random sparse codes. Due to this characteristic, this approach allows the decoding process to be well structured, which permits achieving higher throughput values than other random sparse codes, especially with high generation sizes.

- Fulcrum RLNC [66]: Consists of a concatenated "outer" and "inner" code structure. These codes provide end-to-end performance similar to other large field network codes for high-end receivers, while simultaneously being able to serve lowend nodes that may only, for instance, be able to decode in GF(2).

#### 2.1.6 Advantages and Use Cases

The number of scenarios and use cases where NC might bring benefits are enormous. This section's objective is not to enumerate all of them. Nor is it to formally prove the advantages of NC. Instead its goal is to highlight its benefits and applicability.

As already stated at the beginning of this chapter, NC has successfully been proven to provide reliability and/or to increase (even maximize) throughput of different communication networks. Another benefit is the fact that for certain codes, like linear ones, network nodes don't have the requirement of receiving specific data packets in their totality. Instead, they just have to receive a sufficient number of linearly independent encoded packets to be able to decode and retrieve the original data.

Just like Erasure Correcting Codes (ECC), NC can be used in Point-to-Point Communication Networks with lossy links, to deal with packet losses. If a fairly accurate estimate of the packet loss probability is known, source nodes may pro-actively send extra redundant packets to compensate losses. This technique is known as Forward Error Correction (FEC). Another approach is to send the extra redundant packets retro-actively, which requires the destination to acknowledge the source about the lost packets. In this case, NC simplifies the acknowledgment mechanism, because the destination just has to provide information about the number of lost packets, and not specifically which ones.

Another use case that benefits from NC is reliable multicast, over wireless networks, with lossy links. If no losses were to occur and each channel had ideal bandwidth, all multicast packets would be received by all destination nodes. On the other hand, in the presence of packet losses, reliability can be assured by a retransmission mechanism. Destination

nodes just need to request the missing packets from the source. This means that all lost packets are transmitted again. If the several losses, among all destination nodes, are not correlated, then most of the retransmitted packets will not be useful to specific destinations. Basically, due to the uncorrelated nature of packet losses, each destination usually has a different set of received packets. In the end, network resources are wasted and a single retransmission will most likely serve a single destination node. However, with the use of NC, a single retransmission of an encoded packet, instead of a original one, can serve multiple destination nodes. In this case, the source node can send a linear combination of the original data. Each encoded packet might therefore be useful at different destination nodes during the decoding process, and thus serve several nodes simultaneously, instead of just one.

In best-effort multicast networks, reliability is usually not a requirement neither effectively possible. Considering a video streaming to several destination nodes over a wireless network, where acknowledgments are impractical, NC can help to maximize the impact of each retransmission. In the case of linear codes, reliability is ensured by transmitted a certain number of redundant packets for each generation. The redundancy ratio should be tuned according the estimated Packet Error Probability (PER).

Networks characterized by dynamic nodes, i.e. nodes constantly changing their physical position; or connected in a multi-hop fashion, i.e. where some nodes can be exclusively reached over multiple hops, greatly benefit from NC due to its recoding feature. Basically, with LNC schemes, intermediate nodes can create new recoded packets and thus new linear combinations of previously received and stored packets. Recoded packets can be generated from partially decoded generations. As in these networks, source and destination nodes are several hops away, if the recoding scheme at the several intermediate nodes follows an *interflow* scheme, then the same recoded packets might be used by several different destination nodes, to retrieve original data from different flows (i.e., the desired flow by the given destination node).

Additionally, in multi-hop networks a single node has limited (to none) information about other nodes' state, especially if these nodes are several hops away. LNC requires coordination among all nodes as the statically set of coefficient used must guarantee that the final set of packets received at destination nodes is decodable. RLNC provides an implicit solution for this coordination problem as coefficients are randomly chosen over a significant large finite field, which ensures that the final set of packets received by destination nodes is decodable with very high probability.

#### 2.1.7 Network Coding Applications

Despite being a fairly recent topic, NC has had its fair share of applicability. This is easily proven by consulting just a few surveys [32, 36, 25, 37]. Nonetheless, in this section a few applications, that served as a learning base for NC, and inspiration for the design of our solution, are summarized.

#### COPE

COPE [51] is a packet forwarding architecture for wireless mesh networks that significantly improves its overall throughput. It is based on two key principles: (1) employment of network coding and (2) exploit of the broadcast nature of wireless channels instead of point-to-point link abstractions. This permits taking advantage of coding opportunities to forward several packets in a single transmission. These coding opportunities are detected by a coding layer inserted between the IP and MAC layers. It uses inter-session network coding – packets with different destinations are encoded together. The coding scheme consists of a simple XOR of multiple packets.

COPE incorporates three main techniques:

- **Opportunistic Listening**: Each node is required to store packets in a packet pool to be able to perform coding and decoding. The packet pool consists of two kinds of packets. Packets the node itself has to broadcast, and packets it has overheard. Since wireless is a broadcast medium, there are many opportunities for nodes to overhear transmitted packets. To avoid having nodes discarding overheard packets not meant to them, COPE sets all nodes to promiscuous mode. In this mode, all overheard packets are stored for a limited period of time T. Each node informs its neighbors about its stored packets by broadcasting reception reports.

- **Opportunistic Coding**: Nodes should maximize the number of native packets delivered in a single transmission, while ensuring that each intended next hop has enough information, i.e., all but the native packet, to decode its native packet. This aims to maximize the benefits of coding [51].

- Learning Neighbor State: Nodes ideally would need an accurate global view of the network, i.e., to know which packets each neighbor has stored. This information is given from reception reports. However, if the network is severely congested, reception reports may arrive too late or get lost, and so, the solution is to make well-informed guesses. This process is as follows: (1) compute the delivery probability of all paths, (2) broadcast the results to all nodes and (3) use them in a link-state routing protocol to compute shortest paths. An incorrect guess may be made sometimes, making the native packet un-decodable at the destination. Whenever that

happens, the native packet is retransmitted again, potentially encoded with a different set of packets.

In COPE, each node maintains four data structures: a packet pool to store overheard packets; a FIFO output queue of packets to be forwarded; two per-neighbor virtual queues (one for small and other for large packets); and an hash table indicating for each packet the probability of each neighbor having that packet. Packets contain three blocks of data: IDs of the encoded native packets, reception reports, and set of acknowledgments to be delivered.

COPE never delays packets in order to encode. If no coding opportunity is available, an uncoded packet is sent. Also, packets headed for the same next hop are never encoded together. Preference to XOR-ing packets of similar lengths is given.

The 802.11 broadcast is not used because it lacks reliability, backoff and retransmission mechanism. Instead, COPE relies on a pseudo-broadcast which unicasts packets that are meant for broadcast. The unicasted packet has its MAC address set to one of the nexthops and a XOR-header listing all nexthops of the packet. Nodes that overhear the packet check this header to see if it is a nexthop.

Although COPE works well, it has some limitations and a more efficient architecture is proposed in [50].

### MORE

MORE [28, 29] is a wireless routing protocol for wireless mesh networks. It is also an opportunistic routing protocol, which makes it more reliable against packet losses. Just like COPE [51], MORE detects coding opportunities via a coding layer inserted between the IP and MAC layers. Differently from COPE, MORE employs intra-session network coding – packets with the same destination are encoded together. The coding scheme consists on RLNC.

In this protocol, the rule of each type of node is summarized as follows:

• Source: The source partitions the file to be transmitted into batches of K native packets. Then creates a random linear combination of the K native packets of the current batch, and broadcasts the resulting coded packet. Attached to the packet is the coefficient vector used for encoding, the ID of the batch, the source and destination IP addresses and a forwarder list with eligible nodes to forward the packet. The list includes nodes closer to the destination than the source, ordered by their proximity (computed using the ETX metric [34]) to the destination. The source continues to broadcast coded packets of the current batch until the batch is acknowledged by the destination.

- Forwarders: Forwarders nodes listen for packets on all transmissions. When a new packet is heard, the node first checks if it is in the packet's forwarder list. If so, the node performs two actions. Firstly, it decodes the packet, via Gaussian Elimination [53, 54], to check if it is an innovative packet linear independent from previously received packets for the current batch. Innovative packets are stored and non-innovative are discarded. Secondly, it creates a new random linear combination of all packets heard for the current batch and broadcasts the resulting coded packet.

- **Destination**: The destination stores innovative packets and discards non-innovative ones. Once K innovative packets are received for the current batch, it decodes the whole batch by using a matrix inversion technique. It then sends an acknowledgement back to the source, so that it can start sending packets from the next batch.

#### Avalanche

Avalanche [42] is a peer-to-peer system for file distribution, developed by Microsoft, based on a RLNC coding scheme. An important advantage is that it does not require the knowledge of the underlying topology or any centralized scheduling. In addition, it is robust to extreme situations, such as sudden server and nodes departures and has better performance compared to source coding or no encoding schemes.

Avalanche has a single centralized server, which stores the original files. The server is constantly dividing each file into K blocks and uploading the blocks to different client nodes, at random. To retrieve the original file, the clients exchange blocks only with a small subset of other clients – the neighborhood. The neighborhood is constructed when the client first joins the network and contacts the server to get a list of random clients in the system.

In Avalanche, there are three modes of content propagation: no coding, source coding and network coding. In the case of no coding and source coding, the algorithm for deciding which block to transfer is based exclusively on local information. The block to transfer may be picked among the rarest in the neighborhood, the rarest system-wise among the neighborhood (not practical in large networks), or completely at random.

In the case of network coding, the node generates and sends a random linear combination of all the encoded packets it has received so far, for the given file. Reconstructing the original file is done after receiving K linear independent blocks, associated with the respective coefficient coding vector. With network coding, a client does not need to request specific blocks. Instead, it keeps downloading coded blocks from its neighbors, until it can reconstruct the original file.

Avalanche also offers two incentive mechanisms to discourage free-riding, i.e., having clients take advantage of the network to obtain the desired files without contributing with

uploads to other clients. The first is to allocate more upload bandwidth to neighbors from which the client is also downloading, than to those which it is not. The second (tit-for-tat approach, from BitTorrent) is not to upload to a neighbor until the absolute difference of uploading minus downloading from one to another is bounded.

## **Other Applications**

We close this section with references to a few other interesting applications.

Ncos [64] is a framework for realizing network coding over SDN. The paper discusses the possibility of using an XOR network coding scheme through the extension of the OpenFlow protocol [69, 14] and of the functionality of switches.

KODO [73, 45] is an open source C++ network coding library intended to be used in practical studies of network coding algorithms.

Other areas of NC application include Commercial mobile platforms (e.g., PictureViewer [74]), LTE Networks (e.g., Raptor codes in eMBMS [83]), Mobile *Ad Hoc* Networks (e.g., CONCERTO [39]), network security [81, 80], etc.

Listing all the fields and relevant applications of network coding is a never ending task. Therefore, a read on existing surveys [32, 36, 25, 37] is recommended.

## 2.2 SDN and P4 - Overview

P4 is a declarative language for data plane programming, which works alongside SDN control protocols, such as Openflow. This section provides a brief walktrough over the issues related to traditional computing network equipments, that SDN and Openflow confront and try to solve, which consequently led to the appearance of P4. Finally, the P4 language is explained in detail.

## 2.2.1 Control Plane Programmability and SDN

In traditional computer networks, the functionality of each node can be divided in three planes:

- **Data plane**: Network nodes that forward packets to the next hop based on control plane decisions.

- **Control plane**: Protocols that populate the forwarding tables of data plane nodes.

- Management plane: Services that monitor and configure the control plane.

The problem with traditional architectures, is that these planes are vertically integrated. In particular, the control and data planes are tightly coupled inside vendor-specific closed hardware and software. This results in networks that are complex and hard to manage [56]. In order to change and adapt the existing protocols or even to add new ones, network operators need to configure each network node individually, one-by-one, or use complex low-level scripts to do so. This is the main reason why the innovation of networking infrastructure has progressed at a very slow pace.

Software-Defined Networking (SDN) [56, 77] is a new network paradigm that emerged and aims to solve the shortcomings of more traditional architectures. The Open Networking Foundation [12], defines the SDN architecture as:

- **Directly programmable**: Network control is directly programmable because it is decoupled from forwarding functions.

- Agile: Abstracting control from forwarding lets administrators dynamically adjust network-wide traffic flow to meet changing needs.

- **Centrally managed**: Network intelligence is (logically) centralized in softwarebased SDN controllers that maintain a global view of the network, which appears to applications and policy engines as a single, logical switch.

- **Programmatically configured**: SDN lets network managers configure, manage, secure, and optimize network resources very quickly via dynamic, automated SDN programs, which they can write themselves because the programs do not depend on proprietary software.

- **Open standards-based and vendor-neutral**: When implemented through open standards, SDN simplifies network design and operation because instructions are provided by SDN controllers instead of multiple, vendor-specific devices and protocols.

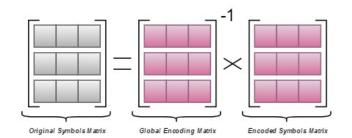

Figure 2.4, shows the SDN architecture in more detail. The lowest layer is the infrastructure layer, also called the data plane. It consists of the forwarding devices. At the middle, there is the control layer, also called the control plane. It is responsible for programming and managing the data plane. To that end, it makes use of the information provided by the data plane. It consists of one or more controllers. At the top, there is the application layer, also called the management plane, which contains network applications that assist the control layer in several tasks, such as security, management, monitoring or configuration of the network. These applications can make use of the global view of the network from the controllers.

Figure 2.4: Example of SDN architecture.

The controller offers two software interfaces to communicate with network application and forwarding devices, referred as the northbound API and southbound API, respectively. The northbound API is not standardized yet and there are many SDN programming languages that fulfill its purpose, such as: Frenetic [41], Pyretic [78] and Procera [84]. On the other hand, for the southbound API, there is a well-known standard – Open-Flow [69, 14].

#### 2.2.2 OpenFlow, Switch Chips and Motivation for P4

OpenFlow [69, 14] was developed with the objective of having a unique way for software control planes to remotely control OpenFlow-compliant switches from a variety of different vendors. The idea is to make the task of writing better control planes easier. In a great majority of computer networks, switches run the same protocols: Ethernet, IPv4, Access Control Lists (ACLs), VLANs, etc. OpenFlow defines a standard, i.e., an open interface to populate the forwarding tables in these switches. For instance, the hash tables for Ethernet address lookup, the longest-prefix match tables for IPv4 and the wildcard lookups for ACLs. At first, OpenFlow didn't please some vendors as it commoditized their switching products. However, the interest in it has grown tremendously since its conception and it has proven to be a huge success. As of today, there are hundreds of OpenFlow-compliant

switches [22, 11, 7, 5, 4, 3, 2] and this architecture has been deployed in enterprise environments [23, 10], service providers [13], and data centers [9, 8].

Still, OpenFlow has a shortcoming. It assumes that switches have a fixed, well-known behavior, typically described in the datasheet of the switch ASIC. Indeed, traditional high-performance switching chips support a fixed set of protocols because they directly implement IEEE and IETF standard protocols in silicon. Changing existing protocols or adding new ones, to measure and control the datapath in a different way, is not possible. Nowadays, it takes about four years to add a new protocol to a fixed-function ASIC. At first, OpenFlow only supported the addition and removal of forwarding entries for four common protocols: Ethernet, VLANs, IPv4 and ACLs. More header-types were added eventually, such as: IPv6, MPLS and VXLAN. Currently, there is support for more than fifty different protocols. Switch vendors can specify which headers the control plane supports, by using the Table Type Patterns (TTP) standard from the Open Networking Foundation (ONF).

In conclusion, OpenFlow doesn't really control the switch functionality. It just provides a mean to populate a set of well-known forwarding tables. An important drawback of using existing switches is their unnecessary complexity and insufficient flexibility. Existing chips are designed to support a huge set of features but only a small subset is usually used. Also, the processing pipelines may be too long. These pipelines contain a fixed number of tables, of fixed size, in a fixed arrangement, and they process a fixed set of headers. The combination of a long fixed pipeline and a large set of features results in resource waste and failure in adapting to new protocols.

To allow switches to expose more of their capabilities to the controller, it is required that more headers and multiple stages of rule tables are added to the OpenFlow specification. This trend can be problematic and unpractical, and it exists because switching chips are not programmable.

If switches offered more support of flexible mechanisms, for parsing packets and matching header fields, thus allowing controller applications to take advantage of these capabilities through a common open interface, a protocol like OpenFlow would not be necessary. Programmers could just define the desired API to create and populate custom tables, as well as define how to process packets.

In fact, reconfigurable (programmable) switch chips already exist for some time (for instance, NPUs and FPGAs). However, their performance is orders of magnitude worse than fixed-function ASICs. Fortunately, recent works in chip design demonstrate that the support to flexible mechanisms, like the ones mentioned above, can be achieved in custom ASICs at terabit speeds [55, 27, 6]. Such programmable switches already exist commercially. Barefoot Tofino [1], for instance, is the first fully programmable switch, and it's also the world's fastest, running at 6.4 Tbps. The problem is that programming these chips is difficult, as each chip has its own low-level interface, akin to microcode programming [26].

This was the motivation to create a common language to program every kind of switch the same way, and thus achieve interoperability between them. This language is known as: Programming Protocol-independent Packet Processors (P4) [26]. Although both Open-Flow and P4 focus on "opening" the forwarding plane, P4 addresses the need to *program* the data plane.

### 2.2.3 Data Plane Programmability and P4

P4 [26] is a prominent high-level declarative language, which works alongside SDN control protocols, such as OpenFlow. As of the writing of this dissertation, there are two versions of the language: P4-14 [15] and P4-16 [16]. Each one has its own specification and differs greatly both in syntax, semantics and underlying constructs. On the context of this dissertation, P4-14 was used, as it is currently the most stable version. Thus, we refer to P4-14, from now on. This section specifies all the necessary details about P4-14 that were used in, and are needed to understand, our implementation.

### Overview

P4 has three main design goals, which also turn out to be its main properties:

- **Reconfigurability**: Packet parsing and processing can be redefined once the switches are deployed.

- **Protocol independence**: Switches are not tied to specific network protocols and packet formats.

- Device independence: Packet parsing and functionality is described independently of the details, and specifics, of the underlying hardware. Instead, by taking the switch's capabilities into consideration, a compiler is used to configure the switch. Basically, it turns a target-independent description (written in P4) into a target-dependent program (used for switch configuration).

P4 expresses how the data plane of a programmable forwarding network device (i.e, router, hardware or software switch, network interface card [NIC], or network function appliance) processes incoming packets. Such P4 compliant devices are classified with the generic term: *target*. According to the specification, a target may directly execute a P4 program but it is assumed that the program is first compiled into a suitable configuration for the target.

Contrary to the data plane, P4 cannot be used to express the control plane of the target. However, in part, it also defines the communication interface between the control plane and data plane.

In traditional fixed-function devices, the data plane and control plane functionalities are defined by the manufacturer. Data plane manipulation is assured by the control plane via table entry management (e.g., routing tables), object configuration (e.g., meters and counters), and control-packets processing (e.g., routing protocol packets) or asynchronous event handling (e.g., link state changes or learning notifications). A P4 compliant target differs from a traditional fixed-function device in two distinct ways. Firstly, it has no built-in knowledge of existing network protocols, as its functionality is not fixed a priori but is defined by the P4 program instead. Secondly, the set of tables and other objects in the data plane are also not fixed and are defined by the P4 program. Hence, control plane and data plane communication is similar but the necessary API, for that purpose, is generated by a P4 compiler.

As such, P4 permits the expression of a broad variety of data plane protocols and behaviors, and thus can be said to be protocol independent. In sum, a P4 program specifies and consists of:

- **Headers**: A header definition describes the sequence and structure of a series of fields. It includes specification of field widths and constraints on field values.

- **Parsers**: A parser definition specifies how to identify headers and valid header sequences within packets.

- **Tables**: Match+action tables are the mechanism for performing packet processing. The P4 program defines the fields on which a table may match and the actions it may execute.

- Actions: A complex action, consisting of a set of simpler protocol-independent primitives. These complex actions are available within match+action tables.

- **Pipeline layout and control flow**: The control program determines the table layout within the data plane pipeline and the packet flow through the pipeline of match+action tables.

P4 addresses the configuration of a forwarding network device. After configuration, tables are populated and packet processing begins. Reconfiguration can still be performed during packet processing, usually by recurring to a runtime CLI interface, exposed by the target.

### **P4** Targets and Compilers

The P4 Consortium [20] provides a GitHub repository with an implementation of a P4 software switch, also known as Behavioral Model 2 [18] (nicknamed **bmv2**). It offers almost complete support for both P4-14 and P4-16. By default, it is prepared for the P4-14 architecture (i.e., Abstract Forwarding Model). The runnable components themselves (i.e., the runnable P4 switches), are within a directory named **targets**. There are three distinct targets: <code>simple\_router</code>, <code>l2\_switch</code> and <code>simple\_switch</code>. Each of these targets implements, in software, the P4-14 specification to a different extent. For instance, *simple\_router* and *l2\_switch* are very limited because they implement exclusively a handful of P4 primitives. On the contrary, *simple\_switch* is the most complete, thus being the reference target for P4. Therefore, *simple\_switch*, whenever bmv2 is mentioned.

To map a P4 program onto the target switch's specific hardware or software platform, we need a compiler. Particularly, P4-14 programs can be compiled to *simple\_switch* with **p4c** [19], which is the official, yet still alpha, P4 compiler.

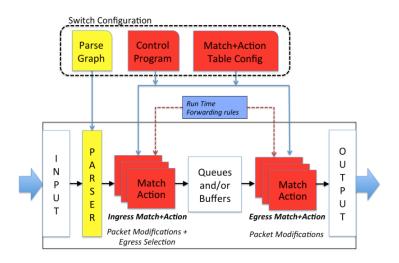

### **The Abstract Forwarding Model**

P4 is based on an abstract forwarding model, which generalizes packet processing in different forwarding devices (e.g., Ethernet switches, load balancers, routers) and by different technologies (e.g., fixed-function ASICs, NPUs, reconfigurable switches, software switches, FPGAs). It consists of a parser and a set of match-action ingress and egress table resources. The parser identifies and extracts headers (and respective fields within) of each incoming packet, for later manipulation. A match-action table performs a lookup on a subset of header fields and, for the first match, applies the respective action.

Figure 2.5: Abstract Forwarding Model [15].

Figure 2.5 shows a high-level representation of the P4 abstract forwarding model. The current "widely supported" P4-14 Specification [15], defines that a target must follow a set of rules, in order to operate:

- For each packet, the parser produces a *Parsed Representation* on which match+action tables operate.

- The match+action tables in the *Ingress Pipeline* generate an *Egress Specification* which determines the set of ports (and number of packet instances for each port) to which the packet will be sent.

- The *Queuing Mechanism* processes the *Egress Specification*, generates the necessary packet instances and submits each of them to the *Egress Pipeline*. Oversubscription for an output port may cause the Egress queuing to buffer packets, although this is not mandated by P4.

- A packet instance's physical destination is determined before entering the *Egress Pipeline*. Once in the *Egress Pipeline*, the destination is assumed not to change (though the packet may be dropped or its headers further modified).

- After all processing by the *Egress Pipeline* is complete, the packet instance's header is formed from the *Parsed Representation* (as modified by match+action processing) and the resulting packet is transmitted.

P4 focuses on the specification of the parser, match+action tables and the control flow through the pipelines. Programmers control this by writing a P4 program which specifies the switch configuration as shown at the top of Figure 2.5.

The *Queuing Mechanism* functionality and the *Egress Specification* semantics are not present in the most recent version of the P4 specification. Packet cloning and recirculation are supported features also.

### **P4** Abstractions

The P4 language provides several abstractions. Together, the set of instances of each, defines a P4 program:

- **Header type**: A specification of the set of fields, and respective sizes, of headers found within a packet.

- Header instance: A specific instance of a packet header or metadata.

- **Parser state function**: Describe the permitted sequences of headers, and how to properly identify and extract the headers and fields, within each received packet.

- Action function: Set of primitive actions that modify header fields, metadata and registers.

- **Table instance**: Specify the set of matching header fields and the permitted action functions within the given table.

- **Control flow function**: Imperative description of the match+tables to be applied, and in which order. The order might be influenced by logical conditions.

- **Stateful memories**: Data structures (counters, meters and registers) which persist across each packet processing.

Adding to the high level abstractions above, the following are used for a header instance:

- **Metadata**: Per-packet state which may or may not be derived from packet data, stateful memories and/or action primitives.

- Header stack: An array of header instances.

- **Dependent fields**: Fields whose values depend on a calculation applied to other fields or constants.

Parser state functions can also make use of:

- Value set: Values updatable at runtime and used to determine parser state transitions.

- **Checksums**: The ability to apply a function to a set of bytes from the packet and test that a field matches the calculation.

### **Headers and Fields**

Header types describe an ordered layout of field names, alongside the respective bit-width, and are used to declare header and metadata instances.

An example declaration for a MPLS header is:

```

header_type mpls_t {

fields {

label : 20; // width in bits

exp : 3;

bos : 1;

ttl : 8;

}

}

```

A packet may contain multiple instances of a given header type. There are two types of instances: packet headers and metadata. A header example is:

header mpls\_t packet\_type;

This indicates that space should be allocated in the *Parsed Representation* of the packet for a *mpls\_t* header. It may be referenced during parsing and match+action by the name *packet\_type*.

A metadata example is:

metadata local\_metadata\_t local\_metadata;

This indicates that a *local\_metadata\_t* type object called *local\_metadata* should be allocated for reference during match+action.

P4 supports the notion of a header stack, which is a sequence of adjacent headers of the same type, and is declared as an array. MPLS is the most common example:

header mpls\_t coefficients[100];

Header stack instances are referenced using bracket notation and such references are equivalent to a non-stack instance reference.