# Digital Dynamic Frequency Dividers for Broad Band Application up to 60 GHz

A. Thiede, M. Berroth, P. Tasker, M. Schlechtweg, J. Seibel, B.Raynor, A.Hülsmann, K.Köhler, W.Bronner

> Fraunhofer-Institute for Applied Solid State Physics, Tullastr.72, D-79108 Freiburg, Germany

#### Abstract

Í

A broad band dynamic frequency divider based on pseudomorphic Al<sub>0.2</sub>Ga<sub>0.8</sub>As/ In<sub>0.25</sub>Ga<sub>0.75</sub>As MODFETs and passive loads will be presented. Stable operation from 28 GHz up to 51 GHz with a power consumption of 440 mW could be shown.

SPICE network simulation predicts operation in the 35 GHz - 60 GHz range for a divider circuit using an advanced E/D AlGaAs/ InGaAs MODFET process.

#### Introduction

Very high speed frequency dividers are key components in many applications, such as in measurement and communication systems. Using 0.2  $\mu$ m GaAs MESFETs [1] and 0.25  $\mu$ m inverted AlGaAs HEMTs [2], operating frequencies of 26.5 GHz have been reported for dynamic dividers. Static dividers based on Si bipolar transistors [3], AlGaAs/GaAs HBTs [4] and AlInAs/ GaInAs HBTs [5] have achieved frequency limits of 25 GHz, 34.8 GHz, and 39.5 GHz, respectively.

A dynamic frequency divider operating in the 18-34 GHz range based on our E/D AlGaAs/GaAs/AlGaAs quantum well transistor process was presented in [6].

A measured operation performance enhancement to 28 GHz - 51 GHz by the use of pseudomorphic Al0.2Ga0.8As/ In0.25Ga0.75As MODFETs and passive loads will be presented here.

# **Process Technology**

We have developed a mix-and-match technology combining e-beam with optical lithography whereby the e-beam is used for writing the gates only. Mushroom shaped gates were used to reduce the resistance of  $0.15 \,\mu\text{m}$  gates [7].

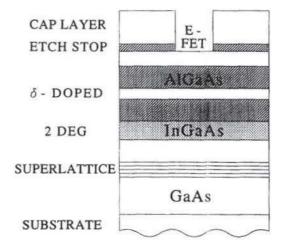

Fig. 1. MODFET layer structure

0-7803-1393-3/93/\$3.00 C 1993 IEEE

GaAs IC Symposium - 91

The layer structure as shown in fig.1 including  $n^+$ -cap,  $\delta$ -doped GaAs supply layer, AlGaAs spacer and pseudomorphic InGaAs channel was grown by MBE.

The typical growth conditions are published in [8]. Precise control of the threshold voltage was guaranteed by an AlGaAs etch stop using a dry etch process.

In our process sequence we have E-type MODFETs, NiCr thin film resistors, MIM capacitors, and two layers for interconnections. The top layer can be formed as air-bridges thus reducing parasitic capacitances.

### **Circuit Design**

The maximum input frequency to static dividers is restricted to about 1/2tpd, where tpd is the delay time of the used logic gate. Dynamic frequency dividers generally can reach two times higher input frequencies. The simplest dynamic frequency divider can be built up using an inverter and a buffer connected in series [1]. The output of the buffer is fed back to the inverter input by a transfergate. The inverter will be switched with half the frequency of the transfergate. The time in which the transfergate is switched on will be shorter than the delay of the inverter buffer chain, and that delay in turn will be no longer than one input pulse period. These conditions give the lower and upper limits for stable operation of the divider.

During that time when the tranfergate is switched off, the logic state is stored only in the capacitance of the high ohmic inverter input node. For short rise and fall times, however, the gate capacitance of the transfergate can cause logic errors. The use of a memory-type flip-flop for data storage as proposed in [2] is more reliable. To switch the memory-type flip-flop symmetrically, two ring oscillator chains are used. Differential outputs then become available.

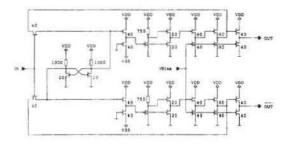

Fig. 2. Divider based on E-type MODFETs

Fig.2 shows a circuit schematic of an appropriate realization based on E-type MODFETs and NiCr ohmic resistors.

The circuit was optimized by SPICE network simulation based on an in-house developed heterojunction field effect transistor model [9].

The inverters of the ring oscillator chains are designed in SBFL for high logic swing and low output impedance. Three source follower buffers are used for appropriate signal delay and level shifting.

The memory-type flip-flop is built up by two E/R-DCFL inverters using  $1 k\Omega$ resistors for high logic swing. They normally would not achieve 30 GHz operation, but in this case the outputs are directly driven.

The gate width of the transfergates is a trade-off between a high on-conductance and a low capacitive load for the driving source follower.

SPICE simulation predicted 26 GHz - 50 GHz operation for this circuit design.

92 - GaAs IC Symposium

# Results

Fig. 3 is a micrograph of the divider circuit. The chip size is 1 mm x 1 mm, the internal divider measures about 200  $\mu$ m x 220  $\mu$ m. The input is applied to the bond pads using a 50  $\Omega$  coplanar line on chip terminated to match 50  $\Omega$ .

Fig. 3. Micrograph of the Divider Circuit

Stable operation was measured in the frequency range from 28 GHz up to 51 GHz with a power consumption of 440 mW.

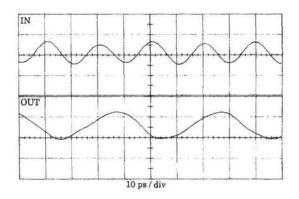

Fig.4 shows the pulse diagram of the 51 GHz input and 25.5 GHz output.

To the best of our knowledge, this is the highest input frequency ever reported for frequency divider circuits in any technology.

The circuit runs at a power supply of  $V_{DD}$ =+3.5 V and  $V_{SS}$ =-0.5 V. The required input voltage swing is less than 800 mV at 28 GHz and decreases as the frequency increases.

Fig. 4. Measured Pulse Diagram

### **Circuit Enhancement by an E/D Process**

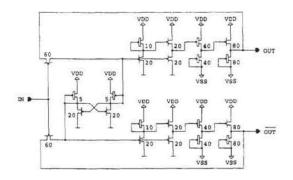

Fig.5 shows the circuit schematic for a similar divider circuit based on an E/D AlGaAs/InGaAs MODFET process.

D-type FET active loads led to a further increase of speed, and a less sophisticated circuit design. Only two source follower buffers are still necessary.

SPICE network simulation predict operation in the 35 GHz - 60 GHz range for that divider circuit.

Fig. 5 Divider based on E/D MODFETs

GaAs IC Symposium - 93

#### Summary

The design and performance of a broad band dynamic frequency divider based on E-type AlGaAs/InGaAs MODFETs was presented. Stable operation could be shown in a frequency range from 28 GHz - 51 GHz with a power consumption of 440 mW.

35 GHz - 60 GHz operation can be predicted for a divider circuit based on an E/D MODFET process available in the next future.

# Acknowledgments

This work was a group effort and the authors are grateful to the entire staff of the laboratory. We especially want to thank H.S.Rupprecht for his directing and continuous encouragement, and T.Jakobus for his expert technology management. The German Federal Ministry of Research and Technology is acknowledged for the financial support through the DFE-project TK357/8.

### References

- Jensen, J.F. et al.: "26 GHz GaAs Room-Temperature Dynamic Divider Circuit" IEEE-GaAs-IC-Symp., 1987, Portland, USA, pp.201-203

- [2] Saito, T. et al.: "0.25 µm Gate Inverted HEMTs for a Ultra-High Speed DCFL Dynamic Frequency Divider" IEEE-GaAs-IC-Symp., 1989, San Diego, USA, pp.117-120

- [3] Felder, A. et al.: "25 to 40 Gb/s Si ICs in Selective Epitaxial Bipolar Technology" ISSCC, 1993, San Francisco, USA, pp.156-157

- [4] Yamauchi, Y. et al.: "A 34.8 GHz 1/4 Static Frequency Divider using AlGaAs/GaAs HBTs" IEEE-GaAs-IC-Symp., 1989, San Diego, USA, pp.121-124

- [5] Jensen, J.F. et al.: "39.5 GHz Static Frequency Divider Implemented in AlInAs/GaInAs HBT Technology" IEEE-GaAs-IC-Symp.,1992, Miami Beach, USA, pp.101-104

- [6] Thiede, A. et al.: "An 18-34 GHz Dynamic Frequency Divider based on 0.2 μm AlGaAs/GaAs/AlGaAs Quantum Well Transistors" ISSCC 1993, San Francisco, USA, pp.176-177

- [7] Hülsmann, A. et al.: "Mushroom Shaped Gates Defined by e-Beam Lithography down to 80 nm Gate Length and Fabrication of Pseudomorphic HEMTs with a Dry-Etched Gate Recess" SPIE, vol.1465, Electron-Beam, X-Ray, and Ion-Beam Submicrometer Lithographies for Manufacturing, 1991, pp.210-208

- [8] Schweizer, T. et al.: "Materials and Device Properties of Pseudomorphic In<sub>x</sub>Ga<sub>1-x</sub>As/Al<sub>0.3</sub>Ga<sub>0.7</sub>As/GaAs High Electron Mobility Transistors (0<x<0.5)" Appl. Phys. A53, 1991, pp.109-113

- [9] Berroth. M.: "Circuit Simulator for Heterostructure Field Effect Transistors" Ph.D. Thesis, Ruhr-University Bochum, 1991

94 - GaAs IC Symposium