# Technology and Physics

Of

Gate Recessed GaN/AlGaN FETs

Masters Thesis

By

Adil Mahmood MALIK

Thesis Title: Technology and Physics of Gate Recessed GaN/AlGaN FETs

Start Date: 8<sup>th</sup> Feb. 2002

End Date: 8<sup>th</sup> Feb. 2003

First Supervisor: *Prof. Dr. H. Schweizer*

Second Supervisor: Prof. Dr. G. Denninger

Thesis completed at: *Microstructures Lab. 4<sup>th</sup> Physics Institute, Stuttgart University.*This thesis is a compulsory part of International Masters Degree Program in Physics at Stuttgart University, Stuttgart Germany.

# My Affections,

To my loving parents who always provided me a shelter under strong sun shines; My brothers who are my arms of strength, courage and directors; A precious gift of God, My sisters

**Adil Mahmood MALIK**

Contents iii

# **Contents**

| 1 | Introduction                                                    | 1  |

|---|-----------------------------------------------------------------|----|

| 2 | Group III-Nitrides                                              | 3  |

| _ | 2.1 Material Properties.                                        |    |

|   | 2.1-1 Crystal Structure                                         |    |

|   | 2.2 Electrical Properties.                                      |    |

|   | 2.2-1 Polarization.                                             |    |

|   | 2.2-1.1 Spontaneous Polarization                                |    |

|   | 2.2-1.2 Piezoelectric Polarization.                             |    |

|   | 2.3 Growth of GaN Layers.                                       |    |

|   | 2.3-1 Sapphire                                                  |    |

|   | 2.3-2 Doping with Si                                            |    |

|   | 2.4 GaN and other III-Nitrides.                                 |    |

| 3 | GaN FETs                                                        | 11 |

|   | 3.1 Family of GaN FETs                                          |    |

|   | 3.1-1 MESFET                                                    | 11 |

|   | 3.1-2 MISFET                                                    |    |

|   | 3.1-3 HEMT/HEMTs                                                | 13 |

|   | 3.2 Heterostructure GaN/Al <sub>x</sub> Ga <sub>1-x</sub> N FET | 14 |

|   | 3.2-1 Theoretical background                                    |    |

|   | 3.2-2 Two Dimensional Electron Gas in GaN/AlGaN                 | 15 |

|   | 3.3 Gate Recessed GaN/AlGaN HFET Modelling                      |    |

|   | 3.3-1 DC characteristics.                                       |    |

|   | 3.3-2 HF characteristics.                                       |    |

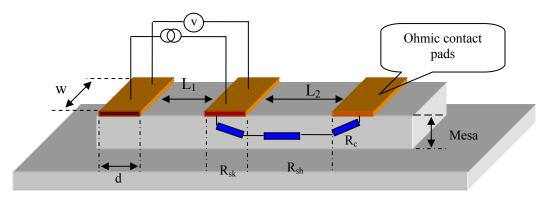

|   | 3.4 Linear TLM                                                  | 22 |

| 4 | Device Technology                                               | 27 |

| - | 4.1 Process Technology.                                         |    |

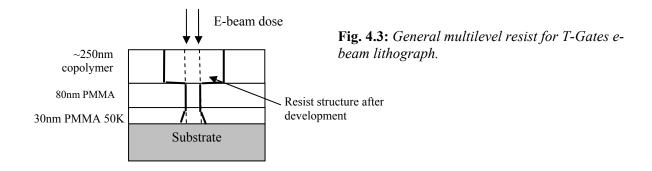

|   | 4.1-1 Micron and sub-micron lithography                         |    |

*Contents* iv

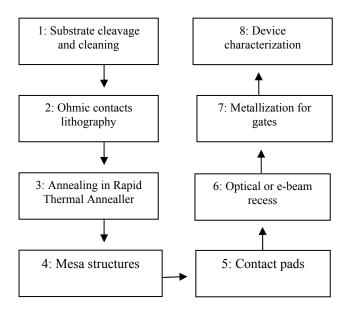

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.2 Fabrica  | tion Processes                         | 30  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------|-----|

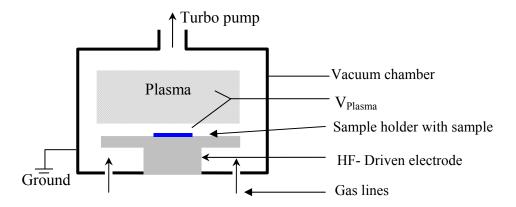

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.3 Dry Etc  | hing Technique                         | 33  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.4 Metalliz | zation                                 | 35  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.4-         | 1 Ohmic Contacts                       | 36  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              | 4.4-1.1 Annealing and ohmic behavior   | 36  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.4-         |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.5 Recesse  |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Device Cl    | haracterization of Gate Recessed HFET  | 43  |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              | •                                      |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.7 III CII  |                                        |     |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Summary      | ······································ | 71  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |     |

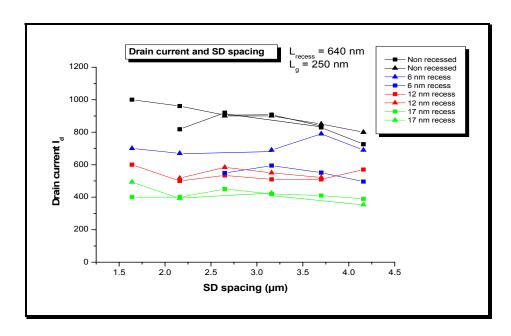

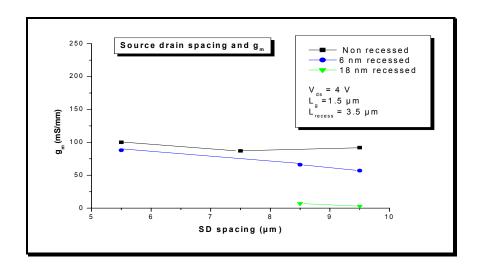

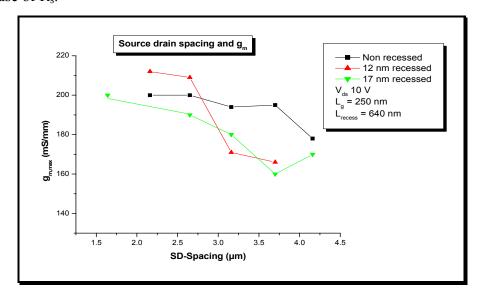

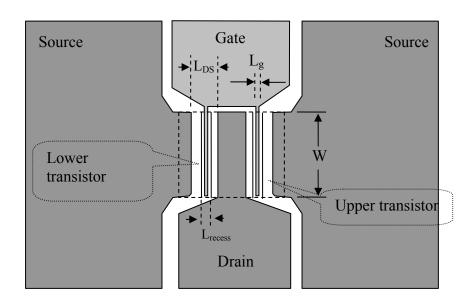

| 4.4-2.1 Physics of Schottky barrier.  4.5 Recessed Gates Technology. 4.5-1 T-gates.  5 Device Characterization of Gate Recessed HFET. 5.1 V (I) Characteristics of gate recessed GaN/AlGaN HFETs. 5.2 Source drain spacing. 5.2-1 Drain source current. 5.2-2 Transconductance. 5.3 Recess spacing. 5.3-1 Drain source current. 5.3-2 Transconductance. 5.4 Recess Depth. 5.4-1 Drain source current. 5.4-2 Transconductance. 5.4-3 Recess depth and threshold voltage (V <sub>th</sub> ). 5.5 Further Analysis. 5.5-1 Concept of virtual gate. 5.5-2 Resistance. 5.5-3 IV-Curve Modeling for Gate Recessed GaN/AlGaN HFET. 5.5-4 Breakdown voltage and recess depth. 5.6 Temperature Treatment. 5.7 HF- Characterization.  6 Summary.  Appendix A Layer structure of the samples. Appendix B Layout of HFET devices. Appendix C Lithographic process details.                                                                                                            |              |                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -            | · ·                                    |     |

| App                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | pendix C     | Lithographic process details           | 77  |

| Api                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |                                        |     |

| 4.4-1 Ohmic Contacts. 4.4-1.1 Annealing and ohmic behavior. 4.4-2 Schottky contacts and Schottky barrier. 4.4-2.1 Physics of Schottky barrier. 4.5 Recessed Gates Technology 4.5-1 T-gates.  5 Device Characterization of Gate Recessed HFET 5.1 V (1) Characteristics of gate recessed GaN/AlGaN HFETs. 5.2 Source drain spacing. 5.2-1 Drain source current. 5.2-2 Transconductance. 5.3 Recess spacing. 5.3-1 Drain source current. 5.3-2 Transconductance. 5.4 Recess Depth. 5.4-1 Drain source current. 5.4-2 Transconductance. 5.4-3 Recess depth and threshold voltage (V <sub>th</sub> ). 5.5 Further Analysis. 5.5-1 Concept of virtual gate. 5.5-2 Resistance. 5.5-3 IV-Curve Modeling for Gate Recessed GaN/AlGaN HFET. 5.5-4 Breakdown voltage and recess depth. 5.6 Temperature Treatment. 5.7 HF- Characterization.                                                                                                                                         |              |                                        |     |

| 4.4-1.1 Annealing and ohmic behavior.  4.4-2 Schottky contacts and Schottky barrier.  4.4-2.1 Physics of Schottky barrier.  4.5 Recessed Gates Technology.  4.5-1 T-gates.  5 Device Characterization of Gate Recessed HFET.  5.1 V (I) Characteristics of gate recessed GaN/AlGaN HFETs.  5.2 Source drain spacing.  5.2-1 Drain source current.  5.2-2 Transconductance.  5.3 Recess spacing.  5.3-1 Drain source current.  5.3-2 Transconductance.  5.4 Recess Depth.  5.4-1 Drain source current.  5.4-2 Transconductance.  5.4-3 Recess depth and threshold voltage (V <sub>th</sub> ).  5.5 Further Analysis.  5.5-1 Concept of virtual gate.  5.5-2 Resistance.  5.5-3 IV-Curve Modeling for Gate Recessed GaN/AlGaN HFET.  5.5-4 Breakdown voltage and recess depth.  5.6 Temperature Treatment.  5.7 HF- Characterization.  6 Summary.  Appendix A Layer structure of the samples.  Appendix B Layout of HFET devices.  Appendix C Lithographic process details. |              |                                        |     |

| 1 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 41113        |                                        | 711 |

# Chapter 1

# Introduction

Gallium Nitride (GaN), a wide band gap semiconductor, gained importance as Heterostructure Field Effect Transistors (HFET) in the early 90s. The fabrication of first HFET [1.1] opened a door for tremendous research over GaN FETs. Currently GaAs/AlGaAs Modulation Doped FETs (MODFET) are utilized with limitations in high power applications. The reason for such limitation is poor physical and electrical properties concerning to GaAs. But now a day GaN with astonishing features compared to GaAs for high power, electrical and optoelectrical devices is a hot topic of research. The reason is based on its interesting physical properties like thermal stability, high breakdown voltage, chemical inertness and electrical properties as well as a property of wide band gap which plays an important role in blue Lasers and devices with low noise. GaN High Electron Mobility Transistors (HEMTs) and MODFETs are important electrical devices for high speed electronics.

With the technological advent to control layer thickness in crystal growth by Metal Organic Vapor Phase Epitaxy (MOVPE) and Molecular Beam Epitaxy (MBE), HFET emerged with new horizons. Structures with different layers are grown and characterized. Group III-Nitride devices are highly promising for numerous applications. For the optical/display applications, LASERs and light emitting diodes (in the visible and UV emission range) are used [1.4, 1.5]. On the other hand

the electrical properties of gallium nitride are being utilized in order to fabricate the electrical devices that provide high performance e.g., field effect transistors working at high temperature, high frequencies or high power. Talking about field effect transistors grown over different substrates, gate recess technology is indeed important to have better control over the channel, higher modulation speed, etc. but, off course, it is a very difficult process step which needs high precision. Gate recessed HFETs are useful to reduce pinch off voltage and the gate leakage current of the device.

In this thesis "<u>Technology and Physics of gate recessed GaN/AlGaN HFETs</u>" some geometrical aspects of recess and gates are investigated. Additionally some problems of the recess technology e.g. etching defects, the control of recess etching depths, misalignments of recess will be discussed.

This thesis is divided into the following chapters,

Chapter 2 is mainly concerned with some of the most important physical properties of III-nitrides. An overview of different types of FET based on GaN is given in Chapter 3. The theoretical models which are used in this thesis are also illustrated.

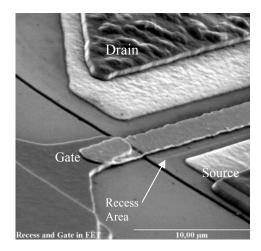

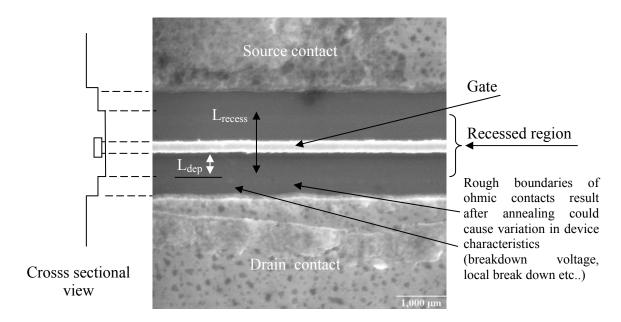

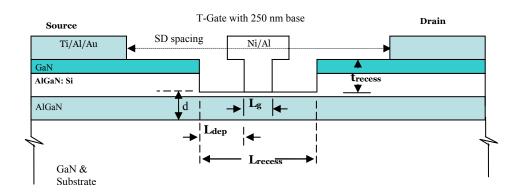

Chapter 4 introduces the technology which is used to fabricate recessed gate GaN/AlGaN HFETs. A *recessed gate* is formed by etching the surface down and then deposition of gate metals in this region. Theoretically it is a way to improve control over the channel [1.3]. Etching is done with Electron Cyclotron Resonance-Reactive Ion Etching (ECR-RIE). Optical and e-beam Lithography is also discussed here.

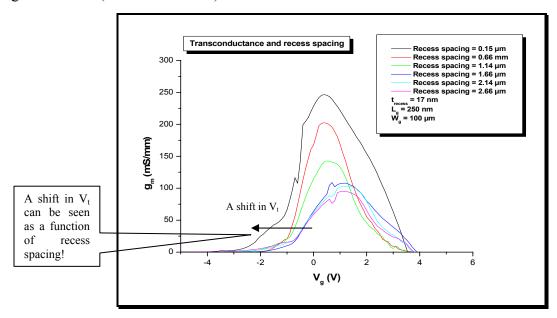

Chapter 5 presents the results and discussion of realized recessed gate HFETs. Here basically characterization is done as a function of recess spacing ( $L_{\rm g}$ ), recess depth ( $t_{\rm recess}$ ), and source drain spacing. Transconductance, drain currents and source resistance are important parameters in transistor characteristics. HFETs with recessed gate fabricated, show good channel control as the transconductance is as high as 220 mS/mm with 250 nm T-gate and a shift in the pinch off voltage could be seen.

A detailed epitaxial layer structure and transistor layout is given in appendixes with process technology and instruments used.

# Chapter 2

# **Group-III Nitrides**

Gallium Nitride is a promising semiconductor for optical, electrical and opto-electrical applications because of its advantageous properties such as large energy bandgap, good thermal and chemical stability, and physical hardness.

## 2.1 -MATERIAL PROPERTIES —

#### 2.1-1 Crystal Structure

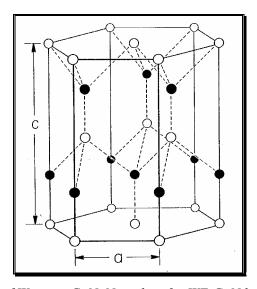

Group III Nitrides are usually found in Wurtzite (WZ), zinc blende and rock salt configurations. At ambient conditions, the thermodynamically stable structure is Wurtzite for bulk AlN, GaN, and InN and zinc blende for BN. The wurtzite structure has a hexagonal unit cell and thus two lattice constants, c and a shown in Fig. 2.1. The hexagonal unit cell contains 6 atoms of each type. The wurtzite structure consists of two interpenetrating hexagonal closed packed (HCP) sub lattices, each of one type of atom, offset along the c-axis by 5/8 of the cell height c.

**Fig. 2.1** Crystal structure of Wurtzite GaN. Note that, for WZ-GaN lattice parameters (a and c) are  $3.1892\pm0.0009$  Å and  $5.1850\pm0.0005$ Å respectively. [2.1]

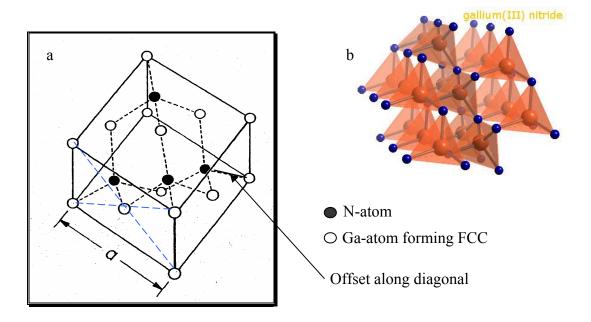

The zinc blende structure has a unit cell, containing four group III elements and four nitrogen elements Fig. 2.2a. The position of atoms within the unit cell is identical to the diamond crystal structure. Both structures consist of two interpenetrating face centered cubic (FCC) sub lattices, offset by one quarter of distance along a body diagonal. Each atom in the structure may be viewed as positioned at the center of a tetrahedron with its four neighbors defining the four corners of a tetrahedron (see Fig. 2.2b)

**Fig. 2.2** Crystal structure of a Zincblende configuration of GaN. (a) FCC unit cell. (b) View of tetrahedron structures of GaN in which each fourth atom (Ga) is shared with the second tetrahedron.

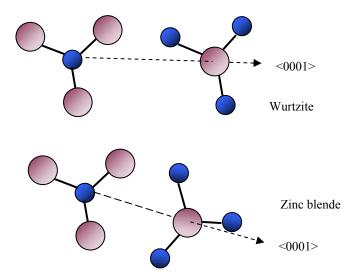

The WZ and zincblende structures are similar. In both cases, each group III atom (Al, Ga, In) is coordinated by four nitrogen atoms; conversely, each nitrogen atom is coordinated by four group III atoms. The main difference between these two structures is in the stacking sequence of closest packed diatomic planes. For WZ, the stacking sequence of (0001) planes is in <0001> direction and for zinc blende the stacking sequence of (111) planes is in <111> direction. The difference in both structures can be seen by viewing along a chemical bond in the <111> or <0001> (c-axis) direction: the second nearest neighbors are staggered in zinc blende crystal but are eclipsed in the WZ (Fig 2.3). All group III-Nitrogen bond lengths are equivalent in the zinc blende structures but there are slightly differing III-Nitrogen bond lengths in the wurtzite structures. [2.2]

**Fig. 2.3** A comparison of bonds between closed packed planes for the crystal structures. In the WZ there is an eclipsed bond configuration while in the zinc blende the bond configuration is staggered.[2.2]

#### 2.2 ELECTRICAL PROPERTIES -

#### 2.2-1 Polarization

It is now widely recognized that built in electric fields due to polarization-induced charges play an important role in the electrical and optical properties of Nitride heterostructures grown in [0001] orientation. These fields also provide a source of a 2-dimensional electron gas in AlGaN/GaN heterostructures. In HFETs, the understanding and controlling of the source of electrons is important for the optimization of their performance.

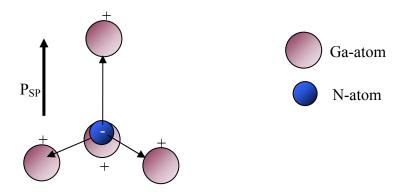

#### 2.2-1.1 Spontaneous Polarization

Due to strong electronegativity of Nitrogen (3) compared to Al (1.5), Ga (1.6) and In (1.7) the binding electron is attracted towards N in III- Nitrides. This results in deformation of regular tetrahedral structure as the c/a becomes smaller than that of an ideal tetrahedral one (c/a = 1.633). So we experience a spontaneous polarization without applying external electric field. The coefficient of spontaneous polarization can be determined theoretically from [2.3].

For AlGaN the spontaneous polarization is [2.4],

$$P_{SP} = (-0.052x - 0.0029) \left[ \frac{C}{m^2} \right]$$

(2.1)

Where x is the aluminium concentration. These field polarizations are compensated by the inner free electrons but for a bi-layer (two materials) system, there will be a local surface charge [2.5].

$$\Delta P = P_{SP}^2 - P_{SP}^1 = \sigma \tag{2.2}$$

$\sigma$  is surface charge density at the interface of the two systems with polarization  $P_{sp}^{-1}$  and  $P_{sp}^{-2}$  respectively.

Fig. 2.4 Spontaneous polarization in GaN

#### 2.2-1.2 Piezoelectric Polarization

This is due to mechanical stress in a crystal. In AlGaN the lattice constant  $a_0$ , is smaller than that of GaN, therefore GaN experiences a tensile stress (if a heterostructure is made from GaN and AlGaN), changing the bond angles and lattice constants from the non-stressed or stress free values. The piezoelectric polarization in the direction of c-plane is given by [2.4]

$$P_{PE} = 2 \frac{a - a_0}{a_0} (e_{31} - e_{33} \frac{c_{13}}{c_{33}})$$

Strain experienced in the bilayer system with substrate lattice constant  $a_0$  and cover lattice constant  $a$ .

Where a is the lattice constant in the strained case and  $a_0$  is the relaxed lattice constants. The piezoelectric coefficients  $e_{ij}$  and elastic constants  $c_{ij}$  can be determined from the table of constants. With the polarization effects, surface states and the density of 2DEG at interface can be increased or decreased [2.7], [2.8].

#### 2.3 GROWTH OF GaN LAYERS —

The high melting temperatures and dissociation pressures are the main obstacles in obtaining large single crystals of III-N compounds, which can serve as substrates for the homoepitaxial growth (when a material is grown epitaxial on a substrate of the same material). Therefore, III-V films have been grown heteroepitaxially (if the layer and the substrate are different materials, like GaN on SiC, GaN on Sapphire, GaN on Si) on a number of substrates [2.9], [2.20-23] which match more or less close to the lattice constants and thermal expansion coefficient of III-V nitrides. [2.10].

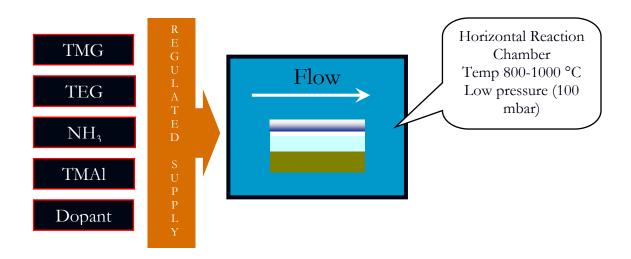

Recent technology named Metal Organic Vapor Phase Epitaxy (MOVPE) is used to grow GaN layers (GaN, AlGaN or doped AlGaN) over substrate of Sapphire (Al<sub>2</sub>O<sub>3</sub>). Fig. 2.5 shows a schematic representation for the process of crystal growth.

**Fig. 2.5** A schematic diagram of MOVPE for GaN layer growth.

In Fig. 2.5 the components (elements) of III-N semiconductor are in the form of gases transported to the substrate in the reaction chamber. Ammonia (NH<sub>3</sub>) with carrier gasses like H<sub>2</sub> or N<sub>2</sub> is injected into the Reactor. Group III elements are fed into the reactor in the form of metal organic compounds like Tri Methyl Gallium TMG [(CH<sub>3</sub>)<sub>3</sub>Ga] or Tri Ethyl Gallium TEG [(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>Ga]. At a high temperature (800-1000 °C) [2.11], [2.12] in the reaction chamber, metal organic compound reacts with the N<sub>2</sub> to form a layer of GaN over sapphire substrate.

With MOVPE a very thin (tens of nanometers) GaN or AlN low-temperature *buffer layer* is grown between the substrate and epitaxial layer in order to

- Reduce the lattice and thermal mismatch.

- To promote nucleation sites for the layers grown over the substrate.

- The buffer layer decreases interfacial free energy, permitting two-dimensional growth of the III-N layer.

- The most important development is the discovery that AlN and GaN buffers lead to significant improvements in surface morphology and the electrical properties of the films [2.13].

### **2.3-1** Sapphire (Al<sub>2</sub>O<sub>3</sub>)

Sapphire was a first standard substrate on which GaN was epitaxially grown and remains the most frequently used substrate for GaN epitaxial growth so far [2.9],[2.23], mostly due to its low price, the availability of large-area crystal of good quality and its transparent nature.

For device application the structural quality of the epitaxial films is very important, since dislocations, stacking faults and other extended defects may significantly reduce carrier life times and consequently device efficiency. Defects originate due to large thermal mismatch between the nitrides and their substrate materials, most epitaxial nitride films are subject to some degree of strain, which is introduced during the post cooling. Stacking faults are a common form of a strain relaxation in face-centered cubic crystals. The most seen defect represents dislocations, which are formed in the epitaxial layer to reduce the lattice mismatch and the strain of postgrowth cooling. These dislocations are also a result of thermal expansion mismatch that is propagated through all layers [2.10].

# 2.3-2 Doping with Si

Controlled n-type conductivity in GaN is generally achieved by Si doping. Si substitutes Ga atoms in the lattice, providing a loosely bounded electron. The ionization energy of the Si level (temperature dependent) in GaN was reported approx. 27 meV [2.14], [2.15] and 12-17 meV as measured by Hall Effect [2.16]. The solubility of Si in GaN is high, of the order of  $10^{20}$  cm  $^{-3}$ . Therefore, Si is suitable for III-Nitrides doping and most frequently used [2.10].

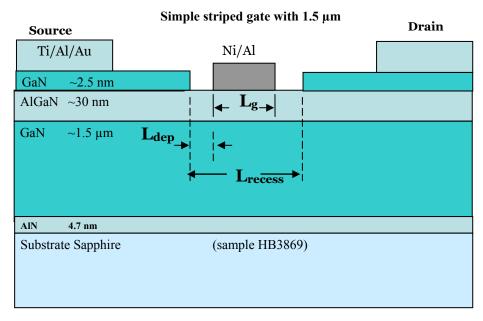

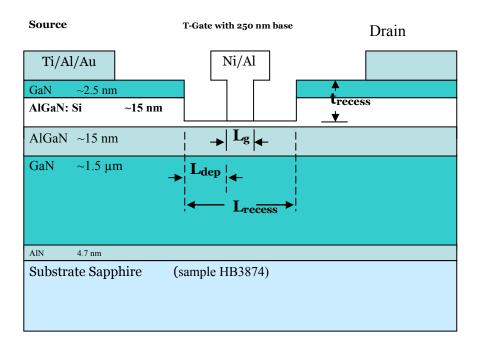

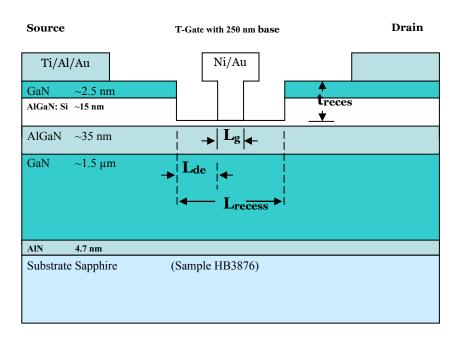

The thicknesses of Si doped AlGaN spacer layers of samples we used to fabricate HFET/MODFET are given in Tab. [2.1] and the layer structure is shown in appendix A.

| Sample         | Doping | Thickness of Doped AlGaN layer (≈ nm) | Thickness of<br>AlGaN layer<br>(≈ nm) |

|----------------|--------|---------------------------------------|---------------------------------------|

| HB3869 b, c, d | -      | -                                     | -                                     |

| HB3874         | Si     | 15                                    | 15                                    |

| HB3876         | Si     | 15                                    | 35                                    |

| HB3877         | Si     | 5                                     | 45                                    |

**Table 2.1** *Samples and doped layer thickness.*

# 2.4 GaN AND OTHER III-Nitrides .

Table (2.2, 2.3, and 2.4) shows some useful information regarding to GaN and other III-Nitrides. GaN is a mostly favored semiconductor as its promising properties are suitable for both electrical (FETs, BJTs) and optoelectrical device (LD, LEDs). The use of GaN is due to its wide band gap, high electron velocity and high break down voltages.

| Properties of GaN    |                         |                              |

|----------------------|-------------------------|------------------------------|

| Wurtzitic polytype   |                         |                              |

| Band gap             | 3.39 eV at 300K         | 3.50 eV at 1.6K              |

| Lattice constants    | a = 3.189 Å             | c =5.185 Å                   |

| Thermal expansion    | $5.59 \times 10^{-6}/K$ | $3.17 \times 10^{-6}$ /K     |

| Thermal conductivity | 1.3 W/cmK               |                              |

| Index of refraction  | n (1eV) = 2.33          | n(3.38) = 2.67               |

| Dielectric constants | $\varepsilon_0 = 10$    | $\varepsilon_{\infty} = 5.5$ |

| Zinc blende polytype |                         |                              |

| Band gap energy      | 3.2-3.3 eV at 300K      |                              |

| Lattice constant     | a = 4.52                |                              |

| Index of refraction  | n (3eV) = 2.9           |                              |

**Tab. 2.2** Properties of GaN, source: [2.10]

The breakdown voltage for GaN is > 70 V, compared to that of GaAs 30V [2.19]. The saturation velocity of carriers is nearly  $2x10^7$  cm/sec which is higher than that of GaAs [2.17]. Another interesting feature of GaN/AlGaN over GaAs/AlGaAs system is the large band gap discontinuity (discussed in chapter 3).

| <b>Properties of AlN</b> |                           |                                      |

|--------------------------|---------------------------|--------------------------------------|

| Wurtzitic polytype       |                           |                                      |

| Band gap                 | 6.2 eV at 300K            | 6.28 eV at 5K                        |

| Lattice constants        | a = 3.112 Å, c = 4.982  Å |                                      |

| Thermal expansion        | $4.2 \times 10^{-6}$ /K   | $5.3 \times 10^{-6} / \text{K}$      |

| Thermal conductivity     | 2 W/cmK                   |                                      |

| Dielectric constants     | $\varepsilon_0 = 8.5$     | $\varepsilon_{\infty} = 4.68 - 4.84$ |

| Zincblendee polytype     |                           |                                      |

| Band gap energy          | 5.11 eV at 300K theory    |                                      |

| Lattice constant         | a = 4.38  Å               |                                      |

**Tab.2.3** Properties of AlN; source [2.10]

| Properties of InN    |                         |                                 |

|----------------------|-------------------------|---------------------------------|

| Wurtzitic polytype   |                         |                                 |

| Band gap             | 1.89 eV at 300K         | _                               |

| Lattice constants    | a = 3.548Å              | c = 760 Å                       |

| Thermal expansion    | $4.2 \times 10^{-6}$ /K | $5.3 \times 10^{-6} / \text{K}$ |

| Thermal conductivity | 2 W/cmK                 |                                 |

| Dielectric constants | $\epsilon_0 = 15.3$     | $\varepsilon_{\infty} = 8.4$    |

| Zincblendee polytype |                         |                                 |

| Band gap energy      | 2.2 eV at 300K theory   |                                 |

| Lattice constant     | a = 4.98  Å             |                                 |

**Tab. 2.4** Properties of InN; source [2.10]

Impressive progress in the development of GaN/AlGaN materials and devices for high power, high temperature application was obtained during the past few years. Record microwave power of 6.8 W/mm, as well as high temperature and low noise performance of GaN/AlGaN HFET have been demonstrated [2.18].

# Chapter 3

# GaN FETs

A *Field Effect Transistor* is an important device in electrical application. It is worthy to mention that a FET as a uni-polar device and there is only one type of carrier in the conducting channel. Off course, this enhances the mobility of the carriers and efficiency of the structure compared to a bipolar transistor. The reason is manifold, like recombination of holes and electrons, inter scattering and diffusion of carriers, etc...

## 3.1- FAMILY OF GaN FETs —

Because it is easy to grow vertical structure for FET using GaN, we see following types of FETs using gallium nitride.

**Fig. 3.1:** Family of FET which could be fabricated using Gallium Nitride.

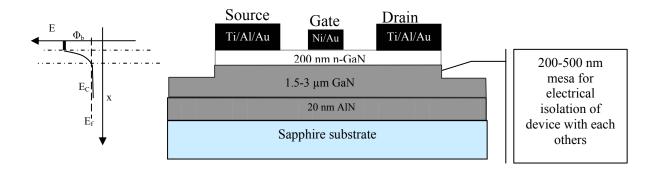

#### **3.1-1 MESFET**

Fig. 3.2 shows a typical n-channel MESFET-Structure. The name, **Me**tal **S**emiconductor **FET** is given because *a metallic gate is directly deposited on the surface of semiconductor*. The n-channel is from 200- 600 nm thick, Si-doped and it is modulated by the gate contact (by the barrier potential  $\Phi_b$  that creates depletion region of Schottky diode) which is typically Pt/Au or Ni/Au. The carrier concentration in the channel is of the order of  $10^{17}$  cm<sup>-3</sup>. The first field effect transistor from GaN was a MESFET from M. A. Khan. [1.1]

**Fig. 3.2:** A Schematic diagram for GaN MESFET. Note that mesa is necessary for all structure fabrication. Ohmic contacts and gate is directly metallized over the surface of semiconductor. At the left side a conduction band diagram for MESFET is shown.

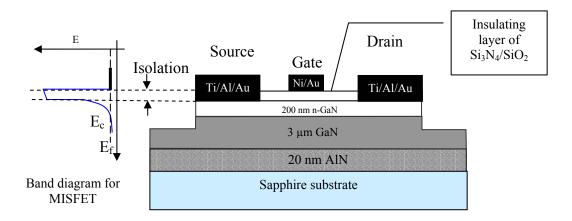

#### **3.1-2 MISFET**

*Metal Insulator Semiconductor FET*, shown in Fig.3.3 an insulator layer (usually silicon nitride or silicon oxide) is used to make the gate contact. It is necessary to reduce the injection of carrier through the gate barrier. Metal Oxide Semiconductor FET (MOSFET) is a good example of MISFET as metal oxides beneath the gate play an important role of insulation.

**Fig. 3.3:** Schematic diagram of MISFET. Note that only ohmic contacts are metallized over the surface of semiconductor where as gate contact is isolated by oxide layers.

In Fig. 3.3 a band diagram for MISFET is shown. The conduction band moves towards  $E_{\rm f}$  or crosses it in enhancement mode, with the applied gate voltage and determines the flow of current (carriers) through the active channel of the transistor.

#### 3.1-3 HEMTs and MODFETs

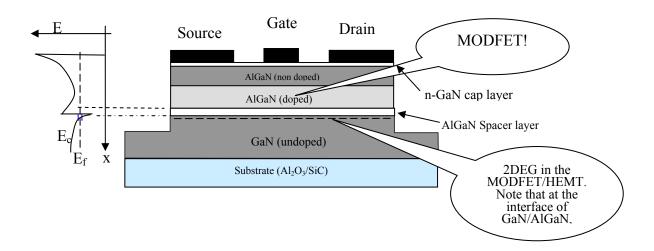

A class of Heterostructure FETs (HFETs) named High Electron Mobility Transistor (HEMT) is obtained when the channel layer is doped to spatially separates ionized donors form the electrons in the 2DEG, leading to enhanced channel mobility [3.2] Fig. 3.4. The coulomb interaction between electrons and donors in n+ AlGaN layer is reduced resulting higher mobility of the physically separated electrons. At present the maximum mobility recorded is nearly 1700 cm<sup>2</sup>/Vsec with carrier density  $1 \times 10^{13} / cm^2$  [3.3] for the samples grown by MOVPE.

**Fig. 3.4** Layer structure for GaN MODFET/HEMT. In a sense HEMT is also called PI-HEMT as there is polarization induction.

Modulation-doped Transistor (MODFET) is another kind of field effect transistor that can be grown on GaN. As described above, the semiconductor layer needs to be doped with n-type impurities to generate more electrons in the layer. However, this procedure causes the electrons to slow down because they end up colliding with the impurities residing in the same region that were used to generate them in the first place. MODFET is a smart device to resolve this contradiction because in the MODFET the electrons are additionally separated in a confinement layer e.g. InGaN layer with high mobility.

A MODFET accomplishes this by use of high mobility electrons generated using the *hetero-junction* of a thin doped AlGaN layer or a thin InGaN layer and a GaN layer. The electrons generated in AlGaN drop completely into the next GaN layer to form a depleted AlGaN layer, because the hetero-junction created by different band-gap material forms a steep canyon in the

GaN side where the electrons can move quickly without colliding with any impurities. (For the details of 2DEG see section 3.2.)

The advantage of the GaN/AlGaN system is in the availability of more band gap discontinuity. This leads to higher mobility and also provides a dense 2DEG (> 10<sup>13</sup> cm<sup>-2</sup>) because of the availability of more density of states [1.3], compared to band gap discontinuity of GaAs/AlGaAs system that gives only 10<sup>12</sup> cm<sup>-2</sup> carriers. Real spatially transferring of hot electrons from channel to barrier is negligible for GaN systems. Injection from the gate contact is also reduced by the larger Schottky barrier height. Formation of 2DEG in GaN/AlGaN interface is due to electron affinity and bandgap discontinuity. AlGaN is wider in bandgap (lower electron affinity) compared to the bandgap of GaN (high electron affinity). See more details in next section.

# 3.2 HETERO STRUCTURE GaN/Al<sub>x</sub>Ga<sub>1-x</sub>N FET \_

A Hetero Structure is a structure grown with semiconductors of different energy band gaps. Using nice compromising features of GaN and AlGaN for 2DEG (two dimensional Electron Gas at the interface of GaN/AlGaN interface as already discussed in chapter 2), High electron mobility transistor can be fabricated.

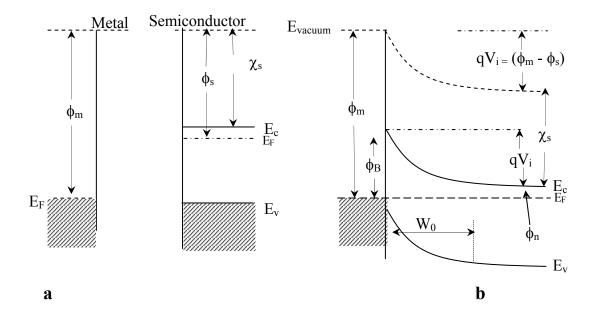

# 3.2-1 Theoretical background

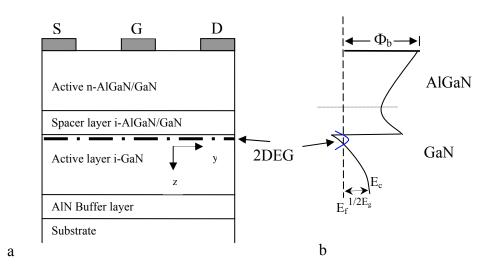

GaN and AlGaN are two different semiconductors as differing in their band gaps. GaN/Al<sub>x</sub>Ga<sub>1-x</sub>N Heterostructure is grown as Wurtzite AlGaN layer over Wurtzite GaN substrate. The type I band alignment (in which the discontinuities conduction band and valance band are at same **k**) between AlGaN and GaN has been shown to form a potential well and a Two Dimensional Electron Gas (2DEG) at the heterointerface [1.3], [3.4]. When these materials are brought into contact, thermal equilibrium requires alignment of their respective Fermi levels (E<sub>f</sub>). This induces conduction (E<sub>c</sub>) and valence (E<sub>v</sub>) band bending in both the AlGaN and GaN layers and can cause the GaN conduction band at the interface to drop below E<sub>f</sub>. Since ( for n- type material) the Fermi level can be viewed as an electrochemical potential for electrons, majority electrons will accumulate in the narrow gap material just below the heterointerface to fill the *quasi triangular potential well* between E<sub>c</sub> and E<sub>f</sub>.

The electrons are confined by a distance shorter than their deBroglie wavelength, causing quantization of allowed energy levels in the potential well. Depending on the structures, there may be more than one allowed energy levels below E<sub>f</sub>, although only the lowest allowed level

will be substantially populated at room temperature. With the heterointerface on one side and a potential barrier on the other, electrons in the 2DEG are only free to move along the plane of the interface. A thin 'Sheet' of negatively charged (electrons) is formed responsible for the electrical transport. Fig. 3.5 a, b shows a schematic layer structure and band diagram with triangular quantum well formation.

### 3.2-2 The Two-Dimensional Electron Gas (2DEG) in GaN/AlGaN

In order to obtain the 2DEG concentration in the triangular QW at the interface of GaN/AlGaN, Poisson's Eq (3.1) and Schrödinger's Eq (3.2) are solved self consistently [1.3].

$$\frac{d^2 E_c}{dz^2} = -8\pi n(z) \tag{3.1}$$

$$-\frac{\hbar^2}{2m^*} \frac{d^2 \psi_i}{dz^2} + E_c(z) \psi_i = E_i \psi_i$$

(3.2)

Where z is the coordinate in a direction perpendicular to the i-AlGaN/i-GaN heterostructure with origin at the i-AlGaN/i-GaN heterointerface, positive values in the i-GaN active layer, and negative values are in i-AlGaN layer. As shown in Fig 3.5b the  $E_c(z)$  is the conduction band position,  $\Psi_i$  is the wave function of the electron,  $m^*$  is the effective mass of the electron in GaN, n(z) is the electronic concentration at point z, h is the Planck's constant.

**Fig. 3.5:** (a) The layer sequence in GaN/AlGaN HFETs. (b) Quantum Well formation at the band edge discontinuity, and creation of 2DEG.

A simultaneous solution of Eq. (3.1) and Eq. (3.2) thus gives the concentration of electrons n(z) at various locations along the width of the triangular Quantum well. When unintentionally doped, GaN shows a donor implanted behavior. However, these donors don't affect the 2DEG concentration, because most of them are not ionized at the interface, owing to the Fermi level lying above the conduction band. If, for the sake of convenience, the origin of the energy is chosen at the edge of conduction band level of GaN at the GaN/Al<sub>x</sub>Ga<sub>1-x</sub>N interface, and if the unintentional donor concentration in the bulk of GaN is accounted for, then the first boundary condition may be written as

$$E_c(z \to +\infty) = E_F + \frac{1}{2}E_g \tag{3.3a}$$

which is plotted in Fig. 3.5b

or

$$E_c(z \to +\infty) = E_F + k_B T \ln\left(\frac{N_c}{N_d}\right)$$

(3.3b)

Where  $N_c$  is the effective electron density of states,  $N_d$  is the donor impurity density in the bulk GaN,  $E_f$  is the Fermi level, and  $E_g$  is the energy band gap, all for GaN. Note that for practical situation, this boundary condition affects the 2DEG concentration. The two other conditions are

$$\left(\frac{dE_c}{dz}\right)_{z=0} = 8\pi n_{2D} \tag{3.4a}$$

$$\psi_i(z \to \pm \infty) = 0 \tag{3.4b}$$

Where  $n_{2D}$  is the 2DEG. The value of the electron concentration at the point z, n(z) is given as,

$$n(z) = \sum_{i=1}^{\infty} N_i |\psi_i(z)|^2$$

(3.5)

Where,

$$N_i = \frac{k_B T}{2\pi} \ln \left[ 1 + \exp\left(\frac{E_F - E_i}{k_B T}\right) \right]$$

(3.6)

Equations (3.1) and (3.2) are solved using trial wave function of the form

$$\phi_n(z) = (z + z_0)e^{-b_n z}$$

For  $z \ge 0$  (3.7a)

$$\phi_n(z) = z_0 e^{\left(\frac{1}{z_0} - b_n\right)z}$$

For  $z < 0$  (3.7b)

The wave function is obtained by employing Eq.(3.8) with  $C_v^i$  as a variation parameter

$$\psi_i = \sum_{\nu=1}^{\infty} C_{\nu}^i \phi_{\nu} \tag{3.8}$$

Although theoretically the summation series of Eq.(3.5) and (3.8) can extend up to infinity, a value of v = 10 appears to be sufficient for self-consistency. This calculation, for a given 2DEG concentration, yields the conduction band, the Fermi level (also the quasi Fermi level of the electrons), the energy levels of the electrons in the triangular well, and the electronic concentration as a function of z. The drain current and the transconductance can also be calculated [1.3]. One can extract from this mathematical model the information about the 2DEG as a function of gate voltage, the transconductance with different thickness of Al<sub>x</sub>Ga<sub>1-x</sub>N layer, where x is the concentration of Aluminum. For example, the concentration of 2DEG is simulated as a function the thickness of AlGaN layer. These supporting calculations could also be a base to explain the characteristics of a gate recessed HFETs, where the thickness of AlGaN is varied only under the gate electrode.

# 3.3 GATE RECESSED GaN/AlGaN HFET MODELLING -

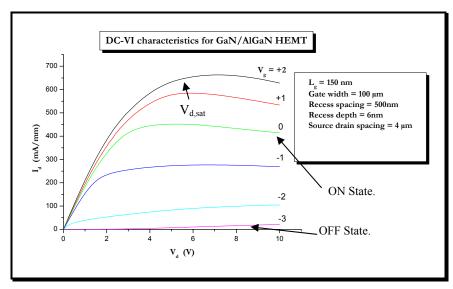

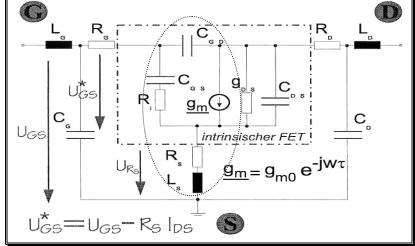

Field effect transistor (FETs) involve transport of one type of carriers only, which are electrons in most cases, as the electron mobility is higher than that of holes. In a HFET ( as discussed in chapter 2) the 2DEG plays a key role for electrical charge transport where the charge flows in a channel parallel to the device surface between two ohmic source and drain contacts. A third electrode (gate) is metallized in between of the source and drain contacts. It modulates the 2DEG density by field effect. The source is grounded and the drain-source voltage is called  $V_{ds}$ , while the gate-source voltage is called  $V_{gs}$ .  $I_{ds}$  are the current between source and drain and  $I_{gs}$  is the current entering into the gate. The ability of the gate to modulate the current flow between source and drain is expressed by the transconductance ( $g_m = \frac{\partial I_{ds}}{\partial V_{gs}}$  at constant  $V_{ds}$ ). Fig. 3.7 shows an equivalent circuit with the most important electrical components to describe a FET.

#### 3.3-1 DC Characteristics

An idealized FET is characterized as follows, in order to give a large current in the On-state, the density, mobility, and saturation velocity of the electrons in the channel are large, and the parasitic resistances i.e.  $R_s$  are small. To reduce the currents in the OFF-state, the gate has to sustain electric fields without leaking. In the following discussion *capital alphabets in subscripts* are used to show parameters when transistor is characterized using DC values and small subscripts for AC/HF characterization.

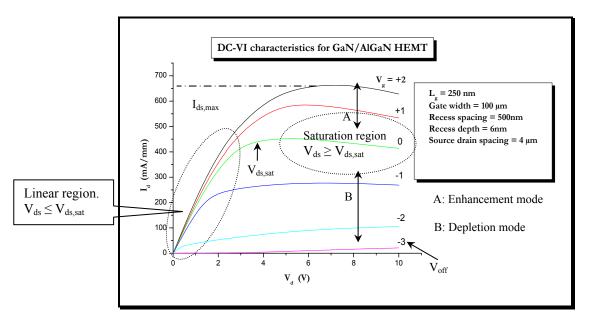

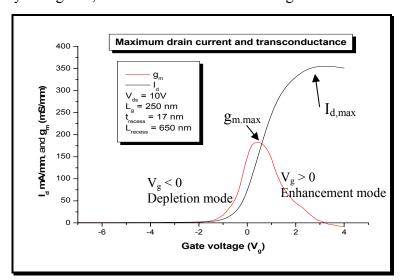

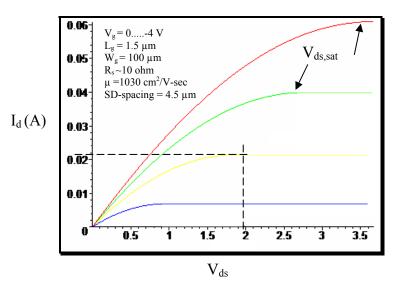

**Fig. 3.6:** *I(V)* characteristics of a gate recessed FET working in enhancement and depletion modes.

Fig. 3.6 is a plot of drain current as a function of source drain voltage. The picture shows the DC characteristics of FET in depletion and enhancement mode. A drain current, ( $I_D$ ) flows in the channel when drain source voltage ( $V_{DS}$ ) is applied and under a gate voltage ( $V_G$ ). For small drain source voltages (given for linear region of drift velocity  $v_D = \mu E$ ) the drain current is calculated [5.1] as given in Eq. 3.9

$$I_{D} = \left(\frac{W}{L_{G}}\right) \mu C_{G} \left[ (V_{G} - V_{th}) V_{DS} - \frac{V_{DS}^{2}}{2} \right]$$

for  $V_{DS} \le V_{DS,sat}$  (3.9)

And for saturation region, e.g.  $v_D = v_{sat}$

$$I_{D} = \frac{1}{2} \left( \frac{W}{L_{G}} \right) \mu C_{G} (V_{G} - V_{th})^{2} \text{ for } V_{DS} > V_{DS,sat}$$

(3.10)

Where W is the gate width,  $C_G$  is Gate capacitance, and  $V_{th}$  is threshold voltage as shown in Fig. 3.6. With different gate voltages we can drive the transistor either in enhancement mode or in depletion mode.

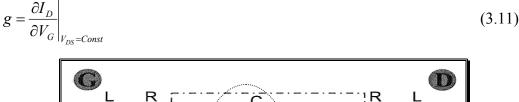

The measurement of  $I_d$  is done at a given gate voltage. The transconductance of an FET is defined as follows.

**Fig. 3.7:** FET equivalent circuit. Note intrinsic transconductance is different compared to the extrinsic transconductance. FET is a two port network.

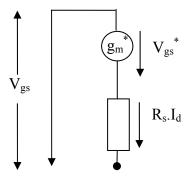

It is interesting to note that parasitic resistance affects the characteristics of HFET. Therefore, a very important motivation for a gate recess is the reduction of the effective gate-source voltage by the voltage drop on  $R_s$  (feedback) induced by  $I_d$ . The source resistance is the most important (see chapter 5). The intrinsic transconductance of FET can be derived from Fig.3.7 (more simplified circuit is shown in Fig. 3.8) and a simple circuit calculation as,

**Fig. 3.8:** An equivalent circuit for the FET with intrinsic voltage source  $V_{gs}^*$  and connected source resistance.

$$V_{gs} = V_{gs}^* + I_{ds} \cdot R_s \equiv \frac{I_{ds}}{g_m^*} + I_{ds} \cdot R_s \equiv I_{ds} \left( \frac{1}{g_m^*} + R_s \right)$$

(3.12)

For

$$g_m = \frac{I_{ds}}{V_{gs}}$$

we have  $g_m^{-1} = \frac{1}{g_m^*} + R_s$

or  $g_m = \frac{g_m^*}{1 + R \cdot g_m^*}$  (3.13)

Where  $g^*_m$  is intrinsic transconductance and  $R_s$  is source resistance as shown in the Fig.3.7 and Fig. 3.8. From Eq. 3.13, we see that the intrinsic transconductance is of FET is always larger than its extrinsic transconductance.

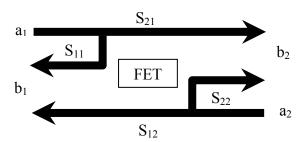

#### 3.3-2 HF Characteristics

As discussed in [3.5], a HFET is like a two port network. The input signal is applied to the gate and source, and output is measured between the drain and source. The scattering parameters (Sparameters) are used for HF characterization of a FET. Fig. 3.9 shows a schematic representation of two port network of a FET.

**Fig. 3.9:** S-parameters with incident waves  $(a_1, a_2)$  and reflected waves  $(b_1, b_2)$  for a device to be tested.

The linear equations describing the two-port network are given as [3.6].

$$b_1 = S_{11}.a_1 + S_{12}.a_2$$

i.e, reflected + transmitted

$b_2 = S_{21}.a_1 + S_{22}.a_2$  i.e, transmitted + reflected (3.14)

Where  $a_1$  and  $a_2$  are amplitudes of the incident waves (flow into) and are independent variables.  $b_1$  and  $b_2$  amplitudes of the reflected and transmitted waves (flow out of the network  $S_{ij}$ ) and are dependent variables. We can write,

$$S_{ij} = \frac{b_i}{a_j} \bigg|_{a_j = 0} \tag{3.15}$$

The coefficients of  $S_{ij}$  are called scattering parameters and are defined as follows (Eq. 3.16)

$$S_{11} = \frac{b_1}{a_1}\Big|_{a_{2=0}}$$

Forward reflection coefficient

$S_{12} = \frac{b_1}{a_2}\Big|_{a_{1=0}}$  Backward transmission coefficient

$S_{21} = \frac{b_2}{a_1}\Big|_{a_{2=0}}$  Forward transmission coefficient

$S_{22} = \frac{b_2}{a_2}\Big|_{a_{1,0}}$  Backward reflection coefficient

As an FET is not only a passive two port network, but shows also amplification of transmitted signals and it is characterized by the maximum available gain (MAG) which is the power gain of a two port network when both the input and the output are conjugate impedance matched and it is the highest gain that can be achieved by lossless tuning on the input and output ports. (That means  $b_2 = \max$ , and  $b_1 = \min$ , so that all power is in one direction)

$$MAG = \left| \frac{S_{21}}{S_{12}} \right| \left( k \pm \sqrt{k^2 - 1} \right)$$

(3.17)

MUG, maximum unilateral gain, another parameter, which is the gain that would exist if the output-to-input feed back in the transistor is cancelled by another feedback network, with both ports conjugate matched. [5.10]

$$MUG = \frac{1}{2} \frac{\left| \frac{S_{21}}{S_{12}} - 1 \right|^2}{k \left| \frac{S_{21}}{S_{12}} \right| - R_e \frac{S_{21}}{S_{12}}}$$

(3.18)

Where k, the stability factor, is defined below

$$k = \frac{1 + \left| \det S \right|^2 - \left| S_{11} \right|^2 - \left| S_{22} \right|^2}{2 \left| S_{12} S_{21} \right|} > 1 \quad \text{and } \det S = S_{11} S_{22} - S_{12} S_{21}$$

(3.19)

In the HF measurements another factor  $h_{21}$ , which is the forward current gain with the output shorted circuit. It is related to the S matrix as,

$$h_{21} = \frac{-2S_{21}}{1 - S_{11} + S_{22} - \det S} \tag{3.20}$$

It is related to transit frequency such that the gain  $h_{21}$  approaches to one for  $f = f_t$ . The unity short-circuit current-gain frequency,  $f_t$  is defined as [3.5] in Eq. 3.21

$$h_{21}|_{f=f_t} = 1$$

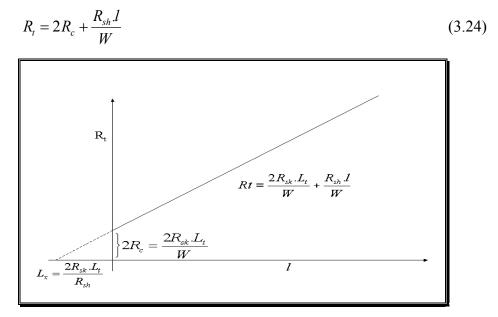

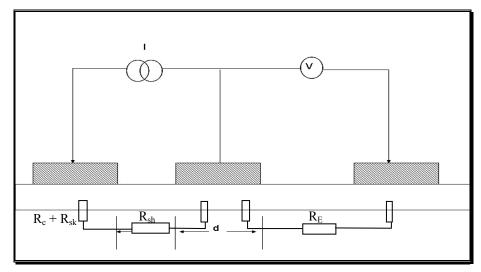

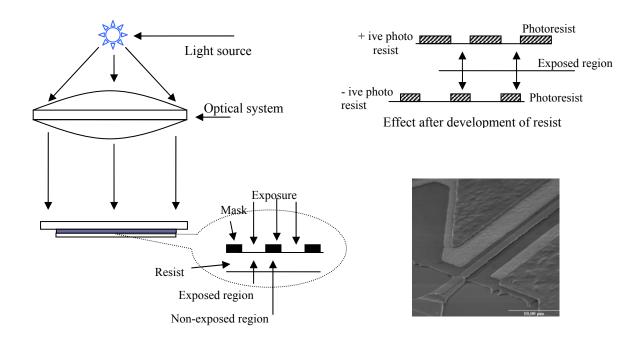

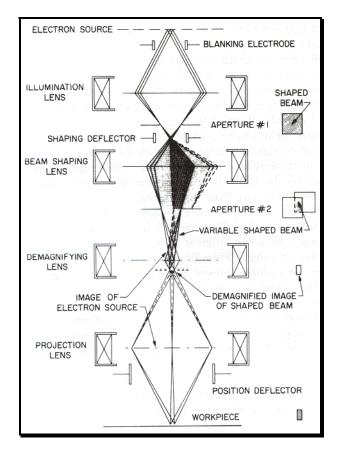

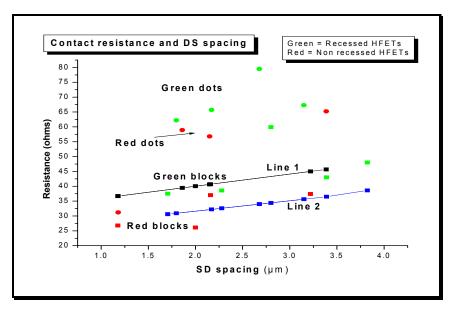

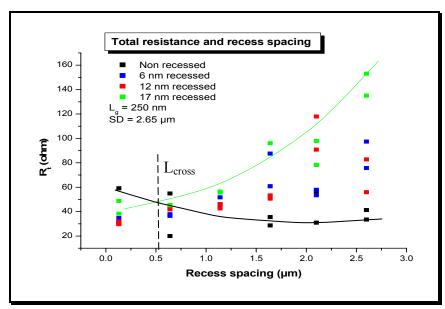

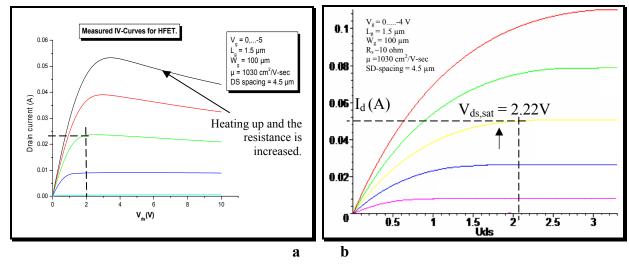

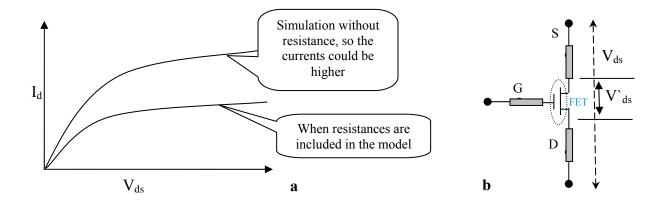

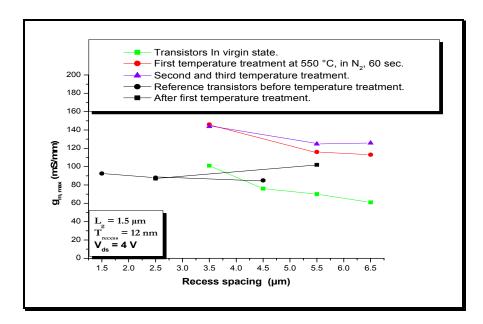

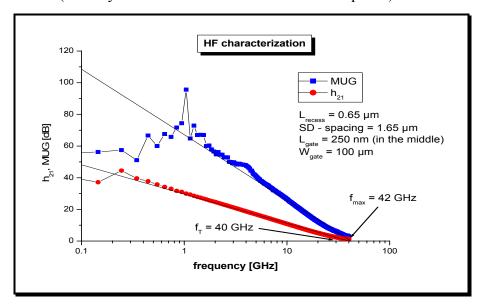

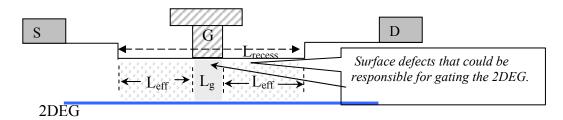

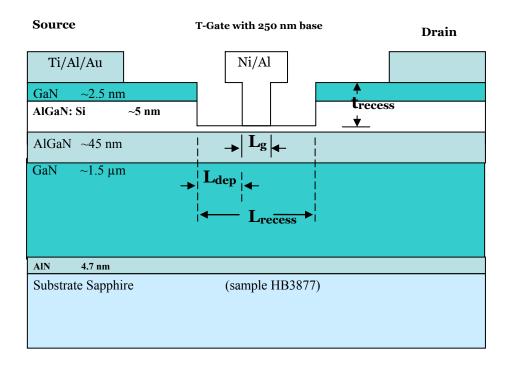

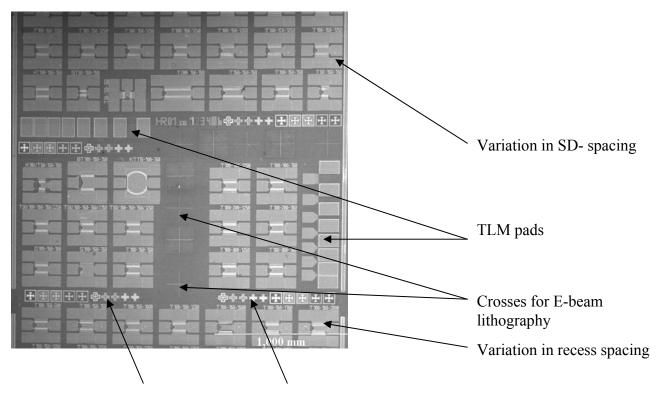

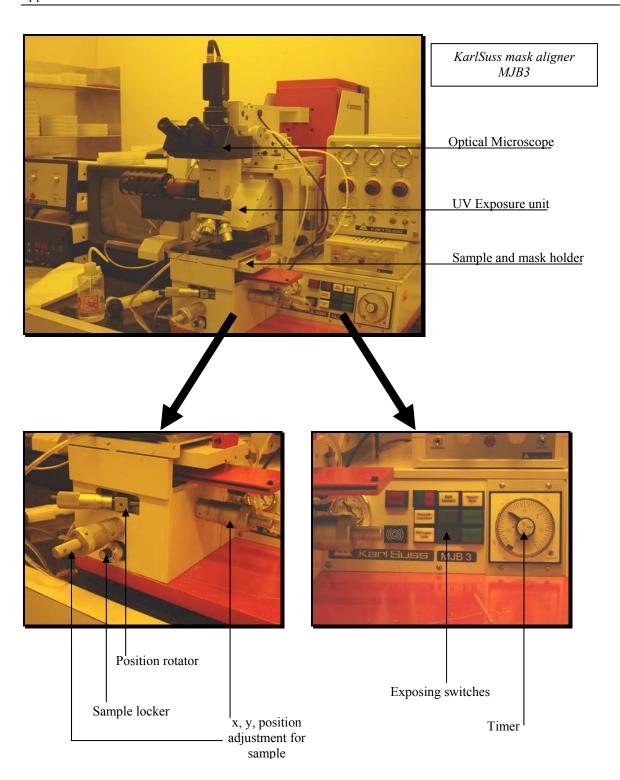

$\Leftrightarrow$   $20\log(h_{21})|_{f=f_t} = 0$  (3.21)