#### Institute of Software Technology

#### Department of Programming Languages and Compilers

University of Stuttgart Universitätsstraße 38 D–70569 Stuttgart

Master Thesis Nr. 3554

# Language Independent Modelling of Parallelism

Nazmul Alam

Course of Study: INFOTECH

**Examiner:** Prof.Dr.rer.nat./Harvard Univ. Erhard Plödereder

**Supervisor:** Dipl.-Inf. Mikhail Prokharau

Commenced: August 23, 2013

Completed: May 09, 2014

**CR-Classification:** C(1.1,1.2,4b),D(1.3b,2.5f,3.4f,3.4g,4.1,4.2d,4.7e,4.8)

# Abstract

To make programs work in parallel contexts without any hazards, programming languages require changes to their structures and compilers. One of the most complicated parts is memory models and how programming languages deal with memory interactions. Different processors provide a different level of safety guarantees (i.e. ARM provides relaxed whereas Intel provides strong guarantees). On the other hand, different programming languages provide different structures for parallel computation and have individual protocols for communicating with parallel processes. Unfortunately, no specific choice is best in all situations. This thesis focuses on memory models of various programming languages and processors highlighting some positive and negative features from the point of view of programmability, performance and portability. In order to give some evidence of problems and performance bottlenecks, some small programs have been developed. This thesis also concentrates on incorrect behaviors, especially on data race conditions in programs, providing suggestions on how to avoid them. Also, some litmus tests on systems featuring different vendors' processors were performed to observe data races on each system. Nowadays programming paradigms also became a big issue. Some of the programming styles support observable non-determinism which is the main reason for incorrect behavior in programs. In this thesis, different programming models are also discussed based on the current state of the available research. Also, the imperative and functional paradigms in different contexts are compared. Finally, a mathematical problem was solved using two different paradigms to provide some practical evidence of the theory.

# Acknowledgments

I would like to express my gratitude to Prof. Dr. rer. nat./Harvard Univ. Erhard Plödereder for creating the opportunity and allowing me to do my master's thesis at the Department of Programming Languages and Compilers, Institute of Software Technology, University of Stuttgart.

Moreover, I would like to express the deepest appreciation to my supervisor Dipl.-Inf. Mikhail Prokharau who has continuously supervised, suggested and corrected different problems with his great enthusiasm and passion throughout my whole thesis work. He also provided guidance and productive discussions for structuring of my thesis work. Furthermore, he also supported me with vital suggestions of corrections all the way through the writing process of my thesis.

In addition, my sincere appreciation to (Dipl.-Ing. FH) Klemens Krause and Ms. Kornelia Kuhle for their continuous support. They ensured a flawless working environment for this thesis by instant support and provision of tools, information and required access permissions to the server and computer lab.

I would like to thank the Department of Programming Languages and Compilers, especially those members who provided some constructive suggestions after my intermediate presentation of this thesis, as well as my colleagues who were doing their master's thesis in this department at the same time with me.

Finally, and most importantly, I would like to thank Miss Mounomita Nasreen for her support, encouragement and always having a warm-hearted ear. Without her unconditional love, I could not have completed this study. I would like to give special thanks to my parents for their faith in me and allowing me to be as ambitious as I wanted. It was under their watchful eye that I gained so much drive and the ability to tackle challenges head on. I also thank all of my friends for their support in all the ways during my master's study.

# Contents

| 1. | Basi | ic Conc | epts                                                                             | 1  |

|----|------|---------|----------------------------------------------------------------------------------|----|

|    | 1.1  | Defini  | tions                                                                            | 1  |

|    |      | 1.1.1   | Memory Model                                                                     | 1  |

|    |      | 1.1.2   | Atomic Variable                                                                  | 1  |

|    |      | 1.1.3   | Data Race                                                                        | 1  |

|    |      | 1.1.4   | Sequential Consistency (SC)                                                      | 1  |

|    |      | 1.1.5   | Sequential Consistency for Data Race Free Programs (SC-DRF) $$                   | 2  |

|    | 1.2  | Why '   | Threads?                                                                         | 2  |

|    | 1.3  | Trans   | formations & Optimizations                                                       | 3  |

|    | 1.4  | Comp    | iler Optimizations                                                               | 3  |

|    | 1.5  | Proces  | ssor Out-of-Order (OoO) execution                                                | 4  |

| 2. | Vari | ous Pa  | rallelisation Concepts                                                           | 7  |

|    | 2.1  | Types   | of parallel computers                                                            | 7  |

|    |      | 2.1.1   | Flynn's Classical Taxonomy of computer architectures [45]                        | 8  |

|    |      | 2.1.2   | According to memory arrangement and communication among Processing Elements(PEs) | 11 |

|    |      | 2.1.3   | According to Interconnection Networks                                            | 16 |

|    |      | 2.1.4   | Cache Coherency [37]                                                             | 16 |

|    | 2.2  | Efficie | ency analysis of multiprocessor architectures [40]                               | 18 |

|    | 2.3  | Predic  | etability analysis of multiprocessor architectures                               | 20 |

|    | 2.4  | Types   | of Parallel Programming Models                                                   | 21 |

|    |      | 2.4.1   | Instruction Level Parallelism (ILP)                                              | 21 |

|    |      | 2.4.2   | Thread Level / Task Level Parallelism (TLP)                                      | 22 |

|    |      | 2.4.3   | Data Level Parallelism (DLP)                                                     | 22 |

|    | 2.5  | Tests   | and Analysis                                                                     | 23 |

viii Contents

| 3. | Inco  | rrect Be | ehaviors                                                | 25 |

|----|-------|----------|---------------------------------------------------------|----|

|    | 3.1   | Comm     | on incorrect behaviors in a concurrent program          | 25 |

|    | 3.2   | Factor   | s that are commonly responsible for incorrect behaviors | 26 |

|    |       | 3.2.1    | Race condition                                          | 26 |

|    |       | 3.2.2    | Deadlock                                                | 28 |

|    |       | 3.2.3    | Livelock                                                | 28 |

|    |       | 3.2.4    | Starvation                                              | 28 |

|    | 3.3   | Way to   | o avoid/eliminate/prevent incorrect behaviors           | 29 |

|    |       | 3.3.1    | Race Condition                                          | 29 |

|    |       | 3.3.2    | Deadlock                                                | 33 |

|    |       | 3.3.3    | Starvation                                              | 35 |

|    | 3.4   | Tests a  | and Analysis                                            | 35 |

| 4. | Inter | raction  | Between Software and Hardware                           | 39 |

|    | 4.1   | Memor    | ry Models                                               | 40 |

|    |       | 4.1.1    | Hardware Memory Models                                  | 40 |

|    |       | 4.1.2    | Software Memory Models                                  | 47 |

|    | 4.2   | Real-ti  | me systems                                              | 60 |

|    |       | 4.2.1    | Predictability in real-time systems                     | 60 |

| Contents   | ix |

|------------|----|

| Contection | 1. |

| 5. | Prog | grammi  | ing Paradigms                                          | <br>. 63 |

|----|------|---------|--------------------------------------------------------|----------|

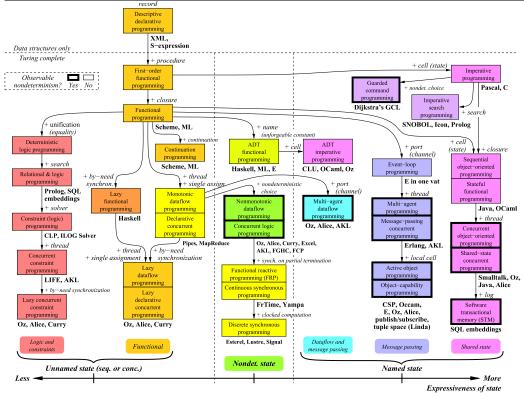

|    | 5.1  | Introd  | duction                                                | <br>. 63 |

|    | 5.2  | Types   | s of Programming Paradigms                             | <br>. 65 |

|    |      | 5.2.1   | Imperative Paradigm                                    | <br>. 65 |

|    |      | 5.2.2   | Functional Paradigm                                    | <br>. 66 |

|    |      | 5.2.3   | Logic Paradigm                                         | <br>. 66 |

|    |      | 5.2.4   | Object Oriented Paradigm                               | <br>. 66 |

|    | 5.3  | A com   | mparison between Functional and Imperative Programming | <br>. 66 |

|    | 5.4  | Test a  | and Analysis                                           | <br>. 67 |

|    | ~    |         |                                                        | 0.0      |

| 6. | Con  | clusion | and Future Work                                        | <br>. 69 |

|    | 6.1  | Conclu  | lusion                                                 | <br>. 69 |

|    | 6.2  | Future  | re Work                                                | <br>. 70 |

x Contents

# List of Figures

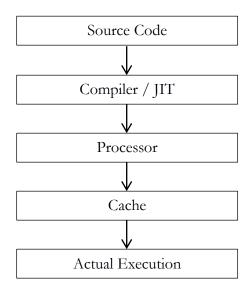

| 1.1  | Phase of execution [9]                                | 3  |

|------|-------------------------------------------------------|----|

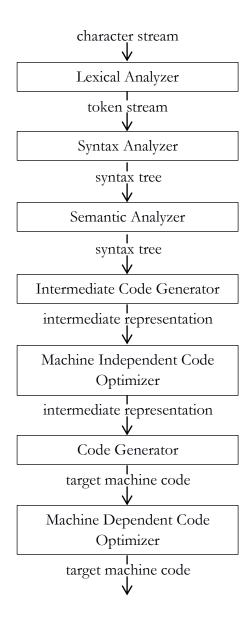

| 1.2  | Phases of compiler translation [9]                    | 4  |

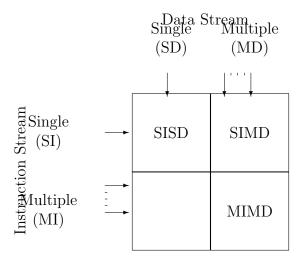

| 2.1  | Flynn's Classical Taxonomy of computer architectures  | 8  |

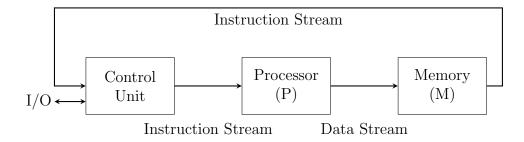

| 2.2  | SISD Architecture                                     | 9  |

| 2.3  | MIMD Architecture                                     | 11 |

| 2.4  | Shared Memory Architecture                            | 11 |

| 2.5  | UMA Shared Memory Architecture                        | 12 |

| 2.6  | NUMA Shared Memory Architecture                       | 13 |

| 2.7  | Distributed Processor Computer Architecture           | 14 |

| 2.8  | Hybrid Processor Computer Architecture                | 15 |

| 2.9  | Bus Snooping Protocol architectures                   | 17 |

| 2.10 | Directory-Based Protocol architectures                | 18 |

| 2.11 | Instruction level parallelism example                 | 22 |

| 3.1  | Compiler Optimization may introduce unexpected result | 27 |

| 4.1  | A state diagram of a computer start-up process        | 39 |

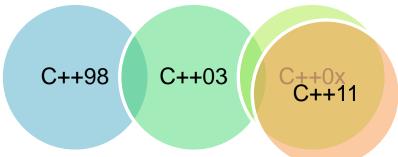

| 4.2  | C++ Development History                               | 52 |

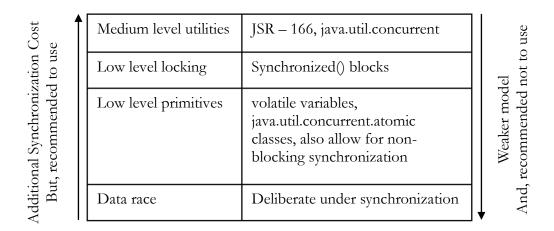

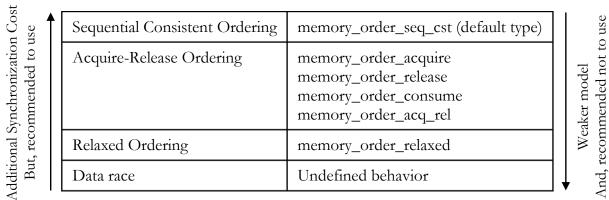

| 4.3  | Hierarchical Table of C++ Synchronization Mechanisms  | 53 |

| 4.4  | Scheme of a task with a call point                    | 57 |

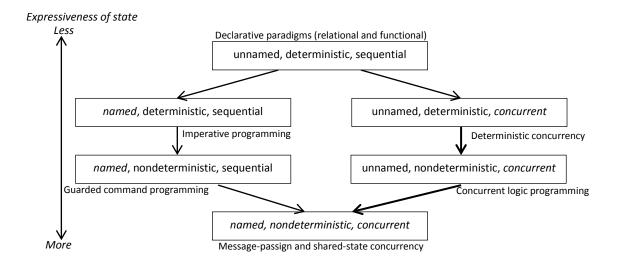

| 5.1  | Taxonomy of programming paradigms [104]               | 64 |

| 5.2  | Different levels of support for state[104]            | 65 |

# List of Tables

| 2.1 | A SISD instruction sequence                                               | 8  |

|-----|---------------------------------------------------------------------------|----|

| 2.2 | A SIMD instruction sequence                                               | Ĝ  |

| 2.3 | A MISD instruction sequence                                               | 10 |

| 2.4 | A MIMD instruction sequence                                               | 10 |

| 3.1 | Deterministic concurrent state in different programming paradigms $[104]$ | 29 |

| 3.2 | Test Machine Specification                                                | 36 |

| 3.3 | Number of data races detected on different machines                       | 37 |

| 4.1 | A Violation of Sequential Consistency                                     | 49 |

| 4.2 | Hierarchical table of Java synchronization mechanisms                     | 50 |

| 4.3 | Java synchronization mechanisms performance table                         | 50 |

| 4.4 | An Out of Thin Air Result                                                 | 51 |

| 4.5 | Happens-Before relations example                                          | 51 |

| 4.6 | Ada mutual exclusion mechanism performance table                          | 58 |

| 47  | Ada explicit processor allocation check                                   | 50 |

# 1. Basic Concepts

# 1.1 Definitions

## 1.1.1 Memory Model

A memory model is a specification of the memory system for hardware or software system that will appear to programs. It eliminates the gap between the expected behavior and the actual behavior supported by the system [6].

#### 1.1.2 Atomic Variable

A thread concurrently reading the object from shared memory will see the old value or the new value, never see any value in-between. In order to ensure this, an atomic type variable may have stricter alignment than a plain type variable [100].

## 1.1.3 Data Race

A **Data race** occurs when multiple threads want to access same shared memory location during the execution, and at least one of them tries to modify that location. It may introduce unpredictability, unexpected results that are often hard to detect[76].

## 1.1.4 Sequential Consistency (SC)

A multiprocessor based parallel system is called sequentially consistent if, the result of any execution is the same as if all processors executed their operations in some sequential order and the operation result for each processors appears in this sequence the way the program specified the order[67].

# 1.1.5 Sequential Consistency for Data Race Free Programs (SC-DRF)

If a program does not allow data races and synchronizes with only the following options-

- Sequentially consistent atomic, and

- Use acquire and release semantics for Lock and Unlock operations respectively.

-then the program follows sequential consistency order of execution, i.e. the result for any execution appears as if the program executed sequentially interleaving its actions letting all read operations see the preceding value stored to the location in this interleaving sequence [4].

# 1.2 Why Threads?

A thread executes as a small sequence of program instructions. An operating system scheduler can manage it independently.

Threads can change the timing of operations, but threads should not change the semantics of a program. For this reason, thread programming is always a smart solution for program performance issues[54]. Following are some examples where programmer might use threads:

- Lengthy processing: when an operating system is performing some long mathematical calculation, it cannot process any more messages. As a result, the display driver is unable to update data.

- Background processing: Some tasks may need to perform continuously but might not if time is critical. There could be some task which needs to perform continuously with a fixed time interval.

- IO work: DMA (Direct Memory Access) operation or I/O to a memory disc can have unpredictable delays. The programmer confirmed that I/O latency of thread operations does not delay unrelated parts of the application.

Some real-time operations sometimes have limited execution, however, some operations experience unpredictable delay or CPU hogging. In thread programming, tasks with unavailable resources or low priority wait in a waiting-state until resources become available and then are scheduled for execution. Threads also make use of multi-core processor systems in a multi-threaded program. It is not expected that a multi-core processing system will be used by only one application with one thread. Threads also do efficient time-sharing, programmers can make sure that all threads have fair allocation of CPU time by using threads and process priority[54].

# 1.3 Transformations & Optimizations

A processor does not execute the program that a programmer wrote. Because, there are some other factors that come in between program code and processor execution[9], i.e. Compiler Optimizations, Processor Out of Order (OoO) execution, Cache Coherency.

Fig. 1.1: Phase of execution [9]

Usually a programmer cannot tell on which level the optimization happens. The only thing programmers care about is that the program is synchronized correctly.

# 1.4 Compiler Optimizations

A compiler knows all memory operations in a thread and exactly what they will do, including data dependencies and how to be conservative enough in the face of possible aliasing[9]. On the other hand, a compiler does not know which memory locations are "mutable shared" variables and could change asynchronously due to memory operations in other threads and how to be conservative enough in the face of possible sharing.

Fig. 1.2: Phases of compiler translation [9]

# 1.5 Processor Out-of-Order (OoO) execution

In pipelined programming, cycles are sometimes wasted for stalling[9]. In order to reduce the number of stalls in the execution, processor needs to execute the program instructions out of order.

In an out-of-order execution the system processor tries to find the instructions in the instruction stream that are independent of the current (stalled) instruction and can be executed in parallel with it, i.e. the x64 family of processors supports out-of-order execution.

An obstacle is that processors become more complex rapidly as the degree of "Out-of-Orderness" is increased [9].

# 2. Various Parallelisation Concepts

The concept of parallel computing is to solve a large computation problem with multiple processing units simultaneously by dividing the problem into small tasks assigned to all processing units. There are several different types of parallel computer architectures and parallel computing styles. Although parallel computing was confined to scientific applications, nowadays it is coming into commercial and business applications to provide high performance computing capabilities for decision support, data mining and risk management applications.

There are several different types of parallel computers and parallel computing (programming) styles that exist from different points of view.

# 2.1 Types of parallel computers

Parallel computer architectures can be categorized from different points of view, some of them are as follows:

- 1. Flynn's Classical Taxonomy of computer architectures [45].

- i Single Instruction, Single Data stream (SISD)

- ii Single Instruction, Multiple Data stream (SIMD)

- iii Multiple Instruction, Single Data stream (MISD)

- iv Multiple Instruction, Multiple Data stream (MIMD)

- 2. Classification according to memory arrangement and communication among Processing Elements (PEs).

- i Shared Memory Multiprocessor

- Uniform Memory Access (UMA)

- Nonuniform Memory Access (NUMA)

- Cache-only Memory Architecture (COMA)

- ii Message passing multiprocessors / Distributed memory multiprocessors.

- iii Hybrid distributed model.

- 3. According to Interconnection Network.

# 2.1.1 Flynn's Classical Taxonomy of computer architectures [45]

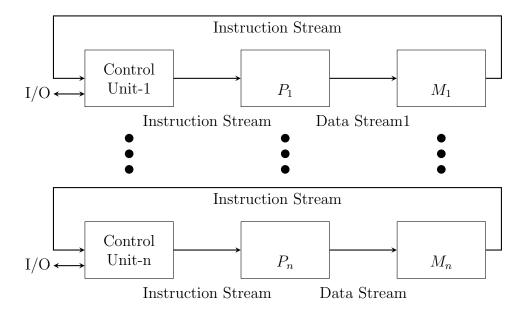

Since 1966, one of the most popular used classifications is Flynn's classical Taxonomy. It distinguishes multi-processor computer architectures with respect to two independent dimensions: **Instruction Stream** and **Data Streams**: **single** or **multiple**[45].

Fig. 2.1: Flynn's Classical Taxonomy of computer architectures

# 2.1.1.1 Single Instruction, Single Data stream (SISD):

SISD is the standard for uniprocessor computers. CPU can execute only one instruction stream in one clock cycle. So, only one data stream is being used as input during any one clock cycle. The result of execution is deterministic [45].

| Load X    |              |

|-----------|--------------|

| Load Y    |              |

| Z = X + Y | eA           |

| store Z   | Lim          |

| X = Y * 2 |              |

| store X   | $\downarrow$ |

Tab. 2.1: A SISD instruction sequence

Fig. 2.2: SISD Architecture.

## 2.1.1.2 Single Instruction, Multiple Data stream (SIMD):

SIMD is a parallel computer architecture. Processors execute the same instruction stream with different data, e.g., graphical machine (RAW to JPEG conversion). This taxonomy is best suitable for solving specially categorized problems characterized by a high degree of regularity, such as graphics/image format conversion. This execution is always synchronous and deterministic [45].

There are two varieties of SIMD:

- i Processor arrays: connection machines ILLIAC IV, CM-2, MasPar MP-1 & MP-2.

- ii Vector pipelines: Fujitsu VP, Cray X-MP, IBM 9000, Y-MP & C90, NEC SX-2, Hitachi S820, ETA 10

| Prev. Inst.        | Prev. Inst.        | Prev. Inst.        |              |

|--------------------|--------------------|--------------------|--------------|

| Load X(1)          | Load X(2)          | Load X(n)          | A            |

| Load Y(1)          | Load Y(2)          | Load Y(n)          | me           |

| Z(1) = X(1) * Y(1) | Z(2) = X(2) * Y(2) | Z(n) = X(n) * Y(n) | ti           |

| store Z(1)         | store Z(2)         | store Z(n)         | $\downarrow$ |

Tab. 2.2: A SIMD instruction sequence

The computer with a Graphics Processing Unit (GPU) and most modern computers employ SIMD instructions and execution units.

## 2.1.1.3 Multiple Instruction, Single Data streams (MISD):

MISD is another parallel computer architecture type. All processing units execute a single data stream independently with separate instruction streams. In real life, only few computers were built using this architecture. One of these is the experimental Carnegie-Mellon C.mmp computer (1971)[110][45].

| Prev. Inst.     | Prev. Inst.     | Prev. Inst.     |              |

|-----------------|-----------------|-----------------|--------------|

| Load X(1)       | Load X(1)       | Load X(n)       | A            |

| Z(1) = X(1) * 1 | Z(2) = X(1) * 2 | Z(n) = X(1) * m | timeA        |

| store Z(1)      | store Z(2)      | store Z(n)      | ti           |

| Next Inst.      | Next Inst.      | Next Inst.      | $\downarrow$ |

Tab. 2.3: A MISD instruction sequence

#### 2.1.1.4 Multiple Instruction, Multiple Data stream (MIMD):

This architecture is used in modern types of parallel computers. Every processor can work with a different data stream and every processor can execute a different instruction stream. Synchronous and asynchronous execution, deterministic or non-deterministic execution can co-exist on this architecture. Today's high performance computer architectures are built using this concept. Most of the commonly used personal computers and supercomputers use this architecture [45].

| Prev. Inst.        | Prev. Inst.    | Prev. Inst.     |              |

|--------------------|----------------|-----------------|--------------|

| Load X(1)          | Call funcD     | do $10 i = 1,N$ |              |

| Load Y(1)          | X = Y * Z      | alpha = W * 3   | timeA        |

| C(1) = X(1) * Y(1) | sum = X * 2    | Zeta = C(i)     | tin          |

| store Z(1)         | call sub1(i,j) | 10 continue     |              |

| Next. Inst.        | Next. Inst.    | Next Inst.      | $\downarrow$ |

Tab. 2.4: A MIMD instruction sequence

Fig. 2.3: MIMD Architecture.

Many MIMD architectures also include SIMD execution units as sub-components.

# 2.1.2 According to memory arrangement and communication among Processing Elements(PEs)

From the point of view of interconnection between processor and memory, parallel computer architectures can be classified into following categories.

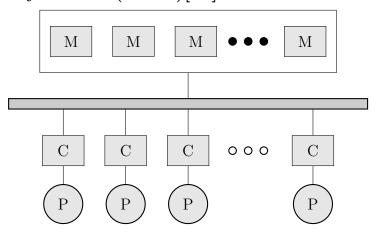

### 2.1.2.1 Shared Memory Multiprocessors[97]

Fig. 2.4: Shared Memory Architecture

In a shared memory multiprocessor architecture, all processors have equal access to the memory module and these memory modules are seen as a single address space by all processors. Each memory module stores data as well as serving to establish communication among the processors via some bus arrangement. Programming in this architecture is quite straightforward and attractive. The executable programming code and data related to the program are stored in memory for each processor to execute. There is no direct processor-to-processor communication involved in the programming process; instead communication is handled mainly via shared memory modules. Access to these memory modules can easily be controlled through appropriate programming mechanisms such as multitasking. However, this architecture suffers from a bottleneck problem when a number of processors endeavors to access global memory at the same time[97]. This limits the scalability of the system.

There are different types of shared memory architectures in existence

- Uniform Memory Access (UMA)[97]

- Nonuniform Memory Access (NUMA) [97]

- Cache-only Memory Architecture (COMA) [52]

#### Uniform Memory Access (UMA)[97]:

Fig. 2.5: UMA Shared Memory Architecture

UMA architecture is also called symmetric multiprocessor. A UMA architecture is composed of multiple processors with identical characteristics. The processors share the same main memory and IO facilities and are interconnected by some form of bus-based interconnection scheme such that the memory access time is approximately the same for all processors. The **Sun Starfire servers**[28] are an example of UMA architecture.

A subclass of UMA is called Cache Coherence UMA (CC-UMA). Cache coherence means that if one processor updated a shared global memory then all other processors should know about the newly updated values. At the hardware level, cache coherency is accomplished.

### Non-Uniform Memory Access (NUMA)[97]:

Fig. 2.6: NUMA Shared Memory Architecture

The NUMA architecture is often created by physically linking two or more UMA architectures. In NUMA architectures, the memory access time depends on the different regions of memory. Memory access across the links is slower. **Intel Nehalem**[98] and **Tukwila**[33] CPUs support NUMA. Both CPU families share a common chipset (Intel Quick Path Interconnect (QPI)) for interconnection between CPUs.

A subclass of NUMA systems is Cache Coherent NUMA (CC-NUMA) where cache coherence is maintained among the caches of various processors. The main advantage of the CC-NUMA is that it can deliver efficient performance at higher levels of parallelism than UMA architecture. The **Stanford DASH**[111] is based on the CC-NUMA architecture.

### Cache-only memory architecture (COMA)[52]:

COMA is similar to NUMA, in this architecture shared memory is divided into processor-related blocks and the memory is connected through an interconnected network. However, in this system shared memory is made of cache memory. In a COMA system data need to migrate from one processor block to another on a processor request. To migrate the data, the cache directory (D) is used for access from a remote processor. An example of COMA machine is "The Kendall Square Research's KSR-1"[111].

#### Advantages of the shared memory architecture:

- Global address space architecture provides an easy, and user-friendly programming perspective to memory.

- Due to the proximity of memory to CPUs, data sharing between tasks is uniform

#### Disadvantages of shared memory architecture:

- Primary disadvantage is the lack of scalability among CPUs and memory. Adding more CPUs can geometrically increase traffic on the shared memory-CPU path, and for a cache coherent system, geometrically increase traffic associated with cache/memory management.

- The programmer is responsible for synchronization constructs that ensure correct access to global memory.

- To design and produce large scale shared memory machines, difficulties and cost increase with the increasing number of processors.

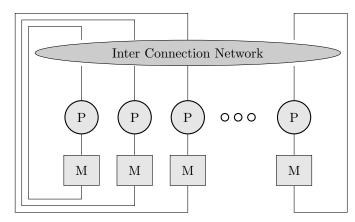

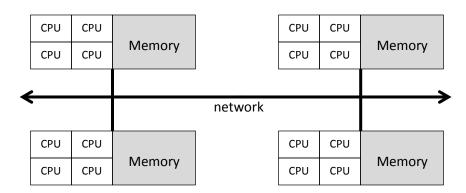

# 2.1.2.2 Message passing multiprocessors / Distributed memory multiprocessors [94]

The distributed memory multiprocessor architecture is different from shared memory architecture in that each unit of the architecture is a complete computer building block including processor, memory and I/O system. A processor can access directly attached memory. A processor can communicate with another processor in the form of I/O operations through message signaling and bus networks. Changes a processor made in its local memory have no effect on the memory of other processors. Hence, the cache coherency does not apply.

#### Advantages of the distributed memory architecture:

• Memory is scalable with the number of processors. Memory increases proportionally with increment of the number of processors.

- Each processor can access its own memory without interfering with other processors.

- Cost effective: can use commodity, off-the-shelf processors and networking.

#### Disadvantages of the distributed memory architecture:

- The programmer is responsible for many of the details associated with data communication among processors.

- Difficult to map data structures based on global memory confined to this memory organization.

- Non-uniform memory access time data residing on a remote node take longer to access than node local data.

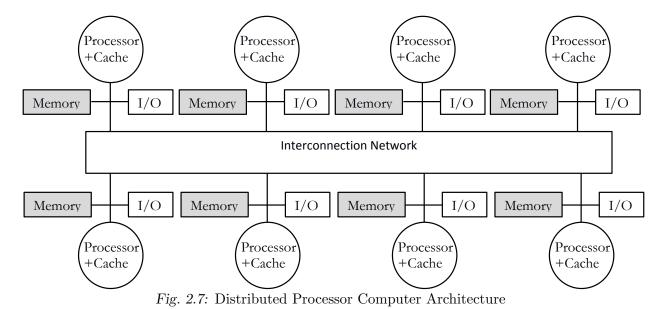

# 2.1.2.3 Hybrid distributed model[99]

The largest and fastest computer in the world employs both shared and distributed memory architectures. The shared memory components can be accessed by shared memory-CPUs and remote memory locations can be accessed through the interconnection network. Therefore, network communication is required to transfer data from one processor to a remote processor.

Fig. 2.8: Hybrid Processor Computer Architecture

#### Advantages and disadvantages of the hybrid memory architecture:

- Whatever is common to both shared and distributed memory architectures.

- The most significant advantage is it increases scalability.

- The most significant disadvantage is it increases programmer time.

## 2.1.3 According to Interconnection Networks

Parallel computers can be categorized according to the interconnection network between processors and memory.

- i Linear network

- ii A single shared bus network

- iii Multiple shared bus network

- iv Crossbar interconnection network

- v Star interconnection network

- vi Ring interconnection network

- vii Tree interconnection network

- viii Hypercube interconnection network

- ix Mesh and torus interconnection network

- x Complete graph interconnection network

- xi Switching or dynamic interconnection network

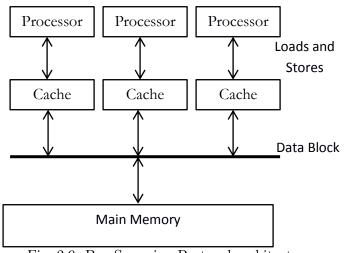

# 2.1.4 Cache Coherency [37]

In a shared memory multiprocessor architecture with each processor containing a separate cache memory, it is possible to have several copies of any single instruction operand (main memory, each processor cache). All copies for each processor should be updated to their new values with an update of a single processing unit.

Cache coherency protocol is the discipline that ensures that changes in the shared operand values are propagated throughout the system in a timely fashion.

There are three distinct levels of cache coherence:

- 1. Every write operation appears to occur instantaneously.

- 2. All processes see exactly the same sequence of changes of values for each separate operand.

- 3. Different methods may see an operand assuming different sequences of values. (This is considered non-coherent behavior.)

#### Possible solution to cache coherence problems:

- 1. No data cache memory

- Eliminating the data cache memory from a shared memory architecture could be a solution of the cache coherence problems, e.g., **Cray MTA -2** uses no data cache [10]. This reduces CPU complexity and eliminates the cache coherence problem. However, no data caching introduces performance problems [13], e.g. memory reference takes 150-170 cycles which is a much higher latency than when using a slower cache.

- 2. By software: disallow caching of shared variables[72] By disallowing cache memory to have a local copy of shared operands could be another way to avoid cache coherence problems, e.g. **Cray T3D** [81][61]. Nowadays generic programming languages are using this concept to access shared variableS exclusively, e.g. **volatile in Java**[72].

- 3. Use a cache coherence protocol

#### 2.1.4.1 Cache coherence protocols[14]

In shared memory systems of modern computers two types of cache coherence protocols are used.

#### 1. Bus Snooping Protocol [101]:

Fig. 2.9: Bus Snooping Protocol architectures

This protocol is used by bus-based and small scale interconnected shared memory systems. It relies on a common channel (or bus) connecting the processors to main memory. This protocol may be further classified into two schemes.

#### i Write Update Scheme

With this scheme processor immediately broadcasts the performed write operation on the bus; thus as other processors observe the new data being broadcast over the bus, they update their copy of the block data. This scheme creates much traffic on the bus.

#### ii Write Invalidates Scheme

In this scheme processor perform an invalidate bus transaction before writing the data, in order to ensure that it has the only valid copy of the data block.

Snooping protocols are extensively used in commercial multiprocessor systems such as **Pentium 4** and **PowerPC**.

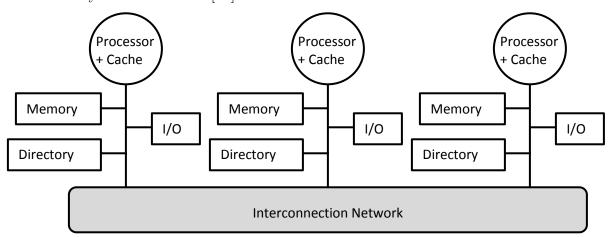

#### 2. Directory Based Protocol [69]

Fig. 2.10: Directory-Based Protocol architectures

In a directory-based system, a common directory is used for shared data to maintain the duplicate data from different caches. The directory works as a filter. To load data into its cache memory from main memory, the processor must ask for the permission. The directory either changes or updates whenever the entry is changed. The **DASH** multiprocessor system uses this protocol.

# 2.2 Efficiency analysis of multiprocessor architectures [40]

If n is a number of subtasks of a given task,  $t_s$  is the execution time of the whole task using a single processor and  $t_m$  is the time to execute the whole task on n processors, then  $t_m = t_s/n$ ; the speedup factor of a parallel system is

$$S(n) = Speedup Factors$$

$$= \frac{t_s}{t_m}$$

$$= \frac{t_s}{\frac{t_s}{n}}$$

$$= n$$

The communication overhead factor has been overlooked in the above derivation, which results in the time needed for processor to communicate and synchronize with each other. If to is the time to communication then  $t_m = (t_s/n) + t_c$ .

$$\begin{split} S(n) &= Speedup \ factor \ with \ communication \ overhead \\ &= \frac{t_s}{t_m} \\ &= \frac{t_s}{t_m} \\ &= \frac{t_s}{\frac{t_s}{n} + t_c} \\ &= \frac{n}{1 + n \times \frac{t_c}{t_s}} \end{split}$$

The efficiency  $(\eta)$  measurement of a parallel system is-

$$\eta = \frac{1}{1 + n \times \frac{t_c}{t_s}}$$

Let (f) be a fraction of the given task of a concurrent program that has to execute sequentially. The remaining part (1-f) is assumed to be divisible into concurrent subtasks executed concurrently. Now, time required to execute the task on n processors is  $t_m = ft_s + (1-f)(t_s/n)$ . The speed-up factor is now -

$$S(n) = \frac{t_s}{ft_s + (1 - f)(t_s/n) + t_c}$$

$$= \frac{nft_s + t_s - ft_s + nt_c}{nf + 1 - f + n\frac{t_c}{t_s}}$$

$$= \frac{n}{f(n-1) + 1 + n\frac{t_c}{t_s}}$$

The maximum speed-up factor under such condition is given by -

$$\lim_{n \to \infty} S(n) = \lim_{n \to \infty} \frac{n}{f(n-1) + 1 + n\frac{t_c}{t_s}}$$

$$= \frac{1}{f + \frac{t_c}{t_s}}$$

Again, the maximum speed-up factor without communication overhead is -

$$\lim_{n \to \infty} S(n) = \frac{1}{f}$$

Now, the new efficiency  $(\eta)$  is -

$$\eta(\text{with no communication overhead}) = \frac{1}{1 + n \times \frac{t_c}{t_b}}$$

$$\eta(\text{with communication overhead}) = \frac{1}{f(n-1) + 1 + n\frac{t_c}{t_s}}$$

# 2.3 Predictability analysis of multiprocessor architectures

Nowadays, multi-core processors are conquering the world to meet the demand for computational power. As computer processors are becoming more capable, new intelligent applications will emerge, such as, real-time image processing and object recognition, multiple-sensor information fusion, and online spectral analysis for state-based maintenance. Some of these applications will have hard real-time constraints, and these constraints will then have to be predictable on hardware level with respect to time. This requires a Worst Case Execution Time (WCET) analysis for the involved tasks to make the system predictable.

Estimating WCET is very hard. If the estimation is too tight for the system, it becomes possible to violate task deadlines for hard real-time systems, causes being buffer overflow or cache-misses. On the contrary, if estimation is relaxed enough the system efficiency will go down because processor idle time will increase. Moreover, the fundamental problem with the WCET analysis on multiprocessor systems is that the load on other processors is generally unknown. For a task the number of cache misses and their location in time depend on the program control flow path. This means that it is very hard to foresee where there will be bus access collisions, since this will differ from execution to execution. Furthermore, the worst-case control flow path of the task will change depending on the bus load originating from other concurrent tasks.

On the other hand, programming languages contain observable non-determinism properties, which make programs unpredictable with respect to the result of the program execution. Non-determinism is caused when a program execution is not completely determined by its specification; during execution, program can choose the next step by using the run-time scheduler. For instance, observe the following example with parallel thread T1 and T2, sharing the variable n:

```

T1: x; n = 1,000,000;

T2: y; n = 10; fori = 1 to n do r;

```

Here, there is a race condition for the global variable n. If the processor executes T1 first, the loop will iterate 10 times, if the processor executes T2 first then switches to T1 by preemption before executing the loop then the loop will iterate 1,000,000 times. Moreover, if the programs use synchronization through locks, then an imprecise analysis might even falsely detect deadlocks. For instance, the following example with parallel threads T1 and T2 using a global variable n might create deadlock of a program.

```

T1: x; lock l;

T2: y; lock l; n = 10; unlock l;

```

Way to avoid non-determinism in a concurrent language: The easiest way to avoid non-determinism is to design a language that does not support any non-determinism. However, this is unrealistic in practice, because most programming languages must allow some internal optimization to make the program more efficient. So, the problem could be solved by distinguishing non-determinism into two types. The first one is inside non-determinism, which cannot be avoided, the second is observable non-determinism, which might be avoidable.[104]

The table 3.1 on chapter 3 shows a comparison of five programming paradigms with respect to their non-deterministic properties.

# 2.4 Types of Parallel Programming Models

## 2.4.1 Instruction Level Parallelism (ILP)

Instruction Level Parallelism (ILP) [56] is a process where several instructions can execute in parallel. In pipelined processes, only one instruction per cycle can execute, but in ILP multiple instructions per cycle can execute. In these processes instructions which are not dependent on previous instruction can execute simultaneously. For example, consider the following program optimization by ILP. In this example, ILP process required 3 instruction cycles instead of 5.

```

Cycle 1: LOAD r1, (r2);

Cycle 2: ADD r5, r6, r7;

Cycle 3: SUB r4, r1, r4;

Cycle 4: MUL r8, r9, r10;

Cycle 5: STORE (r11), r4;

Cycle 7: LOAD r1, (r2);

Cycle 1: LOAD r1, (r2);

Cycle 2: SUB r4, r1, r4;

Cycle 3: STORE (r11), r4;

```

Fig. 2.11: Instruction level parallelism example

The available parallelism is limited by any sequence of instructions [106]. ILP is limited by following hazards/dependencies.

- Data Dependencies: RAW (Read After Write), WAR (Write After Read), WAW (Write After Write);

- Control Dependencies: If a program has a condition branch then until execution of this condition all later instructions must wait.

- Memory Dependencies: 100(r1) and 35(r3) may indicate the same memory location. Dependencies that flow through memory locations are difficult to detect.

## 2.4.2 Thread Level / Task Level Parallelism (TLP)

An alternative model of parallelism is Thread/Task Level Parallelism (TLP) [60] where multiple flows of executions run on a single processor. Sometimes processes wait for their resources (e.g. printer acknowledgement signal), and the processor has some idle time. In this idle time, the processor can start another independent process. To do this, a big process is divided into a few independent small chunks named threads/tasks. Each thread contains its own instruction and data. In a multiprocessor system, TLP is achieved by running different threads/tasks on a different processor with the same or different data. When a thread's resource is not available then the thread goes into a blocked state and waits until the resource is available. Once the resource becomes available afterwards, the thread goes into a waiting queue and finally executes. The thread may execute the same or different code. Different threads can communicate with each other through message passing or using shared global memory. With this method processes need an extra mechanism to synchronize with each other.

### 2.4.3 Data Level Parallelism (DLP)

In a multiprocessor system Data Level Parallelism (DLP) [70] is a method where data are distributed into different parallel computing nodes. For example in the image processing engine, different processors execute the same line of instructions with a different set of data, vector processing is also an example of DLP.

# 2.5 Tests and Analysis

To test and analyze the performance and efficiency of different parallelization techniques, it is necessary to have different hardware resources. The following section discusses the resulta of different parallelization tests taken from the currently available published research.

Case 1: Efficient Parallelization using Combined Loop and Data Transformations [77].

Usually some parts of the program consist of a loop or an array access which requires particular transformation while other parts of that program require completely different transformations. For these various transformation techniques large cache memory is required, or else, cache misses occur. To solve this problem, parallelizing compilers need to minimize the degree of internal synchronization and inter-processor communication and also need to maximize temporal and spatial locality within a program. To improve spatial locality, Cierniak and Li [30] and Kandemir et al. [58],[57] have combined non-singular loop transformations with data transformations.

The research has been done to develop a compiler heuristic MARS [21] to minimize parallelization overheads, which explore how to resolve the requirement of a conflicting loop by data transformation and vice-versa[77]. This is achieved by treating data and loop transformation in a unified manner. They used seven theorems for their compiler to develop a communication and synchronization mechanism. Finally, they combined loop and data transformation for optimization.

For testing they developed a compiler to test alternative techniques in a number of experiments on an SGi Origin 2000. Three SPECfp92 kernels: vpetst, btrtst, chotst were selected, and four different approaches tested: combined, data, loop, PFA(a commercial loop-oriented parallelizing compiler). Their performance was plotted into a graph against the number of processors used[77]. With the VPETST kernel, the combined method shows a vast performance improvement on a larger number of processors (e.g. 32). The results were 50% faster over PFA and 20% over 30% faster over loop method, and with BTRTST kernel the combined approach is a factor of 2 faster than PFA for a large number of processors. Finally, the CHOTST kernel test shows that combined, data and loop give the same result whereas PFA process is 80% slower than the other method[77].

#### Case 2: A detailed analysis of contemporary ARM and x86 Architectures [20]:

In a processor architecture design system the Instruction Set Architecture (ISA) plays a vital role in the performance, efficiency and consumption power of that processor. The development of RISC and CISC ISA began in the 1980 when the design complexity and cheap area were the primary concerns. Today, the low power ARM ISA enters into the high-performance market for desktop server PCs, while the traditional high-performance Intel x86

ISA is trying to enter into the low-power mobile device market. Thus, the question arises whether the energy efficiency is dominating the market over ISA or vice-versa.

Clark and Bhandarkar compared the VAX and MIPS ISA by comparing the Digital VAX 8700 to the M/2000 implementations [19] and summed up with "RISC as exemplified by MIPS provided a significant processor performance advantage." In 1995 another research by Bhandarkar compared the Alpha 21164 to Intel Pentium-Pro [19], this study focused on performance and concluded "the Pentium Pro processor achieves 80% to 90% of the performance of the Alpha 21164".

A detailed analysis has been done on Intel Atom and Sandybridge i7 and ARM cortex-A8 and cortex-A9 microprocessors [20]. The test used four different workloads spanning mobile, desktop INT and FP memory footprints and server computing. This test demonstrates the role of ISA on modern processors in performance and efficiency. For this test, they used Linux 2.6 LTS kernel with some minor board-specific patches and a gcc4.4 cross compiler [20]. Machine specific tuning and THUMB instructions were disabled and x86 32-bit processors were used. For the application in mobile client WebKit regression tests [50], desktop SPECCPU2006 (www.spec.org) and server Cloud Suite workload[43] were used [20].

The performance analysis from this test found a large performance gap across the four platforms, where Intel was showing high performance. Compared to A9, i7 perform 5 times to 102 times faster and compared to A8, Atom performs 2 times to 997 times faster. In cycle count comparison i7 took 2.5 times less cycle time than A9 and Atom took 1.5 times less time than the A8 processor[20]. So, finally, in Power and Energy test i7 consumed 17 to 21 times more power than the A9 processor and Atom consumed about 3 times more power than the A8 processor [20].

The result was as expected that Intel processors provide high performance but consume much power, on the other hand, ARM processors provide energy efficiency but perform comparatively slowly.

# 3. Incorrect Behaviors

In order to build compatible software for modern high performance multicore computers, programmers have to design complicated parallel software architectures to achieve performance improvement and hardware efficiency.

Several level optimizations are required for creating mainstream software applications that utilize the full power of parallel hardware. Mainstream generic programming languages like C++, Java, Ada [22]allow the non-determinism in a program to achieve maximum efficiency of the processors. The execution is called non-deterministic if, during its execution a program has to decide the next line of instruction to execute. This non-deterministic behavior may introduce bugs into the program that will cause its incorrect functionality.

# 3.1 Common incorrect behaviors in a concurrent program

There are several kinds of bug that may appear in a program [102] -

- Race condition

- Deadlock

- Livelock

- Starvation

Race Condition: A race condition affects program's correctness by changing the timing and ordering of program events [76]. More generally, some external efforts need to change the timing and ordering of the program, to produce a race condition. General examples are OS signals, hardware interrupts, context switching and memory operations on a multiprocessor system.

A **Data race** occurs when multiple threads want to access same shared memory location during the execution, and at least one of them tries to modify that location. It may introduce unpredictability and unexpected results that are often hard to detect.

Race condition usually depends on the execution order of a program that may vary on different hardware architectures. So, a program with a race condition may perform normally on particular hardware. Race conditions can only be avoided but not eliminated from the program in programming languages that allow the non-determinism.

**Deadlock:** If two or more threads wait on each other, forming a cycle that prevents all of them from making any further progress, this is called Deadlock[113]. It could be created by the programmer while trying to avoid race conditions. For example, incorrect use of synchronization condition primitives such as locks may introduce multiple threads waiting for each other. Deadlock is also possible without synchronization mechanisms; circular wait in a program can result in a deadlock.

**Starvation:** Starvation is a situation in a multi-threaded application, where single or multiple threads are delayed indefinitely or blocked permanently[3]. For example, a thread with a low priority is waiting for being scheduled, but high priority threads are executed although this lower priority thread is neither blocked nor waiting for any resources. Typically, scheduling rules and policies are the reasons for starvation in a multi-threaded program.

**Livelock:** Livelock is a situation where multiple threads depend on each other and changes of their own states result in a circular way in response to changes in the other threads. The result is none of them will complete [36].

# 3.2 Factors that are commonly responsible for incorrect behaviors

# 3.2.1 Race condition

The first and main source of race conditions in a program is observable non-deterministic[104] behavior of mainstream programming languages e.g. C++, Java. On the other hand, programming languages like Oz or Alice do not support any race conditions, because they are free of observable non-determinism.

Among the programming languages that support observable non-determinism, shared memory / variables are responsible for producing data races into programs. However, shared memory plays a vital role for communication among processors in a shared memory computer architecture. It is also possible to use message passing communication mechanisms in systems with shared memory architectures, but, performance and efficiency of those systems will fall dramatically. So, to achieve performance and efficiency at an optimum level, programmers have to use shared variables while maintaining specific rules and regulations.

To introduce a race condition into a program, concurrent access is required in a multiple threaded shared memory program. Multi-threaded sequential consistent program cannot produce race condition.

Compiler optimizations may change order of program events and may produce an unexpected result[9]. For example, the following optimization may introduce a race condition into a program.

| Initially $A = 0$ ; $B = 0$ ; |             | Initially $A = 0$ ; $B = 0$ ; |          |

|-------------------------------|-------------|-------------------------------|----------|

| Thread 1                      | Thread 2    | Thread 1                      | Thread 2 |

| r1 = 1;                       | r2 = 2;     | r1 = 1;                       | B = 2;   |

| A = 1;                        | A = r2;     | A = 1;                        | r2 = 2;  |

| B = 3;                        | if (A == 2) | B = 3;                        | A = r2;  |

|                               | B = 2;      | After compiler opti           | mization |

| Original Code                 |             |                               |          |

The final value of B = 2/3?

Fig. 3.1: Compiler Optimization may introduce unexpected result

In some programming languages, adjacent data field may introduce data races. For example, the following program may create data races in the C++ programming language. According to the C++11 standard, adjacent bit fields are one "Object" [23].

a global s of type struct {char m:9; char n:7;}

Finally, execution order may also introduce data races into a program. As an example, the following program shows "Dekker's" example (all variables are initially zero):

```

Thread 1 Thread 2 x = 1; y = 1; r1 = y; r2 = x;

```

Could be executed as:

$$x = 1; y = 1; r2 = x; r1 = y;$$

or,

$x = 1; y = 1; r1 = y; r2 = x;$

Whereas, second execution sequence has a **data race** with y variable e.g.- r1 variable trying to read y while y is updating its own values.

### 3.2.2 Deadlock

Deadlock can arise in any concurrent program, where processes can preempt each other and generate a waiting cycle chain with each program/thread. More generally, deadlock can be introduced in any system that satisfies Coffman's four conditions [31].

Mutual exclusion: Threads claim accesses of resources exclusively. (e.g. Threads grab a lock)

**Hold-and-wait:** Threads that already hold a resource claim new resources.

No preemption: Thread holding a resource cannot be forcibly removed, only a process/thread holding a resource can release it.

Circular wait: Multiple processes create a circular waiting chain where all processes request a resource that the next process in the chain holds.

Concurrent programs may satisfy these requirements, as they use synchronization mechanisms and may deadlock. Deadlocks can be avoided by rearranging the program so that one of the Coffman conditions does not hold.

### 3.2.3 Livelock

A livelock is almost the same as a deadlock, except that the involved process states constantly change one after another, but no one can progress[16].

# 3.2.4 Starvation

Typically following factors cause process/thread starvation [59]

- 1. Processes hand over resources to other processes without any control. If resource allocations for processes are decided locally without considering the overall resource requirements for the system, irregularities can occur and result in some processes suffering starvation.

- 2. Higher priority processes consume all CPU time from lower priority processes. For example, the programmer sets process priority so that longer execution time processes will have higher priority. So, the processes with lower execution time may never execute and suffer starvation.

- 3. Randomly selected processes using resources may also cause starvation. If a waiting queue is not maintained for processes waiting service, some processes can never use required resources and may suffer starvation.

- 4. If the number of processes is much higher than the number of resources, some process execution periods may be exceeded before the process can use required resources.

Starvation can occur at any organized scheduling level though it more often takes place in the automatic process allocation than in the higher-level manual process allocation parts.

# 3.3 Way to avoid/eliminate/prevent incorrect behaviors

### 3.3.1 Race Condition

### 3.3.1.1 Avoid observable non-determinism

The easiest way to eliminate a race condition from a program is by using a programming language that doesn't have non-determinism. However, nearly all main stream programming languages support non-determinism[104]. So, the programmer has to make a clear distinction between non-determinism *inside*the system, which cannot be avoided, and *observable* non-determinism, which may be avoidable. This can be done with two following steps:

First, separate and limit observable non-deterministic events from a program. The remaining part of the program should have no observable non-determinism.

Second, define the programming languages so that it would be possible to write concurrent programs without observable non-determinism.

| Concurrent Paradigm               | Example Languages        | Race   | Input     |

|-----------------------------------|--------------------------|--------|-----------|

|                                   |                          | Possi- | can be    |

|                                   |                          | ble?   | nondeter- |

|                                   |                          |        | ministic? |

| Declaration concurrency           | OZ[32], Alice[103]       | No     | No        |

| Constraint programming            | Gecode[89], Numerica[82] | No     | No        |

| Functional respective programming | FrTime[51], Yampa[53]    | No     | Yes       |

| Discrete synchronous programming  | Esterel[46], Lustre[75]  | No     | Yes       |

| Message-passing concurrency       | Erlang[15], E[74]        | Yes    | Yes       |

Tab. 3.1: Deterministic concurrent state in different programming paradigms [104]

Java, C++ and C# use shared state concurrency[27] and Erlang, E use message passing concurrency [15] [74]; both paradigms have observable non-determinism. Fortunately, there are at least four useful programming paradigms in existence that are concurrent but do not allow observable non-determinism[104]. Table 3.1 lists these paradigms together with message passing concurrency.

# 3.3.1.2 Use of Synchronization Mechanisms

#### **Mutex Locks:**

Mutex lock: Mutex lock is the basic form of synchronization between processes/threads[72][23], where Mutex stands for Mutual Exclusion. It guarantees that only one process/threads can access into Mutex block. If a code section is blocked by Mutex then it makes sure that only one thread can lock this code section. Other thread can lock this block only after the first thread unlocks this block.

```

//The mutex has been previously constructed lock_the_mutex();

//This code will be executed only by one thread

//at a time.

unlock_the_mutex();

```

#### Condition Variable:

Condition variables allow threads to wait until the occurrence of a particular condition [38]. They cannot be shared across processes; they are user mode objects. They allow threads to release the lock automatically and enter the sleeping state. A condition variable can do two following things:

First, wait: the thread has to wait until some other thread notifies that it can continue because of fulfillment of the condition.

Second, notify: the thread sends a signal to a particular thread or to all threads to tell them that the condition that provoked their wait is fulfilled.

```

CRITICAL SECTION CritSection;

CONDITION VARIABLE ConditionVar;

void condition variable()

{

EnterCriticalSection(&CritSection);

// Wait until the predicate is TRUE

while( TestPredicate() = FALSE )

{

SleepConditionVariableCS(&ConditionVar, &CritSection, INFINITE);

}

// The data can be changed safely because we own the critical

// section and the predicate is TRUE

ChangeSharedData();

```

```

LeaveCriticalSection(&CritSection);

// If necessary, signal the condition variable by calling

// WakeConditionVariable or WakeAllConditionVariable so other

// threads can wake

}

```

### **Semaphores:**

Semaphore is a synchronization mechanism that uses an integer type variable or abstract data type that is used to control the access of shared resources by multiple processes[62]. It uses the following two types of signals for the process synchronization.

Wait: Processes will test the variable values and wait until the value become greater than zero. Otherwise, process will decrement the semaphore variable. If S is the variable for semaphore then wait can be defined as -

Signal: Increment the value of the semaphore and awake a process if any of them is blocked. If S is the variable for semaphore then Signal can be defined as -

```

signal(S){

S++;

}

```

If the initial value of the semaphore variable is 1, a wait operation is similar to Mutex locking and Signal value is similar to Mutex unlocking. To synchronize multiple threads with a semaphore -

```

\\wait for access into critical section

wait(S);

\\enter critical section

GlobalVaribal = GlobalVariable + 2;

\\exit from critical section

signal(S);

```

### Low level primitives:

Many popular generic programming languages include low-level primitives for synchronizing programs/threads at low level. However, different languages were implemented using different names for their own low level primitives. For example, C++ uses atomic type variables [18] whereas Java uses volatile and atomic as volatile with some extra features [84], Ada uses volatile and atomic pairs via pragmas[1]. Low level primitive read and write operations are not stored into the cash register, but are directly transferred to the memory location. Moreover, this prevents compiler optimizer to reorder memory access and automatically includes Read/Write operations as memory acquire/release respectively. Furthermore, its write operation happens-before all following reads of the same variable. Compared to lock/unlock or monitor exit/monitor enters operations, writes work as unlock or monitor exit and reads work as lock or monitor enter. In addition, it also guarantees the visibility and ordering of operations and these types of operations are cheaper than other synchronization operations. The main disadvantage of low level primitives is that even if there is only a limited set of operations using this variable in a program, it is very complicated and requires sophisticated analysis to verify, although it looks very easy to use. An example of low level primitives in Java could be as follows:

```

import java.util.concurrent.atomic.AtomicInteger;

class AtomicVariableExample {

private AtomicInteger num = new AtomicInteger(0);

public void increment() {

num.incrementAndGet();

public void decrement() {

num.decrementAndGet();

11

12

public int value() {

14

return num.get();

15

16

17

18

```

# 3.3.1.3 Sequential Consistency for Data Race Free (SC-DRF)

If a program does not allow data races and synchronizes with only following options -

- Sequentially consistent atomic, and

- Uses acquire and release semantics for Lock and Unlock operations respectively.

- then the program follows sequential consistency rules, i.e. it behaves as though it had been executed by sequentially interleaving its actions, and letting each load instruction see the last preceding value stored to the same location in this interleaving.

Software memory model has converged on SC-DRF. Java required SC-DRF since 2005 [72] and in C/C++ since 2011[23] it is the default type memory ordering.

### 3.3.1.4 Use Race detection algorithm

Several algorithms have been developed to detect race conditions in a program. Further mentioned some of the well-known algorithms that are used to detect race conditions in programs.

- FastTrack:Efficient and Precise Dynamic Race Detection [44]

- HARD: Hardware Assisted Lockset Based Race Detection[112]

- Eraser: A Dynamic Data Race Detector for Multithreaded Programs[88]

- Hybrid Dynamic Data Race Detection[78]

### 3.3.2 Deadlock

### 3.3.2.1 Deadlock Prevention

To prevent deadlocks, it is necessary to make it logically impossible for one of the four Coffman deadlock situations to hold in a concurrent program[105]. To achieve this, several methods have been already developed:

Elimination of "Mutual Exclusion" condition: To eliminate mutual exclusion from a program means that no process will have exclusive access to a resource. On the other hand, avoiding data races in program tasks means exclusive use of resources is needed. Non-blocking synchronization algorithms [48] can be used to avoid mutual exclusion in a program. Low level primitives are also useful to avoid mutual exclusion in a concurrent program.

Elimination of "Hold-and-wait" condition: There are two techniques that can be used to eliminate hold-and-wait conditions[105]. The first method is achieved by acquiring all locks at once atomically. In practice, this could be achieved as follows:

```

lock (holdandwait);

lock (R1);

lock (R2);

lock (R3);

... ...

unlock (holdandwait);

```

The first lock guarantees that only one process can acquire all resources and no other process can acquire these resources until the first process releases it. However, this method is problematic for a number of reasons, i.e. this method decreases the concurrency as all shared resources are acquired early on (at once) instead of exactly when they are truly needed. Second method is by disallowing processes to request a resource whenever it was allocated previously. In this technique the system has to grant resources on one or none basis. If the full set of resources that is needed by a process cannot be acquired then it has to wait until the complete set is available. So while waiting, processes may not hold any resources to avoid a deadlock situation. However, this approach also can lead to waste of resources and processes may have to wait for a long time.

Elimination of "No-preemption" condition: The non-preemption condition can be eliminated by sending the process that is waiting for a resource that cannot be allocated immediately to a waiting state to hand over all of its currently held resources, so that other processes may use those resources. However, eliminating no-preemption situation from a concurrent program may introduce circular wait for processes and result in a deadlock.

Elimination of "Circular Wait" condition: by imposing a total ordering on all resource types circular wait condition can be eliminated. All processes request resources in a certain order. This method imposes a totally ordered use of all resource types with this rule; the resource allocation graph can never have a cycle. Lamport's happens before relation [66] could be used for a total order of resource access.

# 3.3.2.2 Avoiding Deadlock

In some scenarios, deadlock avoidance is preferable to preventing a deadlock. This technique to the deadlock problem predicts deadlock before it occurs. A process uses an algorithm to predict the possibility of a deadlock and to act accordingly. This method is not similar to the deadlock prevention that guarantees that deadlock cannot occur by denying one of the four necessary conditions for deadlocks. Moreover, with this approach if necessary conditions for a deadlock are in place, deadlock avoidance would be still possible. One famous example algorithm for this method is Dijkstra's Banker's algorithm[35]. In addition, resource allocation graph algorithm is also useful where only one instance per resource is present.

### 3.3.2.3 Deadlock Detection

The final strategy is deadlock detection. In this approach, the system may enter into a deadlock state. In that state, the system needs an algorithm that periodically examines if a deadlock has occurred in the system and offers a procedure to recover from the deadlock [92]. The deadlock detection algorithms maintain a wait-for graph and periodically invoke an algorithm that searches for cycles in the graph. A deadlock is detected in that system if any cycle is completed. If a deadlock is detected, the system needs to recover from that state. Recovery can be done using two approaches. One is terminate all processes in the cycle; it works fast but may lose process work. Second is terminate one process from the cycle and run deadlock detection algorithm again; it's better in terms of process work, but with an extra work to resolve a deadlock.

### 3.3.3 Starvation

Remedies for starvation are applied by ensuring the conditions for starvation cannot happen[3]. Here is a selection.

- 1. There should be an independent manager for each resource, which will manage all allocation for its resources; this will guarantee that processes do not just pass resources around between themselves without making them available for general allocation.

- 2. Fair scheduling method for all processes may avoid starvation by changing process priority at execution level.

- 3. There should be a waiting queue for processes that need to access the resources. Random selection technique, uncontrolled competition, should be avoided for resource allocation.

- 4. Provide fair number of resources compared with the number of processes, though this solution can cost money. However, it is better than having process starvation which may cause some serious issues in the system.

# 3.4 Tests and Analysis

In this thesis data race detection test has been done on two different machines with two different versions of Linux kernel and one Windows version in two different programming languages. In this test, a simple multi-threaded program with global and local variable runs 1,000,000 times using different hardware, operating system and programming languages. The pseudo code of this program is as follows:

#### Pseudo Code:

| Initial state: $x = 0$ ; $y = 0$ ; |  |  |

|------------------------------------|--|--|

| Thread 1 Thread 2                  |  |  |

| x = 1; r1 = y;                     |  |  |

| y = 1; r2 = x;                     |  |  |

| Race if r1 != r2;                  |  |  |

In the above program, one thread updates global variables and another thread reads global variables and copies them into local variables. In a sequential consistent execution, either thread 1 or thread 2 will execute first and the values for local variables r1, r2 will be 0 or 1. But, two different values of r1 and r2 will cause a data race.

**Implementation Platforms:** Hardware Platform: In this thesis two different hardware platforms: one server and one desktop PC were used. The detailed information about both hardware systems is shown in table 3.2.

|                  | Machine 1 (Server)   | Machine 2 (Desktop)           |

|------------------|----------------------|-------------------------------|

| Number of        | 48 (4 processor with | 2 (One processor with 2 core) |

| processing Unit  | 12 Core each)        |                               |

| Vendor           | AMD Opteron ™        | Intel core 2 duo              |

| Clock Speed      | 2.194 GHZ            | 1.8 GHZ                       |

| Instruction bit  | 64-bit               | 32 bit                        |

| Cache            | L1d:64K              | L1: 128K                      |

|                  | L1i:64K              | L2: 2048K                     |

|                  | L2: 512K             |                               |

|                  | L3: 5118K            |                               |

| Memory           | 264 GByte            | 2 GByte                       |

| Operating System | Linux server (debian | Windows 8.0                   |

|                  | version 6.0.9)       | Ubuntu 12.04 LTS              |

Tab. 3.2: Test Machine Specification

**Operating System:** Three different operating systems were used on two different types of hardware systems. Linux Server (Debian version 6.0.9) was used on the server machine and Desktop PC Windows 8.0 and Ubuntu 12.04 operating system were used on the desktop machine.

Compiler: On both machines, three different operating systems, eclipse IDE for Java and C++ data race check were used. On the server machine, the Java version JDK 1.6 and gcc version 4.4.5 were used. So on the desktop machine JDK 1.7 for the Java compiler in Windows, JDK 1.6 in Linux and gcc 4.4.7 for C++ in Linux were used. Compiler optimization level was manually turned off for this test process.

**Test process:** The above program ran on both machines on three different operating systems. For a single tested data set, the same program was run in the same environment several

times then the maximum number of data races was counted. Each time the above threads ran 1,000,0000 times and the number of data race was counted in the program. The resulting data is shown in table 3.3.

|                                                           | Execution time (millisecond) | Maximum<br>number of data<br>race detected |

|-----------------------------------------------------------|------------------------------|--------------------------------------------|

| Machine 1 with -Java Compiler (JDK 1.6) -OS: Linux server | 418,053 ms                   | 0                                          |

| Machine 2 with -Java Compiler (JDK 1.7) -OS: Window 8.0   | 208,740 ms                   | 4                                          |

| Machine 2 with -Java compiler - OS: Linux (Ubuntu )       | 206,568 ms                   | 173                                        |

| Machine 1 with -gcc compiler (4.4.5) -OS: Linux Server    | 58,640 ms                    | 7                                          |

| Machine 2 with -gcc compiler -OS: Linux (Ubuntu)          | 57,260 ms                    | 7                                          |

Tab. 3.3: Number of data races detected on different machines

Analysis: Data races are very hard to detect. Their number depends on compiler and hardware optimization systems. In this test a huge change in result was observed on machine-two; for the Java compiler the number was four in Windows whereas 173 races were detected on the Linux (Ubuntu) operating system, although the hardware and the code were the same in both cases.

# 4. Interaction Between Software and Hardware

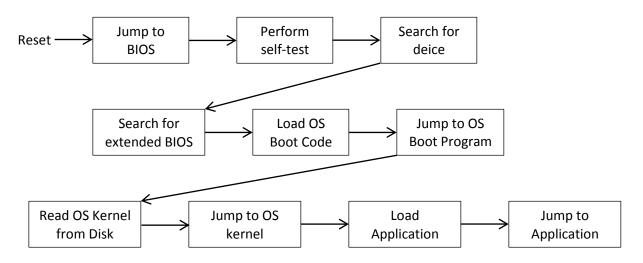

A computer is a state machine. If a processor is forced into its initial condition, then its next state is completely predictable. We can use this simple fact to see what happens when a computer system boots.

Fig. 4.1: A state diagram of a computer start-up process

Over the past few decades processors developed rapidly showing increases in performance, speed and power while coming from different vendors (e.i. Intel, ARM, POWER PC, etc.) using different architectures but none of them is best for all tasks. For example, Intel chips are good in performance but have had highest power consumption and price; ARM chips have lower power consumption and are significantly less expensive, but suffer from the performance problem. Moreover, each vendor has its own multicore processing architecture. As a result, software portability became limited to a particular vendor's design. So, software developers had to develop several versions of software with the same functionality.

The interface between a program and any software or hardware (for example, the virtual machine, operating system, the compiler, or any dynamic optimizer) is defined by a memory model. In a concurrent hardware or programming system, it is not possible to meaningfully write a program (written either in a machine language, assembly, byte code, or a high-level language) or any part of the program without an explicit memory model.

# 4.1 Memory Models

The memory consistency model or memory model defines the set of rules of a system or program stating what it is allowed to do. It is the heart of the concurrency semantics of a shared memory system or program, thereby defining the basic semantics of shared variables[5], for example, the return value of a memory read operation, thread synchronization mechanism, concurrent write operation rules for two adjacent data fields, eliminating out-of-thin air values.

It is difficult to write a program with a complex memory model. An extremely complex one may limit the compiler and hardware optimization, critically reducing performance, portability and maintainability of programs. Therefore, the memory model has long lasting effects. The hardware architecture with a strong memory model cannot change later without breaking binary compatibility for a weaker model, and a compiler with a weaker memory model may require rewritten source code. Finally, memory-model-related decisions must be considered for the rest of the system. If the memory system designer gives a weaker memory model, processor vendors cannot guarantee a strong hardware model, and a strong hardware model cannot provide full performance with a program that compiled using a weak memory model programming language. However, the importance of memory models has often been emphasized. The reason behind that could be the surprising complexity to specifying a model, which balances all desirable properties of portability, performance and programmability.