#### Institute of Computer Architecture and Computer Engineering

University of Stuttgart Pfaffenwaldring 47 D-70569 Stuttgart

Master's Thesis Nr. 3505

# Delay Characterization in FPGA-based Reconfigurable Systems

Shihao Zhang

**Course of Study:** Information Technology/InfoTECH

**Examiner:** Prof. Dr. rer. nat. habil.

Hans-Joachim Wunderlich

**Supervisors:** M.Sc. Francesco Cervellera

Dipl.-Inf. Michael Imhof

Dipl.-Inf. Michael Kochte

**Commenced:** 2013-06-03

**Completed:** 2013-12-03

**CR-Classification:** B.6.1, B.8.1

# Acknowledgement

I would like to thank, first and foremost, Prof. Dr. rer. nat. habil. Hans-Joachim Wunderlich for the opportunity to write this thesis at the Institute of Computer Architecture and Computer Engineering, University of Stuttgart.

This thesis would not have been possible without the help of many people. I would like to express the deepest gratitude to my supervisors, Dipl.-Inf. Michael Kochte, Dipl.-Inf. Michael Imhof and M.Sc. Francesco Cervellera. Their insightful viewpoint and continuous support have offered immense help during my work.

In addition, I am very grateful for all of my friends, whose offered suggestions and critiques on this thesis. Last but not least, I would like to give my very special thanks to my family and Huawen Dai, for their continuous love, encouragement and support.

## Abstract

Runtime reconfigurable architectures accelerate the operation of a standard processor core by hardware accelerators implemented in Field Programmable Gate Arrays (FPGAs). Partial runtime reconfiguration allows the hardware accelerators to efficiently adapt to different computational tasks dynamically. Nowadays, the FPGAs from major vendors, such as Xilinx and Altera, support this feature, including the Xilinx Virtex-5 FPGA family which is the implementation platform of this work.

Manufactured at 28 nm scaled technological node or lower, concerns rise about the impact of aging-related failure mechanisms on the modern generations of FPGAs. To detect degradation in the reconfigurable gate arrays, dedicated on- and offline test methods must be employed in the field. Design for dependability requires that the degradation is detected and localized, so that the degraded logic elements will not be used as a first choice in the reconfiguration.

This thesis presents the development and the evaluation of a delay characterization method for FPGA CLBs which comprise most of the FPGA logic elements. The purpose of FPGA delay characterization method in this work is to detect and localize the delay variance. This delay variance information may be used for achieving a speed optimized reconfiguration for a FPGA-based runtime system. Different delay characterization methods have been studied in this thesis for determining a suitable method to be implemented in the partial reconfigurable system. The delay characterization is performed in a part of area in the FPGA before a module is placed in this area to avoid the degraded portion. This thesis uses low level hardware description language to generate the fine-grained measurement units which can cover the target area. VHDL is used to generate the test wrapper, control circuit, and the circuit for communicating between the FPGA and the workstation. Several measurement techniques are used to evaluate the accuracy of the delay characterization method. Additionally, this thesis evaluates the temperature influence on the delay characterization.

The results show that this delay characterization method can compare the speed of logic elements in the partial runtime reconfiguration area with high accuracy. The degradation can be detected and localized. The results also show that this method can be adapted to different size and location, fitting in the partial runtime reconfigurable design. Twelve configurations are required to have a full coverage of all the CLBs in the area under test.

# Contents

| Αc  | knov       | vledgement                                            | i             |

|-----|------------|-------------------------------------------------------|---------------|

| Αl  | ostra      | c <b>t</b>                                            | iii           |

| Lis | st of      | Figures                                               | x             |

| Lis | st of      | Tables                                                | хi            |

| 1   | Intr       | oduction  Motivation                                  | <b>1</b><br>1 |

|     | 1.2<br>1.3 | Goal and Objectives of this work                      | 2 3           |

| 2   | Bac        | kground                                               | 5             |

|     | 2.1        | Reconfigurable Architecture                           | 5             |

|     |            | 2.1.1 Partial Runtime Reconfiguration                 | 6             |

|     | 2.2        | FPGA Overview                                         | 7             |

|     |            | 2.2.1 FPGA Architecture                               | 7             |

|     |            | 2.2.2 Configurable Logic Block                        | 7             |

|     | 0.0        | 2.2.3 Interconnect                                    | 9             |

|     | 2.3        | Implementation Platform                               | 10            |

|     |            | 2.3.1 CLB                                             | 11<br>14      |

| 3   | Dela       | ay Measurement in FPGAs                               | 15            |

|     | 3.1        | Temperature Influence on Delay                        | 15            |

|     |            | 3.1.1 Overall Power Consumption in CMOS Logic Circuit | 16            |

|     | 3.2        | Delay Fault Model                                     | 17            |

|     |            | 3.2.1 Transition Fault                                | 17            |

|     |            | 3.2.2 Path-Delay Fault                                | 17            |

|     | 3.3        | Delay Characterization using Delay Test               | 18            |

|     |            | 3.3.1 Delay Test                                      | 18            |

|     |            | 3.3.2 Delay Test for Delay Characterization           | 19            |

|     | 3.4        | Delay Characterization using Ring Oscillator          | 20            |

|   |      | 3.4.1 Ring Oscillator                                       | 20 |

|---|------|-------------------------------------------------------------|----|

|   |      | 3.4.2 Temperature Dependency of Ring Oscillator             | 21 |

|   |      | 3.4.3 Ring Oscillators-Based Delay Characterization in ASIC | 22 |

|   |      | 3.4.4 Ring Oscillators-Based Delay Characterization in FPGA | 22 |

|   | 3.5  | Delay Measurement Method Comparison                         | 24 |

| 4 | Arch | nitecture for Delay Characterization                        | 27 |

|   | 4.1  | Overview                                                    | 27 |

|   | 4.2  | Ring Oscillator Design                                      | 28 |

|   |      | 4.2.1 Design to cover all Paths in the Lookup Table         | 29 |

|   |      | 4.2.2 Hard Macro                                            | 33 |

|   |      | 4.2.3 Proxy against the Pin swapping problem                | 33 |

|   | 4.3  | Counter Design and Connection to Ring Oscillator            | 34 |

|   | 4.4  | Control Circuit Design                                      | 36 |

|   |      | 4.4.1 Serial Communication                                  | 37 |

|   |      | 4.4.2 Data Control Circuit                                  | 37 |

|   |      | 4.4.3 Ring Oscillator Control Circuit                       | 39 |

|   |      | 4.4.4 Selection wrapper                                     | 40 |

|   | 4.5  | System Monitor                                              | 41 |

| 5 | Impl | lementation                                                 | 43 |

|   | 5.1  |                                                             | 43 |

|   |      |                                                             | 43 |

|   |      |                                                             | 44 |

|   |      | •                                                           | 44 |

|   |      |                                                             | 45 |

|   | 5.2  |                                                             | 45 |

| 6 | Resu | ulte                                                        | 47 |

| U | 6.1  |                                                             | 48 |

|   | 0.1  |                                                             | 48 |

|   |      | 6.1.2 Implementation Result                                 |    |

|   |      | 6.1.3 Comparison of Simulation and Implementation           | 49 |

|   | 6.2  | Validating the measurement of Ring Oscillator Arrays        | 50 |

|   | 0.2  | 6.2.1 Delay Estimation                                      | 50 |

|   |      | 6.2.2 Measurement Precision                                 | 51 |

|   |      | 6.2.3 Measurement Accuracy                                  | 52 |

|   |      | 6.2.4 Summary                                               | 54 |

|   | 6.3  | Delay Variation                                             | 55 |

|   | 0.0  | 6.3.1 Test Cases                                            | 56 |

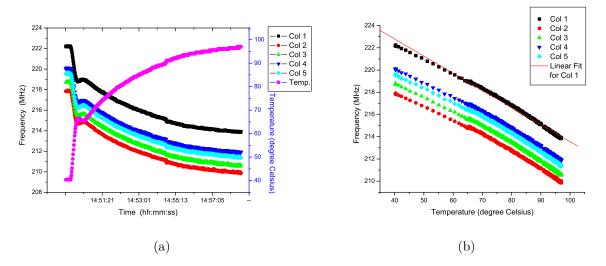

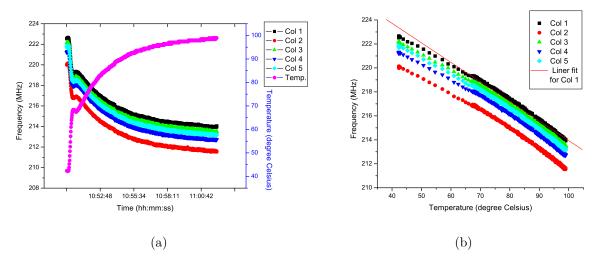

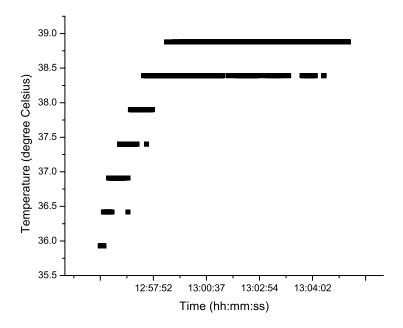

|   | 6.4  | Temperature Dependency of Delay                             | 59 |

|   |      | 6.4.1 External Heating                                      | 59 |

|   |      |                                                             | 61 |

|   |      |                                                             | 62 |

|   |      |                                                             |    |

|    | 7.1   | Conclusion and Future Work  Conclusion |    |

|----|-------|----------------------------------------|----|

| Bi | bliog | raphy                                  | 65 |

# List of Figures

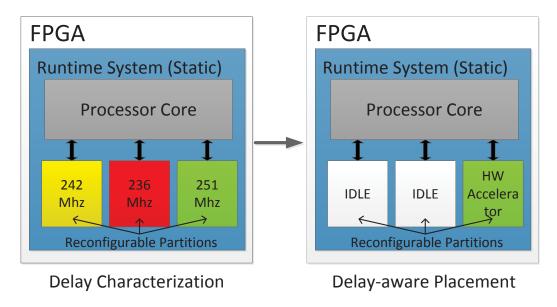

| 1.1  | The delay characterization method applied on a runtime reconfigurable system | 3  |

|------|------------------------------------------------------------------------------|----|

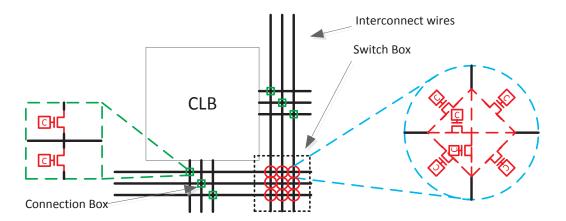

| 2.1  | Overview of FPGA Architecture                                                | 8  |

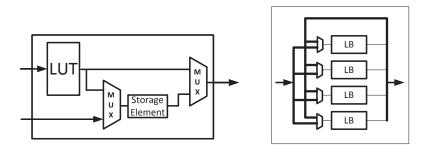

| 2.2  | Simplified Configurable Logic Block                                          | 8  |

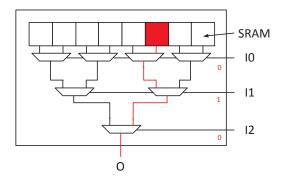

| 2.3  | A 3-input LUT                                                                | 9  |

| 2.4  | Switch box and interconnect wires                                            | 10 |

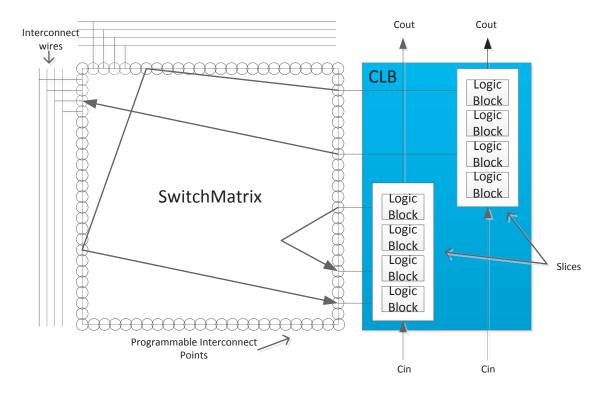

| 2.5  | Switch matrix and slices within CLB                                          | 11 |

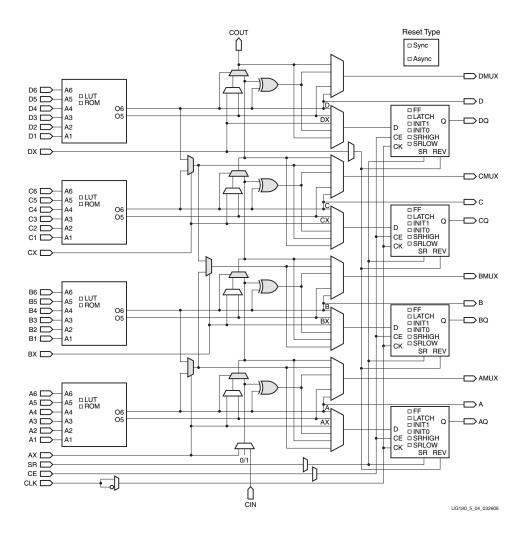

| 2.6  | Diagram of SliceL                                                            | 12 |

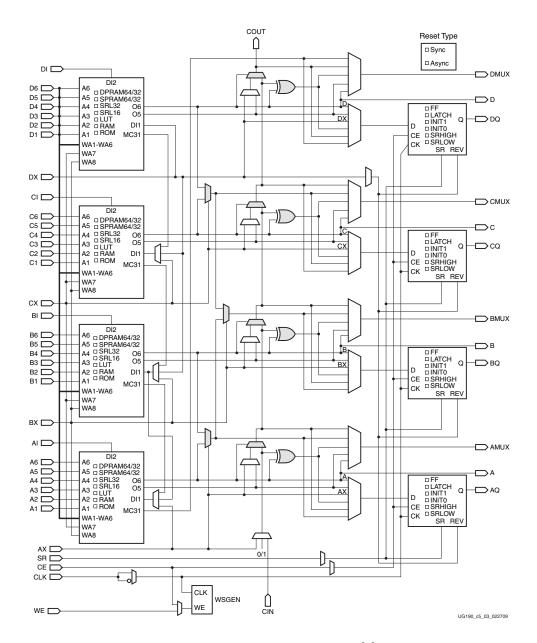

| 2.7  | Diagram of SliceM                                                            | 13 |

| 3.1  | Slow-to-fall transition fault                                                | 17 |

| 3.2  | Sum of propagation delays exceeds clock period                               | 18 |

| 3.3  | Test architecture for delay fault                                            | 18 |

| 3.4  | Timing diagram of the test circuit                                           | 19 |

| 3.5  | N-stage ring oscillator with enable signal                                   | 20 |

| 3.6  | Structure under test is added to ring oscillator                             | 23 |

| 3.7  | Characterizing the delay of omitted LUT                                      | 24 |

| 4.1  | Overview of the ring oscillator array design                                 | 28 |

| 4.2  | 1 / 0 0 1                                                                    | 29 |

| 4.3  | Required Boolean function for the ring oscillator design based               | 30 |

| 4.4  | Input I2 disable the ring oscillator                                         | 31 |

| 4.5  | •                                                                            | 32 |

| 4.6  | The control signals of the CLB ring oscillator                               | 32 |

| 4.7  | CLB ring oscillator hard macro with proxy                                    | 34 |

| 4.8  |                                                                              |    |

| 4.9  | Decoupling input and output of ring oscillator                               | 36 |

| 4.10 | Using UART serial communication to control the FPGA                          | 37 |

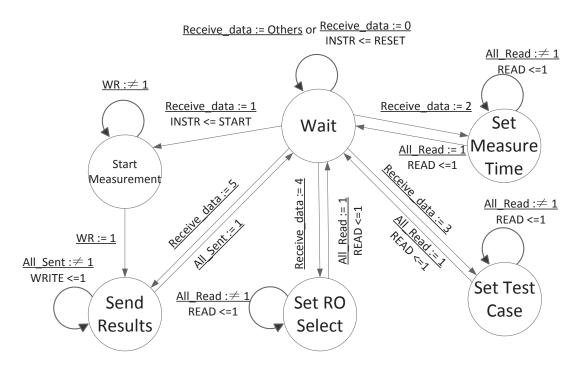

| 4.11 | The Finite State Machine of the Ring Oscillator Data Control                 | 39 |

| 4.12 | The Finite State Machine of the Ring Oscillator Control                      | 40 |

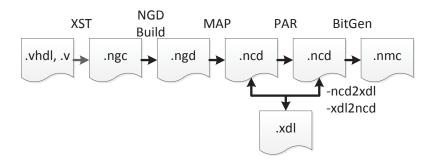

| 5.1  | Xilinx Design flow with XDL                                                  |    |

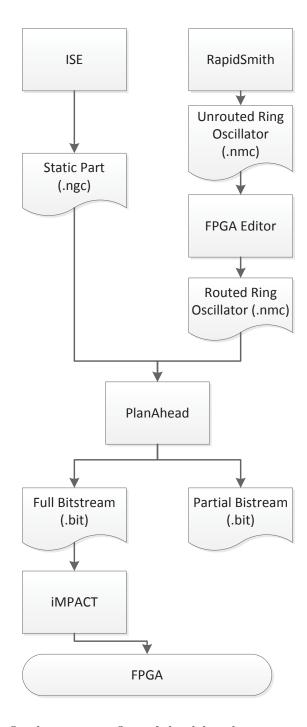

| 5.2  | Implementation flow of the delay characterization method                     | 46 |

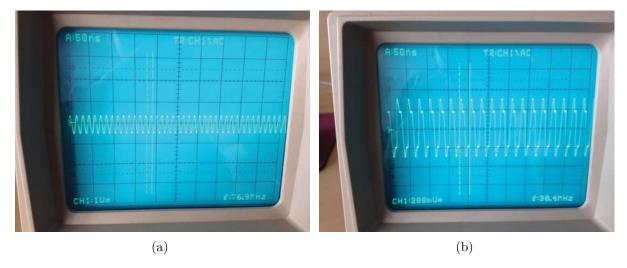

| 6.1  | Measurement result with oscilloscope via the expansion I/O pin           | 49 |

|------|--------------------------------------------------------------------------|----|

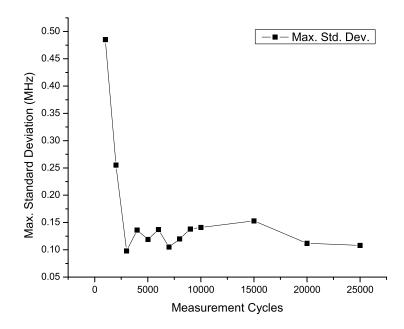

| 6.2  | The correlation between reference clock cycles and measurement precision | 52 |

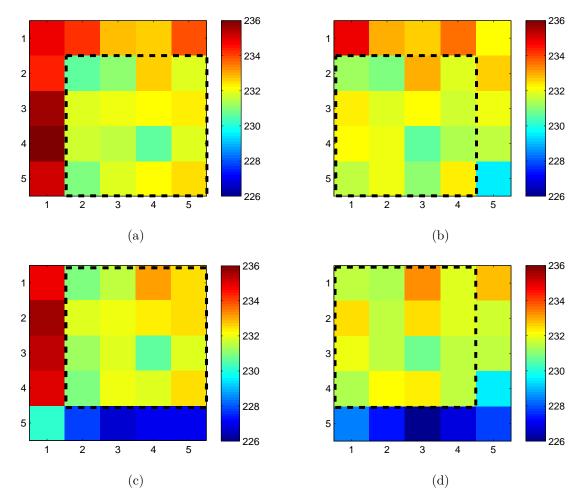

| 6.3  | Shifting the ring oscillator array in four positions                     | 55 |

| 6.4  | A $10 \times 20$ CLB area measured by two ring oscillator arrays         | 56 |

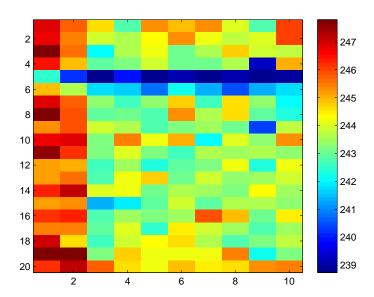

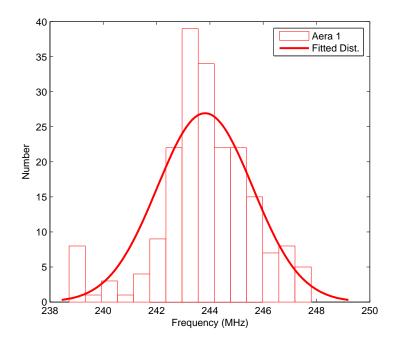

| 6.5  | Frequency distribution of $10 \times 20$ CLB area                        | 57 |

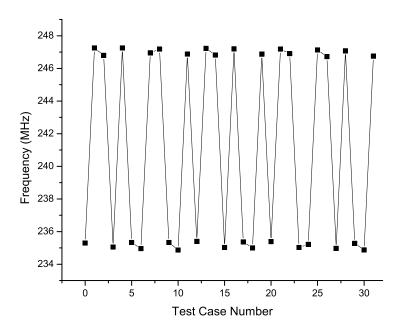

| 6.6  | Frequency comparison of 32 different test cases                          | 58 |

| 6.7  | The experiment setup for external heating                                | 59 |

| 6.8  | Temperature and frequency correlation of CLB row 5                       | 60 |

| 6.9  | Temperature and frequency correlation of CLB row 9                       | 60 |

| 6.10 | Heat up due to continuous measurement                                    | 61 |

# List of Tables

| 4.1 | Definition of Control Command                                                     | 38 |

|-----|-----------------------------------------------------------------------------------|----|

| 6.1 | Estimated delays for six test configurations                                      | 51 |

| 6.2 | The standard deviations (Mhz) for different measurement cycles                    | 51 |

| 6.3 | Results comparison for the ring oscillator array of different counter locations . | 53 |

| 6.4 | Results comparison for the ring oscillator array at random locations              | 54 |

| 6.5 | Parity dependence of the frequency                                                | 58 |

# Chapter 1

## Introduction

| <u>_</u> | 4                      |    | 1 - |

|----------|------------------------|----|-----|

| Co       | $\mathbf{n}\mathbf{t}$ | en | its |

| 1.1 | Motivation                       | 1 |  |

|-----|----------------------------------|---|--|

| 1.2 | Goal and Objectives of this work | 2 |  |

| 1.3 | Thesis Organization              | 3 |  |

| 2.0 | Thesis or gammaton               | • |  |

#### 1.1 Motivation

Reconfigurable systems have been developed and studied in the past two decades. The configuration-ability after fabrication permits the reconfigurable system to adapt to different requirements of the applications by programming the logic elements and the connection among them. Reconfigurable systems require reconfigurable hardware platforms, such as Field Programmable Gate Arrays (FPGAs). An FPGA has pre-fabricated integrated circuits that can be programmed by the designer. To date, the modern FPGAs from the major FPGA vendors have the ability to be partially reconfigured at runtime while the remaining parts continue operating without any data loss or interruption [1, 2]. This feature is called Partial Runtime Reconfiguration and it helps to reduce the power consumption or improve the performance [3]. For example, some applications use this feature of FPGAs to implement hardware application specific accelerators to accelerate the operation of a standard processor core by dynamically replacing the hardware modules to handle the different application tasks requested by the operating system [4]. Due to the flexibility, high performance and power saving, runtime reconfigurable systems are becoming attractive for a wide range of applications.

When FPGAs are manufactured at 28 nm scaled technological node or lower, concerns rise about the impact of aging mechanism like Hot Carrier Effect [5], Time Dependent Dielectric Breakdown (TDDB) [6], Electromigration [7], and Negative Bias Thermal Instability (NBTI) [8]. These degradation mechanisms will slow down the speed of the FPGA fabric, or in the worst case can affect the FPGA lifetime and dependability [9]. For example, electromigration

will cause a wear-out failure of interconnect by generating voids or shorts in the metal lines due to the high current density.

The speed of aging in the FPGA depends on different factors including switching activity. The aging effect due to switching activity is presented in [10]. The authors introduced an aging model that shows the proportional relation between aging and the switching rate of the circuit. Because every design on the FPGA is different, the workload of each component inside the FPGA is not the same. Different components of the FPGA have various switching currents and leakage currents. If a design is implemented on the FPGA for a long period of time and certain logic components are configured to have more computational activities than others, the impact of aging on these component is more significant so that different parts of the FPGA will have different aging speed.

To prevent the FPGA from the reliability threat caused by these aging mechanism, many test strategies have been discussed [11, 12]. These online test strategies can be applied to check that the reconfigurable fabric is fault free before the module reconfiguration is performed on the FPGA. The test just provides the pass/fail results, but it does not consider timing explicitly. When the transition on a certain path is too slow, it means the path is faulty. However, when the circuit under test passes the test, the delay of the circuit remains unknown. It is necessary to find out that if the degradation caused by the aging effect affects the reconfigurable fabric and localize it.

If we can find out the delay variation in the FPGA, then with the ability of reconfiguration, different placement and routing methods can be instantiated to avoid the aged area. Consequently, with Partial Runtime Reconfiguration, the delay variation in the FPGA chip can be considered before the circuit is mapped in the FPGA to utilize the actual speed of the available hardware resource and to increase the device reliability with delay-aware placement and routing methods [13, 14, 15].

To detect the degradation and provide the delay information in the FPGA, a method that can characterize the delay of the logic elements in a specific area on the FPGA is needed.

### 1.2 Goal and Objectives of this work

The goal of this thesis is to develop a delay characterization method for the reconfigurable logic element in the runtime reconfigurable system. The purpose of this FPGA delay characterization method is to detect and localize the degradation of the reconfigurable logic element so that with the spatial delay variation information the runtime reconfigurable systems can select the elements with relatively low delay to implement the design for better performance and reliability.

A delay characterization is performed in the partial runtime reconfigurable area of the FPGA before a module is placed as shown in Figure 1.1. The method has to provide the delay of each partition in this area. By comparing the delay characterization results, the system can select the area with appropriate performance to implement the module which has a specific demand for speed.

Figure 1.1: The delay characterization method applied on a runtime reconfigurable system

To achieve the goal of this thesis, different delay characterization methods from the literatures have been studied for determining a suitable method in the partial reconfigurable system. A simulation model is required to evaluate the method before the implementation of infrastructure on the FPGA board. The result analysis will be performed on the workstation and the effectiveness of the technique will be evaluated.

### 1.3 Thesis Organization

After the introduction, the remainder of the thesis is structured as follows. Chapter 2 briefly introduces the background information. Then, the state of art of delay characterization methods is reviewed in Chapter 3. The architecture of the delay characterization method and implementation details are stated in Chapter 4 and 5. Chapter 6 shows the results and the analysis. Finally, the conclusion is given in Chapter 7 with a summary and possible future tasks.

# Chapter 2

# Background

| 2.1 | Reco  | onfigurable Architecture                    | 5  |

|-----|-------|---------------------------------------------|----|

|     | 2.1.1 | Partial Runtime Reconfiguration             | 6  |

| 2.2 | FPG   | A Overview                                  | 7  |

|     | 2.2.1 | FPGA Architecture                           | 7  |

|     | 2.2.2 | Configurable Logic Block                    | 7  |

|     | 2.2.3 | Interconnect                                | 9  |

| 2.3 | Impl  | lementation Platform                        | 10 |

|     | 2.3.1 | CLB                                         | 11 |

|     | 2.3.2 | Programmable Switch Matrix and Interconnect | 14 |

|     |       |                                             |    |

In this chapter, the concept of reconfigurable system and partial runtime reconfiguration is introduced. Then the general overview of SRAM-based FPGA architecture is given. Finally the implemented platform in this thesis is presented.

### 2.1 Reconfigurable Architecture

Reconfigurable architectures are devices with programmable logic blocks and programmable interconnects among them. Reconfigurable architectures compute with logic blocks instead of fixed instruction sets, which avoids multiple stages of fetch, decode, and finally execute of instructions.

Reconfigurable architecture can be seen as a choice to balance the performance, flexibility and power. It has a shorter time-to-market than an application specific architecture. The reconfigurable device is prefabricated and tested. The designer can implement the design in the reconfigurable device by using hardware description language (HDL) and CAD tools provided by the vendor in a relative short time, because when it compares to the application specific architecture, the design doesn't have to be sent to the foundry to go through the manufacture

process, including lithographic, etching, testing, packaging. However, application specific architecture gives high performance due to the optimization for a particular application. For a small quantity of products that do not have particular requirements on area or power consumption, a reconfigurable architecture is a better choice. Rapid prototyping is one of the advantages of a reconfigurable architecture compared to application specific architectures.

In reconfigurable architectures, the function of the structure can be modified for adapting to different applications. A feature called Partial Runtime Reconfiguration allows all or part of the hardware function to be changed partially or completely during compile time or run time. This feature has been study in academia during the past decade and now supported by reconfigurable devices and it is discussed in the following subsection.

#### 2.1.1 Partial Runtime Reconfiguration

Partial runtime reconfiguration or dynamic partial reconfiguration, allows reconfiguration of a part of the system while other parts typically keep on running without any loss of data or interruption. The partial runtime reconfiguration helps in several ways [3]:

- 1. Reduce the area and power consumption. With partial runtime reconfiguration, the device resources can be better utilized. By dynamically configuring an area of a system, different functionalities are implemented for different operational demands. Even though more switching activity in the circuit will increase the dynamic power consumption, the static power consumption will reduce because of the reduced logic resource. As the static power dominates the total power consumption in modern CMOS process technology, the total power consumption will reduce (the power consumption problem will be discussed later in section 3.1.1). An example is the partial runtime reconfiguration in software-defined radio application. The applicability has been evaluated and shows that it has benefits using partial runtime reconfiguration [16, 17].

- 2. Improve the performance. For example, an array of partial runtime reconfiguration processing and memory cell is proposed. The performance of 18 times higher throughput than a traditional DSP solution shows the partial runtime reconfiguration is feasible for device acceleration [18].

- 3. Fast start up. For some modern automotive applications there are strict timing requirements for the start up time. Those applications require the device to answer the system request within 100 ms after the system is booted [19]. Meanwhile, coming along with the process technology progress, the number of the logic resource in the reconfigurable system growth, so that the configuration data for the complex design is becoming lager and it takes more time to configure the device. Consequently, even using fast configuration method, only the smaller size device can meet the timing specification [3]. Hence the authors purposed the two steps method to achieve the fast start up requirement. In the first step the critical part are configured in the system when it is booted using the priority configuration data. The remaining part of the system which is not timing critical will be configured in the second partial reconfiguration step. The experiment

results show that the fast start up approach can be up to four times faster than the traditional configuration method.

In some dynamically reconfigurable systems, a reconfigurable region is spared for the partial runtime reconfiguration and the region is divided into several slots for practical reason [4]. These slots are called containers, each of which can implement specific hardware for a particular application. When the containers are not needed, they are shut-down to reduce the power consumption. When one or some of the containers is needed for some applications as accelerator, delay characterization of this work can be used to select the one with better performance/without aging effect.

#### 2.2 FPGA Overview

The Field-programmable gate arrays (FPGAs) is a type of reconfigurable architectures. The programmable logic components provide FPGA the reconfigurability. Unlike the Application Specific Integrated Circuits (ASICs), where the device is customized for particular application, FPGAs can be configured to any desired application or functionality when there is enough logic resource. Currently, most commercial FPGAs are SRAM-based because of its re-programmability and the use of standard CMOS processing technology.

#### 2.2.1 FPGA Architecture

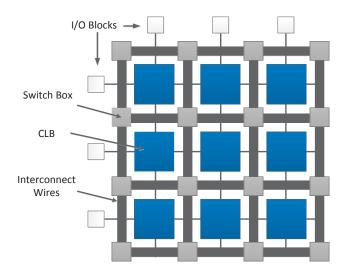

FPGA commonly consists of the Configurable Logic Blocks (CLBs) which implement the logic functions; the Programmable Switch Matrices (PSMs) and interconnect wires that connect these logic functions; the I/O blocks (IOBs) connect the logic blocks to the external connections. Additionally, modern FPGA is also integrated with some application specific blocks including memory blocks, Digital Signal Processor (DSP) block and the clock management blocks. A general circuit schematic of an FPGA is shown in Figure 2.1.

It shows one traditional FPGA routing architecture, island style architecture. Each of the blue box in the two dimensional grids is representing one CLB. The interconnect wires are around the CLBs. They are connected to the CLBs via the PSM in grey and the IOBs at the periphery.

#### 2.2.2 Configurable Logic Block

A Configurable Logic Block (CLB) is the main logic component of an FPGA that makes the FPGA a reprogrammable device. It comprises of the Lookup tables (LUTs), interconnection multiplexers and storage element like flip-flops. Each of these elements is introduced in the following subsection.

A LUT, a storage element and multiplexers form a basic logic block. The CLB consists of one or a cluster of intra-connected basic logic blocks as it is shown in Figure 2.2.

Figure 2.1: Overview of FPGA Architecture

Figure 2.2: Simplified Configurable Logic Block

#### 2.2.2.1 Lookup Table

The Lookup Table (LUT) is the basic logic element that calculates a function in a FPGA. A n-input LUT can calculate an arbitrary n-input Boolean function. It can be implemented as a tree of multiplexers that select an entry of the functions truth table which is stored in a memory element with the length of  $2^n$  bits. In the SRAM-based FPGA, these entries are represented by configuration bits stored in SRAM cells. For example, Figure 2.3 shows a general 3-input LUT. It uses 8 SRAM bits to set the truth table value for any 3-input Boolean function. The input pins control the multiplexers which can be implemented with pass transistors or transmission gates to pass the value to the output [20].

#### 2.2.2.2 Configurable Logic Block internal interconnect

The interconnect multiplexers are used to select the signal connections inside the CLBs for different signal forwarding strategies. The multiplexer selection is controlled by dedicated

Figure 2.3: A 3-input LUT

configuration bits and does not depend on the input signals. The signal connection is configured after the configuration bits are downloaded. By configuring the multiplexer, the output signal of the CLB can be connected to either the output of the storage elements, or directly to the LUT output, see Figure 2.2.

#### 2.2.2.3 Storage Element

To allow implementation of sequential circuits in the FPGAs, it is essential for the CLB to contain storage elements. The storage elements store the output values of corresponding LUTs every clock cycle. The generic storage element can be configured as an edge sensitive D-type flip-flop or a level sensitive D-type latch.

#### 2.2.3 Interconnect

Figure 2.1 shows that the CLBs are surrounded by the programmable interconnect consisting of switch boxes and interconnect wires. The programmable interconnect routes the signal between the CLBs, to and from the I/O blocks. Routing is conducted by the switch box by connecting or disconnecting the fixed interconnect wires in vertical or horizontal direction. And the input and output pins of the CLB can be connected to the interconnect wire or the connection box depending on different routing architectures [21].

A possible implementation of the switch box is shown in Figure 2.4. There are six pass transistors per switch box interconnect point. The pass transistors act as the programmable switches to control the interconnect wires connection. The pass transistors are controlled by configuration bits.

The interconnect wires can have different lengths, such as direct, double and hex line. The direct line can connect the CLB directly to the neighbour CLB. The double line can connect the CLB to the first and the second neighbour CLBs. And the hex line can connect the CLB to the third and the sixth neighbour CLBs. The longer the interconnect wires are, the fewer programmable switches are needed. As a result, the routing area and delay are reduced [22].

Figure 2.4: Switch box and interconnect wires

However, the long interconnect wires may cause routing flexibility problem, the probability of successfully routing the circuit may decrease. By combining different lengths of interconnect wires in the FPGA, it reaches a better balance among the routing flexibility, area and delay.

### 2.3 Implementation Platform

Modern FPGAs from different vendors, including Xilinx and Altera, support the partial reconfiguration feature. They also provide the development software to support this function. Xilinx Virtex-5 is one of these FPGAs and it is the implementation platform of this work.

Besides the common components mentioned in Section 2.2, Xilinx Virtex-5 also contains many advanced components including [1]:

- The Embedded Block RAM memory that is for on chip memory in the design;

- The Digital Clock Management (DCM) and Phase-locked Loop (PLL) that provide precise clock signals manipulation;

- The Digital Signal Processor (DSP) slices for digital signal processing like processing multiplication;

- The System Monitor that measures the on-chip physical operating parameters of the FPGA.

This work focus its attention on the CLB logic elements and CLB internal interconnections, and uses carry chain logic. This section introduces the Xilinx Virtex-5 architecture.

Figure 2.5: Switch matrix and slices within CLB

#### 2.3.1 CLB

In Virtex-5, each CLB is connected to a Programmable Switch Matrix (PSM) to access the global interconnect as shown in Figure 2.5. There are two types of CLB in Virtex-5, CLBLM and CLBLL. Both of them contain two slices. CLBLL has two SLICELs while CLBLM has one SLICEL and one SLICEM. These two types of CLB occur every other column. The two slices in each CLB have no direct connection between each other so the PSM need to be used. Each of the slice belongs to an independent carry chain. For each CLB, Xilinx labels the slice on the left SLICE(0) and the one on the right SLICE(1). So the carry out of the SLICE(0) can be passed to the carry in of the SLICE(0) in the upper row. As the same, SLICE(1) can propagate the carry to SLICE(1).

A SLICEL has four logic blocks which mentioned in Section 2.2.2. Each of the logic block is comprised of a 6-input LUT, multiplexers for path selection, and a storage element that can be configured as a flip-flop or a latch. Additionally, the slice has a carry chain which can perform fast lookahead addition and subtraction, see Figure 2.6.

The SLICEM adds more functionality to the SLICEL. The LUT inside SLICEM can be configured not only as a LUT, but so be configured as random-access memory (RAM) or shift register, see Figure 2.6.

This work considers both SLICEL and SLICEM, but only focus on logic elements and internal interconnections. As a result, we ignore the memory structure of SLICEM.

Figure 2.6: Diagram of SliceL [1]

#### 2.3.1.1 Lookup Table

The Lookup Table (LUT) in Virtex-5 has six independent inputs and two outputs. The LUT can be configured as one 6-input LUT or two 5-input LUTs as long as the two implemented Boolean functions share the same inputs. By configuring the multiplexers, up to four LUTs can be combined to implement an arbitrary seven or eight input Boolean function in one slice.

The output signals of the LUT can directly exit the slice, enter a XOR gate or multiplexer of the carry chain, control the multiplexer of the carry chain, or go into the D input of the storage elements as shown in Figure 2.6 and Figure 2.7.

Figure 2.7: Diagram of SliceM [1]

#### 2.3.1.2 Carry Logic

The carry logic allows an area-efficient implementation of addition and subtraction in a slice. Each slice can compute four result bits plus a carry bit. As mentioned earlier in this section, each CLB has two separated carry chains that can pass on the carry bit from the bottom CLB row to the upper CLB row for the add and subtraction operation which is more than four bits. An example implementation with the carry logic is Ripple-carry Adder.

The carry chain is constructed with carry multiplexers and dedicated XOR gates for calculating the operand. The XOR gate at the bottom of SLICE(0) in the carry chain is used in the ring oscillator design of this work.

#### 2.3.2 Programmable Switch Matrix and Interconnect

Xilinx FPGAs use an island-style routing architecture, CLBs are on the "islands" surrounded by the programmable routing network. The switch box is called Programmable Switch Matrix (PSM) and it is adjacent to the CLB. The PSM is formed of wires and the programmable interconnections called the programmable interconnect points (PIPs) represented by the small circles in Figure 2.5. A PIP is implemented as a multiplexer which is controlled by the configuration bits for selecting the wire segment to connect the next PIP or interconnect wires.

The interconnect wires in Virtex-5 have different lengths. Even though the detail information is not documented in the official user guide, the interconnect details can be seen from the Xilinx FPGA Editor. The Virtex-5 wire types can be found in the tool are: Bounceacross, Double, Pent, Long and Global line. Bounceacross and Double are Direct and Double lines mentioned in Section 2.2.3. While the Pent line connects the CLB to the second and the fifth neighbour CLBs, the Long line connects the CLB to sixth, thirteenth, and the twentieth neighbour CLBs. Finally, the Global connects the CLB from the first to the twentieth neighbour CLBs.

# Chapter 3

# Delay Measurement in FPGAs

| Contents |       |                                                                           |    |

|----------|-------|---------------------------------------------------------------------------|----|

| 3.1      | Tem   | perature Influence on Delay                                               | 15 |

|          | 3.1.1 | Overall Power Consumption in CMOS Logic Circuit                           | 16 |

| 3.2      | Dela  | y Fault Model                                                             | 17 |

|          | 3.2.1 | Transition Fault                                                          | 17 |

|          | 3.2.2 | Path-Delay Fault                                                          | 17 |

| 3.3      | Dela  | ay Characterization using Delay Test                                      | 18 |

|          | 3.3.1 | Delay Test                                                                | 18 |

|          | 3.3.2 | Delay Test for Delay Characterization                                     | 19 |

| 3.4      | Dela  | y Characterization using Ring Oscillator                                  | 20 |

|          | 3.4.1 | Ring Oscillator                                                           | 20 |

|          | 3.4.2 | Temperature Dependency of Ring Oscillator                                 | 21 |

|          | 3.4.3 | Ring Oscillators-Based Delay Characterization in ASIC $\ \ldots \ \ldots$ | 22 |

|          | 3.4.4 | Ring Oscillators-Based Delay Characterization in FPGA                     | 22 |

| 3.5      | Dela  | y Measurement Method Comparison                                           | 24 |

Delay measurement methods have been widely used on both ASIC and FPGA platforms. The main delay measurement methods can be grouped in at-speed delay test method and ring oscillator based method. This chapter first introduces the temperature influence on the circuit delay briefly, then discusses the fault models which are related to the delay measurement, and finally reviews and compares the state of the art in the literature.

### 3.1 Temperature Influence on Delay

The temperature affects the speed performance, power, and reliability of the system. With higher temperature, the integrated circuits become slower due to reduced carrier mobility and higher interconnect resistivity. In this section, the overall power consumption theory is introduced.

#### 3.1.1 Overall Power Consumption in CMOS Logic Circuit

The power consumption of CMOS logic circuit consists of two parts: dynamic power and static power. Dynamic power consumption has two parts. The first part is the power dissipation that is caused by the charging and discharging activities of the CMOS capacitance load: the power consumption due to the switching current. The second part is the power dissipation that is caused by the short circuit generated during switching: the power consumption due to the short circuit current. The static power consumption is always dissipated even when the CMOS does not perform any activity.

Dynamic power consumption:

$$P_{dynamic} = P_{switching} + P_{sc} (3.1.1)$$

where  $P_{switching}$  and  $P_{sc}$  are the power consumptions due to the switching current and short circuit current.

Power consumption due to the switching current:

$$P_{switching} = AC_L V_{dd}^2 f (3.1.2)$$

where A is the factor of the gates switching activities,  $C_L$  is the total effective load capacitance of all the gates,  $V_{dd}$  is the supply voltage, and f is the clock frequency.

Power consumption due to the short circuit current:

$$P_{sc} = I_{sc}V_{dd} \tag{3.1.3}$$

where  $I_{sc}$  is the short circuit current generates during signal transaction when both the NMOS and PMOS are active and directly conducts the  $V_{dd}$  to the ground.

Static power consumption:

$$P_{static} = I_{leakage} V_{dd} (3.1.4)$$

where  $I_{leakage}$  is the leakage current including reverse biased p-n junction current, subthreshold leakage and some other components which would not be discussed here.

The above equations define the overall power consumption:

$$P = P_{dynamic} + P_{static} = P_{switching} + P_{sc} + P_{static} = AC_L V_{dd}^2 f + I_{sc} V_{dd} + I_{leakage} V_{dd}$$

(3.1.5)

The activities in the FPGA will not influence the static power dissipation as it always occurs. However, when the switching activities increase, the dynamic power consumption rises as both of the switching current and short circuit current will increase.

### 3.2 Delay Fault Model

Delay faults affect the propagation delay of the circuit and cause the delay to exceed the clock period. If the circuit is operating at high frequency, it is more likely to fail due to the delay faults. Two specific delay faults are introduced in detail this section: transition faults and path-delay faults [23].

#### 3.2.1 Transition Fault

In a fault-free circuit, all the gates have some delays. Assuming all the gates in the fault-free circuit have delays, when one of the gates becomes faulty and the delay increase is large enough, then transitions on all the paths through this gate can not reach any observable output within the clock period, even for the shortest path. For each gate, the transition is either from 0 to 1 or from 1 to 0, correspondingly there are two types of transition faults for each gate, slow-to-rise (StR) and slow-to-fall (StF).

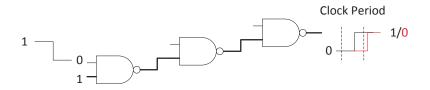

Here is a simple example of the transition fault with a NAND gate (Figure 3.1)

Figure 3.1: Slow-to-fall transition fault

Assume that the initial value of the upper signal is 1, when a 1 to 0 transition happens, the output should rise from 0 to 1 within the clock period if this gate is not faulty. However, if the gate is affected by a transition fault, the effect will be observed as a 0 at the primary output instead of the expected value 1.

#### 3.2.2 Path-Delay Fault

The path-delay fault causes the sum of the propagation delays on a combinational path to exceed a specified clock interval as depicted in Figure 3.2. The combinational path consists of a chain of connected gates and interconnections from a primary input to a primary output. Propagation delay is the time that a signal transition takes to pass though the path and it consists of switching delays of devices and transport delays of interconnects on the path [23].

The number of the paths in the circuit may be exponential in number of the gates. It is not practical to test all of the path-delay faults in the circuit. Primarily, a set of longest paths are selected for testing as the sum of delay on shorter paths may not be large enough to prevent a passing transition from reaching an output within the clock interval.

For each combinational path, there are two path-delay faults considering the rising and falling transitions. Therefore, the total number of path-delay faults is twice the number of paths in the circuit

Figure 3.2: Sum of propagation delays exceeds clock period

#### 3.3 Delay Characterization using Delay Test

Most of the existing at-speed delay fault tests are used to make the pass/fail decision of a specific integrated circuit design at a specific frequency, i.e. to find out if a circuit operates without timing failure at a target frequency. However, they can also be adopted to obtain the precise propagation delay information of a combinational path in the design [24]. This section will firstly introduce the basic idea of delay test, and then how this test methodology can be employed to get the propagation delay information of the combinational path.

#### 3.3.1 Delay Test

Depending on the type of Circuit Under Test (CUT), different delay test methodologies can be used. Here in this work, only a simple delay test methodology is introduced, which is later used for the delay characterization.

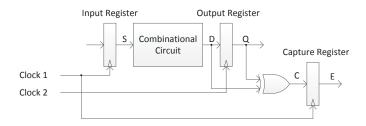

The test architecture in Figure 3.3 is suitable for combinational circuits or for sequential circuits with registers only at primary inputs and primary outputs [24, 25].

Figure 3.3: Test architecture for delay fault

The input register and the error capture register are clocked by the test clock 1 and the output register is clocked by the test clock 2 which is of the same frequency but skewed by a predefined time period. The input register stores the stimuli S from the test stimuli generator

and pass it to the CUT. Then the circuit will have the transient signals and the output signal D toggles after the propagation delay in the CUT. This output signal D will be compared with the value sampled by the output register with an XOR gate and the compared result C will be captured by a register at the rising edge of the test clock 1 to generate the error detection signal E. Figure 3.4 illustrates the test operation.

Figure 3.4: Timing diagram of the test circuit

Delay 1 is the propagation delay for the 0 to 1 transition in the CUT which is within the predefined time period, so there is no delay fault. In contrast, Delay 2 is a propagation delay larger than the predefined time period so that it is observed as a slow-to-fall fault. The predefined time period can be changed by the clock source, therefore the delay test can be set to specific frequencies according to the design requirement. When the phased-shift between test clock 1 and test clock 2 is smaller, the predefined time period is shorter and, as a consequence, the delay test becomes more strict. Hence, controlling the phase offset or changing the clock frequency allows to determine the propagation delay in the design. Examples of delay measurement methods using delay test are introduced in the following subsection.

#### 3.3.2 Delay Test for Delay Characterization

The at-speed delay test is adopted for delay characterization in FPGAs [24, 25]. They all use a same idea of changing the time between the clock edges of input and output registers to measure the propagation delay using the on-chip clock generation resources like Digital Clock Manager (DCM) on the Xilinx FPGA.

A double sampling delay characterization method is introduced in [25]. Different from the test architecture in Figure 3.3, another register which is clocked by the test clock 1 is added between the CUT and the XOR gate so that its output value is compared with the output register which is clocked by test clock 2. The test clock 1 remains constant so that the CUT is not interrupted by the delay characterization testing. The phase shift of test clock 2 is increased with a small step to reduce the predefined time period after a certain number of cycles. For each paths in the CUT, the predefined time period is recorded when the error is first time captured. The test process is repeated until all the paths in the CUT are characterized. This method is suitable for charactering combinational path delay in a specific design.

In [24], the test clock 2 is inverted from the test clock 1, so the predefined time period is always half of the test clock period. As the test clock steps from the lower frequency to a higher frequency, the CUT is observed from working correctly to working with delay error. A counter is used to count the total number of the timing errors during a predefined test cycle for each test clock frequency and then calculate the so called failure rate to estimate the delay of the CUT. It claims that all the LUTs on the Altera FPGA can be precisely characterized at a high resolution.

### 3.4 Delay Characterization using Ring Oscillator

Ring oscillators are widely used for thermal sensing, measuring the effects of manufacturing process variation and delay characterization in ASICs and FPGAs. In this section, the basic concept of a ring oscillator, different ring oscillators in circuit design and the ring oscillator-based delay characterization method will be presented.

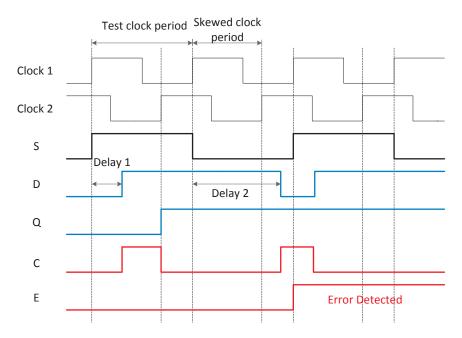

#### 3.4.1 Ring Oscillator

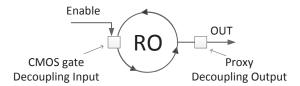

A Ring Oscillator (RO) consists of an odd number of inverting elements. These inverting elements are chained in a loop and the output toggles between the low voltage level and the high voltage level, as depicted in Figure 3.5.

Figure 3.5: N-stage ring oscillator with enable signal

The period T of the ring oscillator equals to twice of the propagation delay of the loop.  $T = 2 \times (Delay \ of \ the \ inverters + Delay \ of \ the \ interconnect)$ . Hence the delay on the

loop can be translated to the frequency  $f = 1/T = 1/(2 \times (Delay \ of \ the \ inverters + Delay \ of \ the \ interconnect)).$

#### 3.4.2 Temperature Dependency of Ring Oscillator

As mentioned in Section 3.1, the switching activity in the FPGA will consume power and the resulting heat dissipation will heat up the FPGA. In contrast, the increased temperature will slow down the switching speed in the FPGA. In this section the methods that study and make use of the relation between ring oscillator frequency and temperature are presented. They are classified into two groups.

- Ring oscillator as a heater: study how the ring oscillator frequency influences the temperature in the FPGA.

- Ring oscillator as a thermal sensor: study how the temperature influences the oscillation frequency which is then used to measure the temperature in the circuit.

#### 3.4.2.1 Ring Oscillator as a Heater

From Equation 3.1.1, assume that in FPGA the total effective load capacitance of all the gates and the supply voltage are constant: the dynamic power consumption will increase when the gate switching activity and the clock frequency increase. In the FPGAs, temperature can be increased significantly by maximizing the dynamic power consumption using different resources [26]. For example, a large number of 1-stage ring oscillators can heat the FPGA to 134 °C on Virtex-5 LX110t FPGA which is also the used device in this work. In [26], every 1-stage ring oscillator is implemented with a single LUT with its output directly fed back to its input.

#### 3.4.2.2 Ring Oscillator as a Temperature Sensor

In an FPGA, thermal sensors can be implemented as a lookup table (LUT) based ring oscillator style design. The LUTs are configured as separate signal inversion elements similar to individual inverters in a normal ring oscillator with hardware description language (HDL) or other design method [27]. The frequency of ring oscillator is related to the total delay of the logic elements and interconnects in the loop so that the way of designing the ring oscillator, using different FPGA resources, affects the sensitivity of frequency change due to temperature change.

It is demonstrated that the ring oscillator design that includes latches is more sensitive to temperature than the one without latches. That is possibly because the temperature effect is more significant on transistor delay than on wire delay [28]. In [29] the authors also claim for the similar result that the ring oscillator comprising 23 inverters and 24 latches gives the best overall sensitivity to temperature.

These works all showed that the correlation between the temperature and the ring oscillator frequency is linear. A ring oscillator combined with timer counter and capture counter is used as temperature sensor.

The sensor designed in [29] was synthesized from a VHDL specification using vendor tools to route the design automatically, hence resulted in differently routed sensors. As a result, the authors placed more sensors on the FPGA and took the average value of the results to decrease the impacts of routing variations. This implementation method is not suitable for using ring oscillators to characterize delay on FPGA, as the frequency differences are not caused by the speed difference of the logic elements, but the routings.

#### 3.4.3 Ring Oscillators-Based Delay Characterization in ASIC

Ring Oscillators have been used for delay measurement and process variation measurements in ASICs. ASICs are normally not tuned after manufacture, the aforementioned methods are used to monitor the process variation, fabrication parameter and to estimate the maximum speed of system [30, 31, 32, 33, 34]. The on-chip test structures in [30] provide path delay prediction for chip performance evaluation. And the ring oscillators are placed in various locations across the chip to provide information on process variations within-die [31, 32]. Moreover, the ring oscillators are used to identify and localize power-related failures [33]. In [34], the measurement method can characterize the gate delay for early process characterization in manufacturing. Hence, the use of ring oscillators is a standard and well known technique for delay measurement for ASICs.

#### 3.4.4 Ring Oscillators-Based Delay Characterization in FPGA

On FPGA platforms, the main approaches for ring oscillators-based delay characterization are:

- 1. Delay variation comparison that compares the spatial delay variation [24, 25].

- 2. Differential delay measurement that directly measures the delay of the path under test [35, 36].

This subsection will introduce the two types of method in detail.

#### 3.4.4.1 Delay Variation Comparison

The idea of delay variation comparison is a delay characterization method that compares the frequency of the ring oscillators at different locations on the FPGA. Due to the process variation and the impact of aging mechanism, the delay of the logic elements and interconnect wires at different locations on the FPGA are not identical. When the ring oscillators are implemented with these logic elements and interconnect wires, the delay variation between these resources result in the variation of ring oscillator frequencies. For example, an array of

ring oscillators which covers an area of an FPGA is used for the purpose of within-die delay characterization [37, 38].

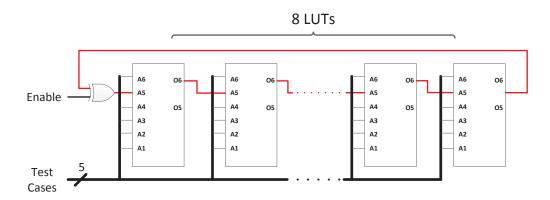

How the measurement is performed on FPGAs is described in [38]. The area under test implements a two dimensional array of identical ring oscillators, which are activated one at a time and measured by the counter under the control by a timer. However, the ring oscillators are implemented with a part of the LUTs. Instead of measuring all the LUTs in the area under test to obtain the delay variation of the whole area, the authors use an equation to model and estimate the systematic and stochastic delay variation. And the accuracy of the equation is calibrated by measuring different stages of ring oscillators at each location. In this way, the characterization may not detect the degradation in a certain part of the FPGA due to the low coverage of LUTs in the area under test.

Moreover, the ring oscillator sensor used in [39] can measure variations in delay, leakage, power and temperature. The scattered sensors can also be arranged as an array. Compact shift register counters are introduced and are attached to each ring oscillator. The consuming time of the test is shorten because all the ring oscillators are measured simultaneously. However, as mentioned in Section 2.3, only the LUTs in CLBLM can be configured as shift register. As a result, the ring oscillator design with a compact counter is not possible to be implemented in CLBLL on Virtex-5 FPGA platform.

#### 3.4.4.2 Differential Delay Measurement

The basic idea of differential delay measurement is that if a logic element or an interconnect wire is added to the ring oscillator loop, then the delay on the loop will increase and the frequency will decrease. By comparing the frequency changes, the delay of the added logic element or interconnect wire can be calculated.

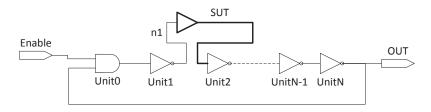

In [35] a method which compares two Ring Oscillators to measure the propagation delay on the interconnect wire is proposed. A reference RO is compared with the RO which with similar structure but includes the path under test in the loop. The structure under test (SUT) can be any arbitrary non-inverting path, including many different interconnect wire segments and logic elements. The propagation delay of the SUT shown in Figure 3.6 is measured from the frequency difference between the ring oscillator shown in figure and the same ring oscillator with inverter Unit 2 directly driven by inverter Unit 1. However, this measurement method has a problem, that this propagation delay also includes the delay difference between net n1 in Figure 3.6 and a net directly connecting inverters Unit 1 and 2.

Figure 3.6: Structure under test is added to ring oscillator

The same structure is implemented in different locations to measure the delay variation and also different wire types and length are measured and the results are compared with the estimation from the vendor tool in [35]. The results are directly measured with oscilloscope.

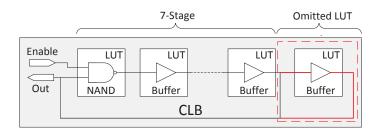

Similar idea is used in [36] to characterize the delay of a single logic element. Their design is based on Xilinx Spartan-3e FPGA. The CLB structure is different from Virtex-5 but it contains eight LUTs as well. One of the LUTs is implemented as a NAND gate, the others are implemented as buffer with identity function as shown in Figure 3.7. The delay of a single 4-input LUT is measured by comparing the frequency of the 8-stage ring oscillator and the 7-stage ring oscillator omitting one of the LUT. When it compares to the previous direct measurement method in [35], this method also has the problem of delay changes in the interconnect wires. The delay estimation information is extracted from the Xilinx timing analysis tool and is used to calculate the delay of a single LUT. The estimation result is pessimistic and it is 80% larger than the actual measurement result. As the interconnect wire composition and the connection order of the LUTs are chosen based on the minimum estimation delay, the input pins of the LUTs of the 8-stage ring oscillator and the 7-stage ring oscillator would be different because of the limited direct connection between the LUTs. As a result, this design is measuring the LUT delay under the assumption that all the inputs of the LUTs have the same speed. This may not be the case when some of them degraded more quickly due to the different aging and the switching rate. Nine test configurations are needed. The CLB based ring oscillators cover all the LUTs in the area under test.

Figure 3.7: Characterizing the delay of omitted LUT

## 3.5 Delay Measurement Method Comparison

Both of the delay characterization methods using delay test and using ring oscillators can be adopted in the runtime reconfigurable system to test the container. The delay test method in [24] can accurately measure the path delay, but the resolution of the measurement depends on the size of frequency sweeping step and a Xilinx FPGA is used to provide the clock generation to the Altera FPGA. Even though the newer FPGAs can provide on-chip test clock generation, it still increases the design complexity of the system. In contrast, the method using ring oscillator does not require complex clock control. Once the ring oscillator is activated, it automatically oscillates at the maximum frequency depending on the speed of the FPGA fabric. Moreover, the control and analysis of the circuit is simpler than the method using delay test. Considering the complexity of extending the method to a runtime reconfigurable

system application, the delay characterization method using ring oscillators is developed and implemented in this work.

Although the ring oscillator method is well-known and has been studied for delay characterization, the existing method is not perfect for detecting the degradation due to the aging mechanism in the reconfigurable system. For example, only one fix routing of ring oscillator is implemented in the design and the input pins of the LUTs are randomly chosen in [36], not to mention that the method in [24] doesn't cover all the LUTs in the area under test. The characterization method in this work complements these approaches and is able to cover all the input pins of the LUTs in the container.

## Chapter 4

# Architecture for Delay Characterization

| Contents |       |                                               |    |

|----------|-------|-----------------------------------------------|----|

| 4.1      | Ove   | rview                                         | 27 |

| 4.2      | Ring  | g Oscillator Design                           | 28 |

|          | 4.2.1 | Design to cover all Paths in the Lookup Table | 29 |

|          | 4.2.2 | Hard Macro                                    | 33 |

|          | 4.2.3 | Proxy against the Pin swapping problem        | 33 |

| 4.3      | Cou   | nter Design and Connection to Ring Oscillator | 34 |

| 4.4      | Con   | trol Circuit Design                           | 36 |

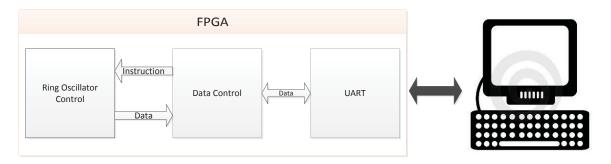

|          | 4.4.1 | Serial Communication                          | 37 |

|          | 4.4.2 | Data Control Circuit                          | 37 |

|          | 4.4.3 | Ring Oscillator Control Circuit               | 39 |

|          | 4.4.4 | Selection wrapper                             | 40 |

| 4.5      | Syst  | em Monitor                                    | 41 |

#### 4.1 Overview

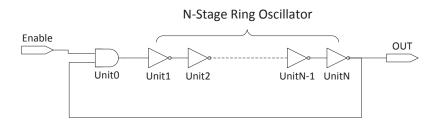

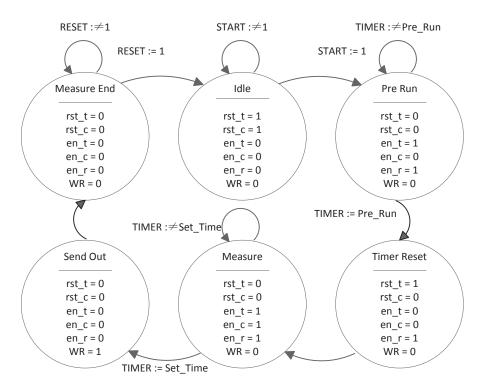

A ring oscillator array methodology is used for delay characterization in this work. A new ring oscillator design that can cover all the path in the LUTs of a single CLB is proposed. In this chapter, the idea and the advantages of this CLB based ring oscillator design are given. Then the auxiliary circuit design of counter and control circuit are introduced. The system monitor of Virtex-5 is also presented.

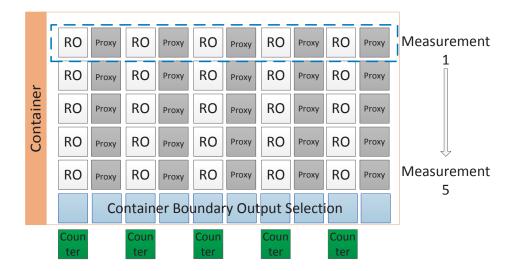

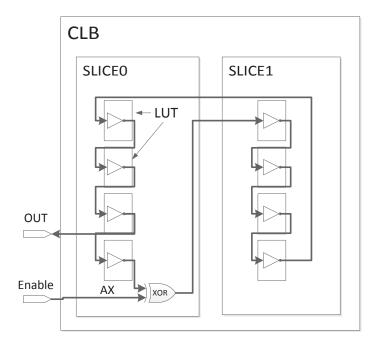

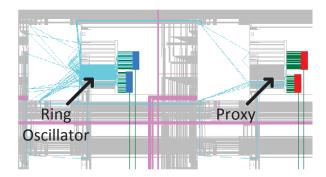

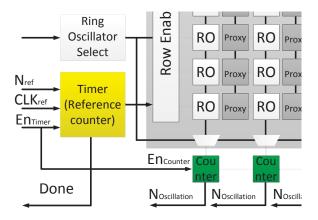

A ring oscillator array that fits in a container is shown in Figure 4.1. Each small block is representing a CLB. Ideally, if we can place the ring oscillator design in every CLB within the container, then we can reach the minimum number of test configurations. However, as

Figure 4.1: Overview of the ring oscillator array design

low level design is not well supported by the CAD tools, a proxy must be attached to each ring oscillator to fix a problem caused by the tool. Therefore, the test configurations have to be doubled to cover all the CLBs in the whole container area. The proxy is explained in Section 4.2.3.

One row of counters measure multiple rows of ring oscillators. For each measurement, one row of ring oscillators are selected and the oscillations in a time period are measured by the counters in parallel.

## 4.2 Ring Oscillator Design

This work is focusing on the delay variation on the chip of one FPGA device by comparing the speed of ring oscillators in different locations. The reason of using a special design method here is because the ring oscillator in this work is a low level design. Any factor that can contribute to the differences in the speed of the ring oscillator must be avoided as they will disturb the measurement of the speed difference caused by aging. Besides, specific pins are used in the ring oscillator. Using VHDL or Verilog Hardware Description Language (HDL) for the design can not satisfy the low level design requirement.

VHDL and Verilog HDL and the synthesis tool may be used to generate the ring oscillator design. It is possible to place this kind of ring oscillators on different FPGA devices and compare the frequency of the ring oscillators at the same location to measure the chip-to-chip variation. However, it is not suitable for the delay variation measurement within a single chip for the following reason. Even if the descriptions of ring oscillators are identical, for example using the generic statement in VHDL, the LUTs inside the ring oscillators of different locations may have different placements. Moreover, even if the LUTs are placed exactly the same for all

the ring oscillators, the interconnect routing may not be exactly the same [29]. The difference of the interconnect routing may have more delay impact than the aging effect.

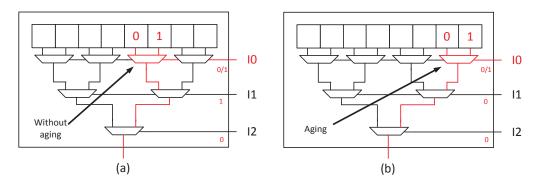

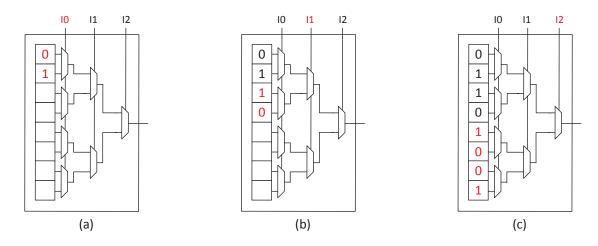

Using different LUT inputs may also influence the ring oscillator delay. In [21], it is stated that the inputs of the LUT are logically equivalent. However, it is mentioned in Section 2.2 that the LUTs are implemented as tree of multiplexers, the delays through the multiplexers are different. For example, in Figure 4.2 (a) the multiplexer in red is without aging and it is switching as input value I0 is changing. Its delay is smaller than the one with aging effect in Figure 4.2 (b). As a result, it is essential to characterize the delay of each multiplexers by using different input value combinations and selecting different input pins to switch.

Figure 4.2: LUT inputs select multiplexer with/without aging in a 3-input LUT

The synthesis tool will choose the input of the LUT during place and route stage based on a certain rule. And we could not control each LUT at the same position in the ring oscillators to use a same input by using a high level HDL to generate the design. Hence, not only a new design of ring oscillator is necessary, but also a special design method is needed.

#### 4.2.1 Design to cover all Paths in the Lookup Table

In previous work of delay characterization methods using ring oscillators [35, 37, 38], it is ambiguous how the path on the loop looks like, and which pins of the LUTs are used. In [36] the authors choose the interconnect with minimum estimated delay and we can infer that only one set of LUT pins are used in their work. In [38], the ring oscillators are implemented using some of the LUTs in the logic array block, but not all the LUTs in the area under test are covered.

These methods can have a good spatial evaluation of the process variation assuming the chip is in a healthy condition without fault or aging impact. However, when a certain part of the chip is suffering from the aging effect, a method which only characterizes the delay of one path or some paths within a CLB is not comprehensive enough to give a complete delay characterization of the area under test. For example, if in the worst case one of the LUT inputs of a CLB was almost slow enough to be considered as faulty wasn't on the path of the loop, then the delay characterization result may show that the speed of the CLB was not slow and that it's not seriously affected by aging. As a result, the aforementioned method could

not avoid using the CLBs which were actually suffering from aging and a more sophisticated ring oscillator design for delay characterization is needed.

We decide to implement a ring oscillator per CLB for the following reasons:

- 1. Considering a Virtex-5, CLBs have two slices, four LUTs per slice, in total eight LUTs (see Section 2.3.1). Thus, a CLB has enough logic elements to implement a ring oscillator within a frequency range that can be robustly measured by a built-in counter.

- 2. One ring oscillator per CLB is a suitable granularity to cover all the paths in the LUTs of all the CLBs in the containers. With the basic unit size, the ring oscillator can fit in different sizes of containers.

The idea of covering all the paths and pass transistors in all the LUTs of a CLB is given:

- 1. All the input pins of the LUT should be at least once on the ring oscillator loop.

- 2. All the truth table values should be read out at least once per test configuration.

As a result, we search for a Boolean function that selects all the entries of the functions true table. For Virtex-5, it is a 6-input Boolean function that uses all the inputs of a LUT. Besides, we have to assure that, when enumerating the paths in the LUT, the ring oscillator has an odd number of inversions so that it can oscillate.

Again a 3-input LUT is used as an example, see Figure 4.3:

Figure 4.3: Required Boolean function for the ring oscillator design based on a 3-input LUT

When I0 is toggling on the ring oscillator path, the truth table values should invert. So every pair of the SRAM bits controlled by the same multiplexer should be either 01 or 10, as for example in Figure 4.3 (a). When I1 is on the path, it inverts the value of first two bits. For example, if I0 is set to 0, the first and the third bits should have inverted value while I0 is 1, the second and the fourth bits should have inverted values like in Figure 4.3 (b). The situation is the same for I2, so the value of the fifth to the eighth bits are with the inverted values of the first to the fourth bits, see Figure 4.3 (c). If we just consider I0 I1 and write

down the input values and SRAM bit value they will fetch, then we see that we are actually implementing the XOR function for I0 and I1. The I1 and I2 are also implementing an XOR. It's a hierarchy of XORs. The Boolean function is  $O6 = A0 \oplus A1 \oplus A2 \oplus A3 \oplus A4 \oplus A5$ .

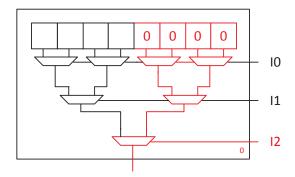

The ring oscillator implemented with seven LUTs configured as inverter plus a LUT configured as an AND gate is a practical design choice when it is not necessary to cover all the paths and pass transistors of LUTs within a CLB. However, since we target full coverage here, the test configurations have to be doubled since the pins which are used as enable pins disable half of the paths in the LUT. For example, in Figure 4.4 I2 is chosen as enable pin. When I2 is set to 0, output is always 0 and the ring oscillator won't oscillate. The delay of the three multiplexers on the right can not be characterized. Another configuration which enables the ring oscillator when I2 is set to 0 is needed to cover these three multiplexers.

Figure 4.4: Input I2 disable the ring oscillator

If we need to apply this work in a partial runtime reconfigurable system, we have to minimize of the number of test configurations. The less test configurations, the smaller the required storage size of configuration data, and the smaller the required time for delay characterization. A nine stages ring oscillator is purposed in this work and it can reduce the test configurations.

We configured all the eight LUTs in a Virtex-5 CLB as inverters. However, an even number of inverters on the loop will not oscillate, and another inverting element is required. So the XOR gate from the carry chain in CLB can be used as the ninth inverter. One input of the XOR gate is from the ring oscillator loop and another is from the enable signal. The inequality function of the XOR gate determines that once the enable signal is set to 0, the output signal of the XOR gate is identical to the input from the loop; in the other case, the enable signal is set to 1, the output signal of the XOR gate is the inverted value of the input from the loop. In the first case, the design will not oscillate because there is an even number of inverting functions in the loop and in the later case, the design oscillates as a nine stages ring oscillator.

The schematic of the ring oscillator within a CLB is shown in Figure 4.5. The LUTs are first chained within a slice, pass through the first XOR gate of the carry chain and then to another slice.

As the internal connects between the LUTs on ring oscillator loop are fixed after the configuration bits are downloaded, the ring oscillator loop goes through only one set of LUT inputs

Figure 4.5: One ring oscillator per CLB

and it is fixed before the next reconfiguration. In this design, for each configuration we choose the input of the same pin number for every LUT in the CLB for the delay characterization (Figure 4.6).

For the other five LUT input pins, the input pins with the same pin number are connected to the same input net, for example, all the input pins A6 are connected together. These five input pins nets together are defined as test cases control signal. The test cases control signal has  $2^5$ , i.e. 32 combinations. By changing this 5-bit signal for the six different input pins combinations, all the paths and multiplexers inside the LUTs of a single CLB can be covered.

Figure 4.6: The control signals of the CLB ring oscillator

The line in red in Figure 4.6 represents the path on the ring oscillator loop. The test case control signal is five bits wide, each bit connecting to the LUT inputs with the same pin number. In the best case, we will just need six test configurations. However, due to the implementation problem which is explained in Section 4.2.3, additional test configurations are required.

#### 4.2.2 Hard Macro

The ring oscillator is implemented as a reusable physical module called hard macro. A design can contain a hard macro many times. A hard macro is a logical function created from components of a specific device family. It specifies the actual configuration of the contain LUTs and their interconnect. As the ring oscillators in the array are using the same hard macro, it is sure that they have an identical logic function and routing, so the delay of each CLB can be compared.

However, a hard macro can not be instantiated in any location. The hard macro must be placed at a location which has the same component type as the original location. For example, when the ring oscillator hard macro is generated for a CLBLM, it can not be placed in the CLBLL as SLICEL and SLICEM are components with a different type.

#### 4.2.3 Proxy against the Pin swapping problem

We used a low level design specification to generate dedicated interconnection to characterize the delay of a CLB using different inputs of LUTs. The pin to pin connection information can be given in the design. However, the CAD tools provided by the FPGA manufacturers are not prepared for such kind of low level application. Normally the routing details are hidden and the users do not need to worry about that. The CAD tools will optimize the design for different targets, for example using fewer resources or having lower delay. In our design, as long as the routing, the LUTs functions, and the input pins of the LUTs are identical, the delay comparison between the CLBs is reasonable, because, in that case, ideally the speed of the ring oscillator should be the same. Any speed difference detected by this delay characterization method can prove that some of the CLBs under test are suffering from more process variation or aging effects. Hence, the design optimization is not desired and may in the worst case influence routing and the LUT functions with adverse impact on measurement accuracy.

In [21], it is stated that the inputs of the LUT are logically equivalent. By rearranging the bits in the truth table and the routing, the input pin of LUT to which a signal is connected can be changed. Furthermore, the timing of the LUT only depends on the access time of the SRAM cells and the multiplexers instead of the complexity of the functions. As a result, the placement and routing (PAR) tools may swap the logically equivalent LUT input pins to achieve a delay-optimized routing.

The ring oscillator design here configures the Boolean function of each LUT as a 6-input XOR function. So logically the six inputs of a LUT are equivalent. This leads to a situation that even though we use different LUT input pins and routing in different test configurations as

mentioned in the previous subsection, the PAR tool considers they are logically equivalent and swaps the used LUT pins for delay-optimized routing. As a result, all the six different test configurations are modified to use identical LUT input pins and routing after PAR. This completely changes our ring oscillator design, and it fails to cover all the multiplexers in the LUTs.

Therefore we tried to stop the automation routing of the tools from modifying the routing of the ring oscillator design by adding constraints in the User Constraints File (UCF). However, it doesn't work. As long as the a net is unrouted in our design, the tool will rearrange the pins and update the routing. Because the net of the test case signal has no driver in the hard macro design stage, the tool can not route the net. A proxy is introduced to fix this problem as shown in Figure 4.7. A proxy is a CLB which is adjacent to the CLB ring oscillator and it provides the unrouted nets with a driver so they can be routed. The LUTs in the proxy are configured as identity functions. All the external pins are connected to the inputs of the identity function, and the outputs of the identity function are connected to the net these external pins drive.

Figure 4.7: CLB ring oscillator hard macro with proxy (screen-shot from FPGA editor)

The PAR tool will not swap the pins of the LUTs as all the nets in the ring oscillator design hard macro are routed. The input pins of the LUTs are routed in a order as we designed. We can generate six different test configurations with 32 test cases by using the proxy. However, as the design uses two CLBs (see Figure 4.7), the CLB which is implemented as a proxy can not be tested using these test configurations. Since we target full coverage of the container, extra test configurations are needed.

## 4.3 Counter Design and Connection to Ring Oscillator