Institute for Parallel and Distributed Systems Universität Stuttgart Universitätsstraße 38 70569 Stuttgart Germany

Master Thesis Nr. 3385

# **DEVELOPMENT OF GENERIC** SCHEDULING CONCEPTS FOR OpenGL ES 2.0

Waqas Tanveer

Study Program:

INFOTECH

Examiner: Prof. Dr. Kurt Rothermel

Supervisor: Dipl.-Inf. Stephan Schnitzer

External Supervisor: Dipl.-Inf. Simon Gansel (Daimler AG)

Begin date: 01.11.2012 End date: 05.07.2013

CR-Classification: D.4.1

#### ABSTRACT

The ability of a Graphics Processing Unit (GPU) to do efficient and massively parallel computations makes it the choice for 3D graphic applications. It is been extensively used as a hardware accelerator to boost the performance of a single application like 3D games. However, due to increasing number of 3D rendering applications and the limiting resource constraints (especially on embedded platforms), such as cost and space, a single GPU needs to be shared between multiple concurrent applications (GPU multitasking). Especially for safety-relevant scenarios, like, e.g., automotive applications, certain Quality of Service (QoS) requirements, such as average frame rates and priorities, apply.

In this work we analyze and discuss the requirements and concepts for the scheduling of 3D rendering commands. We therefore propose our Fine-Grained Semantics Driven Scheduling (FG-SDS) concept. Since existing GPUs cannot be preempted, the execution of GPU command blocks is selectively delayed depending on the applications priorities and frame rate requirements. As FG-SDS supports and uses the OpenGL ES 2.0 rendering API it is highly portable and flexible. We have implemented FG-SGS and evaluated its performance and effectiveness on an automotive embedded system.

Our evaluations indicate that FG-SGS is able to ensure that required frame rates and deadlines of the high priority application are met, if the schedule is feasible. The overhead introduced by GPU scheduling is non-negligible but considered to be reasonable with respect to the GPU resource prioritization that we are able to achieve.

#### ACKNOWLEDGEMENTS

First of all I would like to thank Almighty God who has given me all the strength and the abilities to conduct this work.

I would like to pay special gratitude to my supervisor at the university, Mr. Stephan Schnitzer, who has encouraged, guided and motivated me during my thesis. He was always ready to take my questions patiently and arrange meetings whenever needed. I would also like to thank Mr. Simon Gansel for all the support he gave me at Daimler AG during this work.

Moreover, I am also thankful to Prof. Dr. Kurt Rothermel for giving me an opportunity for the thesis in his department.

I am also grateful to my family for their continuous support and encouragement which has helped me to meet my goals. Lastly, I am thankful to all those who have helped me in any way during the course of this work.

# **TABLE OF CONTENTS**

| Abstract                                    | i    |

|---------------------------------------------|------|

| Acknowledgements                            | iii  |

| Table of Contents                           | V    |

| List of Figures                             | vii  |

| List of Tables                              | viii |

| Acronyms                                    | ix   |

| 1. INTRODUCTION                             | 1    |

| 1.1. Motivation                             |      |

| 1.2. Challenges in GPU Scheduling           |      |

| 1.3. Contribution                           | 4    |

| 1.4. Organization                           | 6    |

| 2. RELATED WORK                             | 7    |

| 2.1. DRI                                    |      |

| 2.2. GERM                                   |      |

| 2.3. TimeGraph                              |      |

| 2.4. WDDM                                   |      |

| 2.5. Real-time scheduling algorithms        |      |

| 3. TECHNICAL BACKGROUND                     |      |

| 3.1. OpenGL ES and OpenGL ES 2.0            | 11   |

| 3.2. EGL                                    |      |

| 3.3. OpenGL ES 2.0 Graphics Pipeline        |      |

| 3.3.1. Vertex Arrays and Buffer Objects     |      |

| 3.3.2. Primitive Assembly                   |      |

| 3.3.2.1. Primitives                         |      |

| 3.3.2.2. Primitive Assembly Operations      |      |

| 3.3.3. Rasterization                        |      |

| 3.3.4. Vertex Shader                        |      |

| 3.4. Basic Scheduling Concepts              |      |

| 3.4.1. A Generic Scheduling Scenario        |      |

| 4. FINE-GRAINED SEMANTICS DRIVEN SCHEDULING |      |

| 4.1. Basic Idea                             |      |

| 4.1.1. Scheduling Goals                     |      |

| 4.1.2. Scheduling challenges                |      |

| 4.1.3. FG-SDS                               |      |

| 4.2. System Model                           |      |

| 4.3. A Sample GPU Multitasking Scenario     |      |

| 5. IMPLEMENTATION                           |      |

| 5.1. Overview                               |      |

| 5.2. FG-SDS Queues Architecture             |      |

| 5.2.1. GPU Scheduler Queue                  |      |

| 5.2.2. GPU Command Block Queue              |      |

| 5.2.3. GPU Command Queue                    |      |

| 5.3. GPU Command Classes                    |      |

| 5.4. Rendering Thread Context               |      |

| 5.5. Rendering Thread Functional Behavior   |      |

| 5.5.1. RT Initialization                    |      |

| 5.5.2. Enqueue Commands                                        |    |

|----------------------------------------------------------------|----|

| 5.5.3. Command Block End                                       |    |

| 5.5.4. Dispatch Policy                                         |    |

| 5.5.5. RT Exit Policy                                          |    |

| 5.6. GPU Scheduler Initialization                              |    |

| 5.7. Scheduling Thread Functional Behavior                     |    |

| 5.7.1. Sorting Based on RT Priorities                          |    |

| 5.7.2. Scheduling Policy                                       |    |

| 6. EVALUATION AND RESULTS                                      | 49 |

| 6.1. System Specifications                                     |    |

| 6.2. Multitasking Scenarios                                    |    |

| 6.2.1. Multitasking Scenario 1                                 |    |

| 6.2.2. Multitasking Scenario 2                                 |    |

| 6.3. Evaluation Metrics                                        |    |

| 6.3.1. Average Frame Rate (AFR)                                | 51 |

| 6.3.2. Probability of Meeting Deadlines (PMD)                  |    |

| 6.3.3. Probability Distribution of Frame Finish Times (PD-FFT) | 51 |

| 6.4. Results                                                   | 51 |

| 6.4.1. MTS-1                                                   |    |

| 6.4.1.1. Average Frame Rates                                   |    |

| 6.4.1.2. Probability of Meeting Deadlines                      | 53 |

| 6.4.1.3. Probability Distribution of Frame Finish Times        |    |

| 6.4.2. MTS-2                                                   |    |

| 6.4.2.1. Average Frame Rates                                   |    |

| 6.4.2.2. Probability of Meeting Deadlines                      |    |

| 6.4.2.3. Probability Distribution of Frame Finish Times        |    |

| 6.5. Summary                                                   |    |

| 7. CONCLUSION AND FUTURE WORK                                  | 65 |

| 7.1. Conclusion                                                | 65 |

| 7.2. Future Work                                               |    |

| 8. BIBLIOGRAPHY                                                | 67 |

| Declaration                                                    |    |

# **LIST OF FIGURES**

| Figure 1.1) Mercedes-Benz F125! research vehicle                                                | 2   |

|-------------------------------------------------------------------------------------------------|-----|

| Figure 1.2) system overview (a) typical (b) Fine-Grained Semantics Driven Scheduling (FG-SDS)   | 5   |

| Figure 2.1) DRI - a high-level overview                                                         | 7   |

| Figure 3.1) OpenGL ES 2.0 graphics pipeline [28]                                                | 12  |

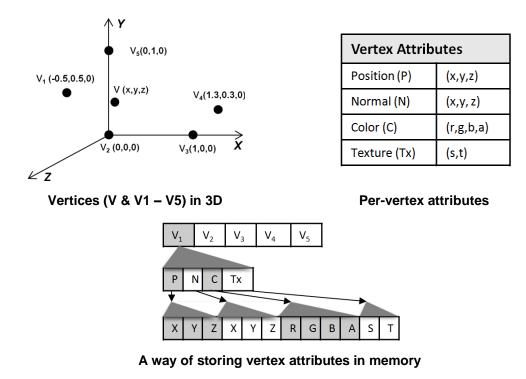

| Figure 3.2) An example of representing and storing vertex attributes                            | 13  |

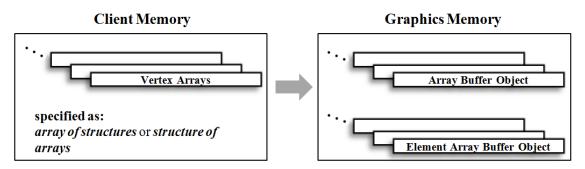

| Figure 3.3) An overview of data objects in client and graphics memory                           | 14  |

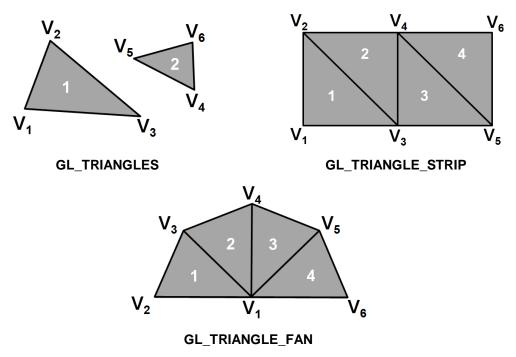

| Figure 3.4) Examples of triangle primitive types in OpenGL ES 2.0                               | 15  |

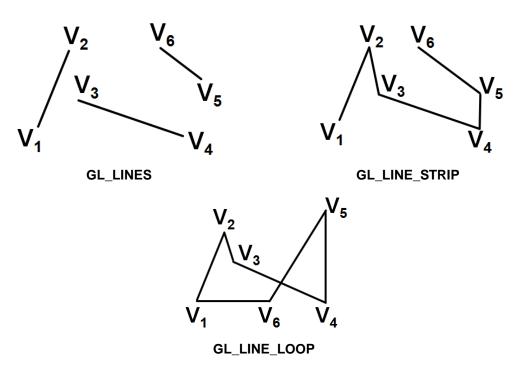

| Figure 3.5) Examples of line primitive types in OpenGL ES 2.0                                   | 16  |

| Figure 3.6) Example of points primitive type in OpenGL ES 2.0                                   | 16  |

| Figure 3.7) Primitive assembly stage operations and                                             | 17  |

| Figure 3.8) Viewing volume for clipping [28]                                                    | 18  |

| Figure 3.9) A depiction of perspective division [28]                                            | 19  |

| Figure 3.10) viewport transformation operation [28]                                             | 19  |

| Figure 3.11) A depiction of a window                                                            | 20  |

| Figure 3.12) An overview of rasterization stage with an example                                 | 20  |

| Figure 3.13) OpenGL ES 2.0 vertex shader, overview [28]                                         | 21  |

| Figure 3.14) OpenGL ES 2.0 vertex shader, example [28]                                          | 22  |

| Figure 3.15) Generic scheduling scenario with some requirements and goals                       | 24  |

| Figure 4.1) System Model                                                                        | 27  |

| Figure 4.2) Frame rendering of a sample graphic application set using GPU                       | 29  |

| Figure 5.1) FG-SDS implementation architecture                                                  | 31  |

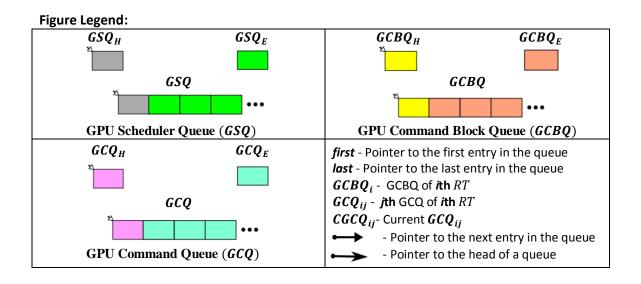

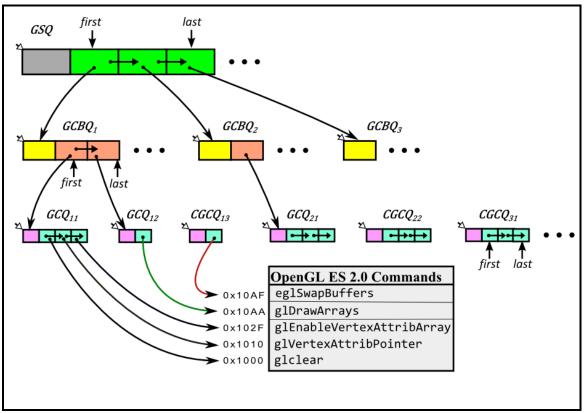

| Figure 5.2) FG-SDS Queues Architecture                                                          | 33  |

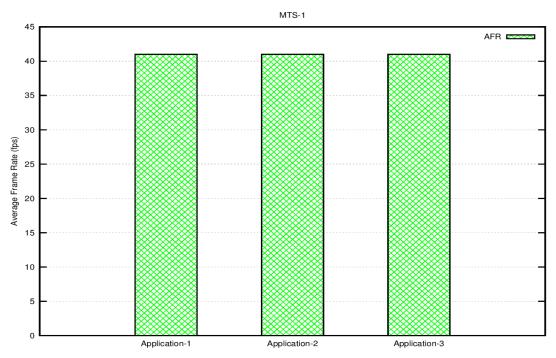

| Figure 6.1) AFRs of applications without any scheduling                                         | 52  |

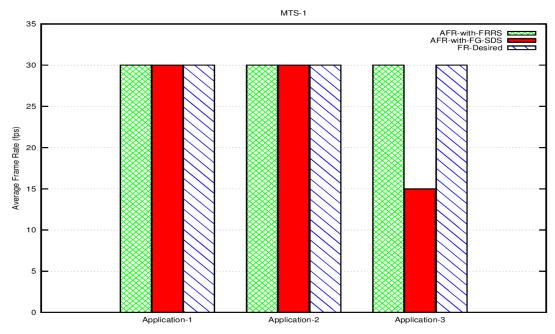

| Figure 6.2) A comparison of AFRs of applications with FRRS and FG-SDS (HPF) scheduling schemes  | 53  |

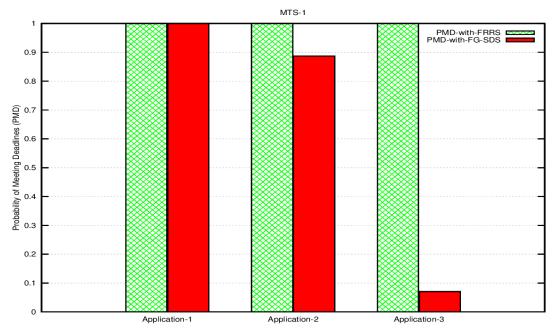

| Figure 6.3) A comparison of PMDs of applications with FRRS and FG-SDS (HPF) schemes             | 53  |

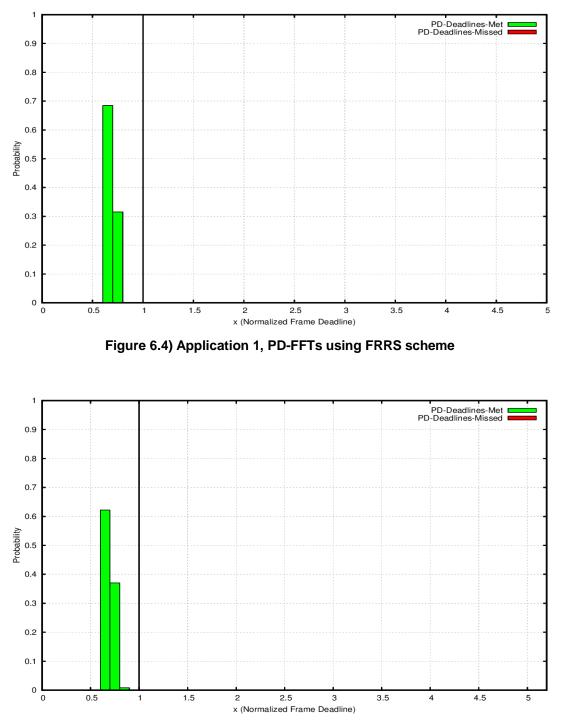

| Figure 6.4) Application 1, PD-FFTs using FRRS scheme                                            | 54  |

| Figure 6.5) Application 1, PD-FFTs using FG-SDS (HPF) scheme                                    | 54  |

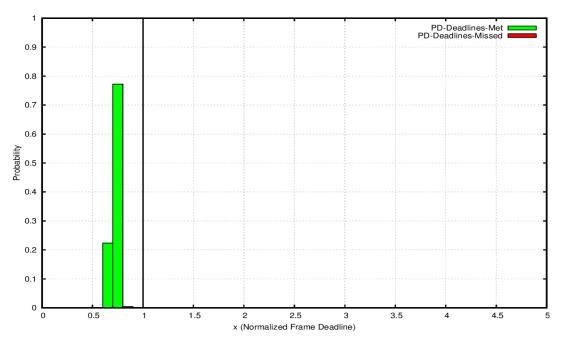

| Figure 6.6) Application 2, PD-FFTs using FRRS scheme                                            | 55  |

| Figure 6.7) Application 2, PD-FFTs using FG-SDS (HPF) scheme                                    | 55  |

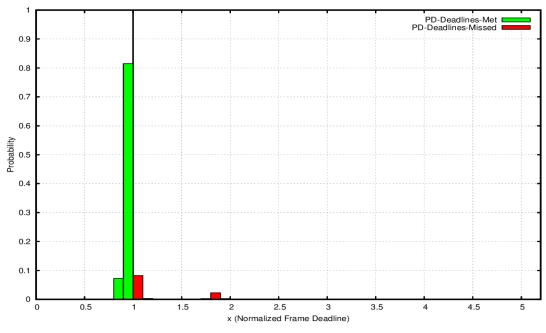

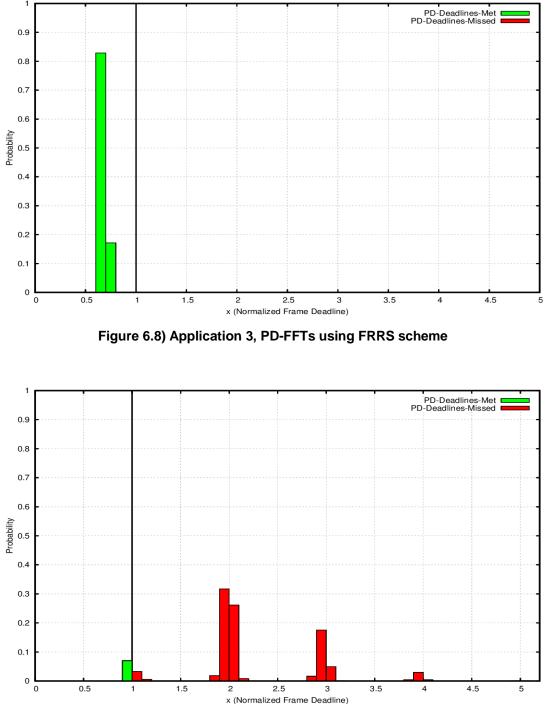

| Figure 6.8) Application 3, PD-FFTs using FRRS scheme                                            | 56  |

| Figure 6.9) Application 3, PD-FFTs using FG-SDS (HPF) scheme                                    | 56  |

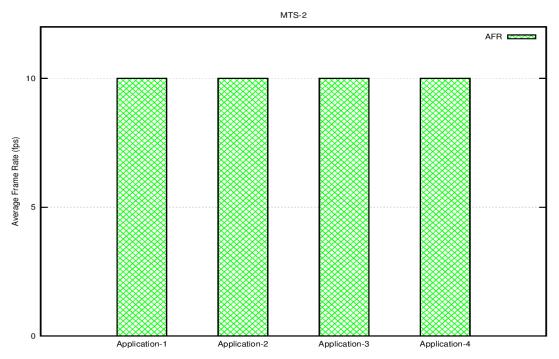

| Figure 6.10) AFRs of applications without any scheduling                                        | 57  |

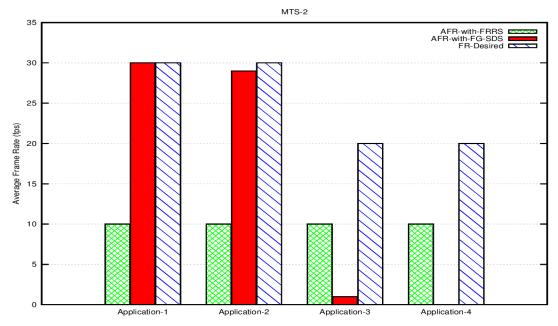

| Figure 6.11) A comparison of AFRs of applications with FRRS and FG-SDS (HPF) scheduling schemes | .58 |

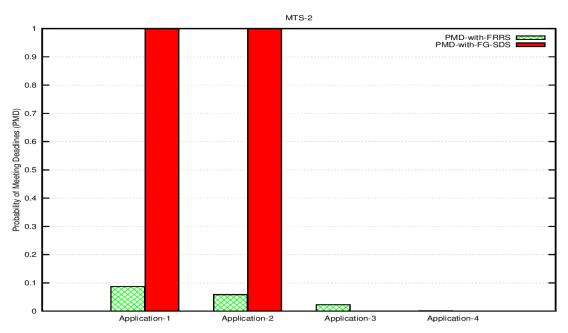

| Figure 6.12 ) A comparison of PMDs of applications with FRRS and FG-SDS (HPF) schemes           | 58  |

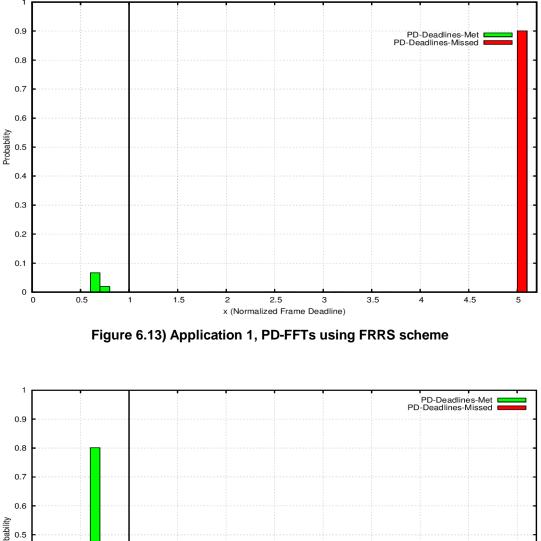

| Figure 6.13) Application 1, PD-FFTs using FRRS scheme                                           | 59  |

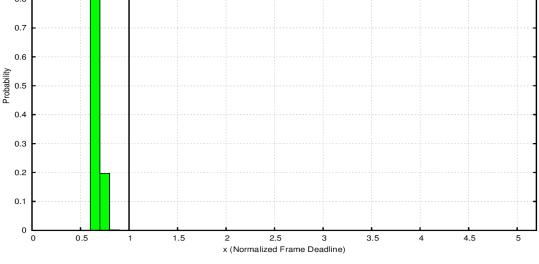

| Figure 6.14) Application 1, PD-FFTs using FG-SDS (HPF) scheme                                   | 59  |

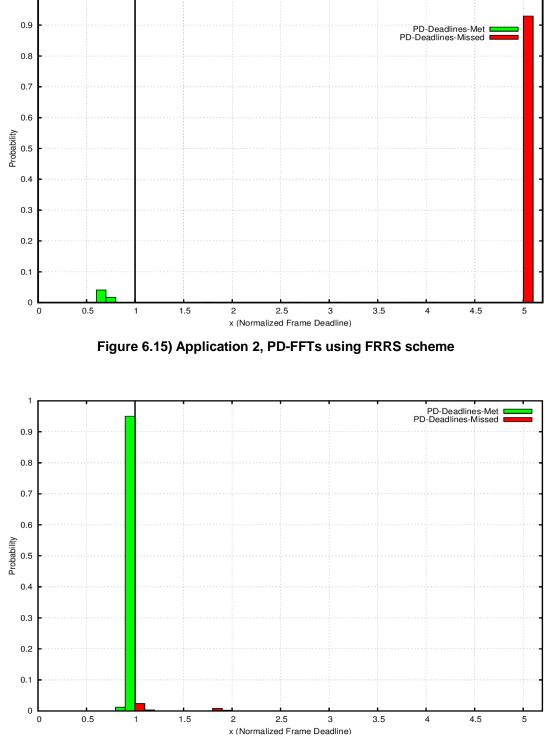

| Figure 6.15) Application 2, PD-FFTs using FRRS scheme                                           | 60  |

| Figure 6.16) Application 2, PD-FFTs using FG-SDS (HPF) scheme                                   | 60  |

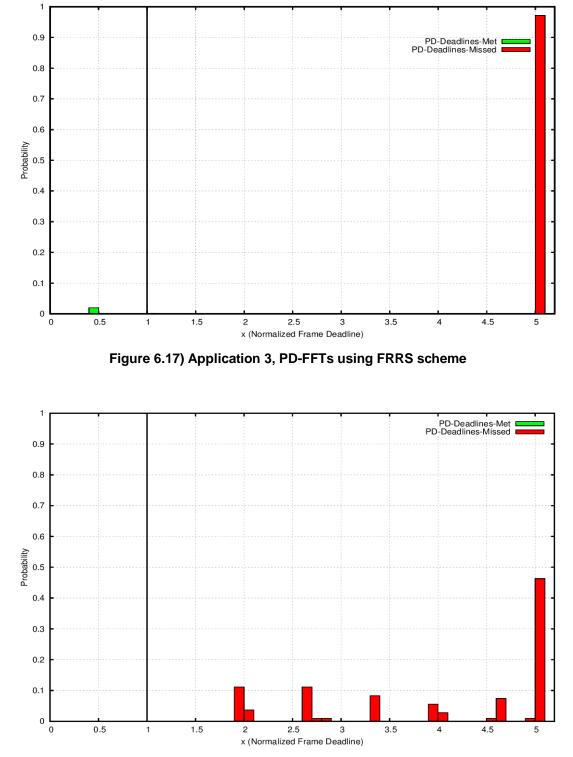

| Figure 6.17) Application 3, PD-FFTs using FRRS scheme                                           | 61  |

| Figure 6.18) Application 3, PD-FFTs using FG-SDS (HPF) scheme                                   | 61  |

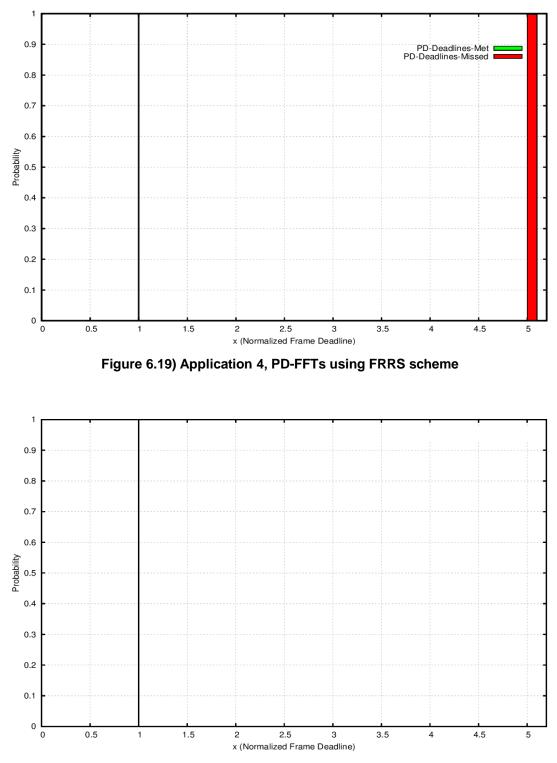

| Figure 6.19) Application 4, PD-FFTs using FRRS scheme                                           | 62  |

| Figure 6.20) Application 4, PD-FFTs using FG-SDS (HPF) scheme                                   | 62  |

# LIST OF TABLES

| Table 2-1) A summanry of key differences between                                         | .9 |

|------------------------------------------------------------------------------------------|----|

| Table 4-1) sample soft real-time graphic application set                                 | 28 |

| Table 5-1) List of parameters in a $GSQ_H$ and a $GSQ_E$                                 | 34 |

| Table 5-2) List of parameters in a $GCBQ_H$ and a $GCBQ_E$                               | 34 |

| Table 5-3) List of parameters in a $GCQ_H$ and a $GCQ_E$                                 | 35 |

| Table 5-4) List of OpenGL ES 2.0 Command Classes, their description and                  | 36 |

| Table 5-5) Parameters stored in Rendering Thread Context                                 | 36 |

| Table 5-6) Function called by an RT for initialization of required resources             | 37 |

| Table 5-7) Function called by an RT for enqueuing commands                               | 38 |

| Table 5-8) Function called by an RT at the end of a command block                        | 39 |

| Table 5-9) Function called by an RT for dispatching its command blocks (Part-1)          | 40 |

| Table 5-10) Function called by an RT for dispatching its command blocks (Part-2)         | 41 |

| Table 5-11) Function called by an RT when it exits                                       | 42 |

| Table 5-12) Function called for GPU Scheduler initialization                             | 43 |

| Table 5-13) Function called by the ST                                                    | 44 |

| Table 5-14) Function called by the ST for sorting RTs accoring to their priorities       | 45 |

| Table 5-15) Function which implements the Highest Priority First (HPF) scheduling policy | 47 |

| Table 6-1) An overview of the system specification of the i.MX6 embedded platform [31]   | 49 |

| Table 6-2) MTS-1 application set with some QoS parameters                                | 50 |

| Table 6-3) MTS-1 application set with some QoS parameters                                | 50 |

### ACRONYMS

| AFR              | Average Frame Rate                                     |

|------------------|--------------------------------------------------------|

| FG-SDS           | Fine-Grained Semantics Driven Scheduling               |

| FRRS             | Frame Rate Restricted Scheduling                       |

| GCBQ             | GPU Command Block Queue                                |

| GCQ              | GPU Command Queue                                      |

| GPU              | Graphics Processing Unit                               |

| GPU Multitasking | Execution of multiple concurrent applications on a GPU |

| GSQ              | GPU Scheduler Queue                                    |

| HPF              | Highest Priority First                                 |

| MTS - I          | Multitasking Scenario - I                              |

| PD-FFT           | Probability Distribution of Frame Finish Times         |

| PMD              | Probability of Meeting Deadlines                       |

| RT               | Rendering Thread                                       |

| RTC              | Rendering Thread Context                               |

| ST               | Scheduling Thread                                      |

### 1.1. Motivation

As we move forward in this technological era, besides discovery of new technologies there is also a strong focus on the efficient and optimal use of those we already have. For example, in terms of computing technology on one side there is a thirst for more and more computational power on a single small chip which is being addressed in one way by scaling down individual transistor size and increasing its density [1, 2]. While on the other side, there is an effort to use this computational power efficiently for a variety of application areas such as graphics, simulations, multimedia and communications etc.

One of the parts of this latter effort is multitasking, concurrent execution of multiple applications sharing common computing resources. It is needed due to the tightness of the resource constraints, such as processing power, memory, space and cost etc., and increasing number of applications of the computing devices. The challenge in multitasking is to find a scheduling mechanism for the applications sharing computing resources, as per specified requirements such as priorities. This mechanism is typically enforced with the help of a scheduler which works on the basis of a scheduling policy. For this purpose numerous scheduling techniques [3, 4] have been developed depending on different requirements of applications and scheduling goals. This work contributes to the latter effort, as discussed earlier, by providing some scheduling concepts for the multitasking of graphic applications on a Graphics Processing Unit (GPU).

Computer graphics, like many other application areas, is growing rapidly [5] due to the rise of ubiquitous computing and the advances in processor technology. There is a wide range of graphical applications [6], such as Graphical User Interfaces (GUIs), video games, animation, advanced visualization, augmented and virtual reality etc., which facilitate enhanced user experience, entertainment and scientific research etc. Most of these applications use traditional 2D rendering techniques such as rasterization; however, due to advances in hardware capabilities 3D rendering techniques [7], such as ray tracing, bump mapping etc., are also getting pace in their usage. The applications which use 3D rendering are highly compute intensive and typically require a hardware accelerator to boost their execution. A GPU serves that purpose by working in cooperation with a Central Processing Unit (CPU).

A GPU is also a processor like CPU. However, it has more processing power due to a larger number of cores. It has the ability to perform efficient and massively parallel computations. It is extensively used as a graphics engine for 3D rendering in graphic applications such as 3D games, advanced navigation etc. It is also used for general purpose computing (GPGPU) to boost the performance of many compute intensive applications, such as advanced scientific simulations, using CUDA framework [8]. Due to these capabilities it is now an integral part, integrated or dedicated [9], of many computing systems that range from desktop PCs, laptops and handheld devices like smart phones and tablets at one end to supercomputers on the other. By having a huge computational power bank, these systems can address the computational needs of a broad scope of applications.

However, as the number of applications accelerating on GPU increase with having less flexibility in constraints such as power, space and cost especially on small handheld, mobile and embedded devices, a GPU has to allow multitasking in such a way that applications meet their Quality of Service (QoS) requirements besides maximizing GPU utilization. In case of multitasking for 3D rendering applications, QoS requirements could be average frame rates, priorities and frame deadlines (for real-time applications).

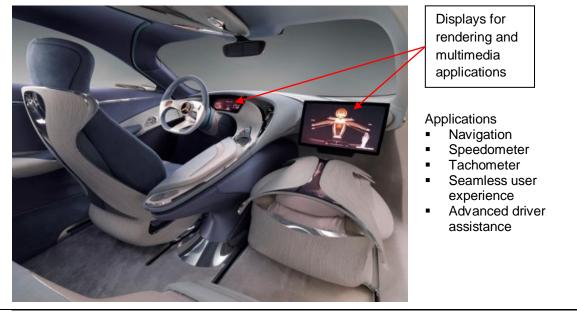

Consider an example of a future car, as shown in Figure 1.1, providing infotainment and telematics applications [10]. The displays on the dashboard are used to provide an interactive interface and seamless experience to the user/users. In this environment we could have a number of applications, such as navigation, displaying speedometer & fuel statistics, audio and/or video communication and advanced driving assistance etc. Some of these applications, such as speedometer, tachometer and navigation etc., use 3D rendering for their execution which is done with the help of GPU platform/platforms.

Figure 1.1) Mercedes-Benz F125! research vehicle future telematics "@yourCOMAND" [11]

Typically, each 3D rendering application has its own QoS requirements, as discussed earlier, depending on its quality and safety. For example, the real-time applications, such as speedometer, must be prioritized over other applications such as a video call or some non real-time application. Additionally, frame rendering of these real-time applications have to be done before their deadlines, otherwise it may cause an accident due to the delayed response.

In the earlier discussion we pointed out some constraints on the computing resources, same constraints apply in this example and a single GPU has to be shared by multiple applications executing concurrently. From the user's point of view some applications may seem to be running at the same time, however, a scheduling mechanism is needed at the device end which can grant access to the applications for execution on the GPU depending on their QoS requirements.

Multitasking on a GPU can be done either in time domain [12, 13, 14] by allowing concurrent execution of multiple applications or in spatial domain [15] by partitioning GPU resources among applications and allowing them to run in parallel. This work comes under the domain of the former approach and is focused on the development of scheduling concepts for multitasking of OpenGL ES 2.0 graphic applications executing concurrently on a GPU. In order to understand the challenges of GPU scheduling we have to analyze the concepts of CPU scheduling which are not fully applicable for a GPU. These challenges are discussed in the following subsection.

### 1.2. Challenges in GPU Scheduling

Typically, a CPU scheduler has the flexibility of preemption, which means it can stop an application's execution at any time and grant access to another application for execution on the CPU, depending on the scheduling policy. This capability of preemptive multitasking enables a CPU to comply with the requirements of high priority applications executing concurrently with other applications. Moreover, it also enables the scheduler to grant access to an application without knowing its execution cost.

However, once a task is submitted for execution to a GPU it cannot be preempted which is an unpleasant limitation for real-time multitasking [14]. The main reason for this limitation is the dependency of GPU commands of graphic applications on specific execution context or GPU state such as transformation matrices, lighting parameters etc. Since graphic applications, such as those discussed in car example, have to maintain average frame rates and some also have real-time requirements, GPU preemption will not only result in QoS degradation but also the execution results of commands may not be correct due to their execution against incorrect or undetermined GPU state. If it occurs in time critical application then it may also result in bad consequences as well. Therefore a GPU scheduling approach is needed which has to meet QoS requirements of applications without preemption.

Additionally, the execution cost of command/commands has to be known before dispatching them to the GPU [12, 13, 14]. In this way an application can also be stopped from monopolizing the GPU resources thus allowing other applications to execute their commands on the GPU and meet their real-time requirements.

Normally a graphic application is linked to a graphics library, such as OpenGL [16] for desktop computers or OpenGL ES [17] for embedded or handheld platforms, which is part of the user-level GPU driver. Here the commands are translated to low level GPU specific commands. In Direct Rendering Infrastructure (DRI) [18], applications accumulate their commands in a command buffer before they are sent to the GPU. There are two cases in which these buffered commands are dispatched to the kernel level driver, either the command buffer is full or there is an explicit flush, using **ioctl** [13] call. The kernel level driver handles this call and enqueues the command group metadata to the ring buffer. The GPU has direct access to the ring buffer from where it takes the command group metadata and using DMA fetches the commands and executes them [13]. To the best of our knowledge, once the commands are in the ring buffer it may not be possible to change their order of execution. Therefore for GPU multi-tasking any scheduling has to be performed before the commands are inserted into the ring buffer.

There are two possibilities for the implementation of a GPU scheduler, it could be implemented either in user space or kernel space. In kernel space a better GPU utilization could be achieved as commands are enqueued in groups or batches [12, 13, 14]. Also scheduling at this coarse granularity also results in less scheduling overhead. However, because we cannot interpret command semantics at this level, it is possible that GPU gets occupied longer by an application which can delay the execution of another high priority application's commands. Also the lack of accuracy in the execution time prediction of command groups can cause errors in scheduling decisions. Therefore for real-time multitasking environments scheduling at this level may not be the optimal solution.

## 1.3. Contribution

In this thesis we have devised, implemented and evaluated a GPU scheduler in user space for multiple OpenGL ES 2.0 applications executing concurrently on a GPU.

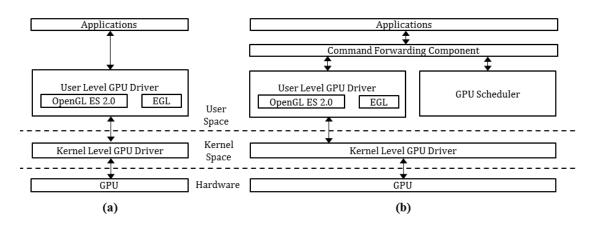

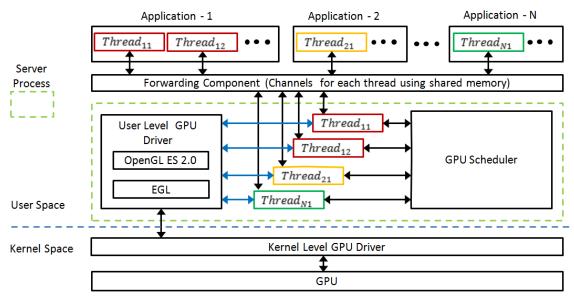

A comparative overview of a typical system and our Fine-Grained Semantics Driven Scheduling (FG-SDS) system is presented in Figure 1.2 (a) and (b) respectively. At the top level, we have multiple OpenGL ES 2.0 applications running concurrently. For the execution of their GPU commands these applications need access to the GPU hardware, shown at the lowest level in the figure, which is provided with the help of a software mechanism consisting of a run time framework and a kernel level driver. Normally, as shown in (a), an application executes its commands by calling the native implementation of the OpenGL ES 2.0 in the user level driver. The final access to the GPU is provided by kernel level GPU driver depending on its scheduling policy. The disadvantages of scheduling at this level are already discussed in the previous section.

Figure 1.2) system overview (a) typical (b) Fine-Grained Semantics Driven Scheduling (FG-SDS)

In FG-SDS system, as shown in (b), instead of calling the native implementation of the OpenGL ES 2.0 directly, the commands of each application are passed to the GPU scheduler by forwarding component using shared memory. The GPU scheduler makes logical command blocks for each application's thread separately and depending on its scheduling policy selects one of these threads to dispatch their commands to the GPU. In Once an application's thread is granted permission to dispatch, it does so by calling the native implementation of the commands in its command block one by one through forwarding component. This scheduling approach is driver independent, however, it is runtime dependent and works for OpenGL ES 2.0.

The main advantage we get by scheduling in user space is the possibility to interpret individual command semantics. By using command semantics the granularity at which the scheduling is performed is fine grained to a command block level which may consist of one to a few number of commands. Moreover, it allows us to dispatch command blocks on per frame basis which enables the applications to meet their frame deadlines. It also reduces the time for which an application can occupy GPU thus allowing other applications to execute their commands. This idea uses time prediction for individual command blocks. This prediction is based on an earlier work [19] which measures execution times of different OpenGL ES 2.0 commands.

Based on these concepts, we have devised a scheduling policy known as Highest Priority First (HPF). The main features of HPF are as follows:

- Highest priority application always gets a chance to execute its commands therefore there is a high probability that it meets its frame deadline.

- Low priority applications cannot monopolize the GPU and are only allowed to execute their command blocks if the highest priority application is not ready and if its deadline is guaranteed.

- The opportunity for execution of an application follows a descending order of their priorities, therefore higher priority applications have more chance to execute than lower priority applications.

- Because of the fine-grained granularity (command blocks) of scheduling, there is a possibility for low priority applications to execute if feasible.

# 1.4. Organization

The rest of this report is organized in the following sequence. In Chapter 2, some related work has been presented briefly which is also focused on similar scheduling challenges of GPU multitasking. Chapter 3 discusses the concepts related to OpenGL ES 2.0, EGL, graphics pipeline and basic scheduling. The basic idea and the detailed concepts of our FG-SDS model are presented in Chapter 4. In Chapter 5, the implementation details of FG-SDS model and the HPF scheduling policy are discussed. The generic evaluation metrics and the results obtained for some multitasking scenarios are presented in Chapter 6. Finally, all the work we have done has been concluded in Chapter 7 along with its future direction.

# **2. RELATED WORK**

We discussed in Chapter 1 that a GPU needs multi-tasking in order to cope with increasing number of applications and narrowing resource constraints. We also pointed out some of the challenges in GPU scheduling that are posed in this regard due to non-preemptive behavior of GPU execution model. We also introduced our FGS system, incorporating a GPU scheduler, to address the QoS requirements of OpenGL ES 2.0 applications. In this Chapter we briefly discuss some of the previous works, which are also focused on resolving similar issues, along with the key conceptual comparisons to our scheduling concepts. We also look in to the limitations of driver support, provided by Windows and Linux, for real-time multitasking on a GPU.

### 2.1. DRI

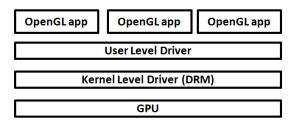

Direct Rendering Infrastructure (DRI) [18] [20] is a software framework which allows a GPU to be used directly, without making a path through the X server (although it is used to render frames to the screen), for 3D hardware acceleration on UNIX like platforms in a safe and efficient manner [18]. Primarily, it has been developed to support fast implementations using Mesa 3D graphics library [21], an open source implementation of OpenGL specification. Besides OpenGL, Mesa also provides support for OpenGL ES [21], an open source graphic library for 3D graphic applications running on embedded and handheld platforms.

Figure 2.1) DRI - a high-level overview

Under DRI framework several open source drivers [21], such as Nouveau [22] for Nvidia graphic cards, are available. A high level overview of DRI is presented in Figure 2.1. The user level driver translates commands of a 3D graphic application to device specific commands and passes them to the kernel level driver which is also known as Direct Rendering Manager (DRM). Depending on the scheduling policy the DRM submits these commands to the command ring buffer from where they are read and executed by the GPU [13]. The next two subsections describe the modifications proposed to this basic DRI frame-work for GPU multitasking.

### 2.2. GERM

In order to provide a fair share, approximately same amount of GPU execution time, of GPU resources for multiple applications concurrently executing on a GPU, Graphic Engine Resource Manager (GERM) [12, 13] was introduced. It provided modifications to both user level and kernel level drivers to address the limitations of Direct Rendering Infrastructure (DRI) [20]. Prior to GERM, applications were not provided with fair share of GPU resources due to following limitations [13] of DRI:

- Before submitting commands to the kernel level driver a client application needed hardware lock to ensure isolation, one application executing its commands on a GPU against its correct graphics state. The user level driver used to fulfill this requirement for each client application. However, it made possible for a malicious application to hold lock for indefinite time thus starving other applications of their share of GPU time.

- There was also an imbalance between the times consumed by an application on a CPU and a GPU. Moreover, the granularity of scheduling was a command batch, commands sent between lock acquisition and its release by a client application. Since the execution time was not known for a command batch, could be an arbitrarily long value, some applications got more share than others.

GERM removed these limitations by introducing command queues in the kernel space for each client application. Additionally, the granularity of scheduling was also fine grained from command batch to a command group which is a group of commands sent atomically to the GPU. The GPU scheduler, with the help of command group execution time prediction, dispatched commands to the command ring buffer based on deficit round robin policy [12, 13]. It was implemented in kernel space as part of the device driver.

However, there are some key differences between GERM and FG-SDS approaches. A summary of these differences is also presented in Table 2-1. First of all, the scheduling goals of GERM are fundamentally different from those of FG-SDS. GERM's main scheduling goal is to provide fairness between multiple applications with no real time requirements or priorities, while FG-SDS has soft real-time requirements and it also has to provide prioritization. If we also compare the granularity of scheduling in GERM, based on command groups, to that of FG-SDS, based on command blocks, the one in former is coarse-grained as compared to the latter one. Using such a coarse-grained scheduling granularity it is difficult to meet real-time requirements. Moreover, the complexity of implementation, modification to both user level and kernel level drivers, makes GERM less portable which is not the case for FG-SDS.

# 2.3. TimeGraph

One of the works related to our work is TimeGraph [14]. It is a scheduling mechanism implemented in the kernel space, as part of the device driver (Nouveau [22]), to support multi-tasking on a GPU in soft real-time environments. It provides prioritization and isolation for multiple OpenGL applications with the help of a GPU Command Scheduler and a GPU Reserve Manager respectively. The high priority applications are prioritized over low priority applications and at a time only one application executes on the GPU. The scheduling is performed at the granularity of GPU command groups where each such group may consist of multiple GPU commands. Moreover, for the prediction of the execution time of a GPU command group, TimeGraph also provides a GPU Command Profiler.

However, there are some key differences between TimeGraph and our FG-SDS model. The major difference is the level of implementation which is kernel space and user space in each case respectively. The other differences and benefits are intuitively derived on the basis of this basic difference. TimeGraph doesn't interpret individual command semantics whereas FG-SDS model is based on command semantics interpretation. This is one of the major benefits we get at the user space level. Due to this capability we can create fine-grained scheduling granularity of command blocks. Moreover, FG-SDS model takes care of frame deadlines in case of time critical applications whereas there is no such notion in TimeGraph.

|    |                                    | GERM                                                        | TimeGraph                                                         | FG-SDS                                                            |

|----|------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|

| 1. | Scheduling goals                   | Fairness (non real-<br>time requirements, no<br>priorities) | Prioritization and<br>Isolation with<br>real-time<br>requirements | Prioritization and<br>Isolation with<br>real-time<br>requirements |

| 2. | Implementation<br>level            | Both user space and kernel space                            | kernel space                                                      | user space                                                        |

| 3. | Scheduling<br>granularity          | Coarse-grained based<br>on<br>command groups                | Coarse-grained based<br>on<br>command groups                      | Fine-grained based on command blocks                              |

| 4. | Frame deadlines                    | No notion                                                   | No notion                                                         | Yes                                                               |

| 5. | Individual<br>command<br>semantics | Are not interpreted                                         | Are not interpreted                                               | Based on the<br>interpretation of<br>command semantics            |

A summary of major differences between the GERM, TimeGraph and our FG-SDS approaches are listed in the following table.

Table 2-1) A summanry of key differences between

GERM,TimeGraph and FG-SDS

### 2.4. WDDM

Windows Display Driver Model (WDDM) provides basic architectural design principles for the display driver development for Windows Vista and later [23]. Typically, the graphic applications for Windows are developed using Direct3D API. However, OpenGL applications are also portable to Windows. Applications need one of these API's to communicate to the user level driver which is a Dynamic-link library [23]. The GPU access for an application is finally provided by kernel level driver, known as display miniport driver, through DirectX graphics subsystem which manages display port, video memory and GPU scheduling [23].

The commands of an application are passed to the GPU in the form of batches, which are coarse-grained with indefinite execution time, similar to the command batch idea discussed in section 2.2. If a command batch takes longer than the time it is permitted on a GPU then the GPU scheduler tries to preempt currently executing application's task by initiating a "wait" on a timeout [24]. If this task is not preempted within timeout then GPU scheduler initiates a Timeout Detection and Recovery (TDR) process to reset the GPU [24]. GPU preemption is possible at various granularities for graphics and compute applications sharing a GPU [24]. In order to avoid the initiation of TDR process the preemption granularity has be less than timeout.

To the best of our knowledge, although the preemption mechanism, as discussed above, allows high priority GPU tasks to be more responsive, however, it is not suitable for real-time applications because of following reasons [24]:

- Time taken by preemption is not known and could be indefinite; therefore there is no guarantee that high priority or time-critical applications would meet their deadlines. In worst case, GPU would be reset resulting in a system failure.

- GPU state has to be saved which adds more latency, therefore making it more difficult to meet real-time requirements.

### 2.5. Real-time scheduling algorithms

There are many classical scheduling algorithms [4], such as Rate-Monotonic scheduling (RMS), Earliest Deadline First (EDF) etc., which are used for real-time multitasking on a CPU. However, owing to the limitations of 3D graphical applications, such as dependency of GPU commands on specific graphic context, indefinite execution time of tasks executed on a GPU and non-preemptive nature of GPU scheduling, most of these algorithms are not applicable, as it is, in case of a GPU. In order to overcome these limitations, a new preemption mechanism is needed with a fine-grained preemption granularity. Moreover, execution time prediction of each individual grain, block of commands, is also required which can be used before the submission of a task to the GPU to stop an application from monopolizing a GPU. However, basic concepts remain the same such as deadlines, priorities etc.

# **3. TECHNICAL BACKGROUND**

In the previous chapter, we discussed some of the related work and also presented some key conceptual differences to our work. Before going in to the discussion of our main idea, in this chapter we briefly look into some background concepts that are needed to facilitate the understanding of details presented in the next chapters.

This chapter has been divided into two major parts. The first part includes an introduction to OpenGL ES [17]/OpenGL ES 2.0 [25] and a brief description of OpenGL ES 2.0 graphics pipeline (individual stages and related concepts with some examples). It also includes a brief introduction to EGL [26], a native platform graphics interface [27]. In the second part, some basic concepts related to scheduling are discussed.

### 3.1. OpenGL ES and OpenGL ES 2.0

OpenGL ES [17] is an open source and cross-platform API for advanced 2D/3D graphics on embedded and handheld platforms such as smart phones, gaming consoles and others used in vehicles, avionics etc [28]. Besides providing high performance graphics, it is specifically designed to address the resource constraints, such as processing power, memory and power budget, of these platforms.

It has been derived from OpenGL [16] which is also an open source and crossplatform API for 2D/3D desktop graphics. To address the constraints, as mentioned previously, unnecessary redundancies have been removed from OpenGL API and required extensions have been added. Each version of its specification has been derived from the corresponding version of OpenGL, e.g. OpenGL ES 2.0 has been derived from OpenGL 2.0.

As we are focused on the development of scheduling concepts for OpenGL ES 2.0 specification, which consists of OpenGL ES 2.0 API specification [25] and OpenGL ES Shading Language specification (OpenGL ES SL) [29], therefore some important concepts from these specifications along with some details from OpenGL ES 2.0 Programming Guide [28] are presented in this chapter unless specified otherwise.

### 3.2. EGL

Typically, the graphic applications need surfaces such as windows to which they can render, which are managed by native windowing system such as X window system for UNIX like systems. EGL [26] is an interface between client graphic APIs such as OpenGL ES 2.0 and a native platform window system. Some of the major services provided by EGL to client APIs are summarized as follows [27, 28]:

• Communication mechanisms between different client APIs (e.g. OpenGL ES 2.0 and OpenVG) and the native window system.

- Management of on-screen and off-screen rendering surfaces (windows, pbuffers and pixmaps) which include their creation and sharing between different APIs. OpenGL ES 2.0 supports double-buffered windows only.

- Creation and management of graphics contexts for client applications

- Synchronization between client APIs and native windowing system

## 3.3. OpenGL ES 2.0 Graphics Pipeline

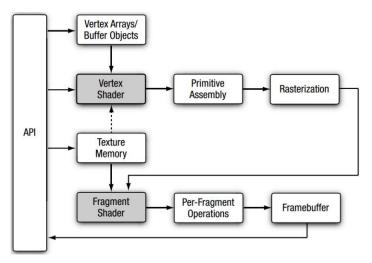

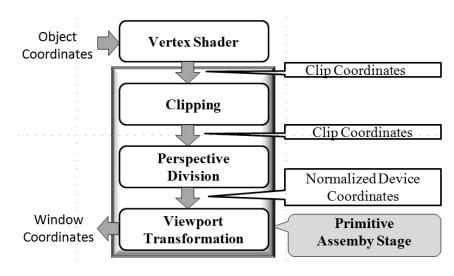

Typically in graphics, objects in 3D space are represented by polygon meshes which are collections of vertices, edges and faces [30]. The graphics pipeline, typically same as shown in Figure 3.1, takes these vertices with appropriate attributes, discussed in the next section, along with some other data as input and perform geometric operations specified by shaders, vertex and fragment shaders (programs), with some additional operations. The end result is a 2D image, stored in framebuffer as a pixel collection, which can be displayed on a screen such a monitor.

Figure 3.1) OpenGL ES 2.0 graphics pipeline [28]

The graphics pipeline of OpenGL ES 2.0 is shown in Figure 3.1. There are a number of stages in this pipeline, with grey boxes showing programmable stages. A brief description of each stage with some examples is presented in the upcoming sections.

#### 3.3.1. Vertex Arrays and Buffer Objects

In the previous section, we discussed that vertices are the basic input to a graphics pipeline besides some other input parameters such as constants. Before any operations are performed on these vertices, they need to be stored in an efficient manner. In OpenGL ES 2.0, vertex arrays and buffer objects provide methods for storing and caching vertex data, also known as vertex attributes, respectively [28].

Vertex arrays are buffers mapped to the application's address space, also known as client's space. They are used to store per-vertex attributes in an efficient manner and are specified using glVertexAttribPointer function. Figure 3.2 (a) shows an

example of six vertices represented in 3D coordinate space. Each of these vertices can represented by its attributes, such as position, normal, color and texture coordinates etc., as shown in Figure 3.2 (b).

Figure 3.2) An example of representing and storing vertex attributes

Since OpenGL ES 2.0 implements a programmable pipeline, the names of these attributes can also be specified by the application. In OpenGL ES 2.0, the minimum number of per-vertex attributes is *eight* and the maximum number is specified by GL\_MAX\_VERTEX\_ATTRIBS parameter [28]. Moreover, each attribute is specified by a generic attribute index ranging from 0 to GL\_MAX\_VERTEX\_ATTRIBS-1. There are two commonly used methods for specifying, allocating and storing vertex attributes, each having different performance benefits [28], which are:

- *array of structures* all the attributes of a vertex are stored in a single buffer, contiguous memory. This method has been elaborated in Figure 3.2 (c) where v1 attributes, shown in Figure 3.2 (b), are stored in a single buffer.

- structure of arrays each attribute is stored in a different buffer, not shown here.

In OpenGL ES SL, vertex attributes variables are declared in vertex shaders using attribute qualifier. Before a primitive, discussed in section 3.3.2, can be drawn, these attribute variables need binding to appropriate generic vertex attribute indices. This binding can either be specified by an application or by the OpenGL ES 2.0 itself. In this way vertex data is read from correct locations into the vertex shaders.

However, sometimes vertex data from vertex arrays have to be fetched into the high performance graphics memory before drawing any primitives. Vertex buffer objects are locations in graphics memory specified for this purpose. They are allocated to store or cache the vertex data. Since graphics memory offers a higher bandwidth as compared to the client's memory, buffer objects can significantly improve the performance when the same vertex data is used frequently by the draw commands. Besides vertex data, element indices specifying how the primitives are to be drawn can also be cached in to appropriate buffer objects. OpenGL ES 2.0 provides *array buffer objects* and *element array buffer objects* for storing/caching vertex data and primitive indices respectively. A generic overview of vertex arrays and buffer objects has been presented in Figure 3.3.

Figure 3.3) An overview of data objects in client and graphics memory

The next stage in the graphics pipeline is vertex shader (cf. section 0), however, primitive assembly and rasterization stages are discussed next due to the fact that the type of individual primitives that are to be drawn and their corresponding vertex indices are specified before they are actually passed to the vertex shader.

### 3.3.2. Primitive Assembly

In this stage of the graphics pipeline various primitives, basic geometric objects, are drawn by assembling vertices, transformed by vertex shader, in a specified order. Prior to the explanation of operations that are performed in this stage, these primitives are discussed below.

### 3.3.2.1. Primitives

In OpenGL ES 2.0 three kinds of primitives are supported which are triangles, lines and points sprites. These primitives can be drawn by executing glDrawArrays or glDrawElements command. A brief description of each primitive type along with its subtypes, if any, is presented in the next three subsections.

### 3.3.2.1.1. Triangles

There are three ways in OpenGL ES 2.0 by which triangles primitives can be drawn. An example for each one, named by its specific type, is shown in Figure 3.4 (a), (b) and (c). In Figure 3.4 (a) two triangles are drawn using two sets,  $(V_1, V_2, V_3)$  and  $(V_4, V_5, V_6)$ , of vertices with each one consisting of three unique and adjacent vertices. This mode is specified as GL\_TRIANGLES.

Figure 3.4) Examples of triangle primitive types in OpenGL ES 2.0

Similarly in (b), four triangles are drawn with  $(V_1, V_2, V_3)$ ,  $(V_2, V_3, V_4)$ ,  $(V_3, V_4, V_5)$  and  $(V_1, V_2, V_3)$  sets of vertices respectively, using primitive mode GL\_TRIANGLE\_STRIP. Note that in each case of two consecutive triangles, two vertices are common between the two sets, the last two from the first one and the first two from the second one. Another type of triangle primitive is specified as GL\_TRIANGLE\_STRIP which is shown in Figure 3.4 (c). In this case four triangles are drawn by  $(V_1, V_2, V_3)$ ,  $(V_1, V_3, V_4)$ ,  $(V_1, V_4, V_5)$  and  $(V_1, V_5, V_6)$  sets of vertices respectively. As its name suggests, a fan is drawn with the common vertex between all the sets at the center and all other vertices making its wings. Note the relation between two adjacent sets of vertices in each case.

#### 3.3.2.1.2. Lines

Figure 3.5, (a), (b) and (c), shows three ways in which line primitives can be drawn in OpenGL ES 2.0. In the first case, i-e (a) specified by  $GL\_LINES$ , three separate line segments are drawn with  $(V_1, V_2)$ ,  $(V_3, V_4)$  and  $(V_5, V_6)$  sets of vertices. The next one, shown in (b), is specified as  $GL\_LINE\_STRIP$ . In this case five connected lines are drawn by connecting each vertex with its preceding vertex, with the exception of the vertex with a starting index.

Figure 3.5) Examples of line primitive types in OpenGL ES 2.0

The third case, shown in (c) is similar to (b), however, the vertex with the last index (6) is also connected to the vertex with the starting index (1). It is specified as  $GL\_LINE\_LOOP$ .

#### 3.3.2.1.3. Point sprites

Each vertex can also be drawn separately with the help of GL\_POINTS primitive type. An example of this type is shown in Figure 3.6 where 20 vertices are drawn.

GL\_POINTS

Figure 3.6) Example of points primitive type in OpenGL ES 2.0

#### 3.3.2.2. Primitive Assembly Operations

As the vertices are processed through different stages of the graphics pipeline, their coordinates such as position coordinates undergo various transformations. Figure 3.7 gives an overview of the transformations which are performed as the vertices are processed through the vertex shader and the primitive assembly stages. Moreover, it also

gives information about the operations that are performed during primitive assembly stage.

Figure 3.7) Primitive assembly stage operations and corresponding coordinate systems

In the real world objects are typically represented or modeled in object or local coordinate system as shown in Figure 3.2 (a). Referring to Figure 3.7, it can be seen that the input vertices to the vertex shader are in this coordinate system. After the processing by the vertex shader the vertices are in clip coordinates and are passed to the primitive assembly stage which comprises clipping, perspective division and the viewport transformation operations.

In the following subsections these operations and their corresponding coordinate systems are described briefly. In each case the example is given from the vertex position attribute represented as p(x, y, z, w).

#### 3.3.2.2.1. Clipping

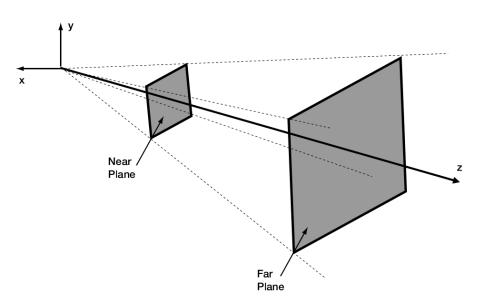

The input and output vertex coordinates in this operation remain in the same coordinate system which is clip coordinate system as shown in Figure 3.7. However, considering position of a vertex which is represented as  $p(x_c, y_c, z_c, w_c)$  in this coordinate system, each primitive, such as triangle etc., is clipped to a viewing volume as shown in Figure 3.8.

Figure 3.8) Viewing volume for clipping [28]

The viewing volume is bounded by six clipping planes which are briefly described as below:

- In the direction of line of sight (along z-axis), a near plane and a far plane as shown in Figure 3.8.

- A top and a bottom plane along y-axis.

- A left and a right plane along x-axis.

The clipping planes discussed above can be found out with the help of following equations which set bounds on clip coordinates.

| $-w_c \leq x_c \leq w_c$ | ••••  | Equation 3-1 [28] |    |

|--------------------------|-------|-------------------|----|

| $-w_c \le y_c \le w_c$   | ••••• | Equation 3-2 [28] |    |

| $-w_c \leq z_c \leq w_c$ | ••••• | Equation 3-3 [28] | 41 |

Once

the clipping

planes are known each individual primitive goes through clipping operation separately and the portion which is outside the viewing volume is clipped away. In some cases, such as for triangles or lines, clipping could result in the generation of new vertices as well. However, if a primitive is completely inside the clipping volume it passes as it is to the output. Similarly, if it is completely outside it is discarded away.

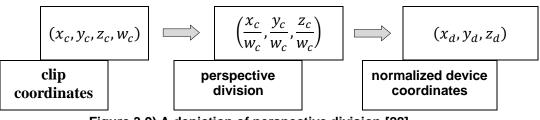

#### 3.3.2.2.2. Perspective Division

The next operation after clipping in the primitive assembly stage is the perspective division as shown in Figure 3.7. With this operation vertex coordinates from clip coordinate system are transformed to the normalized device space. The transformation through perspective division for the position coordinates  $(x_c, y_c, z_c, w_c)$  is depicted in Figure 3.9.

Figure 3.9) A depiction of perspective division [28]

The normalized device coordinate system has a range specified as from  $[-1 \dots + 1]$ .

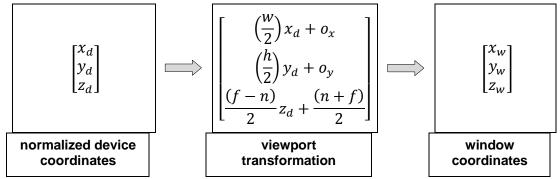

#### 3.3.2.2.3. Viewport Transformation

The viewport transformation is the last operation of the primitive assembly stage, as shown in Figure 3.7. It transforms vertex coordinates from normalized device coordinate system to the window coordinate system of the window to which an application renders. Figure 3.10 specifies the mathematical operation on each vertex coordinate as it goes through this operation.

Figure 3.10) viewport transformation operation [28]

In the central part of the figure,

- *w* and *h* represent the width and height of a window respectively, an example is shown in Figure 3.11.

- $o_x = \frac{(x+w)}{2}, o_y = \frac{(y+h)}{2}$

- n and f represent the depth range values with a specified range of (0.0, 1.0). The values outside this range are clamped to the boundary values which are also the default value.

Figure 3.11) A depiction of a window

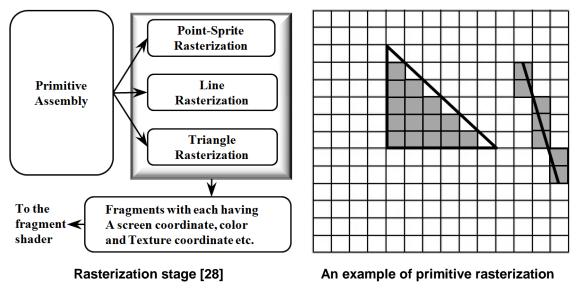

#### 3.3.3. Rasterization

This stage of the graphics pipeline, as shown in Figure 3.12 (a), transforms individual primitives, such as triangles, lines etc., to a 2D image of fragments. Each such fragment has a unique location represented in window coordinates as  $(x_w, y_w)$ . However, unlike the coordinates, represented by floating point values which come out from the primitive assembly stage, these coordinates are represented by integral values. In addition to the position coordinates, each fragment holds some other data values which is used by the fragment shader for further per-fragment procressing.

Figure 3.12) An overview of rasterization stage with an example

The process of rasterization is also illustrated with the help of an example as shown in Figure 3.12 (b). In this example, a triangle and a line primitive are rasterized which is represented by the shaded squares of the grid in each case.

In addition to fragment generation, for primitives like triangles rasterization stage also determines whether a primitive be rasterized at all or not. For this purpose each primitive goes through culling process which is discussed below.

#### 3.3.3.1.1. Culling

In order to avoid unnecessary rasterization, culling process helps determining whether a triangle primitive is front-facing or back-facing. The primitives which are visible to the viewer are called front-facing and the primitives that are hidden are known as back-facing. Once it is known, rasterization is only performed for the front-facing primitives.

For this purpose, orientation of the triangle has to be known which is determined by calculating the signed area of the primitive, under culling process, in the window coordinates. The orientation of a triangle primitive could either be clockwise or counterclockwise and which orientation represents front-facing or back-facing primitives can be specified by the application. Thus by using appropriate commands the rasterization for the specified primitives, that are to be culled, could be avoided.

Before the discussion of a fragment shader, we first discuss the operations performed by a vertex shader.

#### 3.3.4. Vertex Shader

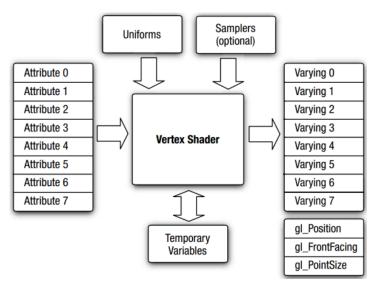

A vertex shader, as shown in Figure 3.13, is a graphics pipeline stage which implements a general programmable function. The input to this function includes parameters such as per-vertex attributes, uniforms and samplers. Typically, this function applies various mathematical operations on the input data such as position transformations, computation of lighting equation to generate per-vertex color values etc. The output of this stage is 1:1 mapped with respect to the input and the output variables are known as varyings.

Figure 3.13) OpenGL ES 2.0 vertex shader, overview [28]

```

1. // uniforms used by the vertex shader

2. uniform mat4 u_mvpMatrix; // matrix to convert P from model

3.

// space to normalized device space.

4.

5. // attributes input to the vertex shader

6. attribute vec4 a_position; // position value

7. attribute vec4 a_color; // input vertex color

8.

9.

// varying variables - input to the fragment shader

10. varying vec4 v_color; // output vertex color

11.

12. void

13. main()

14. {

v_color = a_color;

15.

16.

gl_Position = u_mvpMatrix * a_position;

17. }

```

#### Figure 3.14) OpenGL ES 2.0 vertex shader, example [28]

A simple example of a vertex shader, written in OpenGL ES SL, is shown in Figure 3.14. The input parameters, shown in Figure 3.13 and also specified from line 1 to line 7 in Figure 3.14, to a vertex shader are briefly discussed as follows:

*Attributes:* Each vertex is represented by its attributes, as discussed in the previous section and also shown in Figure 3.2 (b). The input attributes to the vertex shader shown in Figure 3.13 are represented by generic attribute indices from 0 - 7. In Figure 3.14, line 6 and 7 indicate position and color attributes of a vertex.

*Uniforms:* These are the constants that are used by the vertex shader. Typically, a vertex shader can take the vertex attribute values either from vertex arrays or from these uniforms. In Figure 3.14 line 2 indicates a uniform, which is actually a transformation matrix.

Samplers: These are special type of uniforms which represent textures.

Shader program: It is an computer program that is executed on each vertex.

The shader program applies the required operations and writes output varying variables accordingly. In Figure 3.13, output of the vertex shader is specified by varying variables denoted by indices 0 - 7. In Figure 3.14, line 10 shows a single varying variable which represents color information.

In addition to the input and output variables discussed earlier, there are also some built-in variables, such as gl\_Position shown in Figure 3.13 and also specified in line 16 of Figure 3.14, used to store some specific information. Moreover, temporary variables may also be declared and used by a vertex shader.

# **3.4. Basic Scheduling Concepts**

The idea of scheduling is not so uncommon and is being used in our daily lives. It's all about how well can we manage the time and resources we have to do our tasks. A fair schedule helps us to do more tasks and makes us more productive. If we think for a while, we see that all the tasks we have to do don't have same priorities. Some tasks are more urgent than others and have to be done in time; otherwise we could miss their deadlines which in some cases could even lead to bad consequences. Therefore, these tasks need our special attention so that we don't miss their deadlines while being busy with some unimportant task. Even though some tasks might not be that much important, if we just forget doing them makes us less productive. In order to avoid forgetting some important tasks, like an appointment for example, we insert calendar entries by mentioning its time thus making sure its execution in future. That's how we use these scheduling concepts.

The use of scheduling in the context of GPU resource management is also not so different. As we have discussed in Chapter 1, multiple concurrent applications may not leverage GPU's high computational power efficiently without having a scheduler. A GPU scheduler does that job by providing a fair share of GPU resources to applications as per specifications. The specifications of the applications, such as frame rates and priorities, influence the scheduling policy used by the scheduling algorithm. In order to address QoS (Quality of service) requirements of applications these specifications must be met. In this chapter, we discuss in detail some generic scheduling concepts and those we have devised for OpenGL ES 2.0 applications.

### 3.4.1. A Generic Scheduling Scenario

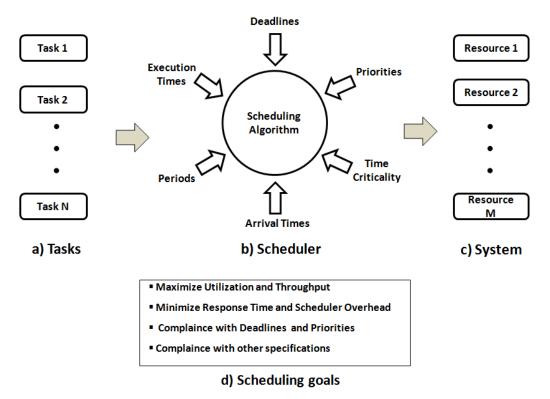

A generic scheduling scenario with some usual requirements and goals is depicted in Figure 3.15. We have N number of tasks which are to be executed on a system with Mnumber of resources, as shown in Figure 3.15 (a) and (c) respectively. M is usually less than N and also a task may use 1 to M resources at a time for its execution. It constrains the order of execution of these tasks and limits the amount of time a task can grab some resource or resources. The scheduler, shown Figure 3.15 (b), implements a scheduling algorithm which takes some scheduling parameters of these tasks such as their periods, execution times etc. as input and finds a solution that can meet some scheduling goals, as shown in Figure 3.15 (d).

Figure 3.15) Generic scheduling scenario with some requirements and goals

A general scheduling goal is to maximize the utilization of the system which means that the system must be doing some useful work most of the time. Another goal is to maximize throughput, number of tasks done per unit time, which helps a system to execute more than one task concurrently. It is also desired to minimize scheduling overhead and response time of the system, which result in greater utilization and makes the system lively respectively. Some tasks may be more important than others which is specified by giving priorities to individual tasks. For real time tasks, it is also required to meet deadlines. In hard real-time systems missing deadlines could result in system failure or even loss of life. However, in soft real-time systems it could result in some quality degradation. In general, scheduling algorithm has to find a fair tradeoff between these scheduling goals.

# 4. FINE-GRAINED SEMANTICS DRIVEN SCHEDULING

So far we have discussed the importance and the challenges of GPU multitasking. We also briefly introduced our scheduling approach. Some basic concepts regarding OpenGL ES 2.0 and scheduling are also described.

In this chapter, we discuss our Fine-Grained Semantics Driven Scheduling (FG-SDS) model in detail. The organization of this chapter is as follows. In the first subsection the core idea of our work has been presented. In the next subsection, the complete system model is described which illustrates the way in which the scheduler is integrated within the system and how the components interact with each other. Finally a sample GPU multitasking scenario has been chosen to describe the way in which our idea works.

In the discussion that follows in this section when we refer to the applications, it is implicit that these are OpenGL ES 2.0 applications.

## 4.1. Basic Idea

In order to present the basic idea of our work, we proceed as follows. Firstly, the scheduling goals of the FG-SDS model are discussed. Secondly, the challenges in achieving these goals are described briefly. Finally, we discuss how the FG-SDS model can overcome these challenges to meet the scheduling goals.

## 4.1.1. Scheduling Goals

As we discussed in section 1 that applications have some QoS requirements, considering these requirements the major scheduling goals of FG-SDS model are as follows:

*Prioritization*: The high priority applications have to be prioritized over the low priority applications.

Maintaining Average Frame Rates: Each application has to maintain a desired Average Frame Rate (AFR).

*Meeting Frame Deadlines*: Besides maintaining an average frame rate, the time critical applications also have to meet their frame deadlines.

## 4.1.2. Scheduling challenges

The key challenges to meet the scheduling goals, which are mentioned above, are as follows.

*No Preemption*: The GPU execution model is non-preemptive. Each application has to be executed with correct graphics context and during the execution it cannot be preempted. Therefore scheduling has to be performed without preemption.

*Indefinite Execution Time Cost*: To avoid the occupation of the GPU resources by an application for an indefinite time, the execution time cost for a task must be known before dispatching its commands to the GPU.

## 4.1.3. FG-SDS

As its name implies, the FG-SDS model is an approach of GPU scheduling by splitting the tasks of an application into fine grain components, also known as command blocks, using the command semantics. The core features of this model are as follows.

*Fine-Grained Scheduling Granularity* - The scheduling granularity has been reduced from a command group (coarse-grained), which is used in [12, 13, 14], to a command block (fine-grained) level in FG-SDS model. The number of commands in a command block can range from one command, which is the minimum possible scheduling granularity, at least to a few commands at most. Reducing the granularity to such a level results in the reduction of time for which an application can occupy a GPU whenever it is allowed to execute. After dispatching the commands of a command block to the GPU, an application safely returns back the control to the scheduler.

In this way the limitation of non-preemption, regarding the GPU execution model, has been addressed in an efficient manner. On one hand it creates more possibilities for the scheduler to address the requirements of high priority applications. On the other hand it allows the low priority applications to dispatch their commands without affecting the high priority applications.

Using the Predicted Execution Times of the Command Blocks - The FG-SDS model also has the knowledge of the predicted execution time for each command block. However, the prediction is not the part of FG-SDS. It has been done in an earlier work [19]. This availability of this knowledge in advance helps FG-SDS model to grant permission to low priority applications in such a way that the high priority applications do not miss their deadlines. It creates a kind of determinism in the system.

Using Command Semantics - The type of commands to be included in a command block, its size and the dispatch procedure is based on the interpretation of command semantics. The knowledge of command semantics helps in splitting the tasks and making command blocks in such a way that each application renders correctly during the interleaving.

## 4.2. System Model

A complete overview of the system model has been presented in Figure 4.1. The top most layer represent the N number of applications which need a concurrent access to the GPU for the execution of their commands. Each application may further have several rendering threads of execution.

Typically, in order to execute their commands each application's thread calls a function in the user level driver or the native implementation. The user level driver converts the function call in to the GPU commands which are dispatched to the GPU through the kernel level driver.

Figure 4.1) System Model

However, in our system model the function calls by the application threads are directed to the server process through a forwarding component. The forwarding component provides communication channels between the applications and the server process using shared memory. The server process creates a separate thread for each corresponding application's thread locally which can also be considered as a duplicate of it regarding their execution behaviour. Now each of these created threads of the server process communicate with its corresponding application's thread using its assigned communication channel. These threads are responsible for dispatching commands of their corresponding applications to the GPU. For this purpose they have to take permission from the GPU Scheduler. In this way applications communicate with the GPU Scheduler and forward their commands to it.

The GPU Scheduler provides a queue for each thread where it can temporarily place its commands. In addition to these queues, the GPU scheduler also provides appropriate functions for the application threads to arrange their commands in to the command blocks by using the forwarded command semantics. Similarly, an application thread becomes ready to dispatch its command blocks to the GPU after it forwards commands of some specific semantics such as the command which changes the contents of frame buffer (eglSwapBuffers) or a synchronous command. At this point the thread stops forwarding commands and waits for the scheduler permission to dispatch its command blocks. The GPU scheduler has a separate scheduling thread which then grants permission to an application's thread to dispatch by using a specified scheduling policy.

When an application's thread is allowed to dispatch, it calls the native implementation in the user-level drive and then it follows the typical execution behavior until the command block under consideration is executed on the GPU. However, an application cannot dispatch indefinite commands to the GPU. The number of command blocks to be dispatched at a time is decided by the scheduler and then the allowed thread can only dispatch those command blocks. The order of the commands for a single thread does not change no matter how long it waits or how often it dispatches.

## 4.3. A Sample GPU Multitasking Scenario

To understand the FG-SDS model, consider a sample application set consisting of three OpenGL ES 2.0 graphic applications with some QoS parameters as specified in Table 4-1. Each application has a priority and an average required frame rate. Moreover, each application has a frame period which is derived from its desired average frame rate. Let's also assume that these applications have soft real-time requirements of meeting their frame deadlines as well. The frame deadlines for an application can be derived as follows:

> FD: Frame Deadline, FP: Frame Period  $FD_i = FP_i * F_{ij} \dots eq. (1)$ i = Application Id,  $F_{ij} = jth$  frame of ith application

| Application | Priority | Frame Rate<br>(FPS) | Frame Period<br>[1/FPS] (ms) |

|-------------|----------|---------------------|------------------------------|

| 1           | High     | 50                  | 20                           |

| 2           | Medium   | 25                  | 40                           |

| 3           | Low      | 20                  | 50                           |

Table 4-1) sample soft real-time graphic application setwith some specified QoS parameters

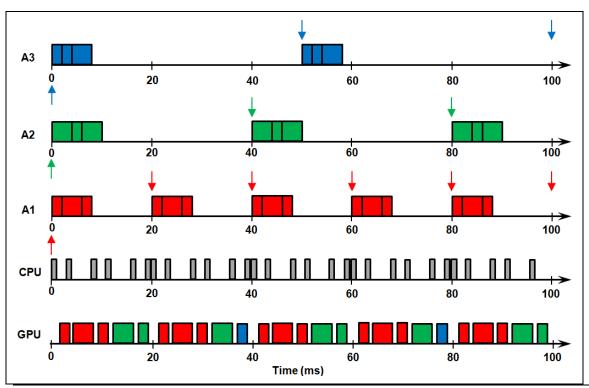

By using the above information we have to schedule these applications to execute on the GPU with our FG-SDS model. Figure 4.2 shows a scheduling approach for the multitasking of applications in the sample set based on FG-SDS model. In order to simply the scenario we assume that each frame of an application is composed of three command blocks. It is also assumed that each application has to render the same frame periodically. The required execution time for each command block of an application is also known. Moreover, we also assume that command blocks are executed on the GPU immediately after they are dispatched by an application.

| ↑                 | First Frame Arrival Time |       | ↓    | Frame deadline/Next Frame Arrival Time |                    | ame Arrival Time |      |

|-------------------|--------------------------|-------|------|----------------------------------------|--------------------|------------------|------|

| СВ                | Command Block            |       |      |                                        | Scheduler Overhead |                  |      |

|                   |                          |       |      | Require                                | d Execution        | Time             |      |

|                   |                          | Frame | CB-1 |                                        | CB-2               |                  | CB-3 |

| A1: A             | pplication-1             |       |      |                                        |                    |                  |      |

| A2: Application-2 |                          |       |      |                                        |                    |                  |      |

| A3: Application-3 |                          |       |      |                                        |                    |                  |      |

Figure 4.2) Frame rendering of a sample graphic application set using GPU

In the figure above, the command blocks of a frame along with the frame arrival times for each application, A1, A2 and A3, are shown on the timeline. The deadline for each frame is also indicated which is also the arrival time for the next frame. As we mentioned in the previous subsection that each applications has its own queue where it enqueues its command blocks, although in the above figure these queues are not shown but we assume that command blocks are inserted in to these queues before being dispatched by an application. The scheduler executing on the CPU selects one application

from the sample set and grants it the permission to dispatch its command block to the GPU.

For example in the start at time 0, all the applications of the sample set are ready to dispatch their commands. However, the scheduler selects A1, which has a High priority, and allows it to dispatch. During this scheduling decision the scheduler takes some time which is known as scheduling overhead. It is shown on the CPU time-line. The A1 after dispatching its first command block sends an acknowledgement to the scheduler that it has dispatched. The scheduler selects A1 in the next two scheduling decision as well as it is the highest priority application. After A1 finishes its first frame, the next application with medium priority is A2 which is given permission the next two times in which a scheduling decision is made.

As the time reaches 20ms, A1 gets ready again to dispatch its next frame command blocks. Again it is selected by the scheduler until its current frame ends. Then A2 is selected. At this point only A3 is ready to dispatch. Now the scheduler selects this low priority application to dispatch. In this way the applications are selected and are given the permission to dispatch.

Within 100 ms, which is the end time shown on the time-line, only A1 and A2 are able to render their frames before their deadlines. While A3 only manages to dispatch the two command blocks of its first frame.

In this way FG-SDS model allows high priority applications to meet their deadlines without allowing low priority applications to occupy the GPU.

## 5.1. Overview

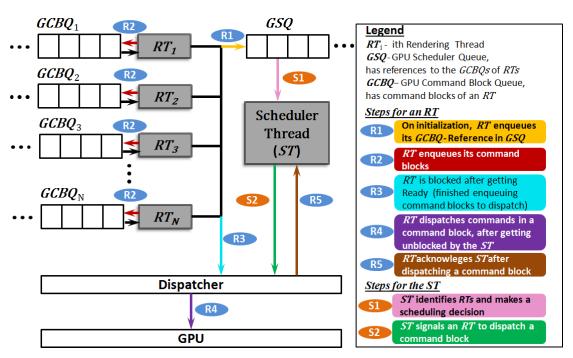

This chapter discusses the implementation details of our FG-SDS model. The implementation architecture of this model is presented in Figure 5.1. The shaded boxes (without color) represent the active components (threads) which can communicate with each other and also perform specified operations on passive components (queues). They can write to (shown with an arrow pointing to the queue to be written) or read from (shown with an arrow pointing away from the queue to be read) the respective queues. Moreover, all the threads shown in the figure belong to the same process. For the sake of clarity, the upper layers (forwarding layer and application layer) are not shown in this diagram. The major components of this architecture are described as follows.

Figure 5.1) FG-SDS implemetation architecture