Institute of Computer Engineering and Computer Architecture Prof. Dr. rer. nat. habil. Hans-Joachim Wunderlich Pfaffenwaldring 47, 70569 Stuttgart

# Master Thesis Nr. 3439 Online Self-Test Wrapper for Runtime-Reconfigurable Systems

Jiling WANG

# MSC THESIS

in partial fulfillment of the requirements for the degree of **Master of Science**

| Supervisors :         | DiplInf. Michael Коснте<br>DiplInf. Michael Імноғ  |

|-----------------------|----------------------------------------------------|

|                       | DiplInform. Claus BRAUN                            |

| Examiner :            | Prof. Dr. rer. nat. habil. Hans-Joachim WUNDERLICH |

| Start Date :          | December 03, 2012                                  |

| $Submission \ Date$ : | June 04, 2013                                      |

| CR Classification :   | B.5.2, B.6.1, B.8.1, B.8.2, C.4                    |

| Study Program :       | M.Sc. Information Technology (Embedded Systems)    |

# Abstract

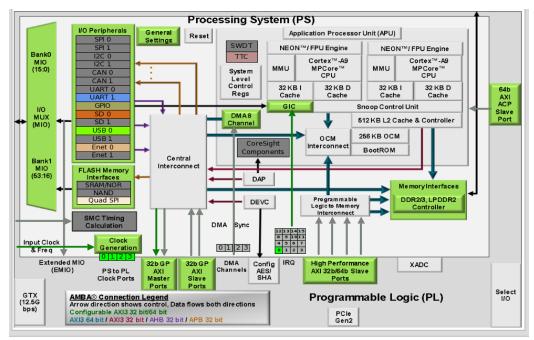

Reconfigurable Systems-on-a-Chip (SoC) architectures consist of microprocessors and Field Programmable Gate Arrays (FPGAs). In order to implement runtime reconfigurable systems, these SoC devices combine the ease of programmability and the flexibility that FPGAs provide. One representative of these is the new Xilinx Zynq-7000 Extensible Processing Platform (EPP), which integrates a dual-core ARM Cortex-A9 based Processing System (PS) and Programmable Logic (PL) in a single device. After power on, the PS is booted and the PL can subsequently be configured and reconfigured by the PS.

Recent FPGA technologies incorporate the dynamic Partial Reconfiguration (PR) feature. PR allows new functionality to be programmed online into specific regions of the FPGA while the performance and functionality of the remaining logic is preserved. This on-the-fly reconfiguration characteristic enables designers to time-multiplex portions of hardware dynamically, load functions into the FPGA on an as-needed basis. The configuration access port on the FPGA can be used to load the configuration data from memory to the reconfigurable block, which enables the user to reconfigure the FPGA online and test runtime systems.

Manufactured in the advanced 28 nm technologies, the modern generations of FPGAs are increasingly prone to latent defects and aging-related failure mechanisms. To detect faults contained in the reconfigurable gate arrays, dedicated on and off-line test methods can be employed to test the device in the field. Adaptive systems require that the fault is detected and localized, so that the faulty logic unit will not be used in future reconfiguration steps.

This thesis presents the development and evaluation of a self-test wrapper for the reconfigurable parts in such hybrid SoCs. It comprises the implementation of Test Configurations (TCs) of reconfigurable components as well as the generation and application of appropriate test stimuli and response analysis. The self-test wrapper is successfully implemented and is fully compatible with the AMBA protocols.

The TC implementation is based on an existing Java framework for Xilinx Virtex-5 FPGA, and extended to the Zynq-7000 EPP family. These TCs are successfully redesigned to have a full logic coverage of FPGA structures. Furthermore, the array-based testing method is adopted and the tests can be applied to any part of the reconfigurable fabric.

A complete software project has been developed and built to allow the reconfiguration process to be triggered by the ARM microprocessor. Functional test of the reconfigurable architecture, online self-test execution and retrieval of results are under the control of the embedded processor. Implementation results and analysis demonstrate that TCs are successfully synthesized and can be dynamically reconfigured into the area under test, and subsequent tests can be performed accordingly.

# Contents

| Al            | bstra | $\mathbf{ct}$ |                                                                    | iii      |

|---------------|-------|---------------|--------------------------------------------------------------------|----------|

| $\mathbf{Li}$ | st of | Figure        | es                                                                 | ix       |

| $\mathbf{Li}$ | st of | Tables        | 3                                                                  | xi       |

| Li            | st of | Abbre         | eviations                                                          | xiii     |

| 1             | Intr  | oducti        | on                                                                 | 1        |

|               | 1.1   | Motiva        | ation                                                              | 1        |

|               | 1.2   | Reliab        | ility Challenges                                                   | 2        |

|               | 1.3   |               | e Test Strategies                                                  | 2        |

|               | 1.4   | Thesis        | Goal and Outline                                                   | 3        |

| <b>2</b>      | FPO   | GA-bas        | sed Reconfigurable Systems                                         | <b>5</b> |

|               | 2.1   | Introd        | uction to FPGAs                                                    | 5        |

|               |       | 2.1.1         | Configurable Logic Block                                           | 6        |

|               |       | 2.1.2         | Switch Matrix and Interconnect                                     | 7        |

|               |       | 2.1.3         | IOBs, Memory and Clock Management                                  | 7        |

|               | 2.2   | Reconf        | figurable Architectures                                            | 7        |

|               |       | 2.2.1         | Coarse-grained Reconfigurable Architectures $\ldots \ldots \ldots$ | 8        |

|               |       | 2.2.2         | Fine-grained Reconfigurable Architectures                          | 8        |

|               | 2.3   | Partial       | l Reconfiguration                                                  | 9        |

|               |       | 2.3.1         | Partial Reconfiguration of a Processor Peripheral                  | 10       |

|               |       | 2.3.2         | ICAP versus PCAP                                                   | 10       |

|               | 2.4   | Target        | Hardware                                                           | 10       |

|               |       | 2.4.1         | Common Features between Virtex-5 and 7 Series CLBs $\ . \ . \ .$   | 11       |

|               |       | 2.4.2         | Virtex-5 CLB Architecture                                          | 12       |

|               |       | 2.4.3         | 7 Series CLB Architecture                                          | 13       |

| 3             | Test  | of Re         | econfigurable Hardware                                             | 17       |

|               | 3.1   | Fault 1       | Models and Principles of Test                                      | 17       |

|               |       | 3.1.1         | Fault Models                                                       | 18       |

|               |       | 3.1.2         | Principles of CLB Test                                             | 20       |

|               |       | 3.1.3         | Test Flow for FPGAs                                                | 21       |

|               | 3.2   | Design        | of Test Configurations                                             | 21       |

|               |       | 3.2.1         | CLB Subcomponent Tests                                             | 21       |

|               |       | 3.2.2         | Extension for 7 Series TCs                                         | 23       |

|               |       | 3.2.3         | Design of TPG and ORA                                              | 24       |

|               |       | 3.2.4         | Test Hardware Design                                               | 26       |

| 4 | Self                | -test V | Wrapper for Hybrid Reconfigurable SoC                 | <b>31</b>       |

|---|---------------------|---------|-------------------------------------------------------|-----------------|

|   | 4.1                 | Overv   | riew                                                  | 31              |

|   |                     | 4.1.1   | General Descriptions                                  | 31              |

|   |                     | 4.1.2   | Implementation Details                                | 32              |

|   |                     | 4.1.3   | Wrapper Design Approaches                             | 33              |

|   | 4.2                 | Self-te | est Wrapper Architecture                              | 34              |

|   | 4.3                 | Design  | n of Self-test Wrapper                                | 34              |

|   |                     | 4.3.1   | ARM                                                   | 35              |

|   |                     | 4.3.2   | AMBA AXI Interconnect                                 | 36              |

|   |                     | 4.3.3   | Xilinx AXI4-Lite Interconnect                         | 37              |

|   |                     | 4.3.4   | Definition of Registers                               | 38              |

|   |                     | 4.3.5   | Wrapper Design Process                                | 40              |

|   |                     | 4.3.6   | Wrapper Communication                                 | 44              |

|   |                     |         |                                                       |                 |

| 5 |                     | l Flow  |                                                       | 47              |

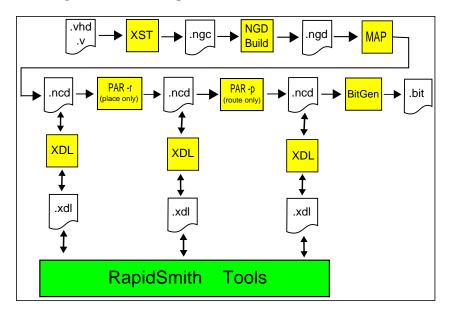

|   | 5.1                 | -       | Smith for TC Generation                               | 48              |

|   |                     | 5.1.1   | XDL Design Flow                                       | 49              |

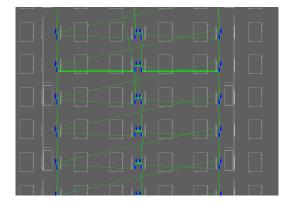

|   |                     | 5.1.2   | TC Implementation for Target Device                   | 50              |

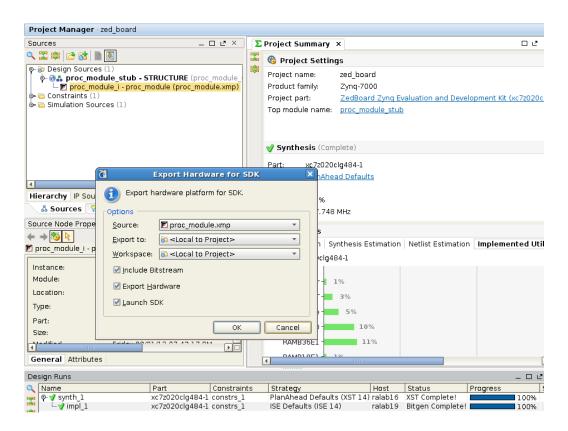

|   | 5.2                 |         | Embedded Design Flow                                  | 51              |

|   |                     | 5.2.1   | EDK tool                                              | 51              |

|   |                     | 5.2.2   | Creation of a Hardware System with Embedded Processor | 52              |

|   |                     | 5.2.3   | Software Project Creation                             | 52              |

|   | 5.3                 |         | al Reconfiguration Flow                               | 53              |

|   |                     | 5.3.1   | Creation of PlanAhead Partial Reconfiguration Project | 54              |

|   |                     | 5.3.2   | Definition of Reconfiguration Partition and Region    | 55              |

|   |                     | 5.3.3   | Creation of Configuration                             | 56              |

|   |                     | 5.3.4   | Bit Files Generation                                  | 57              |

| c | <b>C</b> - <b>C</b> |         | Development                                           | 59              |

| 6 | 6.1                 |         | Development                                           | <b>59</b><br>59 |

|   | 0.1                 | 6.1.1   | ional Test of Self-test Wrapper                       | - 59<br>- 60    |

|   |                     | 0       |                                                       | 60<br>60        |

|   | 6 9                 | 6.1.2   | Test on Board                                         |                 |

|   | 6.2                 | 6.2.1   | e Configuration                                       | 61              |

|   |                     |         | Generate Bin File                                     | 62<br>62        |

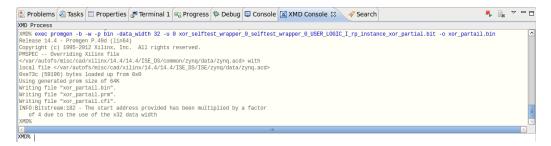

|   |                     | 6.2.2   | XMD Programming                                       | 62              |

|   | <u> </u>            | 6.2.3   | PL Reconfiguration Driver                             | 63<br>67        |

|   | 6.3                 |         | nated Tests Selection and Execution                   | 65<br>65        |

|   |                     | 6.3.1   | Standalone Boot Image Creation                        | 65              |

|   |                     | 6.3.2   | Booting From the SD Card                              | 67              |

| 7 | Eva                 | luatio  | n                                                     | 69              |

| • | 7.1                 |         | n<br>ation                                            | 69              |

|   | 1.1                 | 7.1.1   | Functional Test of Self-test Wrapper                  | 69              |

|   |                     | 7.1.2   | Configuration Time                                    | 69              |

|   |                     |         |                                                       | 00              |

|    |        | 7.1.3  | TC Tests                                | 71 |

|----|--------|--------|-----------------------------------------|----|

|    | 7.2    | Wrapp  | er synthesis Result                     | 71 |

|    |        | 7.2.1  | Resource usage and CLB count            | 71 |

|    |        | 7.2.2  | Timing Result                           | 72 |

|    | 7.3    | Evalua | tion of Standalone Software Application | 72 |

| 8  | Con    | clusio | a and Outlook                           | 75 |

|    | 8.1    | Summ   | ary                                     | 75 |

|    | 8.2    | Furthe | r Tasks and Outlook                     | 76 |

| Α  | Arti   | ix-7 X | DL Code                                 | 77 |

| в  | Dev    | ice Co | nfiguration Driver Code                 | 79 |

| Bi | bliog  | raphy  |                                         | 81 |

| De | eclara | ation  |                                         | 85 |

# List of Figures

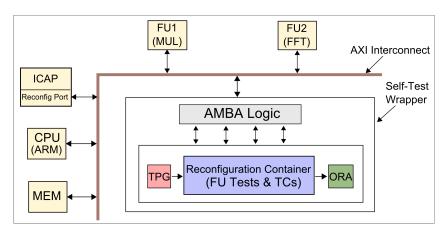

| 1.1          | Online Self-test Wrapper                                              | 3      |

|--------------|-----------------------------------------------------------------------|--------|

| $2.1 \\ 2.2$ | Partial Reconfiguration                                               | 6<br>9 |

| 2.3          | Arrangement of CLBs and Slices 1                                      | 1      |

| 2.4          | Diagram of Virtex-5 SLICEM (from [1]) 14                              | 4      |

| 2.5          | Diagram of 7 Series SLICEM (from [2]) 18                              | 5      |

| 3.1          | Complete list of CLB Fault Models (from [3])                          | 8      |

| 3.2          | Container in a C-testable array with external TPG and ORA $\ldots$ 20 | 0      |

| 3.3          | CLB in a fully interleaved array (from $[4]$ )                        | 0      |

| 3.4          | Slice arrangement of Virtex-5 CLBLM                                   | 4      |

| 3.5          | Slice arrangement of 7 Series CLBLM_L and CLBLM_R 24                  | 4      |

| 3.6          | ORA for all TCs                                                       | 5      |

| 3.7          | TPG for CarrySumFF and CarrySumMux                                    | 7      |

| 3.8          | Overview of User_logic structure                                      | 7      |

| 3.9          | Two non-overlapping Clocks based on System clock                      | 8      |

| 4.1          | Functional Test                                                       | 3      |

| 4.2          | Architecture of Self-test Wrapper                                     | 5      |

| 4.3          | AXI4-Lite Read                                                        | 7      |

| 4.4          | AXI4-Lite Write                                                       | 8      |

| 4.5          | Zynq System Assembly View 40                                          | 0      |

| 4.6          | The Self-test Wrapper Block Diagram 42                                | 2      |

| 4.7          | Bus Connections                                                       | 3      |

| 4.8          | Address Map                                                           | 4      |

| 4.9          | Ports and Clock Connection                                            | 4      |

| 4.10         | SDK Project Explorer                                                  | 5      |

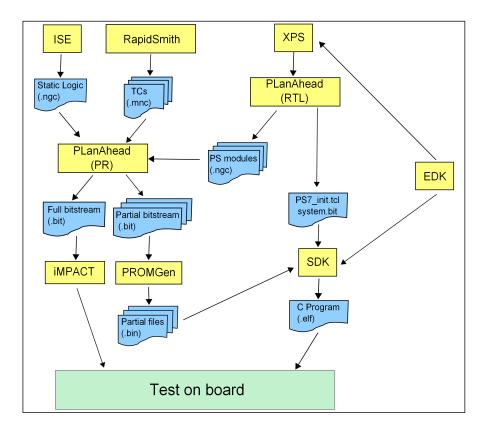

| 5.1          | Overall design Flow Chart                                             | 8      |

| 5.2          | Where XDL fits in the FPGA design flow                                | 9      |

| 5.3          | Close view of Hard Macro from FPGA editor                             | 1      |

| 5.4          | Launch SDK from PlanAhead                                             | 3      |

| 5.5          | Create a new Project in SDK                                           |        |

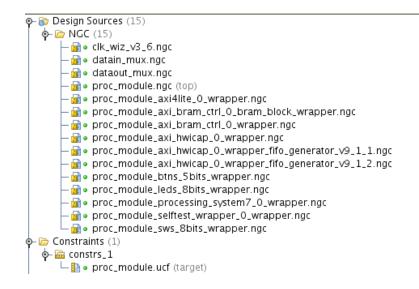

| 5.6          | All NGC files for new PR Project                                      |        |

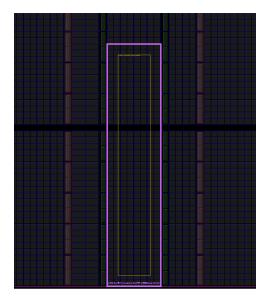

| 5.7          | Closer view of Pblock area                                            |        |

| 5.8          | Without BUFGP                                                         |        |

| 5.9          | Add -bm option for Translate (ngdbuild)                               |        |

| 5.10         | Bitstram generation successfully completed                            |        |

| 6.1          | Unexpected error while Launching program                              | 0      |

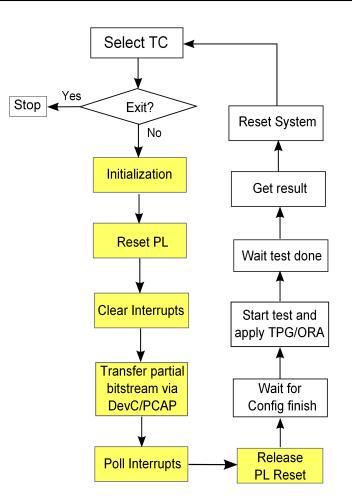

| 6.2 | Device Configuration and Partial Reconfiguration Flow | 61 |

|-----|-------------------------------------------------------|----|

| 6.3 | Convert Partial bitstreams to Binary format           | 62 |

| 6.4 | Load the Bin File into DDR Memory                     | 63 |

| 6.5 | Software Control Flow                                 | 66 |

| 7.1 | Result of the Functional test Inverter                | 70 |

| 7.2 | Result of the Functional test Adder                   | 70 |

| 7.3 | Derived Constraints Report for TS_PS7_FCLK0           | 72 |

| 7.4 | Error encountered during Software execution           | 72 |

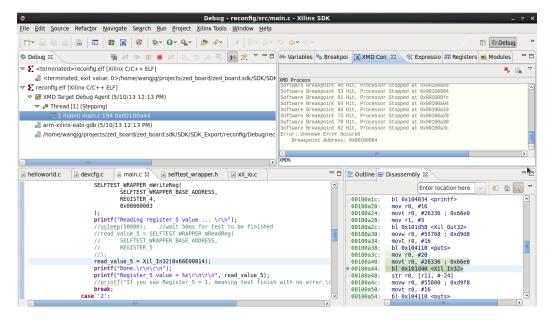

| 7.5 | Unknown error occurred during Debug                   | 73 |

| A.1 | XDL code example for HM xnor_test                     | 77 |

| A.2 | XDL code example for HM ram_test                      | 78 |

| B.1 | DevC/PCAP driver code                                 | 79 |

# List of Tables

| 2.1 | ROM and Multiplexer versus Number of LUTs          | 12 |

|-----|----------------------------------------------------|----|

| 2.2 | Logic resources in one Virtex-5 CLB                | 13 |

| 2.3 | Logic resources in one 7 Series CLB                | 13 |

| 3.1 | MATS++ Algorithm                                   | 26 |

| 3.2 | Port Map                                           | 28 |

| 4.1 | AXI4-Lite interface signals (from [5])             | 36 |

| 4.2 | Internal Registers                                 | 38 |

| 4.3 | Write Register 1 (C_BASEADDR + $0x00$ )            | 38 |

| 4.4 | Write Register 2 (C_BASEADDR + $0x04$ )            | 39 |

| 4.5 | Result_LSB Register (C_BASEADDR + $0x08$ )         | 39 |

| 4.6 | Result_MSB Register (C_BASEADDR + $0x0C$ )         | 39 |

| 4.7 | Control Register (C_BASEADDR + $0x10$ ) = slv_reg4 | 39 |

| 4.8 | Status Register (C_BASEADDR + $0x14$ ) = slv_reg5  | 39 |

| 4.9 | User_logic bus protocol ports                      | 42 |

| 7.1 | Resources utilization for all TCs                  | 71 |

# List of Abbreviations

- AMBA Advanced Microcontroller Bus Architecture

- AXI Advanced eXtensible Interface

- BIF Boot Image Format

- BIST Built-In Self Test

- BSB Base System Builder

- BSP Board Support Package

- CFM Cell Fault Model

- CIP Create or Import Custom Peripheral

- CLB Configuration Logic Block

- DevC Device Configuration

- DMA Direct Memory Access

- DRC Design Rule Check

- EDK Embedded Development Kit

- ELF Executable and Linkable Format

- EPP Extensible Processing Platform

- FF Flip-Flop

- FPGA Field Programmable Gate Array

- FSBL First Stage Bootloader

- HWICAP Hardware Internal Configuration Access Port

- ICAP Internal Configuration Access Port

- IPIC\_IF Intellectual Property Interconnect Interface

- LUT Lookup Table

- MPD Microprocessor Peripheral Definition

- NCD Netlist Circuit Description

- OCM On-Chip Memory

- ORA Output Response Analyzer

- PCAP Processor Configuration Access Port

- PIP Programmable Interconnect Point

- PL Programmable Logic

- PR Partial Reconfiguration

- PRET Pre-configuration Test

- PS Processing System

- PSM Programmable Switch Matrix

- RA Reconfigurable Architecture

- RM Reconfigurable Module

- RP Reconfigurable Partition

- RTL Register Tranfer Level

- SAF Stuck-At Fault

- SDK Software Development Kit

- SoC Systems-on-a-Chip

- SR Shift Register

- TC Test Configuration

- TF Transition Faults

- TPG Test Pattern Generator

- XDL Xilinx Design Language

- XMD Xilinx Microprocessor Debugger

- XPS Xilinx Platform Studio

# Chapter 1 Introduction

#### Contents

| 1.1 | Motivation              | 1        |

|-----|-------------------------|----------|

| 1.2 | Reliability Challenges  | <b>2</b> |

| 1.3 | Online Test Strategies  | <b>2</b> |

| 1.4 | Thesis Goal and Outline | 3        |

# 1.1 Motivation

Reconfigurable architectures are often considered to be able to offer cost saving by time-multiplexing hardware resources that are contained within them. The reconfiguration includes the alteration of the complete system or part of it. However, there is always a trade-off among performance, overhead and efficiency. The most popular reconfigurable architecture is the Field Programmable Gate Array (FPGA), with the dynamic Partial Reconfiguration (PR) enabled in the newer series [6].

Contemporary FPGAs are more prone to aging effects, latent defects and transient effects. The runtime system has to ensure a reliable reconfiguration process, and achieve dynamic adaptability to defective parts in the fabric. To detect the defective fabric in the field, requires part of the logic area to be reprogrammed for testing, while the remaining part of the logic is kept functioning as usual. Once the faulty area is detected, the logic functions can be swapped out from the defective region to a partition where the functionality is tested and known to be good.

With the availability of PR, it is feasible to allow specific regions of the FPGA to be evaluated while the remaining function of the device is preserved. PR performs hardware reconfiguration by dynamically modifying parts of logic blocks in an FPGA, and allows unmodified logic blocks to continue to operate as before [7]. Hence, the defective area in the FPGA can be avoided, a reliable runtime reconfiguration system can be accomplished.

FPGA test includes the Pre-configuration Test (PRET) of unprogrammed logic cells and functional post reconfiguration test. The reconfiguration process can be handled by either an external controller or an embedded processor [3]. This work focuses mainly on online PRET controlled by an on-chip processor core. An embedded processor contained in a runtime system can access the FPGA reconfigurable space by downloading configuration data via the configuration access port [8], and is capable of controlling the execution of Built-In Self Test (BIST) online. This enables the user to implement the reconfigurable architecture by modifying the circuit structure and changing the functionality through software control. Test Configurations (TCs) can be scheduled on a regular basis, and loaded into partitions which are currently not in use. Tests are performed accordingly.

The Xilinx Zynq-7000 SoC leverages the strengths of an ARM processor core and a Xilinx FPGA, it combines ARM cores with 28 nm programmable logic on a single chip, and delivers a reconfigurable embedded processing platform [9]. This core-centric architecture offers processing capability, the ease of programmability and the flexibility of an FPGA [10]. Furthermore, Xilinx embedded solution offers not only a tool to synthesize, place and route the design, but also enables the management of reconfigurable modules; it provides an easy way to floor plan, and acts as the overall project manager when instantiating the embedded systems.

# 1.2 Reliability Challenges

Aggressive low cost requirements and spatial constrains continuously drive transistor scaling, which results in higher on-chip integration and faster operating frequency. Consequently, FPGAs have enhanced system performance. To stay within certain power budgets, the latest 28 nm FPGA platforms include low power process innovations and stacked silicon interconnects.

However, due to the complexity of the manufacturing process, process variations and latent defects are introduced in these high-end FPGAs. On top of that, environment variations and different life spans of the silicon change the behavior of the device as well [11]. Normal production test and burn-in test are no longer able to capture these transient and aging effects. Performance degradation and erroneous behavior lead to reliability threats, and even critical safety concerns.

To improve the reliability of FPGAs and build a fault-tolerant platform, online testing becomes necessary for these reconfigurable systems.

# **1.3** Online Test Strategies

The aforementioned reliability issues raise the test requirements for reconfigurable architectures. Prior to reconfiguring with new functions, the FPGA fabric needs first to be validated with self-test. Based on the previous work implemented for the Xilinx Virtex-5 FPGA family [3], this thesis extends the structural online test method [4] to the Xilinx 7 Series programmable logic family. The PRET process can be triggered through either a hardware state machine or software control from an embedded processor. In addition, this thesis develops a self-test wrapper in a hybrid SoC platform, the reconfiguration process as well as the self-test are triggered by the microprocessor.

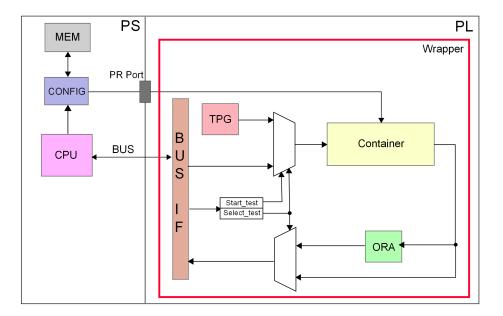

The reconfigurable partition (container) and test benches are integrated into the self-test wrapper, the wrapper is then connected to a Advanced Microcontroller

Bus Architecture (AMBA) Advanced eXtensible Interface (AXI) bus interconnect. The full implementation extends the flexibility of the PR by allowing the software running in the microprocessor to control the loading of TCs. Figure 1.1 shows the target reconfigurable SoC with the developed self-test wrapper.

Figure 1.1: Online Self-test Wrapper

Similar approaches have been adopted to develop the TCs for 7 Series FPGA, built on top of the RapidSmith java framework [12]; where code is modified and reused to certain extend, to suit the Configuration Logic Block (CLB) architecture of the 7 Series. Chapter 2 describes the detailed structural differences between Virtex-5 and 7 Series CLBs.

After the corresponding reconfiguration container is configured as a test array with a TC and is ready to be tested, the Test Pattern Generator (TPG) generates input stimuli to the container and the Output Response Analyzer (ORA) analyzes the outputs from the container. The programmable part of the device consists of a PR module and the static logic; after it is fully configured with a complete bitstream, the partial bitstreams can be downloaded to modify the reconfigurable portion, and change the TC design.

# 1.4 Thesis Goal and Outline

The main purpose of this thesis is to develop and evaluate a self-test wrapper for such a on-line reconfigurable system. The purpose of the wrapper is to encapsulate a block of reconfigurable logic and implement an interface to connect the self-test hardware via the AMBA AXI4-Lite bus interconnect to the ARM microprocessor. The generation of test stimuli and analysis of responses can be performed under the software control, as well as functional evaluation. The tool chains used are introduced and the implementation details are presented.

After a brief introduction, this thesis first introduces FPGA-based reconfigurable systems and partial reconfiguration. It goes on to compare the basic architectural differences between Virtex-5 and 7 Series CLBs. Then in Chapter 3, based on the

comparison results, it describes the test requirements and implementation of TCs for the targeted hardware. Followed by design of TPG and ORA for each TC using hardware description language. Chapter 4 gives the detailed information about designing the self-test wrapper, including an overview of the processor architecture, the AXI interface protocol and requirements.

The remainder of the report is organized as follows. Chapter 5 presents the tool chain for the TC generation, the embedded development tool suite and the steps for partial reconfiguration of a processor peripheral. Chapter 6 demonstrates the design of a software project based on the software development platform, which enables the integration of hardware and software components. Software-controlled TCs reconfiguration and tests execution are also explained. It is followed by the validation and implementation results in Chapter 7. This thesis is concluded in Chapter 8 with a summary and possible further tasks.

# Chapter 2

# FPGA-based Reconfigurable Systems

#### Contents

| 2.1        | Intro | oduction to FPGAs                                                | <b>5</b> |

|------------|-------|------------------------------------------------------------------|----------|

|            | 2.1.1 | Configurable Logic Block                                         | 6        |

|            | 2.1.2 | Switch Matrix and Interconnect                                   | 7        |

| 2          | 2.1.3 | IOBs, Memory and Clock Management                                | 7        |

| <b>2.2</b> | Reco  | onfigurable Architectures                                        | 7        |

| 2          | 2.2.1 | Coarse-grained Reconfigurable Architectures                      | 8        |

| -          | 2.2.2 | Fine-grained Reconfigurable Architectures                        | 8        |

| 2.3        | Part  | ial Reconfiguration                                              | 9        |

|            | 2.3.1 | Partial Reconfiguration of a Processor Peripheral                | 10       |

| 2          | 2.3.2 | ICAP versus PCAP                                                 | 10       |

| 2.4        | Targ  | et Hardware                                                      | 10       |

| 2          | 2.4.1 | Common Features between Virtex-5 and 7 Series CLBs $\ . \ . \ .$ | 11       |

| 2          | 2.4.2 | Virtex-5 CLB Architecture                                        | 12       |

| -          | 2.4.3 | 7 Series CLB Architecture                                        | 13       |

# 2.1 Introduction to FPGAs

Field Programmable Gate Arrays (FPGAs) are silicon devices that are based upon an array of Configurable Logic Blocks (CLBs) connected together through programmable switch interconnects. An FPGA has much more logic resources compared with Programmable Logic Device (PLD) and its programmable nature distinguishes it from Application Specific Integrated Circuit (ASIC); it outperforms an ASIC in the way of dynamical reconfiguring tasks from one to the other at runtime.

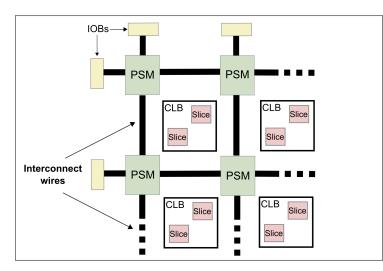

A brief overview of the FPGA architecture gives a basic understanding to the testing of reconfigurable systems. The fundamental FPGA building blocks include CLBs, block RAMs, DSP slices and IO logic resources. CLBs communicate with each other through the programmable switch matrices (PSMs) and interconnect wires. Input/Output Blocks (IOBs) are used to connect the FPGA to the outside world [3]. Figure 2.1 represents the basic FPGA block structure. Due to

reprogrammable capabilities, SRAM-based FPGAs are the dominant type. The following subsections describe the basic components in an FPGA.

Figure 2.1: FPGA basic building Blocks

# 2.1.1 Configurable Logic Block

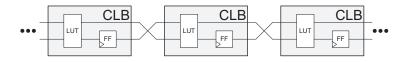

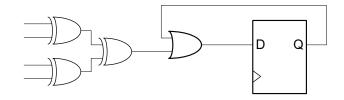

The CLB is the basic logic unit and the foundation of an FPGAs; it is essential for re-programmable digital logic design. A CLB consists of Lookup Tables (LUTs) with 4 to 6 inputs, selection circuitry (Multiplexers, XOR) and sequential elements such as Flip-Flops (FFs). The LUTs act as function generators, and can be flexibly configured as combinatorial logic, shift registers or RAM. Multiplexers are used to specify the signal connections inside the CLB; signals from the logic input portion of a slice are routed through to the sequential elements. The sequential elements can be configured as either a FF or a latch to implement edge or level sensitive designs.

A LUT realizes combinatorial logic functions through SRAM configuration, the SRAM cells store the truth table values based on the logic operation specified. A multiplexer inside the LUT selects the appropriate truth table value for the LUT output depending on the number and combination of LUT inputs. For example, a multiplexer of a 6-input LUT can select from 32 configurable SRAM cells, the SRAM cells are connected to the data inputs of the multiplexer while the 6 inputs act as the functional selection inputs. In this way, the logic function is implemented. The configuration remains stable when a circuit is online and no reconfiguration is performed [3].

The above three subcomponents are combined to form an entire CLB, providing the logic capability of FPGA.

### 2.1.2 Switch Matrix and Interconnect

Interconnect routing is another essential factor for FPGAs. CLBs interconnect to each other and to IOBs using programmable switch boxes. The flexibility of switch matrices allows any point in the circuitry to be able to be connected to another point. Interconnect wires route the signals between CLBs by horizontal and vertical lines crossing over the device, while clock and global signals are routed by global routing. The design tool takes care of the interconnect routing tasks, user interaction is not required.

Routing is determined by configuration, and carried out by interconnect wires and programmable switches, which route the signals into their correct path. The interconnects between the CLB pins are programmable switches, they are grouped together to form the PSM. The PSM makes connections between the various pins attached to it, as such it connects CLB pins to interconnects. The connections that exist within the same CLB (intra-tile connections) are programmable, they are called Programmable Interconnect Points (PIPs). PIPs establish the possible connection between two local wires by using programmable switches [3].

The programmable switches and interconnect wires are organized in a way to realize unique functions specified.

## 2.1.3 IOBs, Memory and Clock Management

Contemporary FPGAs support many different Input/Output standards, they provide compatible interface for the system. IO Blocks are grouped into banks, each bank is able to support different I/O standards independently.

Most FPGAs contain embedded blocks of RAM memory, which are connected to form a large on-chip memory. For instance, the processing system contained in the Xilinx Zynq family provides instruction and data L1 cache, shared L2 cache and on-chip RAM memory, which can be included in the design to support low-latency memory access.

The advanced FPGAs also offer digital clock management, this feature provides precise clocks with less deviation from a reference clock and filtering, allows complete clock management.

# 2.2 Reconfigurable Architectures

Reconfigurable Architectures (RAs) are the devices with programmable logic blocks and programmable interconnects between them. RAs perform computational tasks with logic blocks instead of instruction sets, which avoids the overhead for loading/decoding of instructions and dependence on the sequential execution nature of the application. The programmability and efficiency make RAs a promising solution to bridge the gap between application specific and general purpose architectures for reconfigurable computing [13].

Fine-grained and coarse-grained architectures are the two basic categories of

RAs. RAs can be implemented using FPGAs; the logic elements and interconnects of FPGA are operating at bit-level, they are able to realize applications with arbitrary word-lengths. Therefore, FPGAs are considered as fine-grained reconfigurable architectures. In contrast, coarse grained reconfigurable architectures provide wide-width configurability; increase the granularity (the size of elements can be explicitly reconfigured) of functional blocks and interconnect structures, create less overhead [14].

This section discusses the differences between these two RAs and their major advantages and disadvantages, then comes to the conclusion that tightly coupled hardware architecture with processor and reconfigurable hardware integrated into the same chip gives the most advantage in particular applications.

## 2.2.1 Coarse-grained Reconfigurable Architectures

When implementing word level operations, coarse-grained RAs use multiple-bit wide datapaths instead of bit-level operations. The wide datapath allows efficient implementation of complex operators; avoids the large routing overhead introduced by bit-level processing units, which need to compose complex operators. Coarse-grained RAs consist of higher granularity of computational elements, typically, the volume of configuration data needed is several orders of magnitude lower than that in an fine-grained FPGA. Therefore, the reconfiguration time is reduced. In addition, the interconnects between processing elements have a wider bit-width, which implies a higher area usage for a single line. Hence, fewer number of lines are required, this results in less area usage for global routing. These devices provide efficient performance, high area utilization and reduced power consumption [15].

## 2.2.2 Fine-grained Reconfigurable Architectures

There are several disadvantages for fine granularity to perform computational tasks. Due to bit-level operations, operators for wide data sources have to be processed by several processing units, leading to large routing overhead and low silicon area efficiency. Also, the switched routing wires generate high power dissipation. In addition, the high volume of configuration data needed for the large number of processing units and interconnects requires a long configuration time. On top of this, FPGAs are programmed using a high-level language, the operation at bit-level does not match the functions specified in the high level language, therefore the synthesis process takes a long time [15].

These fine-grained reconfigurable hardware architectures consist of processing elements, which communicate with each other via the programmable interconnects. Theoretically, any computation can be implemented on these fine-grained devices, since they are operating at a bit-level. However, they require more reconfiguration data and longer reconfiguration time compared to coarse-grained RAs, which leads to inefficient usage of the reconfigurable hardware. Furthermore, using pure reconfigurable hardware architectures, the reconfigurable hardware usually is not large enough to load the entire program, reconfiguration may be needed for runtime execution of the application. In this case, the code that is rarely used will also be mapped onto the reconfigurable hardware, which leads to inefficient usage of the reconfigurable hardware and slowdown the program execution [13].

Coupling a general-purpose processor with reconfigurable hardware on the same chip, can result in optimal flexibility and efficiency. Code regions that are frequently used to be mapped onto the reconfigurable hardware, can have faster program execution. Some reconfigurable architectures like RISPP (Rotating Instruction Set Processing Platform) [13], introduces the concept of special instructions (SI) and instruction rotation. A single SI can have multiple implementation instances and the runtime system decides which instance should be loaded onto reconfigurable hardware. At design time, multiple implementations are composed, and at runtime, the RISPP system controls the infrastructure of the reconfigurable fabric and realizes runtime adaptive execution [13].

It concludes that integrating a fine-grained reconfigurable fabric with a processor on the same chip, and utilizing reconfigurable hardware for mapping special instructions, can achieve runtime adaptability, better performance and speed up.

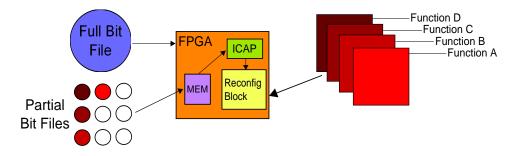

# 2.3 Partial Reconfiguration

An FPGA has the flexibility of being configured and reconfigured after manufacturing, which allows the user to change the functions of the device without refabricating it. The Partial Reconfiguration (PR) feature goes one step further, it allows us to modify a subset of the resources on an operating FPGA by loading the reconfiguration bit file. After downloading the full bit file to configure the FPGA, the design of an operating FPGA can be dynamically modified by loading the partial bitstream in the reconfigurable logic blocks, while the application running on the remaining logic is not interrupted [8]. The overall concept of PR action is depicted in Figure 2.2.

Figure 2.2: Partial Reconfiguration

To date, devices with hardware support for PR have existed for quite a long time. Now with the software and tool support, PR is widely adopted for reconfigurable systems. PR enables specific regions of the FPGA to be tested without compromising the device operation, it brings flexibility, cost and power reduction to the overall system.

## 2.3.1 Partial Reconfiguration of a Processor Peripheral

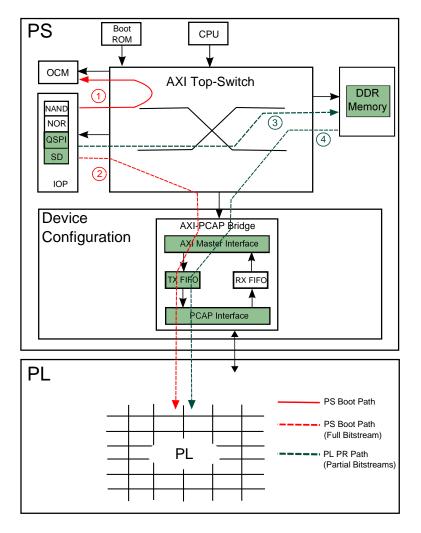

In this thesis, the reconfiguration process as well as the self-test are supposed to be triggered by the embedded processor. In order to perform partial reconfiguration in a system with a microprocessor during runtime, each partial configuration file is first converted into a partial bitstream, and then stored in the memory. The runtime reconfigurable system fetches the partial bitstream out of the memory and sends it through the Internal Configuration Access Port (ICAP) or Processor Configuration Access Port (PCAP) interface into the reconfigurable partitions. After the PR flow loads the partial bits to the reconfigurable region, the content of that region in the FPGA is modified. The AXI Hardware Internal Configuration Access Port (HWICAP) core for the AXI Interface enables an embedded processor to read and write the FPGA configuration space via the ICAP, it supports data reading and partial bitstream loading through AXI4-Lite Interface [16]. This enables the user to write software programs to modify the circuit structure and functionality during runtime, so PR can be conducted for the reconfigurable system under software control.

# 2.3.2 ICAP versus PCAP

This thesis is based on an evaluation board of the Zynq-7000 device. PCAP is the recommended reconfiguration mechanism for Zynq-7000 designs [7]. At power on, the processor selects PCAP as the configuration interface to the Programmable Logic (PL) and configuration is performed by the processor through PCAP to the PL. After configuration, the processor may switch the configuration interface to ICAP (internal to PL) by writing the control bit through an instruction executed on the processor, the control is then passed over to ICAP. PCAP configuration belongs to the processor, while ICAP belongs to the PL [7]. The processor may take over the control of PCAP back at any time. ICAP does not have security management. PCAP and ICAP are mutually exclusive, and cannot be used concurrently.

# 2.4 Target Hardware

The targeted hardware platform of this work is the Xilinx Zynq-7000 SoC. The Zynq family consists of a dual-core ARM Cortex-A9 processor based processing system and PL built on 28 nm process technology. The PL of Zynq device on ZedBoard is an Artix-7 based FPGA, which belongs to 7 Series FPGA. To test the programmable part of this SoC device, we need to know the structure of 7 Series FPGA. DSP blocks, block RAM and IOB are not taken into consideration, they are out of the scope of this thesis. The main logic components in the FPGA are the CLBs, this work will focus only on CLB tests.

In the previous work for Virtex-5 (refer to [3]), the test configurations were

developed based on the RapidSmith Java framework. For porting the existing CLB test designs from Virtex-5 to the programmable resources on the Zynq-7000 device, first let us take a close look at both CLBs.

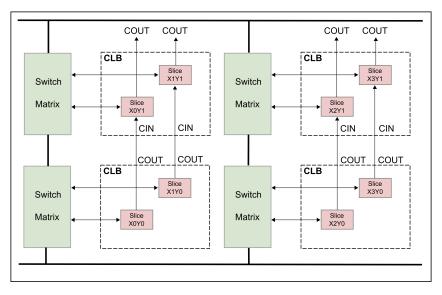

### 2.4.1 Common Features between Virtex-5 and 7 Series CLBs

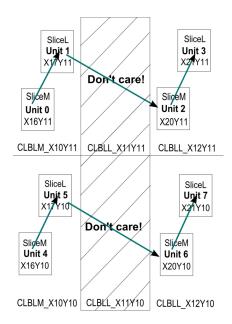

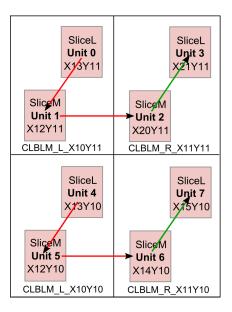

There are many similar aspects between Virtex-5 and 7 Series CLBs. Each CLB contains a pair of logic slices, the two slices in the same CLB have no direct connections to each other. Slices are organized as columns and form independent carry chains [1] [2]. See figure 2.3 below for the arrangement of CLBs and slices for both Virtex-5 and 7 Series.

Figure 2.3: Arrangement of CLBs and Slices

Slices have unique names in the form of XnYn: the X number denotes the column position of the slice, whereas the Y number denotes the row position, the Y number remains the same within a CLB. Starting from the bottom left of the die, the number counts up in sequence from X0Y0. Thus, the position of the slice is identified. Figure 2.3 illustrates how the slices are defined for four CLBs with start point in the bottom-left corner of the die.

A CLB can have two types of logic slices: SLICEL and SLICEM. Each CLB contains either two SLICELs or one SLICEL and one SLICEM. Every slice contains LUTs, multiplexers, carry chain logic and storage elements. These elements provide logic, arithmetic, and memory functions. In addition to LUT functionality, SLICEM LUTs can also be configured as storage elements using distributed RAM and shift registers. SLICEL does not support these additional functions. Therefore, SLICEM represents a superset among all slices [1] [2].

Each slice has 4 basic LUTs, each of which can implement an arbitrarily defined 6-input or 5-input Boolean function. When implemented as a 6-input function, the LUT has only one output. When implemented as dual 5-input LUTs, these two functions share common inputs, and both outputs can be used. In this case, the most significant input bit is driven high by the software. There is no difference in propagation delay through a LUT for a 6-input or 5-input LUT. Refer to figure 2.4 and figure 2.5. Signals that exit from the outputs of a LUT, feed into a multiplexer and finally reach a storage element, which can be configured as either edge-triggered D-type FFs or level-sensitive latches. When configured as a latch, the latch is transparent when the clock signal is low [1]. The carry chain runs upward and has a height of four bits per slice. For each bit, there is a carry multiplexer and a dedicated XOR gate which runs through the middle of the slice to perform fast carry computations. The carry path and multiplexers can also be used with LUTs to implement more logic functions [1] [2].

There are several configuration options for the four sequential storage elements, they can be configured as either FFs or or latches, initialized to "0" or "1", and the reset (SR) can be set as either active-high or active-low. The set and reset function for the slice has several options, such as no set/reset, synchronous set/reset or asynchronous set/reset, the work in this thesis always selects asynchronous reset.

In addition to the LUTs, slices contain three additional multiplexers to combine with the four LUTS to provide seven- or eight-input functions in a slice. These multiplexers will not be tested in the scope of this work, this can be considered for future work. Functions with more than eight-input can also be implemented using multiple slices, in this case, there are no direct fixed connections between slices.

A LUT in both SLICEM and SLICEL can implement a 64 x 1-bit Read Only Memory (ROM), three configuration options are available which depend upon the number of LUTs used. ROM contents are loaded during device configuration. Refer to table 2.1 for details. The number of LUTs needed and associated multiplexers for the implementation are also shown. A LUT in SLICEMs can also be configured as distributed RAM elements and shift registers.

| ROM     | Multiplexer | Number of LUTs |

|---------|-------------|----------------|

| 64 x 1  | 4:1         | 1              |

| 128 x1  | 8:1         | 2              |

| 256 x 1 | 16:1        | 4              |

Table 2.1: ROM and Multiplexer versus Number of LUTs

## 2.4.2 Virtex-5 CLB Architecture

In Virtex-5 CLB, each slice consists of 4 LUTs and 4 FFs. Table 2.2 shows the logic resources within one Virtex-5 CLB.

| Slices | LUTs | Flip-Flops | Arithmetic and<br>Carry Chains | Distributed RAM<br>(SLICEM only) | Shift Registers<br>(SLICEM only) |

|--------|------|------------|--------------------------------|----------------------------------|----------------------------------|

| 2      | 8    | 8          | 2                              | 256 bits                         | 128 bits                         |

Table 2.2: Logic resources in one Virtex-5 CLB

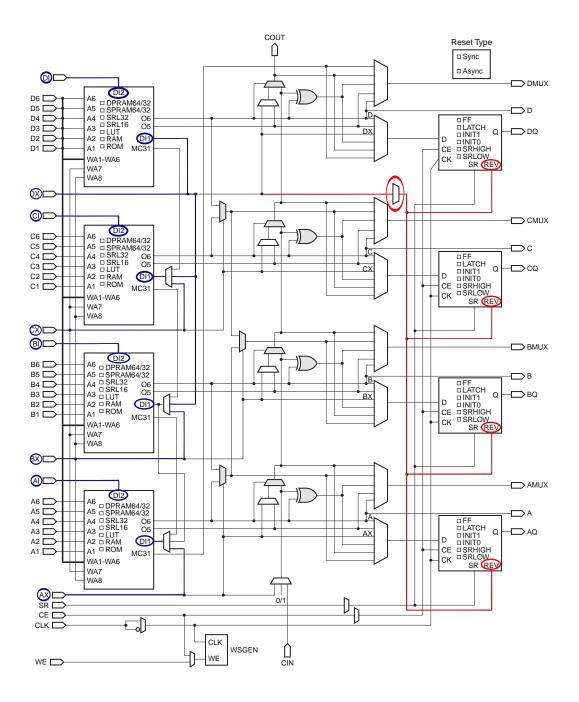

Figure 2.4 shows a SLICEM of Virtex-5. It consists of a circuit repeated four times. This circuit consists of a LUT connected to multiplexers and finally a sequential element.

Every other CLB column contains a SLICEM. In addition, the two CLB columns to the left of the DSP48E columns both contain a SLICEL and a SLICEM.

Note that the control signal reverse (REV) is not present in a 7 Series slice (function equals to REV=0 in Virtex-5).

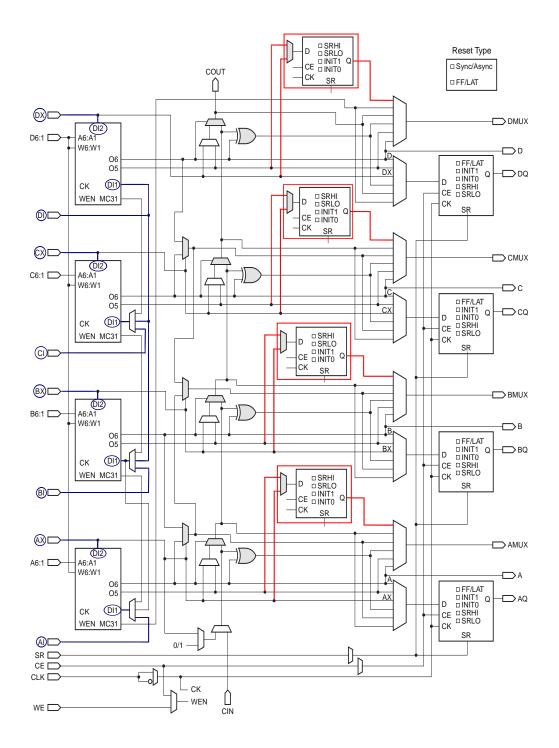

#### 2.4.3 7 Series CLB Architecture

Given the above mentioned Virtex-5 CLB architecture, the main difference in the 7 series CLB is that each slice contains 4 LUTs but 8 storage elements (one additional storage element per LUT). Figure 2.5 shows a 7 Series SLICEM and the differences to Virtex-5 SLICEM. Only four of the eight storage elements can be configured as either edge-triggered FFs or level-sensitive latches. The other four additional storage elements can only be configured as FFs, and the D input can be driven by the output of 5-input LUT (O5) or the BYPASS slice inputs via AX, BX, CX, or DX input. When the original four of the eight storage elements in a slice are configured as latches, the remaining four storage elements in that slice must remain unused.

The multiplexers and arithmetic carry logic are the same as Virtex-5 CLB. LUTs can be used for random logic implementation or distributed memory, and can be configured as either one 6-input LUT (64-bit ROMs) with one output, or as two 5-input LUTs (32-bit ROMs) with separate outputs but common addresses or logic inputs. When memory LUTs are configured as 64x1 or 32x2 bit RAM or shift register, the data inputs are 'I' in 7 Series SLICEM instead of 'X' in Virtex-5 SLICEM. Each LUT output can optionally be registered in a flip-flop. See table 2.3 below for reference.

| Slices | LUTs | Flip-Flops | Arithmetic and<br>Carry Chains | Distributed RAM<br>(SLICEM only) | Shift Registers<br>(SLICEM only) |

|--------|------|------------|--------------------------------|----------------------------------|----------------------------------|

| 2      | 8    | 16         | 2                              | 256 bits                         | 128 bits                         |

Table 2.3: Logic resources in one 7 Series CLB

Based on the above CLB structural comparison results, the test approach and methodology for testing Virtex-5 CLBs can be leveraged for configuring and testing of 7 Series CLB components.

Figure 2.4: Diagram of Virtex-5 SLICEM (from [1])

\* Red Mark: extra in 7 Series. Blue Mark: difference between Virtex-5 and 7 Series CLB.

Figure 2.5: Diagram of 7 Series SLICEM (from [2])

# Chapter 3

# Test of Reconfigurable Hardware

#### Contents

| 3.1 Fau                           | It Models and Principles of Test | 17        |

|-----------------------------------|----------------------------------|-----------|

| 3.1.1                             | Fault Models                     | 18        |

| 3.1.2                             | Principles of CLB Test           | 20        |

| 3.1.3                             | Test Flow for FPGAs              | 21        |

| 3.2 Design of Test Configurations |                                  | <b>21</b> |

| 3.2.1                             | CLB Subcomponent Tests           | 21        |

| 3.2.2                             | Extension for 7 Series TCs       | 23        |

| 3.2.3                             | Design of TPG and ORA            | 24        |

| 3.2.4                             | Test Hardware Design             | 26        |

This chapter discusses FPGA testing. After presenting fault models and FPGA test methodologies, CLB subcomponent tests are introduced. Then based on the previous work on Virtex-5 FPGA, the chapter describes the design of Test Configurations (TCs) for the target hardware of this thesis, as well as the Test Pattern Generation (TPG) and the Output Response Analysis (ORA).

# **3.1** Fault Models and Principles of Test

Modern FPGAs are more prone to latent faults and aging defects. For performing online test of FPGAs in the field, external equipment is not available. It is necessary to perform on-chip self testing, i.e., Built-In Self Test (BIST). By applying test patterns at the inputs and comparing output responses with the expected values, one can tell if the test is a pass or fail [3].

For testing FPGAs, it is required that the structural knowledge of the circuit to be tested. As mentioned in the last chapter, CLB testing is the main focus of this work. To evaluate each subcomponent of CLB, several TCs need to be established to ensure the testability of the circuit, corresponding test stimuli must be applied and outputs need to be analyzed. FPGAs are reprogrammable, so the circuit to be tested can be reconfigured by multiple TCs. Each TC targets a subset of components. It is also required to test the interconnects, however, many of the interconnects are already tested during CLB testing [17]. In addition, due to complexity, the number of TCs required for interconnect testing is much higher. The number of TCs determines the test speed, because the configuration time is several orders of magnitude higher than that of test application [4]. To minimize the test execution time, this work focuses only on CLB structural testing, interconnect testing is not described here.

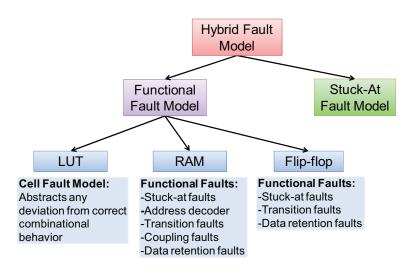

#### 3.1.1 Fault Models

To detect CLB structural defects, the Stuck-At Fault (SAF) model is the most commonly employed for fault derivation [18]. However, CLBs consist of logic gates, memory elements, multiplexers and storage elements, the implementation details of most CLB subcomponents are unknown. To derive a more accurate list of fault models, additional functional faults have to be accounted for a specific set of components. For instance, to detect defects in the RAM and combinational faults in the Lookup Table (LUT), respective fault models are used.

This subsection describes the fault models used for each CLB subcomponent. Figure 3.1 provides an overview of complete CLB fault models for easy understanding.

Figure 3.1: Complete list of CLB Fault Models (from [3])

This thesis is under the presumption of the single SAF model. In this fault model, one of the signal lines in the circuit under test is stuck at a fixed logic value, either "0" or "1", no matter what combination of inputs is applied. Therefore, a circuit with total of n signal lines, the maximum possible number of single stuck-at faults is 2n.

### 3.1.1.1 LUT in Functional Mode

Under the assumption that the internal structure of the unit under test (black box) is unknown, to test LUTs in combinational function mode, the Cell Fault Model

(CFM) [19] is applied. By thoroughly applying any of the input combinations to the black box and comparing the results received from outputs with the expected values, any mismatch is considered as a cell fault. The CFM is a more extensive functional fault model, compared to the SAF [19], for it models any fault that deviates a cell from the correct behavior. All single and multiple stuck-at faults that may occur are covered for the cell under test.

The drawback of CFM is that all of the input combinations must be exercised and the total number of cell faults can be huge for cells with a large number of input and output lines.

#### 3.1.1.2 LUT in RAM Mode

When a LUT is configured as RAM, the functional faults associated are similar to classic memory testing faults, which can be categorized as the following fault models:

1. Address decoder Faults (AFs): The faults in the address decoder cause an incorrect address access.

2. Stuck-At Faults (SAFs): A memory cell is stuck at either a "0" or "1" value.

3. Transition Faults (TFs): A cell is incapable of switching from "0" to "1" or from "1" to "0" promptly.

4. Coupling Faults (CFs): Memory cells undertake a wrong value due to the switching activity in neighbouring cells.

5. Data Retention Faults (DRFs): A memory cell is unable to retain its data value after a certain period.

In this work, to reduce the hardware overhead, only reduced fault sets are taken into consideration. These are AFs, SAFs and TFs. Besides, these three faults predominate all defects in RAM modules [3]. An existing memory test algorithm is used in this work to test RAM faults.

#### 3.1.1.3 LUT in Shift Register Mode and Sequential Elements

When a LUT is in Shift Register (SR) mode, the connection between the SRAM cells in a LUT is similar to Flip-Flops (FFs) connected in series. When testing interconnection of the LUT SRAM cells connected in series, the functional faults detected are the same as the faults occurred during testing FFs. For all sequential elements in a slice, such as the storage elements configured as FFs or latches and LUTs in SR mode, the SAFs (stuck at "0" or stuck at "1") and transition faults (slow to rise or slow to fall) are the four dominant faults [3].

#### 3.1.1.4 Structural Stuck-At Fault Model

The faults in the aforementioned three modes belong to functional faults. For the remaining subcomponents in a CLB, such as the multiplexers, XOR cells and interconnect wires in a CLB, structural faults are targeted, SAFs are used to model the structural faults [3].

# 3.1.2 Principles of CLB Test

As presented in the last chapter, CLB components can be divided into three main subsets, which can be tested separately. These are LUTs, multiplexers and the sequential elements. Different test approaches are applied for each of the CLB subcomponent. The next section explains the underlying test methodology in detail.

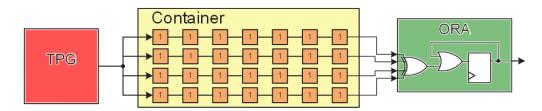

It is important to mention the term of C-testability in the context of CLB testing. An array of logic circuits that can be tested using a fixed number of TCs, irrelevant of array size [3], is called C-testable. The structure of FPGA is fairly homogeneous, CLBs are arranged in a regular array architecture, repeatedly throughout the FPGA. In order to perform an array-based CLB test, a container is set up. The logic elements are configured into an iterative C-testable array inside the container. To have a full-coverage test, the container requires an appropriate number of TCs, each of them targeting specific CLB subcomponents.

When a TC is configured into a dedicated test container, the corresponding TPG for that TC is applied, and ORA is captured at the output accordingly. Figure 3.2 shows the CLBs configured as a C-testable array in a container with external TPG and ORA, it is based on the similar picture taken from [4].

Figure 3.2: Container in a C-testable array with external TPG and ORA

A C-testable CLB array can be fully tested by applying exhaustive test patterns at the input of the first cell in an array, and obtaining the output responses at the last cell of the array, no matter how long the array is. However, to avoid long timing critical paths when the array becomes deep, the CLB subcomponents are pipelined. This is achieved by including the sequential element the sequential element of CLB into the path and connecting the CLBs in an interleaved way [4]. The structure for an interleaved CLB array is shown in figure 3.3.

Figure 3.3: CLB in a fully interleaved array (from [4])

# 3.1.3 Test Flow for FPGAs

The first step is to define the location and size of the container by the two coordinates. The CLBs to be tested are connected in a C-testable array. The appropriate number of TCs needs to be defined and implemented to have a full coverage of the CLB test. Finally the partial bitstreams containing the TCs set-up for the container are generated. For test execution, the container is subsequently configured with all TCs following the Partial Reconfiguration (PR) process, with each TC enabling test of a subset of complete logic elements.

Each TC has its own specific TPG, whereas ORA design is the same among all different TCs, it is implemented with XOR gates providing the required comparison [3]. The TPG applies the suitable test patterns to the CLB array, its responses are captured and evaluated by the ORA. The final test result is then obtained from the output of the ORA. The steps of partially reconfiguring the container followed by the test execution are repeated throughout all TCs to ensure the full coverage of CLB faults.

# **3.2** Design of Test Configurations

In previous work [3], the CLB structural self-test was evaluated on a Virtex-5 evaluation board. It includes 9 test configurations to perform a full structural test of the Virtex-5 CLB. TCs were developed on RapidSmith java framework, the techniques covered the following CLB subcomponents:

- Lookup Table Function mode

- Lookup Table Shift Register mode

- Lookup Table RAM mode

- Multiplexer

- Fast Carry Chain

- Flip-Flop or Latch

Based on Virtex-5 TCs design, this work extends the development of TCs for 7 Series CLBs. For the evaluation of the concepts in real hardware, an evaluation and development board based on the Xilinx Zynq-7000 SoC - ZedBoard is used. The Artix-7 CLBs are the main logic elements inside the programmable logic part of the Zynq device on that board. In addition, the TPGs and ORAs are taken out from java implementation, which were included in Virtex-5 TCs design [3], and are designed separately together with the static logic. This eliminates the BIST hardware overhead from the test architecture.

## 3.2.1 CLB Subcomponent Tests

In this subsection, the test for each of the subcomponents of CLB is presented.

## 3.2.1.1 LUT - Function mode

LUTs are the main functional elements in CLBs. When a LUT is configured as a combinational function mode, to cover all single or multiple internal faults, all cell faults are targeted. An exhaustive set of input patterns is applied as the test patterns. A LUT is configured with either an XOR or XNOR configuration to ensure C-testability.

### 3.2.1.2 LUT - Shift Register Mode

The FFs are configured into a long shift register, both SAFs and TFs are targeted. The scan chain test pattern "01100" is applied, because it contains the transitions from "0" to "1" and from "1" to "0".

The LUTs in SR mode are connected into multiple scan chains. For response analysis, the outputs of the scan chains are compared with each other. To reduce the number of required TCs, the FF in the CLB is included into the scan chain. By placing FFs in-between SRs, these FFs are tested simultaneously with the SR test. Hence, two CLB subcomponents are tested in a single TC.

### 3.2.1.3 LUT - RAM mode

Test patterns are generated based on the MATS++ algorithm to ensure coverage of all SAFs, AFs and TFs. The response analysis is performed by mutually comparing the outputs of these RAM blocks and aggregating the results into the global ORA.

#### 3.2.1.4 Multiplexer

The MUX is tested by applying all possible configurations to exercise all combinations of the selected inputs. SAFs are tested by applying both '0' and '1' stimuli for data inputs. Multiplexer testing is often included in other tests since they are used for internal routing of subcomponents in a slice.

### 3.2.1.5 Fast Carry Chain

The carry chain consists of multiplexers and XOR cells, for which SAFs are targeted. To test carry chain elements effectively, they must be connected in pipelined C-testable arrays. Two TCs are required for a full coverage of carry chain test. In one of the TCs, the multiplexers are transparent and the carry chains are configured into XOR arrays. In the other TC, the carry-out pin has a dedicated interconnect to the carry-in pin of the neighboring slice. The chain elements are connected in a long carry chain and "0" and "1" values are propagated through to test for SAFs. A FF at the end of each column is used to pipeline the test.

#### 3.2.1.6 Latches and Flip-Flops

As described in LUT in SR mode section, testing of the edge sensitive FFs is performed together with the test of the SRs. If sequential elements are configured as level sensitive latches, a separate test is required for the proper latch function. For testing the targeted SAFs and TFs, two non-overlapping clocks are required as input to the scan chain. The same test pattern "01100" is used for both FF and latch testing.

#### 3.2.2 Extension for 7 Series TCs

The number of required TCs can be different for different FPGA families, because the CLB architecture might differ from one to the other. However, after analyzing the architectural comparison results between Virtex-5 and 7 Series CLBs from chapter two, it turns out that CLB test for the target 7 Series hardware can be achieved with the same number of configurations. The test for the four additional FFs in a slice can be integrated into existing TCs. The following subsections explain in detail the changes made to the Virtex-5 TCs for testing 7 Series CLBs.

The additional 4 storage elements can only be configured as edge-triggered D-type FFs. The D input can be driven by the O5 output of the LUT or the BYPASS slice inputs via AX, BX, CX, or DX input. When the original four storage elements are configured as latches, they can not be used [2]. Besides the four additional storage elements, the different input ports for SR and RAM testing of SLICEM must also be considered

After carefully evaluating all the TCs for the possibility to add the tests for the additional 4 FFs, the final decision is to integrate the tests into the TCs for xor\_test and xnor\_test. There is no increase in the number of TCs, so the impact on test time is minimized.

The xor\_test and xnor\_test for the Virtex-5 are somewhat redundant. The 6-bit counters is driving the LUT, the only difference between xor\_test and xnor\_test is the inverted MSB bit of the input. In the modification for the 7 Series, xor\_test has only one output from 5-input LUT configured as an XOR function, which drives the D input of the additional 4 FFs to test the D input path. Xnor\_test tests full 6-input XNOR function as in the Virtex-5, with additional input to X input to test the BYPASS slice input to the 4 additional FFs. For xor\_test, 6-input LUT XOR function is covered by 6-input xnor\_test.

7 Series CLBs have an irregular numbering scheme compared to Virtex-5 CLBs and affect SLICEM Test. Especially for ram\_test, the code for creating the TC has to be changed substantially, to address the numbering differences between CLBLM of the Virtex-5 and CLBLM\_L/CLBLM\_R of the 7 Series. Figure 3.4 and figure 3.5 illustrate the different numbering scheme of these two CLBLMs.

The TCs are developed using java programming, generated with RapidSmith framework. Chapter 5 will give an inside view of the RapidSmith tool flow for TC generation.

Figure 3.4: Slice arrangement of Virtex-5 CLBLM

Figure 3.5: Slice arrangement of 7 Series CLBLM\_L and CLBLM\_R

#### 3.2.3 Design of TPG and ORA

The TPGs generate input stimuli to the reconfigurable modules. The ORAs are used to analyze results by mutually comparing corresponding outputs of similarly configured logic under test. In previous Virtex-5 related work, the TPG and ORA for each TC were designed using java programming, this work moves the testbench design for respective TC out of Java implementation to eliminate PRET overhead. As such, TPGs and ORAs are designed using HDL (Hardware Description Language) instead. Java codes for Virtex-5 are analyzed and interpreted to create VHDL designs for TPGs and ORAs, to realize the equivalent functions. TPGs output test done signal, ORAs give error flag if there is any fault detected.

The ORAs are carried out by mutually comparing the output responses from identically configured C-testable arrays, the result of the comparison is then captured in a storage element (flip-flop) for tracing back. Since ORA is common for all TCs, the implementation is briefly described here. As illustrated in Figure 3.6 below, the outputs are compared with each other using XOR gates, when an error is detected, the last XOR gate outputs a '1' when the test is done [3].

Figure 3.6: ORA for all TCs

The TPGs for all 9 TCs are outlined as follows.

#### 3.2.3.1 TPG for xor\_test and xnor\_test

To test all transition faults, the LUTs are configured as XOR or XNOR. An exhaustive set of test patterns is applied for this combinational logic. The TPG to 5-input or 6-input LUT is basically implemented by a 5-bit counter or 6-bit counter respectively. The counter increases from 0 to the full value to switch each bit. The BYPASS slice inputs 'X' is implemented using toggle flip-flop to provide the transitions for single bit from "0" to "1" and from "1" to "0".

#### 3.2.3.2 TPG for carry\_test\_cout\_and\_ff

The TPG input to both 'A4' and 'X' is from the same source, it is implemented by a toggle flip-flop as well to switch single bit.

#### 3.2.3.3 TPG for sr\_test

Both the clock enable input and the stimuli signal input are implemented using toggle flip-flops, with 180 degree phase difference between them.

#### 3.2.3.4 TPG for ram\_test

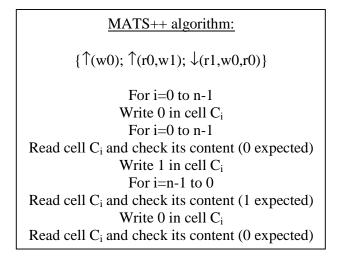

For testing memories, March tests are used [18]. Same as sr\_test, ram\_test is targeting on SLICEM. On the other hand, RAM testing is more complicated. To test the LUT as a 64-bit RAM, the MATS++ algorithm is used to ensure full test coverage. A 6-bit counter is used as an address input and a test pattern is applied to the data input. Table 3.1 describes the detail MATS++ algorithm.

Table 3.1: MATS++ Algorithm

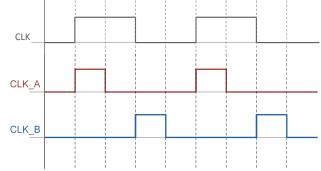

#### 3.2.3.5 TPG for latch\_test\_cy and latch\_test\_o5

Toggle flip-flop is used as stimuli for 'X' input. These two TCs require two nonoverlapping clock signals, depending on the quantity of total slices, respective clock is provided to TPG and ORA. If the total number of slices is modulo 4, then different clock sources are applied to TPG and ORA; otherwise, TPG and ORA use the same clock source.

#### 3.2.3.6 TPG for carry\_test\_sum\_ff and carry\_test\_sum\_mux

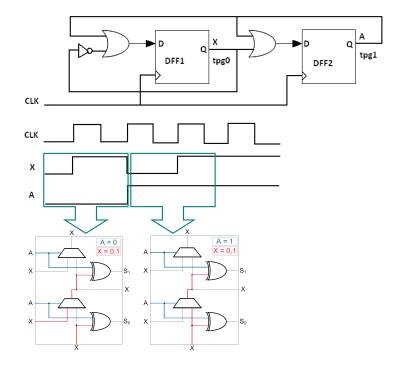

Each slice contains a four-stage fast carry chain. It consists of static multiplexers and XOR cells. For both carry\_test\_sum\_ff and carry\_test\_sum\_mux test configurations, the same input stimulus are applied. Figure 3.7 shows how test patterns connected to 'A' or 'X' are generated, with both initial value equals to "0".

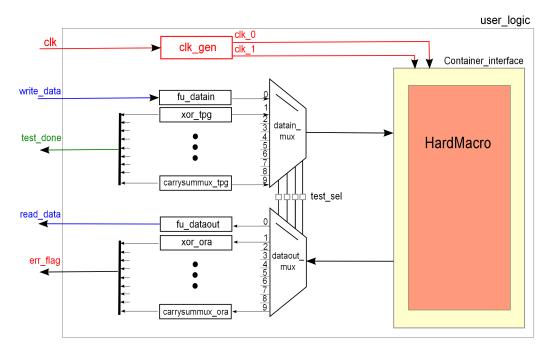

#### 3.2.4 Test Hardware Design

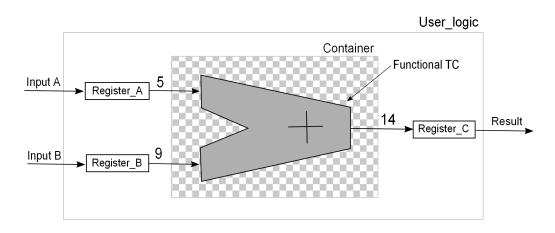

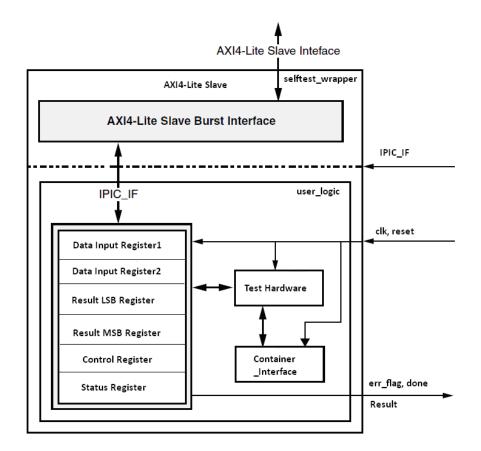

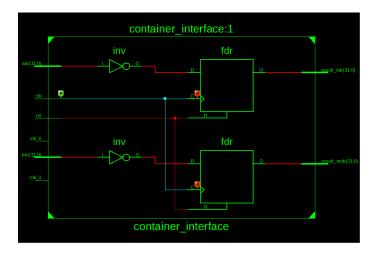

In the previous subsection we have created the TPG and ORA for each TC, here we link them up to form the test hardware to test the container. The container\_interface module is the wrapper for the partially reconfigurable module, i.e., the container. Multiplexers are used for select input stimuli and output response for respective TC, they belong to the static logic. There are variations in the number of inputs and outputs for different TCs, however the container for the TC must have a common test interface. The defined container\_interface consists of follows: one system clock input, two non-overlapping clock inputs (clk\_0 and clk\_1), one reset input, two 32-bit inputs from TPG or functional test data input, and two 32-bit outputs to the ORA or functional test result output. Refer to figure 3.8 for details.

Figure 3.7: TPG for CarrySumFF and CarrySumMux

Figure 3.8: Overview of User\_logic structure

The container communicates with TPG and ORA via this I/O interface. Each TC uses only lower 8 bits of one of the two 32-bit inputs to get input signals from

the TPG and lower 8 bits of one of the two 32-bit outputs to output to the ORA. The container interface is therefore a superset of the signals needed by the TPGs and ORAs.

The two non-overlapping clocks for the latch tests are generated from the system clock. The clock generator is used to create the two clocks with a 25% duty cycle and 180 degree phase shift, it is assigned as a sub-module under top-level user\_logic module. Figure 3.9 shows the two non-overlapping clocks generated from system input clock.

Figure 3.9: Two non-overlapping Clocks based on System clock

The port names and designators have been consolidated in Java codes to match with the port names of container\_interface module. Table 3.2 shows the one-to-one matching between the port names of the TCs and the container\_interface module.

| clk         | => clk               |

|-------------|----------------------|

| clk_0       | $=> clk_0$           |

| clk_1       | $=> clk_1$           |

| rst         | => rst               |

| en          | $\Rightarrow ain(7)$ |

| in_tpg      | => ain(6)            |

| in_tpg5     | => ain(5)            |

| in_tpg4     | => ain(4)            |

| in_tpg3     | => ain(3)            |

| in_tpg2     | => ain(2)            |

| in_tpg1     | => ain(1)            |

| in_tpg0     | => ain(0)            |

| out_ora0    | => result_lsb(0)     |

| out_ora1    | => result_lsb(1)     |

| out_ora2    | => result_lsb(2)     |

| out_ora3    | $=> result\_lsb(3)$  |

| out_oraMUX0 | $=> result_lsb(4)$   |

| out_oraMUX1 | $=> result\_lsb(5)$  |

| out_oraMUX2 | $=>$ result_lsb(6)   |

| out_oraMUX3 | $=>$ result_lsb(7)   |

Table 3.2: Port Map

Some errors encountered during implementation, such as "Clk port has illegal connections, this port is connected to an input buffer and other components", "Clock buffers are lined up in series" and "Input pad net is driving non-buffer primitives". Solutions to these kinds of problems are as follows:

1. Adding global clock buffer to the top level module, eliminate I/O buffers insertion when generating the sub-module netlist.

2. If the IBUF/OBUFs are instantiated in the sub-module, need to manually remove the input clock buffering instantiation from the sub-module and instantiate it in the top level.

The user\_logic top module contains four sub-modules: clock generator, datain\_mux, container\_interface and dataout\_mux. The datain\_mux is used to select the input stimuli to the container whereas the dataout\_mux is to choose the output analyzer module into which the output from container goes based on the test selection.

The sources for datain\_mux are the TPG for each TC described in the last subsection. The ORA are the same for all TCs, except that TCs have variable numbers of outputs, as a consequence, the dataout\_mux has to cater for the differences.

In addition to TC tests, there is an option for the functional test, which uses two 32-bit inputs and two 32-bit outputs of the container interface. The functional test tests the container when it is configured as either an inverter or an adder. The overall architecture of the user\_logic module is shown in figure 3.8.

## Chapter 4

# Self-test Wrapper for Hybrid Reconfigurable SoC

#### Contents

| 4.1 Ove  | rview                         | <b>31</b> |

|----------|-------------------------------|-----------|

| 4.1.1    | General Descriptions          | 31        |

| 4.1.2    | Implementation Details        | 32        |

| 4.1.3    | Wrapper Design Approaches     | 33        |

| 4.2 Self | -test Wrapper Architecture    | 34        |

| 4.3 Des  | ign of Self-test Wrapper      | 34        |

| 4.3.1    | ARM                           | 35        |

| 4.3.2    | AMBA AXI Interconnect         | 36        |

| 4.3.3    | Xilinx AXI4-Lite Interconnect | 37        |

| 4.3.4    | Definition of Registers       | 38        |

| 4.3.5    | Wrapper Design Process        | 40        |

| 4.3.6    | Wrapper Communication         | 44        |

|          |                               |           |

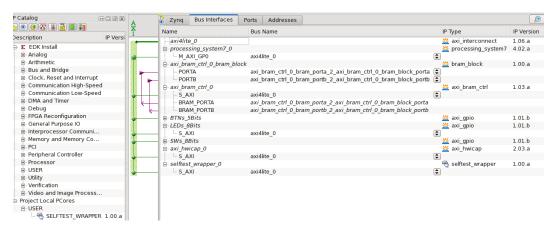

This chapter presents the design of a self-test wrapper for the reconfigurable test hardware, elaborates the wrapper design in a hybrid SoC. The wrapper is to be connected to a standard bus interconnect, so the reconfiguration process and self-test can be triggered by the microprocessor.

## 4.1 Overview

To design a self-test wrapper in a hybrid reconfigurable SoC, we need to consider the type of application processor unit, the bus system that the wrapper is connected to, and the functions for the wrapper to accomplish.

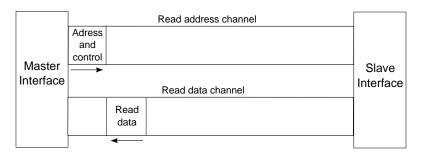

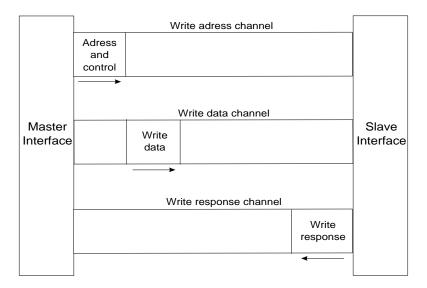

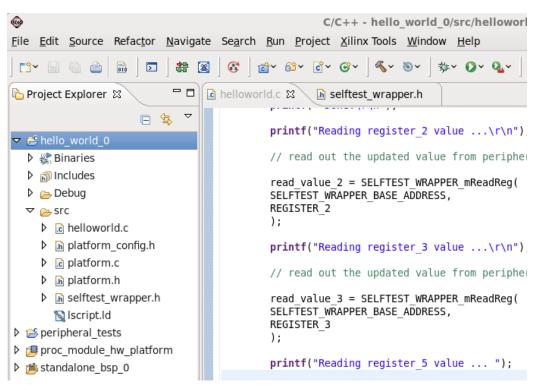

#### 4.1.1 General Descriptions