## University of Stuttgart Faculty of Computer Science

Master Thesis Nr. 3195

# Parallel architectural design space exploration for real-time image compression

Mahesh Krishnappa

**Course of Study:** Information Technology

**Examiner:** Prof. Dr. Sven Simon

**Supervisor:** Dipl. Inf. Simeon Wahl

**Commenced:** May 01, 2011

Completed: December 15, 2011

**CR-Classification:** E.4, F.1.2, I.3.1, I.4.2

Institut für Parallele und Verteilte Systeme Abteilung Parallele Systeme Universitätsstraße 38 D-70569 Stuttgart

### **Acknowlegement**

I would like to express special thanks to my supervisor, Mr. Dipl.-Inf. Simeon Wahl. His valuable inputs and support were vital for successful completion of my master thesis. I would also like to thank the members of "Institute for Parallel and Distributed Systems" for their kind co-operation and support which helped me in completion of my thesis.

I would like to express my gratitude to Prof. Dr.-Ing. Sven Simon for providing me a opportunity to work on this topic.

I would like to extend my gratitude to my parents and friends for their support and encouragement which helped me greatly in successful completion of this thesis.

Mahesh Krishnappa

#### **Abstract**

Embedded block coding with optimized truncation (EBCOT) is a coding algorithm used in JPEG2000. EBCOT operates on the wavelet transformed data to generate highly scalable compressed bit stream. Sub-band samples obtained from wavelet transform are partitioned into smaller blocks called code-blocks. EBCOT encoding is done on blocks to avoid error propagation through the bands and to increase robustness. Block wise encoding provides flexibility for parallel hardware implementation of EBCOT. The encoding process in JPEG2000 is divided into two phases: Tier 1 coding (Entropy encoding) and Tier 2 coding (Tag tree coding). This thesis deals with design space exploration and implementation of parallel hardware architecture of Tier 1 encoder used in JPEG2000. Parallel capabilities of Tier-1 encoder is the motivation for exploration of high performance real time image compression architecture in hardware. The design space covers the following investigations:

- The effect of block-size in terms of resources, speed, and compression performance,

- Computational performance.

The key computational performance parameters targeted by the architecture are

- significant speedup compared to a sequential implementation,

- minimum processing latency and,

- minimum logic resource utilization.

The proposed architecture is developed for an embedded application system, coded in VHDL and synthesized for implementation on Xilinx FPGA system.

## Contents

| Lis | t of Tables                                                                                                                                                                                               | 2                                             |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Lis | of Figures                                                                                                                                                                                                | 4                                             |

| 1.  | Introduction                                                                                                                                                                                              | 5                                             |

| 2.  |                                                                                                                                                                                                           | 7<br>10<br>12<br>15<br>20<br>21               |

| 3.  | 3.1. Architecture                                                                                                                                                                                         | 26<br>28<br>29<br>29<br>30<br>31<br>33        |

| 4.  | 4.1. Architecture 4.1.1. BPC TOP 4.1.2. Input Block 4.1.3. Control Block 4.1.4. Memory Arbiter 4.1.5. SPP, MRP and CUP 4.1.6. BAC TOP 4.2. Verification Methodology 4.3. Simulation and Synthesis Results | 34<br>34<br>37<br>37<br>37<br>41<br>43<br>44  |

| 5.  | 4.3.2. BAC                                                                                                                                                                                                | 45<br>50<br><b>54</b><br>56<br>59<br>60<br>61 |

| 6.  | Conclusion                                                                                                                                                                                                | 65                                            |

| Λn  | nev                                                                                                                                                                                                       | 66                                            |

| A. VHDL Subtype Package | 66 |

|-------------------------|----|

| B. Profiling Images     | 70 |

| C. Pseudo Code of BAC   | 75 |

| Bibliography            | 78 |

## List of Tables

| 1.  | Neighborhood for zero coding context generation                   | 12 |

|-----|-------------------------------------------------------------------|----|

| 2.  | Zero Coding Context Table for Code-Blocks from LL and LH Subbands | 12 |

| 3.  | Zero Coding Context Table for Code-Blocks from HL Subbands        | 13 |

| 4.  | Zero Coding Context Table for Code-Blocks from HH Subbands        | 13 |

| 5.  | Sign coding Context Table                                         | 14 |

| 6.  | Magnitude Refinement Coding reference table                       | 14 |

| 7.  | Coding Operations Context summary table                           | 15 |

| 8.  | BAC lookup table for Qe value and probability estimation[1]       | 22 |

| 9.  | BAC Encoder Register Structures                                   | 25 |

| 10. | Image characteristics table                                       | 28 |

| 11. | Entity of BPC top                                                 | 46 |

| 12. | BPC encoding profile                                              | 48 |

| 13. | BPC synthesis device utilization summary                          | 48 |

| 14. | BPC synthesis macro statistics                                    | 49 |

| 15. | BPC synthesis timing summary                                      | 49 |

| 16. | BPC critical path details                                         | 50 |

| 17. | Entity of BAC top                                                 | 51 |

| 18. | BAC synthesis device utilization summary                          | 51 |

| 19. | BAC synthesis macro statistics                                    | 52 |

| 20. | BAC synthesis timing summary                                      | 52 |

| 21. | BAC critical path details                                         | 52 |

| 22. | State variable access table                                       | 54 |

|     |                                                                   |    |

## List of Figures

| 1.  | JPEG2000 encoder block diagram[2]                               |

|-----|-----------------------------------------------------------------|

| 2.  | Image decompositon by DWT[2]                                    |

| 3.  | Multi level image decompositon by DWT[2]                        |

| 4.  | Sub-band decomposition into code-blocks and bit-planes          |

| 5.  | Bit-plane scan pattern                                          |

| 6.  | Significant Propagation Pass Flowchart                          |

| 7.  | Magnitude Refinement Pass Flowchart                             |

| 8.  | Cleanup Pass Flowchart                                          |

| 9.  | MQ Encoder top level block diagram[1]                           |

| 10. | MQ-Encoder flow chart[2]                                        |

| 11. | Software Architecture block diagram                             |

| 12. | Encoder block diagram                                           |

| 13. | TCD Encoder block diagram                                       |

| 14. | Compressed image Size                                           |

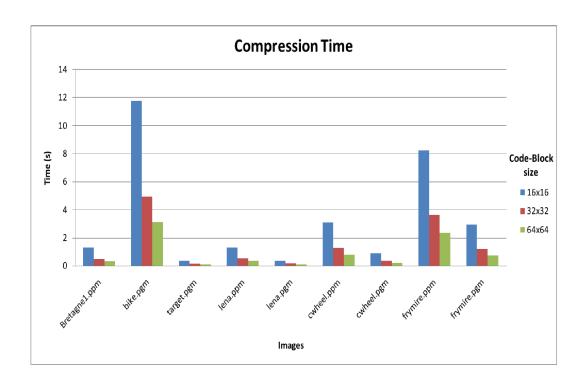

| 15. | Compression time                                                |

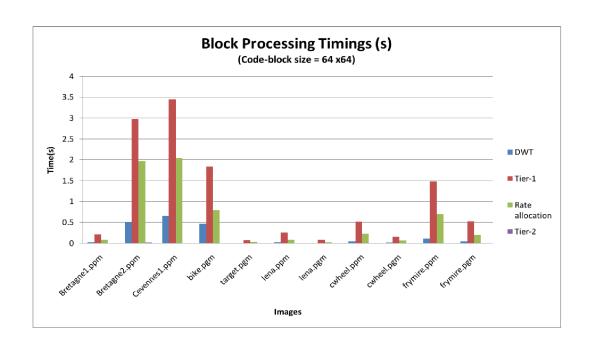

| 16. | Block processing time (code-block $64 \times 64$ )              |

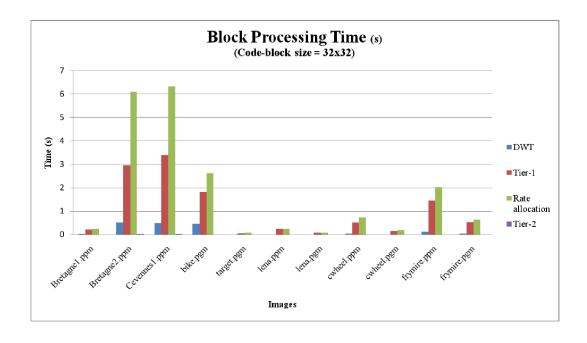

| 17. | Block processing time (code-block $32 \times 32$ )              |

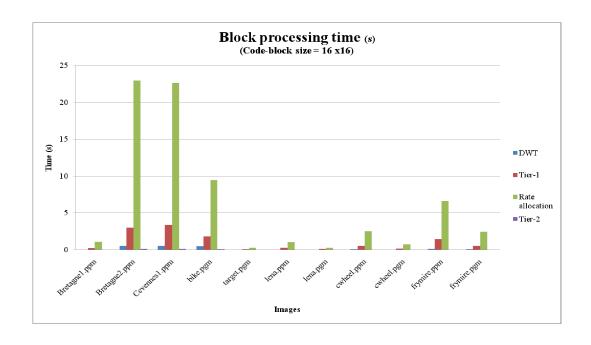

| 18. | Block processing time (code-block $16 \times 16$ )              |

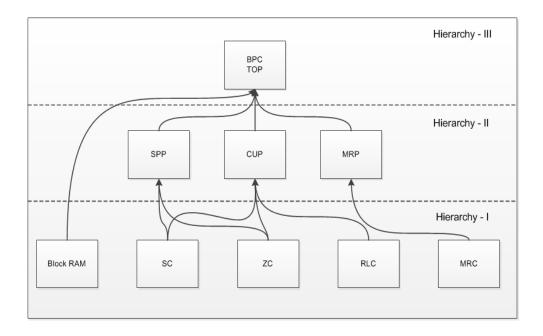

| 19. | Hierarchy of BPC design                                         |

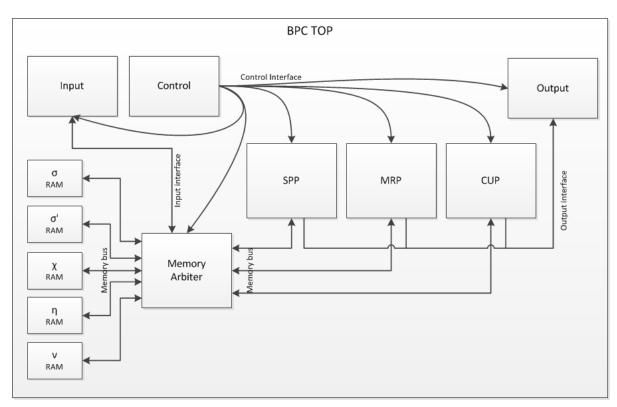

| 20. | Top Level Architecture of BPC                                   |

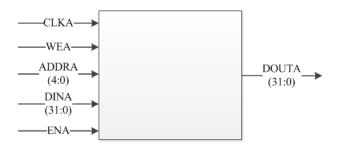

| 21. | Single-port RAM                                                 |

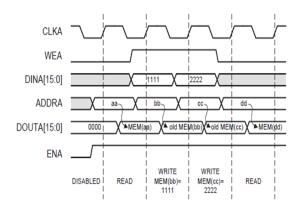

| 22. | Read first mode single-port RAM [3]                             |

| 23. | Input block of BPC                                              |

| 24. | Control block of BPC                                            |

| 25. | SPP Hardware structure                                          |

| 26. | MRP Hardware structure                                          |

| 27. | CUP Hardware structure                                          |

| 28. | Top Level Architecture of BAC                                   |

| 29. | Test bench block diagram                                        |

| 30. | BPC simulation waveform with coding pass sequence               |

| 31. | BPC SPP simulation waveform                                     |

| 32. | BPC MRP simulation waveform                                     |

| 33. | BPC CUP simulation waveform                                     |

| 34. | BAC simulation waveform                                         |

| 35. | BAC critical path                                               |

| 36. | JPEG2000 encoder compression system architecture in serial mode |

| 37. | Neighbor elements accessed in $\sigma$ array                    |

| 38. | Conceptual timing diagram of coding passes                      |

| 39. | Parallel sub-band architecture block diagram                    |

| 40. | Parallel BPC architecture block diagram                         |

| 41. | Parallel BAC architecture block diagram                         |

| 42. | Bretagne 1.ppm                                                  |

| 43. | Bretagne2.ppm                                                   |

| 44. | Cevennes1.ppm                                                   |

| 45. | bike.pgm                                                        |

| 46. | arget.pgm   | 72 |

|-----|-------------|----|

| 47. | ena.ppm     | 73 |

| 48. | ena.pgm     | 73 |

| 49. | ewheel.ppm  | 73 |

| 50. | ewheel.pgm  | 74 |

| 51. | rymire.ppm  | 74 |

| 52. | Trymire.pgm | 75 |

#### 1. Introduction

Joint Photographic Experts Group (JPEG) is a still image compression standard developed in collaboration by the International Organization for Standardization (ISO), and the International Electrotechnical Commission (IEC) and recommended by International Telecommunication Union (ITU). JPEG supports compression of still images with most image sizes in any color space. It aims at achieving compression performance with user-adjustable compression ratio, lossless compression mode and excellent reconstruction quality. Although JPEG compression standard is very successful for more than a decade, there has been significant innovation towards development of technology related to multimedia, internet and communication. JPEG in spite of its excellent performance lacks some of the desired features related to multimedia, internet and communication platforms.

JPEG2000 [1, 4] was developed to overcome the limitation of JPEG, it offers high performance in the application domain such as Internet, medical imaging, mobile multimedia communication, satellite imagery, digital photography, digital library, image archival, 3g cellular telephony, client-server networking, graphics etc. Some of the important features of JPEG2000 are:

- Lossless and lossy compression: Unified compression architecture which supports lossless or lossy modes of compression and decompression.

- Low bit rate compression performance: It can achieve better image quality for a particular compression ratio as compared to JPEG. It offers high Peak signal-to-noise ratio (PSNR) and image quality as compared to JPEG.

- Large image size and components: It can support image size up to  $(2^{32}-1) \times (2^{32}-1)$  and image components up to  $2^{14}$ . This feature supports efficient processing of satellite and astronomical images.

- Progressive transmission by resolution and image quality: It offers flexibility in organizing bit-stream in progressive mode of image quality. This feature allows efficiency and flexibility in real time browsing of images on the internet.

- Random access and compressed domain processing: It offers flexibility in compresseddomain processing such as cropping, rotation, scaling, feature extraction, etc. This can be achieved by randomly accessing and modifying code-block from the compressed bitstream.

- Region of interest (ROI) coding: It offers flexibility in selectively encoding specific region of image with higher quality as compared to rest of the image.

- Robustness to bit-errors: JPEG2000 offers error detection and correction features within the code-block. Robustness is achieved by coding independent small-size code-blocks and using markers for resynchronization in the bitstream

Some of the limitations and drawbacks of JPEG2000 are:

• JPEG2000 requires huge computational resource.

- JPEG2000 requires very high computational time.

- JPEG2000 is very complex standard, hence requires huge development time.

- JPEG2000 introduces artifacts such as blocking and blurring in the compressed images for higher compression ratio as compared to other compression standards such as H.264/ Advanced Video Coding (AVC) and Portable Network Graphics (PNG)[5, 6]

- JPEG2000 has memory bandwidth constraints[6] for high quality and high bandwidth applications, since wavelet transforms is global transform phenomenon the memory bandwidth requirement is high as compared to AVC.

- For applications with communication bandwidth constrains, JPEG2000 with lossy compression (20:1) is used, the quality of the image degrades as compared to H.264 at the same compression ratio [7].

H.264/AVC compression standard is known for excellent image quality at low bit rates. It is based on a block-based integer Discrete Cosine Transform (DCT) analogous to DWT transform used in JPEG2000. Improvement in coding performance is mainly achieved by the prediction block in the image processing chain of H.264/AVC. Inter and intra block prediction phenomena are the key for achieving high quality compressed image with low bit-rate.

JPEG-LS [8] is simple lossless compression algorithm as compared to JPEG2000. JPEG-LS offers lossless compression at less computation time as compared to JPEG2000, however JPEG-LS does not support rich set of features such as scalability, error resilience, progressiveness, etc supported by JPEG2000. The significant enhancement in compression time is achieved by low-complexity processing blocks based on adaptive prediction, context modeling and Golomb coding.

This thesis aims at optimizing the computational resource and enhancing compression time of JPEG2000 by proposing parallel hardware architecture for EBCOT encoder used in entropy encoding phase. Profiling of software implementation of JPEG2000 in subsection 3.3.3 shows that Tier-1 coding phase in JPEG2000 is responsible for considerable portion of overall compression time. Synthesis results discussed under subsection 4.3 shows that EBCOT encoder in Tier-1 coding phase is computational expensive. Section 5 discusses several parallel architectures to improve image compression performance of JPEG2000 encoder.

#### 2. EBCOT ALGORITHM

#### 2.1. Introduction

JPEG2000 aims at compression algorithm that compresses images once and offers flexibility in decompression for different application with multiple image quality and size. It also offers lossless and lossy image compression modes. However JPEG2000 is computationally exhaustive compared JPEG algorithm, this is one of the major drawback of JPEG2000.

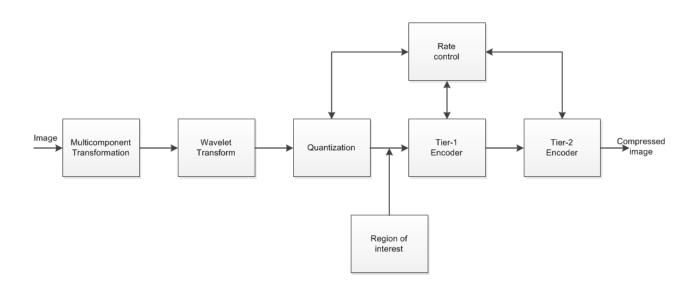

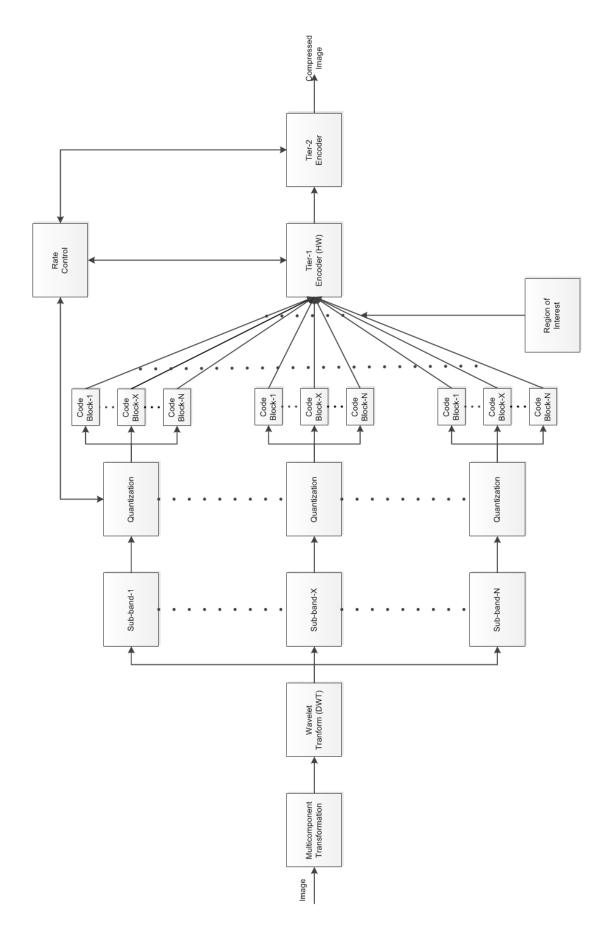

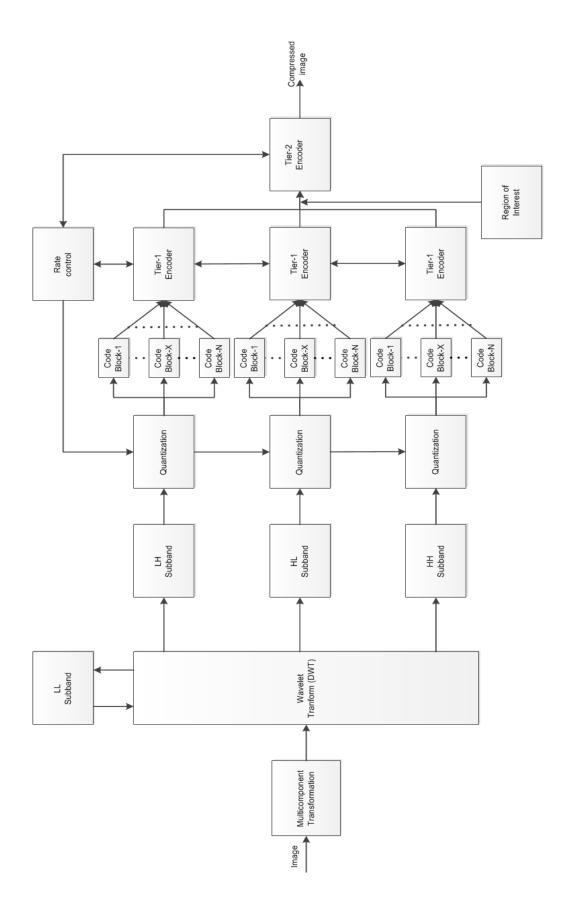

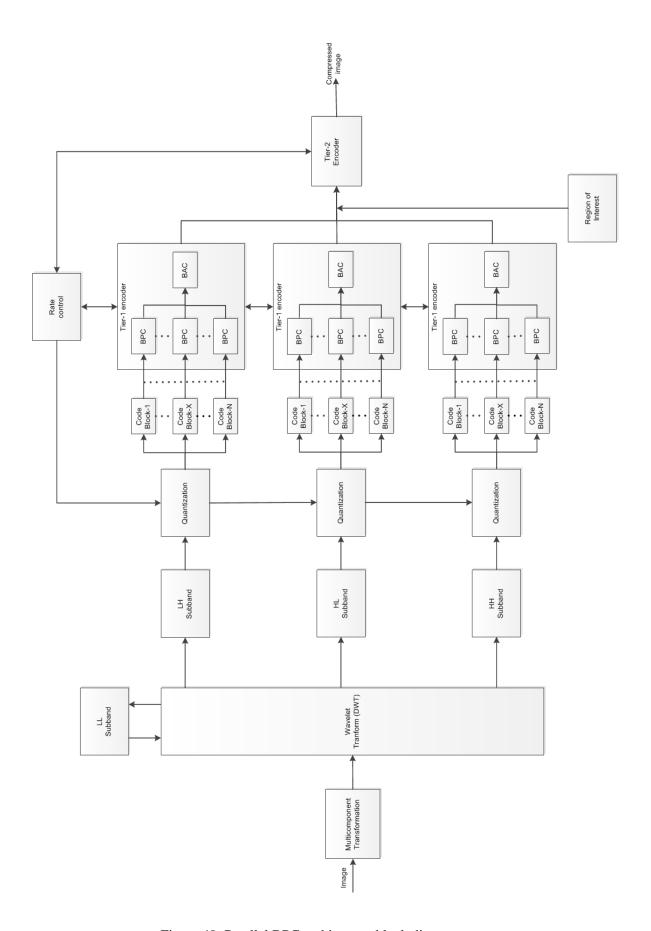

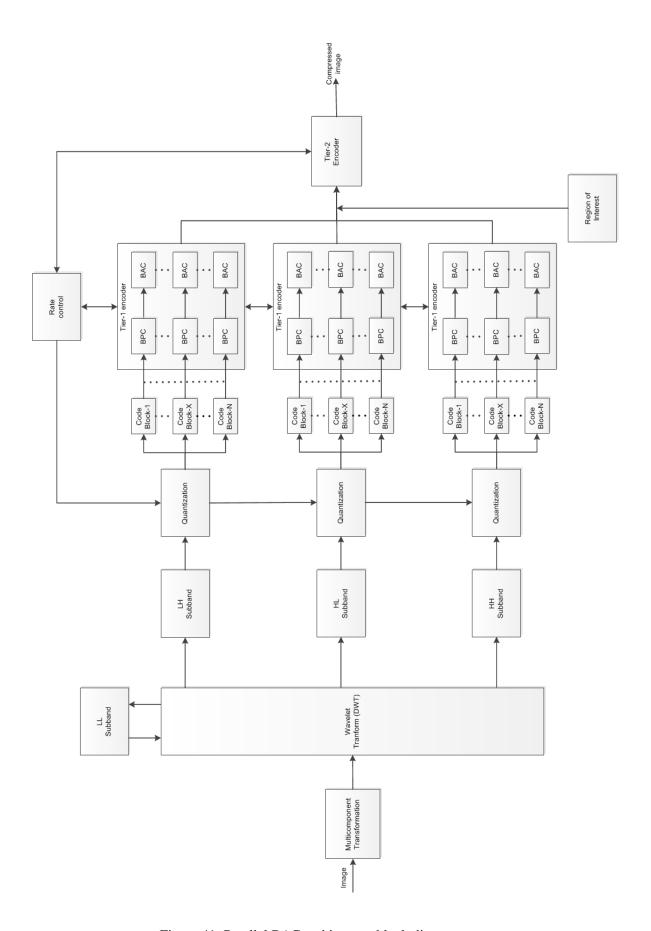

The block diagram of JPEG2000 encoder algorithm is as shown in Figure 1. It shows different phases of JPEG2000 compression algorithm, the compression phases can be mainly divided into three phases

- Discrete wavelet transform (DWT)

- · Quantization and

- Entropy encoding.

Forward multicomponent transformation is done as a preprocessing transformation before the actual compression algorithm starts, in MultiComponent transformation the correlation between multiple components of the image is reduced. This increases the compression performance by reducing the redundant components in the image.

Figure 1: JPEG2000 encoder block diagram[2]

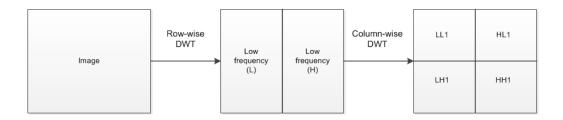

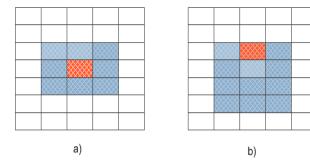

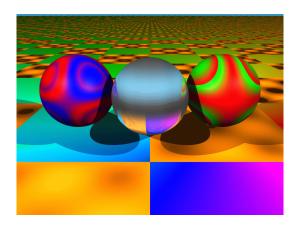

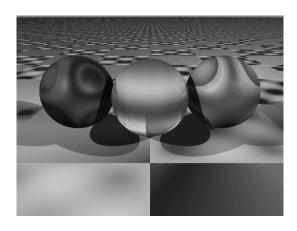

The DWT is done on the image components after preprocessing stage; DWT decomposes each component into number of sub-bands of different resolution levels. Figure 2 is an example of decomposition of image by DWT. DWT decomposes images into low frequency and high frequency sub-bands. Row-wise decomposition of the image results in low frequency (L) and high frequency (H) sub-bands as shown in the Figure 2. Further decomposition of the image

in column-wise results in 4 sub-bands LL1, LH1, HL1 and HH1. Decomposition of the image column-wise first and then row-wise results in same 4 sub-bands. LL1 sub-band represents coarser approximate of the original image and LH1, HL1, HH1 represents detailed high frequency approximate of the original image. LL1 sub-band can be further decomposed into 4 sub-bands recursively as shown in the Figure 3 a) and b).

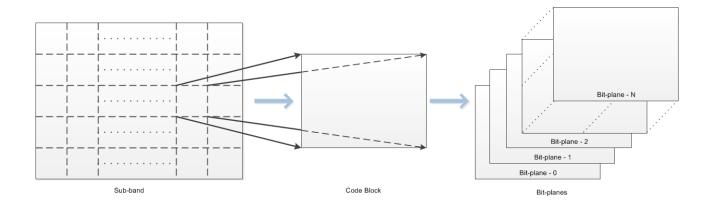

Sub-bands from DWT are quantized independently and divided into number of code-blocks of fixed size as shown in Figure 4. Entropy encoding is applied on each of these sub-bands independently to generate compressed bit stream. Entropy encoding phase consists of Tier-1 and Tier-2 coding steps. Tier-1 coding decomposes the code-block into bit-planes as shown in Figure 4 and coding is done per bit-plane starting from most significant bit-plane to least significant bit-plane. Tier-1 coding consists of two steps, Fractional Bit-Plane Coding (BPC) and Binary Arithmetic Coding (BAC).

Embedded block coding with optimized truncation (EBCOT) algorithm is used for BPC coding and MQ-coder is used for BAC coding. Tier-2 coding engine is responsible for efficient representation of encoding information associated with code-blocks such as block summary information, bitstream layers, truncation points between bitstream layers and most significant bit-plane. Tag Tree data structure is used by Tier-2 coding phase for efficient representation of information.

Figure 2: Image decomposition by DWT[2]

| LL2 | HL2 | HL1 |     | HL2 | HL1 |

|-----|-----|-----|-----|-----|-----|

| LH2 | HH2 | nE1 | LH2 | HH2 | nL1 |

| LH  | 1   | HH1 | LH  | 1   | HH1 |

| a)  |     |     |     | b   | )   |

Figure 3: Multi level image decompositon by DWT[2]

Figure 4: Sub-band decompositon into code-blocks and bit-planes

This chapter discusses EBCOT coding and MQ-coder algorithm in detail. The chapter introduces various terminologies used in the algorithm, basic encoding algorithms and coding stages. Coding stages uses these encoding algorithms to produce Context(CX) and Decision bit(D) outputs of EBCOT coding phase. CX and D bit information are encoded by MQ-coder to generate compressed bit-stream.

Entropy encoding in Tier-1 is done on wavelet sub-bands generated by DWT. The sub-bands are further divided into code-blocks of fixed size as shown in Figure 4. Pixel components of the sub-bands are represented in sign-magnitude representation of integers. Code-block dimensions are restricted by the standard, dimensions has to be power of 2 with minimum height and width being restricted to 2 and 4 and maximum height and width being restricted to 1024. Maximum elements of the code block is further restricted to 4096.  $32 \times 32$  or  $64 \times 64$  code-block size is recommended by standard for good compression performance.

Tier-1 coding in JPEG2000 consists of two processing stages, Bit Plane Coding (BPC) and Binary Arithmetic Coding (BAC). BPC coding is applied on each bit-planes of the code blocks, so the code-blocks are further decomposed into bit-planes as shown in Figure 4. If the resolution of each component is N bits then the code-blocks of each sub-bands are decomposed into N bit-planes and BPC is applied on each of these bit-planes of the code-block. BPC generates context and binary decision value as intermediate output. This intermediate data is input to BAC coding stage.

Embedded Block Coding with Optimized Truncation (EBCOT) algorithm [4] is adapted for implementation of BPC in JPEG2000. This algorithm aims at minimizing bitstream generated and minimizes the statistics to be maintained by exploiting the redundancies within and across bit planes of the code-block. EBCOT encoding is also called as fractional bit-plane coding because encoding is done in three different phases with no overlapping between the phases. Encoding phases of BPC in sequences of their processing are

- Significant Propagation Pass (SPP),

- Magnitude Refinement Pass (MRP) and

• Cleanup Pass (CUP).

These encoding phases will be discussed in detail in subsection 2.4.

#### 2.2. Terminology

This subsection introduces some of the terms used for describing the algorithm.

Code-Block(y): Code-block is a two dimensional array of predetermined dimension. The array elements are the components of the image after DWT and quantization. The samples are represented in sign-magnitude form. Every sample of the code block are associated with  $\sigma$ ,  $\sigma'$  and  $\eta$ (discussed in detail later) to indicate their status of encoding.

Sign Array ( $\chi$ ): Sign array is two dimensional array representing the signs of the sample of code-block. The dimension of sign array is same as that of code-block. Sample  $\chi[m,n]$  represents the sign information of sample y[m,n] of the code-block. Value of  $\chi[m,n]$  is given as below

$$\chi[m,n]$$

$\begin{cases} 1 & \text{if y[m, n]} < 0 \\ 0 & \text{otherwise} \end{cases}$

$\chi[m,n]$  is assigned zero for the cases for which m and n are out of range of code-block size.

Magnitude Array (v): v is a two dimensional array of unsigned integer, the dimension of v array is same as that of the code-block. The array element v[m,n] represents the magnitude of the element at [m,n] location of the code-block. The notation  $v^p[m,n]$  is used to denote the  $P^{th}$  bit of v[m,n].

Bit-Plane: The magnitude of the elements of the code-blocks are decomposed bitwise to form a plane called bit-plane. If the magnitude array  $(\upsilon)$  is represented using P bits then the elements are decomposed into P different bit-planes.

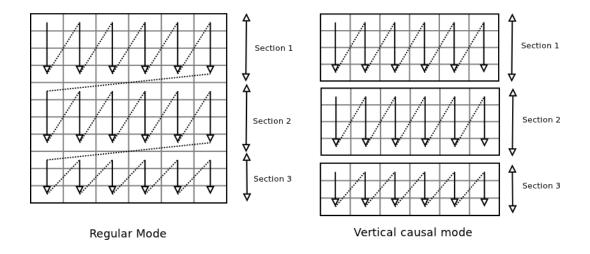

Scan Pattern: Scan pattern defines the sequence in which the elements of the bit-plane are encoded or decoded. Bit-plane of a code-block is conceptually divided into sections: Each section consists of four rows and number of column is same as that of columns of the code-block. If the row dimension of code-block is not a multiple of 4 then all sections has 4 rows except the last section.

Encoding of elements of a code-block starts from first section downto last section. Within each section scan starts from first row first column downto first column fourth row and starts again from first row second column and so on until all the columns are scanned. There are two modes of scan pattern, Regular mode and Vertical causal mode. In regular mode after scan of last element of a section, it start with the first row first column element of the next section, here it uses the information from the previous section. In vertical causal mode each section will be scanned as a independent module, the information will not be shared across sections. Figure 5 shows an example of scan pattern for a bit-plane of a code-block.

Figure 5: Bit-plane scan pattern

State Variables  $\sigma$ ,  $\sigma'$  and  $\eta$ : These state variables are two-dimensional arrays with dimension same as that of the code-block. These state variables indicate the coding status of each element in the code-block during entropy encoding. Initially the values of these elements are cleared to zero and after completion of coding each code-block these variables are cleared again. The values of  $\sigma[m,n]$  and  $\sigma'[m,n]$  are set to 1 based on certain conditions but are not cleared to zero before the completion of coding of entire code-block. The values of variables  $\eta[m,n]$  are cleared to zero after completion of coding of each bit-plane in a code-block. The interpretation of state variables  $\sigma$ ,  $\sigma'$  and  $\eta$  are as below:

$\sigma[m,n]$

- 1: Indicates that first nonzero bit of v[m,n] at row m and column n has been coded.

- **0:** It either indicates that the first nonzero bit of v[m,n] is not coded or m and n are out of range or invalid.

$\sigma'[m,n]$

- 1: Indicates that Magnitude Refinement Coding (MRC) has been applied to element v[m,n].

- **0:** Indicates that Magnitude Refinement Coding (MRC) has been not applied to element v[m,n].

$\eta[m,n]$

- 1: Indicates that zero coding operation has been applied to  $v^p[m,n]$  in Significant propagation pass.

- **0:** Indicates that zero coding operation has been not applied to  $v^p[m,n]$ .

Preferred Neighborhood: An element y[m,n] in the code-block is said to be in a preferred neighborhood if at least one of its eight adjacent neighbors has  $\sigma[m,n]$  value equal to 1.

Zero Coding Tables: Zero coding tables are used for Zero coding operation. Context information is generated from zero coding operation. There are different zero coding table for different sub-bands, and the context information is generated from the significance states  $(\sigma)$  of the eight neighbors of an element being encoded. Table 1 shows an example of eight neighbors of an element X, if for example X is an element in LL or LH sub-band, and if the two horizontal neighbors have significance state value of 1. The context value 8 will be used as shown in Table 2. Similarly Table 3 and Table 4 are used for HL and HH sub-bands respectively.

Table 1: Neighborhood for zero coding context generation

| D0 | V0 | D1 |

|----|----|----|

| Н0 | X  | H1 |

| D3 | V1 | D2 |

Table 2: Zero Coding Context Table for Code-Blocks from LL and LH Subbands

| LL aı | nd LH | Subbands | Context Label |

|-------|-------|----------|---------------|

| ΣΗ    | ΣV    | ΣD       | CX            |

| 2     | X     | X        | 8             |

| 1     | ≥1    | X        | 7             |

| 1     | 0     | ≥1       | 6             |

| 1     | 0     | 0        | 5             |

| 0     | 2     | X        | 4             |

| 0     | 1     | X        | 3             |

| 0     | 0     | ≥2       | 2             |

| 0     | 0     | 1        | 1             |

| 0     | 0     | 0        | 0             |

#### 2.3. Coding operations

This subsections gives detailed explanation about the basic coding operations used by the EBCOT algorithm. There are four basic coding operations used by EBCOT depending on the coding phases, status of the state variables and current element's location. EBCOT algorithm produces context(CX) and decision bit(D) value as output. Context(CX) can take any value among 0 to 18 and decision bit(D) takes binary value 0 or 1. The basic coding operations are as below:

Table 3: Zero Coding Context Table for Code-Blocks from HL Subbands

| HL Subbands |    |    | Context Label |

|-------------|----|----|---------------|

| ΣΗ          | ΣV | ΣD | CX            |

| X           | 2  | X  | 8             |

| ≥1          | 1  | X  | 7             |

| 0           | 1  | ≥1 | 6             |

| 0           | 1  | 0  | 5             |

| 2           | 0  | X  | 4             |

| 1           | 0  | X  | 3             |

| 0           | 0  | ≥2 | 2             |

| 0           | 0  | 1  | 1             |

| 0           | 0  | 0  | 0             |

Table 4: Zero Coding Context Table for Code-Blocks from HH Subbands

| HH Subba        | ands | Context Label |

|-----------------|------|---------------|

| $\Sigma(H + V)$ | ΣD   | CX            |

| X               | ≥3   | 8             |

| ≥1              | 2    | 7             |

| 0               | 2    | 6             |

| ≥2              | 1    | 5             |

| 1               | 1    | 4             |

| 0               | 1    | 3             |

| ≥2              | 0    | 2             |

| 1               | 0    | 1             |

| 0               | 0    | 0             |

Zero coding (ZC): In zero coding operation Decision bit is same as the  $v^p[m,n]$ . Context (CX) values is determined from one of the three Zero coding tables, depending on the type of sub-band (LL, LH, HL, HH) encoded. The context output from Zero coding can take a value from 0 to 8. The context value is decided by the significance states of eight neighbors of the current element encoded.

Sign coding (SC): SC computes CX and D value based on Horizontal reference value (H) and Vertical reference value (V). The value of H and V are calculated as shown in equation 1 and 2, with (m,n) being the current location of the element encoded.

$$H = min[1, max(-1, \sigma[m, n-1] \times (1 - 2\chi[m, n-1]) + \sigma[m, n+1] \times (1 - 2\chi[m, n+1]))] \quad (1)$$

$$V = min[1, max(-1, \sigma[m-1, n] \times (1 - 2\chi[m-1, n]) + \sigma[m+1, n] \times (1 - 2\chi[m+1, n]))]$$

(2)

The reference value calculated indicates three possible status of the neighbor elements. The neighbors for H reference calculation are horizontal adjacent elements and the neighbors for V reference calculation are vertical adjacent elements. A neighbor is said to be significant if state variable  $\sigma$  is equal to 1 and insignificant if  $\sigma$  is equal to 0. The H and V reference values are interpreter as below:

- **0:** Indicates both neighbors are insignificant, or both neighbors are significant but have opposite signs.

- 1: indicates that one or both neighbors are significant with positive sign.

- -1: indicates that's one or both neighbors are significant with negative sign.

Context (CX) and a binary value  $\hat{\chi}$  is calculated from H and V values from the sign coding reference Table 5. Decision bit (D) is calculated by equation 3.

$$D = \hat{\chi} \oplus \chi[m, n] \tag{3}$$

Table 5: Sign coding Context Table

| Н  | V  | χ̂ | CX |

|----|----|----|----|

| 1  | 1  | 0  | 13 |

| 1  | 0  | 0  | 12 |

| 1  | -1 | 0  | 11 |

| 0  | 1  | 0  | 10 |

| 0  | 0  | 0  | 9  |

| 0  | -1 | 1  | 10 |

| -1 | 1  | 1  | 11 |

| -1 | 0  | 1  | 12 |

| -1 | -1 | 1  | 13 |

Magnitude Refinement Coding (MRC): Decision bit value (D) of an element at (m,n) is equal to value of  $v^p[m,n]$ , where p is the bit plane processed by MRC. The value of CX of an element at (m,n) is determined by  $\sigma'[m,n]$  and sum of values of state variable  $\sigma$  of its eight neighbors. The value of CX is determined from  $\sigma'$  and  $\sigma$  from the Table 6

Table 6: Magnitude Refinement Coding reference table

| $\sigma'[m,n]$ | $\sigma[m-1,n] + \sigma[m+1,n] + \sigma[m-1,n-1]$ | CX |

|----------------|---------------------------------------------------|----|

|                | $[1] + \sigma[m-1,n+1] + \sigma[m+1,n-1] +$       |    |

|                | $\sigma[m+1,n+1]$                                 |    |

| 1              | X                                                 | 16 |

| 0              | ≥1                                                | 15 |

| 0              | 0                                                 | 14 |

Run Length Coding(RLC): Run length coding algorithm is capable of coding from one to four consecutive bit elements in the current scan pattern stripe. The number of bits coded depends on the position of first "1" bit in the four consecutive bits. If all the four bits are "0" then all of them are coded. If any of the bits are "1" then all preceding "0" until the bit "1" is coded. In run length coding the number of D bits can be one or four depending on the number of "1" in the scan pattern stripe.

The first D is equal to 0 if all four bits are 0, otherwise it is equal to 1. CX value in both of these cases is equal to 17. Additionally two more D bits are used to indicate the position of first 1 bit among four consecutive scan pattern bits. These two D bits are used with uniform context value 18. Table 7 summarizing the Context value for all four coding operations. Initial index portion of the Table 7 will be discussed in deatil under subsection 2.5.

Table 7: Coding Operations Context summary table

| Operation                      | Context (CX) | Initial Index I(CX) |  |

|--------------------------------|--------------|---------------------|--|

|                                | 0            | 4                   |  |

| Zero Coding                    | 1            | 0                   |  |

|                                | 2            | 0                   |  |

|                                | 3            | 0                   |  |

|                                | 4            | 0                   |  |

|                                | 5            | 0                   |  |

|                                | 6            | 0                   |  |

|                                | 7            | 0                   |  |

|                                | 8            | 0                   |  |

| Sign Coding                    | 9            | 0                   |  |

|                                | 10           | 0                   |  |

|                                | 11           | 0                   |  |

|                                | 12           | 0                   |  |

|                                | 13           | 0                   |  |

|                                | 14           | 0                   |  |

| Magnitude Refinement Coding    | 15           | 0                   |  |

|                                | 16           | 0                   |  |

| Down Lorenth Co. E. a. UNIFORM | 17           | 3                   |  |

| Run-Length Coding UNIFORM      | 18           | 46                  |  |

#### 2.4. EBCOT Coding Passes

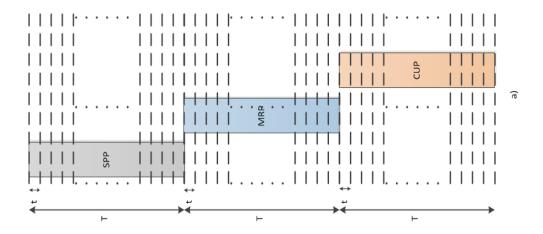

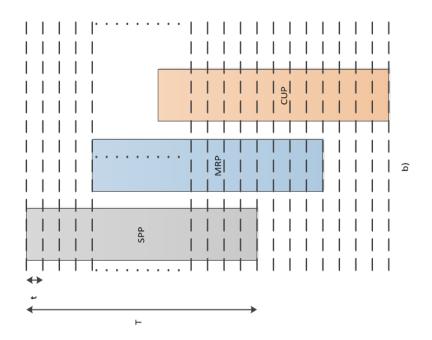

EBCOT coding is done in three different coding passes, coding passes in their order of coding are Significance propagation pass (SPP), Magnitude refinement pass (MRP) and Cleanup pass (CUP). Each of these passes are applied to every bit-plane of the code-block except the most significant bit-plane. For most significant bit-plane only CUP coding pass is applied. In each

of the coding pass the bits are scanned as per scan pattern and encoded, after completion of one coding pass, the next coding pass restarts the scan from the beginning of the bit-plane of the code-block. Coding passes in order of coding in EBCOT algorithm are explained in detail below:

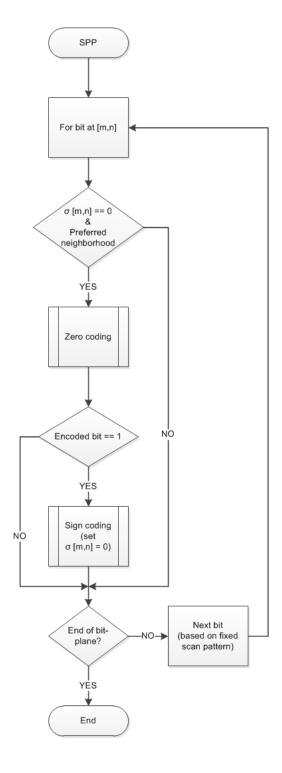

Significance Propagation pass (SPP): SPP is applied to every bit-plane except the most significant bit-plane. SPP checks for possibility of application of Zero coding(ZC) and Sign Coding(SC) to the current scan bit. ZC is applied if the current scan bit (m,n) is in preferred neighborhood and  $\sigma[m,n]=0$  and  $\eta[m,n]$  is set to 1. SC is applied if  $\upsilon^p[m,n]=1$  and  $\sigma[m,n]$  is set to 1. SPP scan is continued until all the bits in bit-plane are coded. Figure 6 shows the flow chart of SPP.

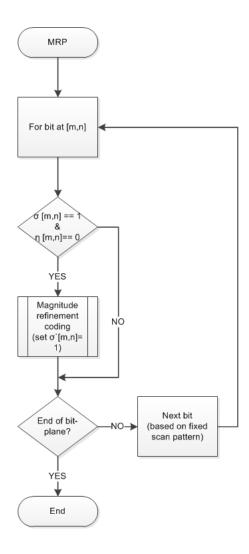

Magnitude Refinement Pass (MRP): MRP coding is applied to every bit-plane except the most significant bit-plane. MRP is applied to the current scan bit at position (m,n) if the state variables  $\sigma[m,n]=1$  and  $\eta[m,n]=0$ , and  $\sigma'[m,n]$  is set to 1. MRP coding is continued until all the bits is the bit-plane are encoded. Figure 7 shows the flow chart of MRP.

Figure 6: Significant Propagation Pass Flowchart

Figure 7: Magnitude Refinement Pass Flowchart

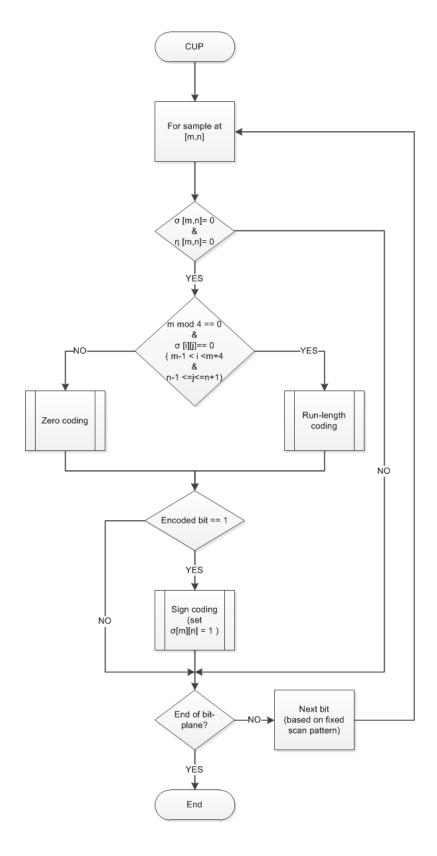

Figure 8: Cleanup Pass Flowchart

Cleanup Pass (CUP): CUP coding is applied to every bit-plane of the code-block. CUP can apply Sign Coding (SC) and one among Run-Length Coding (RLC) or Zero Coding (ZC) to the current scan element (m,n) based on the value of the state variables. If  $\sigma[m,n]$  and  $\eta[m,n]$  are equal to 0 then CUP applies the coding algorithms to the bit, otherwise it skips to next scan bit in the bit-plane. If  $\sigma[m,n] == 0$  and  $\eta[m,n] == 0$  then CUP checks to apply RLC or ZC, below three conditions should be satisfied to apply RLC, if any one of them is not satisfied then ZC is applied to current scan bit.

- m is multiple of four, including m = 0.

- $\sigma = 0$  for the four consecutive locations on the same column, starting from current scan position.

- $\sigma = 0$  for all the adjacent neighbors of the four consecutive bits in the column.

The number of coded bits vary depending on the type of coding applied to the scan bit. CUP after RLC or ZC coding, checks for application of SC. If  $v^p[m,n]$  equals to 1 then SC is applied to the scan bit and  $\sigma[m,n]$  is set to 1. CUP iterates this for all the bits in the bit-plane of the code-block, after completion of all the bits in the bit-plane,  $\eta[m,n]$  is cleared to 0 for all n and m in the bit-plane before starting coding of the next bit-plane. Figure 8 shows the flow chart of CUP coding.

#### 2.5. Binary Arithmetic Coding (BAC)

EBCOT algorithm uses Binary Arithmetic Coding (BAC) to encode/decode symbols generated from BPC. Context (CX) and decision (D) information generated from BPC is encoded by BAC to generate compressed code bytes. BAC used in Tier-1 coding is a special variant of QM-coder used in JPEG, it's a context adaptive BAC know as MQ-coder.

Arithmetic coding is a variable length encoding technique, it encodes a sequence of input symbols to generate specific code. In arithmetic coding the input symbols are encoded into an interval of real number, the encoded interval is confined to a fixed standard range associated with the algorithm. Length of the encoded interval is inversely proportional to the probability of occurrence of the symbol. More probable symbol produces smaller encoded interval than less probable symbol and hence reaching higher encoding efficiency.

Arithmetic coding is highly efficient for coding bi-level symbols as compared to other entropy encoding techniques. However arithmetic coding is computational exhaustive and is more prone to errors. Several coding techniques have been derived from arithmetic coding to overcome computation complexity, QM-coder is one such coding technique. QM-coder is an adaptive binary arithmetic coding algorithm used in JBIG2 (Joint Bi-level Image Processing Group) standard [9] for bi-level image compression. It is an incremental coding technique, where the encoder need not wait until all the symbols are received to generate encoded data and decoder need not wait until all the encoded data are received to start decoding.

The principle idea of QM-coder is to map input symbols to more probable symbol (MPS) and less probable symbol (LPS). For instance if the inputs to QM-coder are binary signals 1 and 0, bit 1 is mapped to MPS if most of the neighbors of the current bit coded are 1 and bit 0 will be mapped to LPS, similarly bit 0 is mapped to MPS if most of the neighbors of the current bit coded are 0 and bit 1 will be mapped to LPS. QM encoder decides if the next input bit belongs to MPS or LPS and compresses this information, similarly decoder determines if the decoded bit is MPS or LPS and generates the decoded symbols based on this information.

QM-coder assigns a portion of predetermined fixed interval to MPS and LPS symbols based on the probability estimates of the symbols, it uses probability estimation table for each of the symbols generated in coding process. MQ coder used in JPEG2000 is a variant of QM coder in terms of the encoding interval, probability estimation table and computation complexity of coder. In this thesis we concentrate on MQ-encoder algorithm and its implementation specifics, MQ-decoders algorithm is beyond the scope of this thesis.

#### 2.5.1. MQ-encoder

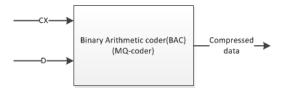

Top level block diagram of MQ-encoder is as shown in Figure 9. Inputs to MQ-encoder are Context (CX) and Decision (D) bit generated from BPC block. MQ-encoder generates compressed data as output. MQ encoder uses several look-up-tables (LUT) for the computation of compressed data, LUTs used by MQ-encoder are probability estimate table (Qe-table), this holds the probability estimates for all possible states reached by the encoder, Index-context table (I(CX)) and More Probable Symbol context table (MPS(CX)) are used along with the Qe-table to keep track of state and the index of Qe-table for different input context value.

I(CX) is used to track the index of Qe-table, initial value of I(CX) is provided by the standard [1], it is as shown in the Table 7. MPS(CX) LUT is initialized to all zeros, it provides the sense of more probable symbol (1 or 0) of CX. NMPS(I(CX)) and NLPS(I(CX)) LUTs are used to identify next MPS/LPS index values respectively. SWITCH(I(CX)) indicates if the sense of MPS(CX) has to be inverted, next section discusses in detail about the condition under which the sense of MPS has to be inverted. LUTs of Qe, NMPS, NLPS and SWITCH with respect to index reference are as shown in Table 8.

Figure 9: MQ Encoder top level block diagram[1]

MQ-encoder requires two 32-bit register for computation. Register A and register C, the structure of these are as shown in Table 9. Register A is the interval register and is initialized to 0x00008000. Register C is code word register and is initialized to 0x00000000. "a" of register A represents fractional bits. In register C "x" represents fractional bits, "s" represents space bits,

Table 8: BAC lookup table for Qe value and probabiliy estimation[1]

| Index | Qe     | NMPS | NLPS | SWITCH |

|-------|--------|------|------|--------|

| 0     | 0x5601 | 1    | 1    | 1      |

| 1     | 0x3401 | 2    | 6    | 0      |

| 2     | 0x1801 | 3    | 9    | 0      |

| 3     | 0x0AC1 | 4    | 12   | 0      |

| 4     | 0x0521 | 5    | 29   | 0      |

| 5     | 0x0221 | 38   | 33   | 0      |

| 6     | 0x5601 | 7    | 6    | 1      |

| 7     | 0x5401 | 8    | 14   | 0      |

| 8     | 0x4801 | 9    | 14   | 0      |

| 9     | 0x3801 | 10   | 14   | 0      |

| 10    | 0x3001 | 11   | 17   | 0      |

| 11    | 0x2401 | 12   | 18   | 0      |

| 12    | 0x1C01 | 13   | 20   | 0      |

| 13    | 0x1601 | 29   | 21   | 0      |

| 14    | 0x5601 | 15   | 14   | 1      |

| 15    | 0x5401 | 16   | 14   | 0      |

| 16    | 0x5101 | 17   | 15   | 0      |

| 17    | 0x4801 | 18   | 16   | 0      |

| 18    | 0x3801 | 19   | 17   | 0      |

| 19    | 0x3401 | 20   | 18   | 0      |

| 20    | 0x3001 | 21   | 19   | 0      |

| 21    | 0x2801 | 22   | 19   | 0      |

| 22    | 0x2401 | 23   | 20   | 0      |

| 23    | 0x2201 | 24   | 21   | 0      |

| 24    | 0x1C01 | 25   | 22   | 0      |

| 25    | 0x1801 | 26   | 23   | 0      |

| 26    | 0x1601 | 27   | 24   | 0      |

| 27    | 0x1401 | 28   | 25   | 0      |

| 28    | 0x1201 | 29   | 26   | 0      |

| 29    | 0x1101 | 30   | 27   | 0      |

| 30    | 0x0AC1 | 31   | 28   | 0      |

| 31    | 0x09C1 | 32   | 29   | 0      |

| 32    | 0x08A1 | 33   | 30   | 0      |

| 33    | 0x0521 | 34   | 31   | 0      |

| 34    | 0x0441 | 35   | 32   | 0      |

| 35    | 0x02A1 | 36   | 33   | 0      |

| 36    | 0x0221 | 37   | 34   | 0      |

| 37    | 0x0141 | 38   | 35   | 0      |

| 38    | 0x0111 | 39   | 36   | 0      |

| 39    | 0x0085 | 40   | 37   | 0      |

| 40    | 0x0049 | 41   | 38   | 0      |

| 41    | 0x0025 | 42   | 39   | 0      |

| 42    | 0x0015 | 43   | 40   | 0      |

| 43    | 0x0009 | 44   | 41   | 0      |

| 44    | 0x0005 | 45   | 42   | 0      |

| 45    | 0x0001 | 45   | 43   | 0      |

| 46    | 0x5601 | 46   | 46   | 0      |

it provides constraints on carryover, "b" represents bits of ByteOut and "c" represents the carry bit.

MQ-encoder subdivides the interval into two sub-interval for each context (CX) and decision (D) pair input. The interval register content is modified accordingly to point to the lower bound of the probability sub-interval of the symbol currently encoded. Partitioning of the sub-interval is done in such a way that the sub-interval of MPS is positioned above the sub-interval of LPS. Hence its necessary for the encoding algorithm to recognize the input symbols as MPS or LPS and keep track of the sense of MPS/LPS along with the interval associated with that. Since the encoding process works on the basis of accumulating several symbol information before finally generating compressed data byte, more probable symbols are encoded with much less than one bit per symbol.

MQ-decoder algorithm performs the inverse operation on the compressed data to generate the encoded symbols. MQ-decoder primarily determines the sub-interval pointed to by the compressed data, it also operates recursively for determination of context and decision information.

The interval considered for MQ-coder is 0.75, MQ-coder uses fixed precision integer arithmetic. Integer representation of the fractional value 0.75 is equivalent to 0x8000 in hexadecimal. Hence the A register is initialized to 0x8000 and C register is initialized to 0x0000. The algorithm is designed to keep the interval in the range of  $0.75 \le a \le 1.5$ , whenever the interval value falls below 0.75, interval correction is made by doubling it. The content of C register is also doubled whenever the A register content is doubled. Compressed data byte is generated from the higher order bits of C register, bit position of C register are as shown in Table 9. Carry over to already generated compressed byte is avoided by the algorithm.

Calculations of the sub-intervals are as shown in equations 4 to 7, a simple arithmetic approximation is used for interval sub-division. For the purpose of illustration if the interval is A and probability estimation of LPS/MPS is Qe then the sub-interval for MPS is given by equation 4 and sub-interval for LPS is given by 5. Since the value of A is close to unity equations 4 and 5 are approximated to equation 6 and 7 respectively. At each sub-interval calculation step, the value of A is checked to determine if renormalization of interval is necessary, in such a case the value of A register and C registers are renormalization.

$$MPS \ sub-interval = A - (Qe * A) \tag{4}$$

$$LPS \ sub-interval = (Qe*A) \tag{5}$$

$$MPS \ sub-interval = A - Qe \tag{6}$$

$$LPS \ sub-interval = Qe \tag{7}$$

The interval subdivision process can run into a scenario where the value of MPS is less than the value of LPS, in such a case the intervals of MPS and LPS are exchanged, such a condition can occur when renormalization is necessary. During renormalization process the value of next probability estimate is determined for the current context value being encoded. The value of next probability estimation is determined from Table 8

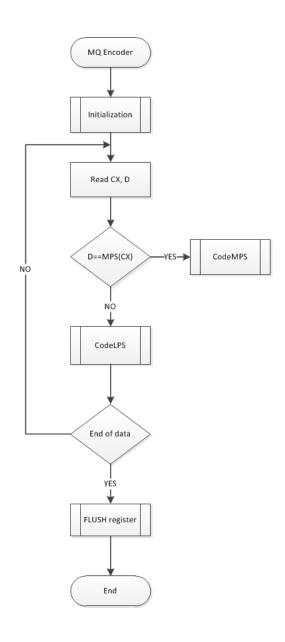

The flow chart of MQ-encoder is as shown in Figure 10. In the "initialization" step the computational register A and C are set to their initial values, the counter and pointer variables used by the algorithm are set to default value and the LUTs are reset to default value. In the "Read CX, D" step the Context (CX) and Decision (D) input symbols are read from BPC stage. The read symbols are used in the decision "D==MPS(CX)" step to compare the D value with the sense of MPS associated with the current context values. If the D value is same as the sense of MPS associated with current CX then MPS coding is performed otherwise LPS coding is performed. After MPS or LPS coding operation, the next CX and D symbol pair is read for encoding, this cycle is repeated until all the symbols are encoded.

In MPS coding step "CodeMPS" Qe value associated with current CX is read from the LUT Table 8. The content of C register is added with Qe value and the interval register A is modified correspondingly. Depending on the value of interval register A, the sense of MPS/LPS may be exchanged and the content of A and C registers may be renormalized. The values of next index for the current CX is determined by NMPS(I(CX)) value from the LUT Table 8.

In LPS coding step "CodeLPS" Qe value associated with current CX is read from the LUT Table 8. The content of A and C registers are modified correspondingly. If the value of SWITCH for the index of current CX is "1" then the sense of MPS is changed. The renormalization procedure is always called in LPS coding and is called in MPS coding procedure if the value of A register is less than 0x8000. The next index for the current CX is given by NLPS(I(CX)) value in the LUT Table 8.

In renormalization procedure the content of A register is shifted left until its value is equal to or greater than 0x8000, during this shifting process the context of C register is also shifted same number of time as it is done with A register. The renormalization procedure may invoke the function to output the compressed byte from the C register, it also avoids propagation of carry into already outputted compressed byte. "FLUSH register" step is reached after all the symbols are encoded, in this step the register C is stuffed with as many "1" bits as possible before outputting the final byte of the compressed stream. Pseudo code[2] for "Initialization", "CodeMPS", "CodeLPS" and "Renormilization" is as shown under Appendix C.

Table 9: BAC Encoder Register Structures

| 32-Bit Register          | MSB                 | LSB                 |

|--------------------------|---------------------|---------------------|

| С                        | 0000 cbbb bbbb bsss | XXXX XXXX XXXX XXXX |

| (Code Register)          |                     |                     |

| A                        | 0000 0000 0000 0000 | aaaa aaaa aaaa aaaa |

| (Current Interval Value) |                     |                     |

Figure 10: MQ-Encoder flow chart[2]

#### **3.** EBCOT ENCODER IN SOFTWARE

The EBCOT hardware architecture design in this thesis is verified against a reference model from OpenJPEG [10]. OpenJPEG is an open-source library for JPEG2000 encoder and decoder. OpenJPEG is implemented in C language. OpenJPEG apart from JPEG2000 codec features, it also supports Motion JPEG2000 (MJ2) features. Some of the features supported by OpenJPEG software are:

- Lossless and lossy compression with different compression ratios.

- Different input image formats like "pgx", "pnm", "pgm", "ppm", "bmp", "tif", "raw", "tga", "png"

- Ouput image formats like J2k and JP2.

- Supports image size up to  $(2^{32}-1)\times(2^{32}-1)$  and image components up to  $2^{14}$

- Code-block size in powers of 2 upto maximum image size.

- Supports tile sizes in powers of 2 upto maximum image size.

- ROI processing support.

- Use of irreversible DWT 9-7

- Cinema 2k and 4k resoultion modes, supports only 24 or 48 frames per second video formats.

- Markers in main header and tile header (SOC SIZ COD QCD COM).

- Progression order (LRCP, RLCP, RPCL, PCRL, CPRL).

- SOP and EPH markers in the code streams.

- Coding of multiple images at a time(10 images at one go, sequentially)

#### 3.1. Architecture

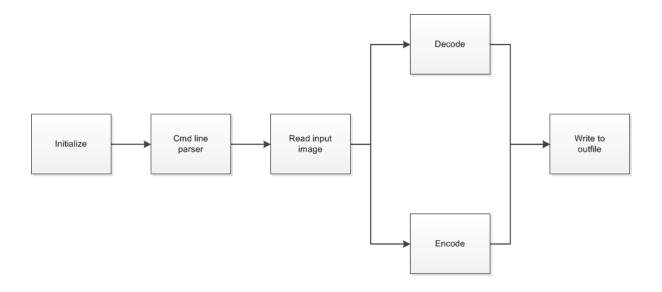

Top level software architecture of OpenJPEG is as shown in Figure 11. In Initialization step, event call-back functions are defined, encoding parameters are set to default values and the indexes used during encoding/decoding are initialized. Command line parser parses the user commands for input image with coding type and coding parameters. Read input image block reads the image to be processed from the specified directory. OpenJPEG can process upto ten images with one command, these images are encoded/decoded sequentially one after the other. Coding type parameter is used to select encoder or decoder function for processing the input image in next step. The generated output stream is written into specified output file in write to outfile block.

Figure 11: Software Architecture block diagram

We focus our discussion on Encoder block in this thesis. Figure 12 shows the block diagram of Encoder. Write markers block writes several markers such as Start of Code stream (SOC marker), Image size and tile size (Size marker), Coding style (COD marker) and quantization default (QCD marker) to code stream. Create tile encoder creates the data structure for tile encoder and returns the handler for further use. Memory required for processing of tile is allocated by allocate memory block, memory required for one tile is allocated and is reused for rest of the tiles.

Start of tile and start of data markers are written in write SOT and SOD markers blocks. Encoding of the data is done in Tile encode block (TCD), TCD encode block encodes the data from input image into JPEG2000 code stream and writes the encoded code stream into buffer. TCD encoding is repeated for all the tiles and the code stream is written into the outfile. Memory allocated for TCD block is freed after completion of encoding operation and is done in Free memory block. EOC marker block writes End of Code stream marker into the code stream.

Figure 12: Encoder block diagram

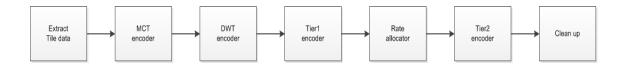

TCD encoder is the block resposible for implementation of coding phases of EBCOT. Block diagram of TCD encoder is as shown in Figure 13. Input image is extracted and processed in terms of tiles, this is done by extract tile data block. Reversible multi-component transform is

applied to the extracted data in MCT encoder. Discrete wavelet transform is applied to MCT encoded data in DWT encode.

Tier 1 encoding is done on the DWT encoded data to produce Context (CX) and Decision value bit (D). Rate allocation block is responsible for construction of bit-stream from encoded code-blocks for a give bit-rate with least distortion. Tier-2 encoding is primarily responsible for efficiently representing layer and block summary information for each code-block. Tag Tree data structure is used in Tier-2 encoding for efficient code stream representation. In clean up step the memory allocated for coding is cleared and the parameters are initialized to default values.

Figure 13: TCD Encoder block diagram

#### 3.2. Profiling

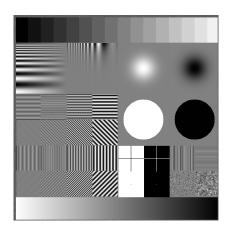

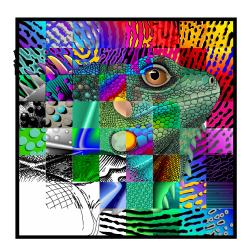

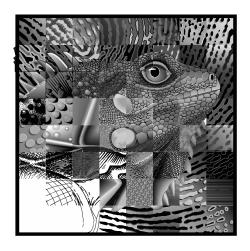

This subsection deals with profiling of JPEG2000 encoder implemented in software. The aim of profiling is to analyze different processing blocks in JPEG2000 encoder in terms of the relative processing time, processing dependencies with respect to different code-block sizes, image sizes, color components, image properties etc. Several images with different characteristics were used for profiling. Characteristics of images used for profiling are shown in Table 10. Images used for profiling are shown under Appendix B.

| Image         | Dimension (pixles) | Size (bytes) | Bits per component | No of components |

|---------------|--------------------|--------------|--------------------|------------------|

| Bretagne1.ppm | 640x480            | 921638       | 8                  | 3                |

| Bretagne2.ppm | 2592 x 1944        | 15116584     | 8                  | 3                |

| Cevennes1.ppm | 2592 x 1944        | 15116584     | 8                  | 3                |

| bike.pgm      | 2048x2560          | 20263700     | 8                  | 3                |

| target.pgm    | 512x512            | 950471       | 8                  | 1                |

| lena.ppm      | 512x512            | 2883036      | 8                  | 3                |

| lena.pgm      | 512x512            | 983503       | 8                  | 1                |

| cwheel.ppm    | 800x600            | 4599557      | 8                  | 3                |

| cwheel.pgm    | 800x600            | 1686904      | 8                  | 1                |

| frymire.ppm   | 1118x1105          | 11781663     | 8                  | 3                |

| frymire.pgm   | 1118x1105          | 4103510      | 8                  | 1                |

Table 10: Image characteristics table

Each of the images in Table 10 were encoded and profiling statistics were collected. Encoding of these images were done with three different code-block size of  $64 \times 64$ ,  $32 \times 32$  and  $16 \times 16$ . The tile size for all the images was configured to 1. J2K Output image format was configured for all image encoding. Three different compression ratio of 100, 20 and 2 were used for encoding and reversible DWT 5-3 was used for encoding of all images.

#### 3.3. Profiling results

Profiling of JPEG2000 software implementation is done with images of different compression parameters, each of the profiling experiments and their results are discussed in detail in the below subsections.

#### 3.3.1. Compressed image size

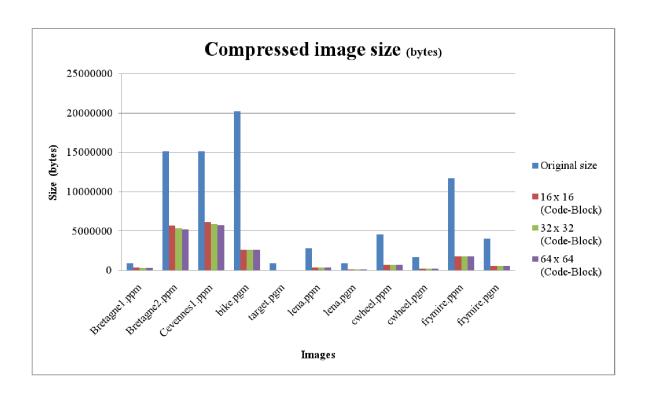

This subsection discusses the dependencies of compressed image size on different compression parameters. Compression algorithm is ran on the images in Table 10 for three different iterations with code-block size of  $64 \times 64$ ,  $32 \times 32$  and  $16 \times 16$  respectively. The size of the compressed images is collected, alone with the size of original uncompressed image.

Compressed image size along with original image size in bytes is plotted against the images. The plot is as shown in Figure 14. The plot shows that increase in code-block size decreases the size of the compressed image since the number of code-blocks formed for the images decrease and hence the size of encoded bit stream. The size of the compressed image also depends on the characteristics of the image; in general synthetic images are compressed better as compared to nature images.

Figure 14: Compressed image Size

#### 3.3.2. Compression time

Dependency of compression time on the size of the code-blocks is analyzed in this subsection. The images in Table 10 are compressed with code-block sizes  $64 \times 64$ ,  $32 \times 32$  and  $16 \times 16$  and the time required to compress in each iteration are noted. Figure 15 shows the plot of compression time against images.

Plot shows that the compression time increases with decrease in code-block size. When the code-block size is decreased the number of code-blocks formed per image increases and processing blocks like Tier-1 and rate allocation consumes significant amount of compression time (discussed in detail in subsection 3.3.3). For the set of images in Table 10, on an average it is observed that compression time with code-block size  $32 \times 32$  decreases by 60% as compared to compression time with code-block size  $16 \times 16$  and compression time with code-block size  $16 \times 16$ .

Figure 15: Compression time

#### 3.3.3. Block processing time

This subsection deals with analysis of processing time consumed by individual blocks of JPEG2000 encoder and the effect of code-block size on processing time of these block. Figure 16 shows the plot of processing time against images, the processing time consumed by each block for a particular image is plotted.

Plot shows that for code-block size  $64 \times 64$  processing time consumed by Tier-1 encoder is higher than the rest of the processing blocks irrespective on the image characteritics. For the set of images in Table 10, on a average it is observed that for code-block size  $64 \times 64$  Tier-1 consumes 65% of total compression time required for each image. Figure 17 and 18 shows block prcessing time plot for clode-block size  $32 \times 32$  and  $16 \times 16$  respectively. It is observed that rate allocation block's processing time increases significantly however Tier-1 processing time marginally increases with increase in code-block size.

Figure 16: Block processing time (code-block  $64 \times 64$ )

Figure 17: Block processing time (code-block  $32 \times 32$ )

Figure 18: Block processing time (code-block  $16 \times 16$ )

# 3.3.4. Conclusion

Profiling results have shown that Tier-1 encoding block consumes significant amount of compression time. Section 2 gives detailed explanation about the resources requirements for implementation of EBCOT in hardware. EBCOT encoder consumes significant amount of computational resource in JPEG2000. The aim of this thesis is to propose parallel architectural design to optimize resource requirement and processing time of EBCOT encoder.

#### 4. EBCOT ENCODER HARDWARE IMPLEMENTATION

This Section discusses the hardware implementation of EBCOT Tier-1 encoder. it discusses the top level architecture of major processing components of Tier-1 encoder in detail. Subsection 4.1.1 to 4.1.6 discusses in detail the architecture and hardware structure of individual components of BPC and BAC. Subsection 4.2 discusses the verification methodology adapted for verification of individual components of BPC and BAC. Simulation and synthesis results of BPC and BAC design are discussed under subsection 4.3.

#### 4.1. Architecture

This subsection discusses the hardware architecture and implementation of BPC and BAC in detail. Architecture is designed keeping in mind the feasibility of implementation on a FPGA (Field Programmable Gate Array), it also takes advantage of the flexibility offered by Xilinx FPGA in terms of block RAM and LUTs available on FPGA. A VHDL package of subtypes with meaningful names is created and these subtypes are used in the design files for better readability, ease of use and to reduce coding complexity. The VHDL package used in the design is given in appendix A.

#### 4.1.1. BPC TOP

Hardware is designed and implemented in a hierarchical fashion. Basic encoding algorithms like sign coding (SC), zero coding (ZC), run length coding (RLC) and magnitude refinement coding (MRC) are at the leaf level of the hierarchy. Instances of these leaf level blocks are used in SPP, MRP and CUP coding passes which forms the next hierarchy. Instances of coding passes and block RAMs along with control, input and output logic are used in top level and it forms the highest level of hierarchy. Hierarchy structure of BPC is as shown in Figure 19. The top level architecture of BPC is as shown in Figure 20. Processing blocks depicted in Figure 20 are explained in detail in the subsections below.

Figure 19: Hierarchy of BPC design

#### Input Block

Input block reads the quantized wavelet coefficients for entropy encoding. Input block reads the coefficients associated with the entire code-block in single iteration. The read coefficients are decomposed into bit-planes and stored in the block RAM associated with the bit-plane. BPC algorithm does processing on each of the bit-planes associated with one code-block. Input block is described along with a flow chart under subsection 4.1.2

# State Variable ( $\sigma$ , $\sigma'$ , $\eta$ , v, $\chi$ ) Block RAM

Block RAMs(Random Access Memory) in FGPA are used to store the values associated with the state variables used in BPC entropy encoding. Each of these block RAMs are accessed by several processing block in BPC. The blocks accessing state variable's block RAMs are Input block, SPP, MRP and CUP. BPC architecture is designed with the assumption that the maximum code-block size processed by the system is  $32 \times 32$  pixels. However the code-block's size variables are parameterized in the design file, hence the system can be easily enhanced to higher code-block size by replacing the block RAMs with relevant dimension and assigning corresponding values to code-block's size parameters.

## **Memory Arbiter**

Block RAMs used by state variable are accessed by several processing blocks. Memory Arbiter arbitrates among the port requesting access to block RAMs. Each input port requesting access is associated with a control signal, on assertion of this control signal the request to access port is granted to the requesting port. Detailed discussion about memory arbiter is done under subsection 4.1.4.

#### SPP, MRP and CUP

SPP, MRP and CUP are the coding passes of BPC algorithm. Each of these coding passes performs encoding operation on bit-planes of the code-block to generate encoded symbols. Section 2.4 covers the detailed description of these coding passes. Coding passes are controlled by the control block; control block controls the sequence of encoding of each of the bit-planes and also the coding passes to be enabled for each of the bit-plane. The encoded symbols generated by these coding passes are passed on to the output block.

### **Output Block**

The encoded symbols generated by the coding passes are collected by the output block and are written into the output memory. These encoded symbols are later accessed by the BAC block for arithmetic encoding.

#### Control Block

Control block generates all the control signals necessary for encoding process of BPC. It generates initialization signals for different blocks at different stages of encoding process. Control block initiates reading of quantized wavelet coefficients through input block. It controls the sequences of coding passes during encoding, it also initiates writing out of generated output symbols through output block. Details of control block along with the flow chart is explained under subsection 4.1.3.

Figure 20: Top Level Architecture of BPC

#### 4.1.2. Input Block

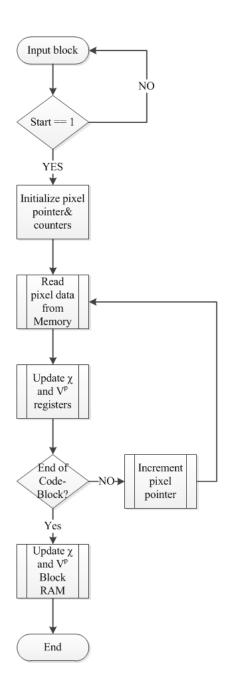

Flow chart of input block is as shown in Figure 23. Input block is enabled by a start signal from control block. Input block waits in the initial state until the start signal is asserted. After the start signal is asserted input block initializes the pointers and counters used in the state machine. It then reads the quantized wavelet coefficients from the memory.

Memory is read through a memory bus protocol, protocol is described in detail under subsection 4.1.4. The read coefficients are processed and temporary registers of sign array ( $\chi$ ) and bit-plane ( $v^p$ ) are updated. The cycle is repeated until all the coefficients of a code-block are read. After the code-block is read completely the content of  $\chi$  and  $v^p$  block RAMs are updated with the temporary  $\chi$  and  $v^p$  register contents.

#### 4.1.3. Control Block

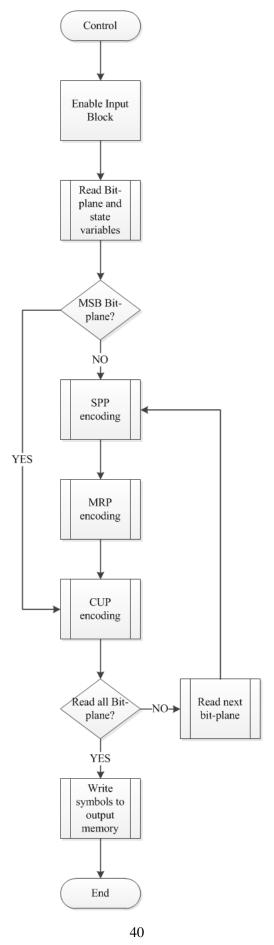

Flow chart of control block of BPC is as shown in Figure 24. Control block enables the input block to read the input coefficients and update  $\chi$  and  $v^p$  RAMs. It then initiate reading of state variables and bit-plane necessary for BPC encoding from the block RAMs. If the bit-plane is MSB bit-plane then only CUP encoding is done otherwise SPP, MRP and CUP encoding is done in sequence respectively. This cycle is repeated until all the bit-planes are encoded. Once encoding of all the bit-planes is completed, control block initiates writing of encoded symbols into the symbol memory. This encoded symbol memory is accessed by BAC to generate compressed bit-stream.

#### 4.1.4. Memory Arbiter

Memory arbiter in BPC arbitrates the requests for the state variable's block RAMs. State variable block RAM is accessed by severable blocks of BPC at different processing instance. Memory arbiter has special memory bus interface [3] to block RAMs, read/write to the block RAM is through memory bus. Memory arbiter functions like a multiplexer; it establishes the connection between the block RAM memory interface and processing block's memory interface when the control signal associated with the processing block is asserted. These control signals are asserted by the control block, it decides which processing block has to be enabled at what processing instance. Memory arbiter is designed with the assumption that no two processing block will request for access to block RAM at the same time.

Figure 21: Single-port RAM

Block diagram of block RAM used in BPC is as shown in Figure 21. It is a single-port RAM with 32 memory locations of 32 bits each and is configured in read first mode. An example waveforms of memory bus protocol configured in read first mode is as shown in Figure 22. This waveform is an example used for explanation of the protocol, width of the signal bus in the Figure 22 does not correspond to the actual bus width used in BPC.

When the enable (ENA) signal is de-asserted, read/write to RAM is disabled. When ENA is asserted and write enable (WEA) is low, RAM is in read mode, it reads from the location addressed by address bus (ADDRA) and the read data is available on output data bus (DOUTA). When ENA is high and WEA is also high, RAM is in write mode and the data on data input bus (DINA) is written into the RAM at the location addressed by the ADDRA bus. Read first configuration mode of block RAM means that the old value of RAM at address X is read out on to DOUTA bus in case of write access to address X of block RAM. The read/write latency of the block RAM is one clock cycle.

Figure 22: Read first mode single-port RAM [3]

Figure 23: Input block of BPC

Figure 24: Control block of BPC

#### 4.1.5. SPP, MRP and CUP

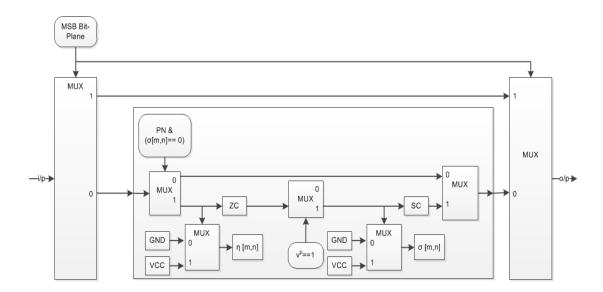

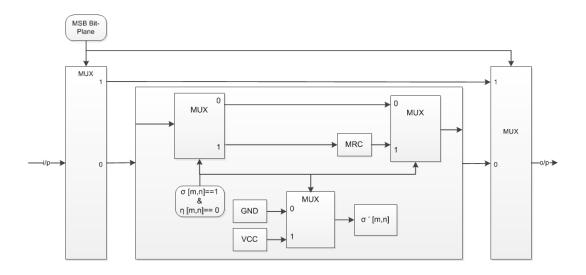

The hardware structure of SPP, MRP and CUP is as shown in the Figure 25, 26, and 27 respectively. Coding passes along with the flow chart are described in detail under subsection 2.4. These hardware structures are not the result of synthesizing VHDL code of coding passes, these structure are conceptual and are used for better understanding of the coding pass hardware.

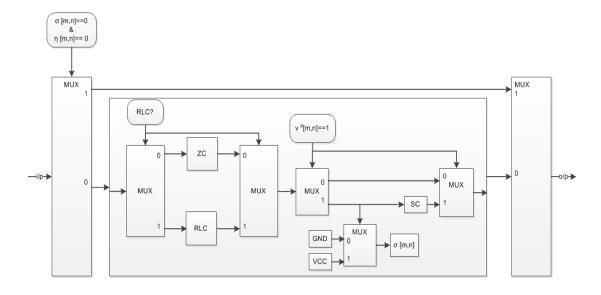

SPP and MRP coding passes are not applied to MSB bit-plane; this can be observed from the Figure 25 and 26 respectively. The first multiplexer (MUX) bypasses the whole processing components if the bit-plane is MSB bit-plane. CUP coding pass is applied to all the bit-planes of the code-block. SPP coding pass applies zero coding (ZC) and sign coding (SC) encoding algorithms on the bit-planes, CUP applies run length coding (RLC), sign coding (SC) and zero coding (ZC) on bit-planes and MRP applies magnitude refinement coding (MRC) on bit-planes. The conditions for application of these encoding algorithms in each coding passes are explained in detail in subsection 2.4.

Figure 25: SPP Hardware structure

Figure 26: MRP Hardware structure

Figure 27: CUP Hardware structure

#### 4.1.6. BAC TOP

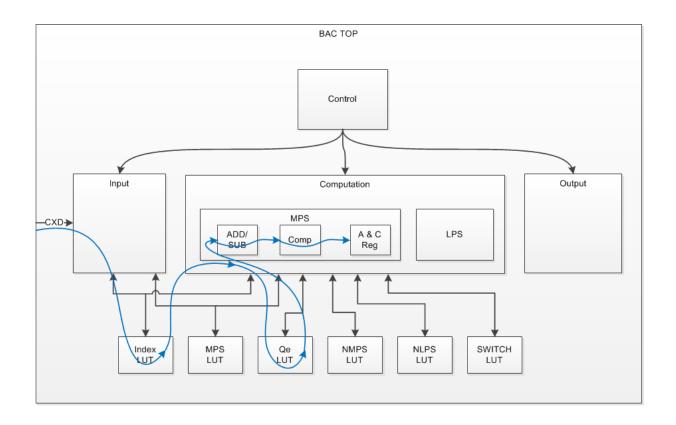

The architectural block diagram of BAC is as shown in Figure 28. BAC is also designed and implemented in hierarchical fashion. BAC has only two level of hierarchy. The leaf level blocks are the LUTs used in the design. Input, computation and output blocks uses instances of LUTs, these form the highest level of hierarchy in BAC. BAC algorithm along with the flow chart is described in detail under section 2.5.

All LUTs used in the design has read interface. Index and MPS LUTs have both read and write interface since the value of these LUT table can be updated by MPS and LPS computational blocks. Input block initializes the counters, register, LUTs and pointers used in the algorithm. MPS and LPS are the main computation block in BAC. The StrucBtyte block is responsible for generation of compressed byte depending on the computational results of MPS and LPS blocks. Flush block is responsible for generation of the last byte when all the input symbols are encoded. Control block generates control signal to sequence the operation of input, computation and output blocks.

Figure 28: Top Level Architecture of BAC

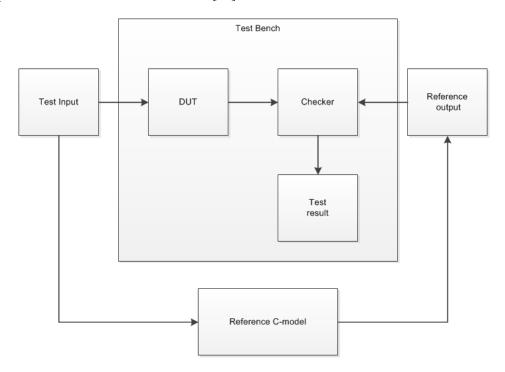

## 4.2. Verification Methodology

Verification methodology followed in this thesis is shown as a block diagram in Figure 29. Verification is done stand alone for individual components at each hierarchy levels of BPC and BAC, also for top level BPC and BAC. Test bench used for verification is designed to be self checking test bench. Device under test (DUT) can be any of the components of BPC or BAC.

Test input represents all possible valid combinations of input vectors. Test inputs are created either manually or through a reference C-model. Test bench needs a reference output to check the correctness of the response generated by DUT for a particular test input vector. Test bench reads the test inputs from a file for verification of top level BPC and BAC components. Test bench reads the reference output from a file; reference output is created either manually or through reference C-model. Reference C-model used in this thesis is discussed in detail under section 3.

Test bench forces the test input into DUT, response generated by DUT is collected by checker and checker also reads the reference output for the particular input. Checker compares the response from DUT with reference output and updates the test result. Test result can be pass or fail; it also logs the information about input vector, generated response and reference output at the point of test failure. Xilinx ISE 13.2 [11] simulation tool is used for verification.

Figure 29: Test bench block diagram

### 4.3. Simulation and Synthesis Results

Simulation and synthesis results of BPC and BAC design are discussed under this subsection. This section also discusses important control signal associated with BPC and BAC with waveforms. Device utilization and timing details of synthesized BPC and BAC design are discussed in detail. The Target FGPA device for which BPC top and BAC top is synthesized is "Virtex - 5" Xilinx FPGA family with device id "XC5VLX110T", package id "FF1136" and speed grade "-1" [12].

#### 4.3.1. BPC

Entity of top level BPC VHDL design is as shown in Table 11. *clk* and *reset* input signals are driven by the testbench. These signals are used to drive *clk* and *reset* inputs of all the instances in BPC design. BPC top has a memory interface to read pixel data associated with the code-block. Input and output ports associated with memory interface are defined as sub-types *mem\_port\_out* and *pixel\_mem\_port\_in* respectively. Description of these subtypes can be found under appendix A. *pixel\_data\_valid* control signal is an input to BPC top, it is used to indicate that the pixel data of code-block is valid to be read and encoded.

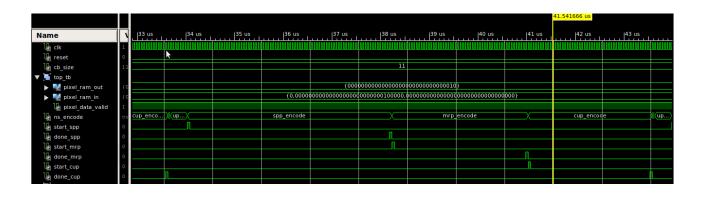

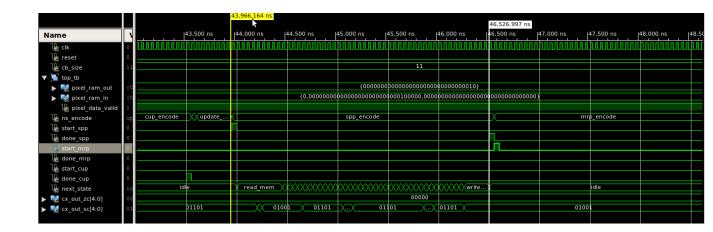

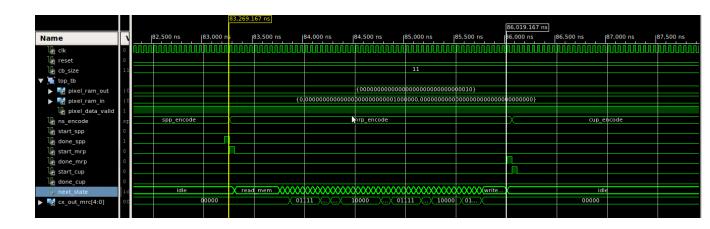

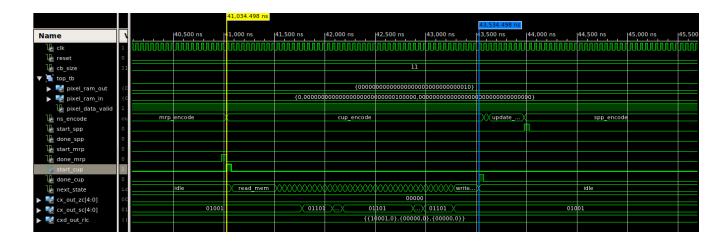

Bit-planes of the code-block are encoded in three coding passes as discussed under subsection 2.4. Simulation waveform of BPC coding passes is as shown in Figure 30. Control signals  $start\_spp/start\_mrp/start\_cup$  and  $done\_spp/done\_mrp/done\_cup$  are used to indicate beginning and end of coding pass SPP/MRP/CUP respectively. All bit-planes apart from the MSB bit-plane are encoded by SPP, MRP and CUP coding pass in sequence as shown in Figure 30.

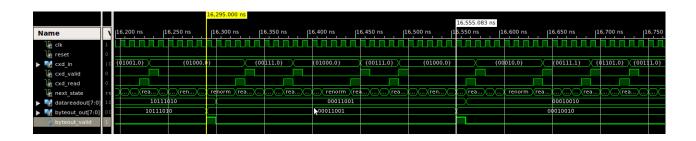

Simulation waveforms of SPP, MRP and CUP encoding are as shown in Figure 31, 32 and 33 respectively. At the start of each of these encoding pass, the memories corresponding to state variables and bit-planes necessary for encoding are read and the state associated with this is read\_mem. At the end of each of these encoding pass, the memories corresponding to state variables are updated and the state associated with this is write\_mem. States in between read\_mem and write\_mem are encoding states of coding pass. Encoding states of SPP, MRP and CUP coding pass are discussed in detail under subsection 2.4.

Maximum and minimum number of clock cycles required to encode a bit in a bit-plane of a code-block for SPP, MRP and CUP coding pass is as shown in Table 12. The numbers of clock cycles mentioned in the Table 12 are number of clock cycles required for pure encoding computation. It does not include the number of clock cycles required to read state variables and bit-plane from RAMs or writing back state variables into RAMs after encoding.

Minimum number of clocks required for all three coding pass is 1 clock cycle. Input bit is checked with certain condition at the beginning of encoding algorithm in each coding pass. If the condition is satisfied then the input bit is encoded otherwise encoding is skipped and algorithm checks with next input bit. This condition check on input bit requires one clock cycle, which is the minimum number of clock cycles required. Maximum number of clock cycles required to encode a bit depends on the number of states associated with each coding pass. The states associated with SPP, MRP and CUP coding pass can be found in Figure 6, 7, and 8 respectively.

Summary of BPC synthesis report is as shown in Table 13, 14, 16 and 15. Device resource utilization is as shown in Table 13. BPC utilizes 21% of FPGA LUT resource, however considerable amount of these resources are used by distributed RAMs associated with state variables and bit-planes. There are 14 RAMs in the design intended for state variables and bit-planes, out of which one is synthesized as block RAM and the rest are synthesized as distributed RAMs.

Macro statistics of BPC synthesis is as shown in Table 14. Synthesis tool has recognized 5 FSMs in BPC design, 1 FSM from each of the coding pass and 2 FSMs from BPC top. Look