# EFECTOS TÉRMICOS Y TRAMPA EN LOS TRANSISTORES AlGaN/GaN HEMT

Mohamed Chaibi<sup>(1)</sup>, Tomás Fernández<sup>(1)</sup>, Asmae Mimouni<sup>(1)</sup>, Kaoutar Zeljami<sup>(1)</sup>, Abdelwahed Tribak<sup>(1)</sup>, Fernando Sánchez<sup>(2)</sup>, Marina Verdú<sup>(2)</sup> chaibim@unican.es, tomas.fernandez@unican.es, fsanchezs@oc.mde.es

(1) Dpto. de Ingeniería de Comunicaciones, Universidad de Cantabria Avd. de Los Castros, s/n, 39005, Santander, Spain

(2) Dpto. de Investigación, Centro de Investigación y Desarrollo de la Armada Arturo Soria 289, 28033, Madrid, Spain

Abstract- Traps effects (due to the presence of surface-state densities and deep-levels) in AlGaN/GaN HEMT devices cause slow current transients referred as gate-lag and drain-lag effects that become a cause of so called current collapse. Current collapse is a reversible reduction of drain-current when both the gate and drain voltages are changed abruptly. This effect cause important deviation between DC and dynamic characteristics that limits the output power of the device at high frequencies. In addition, traps state depends on thermal and illumination conditions of the device. Energy from the illumination and temperature supports the electrons captured in traps states to overcome the energy-barrier to the conduction band. In order to improve the device performance and reliability, understanding the current collapse effects is critical, and it must be taken into account when an accurate large-signal dynamic model is needed. In this paper, drain-current collapse due to gate-lag and drain-lag effects as well as the effects of temperature on traps state are characterised based on pulsed measurements technique.

### I. INTRODUCCIÓN

Los transistores HEMT basados en nitruro de galio (GaN) y su aleación (AlGaN) han surgido en la última década como los dispositivos más prometedores para aplicaciones de alta potencia y alta temperatura gracias a sus propiedades como puede ser su ancho band-gap; estos presentan una mayor estabilidad térmica y tensión de ruptura, lo que les hace muy atractivos como posibles candidatos para dichas aplicaciones [1].

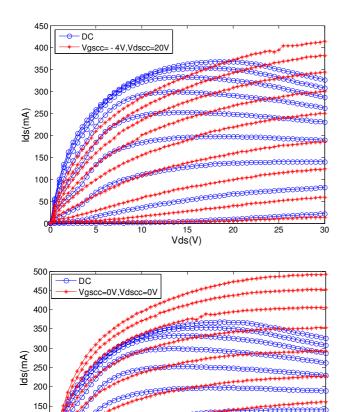

Sin embargo, estos dispositivos muestran una serie de efectos dispersivos como son los efectos térmicos y trampa. Los efectos trampa son unos de los desafíos más importantes para la madurez de tales dispositivos que se traducen en una diferencia entre sus características I/V dinámicas y aquellas llevadas a cabo en el régimen de DC (Fig. 1). Esta deferencia se refiere como dispersión o colapso de la corriente que conduce a una diferencia importante entre la potencia estimada bajo condiciones de DC y la que luego se obtiene experimentalmente cuando el dispositivo está operando en radio frecuencia (RF) [2]. El origen de esa diferencia se encuentra en trampas existentes tanto en los niveles profundos como superficiales que puedan capturar y librar electrones [3-9]. De hecho, al aplicar una señal RF al transistor, el canal del mismo responde a la variación de dicha señal, sin embargo, las constantes de tiempo de las trampas son suficientemente altas como para que los electrones atrapados no pueden seguir la señal RF y, por lo tanto, sin participar en la conducción limitándose la corriente del transistor. También las trampas afectan a la respuesta instantánea del transistor cuando se cambian bruscamente las tensiones de control del mismo, con la aparición de fenómenos transitorios (retrasos) en esa respuesta. Estos retrasos son conocidos como gate-lag y drain-lag. Además de los efectos trampa, las características I/V de estos transistores se ven afectados también por los efectos térmicos debido al auto-calentamiento del dispositivo gracias a la alta potencia que disipan estos transistores y a la temperatura externa, hecho que pone difícil la separación de dichos efectos.

El estado de las trampas depende mucho del estado térmico y de la iluminación del dispositivo debido a que estos dos factores pueden ser los proveedores de la energía necesaria a los electrones atrapados para que pasen a la banda de conducción y, por lo tanto, participar en la conducción aumentando, entonces, la corriente. Sin embargo, puesto que la mayoría de los circuitos usados en las aplicaciones reales están encapsulados, la influencia de la iluminación sobre las trampas no es tan importante mientras que se pueda utilizar como una forma de reducirlas.

La medida pulsada de las características I/V es una herramienta indispensable para la caracterización y la puesta en evidencia de los efectos trampa ya que permite evitar en gran parte los problemas del auto-calentamiento, comparando las características I/V para diferentes estados de trampas elegidos, sobre todo de poder separar los dos fenómenos con el fin de poder analizarlos finamente. Sin embargo, esa medida debe satisfacer, generalmente, unos criterios impuestos por las condiciones de funcionamiento del transistor que son un estado térmico constante durante toda la caracterización y un estado de trampas bien definido.

El objetivo principal de este trabajo es la caracterización de los efectos trampa que presentan los transistores HEMT de AlGaN/GaN y el estudio del efecto de la temperatura sobre esos efectos. Para ello se presenta las medidas típicas, que se han llevado a cabo para un transistor 8x75 GaN HEMT, necesarias para la caracterización y la puesta en evidencia tanto de los efectos trampa como del efecto de la

temperatura sobre ellos así como los requisitos que tienen que cumplir los bancos de medida pulsada para una tal caracterización precisa.

Fig. 1. Características I/V en DC y pulsada para dos puntos de polarización de reposo diferentes de un GaN HEMT.

Vds(V)

# II. GESTIÓN DE LOS EFECTOS TÉRMICOS EN LA MEDIDA PULSADA

Con el fin de evitar los efectos térmicos, la anchura de los pulsos que se aplican al dispositivo, partiendo de un punto determinado de polarización de reposo que determina la potencia disipada, debe ser la más corta posible para que el estado térmico del dispositivo no tenga el tiempo suficiente de cambiarse sea lo que sea la amplitud del pulso. Además, el periodo de los pulsos debe ser muy grande con respecto a la duración de los mismos para que el estado térmico sea únicamente fijado por el punto de polarización de reposo. Sin embargo, la anchura mínima de los pulsos está limitada por la capacidad de los generadores de pulsos utilizados de producir pulsos cortos y por el tiempo mínimo de adquisición de datos que debe ser, en el mismo tiempo, suficientemente grande para garantizar un estado establecido y asegurar una medida precisa y simultanea de las corrientes. Además, estos pulsos tienen que cumplir una determinada relación entre la duración del pulso y el periodo de los mismos. Razón conocida como ciclo de trabajo (Duty Cycle). Elegir adecuadamente el valor de esta razón de magnitudes es especialmente crítica en el caso de medir dispositivos de alta potencia (como es el caso de transistores HEMT de GaN), ya

que para cubrir todo el rango de funcionamiento de los mismos se hace necesario aplicar pulsos de tensión de gran amplitud. Veamos un ejemplo que permite estudiar como puede afectar el valor del ciclo de trabajo al proceso de caracterización, El punto de polarización de reposo (Vgscc=0V, Vdscc=0V) se utiliza como referencia para estudiar los efectos de gate-lag y drain-lag, ya que este punto se considera como estado sin trampas y sin autocalentamiento; desde él se lanzan pulsos para trazar las características I/V completas. Nótese que para trazar dichas curvas, en muchos casos es necesario alcanzar valores de la tensión dinámica de drenador que llegan a 30V o más, lo que implica aplicar un pulso de altura de 30V al dispositivo.

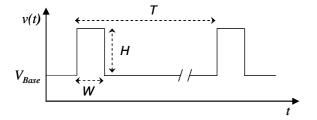

Comenzamos por calcular la componente de continua de un pulso que tiene una tensión de base  $V_{Base}$ , una anchura W, una altura H y un periodo T, tal y como se ve en la Fig. 2. Sabemos que dada una señal temporal v(t) de periodo T, podemos calcular la componente de continua de la misma utilizando la expresión:

$$v_{DC} = \frac{1}{T} \int_0^T v(t)dt \tag{1}$$

Aplicando la ecuación (1) a nuestra señal pulsada se llega a:

$$\begin{split} v_{DC} &= \frac{1}{T} \int_{0}^{T} v(t) dt = \frac{1}{T} \int_{0}^{W} \left( V_{Base} + H \right) dt + \frac{1}{T} \int_{W}^{T} V_{Base} dt \\ &= V_{Base} + \frac{W}{T} H \end{split} \tag{2}$$

Para ilustrar como puede modificar el valor de la componente de continua la elección del ciclo de trabajo, se va a calcular el valor de la componente de continua de una señal pulsada para tres valores diferentes del ciclo de trabajo (Tabla 1), en la que el punto de reposo es nulo y se quiere alcanzar un valor dinámico de 30V. Como se observa comparando los valores presentados en la Tabla 1, sólo el ciclo de trabajo con relación 1:1000 asegura que no se modifica de forma sensible el nivel de continua que se aplica con el pulso, de hecho, en este caso se obtiene un incremento de 0.03 voltios, para un pulso de 30V de altura, sobre el nivel de continua, mientras que para los otros casos se modifica hasta 1.5V el nivel de continua deseado.

El movimiento del punto de reposo durante las medidas pulsada inducirá un cambio del estado térmico del dispositivo. Esto se ve claramente en el caso, por ejemplo, de aplicar el pulso de tensión (*W*=500ns, y *T*=10µs) desde el punto de reposo (Vgscc=0V, Vdscc=0V) donde realmente el dispositivo se encontrará polarizado en (Vgscc=0V, Vdscc=1.5V) si se quiere alcanzar un valor dinámico de 30V donde podría estar entregando una corriente de 0.2A para el transistor bajo estudio y hasta 0.4A en otros dispositivos en ese punto de polarización; este valor de corriente dista mucho del valor deseado (0A), lo que puede desvirtuar las condiciones que se obtengan en términos de disminución de la corriente dinámica (colapso), ya que no se podrá asegurar si dichas disminuciones se deben a fenómenos como gate-lag o drain-lag o al propio calentamiento del transistor.

Fig. 2. Representación de un pulso típico usado en la medida pulsada.

| $V_{Base}(V)$ | H(V) | W     | T    | $V_{DC}(V)$ |

|---------------|------|-------|------|-------------|

| 0             | 30   | 400ns | 10μs | 1.2         |

| 0             | 30   | 500ns | 10μs | 1.5         |

| 0             | 30   | 1µs   | 1ms  | 0.03        |

Tabla 1. Componente de continua de una señal pulsada.

#### III. COLAPSO DE CORRIENTE

El impacto de los efectos gate-lag y drain-lag sobre el comportamiento del transistor se traduce en una degradación reversible de la corriente del drenador (la degradación irreversible se logra por el envejecimiento térmico o eléctrico del dispositivo). Esta degradación se refiere como colapso de corriente. Se puede poner de manifiesto este efecto mediante las medidas pulsada de las características I/V llevadas a cabo en puntos de polarización de reposo concretos.

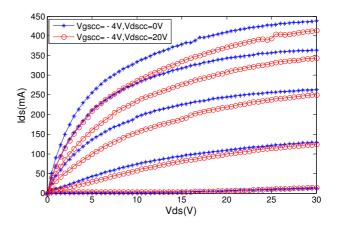

En el caso del colapso debido al gate-lag, se trata de llevar a cabo esas medidas variando el punto de polarización de reposo de la puerta Vgscc mientras que se mantiene la polarización de reposo del drenador igual a cero para todas las medidas. Con esta configuración no circula corriente continua en el dispositivo y, por lo tanto, está asegurada una medida sin auto-calentamiento. En la Fig. 3 se representa la comparación entre las características I/V pulsada llevadas a cabo en dos puntos diferentes de polarización de reposo de la puerta Vgscc=-4V y Vgscc=0V. En esos resultados se ve claramente que el dispositivo bajo estudio presenta un colapso importante debido al efecto de gate-lag.

Fig. 3. Colapso de corriente debido al efecto gate-lag.

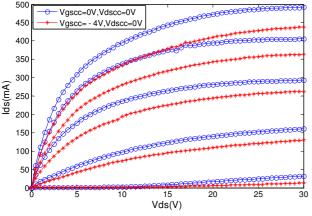

En el caso del colapso debido al drain-lag, se trata de llevar a cabo esas medidas variando el punto de polarización de reposo del drenador Vdscc mientras que se mantiene la polarización de reposo de la puerta igual a al tensión del pinch-off para todas las medidas. La razón de polarizar en pinch-off es asegurar un auto-calentamiento casi nulo. En la Fig. 4 se representa la comparación entre las características I/V pulsada llevadas a cabo para dos puntos diferentes de polarización de reposo del drenador Vdscc=0V y Vdscc=20V. En esos resultados se ve claramente que el transistor presenta una degradación importante de la corriente debido al efecto drain-lag.

Fig. 4. Colapso de corriente debido al efecto drain-lag.

## IV. INFLUENCIA DE LA TEMPERATURA SOBRE LOS EFECTOS TRAMPA

Generalmente el efecto térmico, tanto del autocalentamiento como de la temperatura externa, sobre las características I/V del transistor se traduce en una disminución del nivel de estas características cuando se aumenta la temperatura [10]. Esto debido a que la temperatura disminuye la movilidad y la velocidad de los electrones 2DEG (gas de electrones bidimensional) en el canal del dispositivo y, por lo tanto, disminuyendo la corriente [11]. Sin embargo, el aumento de la temperatura puede ofrecer una energía suficiente a los electrones atrapados en los niveles entremedios entre la banda de valencia y de conducción para que pasen a la banda de conducción y, por lo tanto, participar en la conducción aumentando, entonces, la corriente.

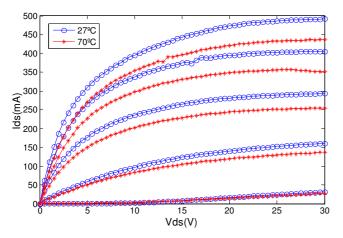

Para determinar el grado de influencia de la temperatura sobre los estados trampa se ha llevado a cabo las medidas pulsadas de las características I/V del transistor en dos puntos diferentes de polarización de reposo para dos temperaturas diferentes (27°C y 70°C). La medida DC de esas características es inútil para este tipo de caracterización puesto que presenta a la vez los efectos del autocalentamiento y trampa. En primer lugar, consideramos las medidas pulsadas I/V que corresponden al punto de polarización de reposo (Vgscc=0V, Vdscc=0V), considerado como un punto libre de trampas, para esas dos temperaturas. En la Fig. 5 se representan esas medidas donde se ve una importante degradación de corriente. Se puede considerar que dicha degradación solamente es debida al efecto de la temperatura externa puesto que el transistor está polarizado en un punto sin trampas y sin auto-calentamiento. En este caso la degradación de corriente en la zona de saturación es de 55mA y corresponde a 11,2%.

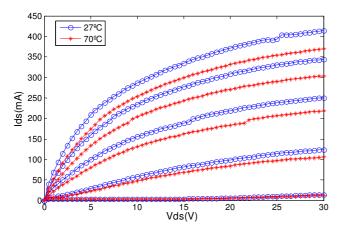

Ahora consideramos las medidas pulsadas de las características I/V que corresponden a un punto de polarización de reposo asociado a un estado de alta ocupación de trampas, pero en el mismo tiempo sin autocalentamiento, llevadas a cabo en las mismas temperaturas externas para guardar el mismo estado térmico del transistor. Este punto no puede ser otro que el que se fija al polarizar el transistor en pinch-off para la tensión de la puerta y en una tensión alta para la tensión de polarización del drenador, por ejemplo, (Vgscc=Vp,Vdscc=20V). En la Fig. 6 se representan las características I/V que corresponden a esas condiciones donde también se ve una degradación importante de corriente, pero en este caso menor que en el caso anterior puesto que una parte de los electrones atrapados se han librado gracias al efecto de la temperatura. En este caso se ha calculado una degradación en la zona de saturación de 43mA que corresponde a 10,4%. La diferencia entre la degradación de corriente en el caso sin trampas y con trampas es el porcentaje de corriente resultado por la liberación de los electrones atrapados debido a los efectos térmicos que es de 0,8% que corresponde a 0.28mA/°C en este caso.

Fig. 5. Características I/V en pulsada (Vgscc=0V,Vdscc=0V).

Fig. 6. Características I/V en pulsada (Vgscc=-4V,Vdscc=20V).

### V. CONCLUSIONES

En este trabajo se ha presentado la caracterización del colapso de la corriente de drenador en los transistores HEMT de AlGaN/GaN así como la influencia de la temperatura sobre las trampas basándose en las medidas pulsadas de las características I/V. Se ha demostrado que existe una relación

directa entre los efectos trampa, que causan los efectos gatelag y drain-lag, y el colapso de la corriente. El estudio y la determinación de los requisitos que tienen que cumplir los bancos de medida pulsada no son de menos importancia puesto que esa medida es la base de tal caracterización y el modelado de dichos efectos. Se ha demostrado también que la energía térmica puede hacer que los electrones atrapados sobrepasan la barrera energética para que pasen a la banda de conducción participando, entonces, en la conducción. Estos efectos, tanto térmicos como trampa, son uno de los desafíos importantes para conseguir la madurez del proceso tecnológico de tales dispositivos lo cual hay que tenerlos en cuenta tanto para el estudio de la fiabilidad del dispositivo como para el desarrollo de modelos precisos.

### **AGRADECIMIENTOS**

Los autores quieren expresar su agradecimiento al proyecto KORRIGAN EDA (RTP 102.052) dentro del cual se han obtenido los resultados presentados en este trabajo.

#### REFERENCIAS

- F. Schwierz and O. Ambacher, "Recent advances in GaN HEMT development" The 11th IEEE Inter. Symp. on Electron Devices for Microwave and Optoelectronic Applications, Nov. 2003.

- [2] J. Joh, J. A. del Alamo and J. Jiménez, "A simple current collapse measurement technique for GaN High-Electron Mobility Transistors" *IEEE Electron Device Lett.*, vol. 29, no. 7, pp. 665-667, Jul. 2008.

- [3] J. M. Tirado, J. L. Sánchez-Rojas and J. I. Izpura, "Trapping effects in the transient response of AlGaN/GaN HEMT devices" *IEEE Trans. on Electron Devices*, vol. 54, no. 3, pp. 410-417, Mar. 2007.

- [4] G. Meneghesso, G. Verzellesi, R. Pierobon, F. Rampazzo, A. Chini, U. K. Mishra, C. Canali and E. Zanoni, "Surface-Related Drain Current Dispersion Effects in AlGaN-GaN HEMTs" *IEEE Trans. Electron Devices*, vol. 51, no. 10, pp. 1554–1564, Oct. 2004.

- [5] J. Y. Shiu, V. desmaris, N. Rosman, K. Kumakura, T. Makimoto, H. Zirath and E. Y. Chang, "DC and microwave performance of AlGaN/GaN HEMTs passivated with sputtered SiNx" Semicond. Sci. Technol., vol. 22, pp. 717-721, 2007.

- [6] M. F. Romero, A. Jiménez, J. Miguel-Sánchez, A. F. Braña, F. González-Posada, R. Cuerdo, F. Calle and E. Muñoz, "Effects of N<sub>2</sub> plasma pretreatment on the SiN passivation of AlGaN/GaN HEMT" *IEEE Electron Device Lett.*, vol. 29, no. 3, pp. 209-211, Mar. 2008.

- [7] M. Faqir, G. Verzellesi, G. Meneghesso, E. Zanoni and F. Fantini, "Investigation of High-Electron-Field degradation effects in AlGaN/GaN HEMTs" *IEEE Trans. on Electron Devices*, vol. 55, no. 7, pp. 1592-1602, Jul. 2008.

- [8] R. Vetury, N. Q. Zhang, S. Kellerand and U. K. Mishra, "The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs" *IEEE Trans. on Electron Devices*, vol. 48, pp. 560–566, Mar. 2001.

- [9] J. M. Tirado, J. L. Sanchez-Rojas and J. I. Izpura, "2D simulation of static surface states in AlGaN/GaN HEMT and GaN MESFET devices" *Semicond. Sci. Technol.*, vol. 20, pp. 864-869, 2005.

- [10] G. Koley, V. Tilak, L. F. Eastman, M. G. Spencer, "Slow transients observed in AlGaN/GaN HFETs effects of SiNx passivation and UV illumination" *IEEE Trans. on Electron Devices*, vol. 50, no. 4, pp. 886–893, Apr. 2003.

- [11] J. D. Albrecht, R. P. Wang and P. P. Ruden, "Electron transport characteristics of GaN for high temperature device modeling" *J. Appl. Phys.*, vol. 83, no. 9, pp. 4777–4781, May 1998.