# Unified Hardware/Software Co-verification Framework for Large Scale Systems

| 著者       | Nana Sutisna                         |

|----------|--------------------------------------|

| その他のタイトル | 大規模システムLSI設計のための統一的ハードウェ             |

|          | ア・ソフトウェア協調検証手法                       |

| 学位授与年度   | 平成29年度                               |

| 学位授与番号   | 17104甲情工第328号                        |

| URL      | http://hdl.handle.net/10228/00006407 |

# UNIFIED HARDWARE/SOFTWARE CO-VERIFICATION FRAMEWORK FOR LARGE SCALE SYSTEMS

NANA SUTISNA

# **Contents**

| 1 | Intr | oduction                                         | 6  |

|---|------|--------------------------------------------------|----|

|   | 1.1  | Background                                       | 6  |

|   | 1.2  | Research Objectives                              | 9  |

|   | 1.3  | Thesis Organization                              | 11 |

| 2 | Desi | gn and Verification in LSI System Design         | 14 |

|   | 2.1  | HW/SW co-design Methodology                      | 14 |

|   | 2.2  | HW/SW Co-verification                            | 17 |

|   |      | 2.2.1 Abstraction Level of Simulation            | 17 |

|   |      | 2.2.2 HW/SW Co-verification Requirements         | 19 |

|   | 2.3  | Platforms for LSI verification                   | 20 |

|   |      | 2.3.1 Software-based Design Verification         | 20 |

|   |      | 2.3.2 FPGA Prototyping for Design Verification   | 21 |

|   |      | 2.3.3 Hardware Assisted Design Verification      | 23 |

|   | 2.4  | HW/SW Communication Interface                    | 25 |

|   | 2.5  | Summary                                          | 26 |

| 3 | Unif | fied HW/SW Co-verification Methodology           | 28 |

|   | 3.1  | Scope of the framework                           | 28 |

|   | 3.2  | Data-driven Simulation                           | 31 |

|   | 3.3  | Task Partition Methodology                       | 33 |

|   | 3.4  | HW/SW Co-verification Platform                   | 34 |

|   |      | 3.4.1 General Architecture HW/SW Co-verification | 34 |

|   |      | 3.4.2   | Flexible and Configurable HW/SW Architecture                      | 36 |

|---|------|---------|-------------------------------------------------------------------|----|

|   |      | 3.4.3   | Hardware-In-The Loop Co-verification System                       | 38 |

|   |      | 3.4.4   | Methodology Comparison                                            | 39 |

|   | 3.5  | Summ    | ary                                                               | 41 |

| 4 | Fast | Co-ver  | rification and Design Exploration in Complex Circuits             | 42 |

|   | 4.1  | Overvi  | iew of MIMO Decoder in High Throughput                            |    |

|   |      | Wirele  | ess Communication System                                          | 42 |

|   | 4.2  | MIMC    | MLD Algorithm                                                     | 45 |

|   | 4.3  | Design  | Exploration in Wireless Communication System                      | 47 |

|   | 4.4  | HW/S    | W Architecture for MIMO Decoder Implementation                    | 51 |

|   |      | 4.4.1   | MIMO MLD Architecture                                             | 51 |

|   |      | 4.4.2   | Architecture for FPGA Implementation of MIMO MLD                  | 57 |

|   |      | 4.4.3   | Building Hardware-in-the Loop Co-verification System              | 58 |

|   | 4.5  | Evalua  | ation of Performance Metrics                                      | 59 |

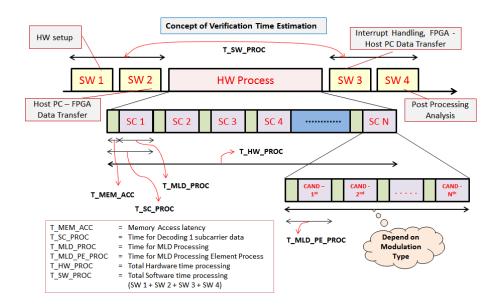

|   |      | 4.5.1   | Estimation of Timing Processing                                   | 59 |

|   |      | 4.5.2   | Verification Efficiency                                           | 61 |

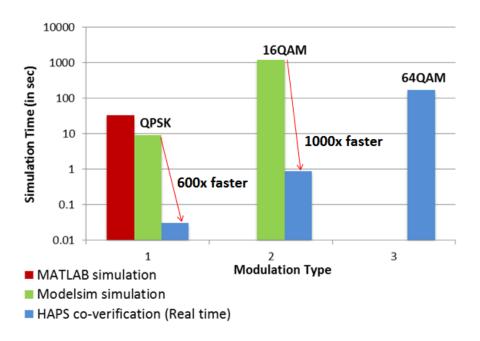

|   |      | 4.5.3   | Verification Runtime Speed-up                                     | 64 |

|   | 4.6  | Experi  | mental Evaluations                                                | 66 |

|   |      | 4.6.1   | FPGA Implementation Results                                       | 66 |

|   |      | 4.6.2   | Example Evaluations                                               | 67 |

|   | 4.7  | Summ    | ary                                                               | 72 |

| 5 | Unif | ied Sys | tem Level Simulator for Very High Throughput Wireless Systems     | 74 |

|   | 5.1  | Systen  | n Level Simulator in Wireless Communication System                | 74 |

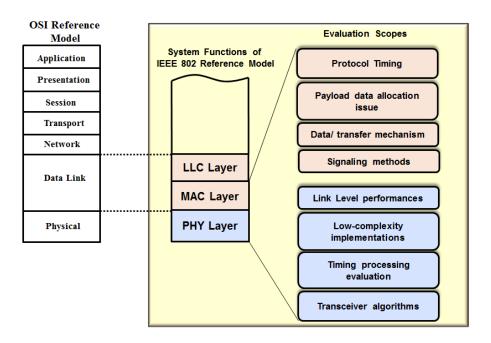

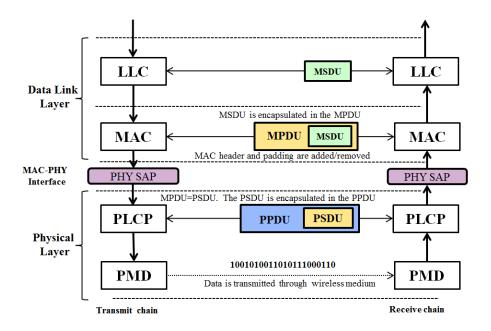

|   |      | 5.1.1   | Cross-layer communication protocol                                | 76 |

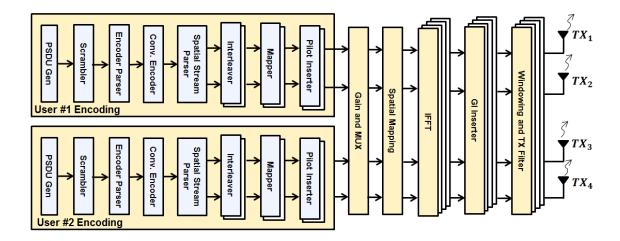

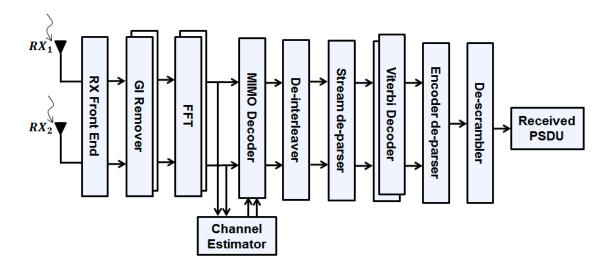

|   | 5.2  | РНҮ Т   | Fransceiver of Very High Throughput Wireless Communication System | 79 |

|   |      | 5.2.1   | Multi User Wireless System                                        | 79 |

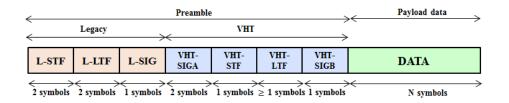

|   |      | 5.2.2   | Transceiver Structure                                             | 80 |

|   |      | 5.2.3   | System Level Issue                                                | 82 |

|   | 5.3  | FPGA    | Architecture and Implementation Results                           | 84 |

|   | 5 1  |         | d HW/SW Simulator                                                 | 86 |

| Bi | bliogr | aphy    |                                   | 99 |

|----|--------|---------|-----------------------------------|----|

| 6  | Con    | clusion | and Future Work                   | 94 |

|    | 5.6    | Summ    | ary                               | 92 |

|    |        | 5.5.3   | Achievable Throughput Performance | 90 |

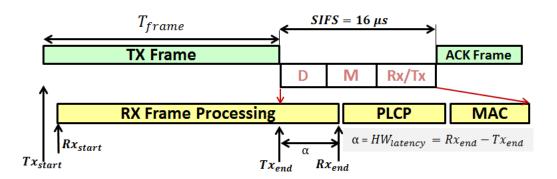

|    |        | 5.5.2   | Latency Performance               | 89 |

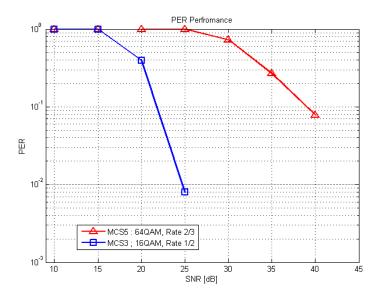

|    |        | 5.5.1   | Error Rate Performance            | 88 |

|    | 5.5    | Systen  | n Level Performance Evaluation    | 88 |

# **List of Tables**

| 2.1 | Comparison Co-verification Methods              | 27 |

|-----|-------------------------------------------------|----|

| 3.1 | Comparison of Co-verification Methodology       | 41 |

| 4.1 | System Parameter                                | 47 |

| 4.2 | Estimation of Verification Time                 | 61 |

| 4.3 | FPGA Implementation Results of MIMO MLD Decoder | 66 |

| 4.4 | Hardware resource usage for different bitwidth  | 71 |

| 5.1 | System Parameter                                | 80 |

| 5.2 | CAPIM Address Assignment                        | 85 |

| 5.3 | FPGA Logic Resource                             | 86 |

| 5.4 | Simulation Condition                            | 88 |

# **List of Figures**

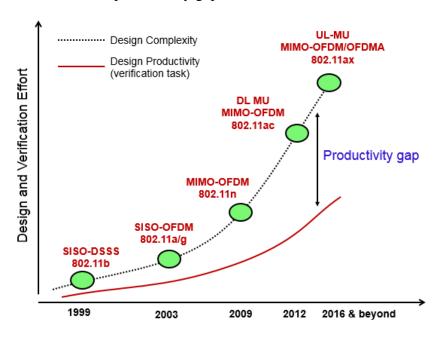

| 1.1 | Design and Verification Productivity in Wireless System development    | 7  |

|-----|------------------------------------------------------------------------|----|

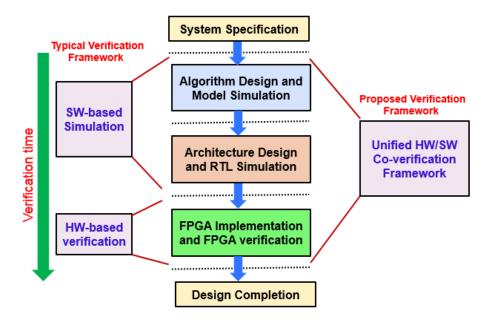

| 1.2 | Design Verification Flow                                               | 8  |

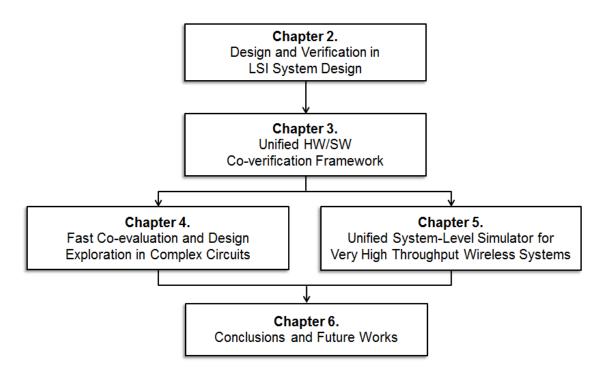

| 1.3 | Thesis Organization                                                    | 11 |

| 2.1 | Conventional LSI design Flow                                           | 15 |

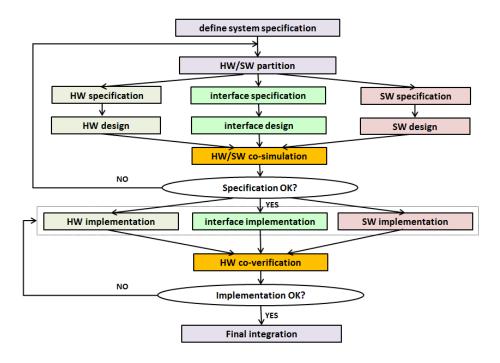

| 2.2 | HW/SW Co-design Flow                                                   | 16 |

| 2.3 | Abstraction of Simulation                                              | 18 |

| 2.4 | Full-software co-verification Architecture                             | 21 |

| 2.5 | Co-verification Architecture in FPGA Prototyping-based                 | 22 |

| 2.6 | HW/SW Co-verification System                                           | 24 |

| 2.7 | HW/SW Communication Interface                                          | 26 |

| 3.1 | VLSI Design and Verification Flow                                      | 29 |

| 3.2 | HW-SW interaction in verification process: Time-driven simulation (up- |    |

|     | per), Data-driven simulation (lower)                                   | 32 |

| 3.3 | Example of verification framework                                      | 33 |

| 3.4 | General HW/SW Architecture                                             | 34 |

| 3.5 | Unified HW/SW design layer                                             | 36 |

| 3.6 | Hardware Interface Structure                                           | 37 |

| 3.7 | HAPS Hardware Platform                                                 | 39 |

| 3.8 | General HW/SW Architecture                                             | 40 |

| 4.1 | NxN MIMO Communication System Model                                    | 43 |

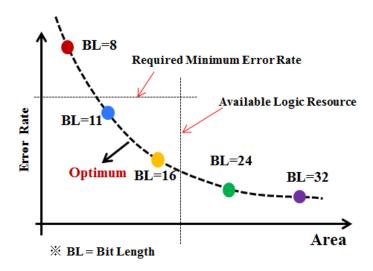

| 4 2 | Multi-metrics Design Exploration                                       | 48 |

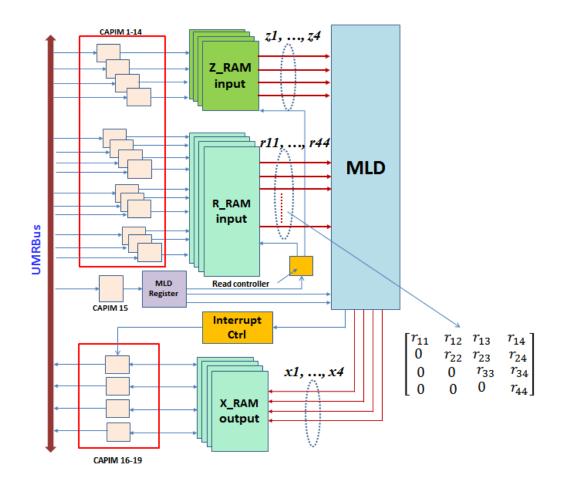

| 4.3  | MLD MIMO Decoder architecture                                         | 5  |

|------|-----------------------------------------------------------------------|----|

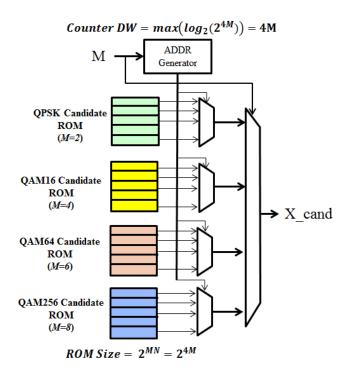

| 4.4  | Conventional architecture of ROM candidate generator                  | 52 |

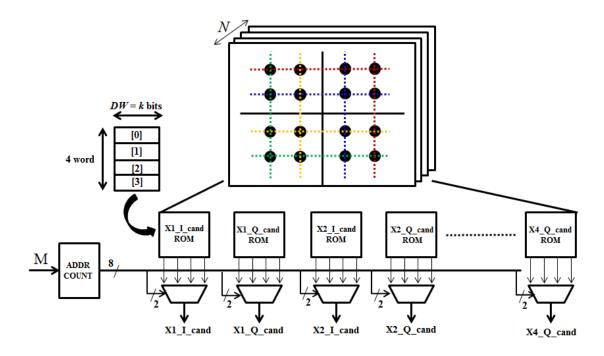

| 4.5  | architecture of 16-QAM ROM candidate generator                        | 53 |

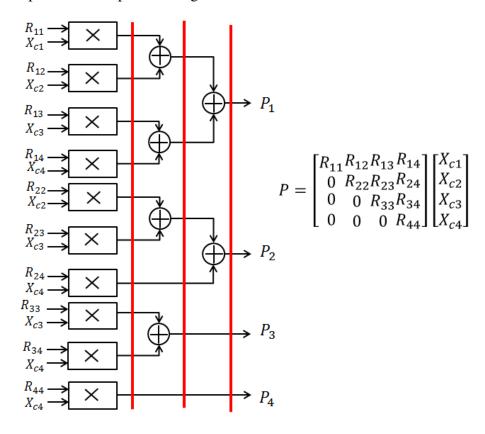

| 4.6  | architecture of Matrix Multiplier Block                               | 54 |

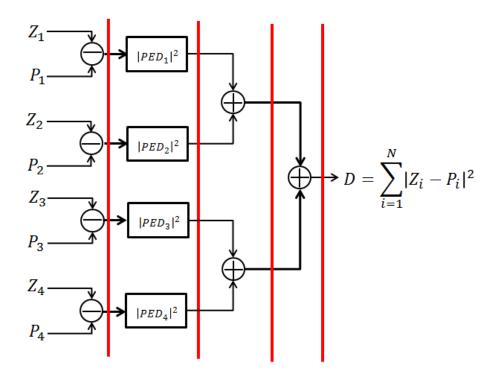

| 4.7  | architecture of Distance Calculator Block                             | 55 |

| 4.8  | Timing Diagram MLD calculation                                        | 56 |

| 4.9  | FPGA Architecture for MLD MIMO Decoder Implementation                 | 5  |

| 4.10 | Task Partitioning and Mapping for Implementation of Co-evaluation MLD |    |

|      | MIMO Decoder                                                          | 59 |

| 4.11 | Hardware-in-the loop for MLD MIMO Decoder co-verification system      | 60 |

| 4.12 | Illustration for Estimating Verification Run-time                     | 6  |

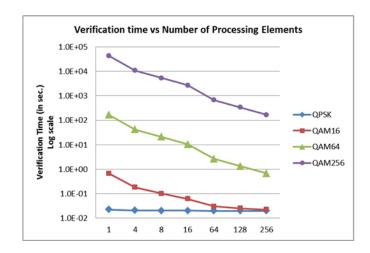

| 4.13 | Verification time for various PE numbers                              | 62 |

| 4.14 | Verification efficiency for various PE numbers                        | 64 |

| 4.15 | Verification Time Comparison                                          | 65 |

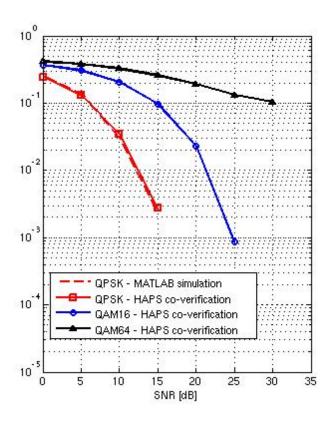

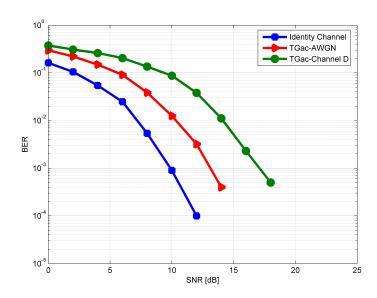

| 4.16 | BER performance on various modulation types                           | 68 |

| 4.17 | BER performance on various channel types (QPSK Mode)                  | 69 |

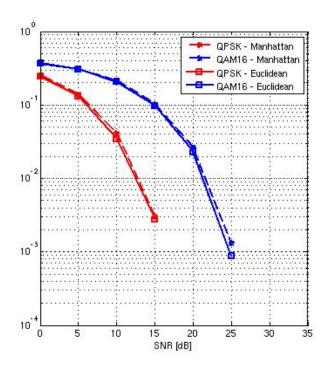

| 4.18 | BER performance for different types of distance calculation           | 70 |

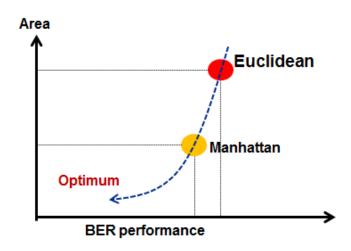

| 4.19 | DSE chart for algorithm exploration                                   | 7. |

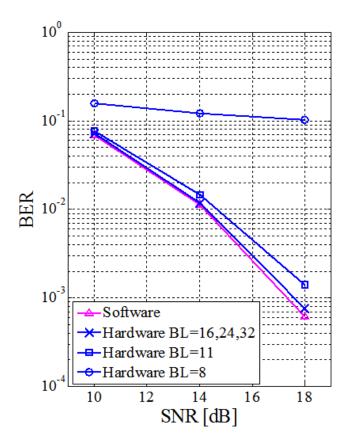

| 4.20 | BER for various datapath bit length                                   | 72 |

| 4.21 | DSE chart for MLD MIMO decoder implementation                         | 73 |

| 5.1  | System Level Framework of Simulation for WLAN system                  | 7  |

| 5.2  | MAC-PHY data flow                                                     | 78 |

| 5.3  | VHT Frame structure                                                   | 79 |

| 5.4  | Multi User MIMO Wireless System                                       | 79 |

| 5.5  | Transmitter Block Diagram                                             | 82 |

| 5.6  | Receiver Block Diagram                                                | 83 |

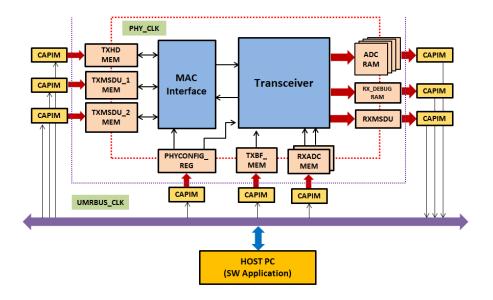

| 5.7  | Minimal WLAN SoC structure in Unified System Level Simulator          | 84 |

| 5.8  | FPGA Architecture Implementation                                      | 86 |

| 5.9  | MIMO Multi-User Co-verification System                                | 87 |

| 5 10 | Error Pota Parformanca of transcaiver                                 | 20 |

| 5.11 | Transceiver processing latency illustration       | 90 |

|------|---------------------------------------------------|----|

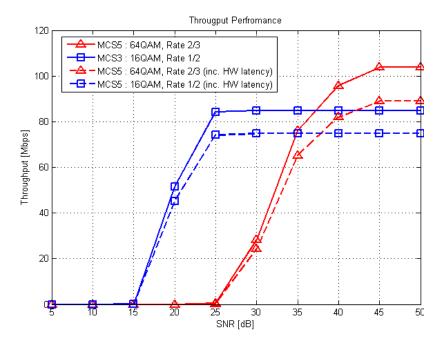

| 5.12 | Achievable Throughput for Different MCS           | 91 |

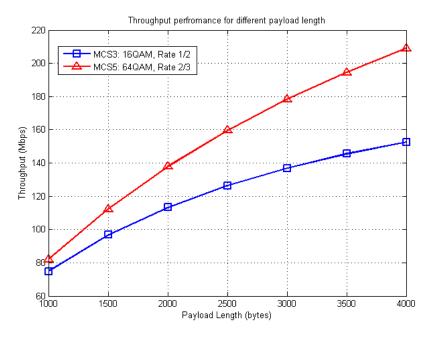

| 5.13 | Achievable throughput for various payload lengths | 92 |

#### **List of Abbreviations**

ADC Analog-to-Digital Converter

API Application Program Interface

ASIC Application Specific Integrated Circuits

AWGN Additive White Gaussian Noise

BER Bit Error Rate

BPSK Binary Phase Shift Keying

CAD Computer Aided Design

CAPIM Client Application Interface Module

CFO Carrier Frequency Offset

DAC Digital-to-Analog Converter

DL Downlink

DUT Design Under Test

DVB Digital Video Broadcasting

DVB-T Digital Video Broadcasting - Terrestrial

EVM Error Vector Magnitude

FEC Forward Error Correction

FPGA Field Programmable Gate Array

FFT Fast Fourier Transform

Gbps Giga byte per second

HAPS High-performance ASIC Prototyping System

HDL Hardware Description Language

HIL Hardware In the Loop

HLS High Level Synthesis

HW Hardware

IFFT Inverse Fast Fourier Transform

LLC Logical Link Control

LSI Large Scale Integrated System

LTE Long Term Evolution

LUT Look Up Table

MAC Media Access Control

Mbps Mega byte per second

MHz Mega Hertz

MIMO Multiple Inputs and Multiple Outputs

MLD Maximum Likelihood Detection MMSE Minimum Mean Square Error

MPDU MAC Protocol Data Unit

MSDU MAC Sevice Data Unit

MU Multi-User

OFDM Orthogonal Frequency Division Multiplexing

OSI Model Open Systems Interconnection Model

PA Power Amplifier

PC Personal Comput

PC Personal Computer

PHY Physical Layer

PE Processing Element

PED Partial Euclidean Distance

PER Packet Error Rate

PLCP Physical Layer Convergence Protocol

PPDU PLCP Protocol Data Unit

QAM Quadrature Amplitude Modulation

QPSK Quadrature Phase Shift Keying

RAM Random Access Memory

ROM Read Only Memory RF Radio Frequency

RTL Register Transfer Level

SAP Service Access Point

SIFS Short Interframe Space

SoC System on Chip

SW Software

TLM Transaction Level Modeling

UMRBus Universal Multi Resource Bus

VHT Very High Throughput

VLSI Very Large Scale Integrated Circuits

WiMAX Worldwide Interoperability for Microwave Access

WLAN Wireless Local Area Network

### **Summary**

Currently, the complexity of embedded LSI system is growing faster than the productivity of system design. This trend results in a design productivity gap, particularly in tight development time. Since the verification task takes bigger part of development task, it becomes a major challenge in LSI system design. In order to guarantee system reliability and quality of results (QoR), verifying large coverage of system functionality requires huge amount of relevant test cases and various scenario of evaluations. To overcome these problems, verification methodology is evolving toward supporting higher level of design abstraction by employing HW-SW co-verification.

In this study, we present a novel approach for verification LSI circuit which is called as unified HW/SW co-verification framework. The study aims to improve design efficiency while maintains implementation consistency in the point of view of system-level performance. The proposed data-driven simulation and flexible interface of HW and SW design become the backbone of verification framework. In order to avoid time consuming, prone error, and iterative design spin-off in a large team, the proposed framework has to support multiple design abstractions. Hence, it can close the loop of design, exploration, optimization, and testing. Furthermore, the proposed methodology is also able to co-operate with system-level simulation in high-level abstraction, which is easy to extend for various applications and enables fast-turn around design modification. These contributions are discussed in chapter 3.

In order to show the effectiveness and the use-cases of the proposed verification framework, the evaluation and metrics assessments of Very High Throughput wireless LAN system design are carried out. Two application examples are provided. The first case in chapter 4 is intended for fast verification and design exploration of large circuit. The Maximum Likelihood Detection (MLD) MIMO decoder is considered as Design Under Test (DUT). The second case, as presented in chapter 5, is the evaluation for system-level simulation. The full transceiver system based on IEEE 802.11ac standard is employed as DUT. Experimental results show that the proposed verification approach gives significant improvements of verification time (e.g. up to 10,000 times) over the conventional scheme. The proposed

framework is also able to support various schemes of system level evaluations and cross-layer evaluation of wireless system.

# **Chapter 1**

# Introduction

# 1.1 Background

Recently, with the tight demand of time-to-market for product deployment, fast verification time has become a main hurdle to guarantee a reliable product. The fast verification time is more demanding particularly in development of a large scale system. The conventional simulation techniques, such as RTL simulation is unacceptable for complex SoC simulation and early embedded software development[1]. In particular, such system also employs various system parameters and supports multiple operational modes. As confirmed by a study conducted by Wilson Research Group and Mentor Graphics, the verification process takes significant amount of overall development time and become a bottleneck for design completion[2]. Furthermore, the gap between design productivity and circuit complexity will constantly happen in the future. It is occurred since the effort on design and verification cannot catch up the increasing of system complexity[3]. Verification is also called as evaluation when the context of assessments are more comprehensive. Some texts refer to evaluation term when the tasks not only cover validation of the correctness, but also include examination the feasibility and the interaction with other metrics or layers of information processing. However, the terms of verification and evaluation will be used interchangeably throughout the thesis.

A suitable example to represent this phenomena is system development in the field of

wireless communication system. For the last two decades, wireless communication technology has evolved in fast and continuous progression. Wireless system standard always changes to meet user experience demands, such as high-throughput, high-reliability, and various uses-cases. Unfortunately, every introduction of new standard always adopts complex and advanced signal processing, as well as has to support various system features. Consequently, the system complexity will increase significantly. For example, in the latest wireless LAN standard IEEE802.11ac[4], Downlink Multi User MIMO (DL MU-MIMO) system and higher-order modulation scheme (up to 256-QAM) are adopted. This standard is well known as very high throughput wireless communication system.

Figure 1.1 shows an illustration of design and verification productivity in wireless system development. The design complexity follows the Moore's Law; the circuit complexity doubled in 2 years, while the design productivity approximately doubled every 39 months. This chart confirms that the productivity gap tends to increase over the time.

Figure 1.1: Design and Verification Productivity in Wireless System development

Verifying the system functionality in all possible conditions need huge relevant test cases in order to achieve a confidence level of acceptance test criteria. Furthermore, in development process, we also must validate each design layer, as depicted in Fig. 1.2. The

verification task in each layer involves:

#### 1. Algorithm evaluation

This task evaluates the correctness of algorithms transformation (e.g. from floating point to fixed-point) and also examines the impact of bit-width optimization in datapath design. Therefore, the employed algorithms do not degrade the overall system performance, exceeding the tolerable margin.

#### 2. Register Transfer Level (RTL) simulation

This task verifies the correctness of functionality of the designed hardware architecture according to the developed algorithm in system-level modeling.

#### 3. Hardware verification

This task performs the evaluation of the final implementation, whether satisfy the system requirements or not.

From those reasons, the verification task become a relevant issue in the development of a complex circuits.

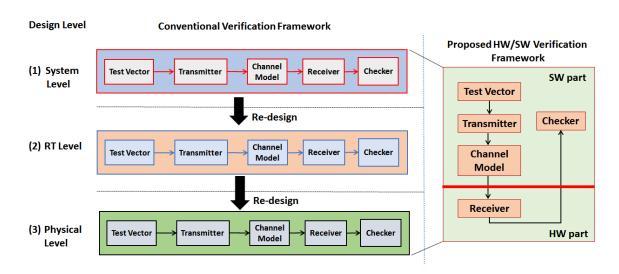

Figure 1.2: Design Verification Flow

The verification task in conventional method is typically carried out in each layer independently (as illustrated by dot line). The algorithm evaluation in system-level simulation and RTL simulation are carried out in software-based platform, while the hardware verification is performed later by using hardware-based platform, such as FPGA prototyping. For large-scale circuits, these conventional verification approaches (full-software verification and full-prototyping) have main drawbacks, which are: (1) excessive run-time verification and (2) low flexibility for covering large numbers of test scenarios and various use-cases of evaluations.

Furthermore, to be used as a comprehensive verification platform for wireless communication system, the existing verification approaches do not quantify clearly all required metrics, such as the efficiency of verification (verification time improvement), the flexibility to be employed with various function blocks, and the integration with system level simulation. As a result, those verification platforms cannot be used as integral part of system development process, particularly in the early stage of development.

To address the limitations of the existing verification methods, this thesis proposes a novel unified framework of HW/SW co-verification. This includes verification methodology, quantitative metrics of the effectiveness of evaluations, application examples, and performance characterizations. For the sake of clarity, the term of HW verification refers to set of system components that are executed in FPGA platform, while the SW verification refers to the code program that runs in host PC. This SW code verifies the rest of system components and maintains data flows with HW platform. Finally, it co-operates with HW design target in HW platform to build unified HW/SW co-verification framework.

### 1.2 Research Objectives

The objectives of this thesis is to present new methodology of verification framework for large scale circuits, specifically for wireless communication system. The study does not intent to promote particular HLS tools or present the advancement of specific FPGA platform. Instead, the study proposes a procedural and reproducible framework of verification for large scale circuits. Hence, the proposed framework is platform-independent and application-independent. Moreover, the framework should be easily employed for different

use cases in various FPGA platforms.

The proposed methodology includes:

#### 1. Unified co-evaluation framework

This allows for evaluation of various design layers with flexible partition of hardware design and software design. Therefore, the verification process can cover all verification stages, from block component up to complete system-level simulation, including algorithm verification, RTL verification, and real-time HW/SW co-verification. Thus, the proposed methodology closes the loop of design, exploration, optimization, and testing. This approach can avoid time consuming, prone error, and multiple iterations of design spin-off in a big research and development team.

#### 2. Data-driven simulation method

This method performs simulation based on the availability of data in HW/SW interface and further eliminates intensive HW/SW interaction. Hence, the proposed simulation method can improve the run-time

#### 3. Generic, flexible and scalable architecture in both HW and SW

These enable design extension and could be applied to different systems with only minor modifications.

#### 4. Tight integration with system level simulation

This feature allows for unified system level evaluation within high-level language (e.g. MATLAB, C/C++) and physical level verification.

In order to show the applicability of the proposed method, the unified HW/SW coverification methodology is applied to our hardware platform with the case study of IEEE 802.11ac system. The co-verification of MLD MIMO Decoder of high throughput system is selected in order to evaluate the proposed method in verifying complex circuit, particularly for reducing computation time. Moreover, the whole 802.11ac transceiver is employed to show the capability of proposed method for system-level evaluation. Experimental evaluations of several performance metrics are carried out to confirm the effectiveness of our proposed co-evaluation framework.

Figure 1.3: Thesis Organization

# 1.3 Thesis Organization

The structure of this thesis is shown by Fig. 1.3. The first chapter describes the motivations and the objectives of research task. The remaining chapters are organized as follows.

#### Chapter 2. Design and Verification in LSI System Design

This chapter presents an overview of existing design and verification methodology in LSI system design. In this chapter, we elaborate and investigate several important features of the existing methods. These include abstraction of simulation, types of verification framework and communication interface. Furthermore, we point out the necessity of research and development task to improve the efficiency of verification methodology in large scale circuits, particularly for Wireless Communication Communication Systems.

#### Chapter 3. Unified HW/SW Co-verification Framework

This chapter focuses on the description of the proposed co-verification methodology. This

includes task partition methodology, general architecture of HW/SW framework, and the development of hardware-in-the loop system. The first-two features, which are task partition methodology and the generic HW/SW architecture, are proposed in order to overcome the flexibility issue of co-verification framework. The task partition methodology in section 3.3 is proposed in order to accommodate various levels of verification task. The task partition is carried out by allocating some blocks to be implemented in HW and the remaining blocks are implemented in SW. Furthermore, all entire blocks could be verified concurrently in unified framework. Hence, we can select interested design more flexibly, while at the same time maintain the verification in the point of view of system-level simulation. The flexible and scalable architecture of HW/SW framework is explained in section 3.4.1.

This proposed framework is provided in order to facilitate the framework usage is applicable and extensible for various designs and applications. Additionally, in order to speed-up the simulation time as well as to cover various system parameters, the verification is carried out using hardware-in-the loop scheme that employs data-driven simulation, as described in section 3.4.3. This proposed scheme is expected to address the limitation of verification speed and also the verification coverage.

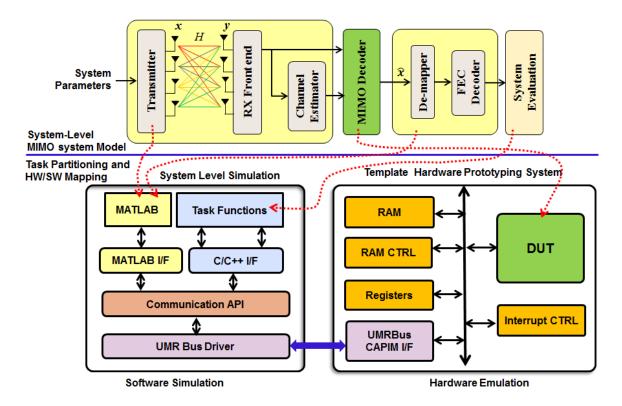

#### Chapter 4. Fast co-evaluation and Design Exploration in Complex Circuits

In order to show the applicability of the proposed co-verification method for evaluating complex circuit, chapter 4 presents application example of MLD MIMO Decoder. This block is selected as DUT since it is considered as the highest complexity circuit in transceiver system. The detail implementation of hardware and software for unified co-evaluation and the proposed data-driven co-simulation are described. In this chapter, the performance metric is also introduced in order to quantify the effectiveness of proposed design methodology. Finally, several examples of experimental evaluations of MLD MIMO decoder are presented, include the verification-time speed-up, the verification efficiency, and the evaluation of multi-dimensional design exploration.

# Chapter 5. Unified System Level Simulator for Very High Throughput MIMO Wireless Communication System

This chapter shows the extension of the proposed co-evaluation framework for system-level

evaluation of wireless system. These include evaluation of transceiver algorithms, providing reproducibility data, supplying reference data for benchmark, and assessing cross-layer performance (PHY and MAC layer). The recent technology of wireless LAN system which is IEEE 802.11ac standard is selected as a case study. In this chapter, we show that the proposed methodology can perform flexible verification task within HW/SW platform and also maintain the verification in the point of view of system-level simulation. The issues of the flexibility such as design partition, tight-integrated with system-level simulation, and large-coverage of test scenarios have been addressed. Latter, the evaluation results are provided in order to show the capability of the proposed unified co-evaluation framework.

#### **Chapter 6. Conclusion and Future Work**

This chapter shows the summary of our whole works and the achievable results. We also discuss about the directions and recommendations on possible research tasks, to further improve the development of LSI system.

# Chapter 2

# Design and Verification in LSI System Design

This chapter aims to provide the reader a fundamental understanding on LSI design methodology and its verification system. Some concepts in HW/SW co-design and co-verification are explained. Furthermore, the key features and the major drawbacks of each method are evaluated to give insight and to provide a basis for conducting the research work.

# 2.1 HW/SW co-design Methodology

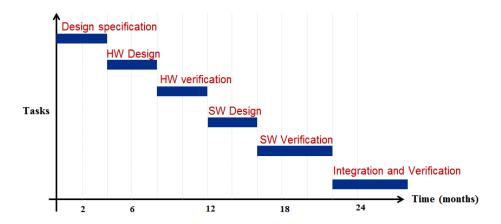

In recent years, we face the steady growth of advanced IC technology and complexity in system integration. The increased number of components in a system will imply higher degree of integration and result more complex designs. Traditionally, designers separate the hardware (HW) and software (SW) of an embedded system in early stage. The two groups of designers will develop their respective components independently. Moreover, the design process is performed sequentially. For example, the software design will be carried out after the hardware components are completely done and the verification task follows the final design task. Figure 2.1 shows illustration of a classical LSI system, involving hardware and software design[5].

From figure 2.1, the system specifications are first defined. Based on the initial specification, system level simulation and hardware design are performed. In many cases, the

Figure 2.1: Conventional LSI design Flow

software team cannot start to develop and test their software until the hardware design is available. This has great risk of delaying the final product delivery when some design errors are detected very late. Additionally, we do not have any chance to explore potential option with respect to several implementation objectives, such as cost, performance and extensibility. Hence, the success of development is typically determined by the experience of designer team.

In summary, there are several main drawbacks of the conventional design flow [?], which are:

- *long development path*, resulting long and unpredictable time-to-market;

- risk of potential errors in each part design cannot be covered;

- risk of over-design (excessive design) or under-design (insufficient design) of system due to lack of early evaluation of design options.

To address the conventional LSI design methodology, HW/SW co-design has been considered as an established method to design complex IC circuits[5]. As supplementary to this design methodology, the verification methodology is also shifted into co-operative perspective. Co-design is a design methodology that allows the concurrent development of HW and SW in order to achieve system specifications. This method able to improve the predictability of embedded system design, by providing methods that tell to designers whether a system satisfies its requirements or not. Co-design methodology includes several tasks,

such as definition of system specification, design partitioning, modeling, validation, and implementation. An important note, co-simulation and co-verification have always been considered as an important topic in the co-design area, which is the main discussion in this thesis.

Figure 2.2: HW/SW Co-design Flow

The typical HW/SW co-design flow for LSI system could be figured out in Fig. 2.2. The development starts with defining initial system specification. Some mandatory parameters are selected in this stage, while other decisions such as architecture, algorithm, etc., could be refined in later stage, according to performance-cost trade-off.

The HW/SW partition stage is carried out to allocate where the set of system processing is executed. Several tasks are performed in hardware design, while the others functions are realized as SW in host processor or emulated in host PC. In this stage, the interface of HW and SW is also specified. The task mapping can be performed by considering cost metrics on each module or function. For HW component, the typical cost metrics are execution time, resource area, power consumption, and testability. On the other hand, SW cost metrics may includes execution time and required memory size. In practical, functions

with regular computation and parallel operation are realized in HW. Other functions that have irregularity and perform complex calculation are mapped into SW.

After partitioning is done, a simulation environment is developed in certain abstraction layer (design layer) to model its behavior, including computational process and data signaling. Some iterations of simulation are performed to estimate system performance. In typical DSP simulation, co-simulation is performed in high-level language. When system-level model satisfy the requirements, the hardware component could be implemented into hardware design in RTL level. At the same time the SW process is also implemented by adopting the data flow as described in system-level. This SW implementation could be re-used for final implementation.

In final stage, the RTL design is synthesized and verified on HW platform, which is FPGA. Hardware verification can be also performed with co-operation with SW design. If any error that affects system performance is found, the design has to move back to the previous stage. The designers need to modify the initial design or even to change specification. This design turn-around results a high cost as well as long cycle development.

## 2.2 HW/SW Co-verification

Verification task has become more challenging due to rapid increasing of system complexity and the requirement to maintain the gap between the productivity and circuit complexity. In the following subsections, we elaborate and investigate several characteristics of verification approaches, for example: achievable simulation time, the cost for system setup, simulation accuracy, debugging flexibility, and the coverage for large test scenarios.

#### 2.2.1 Abstraction Level of Simulation

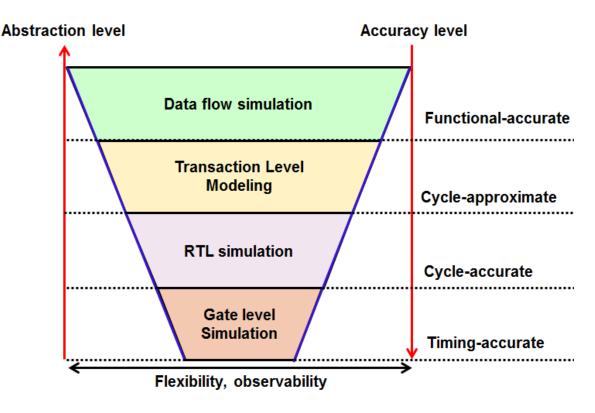

From the perspective of abstraction level, offered accuracy and degree of observability, as shown in Fig. 2.3, simulations can be classified into the following categories:

Data-flow simulation, This simulation represents functional behavior of signals or data stream without notion of time. Each component/block is connected by signal and is executed when the inputs are available. Simulation is performed in high-level

Figure 2.3: Abstraction of Simulation

abstraction during early stage of development. The Main objective of this simulation is to verify the correctness algorithm or data-flow of system. Since this simulation is performed without taking into account the timing behavior, the simulation results cannot predict timing accuracy performance of system.

• Transaction-level simulation. In this simulation, the details of communication (e.g. HW/SW interface) among computation components are separated from the details of the implementation of computation components. Communication is modeled as channel (interconnection) and transaction request takes place by calling interface functions of these channel models. Unnecessary details of communication and computation are hidden. In this simulation, SW function calls are used to model the communication between HW and SW components. For example, transaction level model (TLM) performs burst transfer task by using only single function call, with an object representing burst request and another object representing burst response.

This simulation is consider as cycle approximate simulation.

- RTL simulation. This simulation only calculates the state of the signals at clock edges and it is usually implemented for simulation of RTL hardware design. This simulation can predict the actual processing in cycle-count. However, the simulation does not reflect the design can work at actual speed. Furthermore, in this simulation any signals can be captured and debugged. Hence, it can be used for complex design and verification. However, this simulation suffers from excessive run-time simulation.

- Gate-level simulation. This simulation is the most accurate simulation since every active signals is evaluated during the clock cycle as it propagates. Each signal is simulated for its values and its time occurrence. To perform gate-level simulation, the synthesized version of hardware designs are used. Therefore, this simulation is very useful for timing analysis of HW circuit. However, the achievable simulation time is very slow, particularly when the circuit is quite complex. As a result, this simulation is intended only for HW verification in component (unit) level, not for system-level evaluation.

### 2.2.2 HW/SW Co-verification Requirements

In order to achieve efficient and effective simulation task, the following requirements need to be considered as trade-off metrics by HW/SW co-verification framework:

- speed is one of the most critical requirements to enable fast design exploration and also cover large test scenarios. Main issues that affect maximum achievable simulation speed are the interaction between HW /SW component and and also data synchronization of HW/SW. Hence the design of HW/SW interface will be critical.

- 2. simulation accuracy is an important metric to decide the best design alternative that satisfies requirements. To avoid many iterations of feedback, particularly in very late stage, accurate relevant results should be obtained to assess system performance in early stage development. These include cycle timing processing, fixed-point error rate, and others metrics. Cycle-accurate simulation or stand-alone hardware platform

is typically used to evaluate final performance. However, this approach needs high effort and practically will be available in later design stage. Hence, in order to allow designers make modification in both the design and the specification in early stage, the HW/SW co-verification should provide higher accuracy of simulation results

3. cover multiple abstraction levels. In designing complex embedded system, different team of designers often do not have enough expertise knowledge in other's domain. Moreover, the simulation and verification usually are carried out using different framework. To address this practical issue, it is desirable to provide HW/SW co-verification platform that can be used many different group. Hence, the consistency of results can be guaranteed until final implementation. Furthermore, HW/SW co-verification platform can eliminate effort when any changes made in one domain.

#### 2.3 Platforms for LSI verification

According to the implementation platform, co-verification methods can be categorized into three main groups, which are the software-based approach (Full-software), the hardware-based approach (FPGA prototyping), and the combination of hardware-software (HW-assisted/HW-accelerated).

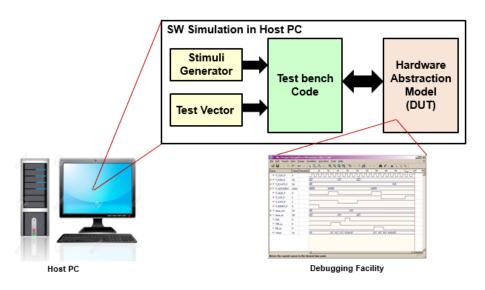

### 2.3.1 Software-based Design Verification

The co-verification approach in full-software platform is mainly characterized with the implementation of testbench program and abstraction of circuit design in SW platform. Both two designs are running within host PC, as depicted in Fig. 2.4. This method includes the conventional one which is Register Transfer Level (RTL) simulation [7] or its extended version with addition of Bus Functional Model (BFM) [8] or Transaction Level Modeling (TLM) features. This approach is able to simulate hardware model at cycle-accurate and also offers the designers to observe any signals in any levels of design hierarchy. Additionally, it is easy to build the verification environment in this platform since it only needs the simulation models. However, the run-time verification is very slow where the simulator can only be run at a speed of about 10 - 100 Hz. For verifying such complex SoC

circuits, it could take several days to simulate within the RTL simulator. Therefore, the RTL simulation can barely be used for complex hardware verification and embedded system verification. This approach is suitable particularly for block-level simulations, instead of whole system of complex-circuit simulations.

Figure 2.4: Full-software co-verification Architecture

In order to address the limitation of RTL-based simulation, the higher-abstraction model such C/C++ or systemC are employed[6], [7]. These simulation frameworks run much faster than RTL simulation. Additionally, in order to rapidly identify the errors in system functionality, various verification techniques such as assertion-based or formal method could be included in the software testbench. Moreover, these approaches also can be easily integrated with system-level simulator. Thus, evaluation of overall system can be performed more comprehensively. However, we cannot evaluate the timing processing performance since the simulation is not cycle-accurate. As a result, the accuracy of system is far from real-world condition.

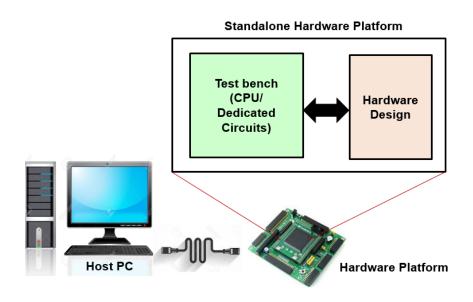

#### 2.3.2 FPGA Prototyping for Design Verification

Another approach is HW-based platform using a hardware emulator in re-configurable devices, such as FPGAs and GPU. In this method, both the testbench and DUT are realized in

hardware platform, as shown in 2.5. The testbench sequence could be implemented in dedicated circuit or implemented on executable code within on-circuit CPU, while the DUT is fully implemented in hardware resource block. The connectivity of host PC is required only for initial system configuration setup, such as writing bit configuration into hardware target.

Figure 2.5: Co-verification Architecture in FPGA Prototyping-based

Recently, The FPGA prototyping has been intensively studied and applied in LSI system development, particularly in wireless communication system. With the availability of affordable FPGA platform, the FPGA prototyping has attracted as a tool for emulating complex systems since it has main advantage on improving verification time dramatically. The state-of the-art FPGA technology can be operated in several hundreds MHz of clock frequency. This feature not only offers the possibility to perform fast verification, but also realizes real-time circuit verification. Several considerable works have shown the capability of wireless communication system, both in block component level or full-system level, such as in [9]-[13]. Furthermore, FPGA-based verification is also able to perform simulation in cycle accurate. However, the signal observability and debugging instrument are very limited and not flexible. In order to provide high degree of observability, the designer should develop and add a dedicated circuit to capture various signals with considerable

efforts, such as Signal-Tracing Technique [].

From the observations of many cases, implementation of all component of a complex circuits into full hardware can not be performed straight forward since frequently the designers experience several problems, such as lack of resource block, timing constraint problem, or other technical issues. Furthermore, implementation of full prototyping into hardware platform limiting the intervention of user for assessing the system, unless the dedicated software or firmware have been implemented inside hardware circuit within a CPU module. To address this challenge, it needs experienced resource as well as extensive labor time for system development until the employed system are ready to be used for system verification. Hence, this verification platform is only suitable for final stage of system development as an product outcome, rather than integral part of system development.

#### 2.3.3 Hardware Assisted Design Verification

With the increasing complexity of modern embedded system design, pure-software and full-hardware verification are limited used in system verification, particularly in system design with intensive HW/SW co-design process. As a consequence, the verification paradigm has shifted into HW/SW co-verification framework since the task processing is not only dominated by the hardware part, but also includes the software part. In order to leverage the capability of FPGA-platform, recently the combination of HW/SW framework is considered as an alternative solution in circuit verification, instead of using full-hardware platform, as illustrated in 2.6

Recently, HW/SW co-verifications become typical approach for system evaluation. The scopes of HW/SW co-verification mainly focus on: 1) mixed-simulation of components in the different abstraction level, 2) integration of various system-level simulator into unified environment, 3) simulation speed up by reducing the overhead communication between software platform and hardware platform.

Another relevant issue on HW/SW co-verification is related to HW/SW partition. The partition is the task of allocating system functions into set HW or SW resources. Various formulations for task partition can be carried out according to 1) **architectural assumption**: degree parallelism, the type of communication flow between each function, etc. 2)

Figure 2.6: HW/SW Co-verification System

partitioning objectives: maximizing the overall speed up or minimizing the overall cost.

The HW/SW co-verification approach complements the conventional FPGA prototyping by offering more flexibilities for verification task, although the achieved verification time is not as fast as the performance of FPGA prototyping. These flexibilities include the facility for modification test scenarios, tight integration with system-level simulation in high-level abstraction, and ability to cover large coverage tests. Hence, the HW/SW coverification can perform comprehensive system evaluation, particularly for complex circuit with various system parameters and many types of signaling between system layers.

The deployment of HW/SW framework recently is enabled by the availability of various interface platforms for connecting host PC and HW platform. Commercial EDA tool such as MATLAB provides Hardware-in-the loop option to perform co-simulation of HW design within Simulink Environment, as presented in [15] or [16]. Other platform such as TCP/IP based interface also one candidate for interfacing host PC and HW platform, as proposed in [17]. A HW/SW co-design framework with operating system support is also considered [18]

By employing HW/SW co-verification, it allows a mixed hardware and software based execution and offers several advantages:

- Avoid to develop different model (re-model) of the design which already available in early system-level modeling or RTL. This may reduce the development cost and enable hardware-assisted verification

- Hardware prototyping can be deployed in faster time because the system testbench has been created earlier, already verified and mature as it applied in previous stages.

- The trade-off between accuracy, speed and run-time can be managed more flexibly.

## 2.4 HW/SW Communication Interface

HW/SW communication interface is one of important component in HW/SW co-verification in order to allow concurrent design verification for both design domains, e.g HW and SW. The communication interface also bridges the gap between different abstraction layers and provide data adaption from one layer to other layers.

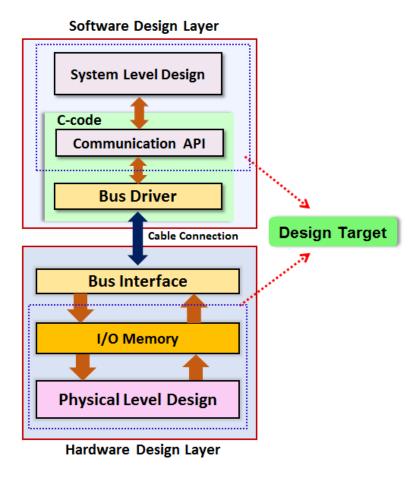

The abstraction of communication model should handle two different parts: one at SW side and the other one in HW side. In SW side the communication interface can be consisted two different layer. The upper layer is API model that serves as interface between user application and the lower layer is hardware-dependent software. The hardware-dependent software model will be different, depending on timing characteristic of hardware interconnection. In general, usually hardware vendor provide bus driver software for handling data transfer from API software to hardware platform. On the other hand, in HW side the communication interface hides the detail of bus protocol through adapter interface which is called as bus interface. This include I/O modules such as memory, FIFO, or registers.

In simple point of view, the communication interface between SW function and HW component provide a channel for data from source node to destination node. The communication channel can be modeled with different abstraction layer, depending on implementation of HW/SW co-verification platform. In data-flow simulation, this communication

interface could be directly mapped as argument for function call as an explicit connection. This communication as a port wiring in hardware side. In more detail abstraction, this HW/SW interface can be modeled as transaction based model in a dedicated function call. The function call usually represents data transfer from one node in SW to other destination node in HW or from one source node in HW to destination node in SW.

The generic architecture of HW/SW communication interface is shown in Fig. 2.7.

Figure 2.7: HW/SW Communication Interface

# 2.5 Summary

As can be observed in the previous description, the HW/SW co-verification method has many promising advantages compared to the conventional ones, which are fully-software simulation and FPGA prototyping. The properties of these methods are provided in Table 2.1.

The HW/SW co-verification methods is the optimal option for verification of complex circuits, considering the trade-off between system flexibility, verification run-time,

Table 2.1: Comparison Co-verification Methods

| Properties       | SW Simulation  |                   | HW Prototyping | HW/SW<br>Co-verification |

|------------------|----------------|-------------------|----------------|--------------------------|

| Model/Platform   | RTL            | C/C++,SystemC     | FPGA           | HIL                      |

| Run-time         | Slow           | Fast              | Real-time      | Fast                     |

| Accuracy         | Cycle accurate | Cycle approximate | Cycle accurate | High                     |

| Flexibility      | Moderate       | High              | low            | High                     |

| Observability    | Full           | Full              | Limited        | High                     |

| Cost Development | Low            | Low               | High           | Moderate                 |

and the development effort. However, the existing HW/SW co-verification has limited the integration with system level simulation and suffer to be implemented as integral part of system development. Hence, the simulation cannot cover verification task in various design levels concurrently, which are: algorithm validation, RTL simulation, and physical verification (in circuit verification). Finally, in order to address these requirements, the unified HW/SW co-verification framework is proposed to leverage the existing HW/SW co-verification methods.

### **Chapter 3**

# **Unified HW/SW Co-verification Methodology**

### 3.1 Scope of the framework

In order to realize an efficient co-verification platform, this thesis proposes an effective approach to obtain reliable and efficient development of large scale systems. An efficient HW/SW co-verification platform should not only be capable of performing a fast simulation, but also at the same time it must have:

- 1. Flexibility: support quick turn-around design modification and design extension,

- 2. *Large coverage* of verification task: cover from algorithm development to hardware implementation,

- 3. *Tight-integration* with system-level simulation: maintain reliable system-level performance.

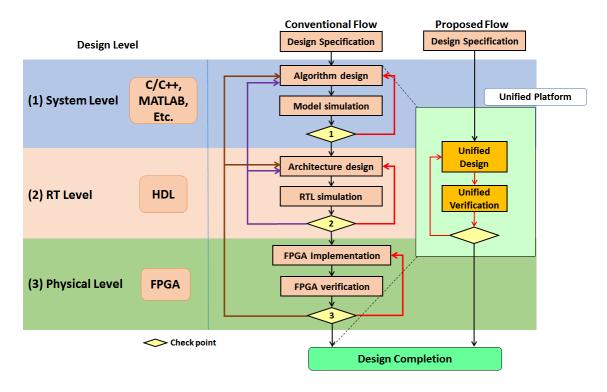

In general, VLSI design and verification flow consist of three design layers, as depicted in left side of Fig. 3.1. In the first layer, a complete system modeling is developed in algorithm/mathematical abstraction using system level language such as MATLAB, C/C++, etc. For example, in wireless communication system, it includes model abstraction of transmitter, channel model, and receiver. Since blocks in wireless communication system,

Figure 3.1: VLSI Design and Verification Flow

especially in receiver, are very sensitive to the employed algorithm and hardware optimization, before translating into hardware design, the designed algorithm should be verified in order to get realistic computational complexity and predictable performance degradation.

After algorithms have been validated, RTL design for hardware implementation can be created depending on hardware target. The process of algorithm transformation, recently, not become a difficult task since the availability of advanced High Level Synthesis CAD tools [19]. A study and evaluation of various HLS tools, including model based RTL design, are thoroughly presented in [20]. In this HLS methodology, the hardware abstraction is created using graphical form that facilitate system development conveniently. This method offers some features, including parameterized design, area and timing optimization options. These features allow the designers to carry out fast design exploration and lead to reduce development time significantly. In this RTL design stage, the verification is also performed to verify that hardware design in generated HDL code is still have same functionality as defined in system level simulation. However, verification time for bit true

model in this CAD environment is very slow. Once the RTL is obtained, hardware implementation can be carried out and once again the verification is carried out in order to ensure that final hardware implementation satisfy required performance.

In the conventional verification system, the verification process of each stage is carried out independently and is also not integrated to system level simulation. Additionally, to verify and to evaluate overall system performance, it needs to implement all blocks into hardware emulation in order to obtain fast verification results. With this approach, all hardware design of overall system should be completed before performing verification. Moreover, another potential problem will be faced when we directly implement a full system, such as lack of FPGA resource or timing problem.

As summary, there are several problems from the conventional verification methodology. The first one, conventional verification process may contain many iteration loops, either within same design layer or different design layer. This process takes longer verification time and gives slow feedback for design modification. As a result, development process requires longer time. The second one, because the verification process is independent between design layer, the verification environment in each layer cannot guarantee the consistency of performance in the point of view of system level simulation. Hence, the expected performance cannot be maintained from system level design into final system implementation.

In our proposed verification platform, the verification of complex system can be carried out efficiently from block component up to system level by employing unified HW/SW coverification platform. In the proposed scheme, we can use multiple of abstraction levels of design. In particular, one component of whole system can be simulated in physical level, while the remain blocks are simulated in other levels, MATLAB or RTL level.

To realize such system, tight integration of hardware platform with system level simulation is a key element. The proposed verification platform can be used by hardware designers to design, implement, and verify related block concurrently. Furthermore, the verification of each block can be performed in the point of view of system level simulation. Hence, the final performance requirements of full system can be maintained and predictable. Moreover, the verification time can be reduced significantly.

### 3.2 Data-driven Simulation

A key feature in proposed verification method is data-driven simulation. In this approach, data processing could be performed in vector based (burst data). Vector based processing is considered since the provided data from system level simulation (e.g MATLAB) is matrix/array-based format. To realize this feature, we provide communication interface that support block data transfer. It includes SW interface and HW interface that support block data transfer. The SW interface can perform burst mode transaction, while HW interface able to handle block data transfer by employing block RAMs or FIFOs. By utilizing this approach, the interaction of hardware software only occur in the beginning and the end of verification run-time. Therefore, the overhead of HW/SW interaction can be reduced significantly, which results significant improvement of HW/SW co-verification run-time.

Furthermore, one of of significant benefit is we do not need intensive synchronization for data transfer in the communication channel. Since the data transfer is performed based on availability of data, it can be synchronized only by simple interrupt-based mechanism. Therefore, the implementation complexity in both software and hardware can be maintained.

This approach is different with HIL verification methodology in [15]. This work employ HIL within Simulink to verify a complex circuit (e.g FFT design). While the Simulink environment can provide more convenience verification, however, the data processing is carried out in cycle-based simulation and time-driven based. This means that the data processing is performed one-by-one data involving intensive interaction HW/SW communication. Thus, this method introduces significant overhead for HW/SW communication for each cycle and affects overall verification speed-up, particularly in high complex circuits.

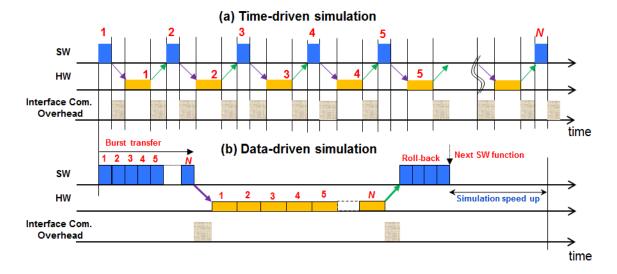

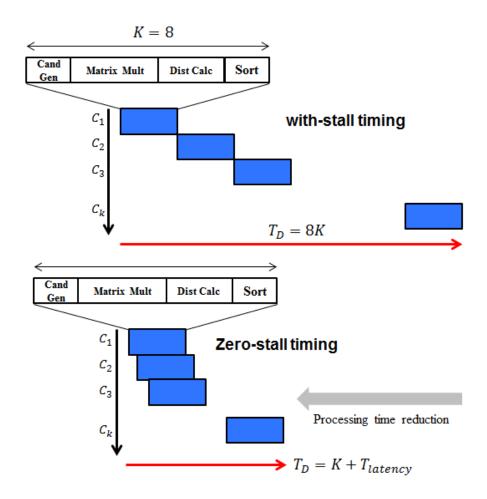

As illustrated in Fig. 3.2, we can characterize the performance of data-driven simulation and time-driven simulation as follows. First, we assume that the data-driven simulation involves the interaction between HW and SW in the beginning and the end of verification run-time. On the other hand, the time-driven simulation involves the HW/SW interaction in each cycle. HW/SW interaction task takes  $T_{comm}$ . Therefore, the total HW/SW communication overhead for data-driven and time-driven simulation are  $2T_{com}$  and  $2NT_{com}$ , respectively. The communication speed and penalty cycle of interrupt handling contribute to

Figure 3.2: HW-SW interaction in verification process: Time-driven simulation (upper), Data-driven simulation (lower)

this communication overhead. For simulating N data, the total hardware processing for the both simulations are same, which is  $T_{HW}$ . Hence, the total of verification run-time for data-driven simulation,  $T_{DD}$ , and time-driven simulation,  $T_{TD}$ , can be calculated as provided in the following equations.

$$T_{DD} = N(T_{SW} + T_{HW}) + 2T_{com} (3.1)$$

$$T_{TD} = N(T_{SW} + T_{HW} + 2T_{com}) (3.2)$$

We can see that the HW/SW communication overhead in data-driven simulation does not longer depend on the number of simulated data (e.g cycle). Therefore, for simulating very large data, the data-driven simulation will offer significant advancement over time-driven simulation. Moreover, by employing our interface, SW data transfer can be performed in high speed transfer, achieving up-to 800 Mbps. Thus, the overhead for HW/SW interaction in the proposed method will also be reduced significantly. As a results, the verification time in the proposed method is much faster than the time-driven simulation.

The data-driven simulation might have a limitation of memory buffer size used for burst data transfer. Principally, the buffer size depends on specification of test vector and the number of I/O ports of DUT. In practical, the boundary limit of buffer size is the remaining

available memory blocks in FPGA target after implementation of hardware core of DUT.

### 3.3 Task Partition Methodology

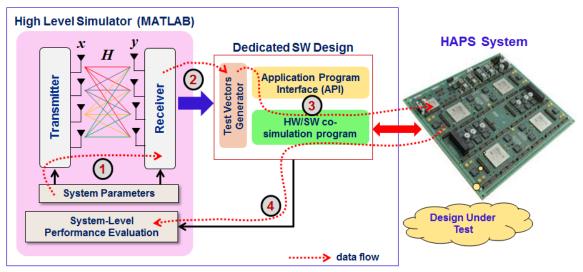

Figure 3.3: Example of verification framework

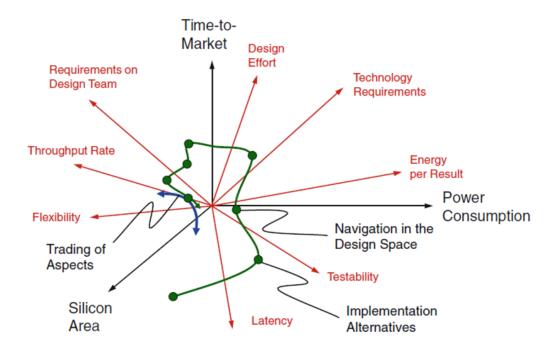

Typically, the design process of a complex signal processing system starts from system level algorithm description, such as MATLAB or C/C++. There are many possible algorithms for implementation, in order to fulfill system requirements, but they give different trade-off between area complexity, efficiency, flexibility, and design effort. Hence, design exploration is mandatory and should be performed quickly at the initial development. Once the algorithm is selected, a submodule can be transferred to hardware development and further verified in the point of view of system level simulation.

The first step to build an efficient HW/SW co-verification system is performing task partitioning of all system process. The task partitioning can be carried out under consideration of area complexity, timing processing, requirement of quick algorithm evaluation, or any design metrics that are determined by system requirements with subject to maximize the verification speed-up and to minimize design effort.

For example, as depicted in Fig. 3.3, signal processing blocks of wireless communication system consist of several consecutive processes: input data and parameter (referred

as Test Vector), Transmitter, Channel Model, and Receiver. Assumed that we perform task partitioning to the system by selecting a complex process (e.g Receiver process) to be simulated in hardware platform, and the rest of processes are simulated in software platform. Furthermore, the transmitter, channel model, and output results checking could be implemented into different software abstraction language. The transmitter and channel model process are implemented in MATLAB, while output checking is implemented using C/C++. Both software platforms, which are MATLAB part and C/C++ part, communicate each other through custom transparent layer communication (API). On the other hand, receiver process, as considered the high complexity system, is implemented in hardware emulated platform.

At the initial stage design, it is possible to implement receiver partially in hardware and allocate other receiver processes in software. When the development stage is growing, more tasks in software processing could be added up to the hardware target and also can re-utilize the verified hardware blocks, achieving a complete full hardware emulation.

### 3.4 HW/SW Co-verification Platform

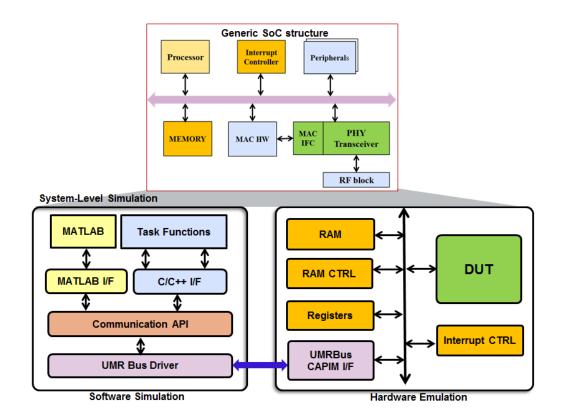

### 3.4.1 General Architecture HW/SW Co-verification

Figure 3.4: General HW/SW Architecture

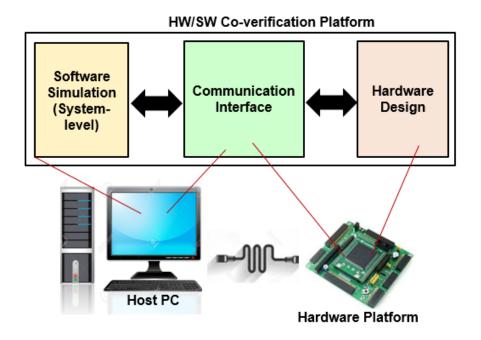

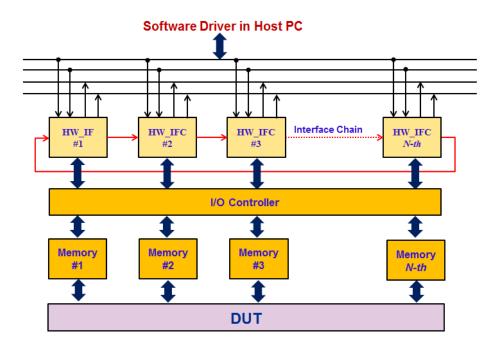

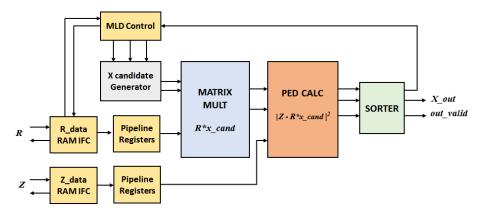

To implement a complete design of HW/SW co-verification, first we have to provide a generic architecture for HW/SW implementation, as shown in Fig. 3.4. The HW/SW design should accommodate flexibility and reconfigurability purpose. Hence, it could be reused for other design targets or applications. This generic architecture also reflects typical SoC point of view, that is constructed from master CPU (host PC), bus (communication interface), and slave as the hardware design target. The hardware design mainly consist of three building blocks, which are: (1) bus interface module for receiving data from end-point physical connection link (e.g. PCIe cable), (2) memory banks for storing input and output stream, and (3) hardware target that is being verified (Design Under Test). On the other hand, the software design consist of 3 main blocks, which are: (1) system level design that performs system level simulation, (2) communication API that handles data communication between software layer, and (3) bus driver that connects data communication of software part and hardware part.

The employed HW/SW platform uses HAPS board from Synopsys [21]. Basically, the original Synopsys HAPS (UMR bus) [22] is aimed for prototyping platform and is not intended for hardware-assisted simulation. Since it cannot be directly connected to higher abstraction of simulation, we provide the API design to extend the UMR Bus function in order to allow the data flow between MATLAB and bus driver software. The second one, the nature of UMR bus is single data transfer. Therefore, we improve the interface, both in hardware in software, to support burst transfer and also capable for parallel I/O connection.

On the other hand, the main objective of our proposed methodology is for unified verification, that covers all design abstraction layers. Our proposed methodology seems similar with Synopsys Hybrid Prototyping Platform [23]. It can also perform system level simulation by utilizing virtual prototyping. However, our hardware platform does not include virtual prototyping packages. Therefore, system level simulation could not be carried out in employed HAPS board. Furthermore, the TLM verification flow in virtual prototyping is being a commercial package which is not an open access package. Additionally, the TLM based verification concept primarily suitable for System on Chip (SoC) prototyping case, where the data communication through on-chip bus among various modules are very important.

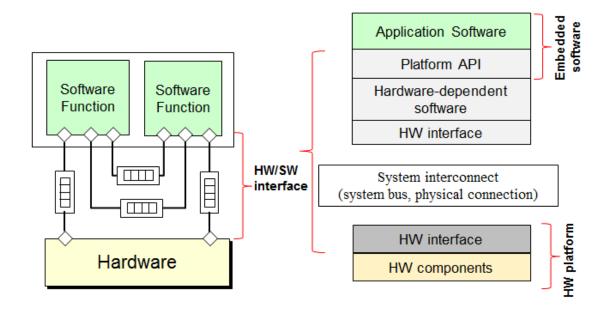

Figure 3.5: Unified HW/SW design layer

### 3.4.2 Flexible and Configurable HW/SW Architecture

In order to address the limitation of basic HAPS platform, we propose unified hardware and software design approach to realize unified HW/SW co-verification, which layer structure is depicted in Fig. 3.5. We also propose flexible and scalable interface, both in hardware and software part.

In hardware side, the flexible interface is employed to handle various transfer modes, for example stream-based mode or pass-through mode. Additionally, to support various interface type in different applications, we use configurable architecture for I/O management. The hardware interface, e.g CAPIM, receives the data from software driver through physical link and multiplexes this data based on specified address. If the address tag of received

Figure 3.6: Hardware Interface Structure

data is identical with interface address identity (address ID), then the data will be written to connected memory or register. Otherwise, the data will pass through connected interface chain. Moreover, we also exploit bandwidth transfer by employing full-matrix cross bar connection. This allows the implementation of hardware interface module in fully parallel architecture. The generalized structure of hardware interface design is depicted in Fig. 3.6.

In software side, to adapt with high level system simulator, we employ customized API software as communication interface. This interface manages the received data from high level simulator or hardware circuit. Specifically, this API has to allocate the data that will be transferred to hardware from host PC. The API also receives and collects the data that are received from hardware for further processing in system level simulation. The designed API considers the flexible length of data transfer in order to enable burst data transfer. Furthermore, the designed API collaborates with software driver to perform data transfer into specific memory (or vice versa) by pointing designated hardware interface address of memory. API requires length of burst data as argument input, while SW driver uses the interface address as additional input argument. Several API codes are constructed into main program to perform whole co-simulation testbench program. Following listing

shows the pseudo-code of generic main testbench software.

```

// Pseudo code software Testbench

umrbus_init();

/* Write vector data to UMRBUS */

for idx=1:CAPIM_NUM

write_data = read_vec_data(data_length, vecin_filename);

umrbus_write (write_data, data_length, CAPIM_address);

end

/* Waiting for Interrupt */

if (interrupt_handler()==1)

// Read data from hardware and send to Simulator

read_data = umrbus_read(data_length, CAPIM_address);

write_vec_data(read_data,data_length, vecout_filename);

end

```

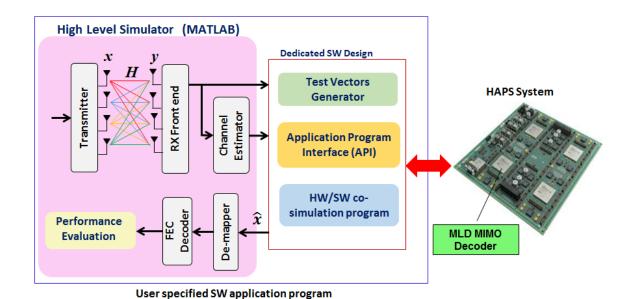

### 3.4.3 Hardware-In-The Loop Co-verification System

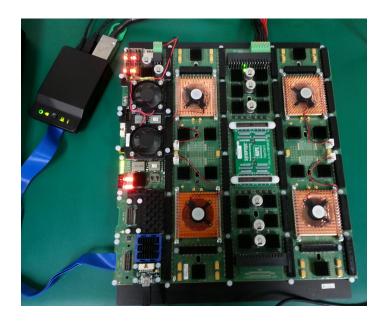

In this work, the hardware platform uses HAPS platform (High-performance ASIC Prototyping Systems) from Synopsys [21], as depicted in Fig. 3.7. The HAPS system consists of 4 FPGA chips of Xilink Virtex6 family. It can occupy upto 7.5M gates for each FPGA chip. The HAPS system is connected to a host computer (PC) through PCI-e cable link.

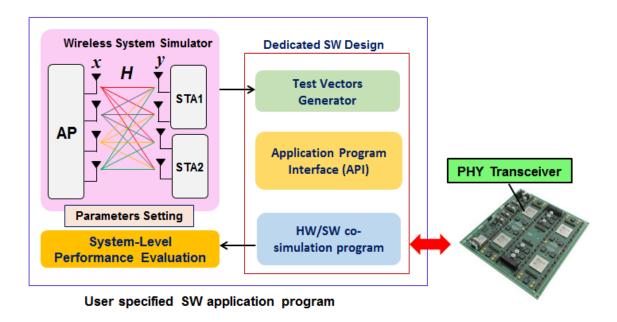

The complete HW and SW design finally build a closed form of co-verification system, which is called as hardware-in-the loop (HIL) co-verification system. The generic structure of HIL system is depicted in Fig. 3.8.

By utilizing this HIL scheme, a system-level verification can be carried out in the following steps:

1. First, the system-level simulation will perform complete system simulation, as specified by system parameters from user. In the same time, the simulation will provide intended input data for DUT block.

Figure 3.7: HAPS Hardware Platform

- 2. The input data for DUT is passed through vectors generator to create set of data vectors as required by DUT.

- 3. When generated data vectors are available, API software passes the re-formatted data to bus driver software and latter sends to the HW platform.

- 4. While the HW performs data processing, the testbench software waits for the interrupt signal from intended test point. As the interrupt signal is available, the software testbench reads out simulation data from the memory, as pointed by specified address. This simulation results are then sent back to system-level simulation for further system-level evaluation.

### 3.4.4 Methodology Comparison

In order to quantify the effectiveness of our proposed methodology, we summarize the comparison of several important features from different methodology/verification environment, as shown in Table 3.1.

Although high level simulation can provide all abstraction of system functionality and also requires low-effort for environment setup, however, the simulation results are too far

User specified SW application program

Figure 3.8: General HW/SW Architecture

from real hardware performance. In order to address this limitation, RTL simulation is carried out to obtain more accurate evaluation. However, performing verification of complex circuit and extensive computation using RTL simulator is prohibited due to very long runtime simulation, particularly for exhaustive verification involving various system parameters and many different design versions. To accelerate design verification and to achieve the optimum performance, the standalone FPGA prototyping is employed, such as in [9]. Unfortunately, the standalone FPGA implementation needs huge effort since it must implement all system into hardware part. Hence, the verification task could only be performed at very late stage of design development. Furthermore, this simulation approach is also less flexible for various test scenarios and difficult to maintain system level performance.

Recently, the hardware-in-the-loop is a promising solution for fast verification. It also has flexibility to support various system parameters. However, there is significant difference between our proposed work and the previous work of HIL system [15]. The HIL method in [15] employs Simulink environment that performs cycle-based simulation. Thus, the simulation is carried out as a time-driven simulation. This methods will introduce large overhead due to HW/SW interaction in each cycle simulation. On the other hand, our proposed verification is performed in data-driven based simulation that requires small overhead

Table 3.1: Comparison of Co-verification Methodology

| Objectives/Metrics           | Synopsys Hybrid<br>Prototyping [23] | HIL [15] | Proposed     |

|------------------------------|-------------------------------------|----------|--------------|

| High Level Simulation        |                                     |          |              |

| a) Time-driven (cycle-based) | $\checkmark$                        | ✓        | $\checkmark$ |

| b) Data-driven (vector-based | ×                                   | ×        | ✓            |

| RTL Simulation               | ×                                   | ✓        | ✓            |

| FPGA simulation              | <b>√</b>                            | ✓        | ✓            |

| Unified HW/SW verification   | <b>√</b>                            | ✓        | ✓            |

| Verification speed           | moderate                            | moderate | fast         |

on the HW/SW interaction. Therefore, the proposed method can achieve fast verification speed .

### 3.5 Summary

In this chapter, the co-verification methodology in unified framework is proposed. The proposed co-verification methodology includes:

- 1. The generic structure of HW/SW co-verification: reflects the recent SoC architecture and has flexible HW/SW interface.

- 2. Task partitioning methodology: allocates the task/function of overall system into implementation platform, either HW platform or SW platform.

- 3. Data-driven simulation within Hardware-in-the Loop co-verification: improves verification time significantly over the HIL platform in [15].

The proposed unified methodology has several main features, which are: (1) high flexibility to support fast turn-around on design modification and design extension; (2) ability to cover various stages of verification task (from algorithm validation to hardware implementation); (3) tightly-integrated with system-level simulation to maintain reliability of system performance.

### **Chapter 4**

### Fast Co-verification and Design Exploration in Complex Circuits

In this section, we describe one application example of the proposed unified framework discussed in Chapter 3, particularly for supporting fast co-evaluation and design exploration of complex circuit. The description covers algorithm-architecture translation, efficient architecture design, and building efficient verification framework. The MIMO decoder circuit of high throughput wireless system is selected to represents complex circuit. Furthermore, the relevant performance metrics are also presented.

## 4.1 Overview of MIMO Decoder in High Throughput Wireless Communication System

Multiple input multiple output (MIMO) wireless communication system is one of technology breakthrough in wireless communication system. Recently, this technology has widely adopted for providing high-data transmission rate. In WLAN standard family, the MIMO technology has been introduced since the deployment of 802.11n standard. Using MIMO transmission scheme the physical layer transmission rate can achieve upto 600 Mbps. MIMO transmission scheme utilizes multiple antennas both in transmitter and receiver to obtain the performance gain, which are spatial multiplexing gain and diversity

gain.

In order to increase system reliability, the MIMO scheme employs spatial diversity. In this scheme, the copy of data are transmitted through multiple antennas and will experience different paths. In the receiver, these multiple independent signals are utilized in decoding process in order to improve transmission reliability. On the other hand, in order to increase transmission rate (e.g. throughput), MIMO scheme sends the different data into each transmit antenna by using multiplexing scheme. Hence the obtained performance gain refers to spatial multiplexing gain. For single link communication with the number of transmit antennas  $N_T$  and the number of receive antennas  $N_R$ , the maximum diversity gain is  $N_T N_R$ , while the maximum spatial multiplexing gain is min $\{N_T, N_R\}$ . However, we cannot achieve both the maximum diversity gain and maximum spatial multiplexing gain in the same time. Hence, there is a trade-off between these two performance gains [24].

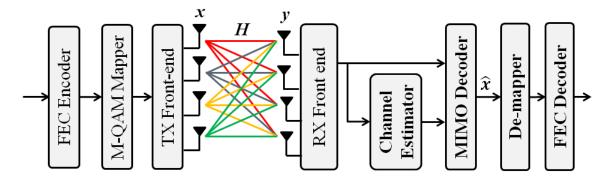

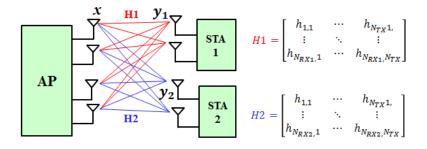

In this thesis, the main objective is to implement high throughput wireless system. Hence, the MIMO system is realized through spatial multiplexing scheme. We consider a MIMO wireless communication system with N transmit antenna and N receive antenna. The transmit symbol is taken from a quadrature amplitude modulation(QAM) which has  $2^M$  constellation points. M denotes the modulation order. For simplification, the employed MIMO system is shown in Fig. 4.1.

Figure 4.1: NxN MIMO Communication System Model

The transmission of each vector **x** over flat-fading MIMO channels can be written as

$$\mathbf{y} = \mathbf{H}\mathbf{x} + \mathbf{n} \tag{4.1}$$

where  $\mathbf{x} = [x_1, x_2, ..., x_N]^T$  is the transmitted signal vector,  $\mathbf{y} = [y_1, y_2, ..., y_N]^T$  is the received signal vector,  $\mathbf{H}$  is the  $N \times N$  channel matrix, and  $\mathbf{n} = [n_1, n_2, ..., n_N]^T$  is independent identically distributed Gaussian white noise vector.

The MIMO decoder block plays an important role in MIMO wireless communication system because the BER performance is highly dependent on employed MIMO decoder algorithm. Many researchers have investigated several techniques that are feasible for practical implementation, such as Zero Forcing (ZF) [25], maximum likelihood detection (MLD) [26], linear minimum mean square error (LMMSE) [27], Bell Labs layered space-time MMSE (BLAST MMSE) [28], and lattice-reduction aided MMSE (LRA MMSE) [29].

ZF algorithm and MMSE algorithm estimate the received signals based on the inverse matrix,  $\mathbf{H}^{-1}$ . In the case of the inverse matrix can not be found, the MIMO detection could employ the pseudo inverse matrix,  $\mathbf{H}_{\mathbf{ZF}}^{+}$  and  $\mathbf{H}_{\mathbf{MMSE}}^{+}$ . As ZF MIMO detection doest not consider the contribution of noise, the MMSE MIMO detection includes the noise variance,  $\sigma_{n}^{2}$ , as the correcting factor for weight calculation in MIMO detection process. The ZF and MMSE MIMO detection algorithms can be expressed as follow.