# Failure Analysis of Power Devices Based on Real-Time Monitoring

| 著者                | Watanabe A., Tsukuda M., Omura I.    |

|-------------------|--------------------------------------|

| journal or        | Microelectronics reliability         |

| publication title |                                      |

| volume            | 55                                   |

| number            | 9-10                                 |

| page range        | 2032-2035                            |

| year              | 2015-07-17                           |

| URL               | http://hdl.handle.net/10228/00006262 |

doi: info:doi/10.1016/j.microrel.2015.06.128

## Failure analysis of power devices based on real-time monitoring A. Watanabe<sup>a, c\*</sup>, M. Tsukuda<sup>b, c</sup>, I. Omura<sup>a, c</sup>

<sup>a</sup> Department of Electrical Engineering/Electronics, Kyushu Institute of Technology, 1-1 Sensui, Tobata, Kitakyushu, 804-8550, Japan

<sup>b</sup> Electronics Research Group for Sustainability, Asian Growth Research Institute, Kitakyushu, Japan

<sup>c</sup> Next generation power electronics research center, Kyushu Institute of Technology, Kitakyushu, Japan

### Abstract

The aim is to provide failure analysis of power devices based on real-time monitoring. The real-time monitoring provides a time-domain data related to a failure mechanism. The data includes important information about primary failure, which is often lost by conventional post-defect failure analysis. Our system monitors interfaces of component material inside the device by scanning acoustic tomography (SAT) under a power cycling test in addition to electrical and thermal condition of the device. A precursor of the failure in an early stage was indicated by the interface image much earlier than a thermal and an electrical technique. Feature identification and extraction from a series of image data by image processing efficiently pointed out the damaged site before the failure was occurred.

### **Corresponding author.**

nave@elcs.kyutech.ac.jp Tel & Fax: +81 (93) 884 3298

© 2015. This manuscript version is made available under the CC-BY-NC-ND 4.0 license http://creativecommons.org/licenses/by-nc-nd/4.0/

### Failure analysis of power devices based on real-time monitoring

A. Watanabe<sup>a, b\*</sup>, M. Tsukuda<sup>b, c</sup>, I. Omura<sup>a, b</sup>

### 1. Introduction and proposal concept

Failure analysis is essential to improve reliability of power devices. Especially, to determine primary failure mechanism is important for fundamental improvement of reliability of power devices. In many cases, post defect or interim samples picking out under acceleration test have been used for the failure analysis. In this way, it is often difficult to determine the primary failure mechanism because of incidental damages especially to high power density modules [1,2]. Moreover, the main failure mechanisms in standerd power modules are caused by internal fatigue of component material; therefore, it is also difficult to determine the primary failure mechanism by well-known monitoring solutions, such as electrical or thermal methods. [1].

Our approach to failure analysis of power devices is based on a real-time monitoring of a device under test (DUT). This technique can record both what happened at a moment of failure occurred and huge back-ground data which include important information related to the primary failure mechanism. The information about primary failure mechanism is 2 lines space

often lost by conventional post-defect failure analysis. In order to implement the failure analysis based on real-time monitoring, it is imperative to identify features and extraction of a parameter related to the failure from the huge data.

In this paper, we demonstrate failure analysis of power devices based on real-time monitoring with scanning acoustic tomography (SAT). In addition to monitoring electrical and thermal condition of the device, this system can monitor interfaces of component material inside the device under a power cycling test. In this demonstration, we were able to identify a precursor of failure in SAT images much earlier than an electrical property had changed.

### 2. Real-time monitoring system for failure analysis

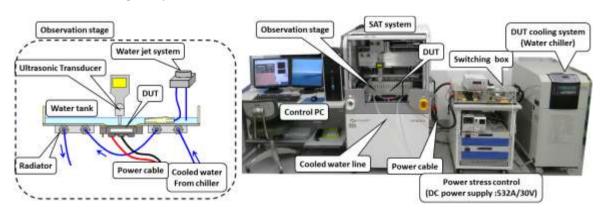

We have developed a real-time monitoring system for failure analysis of power devices [3,4]. The system was designed to record interface images of component materials, forward voltage under constant stress current, junction temperature of the chip and base plate temperature (Fig. 1).

Fig. 1. Real-time monitoring system for failure analysis of power devices

<sup>\*</sup> Corresponding author. nave@elcs.kyutech.ac.jp Tel & Fax: +81 (93) 884 3298

Interface images of component materials of DUT was observed by SAT/SAM (Scanning Acoustic Tomography / Microscopy). This technique, which uses ultrasonic wave, is capable of non-destructive observation of the inside of electronic devices and also microscopic analysis due to its fine resolution [5-10]. Moreover, different interface regions can be observed at the same time by capturing ultrasonicecho signal from different interfaces.

Frame rate of imaging depends on the number of measurement points [3,4]. Therefore, more than 2 frames per minute were acquired as a practical standard for our real-time monitoring. The images obtained in real-time monitoring were rather low resolution to ensure the frame rate; therefore, high resolution images for detail analysis were obtained during the interval of power cycling. Moreover, couplant water for SAT imaging was also utilized for device cooling.

The junction temperature of DUT was estimated by a temperature sensitive parameter (TSP) such as on-state voltage drop at low current. A sense current  $I_{\text{TSP}} = 100$  mA was applied at all times during the power cycling test to measure the TSP voltage. When the stress current was turn-off, the power supply for power stress was cut off by the DUT's switching system and the TSP voltage was monitored during the cooling interval of power cycling. An experimentally obtained conversion formula made it possible to numerically derive the temperature from TSP voltage. Temperature of DUT surface and couplant water was also monitored with fiber optic temperature sensors.

### 3. Power cycling test with DBC module

The real-time monitoring was performed with a diode on DBC substrate. A stress current of 180 A was applied only to a diode and its cycle was 2 s turn-on and 5 s turn-off. The maximal junction temperature  $T_{\rm high}$  and the minimal junction temperature  $T_{\rm low}$  was approximately 128 °C and 18 °C respectively, thus the  $\Delta T_{\rm j}$  was almost 110 °C under this condition.

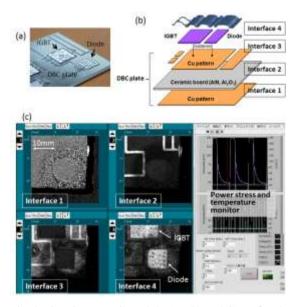

A GUI for the real-time monitoring is shown in Fig. 2. The observed area was 30 mm x 30 mm with 0.2 mm scanning pitch. Under this condition, the frame rate was 3 frames/min.; therefore, complete 1 frame imaging within 1 cycle (7 sec) was impossible in this experiment. Image noise appeared around the

Fig. 2. Specimen DBC module (a), (b) and GUI of realtime monitoring system (c). (b) indicates corresponding interface observed in the GUI.

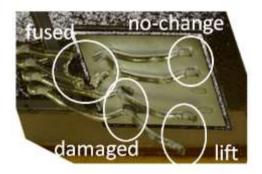

Fig. 3. Failed specimen diode after 4677 cycles. This photograph was flipped upside down to adjust orientation of following SAT images.

diode chip because self-heating of the DUT generated small bubbles.

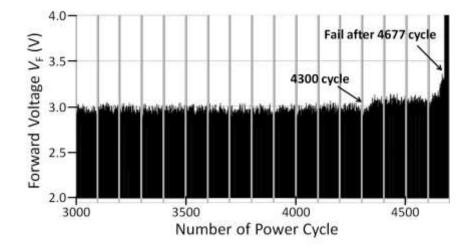

A failure occurred due to bond wire lift-off after 4677 power cycles (Fig. 3). Fig. 4 shows behavior of forward voltage  $V_{\rm F}$  of the DUT at the power cycling test. Remarkable change of  $V_{\rm F}$  was observed after 4300 cycles and in a few ten cycles just before the failure occurred. Fig. 5 shows a series of SAT images at the top of the diode chip, namely interface 4 in Fig. 2(b). Few bonding marks on the diode chip disappeared after 3500 cycles. This disappearance of the bonding marks in the SAT images was not caused by defocus during image acquisition because bonding marks on the IGBT chip, which placed on almost

same level of that on the diode chip, were observed still the same contrast after the failure. A bonding-

wire lift was recognized after the failure at the position where the bonding marks disappeared in the

Fig. 4. Behavior of forward voltage  $V_{\rm F}$  of the DUT at the power cycling test.

SAT images; therefore, the disappearance of the bonding marks in the images was caused by a change of reflection condition of ultrasonic wave at the interface. On the other hand, the thermal dissipation was not affected during this failure process, because remarkable changes of junction temperature behavior and SAT images at the solder layer was recognized (not shown here).

In this case, the SAT images indicated a precursor of the failure earlier than the electrical property had changed. This result strongly suggests that a real-time monitoring of internal structure of DUT is an indispensable technique to identify the primary failure mechanism of power devices.

### 4. Feature extraction from time-domain data

Identifying a feature and extraction of parameters related to the failure from the huge data is essential to implement real-time monitoring based

1

1

4000~4100

4300~4400

4300~4400

1

4100~4200

1

4100~4200

4400~4500

Fig. 6. Image change around 4300 cycle where the  $V_{\rm F}$  change was observed. These images suggest that bonding 'gion condition was not affected in this period. se im

failure analysis. As an example we tried feature extraction from series of SAT images by image-processing.

Fig. 5 also shows a series of subtract images. These images were obtained to subtract a former image from a latter one of a power cycling period. The subtract images illuminates changing point in the interface as high-grayscale value, namely bright pixel. The subtract images in Fig. 5 indicated that the bonding condition varied in the power-cycling period of 3000 ~ 4000 and 4600~failure. This result suggests that the bond lift-off at the lower right site of the chip took place and then the bond lift-off with anode metal damage occurred. The same technique was applied to the power cycling period of around 4300 where a remarkable change of  $V_{\rm F}$  was observed. According to Fig. 6, the change of  $V_{\rm F}$  was most likely caused by a degradation of the bonding wire itself (e.g. heel-crack) because there was no change at the bonding site on the chip.

By comparing the initial image with that after a

Fig. 7. A series of subtract images at an early stage of power cycling test. Bright regions indicate areas where the contrast changed from the initial image. Some bonding sites became brighter after 500 cycles. This result means that the bonding interface was affected in a se in very early stage of the failure process.

power cycling test, changing points become clearer. Fig. 7 shows subtract images obtained with the initial images. The bonding site became brighter after 500 cycles which means that the bonding interface was affected at a very early stage in the failure process. This finding can be obtained only by the timedomain analysis of the real-time monitoring on internal structure of DUT.

We succeeded to extract a feature of image changes with image processing. However, In order to implement real-time monitoring based failure analysis, it is necessary to identify and determine critical parameters of some failure modes.

### 5. Conclusion

Failure analysis of power devices based on realtime monitoring with SAT was demonstrated. The SAT images were indicated a precursor of the failure in an early stage much earlier than a thermal and an electrical technique. This result strongly suggests that real-time monitoring of internal structure of DUT is an indispensable technique to identify the primary failure mechanism of power devices. Feature identification and extraction from a series of image data by image processing efficiently pointed out the damaged site before the failure occurred.

#### Acknowledgements

A part of this work was supported by SCAS (Sumika Chemical Analysis Service).

### References

- Lutz J., Schlangenotto H., Scheuermann U., Doncker R.D., "Semiconductor Power Devices", Springer; 2011.

- [2] Zehringer R., Stuck A., Lang A., "Material requirements for high voltage, high power IGBT devices", Solid-State Electronics, Vol. 42, 1998, pp. 2139–2151.

- [3] Watanabe A., Omura I., "Real-time failure imaging system under power stress for power semiconductors using Scanning Acoustic Tomography (SAT)", Microelectronics Reliability, Vol. 52, 2012, pp. 2081-2086.

- [4] Watanabe A., Tsukuda M., Omura I., "Real time degradation monitoring system for high power IGBT module under power cycling test", Microelectronics Reliability, Vol. 53, 2013, pp. 1692-1696.

- [5] G. De Liso, M. Muschitiello and M. Stucchi, "Failure analysis of encapsulated electronic devices by means of scanning ultra microscopy technique". SCANNING 15, 1993, 236-242.

- [6] L. Angrisania, L. Bechoub, D. Dalletb, P. Dapontec and Y. Oustenb, "Detection and location of defects in electronic devices by means of scanning ultrasonic microscopy and the wavelet transform", Measurement 31, 2002, 77–91.

- [7] L. Feller, S. Hartmann and D. Schneider, "Lifetime analysis of solder joints in high power IGBT modules for increasing the reliability for operation at 150 oC", Microelectronics Reliability 48, 2008, 1161–1166.

- [8] S. Brand, P. Czurratis, P. Hoffrogge, D. Temple, D. Malta, J. Reed and M. Petzold, "Extending acoustic microscopy for comprehensive failure analysis applications", J. Mater. Sci. Mater. Electron. 22, 2011, 1580–1593.

- [9] T. Chung, J. Jhang, J. Chen, Y. Lo, G. Ho, M. Wu and C. Sun, "A study of large area die bonding materials and their corresponding mechanical and thermal properties", Microelectronics Reliability 52, 2012, 872-877.

- [10] P. Mario, M. Josef and I. Michael, "Inverted high frequency Scanning Acoustic Microscopy inspection of power semiconductor devices", Microelectronics Reliability 52, 2012, 2115-2119.