## Design and Analysis of a New Evaluation Circuit for Capacitors Used in a High-Power Three-Phase Inverter

| 著者                | Hasegawa Kazunori, Omura Ichiro, Nishizawa<br>Shin-ichi |

|-------------------|---------------------------------------------------------|

| journal or        | IEEE Transactions on Industrial Electronics             |

| publication title |                                                         |

| volume            | 63                                                      |

| number            | 5                                                       |

| page range        | 2679-2687                                               |

| year              | 2016-05                                                 |

| URL               | http://hdl.handle.net/10228/00006165                    |

doi: info:doi/10.1109/TIE.2015.2511097

# Design and Analysis of a New Evaluation Circuit for Capacitors Used in a High-Power Three-Phase Inverter

Kazunori Hasegawa, Member, IEEE, Ichiro Omura, Member, IEEE, and Shin-ichi Nishizawa, Member, IEEE

Abstract—DC-link capacitors in power electronic converters are a major constraint on improvement of power density as well as reliability. Evaluation of the dc-link capacitors in terms of power loss, ageing, and failure rate will play an important role in design stages of the next-generation power converters. This paper proposes a new evaluation circuit for dc-link capacitors used in a high-power three-phase inverter, which is intended for testing power loss, failure rate, ageing, and so on. The evaluation circuit produces a practical ripple current waveform and a dc bias voltage into a capacitor under test, in which the ripple current is equivalent to that generated by the three-phase inverter on the dc link. The evaluation circuit employs a full-scale current-rating and downscaled voltage-rating inverter for producing the ripple current, so that the power rating of the evaluation circuit is much smaller than that of a full-scale current rating and full-scale voltage rating inverter. Theoretical analysis and simulated results verify the effectiveness of new evaluation circuit.

*Index Terms*—DC-link capacitors, high-power density, reliability, three-phase inverters.

#### I. INTRODUCTION

Power density of power electronic converters are continuously becoming higher and higher as their market size is getting larger and larger, which is accompanied by smaller power loss, lower volume, and lower weight in the converter. The market size growth also requires improvement of reliability not only in power semiconductor devices but also in passive components [1, 2]. Hence, the next-generation power converters will be designed with managing both power density and reliability.

DC-link capacitors in power electronic converters are a major constraint on improvement of power density [3, 4]. They tend to include a design margin of size or capacitance due to power loss. Thus, the minimum design margin of the capacitors is desirable, which should be considered in design stages of the

The authors are with Kyushu Institute of Technology, Kitakyushu 808-0196, Japan (e-mail: hasegawa@life.kyutech.ac.jp; omura@ele.kyutech.ac.jp; nishizawa@life.kyutech.ac.jp). S. Nishizawa is also with the National Institute of Advanced Industrial Science and Technology, Tsukuba 305-8568, Japan.

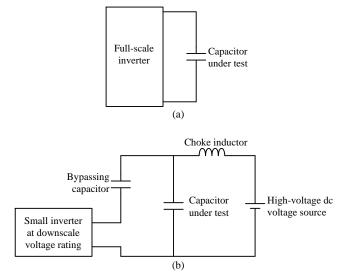

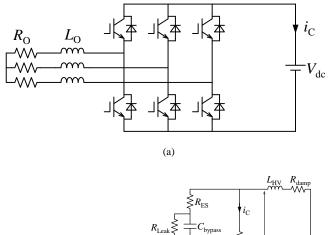

Fig. 1 Basic concepts of an evaluation circuit for a high-power capacitor. (a) Using full-scale inverter. (b) Using full-scale current-rating and downscale voltage-rating inverter.

converters. Furthermore, a lifetime of the capacitors is usually shorter than that of semiconductor devices or magnetic devices, which would degrade reliability of the power converters. Evaluation of the capacitors in terms of power loss, ageing, and failure rate will play an important role in design stages of the next-generation power converters [5-14]. However. characteristics of the capacitors are usually evaluated by a single sinusoidal current such as 120 Hz, 1 kHz, and so on [9, 10, 14-16]. There are some kinds of "ripple current tester" instruments that provide a sinusoidal ripple current as well as a dc-bias voltage into the capacitor [16]. Actual current flowing out of the converter into the capacitor contains multiple frequency components [17], so that characteristics of the capacitors cannot be exactly estimated. Although the so-called fast Fourier transform (FFT) can extract the multiple frequency components from the actual current, a power loss of the capacitor cannot be estimated using the multiple frequency components because power loss in general has a nonlinear characteristic. In addition, the dc bias voltage across the capacitor affects power loss and ageing [2, 7, 13, 14]. Thus, the power converters often employ more capacitors than necessary. It is important to develop an evaluation circuit for component

Manuscript received June 24, 2015; revised October 14, 2015; accepted November 24, 2015.

Copyright (c) 2015 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending a request to pubs-permissions@ieee.org.

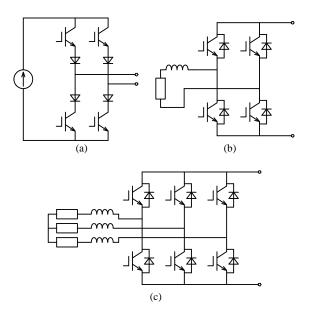

Fig. 2 Possible configurations of the small inverter. (a) Single-phase CSI. (b) Single-phase VSI. (c)Three-phase VSI

testing of capacitors, which will be utilized in design stages or in tests before shipment of the converters. Note that the system should behave as an existing inverter in terms of the dc bias voltage and ripple current waveform of the capacitor.

This paper proposes a new evaluation circuit for dc-link capacitors used in a high-power three-phase inverter, which presents a practical ripple current waveform that is equivalent to that of the existing inverter. The circuit will be utilized for evaluating the capacitor by electric or thermal measurement such as the followings:

- 1. Electrical measurement of ESR and capacitance [8, 11].

- Power loss measurement by electrical or calorimetric measurement [12, 18].

- 3. Accelerated aging [14].

Although this paper does not pay attention to measuring characteristics of the capacitor under test, it just focuses on design and analysis of the evaluation circuit. The following sections describes possible circuit configurations, intensive theoretical analysis, and power rating of the evaluation circuit.

#### II. BASIC CONCEPT

#### A. Evaluation circuit for capacitors

The most effective way to evaluate dc-link capacitors is measuring their characteristics with an existing converter in operation. For example, references [6, 8, 11] discuss real-time monitoring for capacitor condition using equivalent series resistance (ESR) and capacitance. Therefore, a basic idea of the evaluation circuit would utilize the existing inverter. Fig. 1 (a) shows the basic idea of the evaluation circuit, in which a full-scale current-rating and full-scale voltage-rating inverter is connected to a capacitor under test,  $C_{\rm UT}$ . The inverter provides a practical ripple current and dc bias voltage for the capacitor.

There are some special circuits that evaluate the capacitors [10, 14]. Reference [10] presents a simple circuit to evaluate an electrolytic capacitor, which consists of a combination of a dc-voltage supply providing a dc bias voltage, and a line-frequency transformer injecting a sinusoidal ripple current.

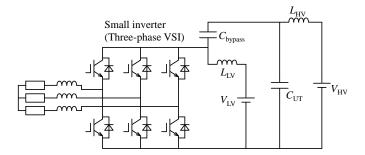

Fig. 3 Proposed evaluation circuit using a three-phase VSI.

The circuit is useful for estimating the capacitance and equivalent series resistance (ESR). Reference [14] presents a test circuit for accelerated aging of metalized film capacitors, which consists of a combination of a resonant inverter producing a sinusoidal ripple current and a dc voltage supply providing a dc bias voltage. Although both the two combinations contribute to reducing the overall power rating of the evaluation circuit, the ripple current waveform is different from the practical one generated by the inverter.

Fig. 1 (b) shows the basic concept of the proposed evaluation circuit that employs a small inverter, the capacitor under test, a bypassing capacitor, a choke inductor, and a high-voltage dc supply. The concept is similar to the circuits proposed in [10] and [14] in terms of a combination of a ripple current source and a dc voltage supply, whereas it presents a practical ripple current waveform, i.e., the same current waveform as that generated by the inverter. Current rating of the small inverter is full-scale, while voltage rating of that is downscale. The high-voltage dc supply keeps the capacitor voltage a desired dc bias voltage. The bypassing capacitor is used for circulating the ripple current generated by the inverter through the capacitor under test. The choke inductor is used for blocking the ripple current, through which only dc current flows. Hence, the proposed circuit operates as a full-scale voltage-rating and full-scale current-rating inverter from the standpoint of the dc bias voltage and ripple current. Thus, power-rating of the small inverter is much smaller than that of the full-scale inverter.

## B. Possible configurations of the small inverter

Candidates for the small inverter can be classified into the followings:

- 1. Single-phase current-source inverter (CSI) (Fig. 2 (a))

- 2. Single-phase voltage-source inverter (VSI) (Fig. 2 (b))

- 3. Three-phase voltage-source inverter (VSI) (Fig. 2 (c))

The evaluation circuit using the single-phase CSI behaves as a full-scale three-phase or single-phase inverter if it can provide the same ripple current waveform as the current generated by the full-scale single-phase or three-phase inverter, respectively. However, not only pulse width but also amplitude should be modulated to synthesize the ripple current waveform. In practice, therefore, quite complex control would be required for the CSI.

The single-phase VSI can be used for an evaluation circuit for the full-scale single-phase inverter. DC-link terminal of the VSI is connected to the bypassing capacitor and capacitor under test, so that the voltage across the bypassing capacitor is slightly lower than that across the capacitor under test by the dc-link voltage. Since instantaneous power in a single-phase circuit

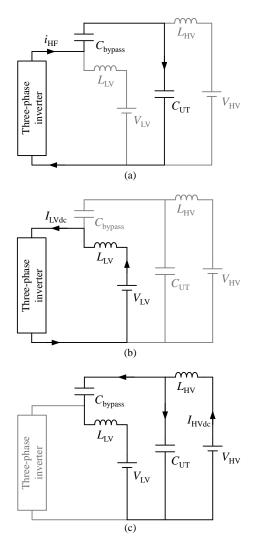

Fig. 4 Current paths of the proposed circuit. (a) AC current flowing out of the VSI. (b) DC current flowing out of the low-voltage dc supply. (c) DC current flowing out of the high-voltage dc supply.

fluctuates at double the fundamental frequency, a ripple amplitude of the dc-link voltage in the single-phase VSI tends to be large. It will be a constraint on the voltage rating of the VSI because the dc-link voltage should be larger than the ripple amplitude. The evaluation circuit consisting of the single-phase VSI would be applicable to capacitors of modular multilevel cascade converters (MMCC) [19], that are also referred to "modular multilevel converters (MMC)" or "cascaded H-bridge converters (CHB)," because they consist of single-phase full-bridge converters.

The three-phase VSI is a candidate for an evaluation circuit for the full-scale three-phase inverter. DC-link terminal of the three-phase VSI is connected to the bypassing capacitor and capacitor under test like the single-phase VSI. On the other hand, a ripple amplitude of the dc-link voltage in the three-phase VSI is much lower than that in the single-phase VSI because the instantaneous power of the three-phase inverter is constant in a steady state [20].

This paper introduces the three-phase VSI as the small inverter because of the following reasons:

- 1. The three-phase inverter is widely used.

- 2. Lower dc-link voltage allows smaller power rating.

Fig. 5 Equivalent circuit focusing on the current flowing out of the inverter  $I_{\rm HF}$  and the capacitor current  $I_{\rm C}$ .

- 3. General-purpose inverters are available as the small inverter.

- 4. No special control is required to the ripple current

Note that the three-phase VSI has only to control its output voltage, i.e., open-loop PWM control is applicable.

#### **III. PROPOSED SYSTEM CONFIGURATION**

### A. Circuit Configuration

Fig. 3 shows the proposed evaluation circuit consisting of the three-phase VSI, a low-voltage dc supply  $V_{LV}$  with a choke inductor  $L_{LV}$ , the high-voltage dc supply  $V_{HV}$  with a choke inductor  $L_{HV}$ , the bypassing capacitor  $C_{bypass}$ , and the capacitor under test,  $C_{UT}$ . The low-voltage dc supply is used for driving the three-phase VSI. The high-voltage dc supply provides a dc bias voltage to  $C_{UT}$ .

Fig. 4 shows current paths flowing out of the two dc voltage supplies and the three-phase VSI. The high-frequency ripple current generated by the VSI,  $i_{\rm HF}$  circulates through  $C_{\rm bypass}$  and  $C_{\rm UT}$  because it does not flow into the two choke inductors  $L_{\rm LV}$  and  $L_{\rm HV}$  as shown in Fig. 4(a). The low-voltage dc supply  $V_{\rm LV}$  provides a dc current  $I_{\rm LVdc}$  to the VSI through  $L_{\rm LV}$  as shown in Fig. 4(b). The high-voltage dc supply charges  $C_{\rm UT}$  and  $C_{\rm bypass}$  to their operating voltages, and then supplies a small amount of leakage dc current of the capacitors,  $I_{\rm HVdc}$  as shown in Fig. 4(c). Hence, the power rating of the high-voltage dc supply is quite small.

## B. Power rating of the small inverter

Since the current rating of the small inverter is the same as that of the full-scale inverter, the relation between the power rating of the small inverter,  $P_{\text{small}}$  and that of the full-scale inverter,  $P_{\text{FS}}$  is given by

$$\frac{P_{\text{small}}}{P_{\text{FS}}} = \frac{V_{\text{DClink-S}}}{V_{\text{DClink-FS}}} = \frac{V_{\text{LV}}}{V_{\text{HV}}},\tag{1}$$

where  $V_{\text{DClink-FS}}$  and  $V_{\text{DClink-S}}$  are dc-link voltages of the full-scale inverter and the small inverter, respectively, and  $P_{\text{FS}}$  is the power rating of the full-scale inverter. As the dc-link voltage of the small inverter,  $V_{\text{DClink-S}}$  contains ripple voltages of  $C_{\text{UT}}$  and  $C_{\text{bypass}}$ , the dc mean of  $V_{\text{DClink-S}}$  should be designed to be more than the ripple voltages. The low-voltage dc supply should provide the dc mean voltage according to the ripple voltages. Since the instantaneous power of the three-phase

TABLE I RATINGS AND CIRCUIT PARAMETERS OF THE PROPOSED CIRCUIT USED IN ANALYSIS AND SIMULATION.

| CIRCUIT USED IN ANALYSIS AND SIMULATION.                                                  |                       |                |  |

|-------------------------------------------------------------------------------------------|-----------------------|----------------|--|

| Power rating of the system                                                                | Р                     | 1 MVA          |  |

| Power rating of the inverter                                                              | $P_{\rm inv}$         | 100 kVA        |  |

| AC current rating                                                                         | $I_0$                 | 300 A          |  |

| AC voltage rating                                                                         | $V_{\rm O}$           | 200 V          |  |

| Low-voltage dc source                                                                     | $V_{\rm LV}$          | 350 V          |  |

| High-voltage dc source                                                                    | $V_{ m HV}$           | 3.5 kV         |  |

| Load inductor                                                                             | Lo                    | 1.23 mH [100%] |  |

| Load resistor                                                                             | Ro                    | 3.9 mΩ [1%]    |  |

| Switching frequency                                                                       | fsw                   | 1 kHz          |  |

| Output frequency                                                                          | fo                    | 50 Hz          |  |

| High-voltage choke inductor                                                               | $L_{\rm HV}$          | 1 mH           |  |

| Low-voltage choke inductor                                                                | $L_{LV}$              | 1 mH           |  |

| Capacitor under test                                                                      | $C_{\rm UT}$          | 3 mF           |  |

| Unit capacitance constant of the capacitor under test [25]                                | Н                     | 18 ms          |  |

| Bypassing capacitor                                                                       | $C_{\mathrm{bypass}}$ | 3 mF           |  |

| Leakage resistance of capacitors                                                          | $R_{\text{leak}}$     | 19 kΩ (0.05%)  |  |

| Equivalent series resistance of capacitors                                                | R <sub>ES</sub>       | 5.8 mΩ (0.05%) |  |

| Damping resistor                                                                          | $R_{\rm damp}$        | 10 Ω           |  |

| () is based on 1 MVA, 2 kV, and 300A<br>[] is based on 100 kVA, 200 V, 300 A, and 50 Hz   |                       |                |  |

| TABLE II RATINGS AND CIRCUIT PARAMETERS OF THE<br>FULL-SCALE INVERTER USED IN SIMULATION. |                       |                |  |

| Power rating        | Р                                       | 1 MVA          |

|---------------------|-----------------------------------------|----------------|

| AC current rating   | $I_0$                                   | 300 A          |

| AC voltage rating   | $V_{\rm O}$                             | 2 kV           |

| DC link voltage     | $V_{ m dc}$                             | 3.5 kV         |

| Switching frequency | fsw                                     | 1 kHz          |

| Output frequency    | fo                                      | 50 Hz          |

| Load inductor       | Lo                                      | 12.3 mH (100%) |

| Load resistor       | Ro                                      | 39 mΩ (1%)     |

| 0 1 1 1             | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 1 50 77        |

() is based on 1 MVA, 2 kV, 300A, and 50 Hz

inverter is constant, dc-link voltage of the three-phase inverter contains only switching ripple component. Thus, one can pay attention to the switching frequency, the current rating, and capacitance of  $C_{\rm UT}$ . In practice, however, attention should also be paid to imbalance of the three-phase load of the inverter because it would cause ripple voltage on the dc link.

Note that, accelerated ageing tests, especially for highly accelerated life tests (HALT), are often accompanied by over voltage or current ratings, so that the ripple voltages would get large. It would be a constraint on reducing the power rating of the small inverter in the accelerating tests.

This paper introduces a condition that the dc-link voltage of the small inverter is 1/20 to 1/10 of that of the full-scale inverter.

#### C. Design of Choke Inductors

Reactances of the two choke inductors should be much larger than that of capacitors  $C_{\text{UT}}$  and  $C_{\text{bypass}}$ .

$$\omega L_{\rm choke} \gg \frac{1}{\omega c_{\rm dc}}$$

, (2)

where  $\omega = 2\pi f_{sw}$ ,  $f_{sw}$  is the switching frequency of the inverter,  $L_{choke}$  indicates a choke inductor of  $L_{HV}$  or  $L_{LV}$ , and  $C_{dc}$  stands for  $C_{UT}$  or  $C_{bypass}$ . The current rating of  $L_{choke}$  is determined by the leakage dc current of  $C_{dc}$ . Since volume of inductor is in proportion to 3/4th power to the maximum stored energy of

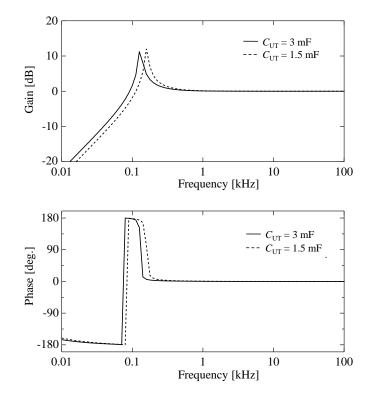

Fig. 6 Bode plot of the transfer function between  $I_{C(S)}$  and  $I_{HF}(s)$ , G(s)

$\frac{1}{2}LI^2$  [21], the volumes of the choke inductors are quite small.

#### D. Example of practical use

Low-voltage (200 or 400 V) general-purpose inverters are available to the small inverter, so that medium-voltage capacitors are suitable for the proposed circuit. The current rating of the general-purpose inverters are up to 1000 A [22, 23]. Thus, the proposed circuit using the general-purpose inverter can evaluate capacitors used in a high-power inverter with a power rating up to 1-10 MVA.

#### IV. ANALYSIS OF THE CAPACITOR CURRENT

This section makes a theoretical analysis of the capacitor current against the current flowing out of the inverter so as to indicate equivalency to the full-scale inverter in terms of capacitor current waveform.

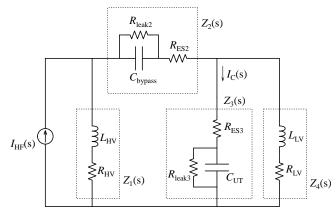

### A. Transfer function for the capacitor current

Fig. 5 shows an equivalent circuit that focuses on the transfer function between the ripple current flowing out of the inverter  $I_{\rm HF}$  and the capacitor current  $I_{\rm C}$ , where  $I_{\rm HF}$  is depicted as a high-frequency ac current source.  $Z_1$ ,  $Z_2$ ,  $Z_3$ , and  $Z_4$  are impedances of the high-voltage choke inductor, bypassing capacitor, capacitor under test, and low-voltage choke inductor, respectively.  $Z_1$  and  $Z_4$  consist of inductances  $L_{\rm HV}$  and  $L_{\rm LV}$ , and series resistances  $R_{\rm HV}$  and  $R_{\rm LV}$  that stand for equivalent series resistances and/or intentionally-installed damping resistors, respectively.  $Z_2$  and  $Z_3$  contain capacitances  $C_{\rm bypass}$  and  $C_{\rm UT}$ , equivalent series resistances  $R_{\rm ES2}$  and  $R_{\rm ES3}$ , and leakage

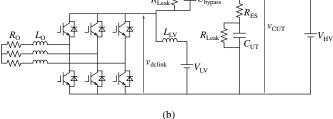

Fig. 7 Circuit configurations used for simulation. (a) Full-scale three-phase inverter. (b) Proposed evaluation system.

resistances  $R_{\text{leak}2}$  and  $R_{\text{leak}3}$ , respectively. The impedances  $Z_1$  to  $Z_4$  are given by the followings:

$$Z_1(s) = sL_{\rm HV} + R_{\rm HV} \tag{3}$$

$$Z_2(s) = \frac{R_{\text{leak2}}}{1 + sC_{\text{bypass}}R_{\text{leak2}}} + R_{\text{ES2}}$$

(4)

$$Z_3(s) = \frac{R_{\text{leak}3}}{1+sC_{\text{UT}}R_{\text{leak}3}} + R_{\text{ES3}} \tag{5}$$

$$Z_4(s) = sL_{\rm LV} + R_{\rm LV}.$$

(6)

$I_{\rm C}(s)$  can be calculated by  $Z_1$  to  $Z_4$  and  $I_{\rm HF}(s)$ . Thus, the transfer function G(s) between  $I_{\rm HF}(s)$  and  $I_{\rm C}(s)$  is expressed as

$$G(s) = \frac{I_C(s)}{I_{HF}(s)} = \frac{Z_1 Z_4}{Z_3 Z_4 + (Z_1 + Z_2)(Z_3 + Z_4)}$$

(7)

#### B. Analytical Result

Table I summarizes the rating and circuit parameters of the proposed circuit used for this analysis as well as simulation described in section V. Reactances of  $L_{\rm HV}$ ,  $L_{\rm LV}$ ,  $C_{\rm bypass}$ , and  $C_{\rm UT}$  under a switching frequency of 1 kHz are given by

$$\omega L_{HV} = \omega L_{LV} = 6.3 \,\Omega \tag{8}$$

$$\frac{1}{\omega c_{bypass}} = \frac{1}{\omega c_{UT}} = 53 \text{ m}\Omega \tag{9}$$

Thus, reactances of choke inductors are adjusted to be much larger than those of the capacitors. Note that  $R_{HV}$  corresponds to the damping resistor  $R_{damp}$  described in section V, and  $R_{LV}$  is set to be zero.

Fig. 6 provides a bode plot of the transfer function G(s) with different capacitors of  $C_{\text{UT}} = 3$  mF and 1.5 mF. The gain of G(s) stays 0 dB and the phase of that does 0 degrees in a range over the switching frequency of 1 kHz, which indicate that the capacitor current  $I_{\text{C}}$  is equivalent to the ripple current flowing out of the inverter  $I_{\text{HF}}$ .

## V. SIMULATION

This section presents simulated results of the proposed circuit with comparing to the full-scale three-phase inverter, where a software package of the "PLECS" is carried out [24].

## A. Full-scale inverter

Fig. 7(a) shows the full-scale three-phase inverter, where a dc voltage source is connected instead of the capacitor under test on the dc link. Sinusoidal pulse-width modulation (SPWM) is applied to the inverter. The inductive load with a small equivalent series resistance of 1% is connected, so that the inverter drives almost only reactive power. Although the ripple current waveform somewhat changes according to the power factor of the inverter output power, it always contains high-frequency ac components that result from the switching frequency and a dc current that synthesizes an active power. Hence, the inverter does not have to drive active power when it operates as a ripple current source. Note that the inverter can also drive active power in return for increased power rating of the dc voltage source.

Table II summarizes the ratings and circuit parameters of the full-scale inverter.

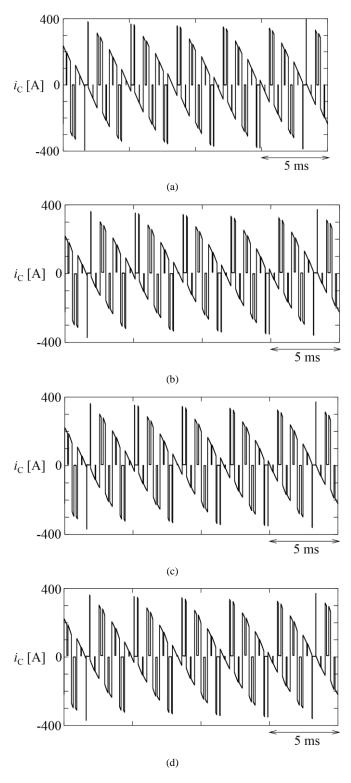

Fig. 8 Simulated waveforms of the capacitor current  $i_c$ . (a) Full-scale inverter. (b) Proposed circuit under Condition 1. (c) Proposed circuit under Condition 2. (d) Proposed circuit under Condition 3.

series resistances and leakage resistances. Power dissipations of the equivalent series resistances and that of the leakage inductances are assumed to be 0.05% of the rated power of the circuit because a dissipation factor of dc-link capacitors used in a high-power inverters is around 0.1%. The damping resistor  $R_{\text{damp}}$  prevents an oscillation caused by the capacitors and the choke inductors. The power consumption of the damping resistor is only 0.1% of the supplied power from the high-voltage dc supply. Note that the proposed circuit can also supply a ripple current in case the load power factor is changed although the low-voltage dc supply has to provide an amount of active power to the small inverter.

This section discusses validity of the proposed circuit with different power ratings and different capacitors as the followings:

- Condition 1: Power rating is 1/10 of the full-scale inverter, and  $C_{\text{UT}} = C_{\text{bypass}} = 3 \text{ mF}.$

- Condition 2: Power rating is 1/20 of the full-scale inverter, and C<sub>UT</sub> = C<sub>bypass</sub> = 3 mF.

- Condition 3: Power rating is 1/10 of the full-scale inverter, and  $C_{\text{UT}} = 1.5$  mF and  $C_{\text{bypass}} = 3$  mF.

The ratings and circuit parameters of the condition 1 are shown in Table I. Condition 2 employs a low-voltage dc source of  $V_{LV}$ = 175 V and the same current rating as the condition 1. Condition 3 uses the same parameters of the condition 1 except for  $C_{UT}$ .

## C. Simulated results

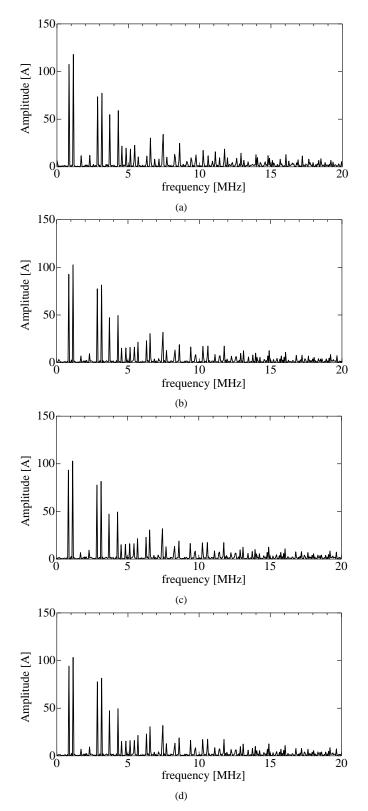

Fig. 8 shows simulated waveforms of the capacitor current  $i_{\rm C}$ . In addition, Fig. 9 illustrates frequency spectrums of the capacitor current extracted by the Fast-Fourier Transform (FFT). All the waveforms of the proposed circuit almost agree with that of the full-scale inverter from the standpoint of time domain as well as frequency domain.

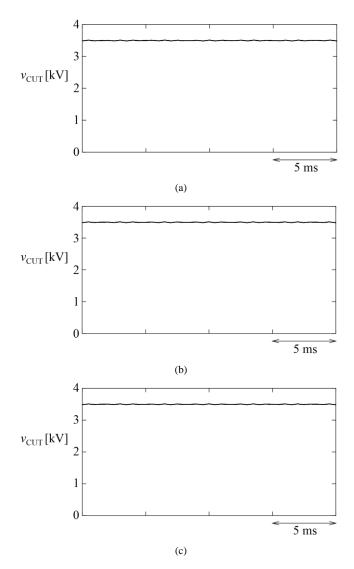

Fig. 10 shows the voltage across the capacitor under test,  $v_{CUT}$  in the proposed circuit. They stay at 3.5 kV that is the dc bias voltage applied by the high-voltage dc supply.

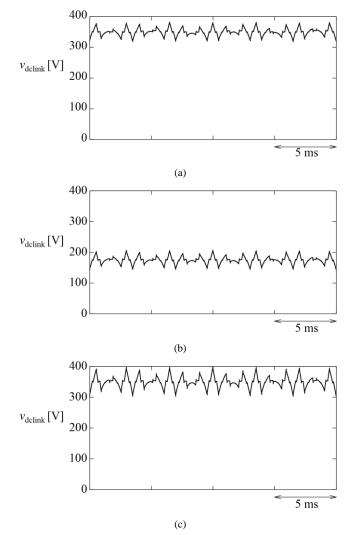

Fig. 11 shows the dc-link voltages of the small inverter in the proposed circuit,  $v_{dclink}$ . Since the peak-to-peak ripple amplitude of  $v_{dclink}$  is determined by  $i_{HF}$  and the capacitors, the amplitude in the condition 1 is equal to that in the condition 2, which is 64 V. This is only 18% of the nominal dc-link voltage of 350 V, and so it would have room for reducing the nominal dc-link voltage, i.e., reducing the power rating of the proposed circuit. On the other hand, the amplitude in the condition 3 are larger than that in the condition 1 and 2 because smaller  $C_{UT}$  is employed.

#### CONCLUSION

Fig. 9 FFT results of the capacitor current  $i_{\rm C}$ . (a) Full-scale inverter. . (b) Proposed circuit under Condition 1. (c) Proposed circuit under Condition 2. (d) Proposed circuit under Condition 3.

## B. Proposed circuit

Fig. 7(b) illustrates the proposed evaluation circuit used for simulation. The capacitors  $C_{\rm UT}$  and  $C_{\rm bypass}$  include equivalent

Fig. 10 Simulated waveform of the voltage across the capacitor under test,  $v_{CUT}$  in the proposed circuit. (a) Condition 1. (b) Condition 2. (c) Condition 3.

This paper has proposed a new evaluation circuit for dc-link capacitors used in a high-power three-phase inverter. The proposed circuit is characterized by combining a small three-phase inverter and a small voltage supply. Although the power rating of the small inverter is less than 1/10 of that of a full-scale three-phase inverter, the proposed circuit is equivalent to the full-scale inverter in terms of the capacitor current and dc-bias voltage. Theoretical analysis has confirmed that the small inverter presents the same ripple current waveform as that of the full-scale inverter. Simulation using a software package of the "PLECS" has confirmed the viability and effectiveness of the proposed circuit, verifying that the proposed circuit presents the same ripple current waveform and dc bias voltage as those of the full-scale inverter to the capacitor under test.

## ACKNOWLEDGEMENT

The authors would like to thank Prof.Tamotsu Ninomiya of Green Electronics Research Institute, Kitakyushu, Japan, and

Fig. 11 Simulated waveform of the dc-link voltage of the small inverter in the proposed circuit. (a) Condition 1. (b) Condition 2. (c) Condition 3.

Prof. Keiji Wada of Tokyo Metropolitan University, Tokyo, Japan, for their fruitful discussion.

#### REFERENCES

- H. Wang, M. Liserre, and F Blaabjerg, "Toward Reliable Power Electronics: Challenges, Design Tools, and Opportunities," *IEEE Ind. Electron. Mag.*, vol. 7, no. 2, pp. 17-26, Jun. 2013.

- [2] H. Wang and F. Blaabjerg, "Reliability of capacitors for dc-ink applications in power electronic converters—an overview," *IEEE Trans. Ind. Appl.* vol. 50, no. 5, pp. 3569-3578, 2014.

- [3] P. Alemi, Y. -C. Jeung, and D. -C. Lee., "DC-Link Capacitance Minimization in T-Type Three-Level AC/DC/AC PWM Converters," *IEEE Trans. Ind. Electron.*, vol. 62, no. 3, pp. 1382-1391, Mar. 2015.

- [4] J. W. Kolar, U. Drofenik, J. Biela, M. Heldwein, H. Ertl, T. Friedli, and S. Round, "PWM converter power density barriers," *IEE Japan Trans. Ind. Appl.*, vol. 128, no. 4, pp.468-480, 2008.

- [5] K. Harada, A. Katsuki, and M. Fujiwara, "Use of ESR for deterioration diagnosis of electrolytic capacitor," *IEEE Trans. Power Electron.*, vol. 8, no. 4, pp. 355-361, Oct. 1993.

- [6] P. Venet, F. Perisse, M. H. El-Husseini, and G. Rojat, "Realization of a smart electrolytic capacitor circuit," *IEEE Ind. Appl. Mag.*, vol. 8, no. 1,pp. 16–20, Jan./Feb. 2002.

- [7] O. Ondel, E. Boutleux, and P. Venet, "A decision system for electrolytic capacitors diagnosis," in Proc. of IEEE Power Electronics Specialist Conference (PESC), pp. 4360-4364, 2004.

- [8] E. C. Aeloiza, J. H. Kim, P. Ruminot, and P. N. Enjeti, "A Real Time Method to Estimate Electrolytic Capacitor Condition in PWM Adjustable Speed Drives and Uninterruptible Power Supplies," IEEE Power Electronics Specialists Conference (PESC), pp. 2867-2872, 2005.

- A. M. R. Amaral, and A. J. M. Cardoso, "A Simple Offline Technique for Evaluating the Condition of Aluminum-Electrolytic-Capacitors," IEEE Trans. Ind. Electron., vol. 56, no. 8, pp. 3230-3237, Aug. 2009.

- [10] A. M. R. Amaral, and A. J. M. Cardoso, "Estimating aluminum electrolytic capacitors condition using a low frequency transformer together with a dc power supply," in Proc. of IEEE ISIE, pp. 815-820, 2010.

- [11] K. Abdennadher, P. Venet, G. Rojat, J. M. Retif, and C. Rosset, "A Real-Time Predictive-Maintenance System of Aluminum Electrolytic Capacitors Used in Uninterrupted Power Supplies," IEEE Trans. Ind. Appl. vol. 46, no. 4, pp. 1644-1652, Jul./Aug., 2010.

- [12] J. M. Miller, C. W. Ayers, L. E. Seiber, and D. B. Smith, "Calorimeter evaluation of inverter grade metalized film capacitor ESR," in Proc. of IEEE ECCE, pp. 2157-2163, 2012.

- [13] M. Makdessi, A. Sari, and P. Venet, "Metallized polymer film capacitors ageing law based on capacitance degradation," ELSEVIER Microelectronics Reliability, vol. 54, pp. 1823-1827, 2014.

- [14] M. Makdessi, A. Sari, P. Venet, P. Bevilacqua, and C. Joubert, "Accelerated Ageing of Metallized Film Capacitors Under High Ripple Currents Combined With a DC Voltage," IEEE Trans. Power Electron., vol. 30, no. 5, pp. 2435-2444, May 2015.

- NICHICON CORPORATION. [15] "General Description of Aluminum Capacitors," Electrolytic [Online]. available: http://www.nichicon.co.jp/english/products/pdf/aluminum.pdf

- [16] RIPPLE CURRENT TESTER MODEL 11800/11801/11810, Chroma 2014. ATE Inc. [Online]. available: http://www.chromaate.com/File/DownLoad/42014

- [17] B. P. McGrath and D. G. Holmes, "A general analytical method for calculating inverter DC-link current harmonics," IEEE Trans. Ind. Appl. vol. 45, no. 5, Sep./Oct. 2009

- [18] D. Christen, U. Badstuebner, J. Biela, and J.W. Kolar, "Calorimetric power loss measurement for highly efficient converters," in Conf. Rec. of International Power Electronics Conference (IPEC), pp. 1438-1445, 2010.

- [19] H. Akagi, "Classification, Terminology, and Application of the Modular Multilevel Cascade Converter (MMCC)," IEEE Trans. Power Electron., vol. 26, no. 11, pp. 3119-3130, 2011.

- [20] H. Akagi, Y. Kanazawa, and A. Nabae, "Instantaneous reactive power compensators comprising switching devices without energy storage components," IEEE Trans. Ind. Appl., vol. IA-20, no. 3, pp. 625-630, 1984

- [21] W. T. McLyman, Transformer and inductor design handbook. New York: Marcel Dekker, 1988.

- [22] High Performance Vector Control Inverter FRENIC-VG Series, Fuji Electric Co., Ltd., Tokyo, Japan, 2014. [Online]. available: https://felib.fujielectric.co.jp/download/index.htm?site=global&lang=en

- [23] F700 Series Brochure, Mitsubishi Electric Automation, Inc. 2011. [Online]. available: https://us.mitsubishielectric.com/fa/en/support/technical-support/knowle

- dge-base/getdocument/?docid=3E26SJWH3ZZR-38-1348

- [24] [Online]. available: http://www.plexim.com/plecs

- [25] H. Fujita, S. Tominaga, and H. Akagi, "Analysis and design of a dc voltage-controlled static var compensator using quad-series voltage-source inverters," IEEE Trans. Ind. Appl., vol. 32, no. 4, pp. 970--977, 1996.

Kazunori Hasegawa (S'09-M'13) was born in Yokohama, Japan, in 1985. He received the B.S. degree in electrical engineering from Tokyo Metropolitan University, Tokyo, Japan, in 2007, and the M.S. and Ph.D degrees in electrical and electronic engineering from Tokyo Institute of Technology, Tokyo, Japan, in 2009 and 2012, respectively.

He was a Research Fellow of the Japan Society for the Promotion of Science for 2010-2012. From November 2010 to January 2011, he was a Visiting Scholar at Michigan State University, East Lansing, MI. He was an assistant professor at Tokyo Institute of Technology for 2012-2013. Since 2013, he has been an assistant professor at Kyushu Institute of Technology, Fukuoka, Japan.

His research interests include power conversion systems, reliability of power converters and components, and motor drives. Dr. Hasegawa was one of the recipients of the Student Paper Award of the 2010 IEEE International Power Electronics Conference-Sapporo.

Ichiro Omura (M'93) received his M.S. degree from Osaka University, Osaka in 1987 and Ph.D. degree in electrical engineering from the Swiss Federal

Institute of Technology (ETH), Zurich in 2001. From 1987 he had been with Toshiba Corporation, Kawasaki, Japan, engaging in research on power semiconductors including high voltage IGBTs, super-junction MOSFETs and GaN power devices. From 1996 to 1997, he was a visiting Researcher at ETH. Since 2008, he has been with the Kyushu Institute of Technology, Japan. He has published papers over 80 journals and conference papers, has filed more than 140 patent applications and holds more than 40 patents in the field of power semiconductors. He has been the director of next generation power electronics

research center in Kyushu Institute of Technology since 2014. His research interests are new power semiconductor device design, reliability testing with new monitoring system and advanced gate drive technology.

Shin-ichi Nishizawa (M'11) received his B.Eng., M.Eng., and Dr.Eng. in Chemical Engineering from Waseda University in 1989, 1991, and 1994, respectively. Then he worked at Waseda University

as the research associate. In 1996, he joined the Electrotechnical Laboratory (from 2001 AIST). Since 1998, he has worked on SiC bulk crystal growth and epitaxy, and promoted the research of semiconductor wafer process for advanced power devices. Since 2013, he has been a visiting professor at Kyushu Institute of Technology. He is a member of the Japan Society of Applied Physics, the Japanese Association for Crystal Growth, and IEEE (EDS and PELS). His research interests include semiconductor wafer technologies for power devices. More recently, his interests have been enlarged to the green

electronics for low carbonated and sustainable society. He is the author and coauthor of over 150

publications and 20 patents.