# Ultra High Speed Short Circuit Protection for IGBT with Gate Charge Sensing

| 著者                | Yuasa Kazufumi, Nakamichi Soh, Omura Ichiro |

|-------------------|---------------------------------------------|

| journal or        | 2010 22nd International Symposium on Power  |

| publication title | Semiconductor Devices & IC's (ISPSD)        |

| page range        | 37-40                                       |

| year              | 2010-06                                     |

| URL               | http://hdl.handle.net/10228/5795            |

## Ultra High Speed Short Circuit Protection for IGBT with Gate Charge Sensing

Kazufumi Yuasa, Soh Nakamichi and Ichiro Omura Kyushu Institute of Technology, 1-1 Sensui-cho, Tobata-ku, Kitakyushu-shi, Fukuoka, 804-8550, JAPAN Phone/Fax:+81-93-884-3268 e-mail: i349553k@tobata.isc.kyutech.ac.jp, omura@ele.kyutech.ac.jp

Abstract— Short circuit (SC) protection for IGBT has been crucial issue since IGBTs have become major switching devices for power electronics applications. According to the IGBT performance improvement, chip current density has been increased and the chip has become as thin as  $100\mu$ m. The high current density and thin wafer chip result in high temperature rising speed during SC condition and hence high speed protection scheme for IGBT is highly required. Conventional methods, such as sense IGBT configuration, have the response time of 5 micro second, for example, which is not sufficient to protect advanced IGBTs. In this paper, we propose a novel protection method with response time shorter than 1 micro second.

#### I. INTRODUCTION

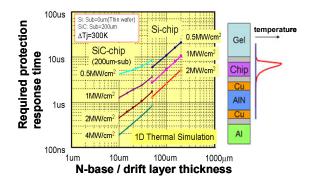

The higher power density and thinner wafer thickness trends in IGBT chips has reduced thermal capacity of the chips. And the junction temperature rising speed of IGBTs have become higher with the higher current flowed into the small chip. Therefore, the high speed protection method against SC destruction is required. Figure 1 shows calculated response time for the IGBT protection as functions of the N-base layer thickness of IGBT [1]. With the wafer thickness induction and the power density increase, the required response time become shorter than 2µsec. With improving IGBT performance, the required protection response time can be shorter.

The purpose of this paper is to propose the novel protection method with higher protection response than conventional method. Proposed method employs the gate charge sense circuit for detecting SC condition instead of the sense IGBT configuration. This method realizes to detect SC condition within very short period. In the following sections, the mechanism and the operating principle of proposed method will be illustrated. The proposed method is experimentally demonstrated.

Figure 1 Required protection speed for power devices[1].

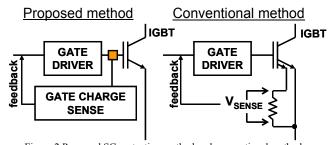

Figure 2 Proposed SC protection method and conventional method.

II. PROTECTION METHOD WITH GATE CHARGE SENSING

## A. Comparison with Proposed method and Conventional method

Proposed method and conventional method are shown in Fig. 2. Conventional method has had a sense IGBT to detect SC condition. A part of collector current flow to the sense resistor connected to sense IGBT and converted into the sense voltage  $V_{sense}$  which is to be proportional to the collector current for main IGBT. Although measuring  $V_{sense}$  is necessary to detect SC condition, the detecting accuracy and the response speed have been limited because of inproportionality of sense current to main current and the noise from the high current circuit next to the sense circuit.

Proposed method employs the gate charge sense circuit for detecting SC condition ([2]) instead of the sense IGBT

configuration ([3], [4]). Proposed method has significant advantage in the protection speed over the sense IGBT method because the gate charge sense circuit is embedded inside the gate driver which is separated from the major noise source, the high current main circuit. According to the gate charge sense circuit is separated from the main circuit, the protection function can be accomplished only in the low-voltage side. Table 1 compares characteristics of conventional method and proposed method.

|                        | Conventional                   | Proposed           |

|------------------------|--------------------------------|--------------------|

| Response time          | Over 5µsec                     | Shorter than 1µsec |

| Detect<br>mechanism    | Sense IGBT +<br>Sense Resistor | Gate charge        |

| Detector<br>connection | Main circuitry                 | Gate terminal      |

| Integration            | Difficult                      | Possible           |

Table1 Comparison of proposed method and conventional method.

#### B. Short circuit detection by gate charge

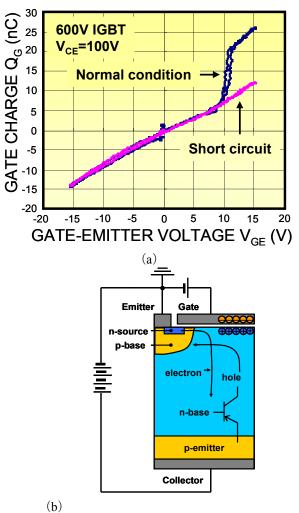

Figure 3(a) shows the measured gate charge during the SC condition in comparison with normal condition. It is found that the gate charge decreases under SC condition. And the difference of the charge between SC condition and normal condition is sufficiently large to detect the change of gate charge dynamically. Therefore, the SC condition can be detected by measuring the decrease of the gate charge than the normal condition. The detecting of the SC condition through the gate charge is very fast since the gate charge directly responds to the electric field inside the IGBT.

Figure 3(b) illustrates the mechanism of the gate charge reduction under SC condition. The gate charge is reduced due to no displacement current through  $C_{GD}$  and positive charge with holes accumulated in the gate insulator interface (Negative gate capacitance).

#### C. Protection circuit integration in gate driver

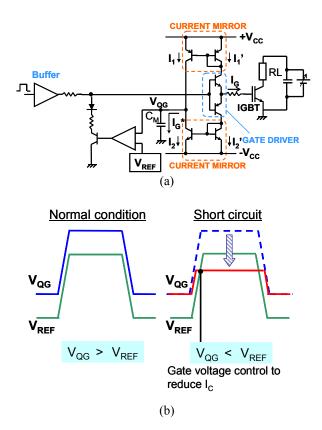

Figure 4(a) shows the proposed protection circuit embedded in the gate driver. The circuit includes the current mirror circuits connected to gate drive transistors to attain the mirror circuit current ( $I_G^*$ ) equivalent to the gate current ( $I_G$ ) flow through the gate terminal of IGBT. Precise operation of the circuit is explained as follows. The gate drive transistor current  $I_1$ ,  $I_2$  equal the mirror current  $I_1$ ' and  $I_2$ ' with the current mirror circuit and hence  $I_G^*$  are equal to  $I_G$ . Since  $I_G^*$ flows into  $C_M$ , the voltage across the capacitor  $V_{QG}$  represents the gate charge of the IGBT. These relationship are shown as follows,

$$I_1 = I_1' \ I_2 = I_2' (1)$$

$$I_G = I_G^* = I_2 - I_1 (2)$$

Figure 3 (a) Measured Gate charge  $Q_G$  for short circuit condition and normal condition. (b) The mechanism of the reduction of gate charge.

Measuring  $V_{QG}$  realizes to detect the gate charge  $(Q_G)$  changes due to mirror circuit current  $I_G^*$  (= $I_G$ ) equals to the time differential of the gate charge  $Q_G$  and,  $Q_G$  is equal to the product of  $V_{QG}$  and  $C_M$ . These relationship are shown as follows,

$$I_G = I_G^* = \frac{dQ_G}{dt} \quad (3)$$

$$Q_G = C_M V_{OG} \quad (4)$$

The relationship between  $V_{QG}$  and a predetermined referential voltage  $V_{REF}$  for normal and SC condition are shown in Fig. 4(b).  $V_{REF}$  is a function of gate voltage  $V_{GE}$ .  $V_{REF}$  is determined to be slightly lower than  $V_{QG}$  under normal condition. According to the gate charge is reduced under SC condition like the above-mentioned Fig. 3(a), this relationship is reversed.

When the comparator detect  $V_{QG}$  becomes lower than  $V_{REF}$ , the protection circuit starts to reduce the gate voltage through a transistor which is driven by the signal of the comparator.

Figure 4 (a) Protection circuit embedded in the gate driver of proposed method. (b) The relationship between  $V_{QG}$  and a referential voltage  $V_{REF}$  for normal and SC condition.

#### III. EXPERIMENT AND RESULT

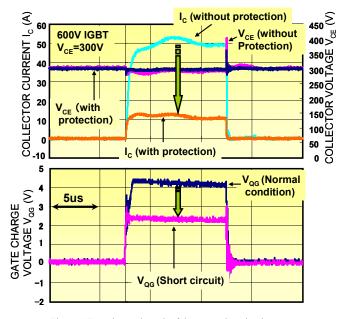

The circuit is experimentally demonstrated for 10µsec single pulse measurement using an IGBT with rated current of 10A and successfully reduced the collector current during SC condition as shown in Fig. 5. This experiment was performed under following conditions, (1) without the protection circuit under SC condition, (2) with the protection circuit under SC condition, (3) influence of the protection circuit existence to the gate waveform under normal condition. RL is  $30\Omega$  during normal condition.

#### (1) Without the protection circuit under SC condition High collector current up to 50A is flowed to the collector of IGBT.

#### (2) With the protection circuit under SC condition

The collector current was reduced due to the gate voltage ( $V_{GE}$ ) reduced by the protection circuit. The lower figure in Fig. 5 shows  $V_{QG}$  during SC condition in comparison with normal condition.

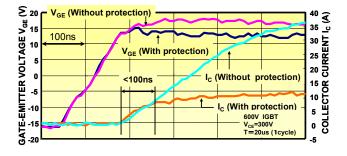

The protection circuit reduced the collector current as soon as the SC condition occurs. Figure 6 shows turn-on transient in the SC protection waveforms in comparison with those without protection circuit. The very high speed response within 1 micro second was demonstrated.

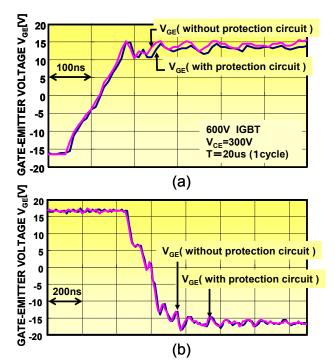

### (3) Influence of the protection circuit existence to the gate waveform under the normal condition

Figure 7 shows turn-on and turn-off transient of the gate voltage under the normal condition with / without protection circuit. The gate voltage waveform was not influenced by the existence of the protection circuit at normal condition. This shows that the protection circuit will not affect the switching characteristics of the IGBT to be protected.

Figure 6 Gate voltage and collector current at turn-on under SC condition.

#### IV. SUMMARY

We experimentally demonstrated the new protection method with gate charge sensing and successfully protected the IGBT under SC condition. Proposed method achieved higher protection response than conventional method. The response time of proposed method was much shorter than 1µsec which enables to protect future thin wafer high current density IGBTs.

Figure 7 (a) Gate voltage with protection circuit and gate voltage withozut protection circuit during turn-on. (b) Gate voltage with protection circuit and gate voltage without protection circuit during turn-off.

#### REFERENCES

- Omura, Presentation at "ECPE Workshop on Power Electronics Research & Technology Roadmaps" -Copenhagen, Denmark, September 2007

- [2] Omura, "IGBT Negative Gate Capacitance and Related Instability Effects", IEEE ED-letters, Vol. 18, No. 12, 1997.

- [3] E. Motto et al. "Large Package Transfer Molded DIP-IPM," Proc. of IAS '08, pp. 1-5, 2008

- [4] M, Kudoh et, al. "Current sensing IGBT for future intelligent power module," Proc. of ISPSD' 96, pp 303-306, 1998