# A SINGLE-PHASE RECTIFIER WITH RIPPLE-POWER DECOUPLING AND APPLICATION TO LED LIGHTING

A Thesis

by

## BO TIAN

## Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

| Chair of Committee, | Robert S. Balog          |

|---------------------|--------------------------|

| Committee Members,  | Prasad Enjeti            |

|                     | Shankar P. Bhattacharyya |

|                     | Ben Zoghi                |

| Head of Department, | Miroslav M. Begovic      |

May 2015

Major Subject: Electrical Engineering

Copyright 2015 Bo Tian

#### ABSTRACT

In recent years, Light-Emitting-Diode (LED) is widely used in lighting applications for its high efficacy and high reliability. However, the rectifier, which is required by the LEDs to convert the AC power from the grid into DC power, suffers from low-reliability caused by the filtering capacitor. In order to fully utilize the long operational hours of the LEDs, this thesis proposes a rectifier that has improved reliability by adding a ripple-port to eliminate the non-reliable electrolytic capacitor. The ripple-port is capable of decoupling the ripple-power inherited in a single-phase rectifier, which enables using the reliable film capacitor to replace the electrolytic capacitor. To guarantee that the ripple-port can effectively decouple the ripple-power, a closed-loop control scheme is designed and implemented in a digital controller. Simulation and experimental results show that the proposed rectifier can reduce the required capacitance by 70%, which results in a 60% increase in lifetime. The proposed ripple-port circuit can be considered as an add-on module to be integrated into the rectifiers used in applications that require long lifetime. A detailed analysis of the efficiency, cost and reliability of applying the ripple-port in LED lighting applications supports the feasibility of the proposed circuit.

## ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my advisor and committee chair, Dr. Balog, for his consistent technical guidance, mentorship and support throughout my graduate study.

I would like to thank my committee members: Dr. Enjeti, Dr. Bhattachaya and Dr. Zoghi for their time and concern.

I also want to thank my fellow research students in the Renewable Energy And Power Electronics Research Laboratory at Texas A&M University and especially Souhib Harb, Haiyu Zhang, Xiao Li and Zhan Wang for their assistance and encouragement for my thesis.

Last but not least, I would like to thank my mother and father for their continuous love and support.

## TABLE OF CONTENTS

| ABSTRACT                                                                                                                           | ii                         |

|------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| ACKNOWLEDGEMENTS                                                                                                                   | iii                        |

| TABLE OF CONTENTS                                                                                                                  | iv                         |

| LIST OF FIGURES                                                                                                                    | vi                         |

| LIST OF TABLES                                                                                                                     | ix                         |

| CHAPTER I INTRODUCTION                                                                                                             | 1                          |

| <ul> <li>1.1 Introduction: Need of rectifier in AC/DC power conversion and LED light</li> <li>1.2 Fundamental challenges</li></ul> | 4<br>4<br>5<br>7<br>8      |

| CHAPTER II REVIEW OF RIPPLE POWER IN AC/DC CONVERTER                                                                               | 10                         |

| <ul> <li>2.1 Introduction</li> <li>2.2 Review of existing solutions</li></ul>                                                      | 11<br>11<br>12<br>13<br>14 |

| CHAPTER III ANALYSIS AND CONTROL THEORY OF RIPPLE-PORT                                                                             | 18                         |

| <ul> <li>3.1 Introduction</li></ul>                                                                                                | 20<br>22<br>22<br>23<br>27 |

|                                                                                                                                    |                            |

| 3.5.2 Phase-locked-loop                                                            |    |

|------------------------------------------------------------------------------------|----|

| 3.5.3 Dynamic response analysis                                                    |    |

| 3.6 Conclusion                                                                     |    |

|                                                                                    |    |

| CHAPTER IV DESIGN OF A RIPPLE-PORT INTEGRATED RECTIFIER                            | 35 |

| 4.1 Introduction                                                                   | 25 |

|                                                                                    |    |

| 4.2 Selection of the decoupling capacitor                                          |    |

| 4.3 Digital controller implementation                                              |    |

| 4.3.1 Voltage and current controllers: 2 <sup>nd</sup> order PR and PID controller |    |

| 4.3.2 Type-2 2 <sup>nd</sup> order PLL                                             | 41 |

| 4.3.3 PR controller                                                                |    |

| 4.4 Efficiency analysis of the ripple-port                                         |    |

| 4.5 Simulation results                                                             |    |

| 4.6 Experimental results                                                           |    |

| 4.7 Conclusion                                                                     | 66 |

| CHAPTER V APPLYING RIPPLE-PORT TO LED APPLICATIONS                                 | 67 |

| 5.1 Introduction                                                                   | 67 |

| 5.2 Common-used circuit topologies for offline LED driver                          | 67 |

| 5.3 Double-line frequency flickers in offline LED lighting application             |    |

| 5.4 Reliability issue of conventional offline LED lighting application             |    |

| 5.5 Comparison between ripple-port configuration and conventional solution         |    |

| 5.5.1 Capacitor size and cost                                                      |    |

| 5.5.2 Efficiency                                                                   |    |

| 5.6 Conclusion                                                                     |    |

|                                                                                    |    |

| CHAPTER VI CONCLUSION AND FUTURE WORK                                              | 79 |

| REFERENCES                                                                         | 87 |

|                                                                                    |    |

## LIST OF FIGURES

| Pag                                                                                                                        | ;e |

|----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1 Block diagram of a rectifier                                                                                      | 1  |

| Figure 2 Comparison between various lighting technologies taken from [3]                                                   | 2  |

| Figure 3 Growth of LED revenue                                                                                             | 3  |

| Figure 4 Waveform of input voltage, current and power of a single-phase rectifier                                          | 4  |

| Figure 5 Block diagram of a practical single-phase rectifier                                                               | 5  |

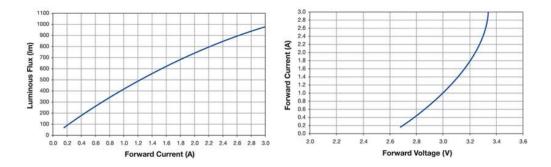

| Figure 6 (a) Luminous v.s. Current (b) Voltage v.s. Current characteristic of LED                                          | 6  |

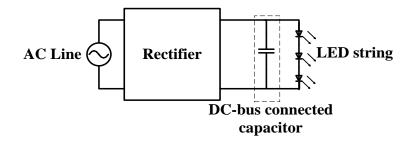

| Figure 7 Using dc-bus connected capacitor in LED driver                                                                    | 6  |

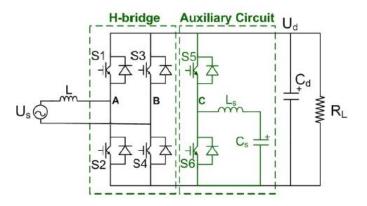

| Figure 8 Example of dc-bus connected ripple-power filter taken from [32]12                                                 | 2  |

| Figure 9 Waveforms of output voltage, output current and input current taken from [38]                                     | 4  |

| Figure 10 Waveforms of input voltage and averaged input current taken from [38]14                                          | 4  |

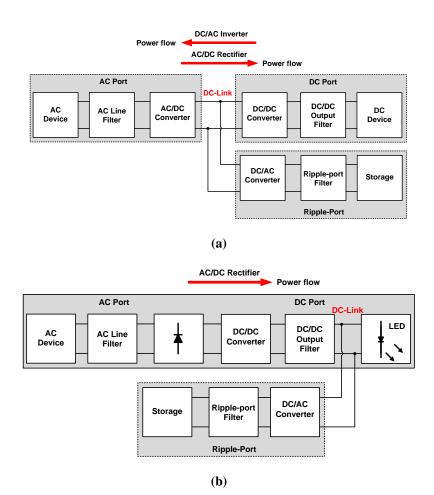

| Figure 11 Block diagram of (a) A generalized converter with ripple-port power decoupling (b)LED driver with ripple-port1   | 5  |

| Figure 12 A generalized block diagram of an AC/DC system with the ripple-port10                                            | 6  |

| Figure 13 Waveforms of input power, ripple-power and output power<br>of ripple-port integrated rectifier taken from [13]17 | 7  |

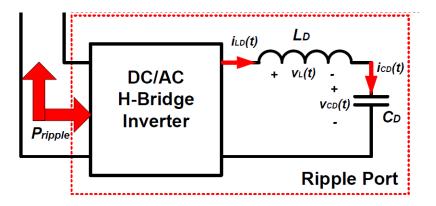

| Figure 14 Circuit diagram of the ripple-port taken from [41]                                                               | 9  |

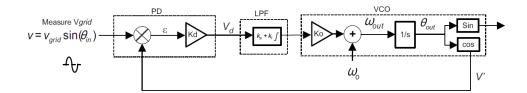

| Figure 15 Diagram of the proposed control scheme                                                                           | 1  |

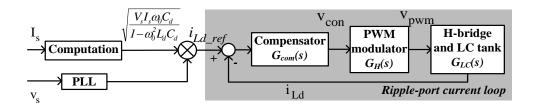

| Figure 16 Small-signal model for ripple-port current loop                                                                  | 2  |

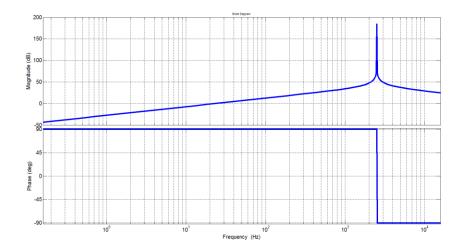

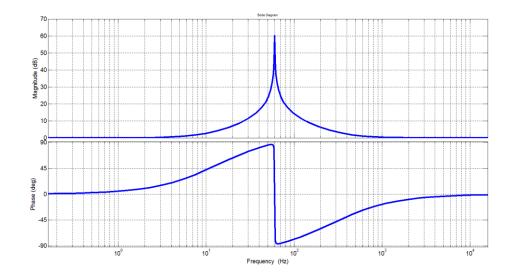

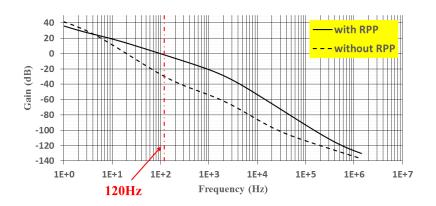

| Figure 17 Bode plot of the control-to-output transfer function of Ripple-port2                                             | 3  |

| Figure 18 Bode plot of a PR controller2                                                                                    | 5  |

| Figure 19 Bode plot of a PR controller with phase compensation                                                             | 6  |

| Figure 20 Bode plot of the loop gain of the ripple-port current loop                       | 26 |

|--------------------------------------------------------------------------------------------|----|

| Figure 21 Block diagram of the feedforward control                                         | 28 |

| Figure 22 Phase lock loop basic structure, taken from [51]                                 | 29 |

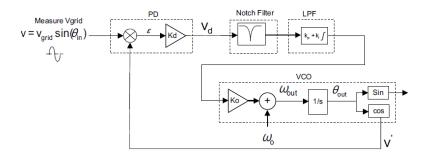

| Figure 23 Phase lock loop with notch filter, taken from [51]                               | 29 |

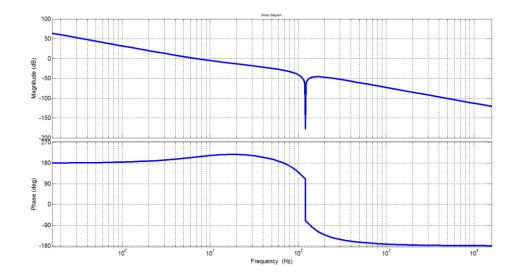

| Figure 24 Phase lock loop open-loop gain                                                   | 31 |

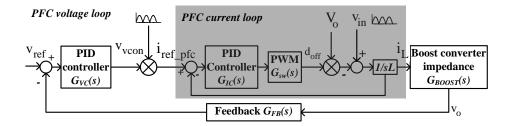

| Figure 25 Small-signal model of a Boost PFC regulator                                      | 32 |

| Figure 26 Open-loop gain of the voltage loop: K <sub>FB</sub> =0.01; K <sub>c</sub> =0.42; | 33 |

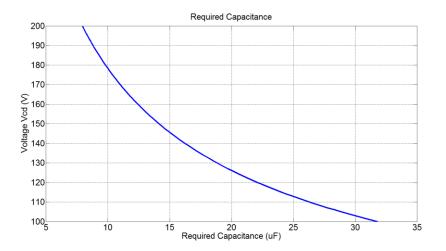

| Figure 27 Capacitor voltage v.s. required capacitance                                      | 36 |

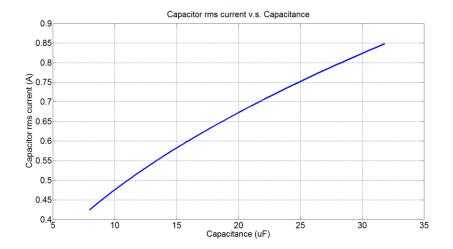

| Figure 28 Capacitor RMS current v.s. capacitance                                           | 37 |

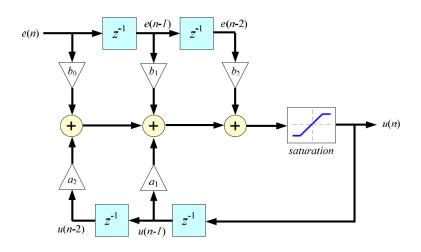

| Figure 29 Block diagram of 2p2z controller                                                 | 38 |

| Figure 30 Block diagram of the control loops in a ripple-port integrated rectifier         | 39 |

| Figure 31 Circuit model of the Ripple-port for loss analysis                               | 43 |

| Figure 32 Current and voltage waveform of the ripple-port                                  | 44 |

| Figure 33 circuit diagram of conducting devices                                            | 45 |

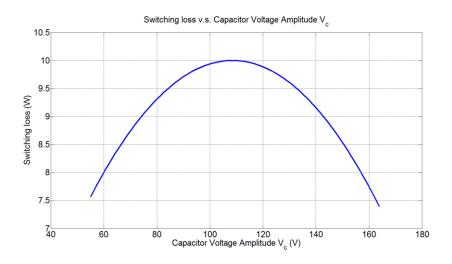

| Figure 34 Switching loss v.s. Capacitor voltage amplitude                                  | 49 |

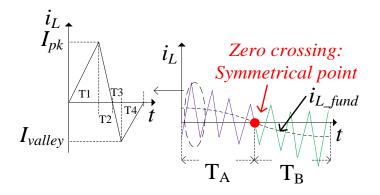

| Figure 35 Inductor current waveform of the ripple-port                                     | 51 |

| Figure 36 Equivalent circuit for calculating conduction loss of the H-bridge               | 52 |

| Figure 37 Effective current for voltage sources loss calculation                           | 52 |

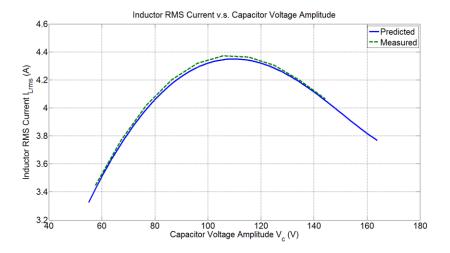

| Figure 38 Comparison between the measured $I_{L_{rms}}$ and calculated $I_{L_{rms}}$       | 54 |

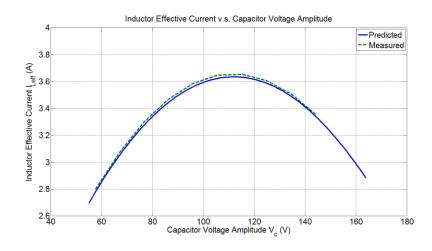

| Figure 39 Comparison between the measured $I_{L_{eff}}$ and calculated $I_{L_{eff}}$       | 55 |

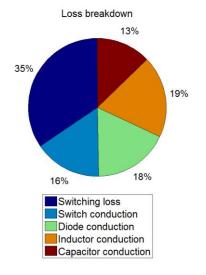

| Figure 40 Loss breakdown                                                                   | 56 |

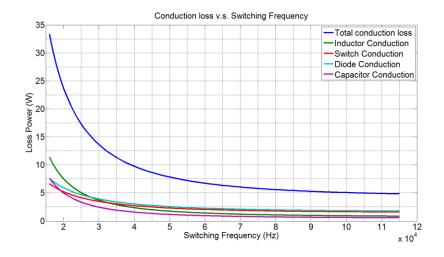

| Figure 41 Correlation between conduction loss and switching frequency                      | 57 |

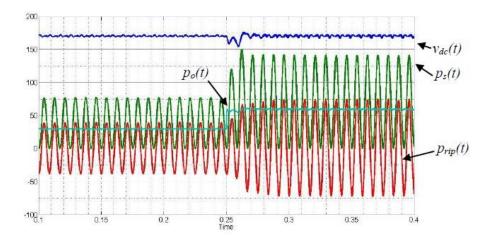

| Figure 42 Simulation results - input, output, and ripple power waveforms                         |

|--------------------------------------------------------------------------------------------------|

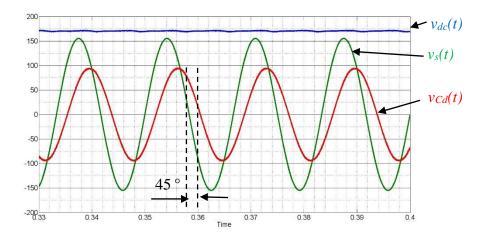

| Figure 43 Input, output voltages, and the voltage across the decoupling capacitor59              |

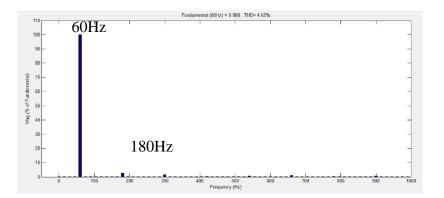

| Figure 44 Calculated FFT of the Input Current (in dB)60                                          |

| Figure 45 Load dynamic response, from half load to full load60                                   |

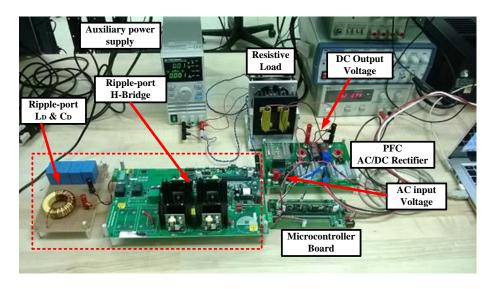

| Figure 46 Hardware prototype of a 60W single-phase rectifier with ripple-port61                  |

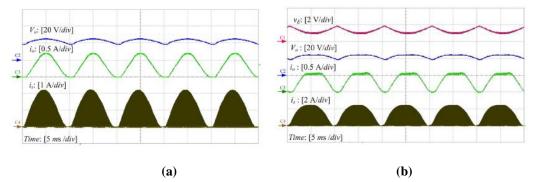

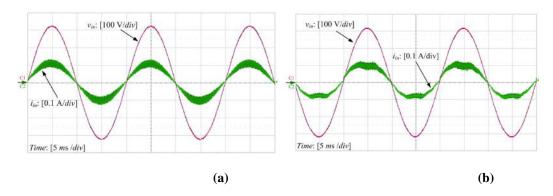

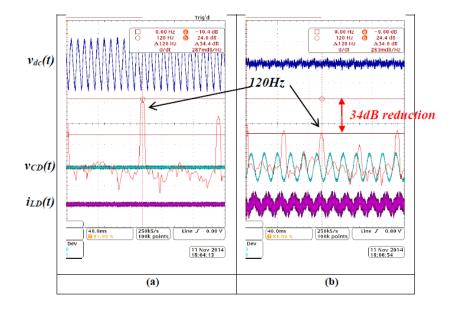

| Figure 47 Experimental results: (a) Ripple-port disabled (b) Ripple-port enabled62               |

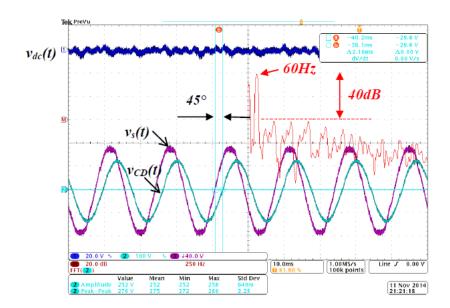

| Figure 48 Phase-shift between input voltage and capacitor voltage to achieve ripple-cancellation |

| Figure 49 Harmonic content of the input voltage and input current to the ripple-port 64          |

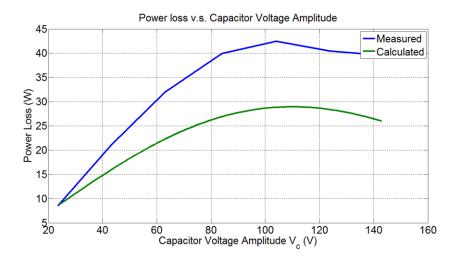

| Figure 50 Comparison of power loss between measured value and calculated value65                 |

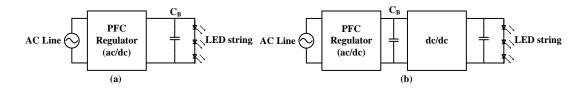

| Figure 51 (a) Single- and (b) Two-stage architecture used for LED drivers67                      |

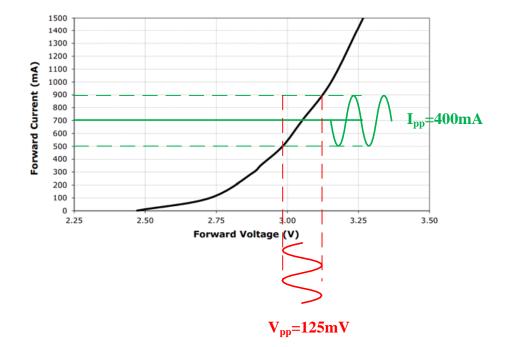

| Figure 52 Correlation between current ripple and voltage ripple of<br>Cree XLamp XP-G LEDs       |

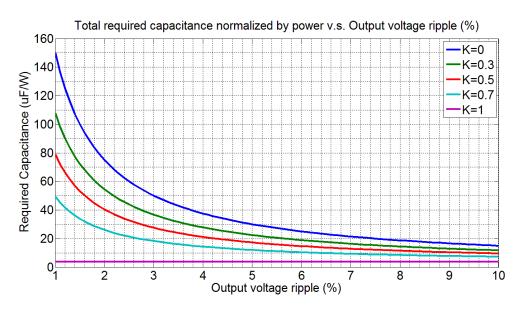

| Figure 53 Normalized required capacitance v.s output voltage ripple74                            |

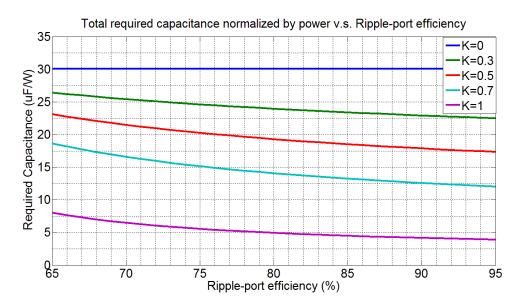

| Figure 54 Normalized required capacitance v.s Ripple-port efficiency75                           |

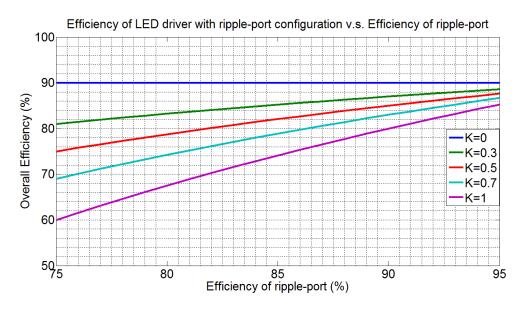

| Figure 55 Overall Efficiency v.s. Ripple-port Efficiency77                                       |

## LIST OF TABLES

Page

| Table 1 PFC controllers in continuous and discrete form                           |

|-----------------------------------------------------------------------------------|

| Table 2 PLL controllers in continuous and discrete form                           |

| Table 3 PR controllers in continuous and discrete form                            |

| Table 4 Conducting devices in different periods within a switching cycle       45 |

| Table 5 Specifications of the ripple-port for loss analysis                       |

| Table 6 AC/DC rectifier with ripple-port simulation parameters                    |

| Table 7 Component values and operating conditions for the hardware prototype62    |

#### CHAPTER I

#### INTRODUCTION

1.1 Introduction: Need of rectifier in AC/DC power conversion and LED lighting

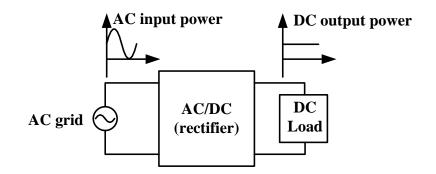

AC/DC power conversion is required by many industrial applications, home appliances and consumer electronics to take the pulsating power from ac system, e.g. grid, and to supply constant DC power to the load. An AC/DC converter, also referred as a rectifier, is the electrical device to perform AC/DC conversion or rectification, shown as Figure 1. Since the full amount of power is processed by the rectifier, the efficiency and reliability of the rectifier is of great importance.

Figure 1 Block diagram of a rectifier

One of the important applications of rectifier is providing power conversion for lighting. In 2012, electricity used for lighting accounts for 17% of the total U.S. electricity consumption [1]. Among the various lighting technologies, the solid-state lighting, i.e. LED, is proven to have superior efficiency and reliability as well as more environmental-

friendly [2]. Figure 2 shows the comparison between the common lighting technologies in terms of energy efficiency and lifetime.

Figure 2 Comparison between various lighting technologies taken from [3]

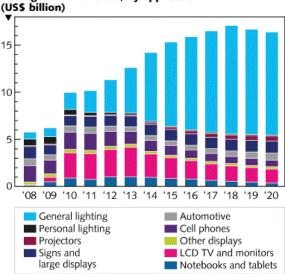

With the advance of semiconductor technology in recent years, the amount of LED installed in general lighting applications has been rapidly increased [4, 5]. The revenue growth of the LED market is shown in Figure 3.

Packaged LED revenue, by application (US\$ billion)

Figure 3 Growth of LED revenue

Source: Status of the LED industry report, August 2012, Yole Development

Unlike conventional incandescent light bulbs, which can be directly connected to AC line, LED requires an AC/DC converter to be driven by the AC main power since it is a DC device. Usually a switching converter is designed as the driver and assembled in the lighting fixture together with LEDs to achieve high efficiency, high power density and high control accuracy [6]. To justify the high manufacturing cost of the LED, the driver circuit, which is a rectifier with some auxiliary circuits, is required to have high efficiency and high reliability to achieve superior performance [7].

#### 1.2 Fundamental challenges

1.2.1. Double-line frequency ripple in single-phase systems

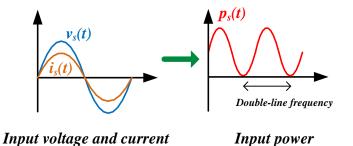

Figure 4 Waveform of input voltage, current and power of a single-phase rectifier

For general lighting applications, LED driver is an ac/dc converter, which is connected to the AC mains. Therefore, high power factor and low total harmonic distortion (THD) of input current are mandatory design requirements [8]. The single-phase PFC (Power Factor Correction) regulator is the most commonly used topology for offline power supplies to meet these requirements [9]. However, the single-phase AC/DC PFC regulator suffers from the inherent double-line frequency power ripple, demonstrated by Figure 4. Since the input voltage  $v_s(t)$  and input current  $i_s(t)$  are sinusoidal and in phase with each other, the input power  $p_s(t)$  is pulsating in a frequency twice as the line frequency, which is referred as the double-line frequency.

Eq.(1) shows that the input power has a constant term, which represents the average power, and a sinusoidal term, which represents the ripple power. Ideally, only the

average power should be delivered to the load while the ripple power should be decoupled by the rectifier.

$$p_{s}(t) = v_{s}(t)i_{s}(t) = V_{s}\sin(\omega_{0}t)I_{s}\sin(\omega_{0}t) = \frac{V_{s}I_{s}}{2} - \frac{V_{s}I_{s}}{2}\cos(2\omega_{0}t)$$

(1)

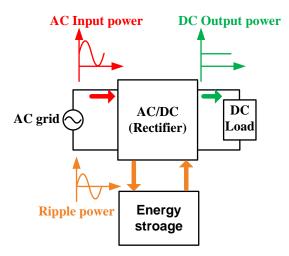

In practical, the rectifier must have an energy storage to make it possible that the output power can remain constant while the input power pulsates. Therefore, the rectifier shown in Figure 1 must be modified to the circuit shown in Figure 5.

Figure 5 Block diagram of a practical single-phase rectifier

## 1.2.2. Need of ripple-free current by LED

LED is a current-driven device and thus the luminous of the LED is determined by current following through it. In addition, the LED has a non-resistive characteristic that the current is not a linear function of the voltage. The typical luminous v.s. current curve and V/I characteristic of a LED are shown in Figure 6.

Figure 6 (a) Luminous v.s. Current (b) Voltage v.s. Current characteristic of LED

When using the single-phase rectifier to drive a LED load, the ripple power introduces a certain amount of ripple on both the voltage and current of the LED, which causes the luminous varying. In other words, the LED flickers in the double-line frequency, which can be harmful for human eyes [10, 11].

The most common practice to reduce the flicker is to connect a capacitor in parallel with the LED string to filter the ripple power, shown as Figure 7. The filtering capacitor is referred as the dc-bus connected capacitor as it is connected to the dc output directly.

Figure 7 Using dc-bus connected capacitor in LED driver

The characteristic of a capacitor, shown in Eq.(2), shows that the amount of ripple power filtered by the capacitor  $P_c$  is related the capacitance C, the average voltage  $V_{dc}$ , the line frequency  $\omega_0$  and the amplitude of voltage ripple  $V_{ripple}$ .

$$C = \frac{P_C}{\omega_0 V_{dc} V_{ripple}} \tag{2}$$

The characteristic of the capacitor indicates that for a finite value of C, there will be a certain amount of  $V_{ripple}$  across the LED. Unfortunately the V-I characteristic of the LED show in Figure 6 suggests that the voltage ripple leads to a larger amount of current ripple. To avoid visible flickers, LED drivers usually require a very large dc-bus connected capacitor to suppress the voltage ripple.

1.2.3. Reliability of rectifier to match the lifetime expectancy of LED

In practical, the selection of the filtering capacitor needs to include the consideration of size and cost. The comparison between different types of capacitors in [12] suggests that electrolytic capacitor enjoys the advantage of high power density (power/volume) and low cost-per-joule, which makes it very popular for LED drivers in the industry. However, the electrolytic capacitor has very short lifetime compared to the LEDs and other components in the driver, which is a severe reliability problem that limits the lifetime of the LED light bulb. Even worse, as the lifetime of the electrolytic capacitor degrades as the temperature rises, the limitation is exacerbated when the capacitor operates under the high-temperature environment in the lighting fixture because the LED itself dissipates a significant amount of heat.

#### 1.3 Research objective

The objective of this research is to propose a high reliability rectifier design by using an alternative approach to filter the ripple-power. Apparently it is difficult to achieve high reliability with the conventional bus-connected capacitor. Instead of using a dc-bus connected capacitor to directly filter the double-line frequency at the dc-link, a ripple-port circuit can be added to the rectifier to decouple the ripple-power from the input-to-output power path. This approach enables the capacitor having arbitrary voltage swing since it is detached from the load. Consequently the required capacitance can be significantly reduced and high-reliability film capacitor can replace the electrolytic capacitor.

Although the ripple-port concept had been proposed in [13], the control strategy has not been investigated and hardware experimental results are needed to verify the feasibility of this concept. This research is to design a control scheme that the ripple-port can always effectively decouple the ripple-power even when the load has changed. A current-mode control of the ripple-port together with a feed-forward control between the rectifier and ripple-port is proposed and proven to improve the load dynamic response. Also, a 60W hardware prototype of a ripple-port integrated rectifier is built to verify the control scheme and the ripple-port topology. Loss model of the ripple-port is also built to analyze the efficiency and study the tradeoff between efficiency and reliability of the ripple-port configuration.

## 1.4 Thesis outline

Chapter I gives an overview of the AC/DC converters and the inherent ripplepower problem in the single-phase rectifier. It is stated that the fast growth of solid-state lighting in recent years introduces the necessity to improve the reliability of the rectifier used in LED drivers. The objective of the research is hence focused on designing a highreliability rectifier.

Chapter II reviews the previous works on eliminating the electrolytic capacitor in the rectifier design. The ripple-port is introduced and a comparison is drawn against the previous solutions. The design challenges of the ripple-port is also introduced in this section.

Chapter III gives in-depth description of the control objectives of the ripple-port and the control scheme to achieve ripple-power decoupling. Small-signal model is built to study the stability of the proposed control scheme. The controller design is also discretized to enable the implementation in digital controller.

Chapter IV introduces the design example of a ripple-port integrated rectifier. The chapter introduces how to design component values and how to implement the proposed control scheme in a TMS320F28035 digital-signal-processor (DSP). Loss modelling is included to study the efficiency. Simulation and experimental results are included to verify the efficiency analysis and the effectiveness of the ripple-port.

Chapter V investigates the application of the ripple-port to LED lighting.

Chapter VI gives a general conclusion of the work and discusses the future work.

#### CHAPTER II

#### **REVIEW OF RIPPLE POWER IN AC/DC CONVERTER**

### 2.1 Introduction

All single-phase power systems, including the single-phase rectifier, are characterized by power that flows at twice the fundamental frequency of the voltage and current. Often called double-frequency power ripple, it is inherent and must be filtered within the rectifier system to prevent it from appearing on the rectifier DC output where it would deteriorate the voltage ripple performance of the system. Conventional approaches use large electrolytic capacitors (often referred to as E-caps) at the DC output to filter this 120Hz (100Hz) power ripple. This is such a common practice that datasheets for rectifier-grade E-caps specifically include performance characteristics at 120Hz. The energy-density and cost-per-joule make aluminum electrolytic capacitors very popular. While this technique may be acceptable for some low-cost applications, for applications that require long service life, such as photovoltaic (PV) inverters or LED lighting drivers, it represents a severe reliability problem that limits the lifetime of the power electronics converter [14-19]. This limitation is exacerbated when considering that the capacitors are exposed to uncontrolled and harsh thermal environments when co-located with the PV module in a micro-inverter or the LED chip in a lighting fixture. While derating techniques are well known, this ultimately adds costs as it results in an over-designed system. An alternative is to consider topologies and controls that enable inherently more reliable capacitors, proven to work under harsh and uncontrolled operating conditions, can be used instead of E-caps.

Film capacitors are known to have a long operating lifetime and high reliability due to self-healing properties and no aqueous electrolyte to dry out over time. As such, they are currently the best replacement option available in the market as a high reliability energy storage device [20]. However, they are more expensive compared to electrolytic capacitors on a microfarad basis, thus preventing a cost-effective simple component substitution approach to reliability improvement. A more elegant and fundamental solution is needed.

There are various ways to filter the double-line frequency ripple, the existing solutions can be categorized into three types, which will be introduced in this chapter.

2.2 Review of existing solutions

2.2.1 Passive ripple-power filter

Magnetic energy storage, e.g. an inductor, can be connected in series with the load to filter the double-line frequency ripple. However, the large volume and weight makes this solution unattractive in practical design [21]. DC-bus connected capacitor, shown as Figure 7, is the most popular way to filter the double-line frequency ripple. The required capacitance, however, is much higher than the minimum required capacitance because only a small voltage ripple is allowed due to the direct connection of the capacitor and the DC load [22].

## 2.2.2 Two-stage cascading architecture

In order to achieve good input current regulation and output voltage regulation at the same time, there are numerous attempts to combine a Power Factor Correction stage and a conventional dc/dc switching converter to form a two-stage architecture [23-30]. The two-stage PFC can achieve very good input current quality, low output ripple and fast dynamic response. Yet the tradeoffs are increased components count and decreased efficiency.

### 2.2.3 Bus-connected ripple-power filter

Numerous ripple-power filtering techniques using active circuits to decouple the energy-storage component from the dc-link had been proposed to improve the reliability of the single-phase rectifier [31-35]. The energy-storage component can be either a capacitor or an inductor and the former is favored in most proposed circuits because of its higher power density. Figure 8 shows the circuit diagram of an example of dc-bus connected filter.

Figure 8 Example of dc-bus connected ripple-power filter taken from [32]

The limitation of dc-bus connected ripple-power filter is the limited voltage swing on the decoupling capacitor and a certain amount of capacitance is still required across the dc-bus. Furthermore, the dc-bus connected ripple-power filter in [32] operates in openloop with pre-programed duty ratio, which may enable the ripple-power in the filter drifting from the desired value when the inductor and capacitor has thermal variation. Therefore, a closed-loop control of the ripple-power filter is of great importance.

### 2.2.4 Input current harmonics injection

An alternative to circuit-topology modifications is to modify the control scheme of the single-phase rectifier to reduce the amplitude of the double-line frequency ripple. The ripple power is reduced by intentionally distorting the input current and sacrifice the power factor [23, 36, 37]. In [38], the input current harmonics injection had been proposed to reduce the ripple-power at the input of the single-phase rectifier. Figure 9 and Figure 10 the comparison of typical waveforms between a conventional single-phase PWM rectifier and a single-phase PWM rectifier using input current harmonics injection. The harmonics injection reduces the peak-to-average value of the output current without the need for extra circuitries. However, this method leads to direct tradeoffs between input current THD and output current ripple. Therefore, it is difficult to be adopted in applications required both low input current THD and tight output regulation.

Figure 9 Waveforms of output voltage, output current and input current taken from [38] (a)without harmonics injection (b)with harmonic injection

Figure 10 Waveforms of input voltage and averaged input current taken from [38] (a)without harmonics injection (b)with harmonic injection

### 2.3 Ripple-port configuration

In order to achieve minimum required capacitance while preserving unity power factor and low input current THD, ripple-port configuration is proposed in [13]. Without loss of generality, the proposed converter topology is based on the commonly used two-stage converter with a third port added to perform the ripple cancellation. One appreciates, however, that any topology can be used as long as a DC-link exists. Figure 11(a) illustrates the generalized block diagram of the ripple-port concept that can be applied for both DC/AC and AC/DC single-phase power conversion. In the DC/AC inverter applications, a DC power source, for example a PV panel, is used to supply power to a passive AC load or the AC grid. On the other hand, for the AC/DC rectifier applications, an AC power source is used to supply a DC load, for example a battery or an LED lighting system, and the system can be redrawn as in Figure 11 (b).

Figure 11 Block diagram of (a) A generalized converter with ripple-port power decoupling (b)LED driver with ripple-port

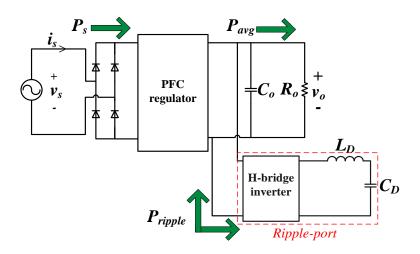

A generalized block diagram of an AC/DC rectifier system with the ripple-port is shown in Figure 12. It shows that the proposed ripple-port decoupling technique does not depend on the used AC/DC topology as long as the DC-link voltage can be regulated. The AC/DC converter for offline application is often referred as PFC regulator since it provides Power Factor Correction. The commonly used Boost PFC converter will be considered in this paper due to its numerous advantages including, simplicity, low components count and low conducted electromagnetic interference (EMI) [39, 40], and is well suited for LED lighting applications.

Figure 12 A generalized block diagram of an AC/DC system with the ripple-port

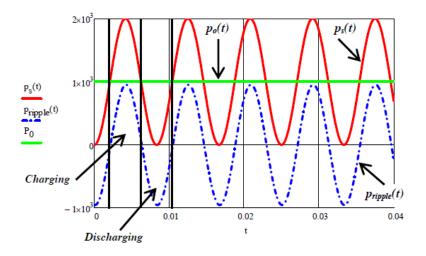

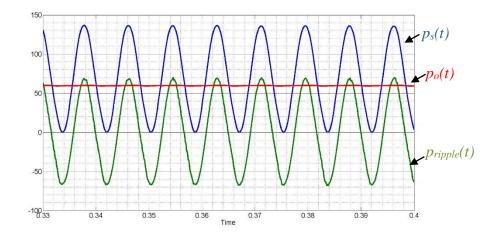

The waveforms of power shown in Figure 13 demonstrates the concepts of ripplepower decoupling. The AC component of the input power,  $p_{ripple}(t)$ , is processed by the ripple-port and only the average component of the input power is passed to the load. Since the ripple-port utilizes a capacitor, which is decoupled from the dc-link, to store energy, the capacitor allows arbitrary voltage swing and reduce the required capacitance, according to Eq.(2).

Figure 13 Waveforms of input power, ripple-power and output power of ripple-port integrated rectifier taken from [13].

## 2.4 Conclusion

The most common solutions for filtering the double-line frequency ripple in singlephase PWM rectifier had been reviewed. While the previous works demonstrate the effectiveness of ripple-power reduction, they bring certain tradeoffs in efficiency, input current THD or reliability. Ripple-port configuration is presented to provide an effective way to filter the double-line frequency ripple using the minimum required capacitance, which enables the replacement of the low-reliability electrolytic capacitor by film capacitor. The analysis and control theory will be presented in the proceeding chapter to understand the ripple-port configuration in depth.

#### CHAPTER III

#### ANALYSIS AND CONTROL THEORY OF RIPPLE-PORT

3.1 Introduction

At steady state, in order to have the ripple-port cancelling the double-line frequency ripple in the single-phase PWM rectifier, the power in the ripple-port must be equal to the ripple-component in the input power of the rectifier. The conditions when the ripple-port is able to cancel the double-line frequency ripple has been discussed in [13] and will be re-visited in section 3.2.

The conditions for ripple-power cancellation introduce the need of a closed-loop control scheme for the ripple-port to regulate the current or voltage, in both amplitude and phase, to avoid the power in the ripple-port drifting with the component imperfections, e.g. parasitic resistance, thermal variation.

This chapter proposes a modified Proportional Resonant (PR) controller to control the power in the ripple-port. Comparison between the PR controller and the conventional PI controller will be covered and demonstrates the advantages of the PR controller.

When being integrated into a single-phase PWM rectifier, the ripple-port needs to adjust the phase and amplitude of the reference signal in real-time to compensate the load and line variation in the rectifier. Therefore, a feed-forward control path from the rectifier to the ripple-port with phase-locked-loop is proposed and the improvement of dynamic response will be discussed. 3.2 Conditions for ripple-power cancellation

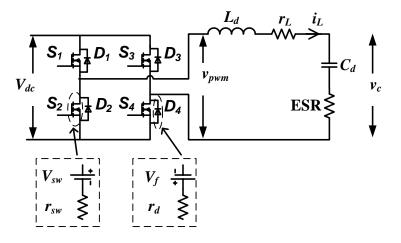

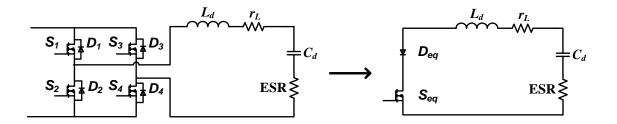

Figure 14 Circuit diagram of the ripple-port taken from [41]

The instantaneous power in the ripple-port can be expressed as the sum of the power in the inductor  $L_d$  and the capacitor  $C_d$ .

$$p_{rpp}(t) = i_{LD}(t)v_L(t) + i_{CD}(t)v_{CD}(t)$$

(3)

According to [41], the instantaneous power in the ripple-port can be re-written in terms of  $L_d$ ,  $C_d$ , the line frequency  $\omega_0$  and the amplitude of the voltage across the capacitor  $V_{CD}$ .

$$p_{rpp}(t) = \frac{V_{CD}^2 C_d \omega_0 (1 - \omega_0^2 L_d C_d)}{2} \sin(2(\omega_0 t + \phi))$$

(4)

According to Eq. (1), the ripple-power can be written as:

$$p_{ripple}(t) = \frac{V_s I_s}{2} \cos(2\omega_0 t) = P_{o_avg} \cos(2\omega_0 t)$$

(5)

where  $P_{o_avg}$  represents the value of average output power.

In order achieve ripple-power cancellation  $p_{rpp}(t)$  must be equal to  $p_{ripple}(t)$ , by equating Eq.(4) with Eq.(5), the following conditions can be obtained:

$$v_{Cd}(t) = \sqrt{\frac{V_s I_s}{\omega_0 C_d (1 - \omega_0^2 L_d C_d)}} \sin(\omega_0 t - \phi - \frac{\pi}{2})$$

(6)

$$i_{Ld}(t) = \sqrt{\frac{V_s I_s \omega_0 C_d}{1 - \omega_0^2 L_d C_d}} \sin(\omega_0 t - \phi)$$

<sup>(7)</sup>

$$\phi = -\frac{\pi}{4}, or, \phi = \frac{3\pi}{4} \tag{8}$$

### 3.3 Control objectives

Since the capacitor  $C_d$  and inductor  $L_d$  are connected in series, the current flowing through the inductor is the same as the current flowing through the capacitor. Therefore, either Eq.(6) or Eq.(7) should be satisfied to meet the conditions for ripple-power cancellation.

Current mode control is inherently more stable than voltage mode control because the dc zero provides sufficient phase margin at the resonant frequency of LC. Therefore, the current mode control is adopted in this research that the inductor current  $i_{Ld}(t)$  is regulated according Eq.(7). Eq.(7) suggests that the regulated inductor current should be sinusoidal with a specific amplitude and phase. The amplitude of the regulated current should be a function of the amplitude of the rectifier input current I<sub>s</sub> since C<sub>d</sub>, L<sub>d</sub>,  $\omega_0$  are all fixed variables and the amplitude of line voltage V<sub>s</sub> is also assumed to be fixed in steady state. The phase of the regulated current should have a phase shift of  $\phi$  relative to the line voltage. In conclusion, the amplitude and the phase of the inductor current are the two control objectives for the ripple-port.

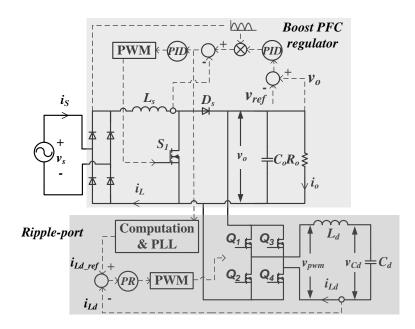

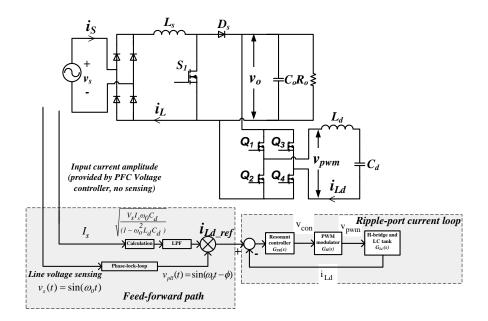

Figure 15 Diagram of the proposed control scheme

Figure 15 shows the control scheme proposed for the ripple-port. The ripple-port has a current feedback control loop that regulates the inductor current  $i_{Ld}(t)$  against a reference signal generated from the rectifier stage. Although the diagram includes a boost

PFC regulator, which is a very common circuit topology for single-phase PWM rectifier, for illustration purpose, the proposed control scheme of the ripple-port is independent from the circuit topology of the rectifier. The reference signal for the current loop is generated by the computation & PLL block shown in Figure 15, which takes phase and amplitude information from the rectifier. The error between the reference signal  $i_{Ld\_ref}$  and the feedback signal  $i_{Ld}$  is fed into a PR compensator. The output of the PR compensator is modulated by the PWM module and becomes the gate-drive signals for the H-bridge. 3.4 Ripple-port current loop design and stability analysis

3.4.1 Small-signal modelling

Figure 16 Small-signal model for ripple-port current loop

Figure 16 is the small-signal model of the current control loop introduced in the previous section. The bandwidth of the current loop should be much lower than the switching frequency since the control objective is to regulate the averaged inductor current. With the frequency band of interest being much lower than the switching frequency, i.e. by a decade, the PWM modulator does not contribute dynamic to the current loop and can

be considered to have a constant gain of  $V_0$  (dc-link voltage). Therefore, the control-tooutput transfer function can be written as:

$$G_{ic}(s) = \frac{i_{Ld}(s)}{v_{con}(s)} = \frac{sC_d V_o}{1 + s^2 L_d C_d}$$

(9)

Figure 17 shows the bode plot of the control-to-output characteristic of the currentloop in the ripple-port. The peak represents the resonance introduced by the LC tank. The phase plot shows that a 90 degree phase shift is formed from dc and a -90 degree phase shift is formed after the resonance.

Figure 17 Bode plot of the control-to-output transfer function of Ripple-port

3.4.2 Comparison between PR controller and PI controller

In dc/dc converter design where the reference signal for voltage/current regulation has a constant value, Proportional Integral (PI) compensator is commonly used to achieve maximum loop gain at dc and hence force the feedback signal to track the constant reference signal tightly [42, 43]. Eq.(10) shows that a PI compensator is a 1<sup>st</sup> order controller and the dc-pole reflects the its integrating characteristic in the time domain.

$$G_{PI}(s) = K_p + \frac{K_I}{s} \tag{10}$$

For dc/ac converter design, however, PI compensator does not provide the maximum gain at the frequency of the reference signal, which is an AC signal with frequency depends on the applications [44-46]. In alternative, Proportional Resonant (PR) controller gives the freedom of designing the maximum-gain-frequency, which makes it a more attractive candidate for the ripple-port since the reference signal of the current loop is a sinusoidal signal in the line frequency [47-50]. The transfer function of a PR controller can be written as [48]:

$$G_{PR}(s) = K_p + \frac{2K_I \omega_{cut} s}{s^2 + 2\omega_{cut} s + \omega_r^2}$$

(11)

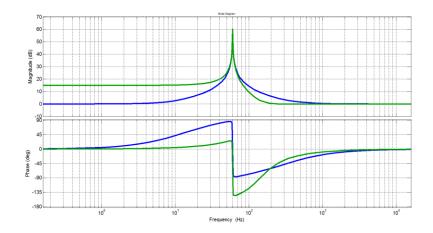

It can be shown in Figure 18 that the peak gain frequency of the PR controller occurs at  $\omega_r$ .  $\omega_{cut}$  defines the Q factor of the PR controller and determines the bandwidth of the resonance. The phase plot of the PR controller shows that the phase-shift approaches 90 degree as the frequency approaches the resonance and a 180 degree phase-shift is presented at the resonant frequency.

Figure 18 Bode plot of a PR controller  $K_p=1, K_i=1000, \omega_{cut}=1, \omega_r=377;$

Recall that in the control-to-output transfer function, a dc zero introduces 90 degree phase shift under resonance of the LC tank, shown as Figure 17, which can cause a 180 degree phase shift near the resonant frequency of the PR controller. This leads to positive feedback and the current-loop is not stable. This problem can be solved by adding a phase-compensating parameter in the PR controller, shown as Eq. (12):

$$G_{PR}(s) = K_p + K_I \frac{2\omega_{cut}s\cos\beta - 2\omega_{cut}\omega_r\sin\beta}{s^2 + 2\omega_{cut}s + \omega_r^2}$$

(12)

Figure 19 Bode plot of a PR controller with phase compensation  $K_P=1, K_I=1000, \omega_{cut}=1, \omega_r=377, \beta=0$ (Blue);  $\beta=-\pi/3$ (Green)

Figure 19 shows the bode plot of a PR controller with a compensation angle of -  $60^{\circ}$ . At frequency slightly lower than the resonant frequency, the phase shift is  $30^{\circ}$  and followed by a  $180^{\circ}$  phase shift caused by the resonance.

Figure 20 Bode plot of the loop gain of the ripple-port current loop

Figure 20 shows the open loop gain of the ripple-port current loop, ignoring the dynamics of the current-sensing circuit. It is shown that the phase margin is sufficient. The peak gain at high frequency is introduced by the LC tank, which has not included the consideration of parasitic resistance in the inductor and capacitor. In practical, the gain resulted from the LC tank resonance is much smaller due to the damping of the parasitic resistance.

3.5 Integrating the ripple-port to a single-phase rectifier

#### 3.5.1 Feedforward control

Recall that in section 3.2 where the conditions of ripple cancellation was introduced, it had been stated that the inductor current must follow the function shown in Eq.(7), and repeated as following:

$$i_{Ld}(t) = \sqrt{\frac{V_s I_s \omega_0 C_d}{1 - \omega_0^2 L_d C_d}} \sin(\omega_0 t - \phi)$$

(13)

Is in Eq.(13) represents the amplitude of the input current to the rectifier, which changes under different load power. To ensure the ripple-port drawing the correct amount of power, the amplitude of the reference signal in the ripple-port current loop must be calculated according to  $I_s$ . To simplify the illustration, it is assumed that  $I_s$  is the only changing variable, while V<sub>s</sub>,  $\omega_0$ , C<sub>d</sub> and L<sub>d</sub> are all fixed parameters.

The rectifier, which is also a PFC regulator, regulates the dc level of output voltage and shapes the input current waveform. For most PFC regulators, the voltage loop, which is an outer loop adjusts the amplitude of the input current to maintain the output voltage level. Therefore,  $I_s$  is in fact the output of the PFC voltage controller.

Figure 21 Block diagram of the feedforward control

The feedforward path is highlighted as red in Figure 21. A low-pass-filter is included in the feedforward path to limit the bandwidth in order avoid the high frequency components in  $I_s$  distorting the reference signal for the ripple-port. Furthermore, the feedforward path also includes a phase-locked-loop to ensure the angle  $\phi$  is regulated as the value shown in Eq. (8).

# 3.5.2 Phase-locked-loop

A phase-locked-loop, or PLL, is used to produce a sinusoidal signal which has its phase locked with an input signal. Shown as Figure 21, the PLL produces a sinusoidal output voltage  $v_{pll}(t)$  with  $\phi$  phase-shift relative to the line voltage. Then  $v_{pll}(t)$  is scaled by the amplitude information derived from the calculation block to generate the reference signal  $i_{Ld\_ref}(t)$ . The PLL used for locking the line voltage can be realized according to the block diagram in Figure 22.

Figure 22 Phase lock loop basic structure, taken from [51]

A PLL consists of a phase detector, a loop filter, and a voltage controlled oscillator (VCO). The phase detector is used to obtain the phase difference between the feedback signal and input signal. Then loop filter provides infinite gain near dc and is realized by a PI controller. The output of the loop filter controls the frequency of the VCO. When analyzing the small-signal model, the VCO can be modeled as an integrator.

Figure 23 Phase lock loop with notch filter, taken from [51]

There are various ways to implement the phase detector. For grid-connected applications with digital controller, the phase detector can be implemented by a mixer followed by a notch filter [51].

Eq. (13) shows that the multiplication of the sensed grid voltage and the output voltage results in a high-frequency term representing the phase sum and a low-frequency term representing the phase difference. The high-frequency needs to be filtered out in order to extract the phase difference.

$$v_d(t) = \frac{K_d v_{grid}}{2} [\sin((\omega_{grid} - \omega_{pll})t + (\theta_{grid} - \theta_{pll})) + \sin((\omega_{grid} + \omega_{pll})t + (\theta_{grid} + \theta_{pll}))]$$

(14)

Since the grid voltage is 60Hz, the frequency separation between the two frequency components in Eq. (13) is as low as 120Hz. Using notch filter other than low-pass filter can provide a sharper attenuation at specific frequency.

$$G_{nf}(s) = \frac{s^2 + 2\xi_2 \omega_n s + \omega_n^2}{s^2 + 2\xi_1 \omega_n s + \omega_n^2}$$

(15)

Eq. (15) shows the transfer function of a notch filter.

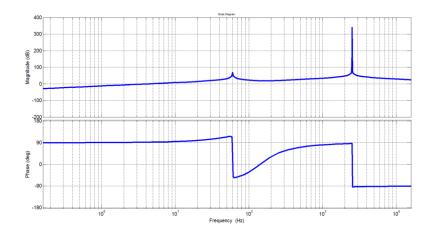

Figure 24 Phase lock loop open-loop gain

The loop gain of the PLL can be written as:

$$G_{lp}(s) = K_{PD}G_{nf}(s)G_{PI}(s)G_{vco}(s) = K_{PD}\frac{s^2 + 2\xi_2\omega_n s + \omega_n^2}{s^2 + 2\xi_I\omega_n s + \omega_n^2} \left(K_P + \frac{K_I}{s}\right)\left(\frac{K_{vco}}{s}\right)$$

(16)

It is shown in Figure 24 that the phase starts from  $180^{\circ}$  due to the two dc poles resulted from the PI controller and the VCO. The zero in the PI controller leads to the phase increasing to gain certain phase margin. The cross over frequency is determined by the DC gain and the location of the zero in the PI controller. To ensure stability, the crossover frequency must be much lower than the notch because the phase will cross  $180^{\circ}$  at the notch frequency.

3.5.3 Dynamic response analysis

Figure 25 Small-signal model of a Boost PFC regulator

Figure 25 shows that the PFC is controlled by a voltage loop and a current loop. The control signal of the voltage loop  $v_{vcon}$  is used to determine the peak of  $i_{ref_pfc}$  which is the reference signal for the current loop. The loop gain of the current loop is sufficiently high near the line frequency so that the inductor current  $i_L$  is regulated to follow  $i_{ref_pfc}$ . Since  $i_L$  and  $i_s$  have same amplitude, the amplitude of  $i_s$  will be the same as the amplitude of  $i_{ref_pfc}$ , which is  $v_{vcon}$ . Therefore, the input of the calculation block,  $I_s$ , in Figure 21 is connected to  $v_{vcon}$  in Figure 25.

From the small-signal model, the loop gain of the voltage loop (open loop) can be written as:

$$G_{PFC}(s) = G_{FB}(s)G_{VC}(s)G_{BOOST}(s) = K_{FB}(\frac{K_d s^2 + K_p s + K_i}{s})(\frac{R_o}{1 + R_o C_o s}K_c)$$

(17)

$K_{FB}$  is the ratio of the voltage divider used in sensing the output voltage.  $K_d$ ,  $K_p$ ,  $K_i$  are the parameters of the PID controller of the voltage loop. And  $K_c$  is the gain from the  $v_{vcon}$  to  $i_o$ , which is a constant designed according to the voltage swing of the PID

controller against the maximum operating power. The dynamic of current loop can be neglected in the voltage loop transfer function because the current loop is much faster than the voltage loop [52]. The bode plot of the voltage loop is shown in Figure 26.

Figure 26 Open-loop gain of the voltage loop: K<sub>FB</sub>=0.01; K<sub>c</sub>=0.42; Dashed curve: K<sub>d</sub>=0; K<sub>i</sub>=500; K<sub>p</sub>=20; R<sub>o</sub>=250; C<sub>o</sub>=200 μF; Solid curve: K<sub>d</sub>=0; K<sub>i</sub>=100; K<sub>p</sub>=0.9; R<sub>o</sub>=250; C<sub>o</sub>=100 μF;

For conventional PFC regulator, due to the presence of double-line frequency ripple in the output voltage, the gain of the feedback circuit and the controller, i.e.  $G_{FB}(s)G_{VC}(S)$ , must have sufficient attenuation at the double-line frequency [53-56], i.e. 120Hz, shown as the dashed curve in Figure 26.

According to [57], the the 3<sup>rd</sup> harmonic in the input current is related to the 120Hz component in vvcon, shown as Eq. (18)

$$\frac{i_{s_{-3}}}{i_{s_{-fundamental}}} = \frac{v_{vcon_{-120Hz}}}{v_{vcon_{-dc}}} = \frac{V_{ripple}K_{FB}G_{VC}(120Hz)}{V_o/(R_oK_c)}$$

(18)

If  $V_{ripple}$  is reduced, voltage controller's gain at 120Hz ( $G_{vc}(120Hz)$ ) can be proportionally increased. For the proposed PFC rectifier, since  $V_{ripple}$  is significantly reduced by ripple decoupling,  $G_{vc}(120Hz)$  can have higher gain, shown as the solid curve in Figure 26. The comparison of dynamic response between the two voltage loop designs in Figure 26 is shown in the simulation results in the proceeding chapter.

## 3.6 Conclusion

The control theory of ripple-port is discussed in this chapter. Current-mode control is adopted to regulate the inductor current. In order to optimize the error-tracking ability of the current loop against a sinusoidal reference signal. The small-signal model of the current control loop has been derived, and it was found that the PR controller needs to have a phase compensation parameter to ensure sufficient phase margin.

To integrate the ripple-port to a single-phase rectifier, a feedforward path and phase-locked-loop needed to be included because the reference signal for the ripple-port must dynamically adjust its amplitude and phase to ensure the ripple-port achieving ripple cancellation.

#### CHAPTER IV

#### DESIGN OF A RIPPLE-PORT INTEGRATED RECTIFIER

## 4.1 Introduction

The chapter introduces the design of a ripple-port integrated rectifier. Since the design of the single-phase rectifier has been presented in many existing literature, this chapter will focus on the controller design, choosing the decoupling capacitor and efficiency analysis.

In recent years, digital control had been widely adapted in controlling power converters for its robustness to PVT variation and high re-configurability [58]. Although in some applications, the digital controller is less preferred than analog controller due to its limited bandwidth, single-phase PWM rectifiers generally do not require aggressive controller speed, which makes digital-signal-processor a very suitable candidate for the controller in the ripple-port. Therefore, while the control theory is discussed in the continuous-time domain in the previous chapter, the implementation of the controller will be discussed in the discontinuous-time domain.

# 4.2 Selection of the decoupling capacitor

According to [41], the required capacitance for decoupling the double-line frequency ripple can be written as:

$$C_{D} = \frac{2P_{o}}{V_{C_{D}}^{2}\omega_{o}(1 - \omega_{o}^{2}L_{D}C_{D})}$$

(19)

Since it is desired that the double-line frequency ripple power being stored in the decoupling capacitor, a small inductor should be used only to limit the current ripple.

Furthermore, the resonant frequency of the LC tank should be much higher than the line frequency to ensure stability, shown as Eq. (20). Consequently, the expression of required capacitance can be written as Eq. (21)

$$\omega_o << \frac{l}{\sqrt{L_D C_D}} \tag{20}$$

$$C_D = \frac{2P_o}{V_{C_D}^2 \omega_o} \tag{21}$$

It can be inferred from Eq. (21) that the required capacitance is inversely proportional to the voltage across the decoupling capacitor  $C_D$ . With the output power  $P_o$  at 60W, the correlation between required capacitance and capacitor voltage can be plotted.

Figure 27 Capacitor voltage v.s. required capacitance

Figure 27 shows that required capacitance increased if the allowed voltage swing is reduced. For the circuit topology proposed in this thesis, the peak voltage across the

decoupling capacitor must be lower than the dc-link voltage because the ripple-port is a voltage source inverter.

Another consideration of choosing the decoupling capacitor is the rms current, which determined the amount of conduction loss on the capacitor. The rms current discussed here is in the line frequency. The magnitude of high-frequency component in the capacitor current is mainly determined by the switching frequency and the inductance L<sub>d</sub>, which will be discussed in the section 4.4.

$$I_{C_{D}-rms} = \frac{V_{C_{D}}}{\sqrt{2}C_{D}\omega_{o}}$$

(22)

Figure 28 Capacitor RMS current v.s. capacitance

Figure 28 suggests that the RMS current increases with the capacitance. Therefore, designing the capacitor to have voltage swing as large as possible can not only reduce the

capacitor size, but also reduce the RMS current in the line frequency, which is beneficial to the efficiency.

## 4.3 Digital controller implementation

The controller is implemented in TMS320F28035 microcontroller from Texas Instruments. The specifications of the microcontroller can be found in [59]. The most important function of the microcontroller used in this project is the 2p2z controller which has two poles and two zeros in its transfer function. The discrete transfer function and the difference equation is shown in Eq. (23) and Eq. (24), respectively. Figure 29 shows the block diagram of 2p2z controller, which shows that the 2p2z controller is in fact an Infinite Impulse Response (IIR) filter, since it has its output feedback.

$$\frac{U(z)}{E(z)} = \frac{b_2 z^{-2} + b_1 z^{-1} + b_0}{1 - a_2 z^{-1} - a_2 z^{-2}}$$

(23)

$$u(n) = a_1 u(n-1) + a_2 u(n-2) + b_0 e(n) + b_1 e(n-1) + b_2 e(n-2)$$

(24)

Figure 29 Block diagram of 2p2z controller

Since all the controllers mentioned in the previous sections, including the notch filter, PI controller and PR controller are 2<sup>nd</sup> order systems. In previous chapters the transfer functions are all in continuous-time domain. Using bilinear transform (also known as Tustin's method), the continuous-time transfer function can be which can be written in the form of Eq. (23).

Figure 30 Block diagram of the control loops in a ripple-port integrated rectifier

Discrete-time controller has a sampling frequency which determines how frequency it updates its variables. Selecting high sampling frequency can avoid aliasing, but also implies occupying more cycles of the CPU. Therefore, the sampling frequency should be selected according to the bandwidth requirement. For example, the bandwidth of the voltage loop in the PFC stage is around a few hundred hertz, hence a sampling frequency of a few kHz will be sufficient for the voltage controller.

Figure 30 shows the block diagram of the control loops with the  $2^{nd}$  order controllers highlighted as red. The following sections will discuss the discretization of these  $2^{nd}$  order controllers.

4.3.1 Voltage and current controllers: 2<sup>nd</sup> order PR and PID controller

The PFC stage has a dual-loop control: a fast current loop as the inner loop and a slow voltage loop as the outer loop. PID controllers are used for both loops. Averaged current mode control is adopted in this design, which had been discussed in many literatures [60, 61] and hence will not be repeated here. Using bilinear transform, the continuous time transfer function discussed in the previous sections can be implemented by digital controller [62-64].

|                    | Voltage controller                                               | Current controller                                                 |  |

|--------------------|------------------------------------------------------------------|--------------------------------------------------------------------|--|

| Continuous         | $H_{s\_PFC\_V}(s) = \frac{3s + 1950}{s}$                         | $H_{s\_PFC\_I}(s) = \frac{0.25s + 1.38 \times 10^4}{s}$            |  |

| Discrete           | $H_{z_{-}PFC_{-}V}(z) = \frac{-2.981z^{-1} + 3.019}{1 - z^{-1}}$ | $H_{z_{-}PFC_{-}I}(z) = \frac{-0.1812z^{-1} + 0.3187}{1 - z^{-1}}$ |  |

| Sampling frequency | 50kHz                                                            | 100kHz                                                             |  |

Table 1 PFC controllers in continuous and discrete form

Table 1 shows the controller design of the PFC stage. At nominal operating point, the current loop has the zero-crossing frequency at around 50kHz, which is around a

quarter of the switching frequency, with a phase margin of 90  $^{\circ}$ . The voltage loop has the zero-crossing frequency around 100Hz, with a phase margin of 70  $^{\circ}$ .

4.3.2 Type-2 2<sup>nd</sup> order PLL

|                       | Notch Filter                                                                                                | Loop filter                                                                                                  |

|-----------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Continuous            | $H_{s_Notch}(s) = \frac{s^2 + 5.11 \times 10^{-13} s + 5.77 \times 10^5}{s^2 + 547.6 s + 5.77 \times 10^5}$ | $H_{s\_LP}(s) = \frac{1.739 \times 10^{-6} s^2 + 90s + 5441}{s^2 + 350.7s - 668.8}$                          |

| Discrete              | $H_{z_Notch}(z) = \frac{-0.9033 - 1.725z^{-1} + 0.9033z^{-2}}{1 - 1.725z^{-1} + 0.8066z^{-2}}$              | $H_{z_{-}LP}(z) = \frac{0.01703 + 4 \times 10^{-4} z^{-1} - 0.017 z^{-2}}{1 - 1.869 z^{-1} + 0.8689 z^{-2}}$ |

| Sampling<br>frequency | 2.5kHz                                                                                                      | 2.5kHz                                                                                                       |

The notch filter shown in Table 2 has the notch at 120Hz in order to extract the low frequency component of the mixer output, which is the phase error between the reference signal and feedback signal.

## 4.3.3 PR controller

|                    | PR Controller                                                                                                                                                                   |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Continuous         | $H_{s_{-}PR}(s) = \frac{s^2 + 1002s + 7.951 \times 10^5}{s^2 + 2s + 142129}$<br>K <sub>P</sub> =1, K <sub>I</sub> =1000, $\omega_{cut}$ =1, $\omega_r$ =377, $\beta$ =- $\pi/3$ |

| Discrete           | $H_{z_{-}PR}(z) = \frac{5.594 + 11.19z^{-1} + 5.594z^{-2}}{1 + 2z^{-1} + z^{-2}}$                                                                                               |

| Sampling frequency | 100kHz                                                                                                                                                                          |

#### Table 3 PR controllers in continuous and discrete form

Table 3 shows the discrete time implementation of the PR controller and the design parameters referred in Eq. (12) are shown in the table.

4.4 Efficiency analysis of the ripple-port

The ripple-port is implemented by an H-bridge followed by an LC tank, which is used to store power when the instantaneous input power is lower than the average input power and supply power when then instantaneous input power is higher than the average input power.

Figure 31 Circuit model of the Ripple-port for loss analysis

Figure 31 shows the circuit model used for loss analysis. Without loss of generosity the switch is modeled as a voltage source in series with a resistor. For MOSFET switch,  $V_{sw}$  is very small while the  $r_{sw}$  dominates the voltage drop across the switch; for IGBT switch,  $r_{sw}$  is small and  $V_{sw}$  dominates the voltage drop across switch.

The inductor is modeled as an ideal inductor in series with a resistor which represents the winding resistance. The capacitor is modeled as an ideal capacitor in series with a resistor which represents the capacitor ESR.

Since capacitors has higher power density than inductor, the ripple-port utilize the capacitor to store ripple energy while the inductor is solely to filter the switching current. Therefore, small inductor should be chosen to reduce the volume of the ripple-port, which results in large inductor current ripple caused by the switching.

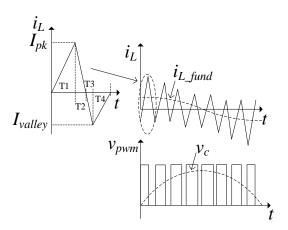

Figure 32 Current and voltage waveform of the ripple-port

Figure 32 shows the typical inductor current waveform in the ripple-port, which utilizes unipolar SPWM control. The waveform shows half of the period in line frequency because the other half is exactly in terms of power loss. In each switching period, the inductor current increases to its peak value and then decreases to negative values. The average value of the inductor current, denoted by  $i_{L_{fund}}$ , is regulated by the current loop and is sinusoidal in the line frequency. Allowing the large inductor current ripple implies high RMS current, which increases conduction loss. Yet it also bring the advantage of zero-voltage turn-ON.

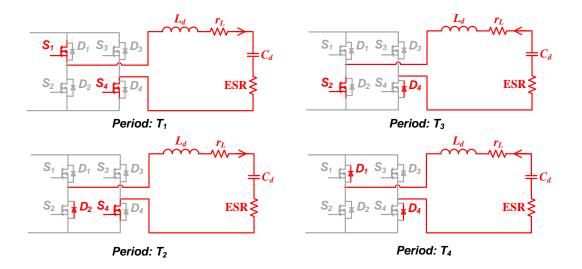

| Period | Conducting devices |

|--------|--------------------|

| T1     | S1, S4             |

| T2     | D2, S4             |

| Т3     | S2, D4             |

| T4     | D1, D4             |

Table 4 Conducting devices in different periods within a switching cycle

Figure 33 circuit diagram of conducting devices

#### Switching loss calculation

Table 4 shows the conducting devices in different period within a switching cycle and Figure 33 graphically shows the conducting devices and current flow. At the transition from T4 to T1 and from T2 to T3, the body diode conducts prior to the commutation of the switch, which enables the switches to turn ON at zero drain-to-source voltage. At the transition from T1 to T2, S1 turns off at hard-switching; at the transition from T3 to T4, S2 turns off at hard-switching. Assuming the turn-ON loss can be negligible due to zerovoltage switching, the switching loss in a switching period can be calculated as the sum of turn-off loss of S1 and S2. The turn-off loss of the IGBT can be calculated according to the  $V_{ce}$  and  $I_{ce}$  by the following equation, assuming the IGBT is operating in room temperature:

$$E_{off} = E_{offref} \left(\frac{V_{ce}}{V_{ceref}}\right) \left(\frac{I_{ce}}{I_{ceref}}\right)$$

(25)

$E_{offref}$ ,  $V_{ceref}$  and  $I_{ceref}$  are parameters provided by the datasheet of the device, and  $V_{ce}$  is the dc-link voltage. Therefore, at a given dc-link voltage, the turn-off loss of a switch is proportional to the turn-off current:

$$E_{off} = k_{sw} i_{off} \tag{26}$$

The turn-off current of S1 and S2 are  $i_{pk}$  and  $i_{valley}$ . Let  $\Delta i_L$  represent the inductor current ripple, the turn-off currents at the transition T1-T2 and T3-T4 can be written as:

$$i_{pk} = i_{L_{fund}} + \frac{1}{2}\Delta i_L \tag{27}$$

$$i_{valley} = \left| i_{L_{fund}} - \frac{1}{2} \Delta i_L \right| = \frac{1}{2} \Delta i_L - i_{L_{fund}}$$

(28)

Therefore the switching loss in a switching cycle can be written as:

$$E_{sw} = k_{sw}i_{pk} + k_{sw}i_{valley} = k_{sw}\Delta i_L$$

<sup>(29)</sup>

The inductor current ripple can be calculated as:

$$\Delta i_L = \left| d \right| \frac{V_{dc} - \left| v_c \right|}{f_{sw} L} \tag{30}$$

where d is the duty ratio of the SPWM signal and  $m_a$  is the modulation index:

$$d = m_a \sin(\omega_0 t) \tag{31}$$

Since a small inductor is chosen, the impedance of the LC tank at the fundamental frequency is dominated by the impedance of the capacitor. Hence  $v_c$  equals to average value of the output voltage from the H-bridge with a small phase shift  $\phi$  caused by the inductor impedance:

$$v_c = V_{dc} m_a \sin(\omega_0 t + \phi) \tag{32}$$

Substituting Eq. (31) and Eq. (32) into Eq. (30), the inductor current ripple at switching frequency can be written as:

$$\Delta i_{L} = |d| \frac{V_{dc} - |v_{c}|}{f_{sw}L} = \frac{V_{dc}[I - |m_{a}\sin(\omega_{0}t + \phi)|]|m_{a}\sin(\omega_{0}t)|}{f_{sw}L}$$

(33)

From Eq. (33), it can be inferred that the inductor current ripple varies from each switching cycle. To represent the inductor ripple in a switching cycle, the discrete form of the inductor current ripple can be written as:

$$\Delta i_L(nT_{sw}) = \frac{V_{dc}[1 - \left|m_a \sin(\omega_0 nT_{sw} + \phi)\right|] \left|m_a \sin(\omega_0 nT_{sw})\right|}{f_{sw}L}$$

(34)

The value of n is from 1 to N. And N can be expressed as the ratio between the line frequency and the switching frequency:

$$N = \frac{f_{sw}}{f_0} \tag{35}$$

The switching loss power can be written as the product of the switching energy loss in a line-frequency period and the line frequency. Since the diodes turn off at zero current, the reverse recovery of the diode does not contribute significantly to the switching loss. Hence the switching loss energy in each switching period is given in Eq. (29). And the switching loss of the ripple-port can be written as:

$$P_{switching} = f_0 \sum_{n=1}^{N} E_{sw}(nT_{sw}) = f_0 \sum_{n=1}^{N} k_{sw} \Delta i_L(nT_{sw}) = f_0 k_{sw} \sum_{n=1}^{N} \Delta i_L(nT_{sw})$$

(36)

As shown in Eq. (36) the switching loss can be calculated by summing the inductor current ripple over a line period. Combining Eq. (34) and Eq. (35) into Eq. (36) leads to:

$$P_{switching} = \frac{V_{dc}m_a k_{sw}}{L} \sum_{n=1}^{N} \frac{\left[1 - \left|m_a \sin(\frac{\omega_0 n}{Nf_0} + \phi)\right|\right] \sin(\frac{\omega_0 n}{Nf_0})}{N}$$

(37)

Eq. (37) indicates that the switching loss is not correlated to the switching frequency. Therefore, it is preferable to operate the ripple-port in higher switching frequency to achieve smaller current ripple and reduce conduction loss, which will be discussed in the following analysis.

However, Eq. (37) is only valid when the ripple-port operates in discontinuous conduction mode shown in Figure 32. When the switching frequency exceeds certain

values and the inductor current ripple is small enough, the ripple-port goes into continuous conduction mode and the above analysis is not applicable.

Figure 34 Switching loss v.s. Capacitor voltage amplitude  $V_{dc} = 170V; L = 100\mu$ H; C = 40 $\mu$ F; k<sub>sw</sub> = 2.9×10<sup>-5</sup>; f<sub>sw</sub> =25kHz

Figure 34 shows the relationship between the switching loss and the capacitor voltage amplitude. The switch used as the example is IRG4PC30FD from International Rectifier. According to the datasheet,  $k_{sw}$  can be calculated as  $2.9 \times 10^{-5}$ . The curve shows that the switching loss is maximized when the modulation index is around 0.65 and starts to decrease when the modulation index is larger than 0.65. Since the modulation index is directly related to the voltage across the decoupling capacitor, shown in Eq. (32), the peak capacitor voltage should be designed as close to the dc-link voltage as possible.

#### Conduction loss calculation

As shown in Figure 32, the inductor current consists of a fundamental frequency component, which represents the average value, and a high frequency component, which represents the current ripple introduced by switching. Therefore the instantaneous value of inductor current is:

$$i_{L}(t) = i_{L_{fund}}(t) + i_{L_{sw}}(t)$$

(38)

The fundamental component  $i_{L_{fund}}$  is a sinusoidal wave. Since the switching frequency is much higher than the fundamental frequency,  $i_{L_{fund}}$  can be assumed to have a constant value within a switching cycle, denoted as  $i_{L_{fund}}(nT_{sw})$

$$i_{L_{_fund}}(nT_{_{sw}}) = I_{L_{_fund}}\sin(\omega_0 nT_{_{sw}} + \phi + \frac{\pi}{2})$$

(39)

The high frequency component,  $i_{L_{sw}}$ , is a triangular wave with a peak-to-peak value of  $\Delta i_L$ . Therefore, over each switching cycle, the RMS value of the inductor current can be written as:

$$i_{L_{rms}}(nT_{sw}) = \sqrt{i_{L_{-}fund}^{2}(nT_{sw}) + (\frac{1}{\sqrt{3}}\frac{\Delta i_{L}(nT_{sw})}{2})^{2}}$$

(40)

Over a line period, the rms value of the inductor current can be calculated by summing up the rms inductor current in each switching cycle and then divided by the number of switching cycles:

$$I_{L_{rms}} = \sqrt{\frac{1}{N} \sum_{n=1}^{N} i_{L_{rms}}^{2} (nT_{sw})} = \sqrt{\frac{1}{N} \sum_{n=1}^{N} [i_{L_{rms}}^{2} (nT_{sw}) + (\frac{1}{\sqrt{3}} \frac{\Delta i_{L}(nT_{sw})}{2})^{2}]}$$

(41)

The result in Eq. (41) can be used to calculate the conduction loss in the resistance associated with the inductor and capacitor.

$$P_{inductor} = I_{L_rms}^2 r_L \tag{42}$$

$$P_{ESR} = I_L^2 \,_{rms} ESR \tag{43}$$

Figure 35 Inductor current waveform of the ripple-port

Figure 35 shows the inductor current waveform for a half of the line period. Since the average inductor current, indicated as  $i_{L_{fund}}$  is symmetrical against the zero crossing point, the instantaneous inductor current in  $T_A$  is also symmetrical to the instantaneous inductor current in  $T_B$ , against the zero-crossing point of  $i_{L_{fund}}$ .

If integrating the inductor current over the period of  $T_A+T_B$ , the total charge in all the T1 periods equals to the total charge in all the T4 periods, because of the symmetric. Similarly, the total charge in all the T2 periods equals to the total charge in all the T3 periods. With this conclusion and referring to Table 4, two conclusions can be drawn. First, the total charge flowing through the switches has the same amount as the total charge flowing through the diodes. Second, at any time instance the inductor current always flows through two devices: a diode and a switch, or, two diodes, or two switches. Therefore to calculate the conduction loss of the diodes and switches, the H-bridge can be transformed to an equivalent circuit of a diode connected in series with a switch, shown as Figure 36.

Figure 36 Equivalent circuit for calculating conduction loss of the H-bridge

In order to calculate the conduction loss on the switches and diodes, the average value of current flowing through the device is needed because there is a voltage source in both the models of the switch and diode. However, since the current always flows into the positive terminal of the voltage source, the effective current needed for calculating the conduction loss on the voltage source should be the absolute value of the inductor current.

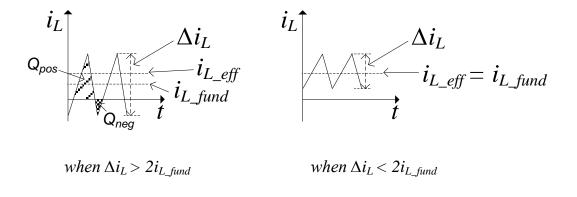

Figure 37 Effective current for voltage sources loss calculation 52

As shown in Figure 37, when the inductor current ripple  $\Delta i_L$  is larger than twice of the average inductor current  $i_{L_{fund}}$  and the inductor current goes to negative for a certain period of time. The effective current is the sum of  $Q_{pos}$  and  $Q_{neg}$  divided by the switching period, while  $i_{L_{fund}}$  is the difference between the charge amount  $Q_{pos}$  and  $Q_{neg}$  divided by the switching period:

$$i_{L_{fund}} = f_{sw}(Q_{pos} - Q_{neg})$$

$$i_{L_{eff}} = f_{sw}(Q_{pos} + Q_{neg})$$

(44)

The ratio of the two triangles` area representing  $Q_{pos}$  and  $Q_{neg}$  can be found by geometric analysis of the waveform shown in Figure 37:

$$\frac{Q_{pos}}{Q_{neg}} = \left(\frac{i_{L_{-fund}} + \frac{1}{2}\Delta i_{L}}{i_{L_{-fund}} - \frac{1}{2}\Delta i_{L}}\right)^{2}$$

(45)

By combining Eq. (44) and Eq. (45), the effective current can be found as:

$$i_{L_{eff}}(nT_{sw}) = \frac{2i_{L_{sw}}^{2}(nT_{sw}) + \frac{1}{2}\Delta i_{L}^{2}(nT_{sw})}{2\Delta i_{L}(nT_{sw})}$$

(46)

When the inductor current ripple  $\Delta i_L$  is smaller than twice of the average inductor current  $i_{L_{fund}}$ , the effective current equals to the average inductor current. Therefore:

$$i_{L_{eff}}(nT_{sw}) = \frac{2i_{L_{fund}}^{2}(nT_{sw}) + \frac{1}{2}\Delta i_{L}^{2}(nT_{sw})}{2\Delta i_{L}(nT_{sw})} when\Delta i_{L}(nT_{sw}) > 2i_{L_{fund}}(nT_{sw})$$

$$i_{L_{eff}}(nT_{sw}) = i_{L_{fund}}(nT_{sw}) when\Delta i_{L}(nT_{sw}) < 2i_{L_{fund}}(nT_{sw})$$

(47)

The average value can be calculated by summing over a line cycle:

$$I_{L_{eff}} = \frac{1}{N} \sum_{n=1}^{N} i_{L_{eff}} (nT_{sw})$$

(48)

$$P_{switch} = I_{L_{eff}} V_{sw} + I_{L_{rms}}^2 r_{sw}$$

$$P_{diode} = I_{L_{eff}} V_f + I_{L_{rms}}^2 r_d$$

(49)

To verify the derivation of  $I_{L_rms}$  and  $I_{L_eff}$ , a Simulink model of the ripple-port is built. The simulation data of the inductor current is logged. The measured inductor RMS current is compared with the predicted inductor RMS current using Eq. (41), shown in Figure 38.

Figure 38 Comparison between the measured  $I_{L_{rms}}$  and calculated  $I_{L_{rms}}$

The measured effective inductor current is obtained by taking the absolute value of the instantaneous inductor current and then taking the average value. The result is compared with the predicted result in Eq. (48), shown as Figure 39.

Figure 39 Comparison between the measured  $I_{L_{\mbox{\scriptsize eff}}}$  and calculated  $I_{L_{\mbox{\scriptsize eff}}}$

Figure 38 and Figure 39 show that the calculation for  $I_{L_rms}$  and  $I_{L_eff}$  are valid and also reveals the peaking characteristic of curve for the inductor current versus the capacitor voltage amplitude. Once again this result suggests the ripple-port should avoid operating near the peak of the inductor current. To achieve that, the amplitude of the capacitor voltage should be designed close to the dc-link voltage to reduce conduction loss.

Table 5 Specifications of the ripple-port for loss analysis shows an example of using the above loss model to analyze the loss of a ripple-port.

| Operating conditions                                                                                                                                                                                          |       |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|

| $V_{dc} = 170V; f_{sw} = 25kHz; V_c = 140V; P_o = 60W$                                                                                                                                                        |       |  |

| Component variables                                                                                                                                                                                           |       |  |

| $ \begin{array}{c} k_{sw} = 2.9 \times 10^{-5}; \ r_L = 0.3\Omega; \ ESR = 0.2\Omega; \ V_{sw} = 1.07V; \ R_{sw} = 31m\Omega; \ V_f = 1.16V; R_d = 44m\Omega; \\ L = 100 \mu H; \ C = 40 \mu F; \end{array} $ |       |  |

| Loss contribution                                                                                                                                                                                             |       |  |

| Switching loss P <sub>switching</sub>                                                                                                                                                                         | 9.2W  |  |

| Switch Conduction Loss P <sub>switch</sub>                                                                                                                                                                    | 4.2W  |  |

| Diode Conduction Loss P <sub>diode</sub>                                                                                                                                                                      | 4.7W  |  |

| Inductor winding loss P <sub>inductor</sub>                                                                                                                                                                   | 5.1W  |  |

| Capacitor ESR loss P <sub>ESR</sub>                                                                                                                                                                           | 3.4W  |  |