# DESIGN OF ENERGY-EFFICIENT A/D CONVERTERS WITH PARTIAL EMBEDDED EQUALIZATION FOR HIGH-SPEED WIRELINE RECEIVER **APPLICATIONS**

### A Dissertation

by

### EHSAN ZHIAN TABASY

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

Chair of Committee, Samuel Palermo Committee Members,

Jose Silva-Martinez

Henry Pfister Eun Kim

Head of Department, Miroslav M. Begovic

May 2015

Major Subject: Electrical Engineering

Copyright 2015 Ehsan Zhian Tabasy

#### ABSTRACT

As the data rates of wireline communication links increases, channel impairments such as skin effect, dielectric loss, fiber dispersion, reflections and cross-talk become more pronounced. This warrants more interest in analog-to-digital converter (ADC)-based serial link receivers, as they allow for more complex and flexible back-end digital signal processing (DSP) relative to binary or mixed-signal receivers. Utilizing this back-end DSP allows for complex digital equalization and more bandwidth-efficient modulation schemes, while also displaying reduced process/voltage/temperature (PVT) sensitivity. Furthermore, these architectures offer straightforward design translation and can directly leverage the area and power scaling offered by new CMOS technology nodes. However, the power consumption of the ADC front-end and subsequent digital signal processing is a major issue. Embedding partial equalization inside the front-end ADC can potentially result in lowering the complexity of back-end DSP and/or decreasing the ADC resolution requirement, which results in a more energy-efficient receiver.

This dissertation presents efficient implementations for multi-GS/s time-interleaved ADCs with partial embedded equalization. First prototype details a 6b 1.6GS/s ADC with a novel embedded redundant-cycle 1-tap DFE structure in 90nm CMOS. The other two prototypes explain more complex 6b 10GS/s ADCs with efficiently embedded feed-forward equalization (FFE) and decision feedback equalization (DFE) in 65nm CMOS. Leveraging a time-interleaved successive approximation ADC architecture, new structures for embedded DFE and FFE are proposed with low power/area overhead. Measurement results over FR4 channels verify the effectiveness of proposed embedded equalization schemes. The comparison of fabricated prototypes against

state-of-the-art general-purpose ADCs at similar speed/resolution range shows comparable performances, while the proposed architectures include embedded equalization as well.

To Sousan

my mother, my hero

#### ACKNOWLEDGEMENTS

There are many people who have impacted my life, and so in many ways this dissertation. Unfortunately, I'm prone to have forgotten mentioning some people with some, hopefully low, probability; we are engineers after all, and everything is happening with a probability in this vast universe.

First and foremost, I'd like to thank my talented advisor Prof. Samuel Palermo. Thank you for believing in me and my research and keeping me on track. Thank you for showing me how a serious research should be organized and followed, and thank you for molding me into a better engineer. I'd like to thank my friends and colleagues in Sam's group. Ayman, Cheng, Younghoon, Byungho, Osama, Noah, and Shengchang. Thank you Ayman. We started this research together and it would never finish without your help and so many discussions that I will cherish forever and miss for sure.

I should thank Prof. Edgar Sanchez-Sinencio, Prof. Jose Silva-Martinez, Prof. Sebastian Hoyos, and Prof. Kamran Entesari in Analog and Mixed-Signal Center, for their teachings. I would also like to thank Prof. Henry Pfister and Prof. Eun Kim for serving on my Ph.D. committee. Also, I appreciate the support of Semiconductor Research Corporation (SRC) and National Science Foundation (NSF) for supporting this research.

Many people have made my stay in Analog and Mixed-Signal Center of Texas A&M University memorable. Thank you Hajir for beside being a great friend always let me pick your brain with my nerdy discussions. Thank you Alireza, Masoud and Samira, Vahid, Shokoufeh, Negar, Mohammadhossein, Mohan, Saman, CJ, Shiva, and the list goes on and on. It's been a ride! There are so many other friends in

College Station, Texas, that I should thank; Masoud, Kamyar, Sardar, Amirhossein, Ali, Morteza, Armin, and others. I may have forgot to mention many others by name but you know who you are. Thank you.

I'd like to thank my previous advisors during Bachelor's and Master's programs as well. Thank you Prof. Lotfi for introducing me to the beautiful world of Analog Integrated Circuit Design many years ago in Ferdowsi University of Mashhad, and thank you Prof. Shoaei, Prof. Kamarei, and Prof. Ashtiani for your teachings in University of Tehran.

I'd like to thank my other friends outside Texas A&M University, Ali, Saman and Mahsa. You were the sanctuary I ran to whenever I needed to escape for a short time from my research and everyday life in order to come back all refreshed and focused.

At last but not the least, thank you Yaser, Omid and Soudabeh, my brothers and sister for always being there for me, although physically you are thousands of miles away from me. Thank you mom for always believing in me, even at times that I didn't myself! With all my heart, I dedicate this dissertation to you.

# TABLE OF CONTENTS

|    |            |                                                                                                                                                                                                            | Page                               |

|----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| AF | BSTR       | ACT                                                                                                                                                                                                        | . ii                               |

| DE | EDIC.      | ATION                                                                                                                                                                                                      | . iv                               |

| A( | CKNC       | OWLEDGEMENTS                                                                                                                                                                                               | . v                                |

| TA | BLE        | OF CONTENTS                                                                                                                                                                                                | . vii                              |

| LI | ST O       | F FIGURES                                                                                                                                                                                                  | . ix                               |

| LI | ST O       | F TABLES                                                                                                                                                                                                   | . xvii                             |

| 1. | INT        | RODUCTION                                                                                                                                                                                                  | . 1                                |

|    | 1.1        | Dissertation Organization                                                                                                                                                                                  | . 3                                |

| 2. | BAC        | CKGROUND ON HIGH-SPEED ADC-BASED RECEIVERS                                                                                                                                                                 | . 6                                |

|    | 2.1        | Time-Interleaving Challenges  2.1.1 Offset Mismatch  2.1.2 Gain Mismatch  2.1.3 Phase Mismatch  2.1.4 Phase Random Jitter  High-Speed Track-And-Holds  2.2.1 T/H Basics  2.2.2 Open-Loop T/H Architectures | . 7<br>. 9<br>. 11<br>. 14<br>. 16 |

|    | 2.3        | High-Speed Sub-ADC Architectures                                                                                                                                                                           | . 29<br>. 34                       |

|    | 2.4        | High-Speed Link Receivers                                                                                                                                                                                  | . 48                               |

| 3. | 6-BI       | T 1.6-GS/S ADC WITH EMBEDDED REDUNDANT CYCLE DFE                                                                                                                                                           | . 54                               |

|    | 3.1<br>3.2 | Embedded Feedback Equalization Modeling                                                                                                                                                                    |                                    |

|    |      | 3.2.1  | Loop-Unrolled 1-Tap Embedded DFE                                    | 60   |

|----|------|--------|---------------------------------------------------------------------|------|

|    |      | 3.2.2  | Redundant-Cycle 1-Tap Embedded DFE                                  | 62   |

|    |      | 3.2.3  | Critical Delay Path                                                 | 64   |

|    |      | 3.2.4  | Switched-Capacitor Implementation                                   | 65   |

|    | 3.3  | ADC I  | Design                                                              | 67   |

|    |      | 3.3.1  | Time-Interleaved Architecture                                       | 67   |

|    |      | 3.3.2  | Unit ADC with Embedded 1-Tap DFE                                    | 68   |

|    |      | 3.3.3  | Front-End Track-and-Hold $(T/H)$                                    | 72   |

|    |      | 3.3.4  | On-Die Offset and Clock-Skew Calibration                            | 73   |

|    | 3.4  | Measu  | rement Results                                                      | 77   |

|    |      | 3.4.1  | Core ADC Characterization                                           | 77   |

|    |      | 3.4.2  | Embedded DFE Functionality                                          | 79   |

|    | 3.5  | Conclu | ısion                                                               | 84   |

| 4. | 6-BI | T 10-G | S/S ADC WITH EMBEDDED EQUALIZATION                                  | 87   |

|    | 4.1  | A 6-Bi | it $10 \mathrm{GS/s}$ ADC with Embedded 2-Tap FFE and 1-Tap DFE     | 87   |

|    |      | 4.1.1  | Embedded Equalization Modeling                                      | 89   |

|    |      | 4.1.2  | SAR ADC with Low-Overhead Embedded FFE and DFE                      | 94   |

|    |      | 4.1.3  | ADC Design                                                          | 98   |

|    |      | 4.1.4  | Experimental Results                                                | 106  |

|    |      | 4.1.5  | Performance Summary                                                 | 117  |

|    |      | 4.1.6  | Conclusion                                                          | 118  |

|    | 4.2  | A 6-Bi | it $10 \text{GS/s}$ ADC with Extended-Range Embedded 3-Tap FFE $$ . | 120  |

|    |      | 4.2.1  | SAR ADC with Extended-Range 3-Tap Embedded FFE $$                   | 120  |

|    |      | 4.2.2  | ADC Design                                                          | 122  |

|    |      | 4.2.3  | Experimental Results                                                |      |

|    |      | 4.2.4  | Performance Summary                                                 | 132  |

|    |      | 4.2.5  | 10Gb/s ADC-Based Receiver with Dynamically-Enabled Dig-             |      |

|    |      |        | ital Equalization                                                   | 132  |

|    |      | 4.2.6  | Conclusion                                                          | 138  |

| 5. | CON  | NCLUSI | ION AND FUTURE WORK                                                 | 140  |

|    | 5.1  | Concli | ısion                                                               | 141  |

|    | 5.2  |        | amendations for Future Work                                         |      |

|    |      | 5.2.1  | Hybrid RX with Dynamically-Enabled Front-End ADC                    |      |

|    |      |        | · · · · · · · · · · · · · · · · · · ·                               |      |

| ΡĮ | RATE | ENCES  |                                                                     | 1/17 |

# LIST OF FIGURES

| FIGUR | E                                                                                                                                                                                                       | Page  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

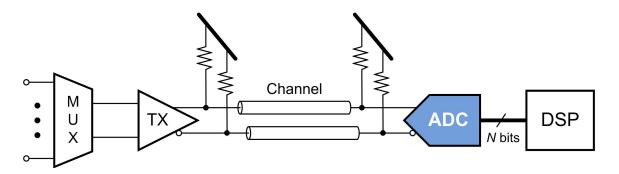

| 1.1   | A high-speed electrical link system with an ADC-based receiver                                                                                                                                          | 2     |

| 2.1   | Simplified block diagram of an N-way time-interleaved ADC                                                                                                                                               | 7     |

| 2.2   | Two-way time-interleaved ADC with offset mismatch                                                                                                                                                       | 8     |

| 2.3   | Simulated output spectrum of a two-way time-interleaved ADC with offset mismatch for two different sets of input frequencies and amplitudes                                                             | 9     |

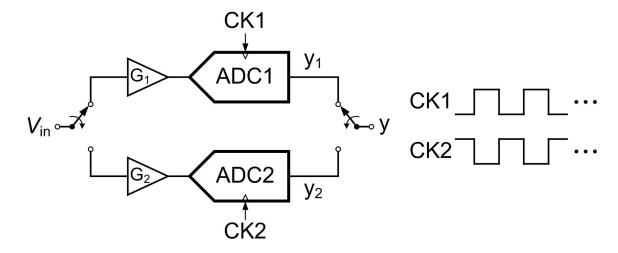

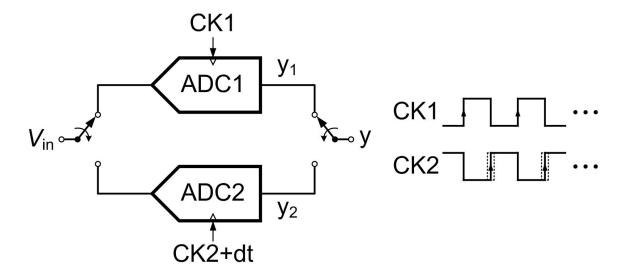

| 2.4   | Two-way time-interleaved ADC with gain mismatch                                                                                                                                                         | 10    |

| 2.5   | Simulated output spectrum of a two-way time-interleaved ADC with gain mismatch for two different sets of input frequencies and amplitudes                                                               | s. 11 |

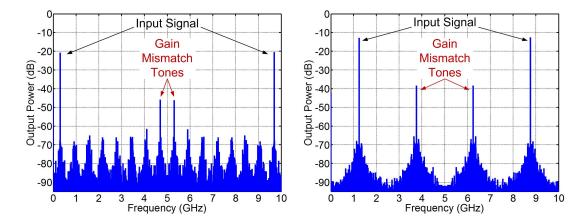

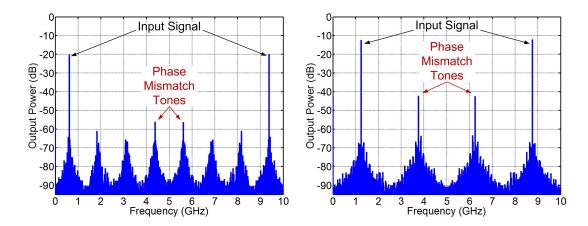

| 2.6   | Two-way time-interleaved ADC with phase mismatch                                                                                                                                                        | 12    |

| 2.7   | Simulated output spectrum of a two-way time-interleaved ADC with phase mismatch for two different sets of input frequencies and amplitudes                                                              | 14    |

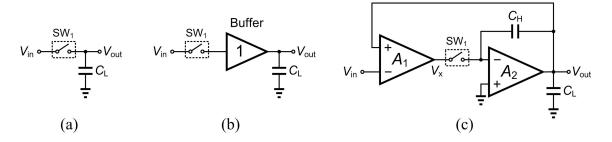

| 2.8   | (a) Simple T/H, b) practical open-loop T/H, and (c) a conventional implementation of closed-loop T/H                                                                                                    | 17    |

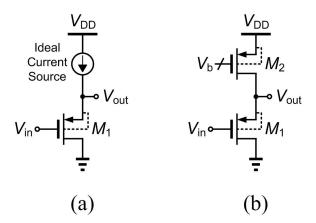

| 2.9   | Source-follower buffer using (a) an ideal current source, and (b) a simple PMOS current source                                                                                                          | 19    |

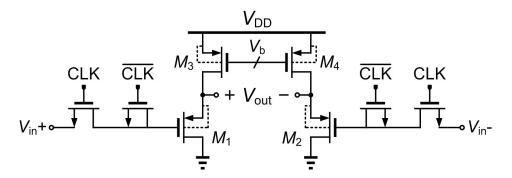

| 2.10  | Pseudo-differential source follower based T/H stage using simple NMOS switches                                                                                                                          | 20    |

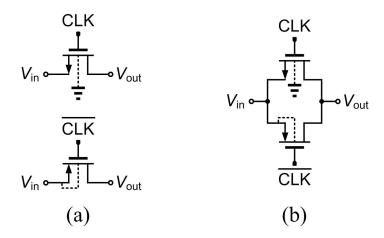

| 2.11  | Simple switch architectures: (a) Single NMOS or PMOS switch, and (b) complementary MOS switch also known as transmission gate                                                                           | 21    |

| 2.12  | On-resistance of NMOS, PMOS and transmission-gate switches versus input voltage amplitude (Wn = $10\mu m$ , Wp = $20\mu m$ , with minimum length L = $100nm$ , and $V_{DD}=1V$ in 90nm CMOS technology) | 22    |

| 2.13 | strapped switch                                                                                                                                                                                |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.14 | Pseudo-differential source-follower based buffer using negative capacitance (a) in a positive feedback configuration, and (b) in a feed-forward configuration.                                 |

| 2.15 | Differential flipped-voltage follower based buffer architectures: (a) Conventional low-swing FVF, (b) folded FVF case 1, and (c) folded FVF case 2                                             |

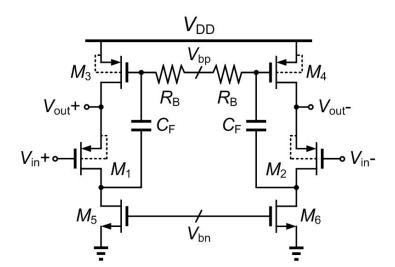

| 2.16 | Pseudo differential flipped-voltage follower based buffer with feedback capacitors                                                                                                             |

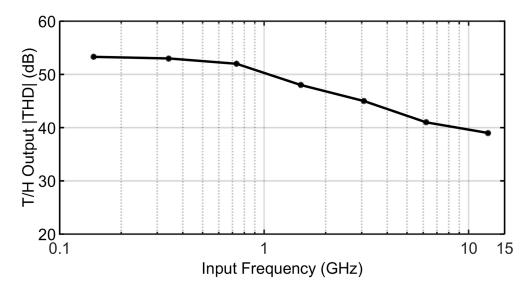

| 2.17 | Linearity performance of T/H with FVF-based buffer and $750mV_{pp}$ output swing                                                                                                               |

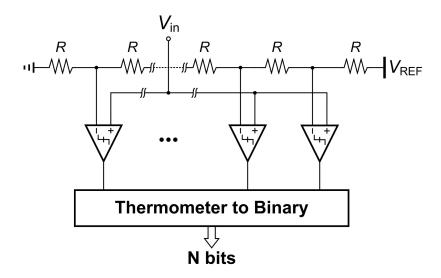

| 2.18 | Basic structure of a flash ADC                                                                                                                                                                 |

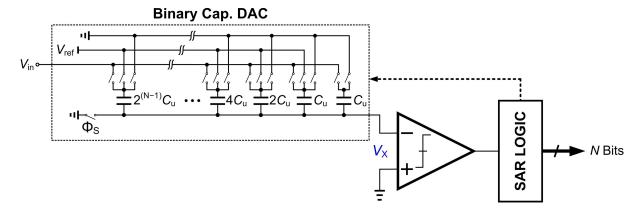

| 2.19 | Basic structure of a SAR ADC with binary-weighted capacitive DAC.                                                                                                                              |

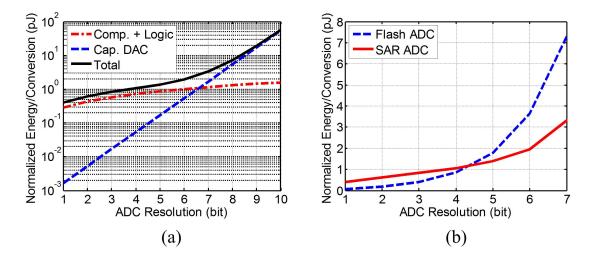

| 2.20 | (a) SAR energy versus resolution, along with the individual components contribution. (b) Energy comparison between SAR and flash ADCs as a function of resolution                              |

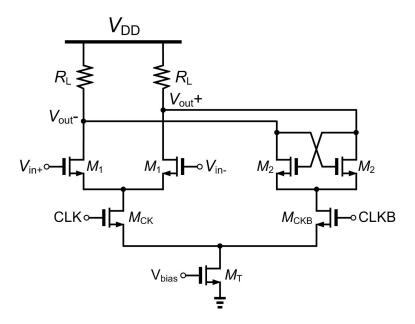

| 2.21 | Schematic of a CML based CMOS comparator                                                                                                                                                       |

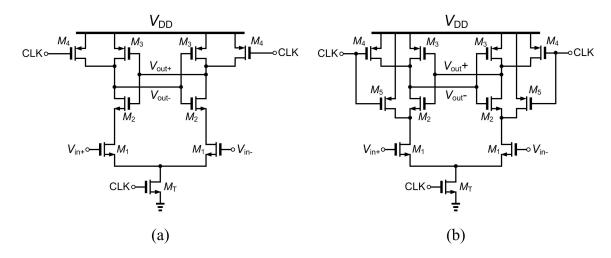

| 2.22 | Schematic of a StrongArm dynamic comparator. (a) Basic schematic, and (b) schematic with extra devices to discharge internal nodes during reset phase for reduced memory effects               |

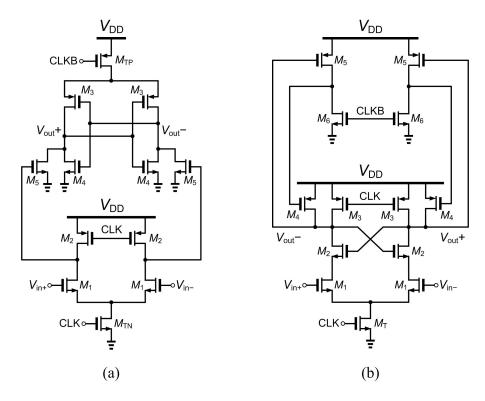

| 2.23 | Schematic of (a) the double-tail dynamic comparator proposed by Schinkel, and (b) the two-stage modified dynamic comparator proposed by Goll                                                   |

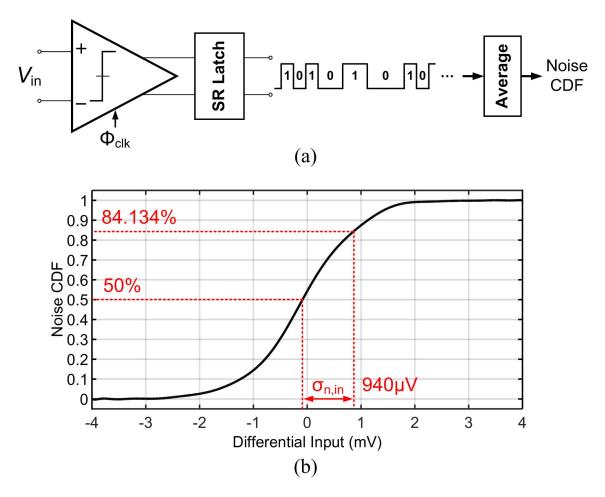

| 2.24 | Input-referred noise (a) transient simulation setup, and (b) CDF for a designed Goll two-stage comparator in 65nm CMOS technology                                                              |

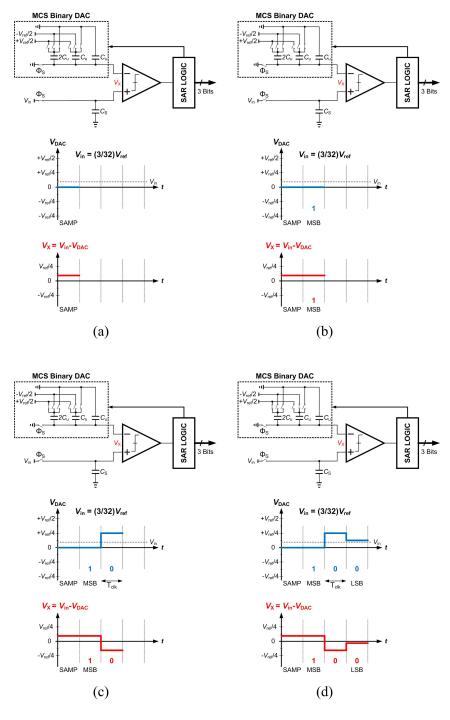

| 2.25 | The simplified operation of a capacitive DAC with merged capacitor switching scheme in a 3-bit SAR ADC: (a) sampling phase, (b) first bit cycle, (c) second bit cycle, and (d) third bit cycle |

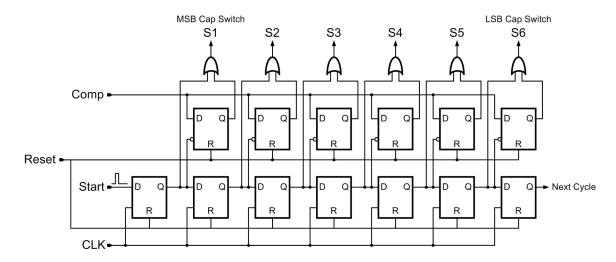

| 2.26 | A common implementation of the SAR control logic in a 6-bit ADC                                                                                                                                |

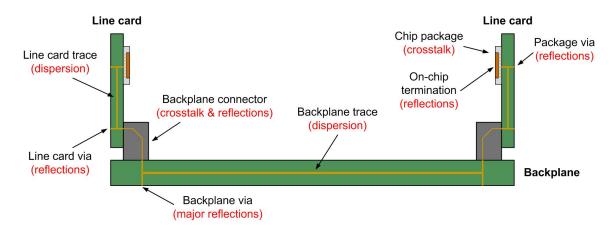

| 2.27 | Example of a backplane system cross-section                                                                                                                                                    |

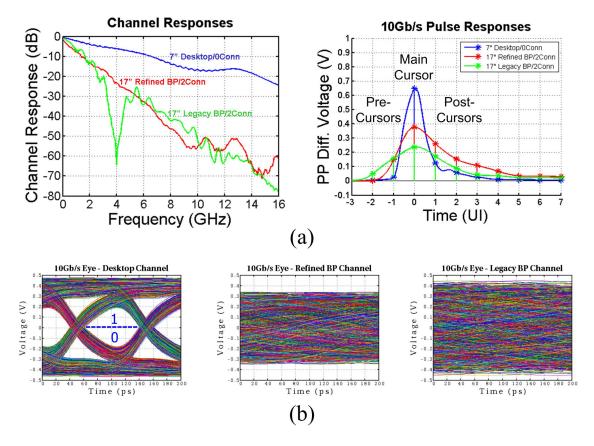

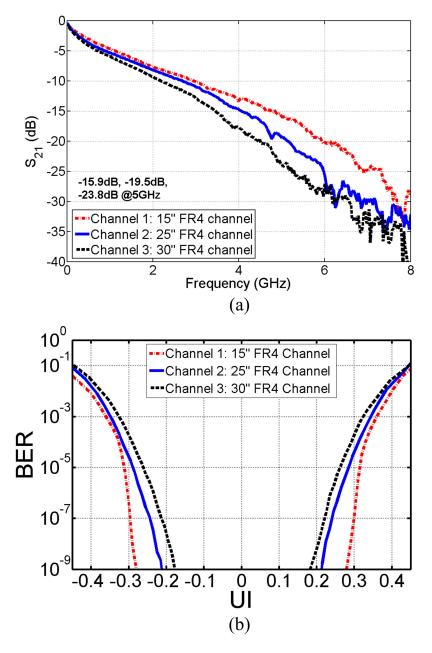

| 2.28       | (a) Frequency response and pulse response of three channels. (b) Eye diagrams after channels without equalization                                                                                                                                                                                                   | 46       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

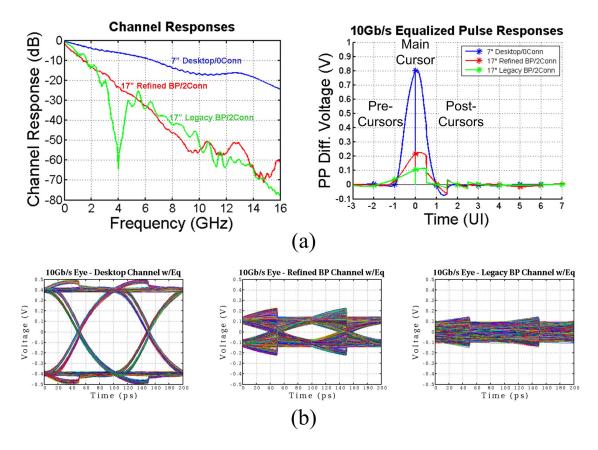

| 2.29       | (a) Frequency response and equalized pulse response of three channels under study. (b) Eye diagrams after channels with equalization                                                                                                                                                                                | 48       |

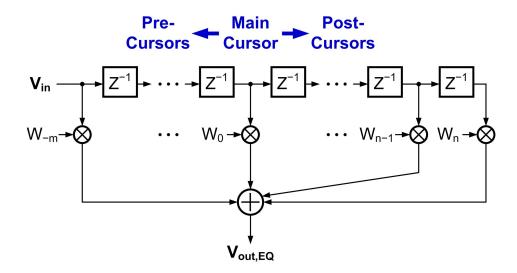

| 2.30       | Block diagram of a receiver feed-forward equalizer                                                                                                                                                                                                                                                                  | 50       |

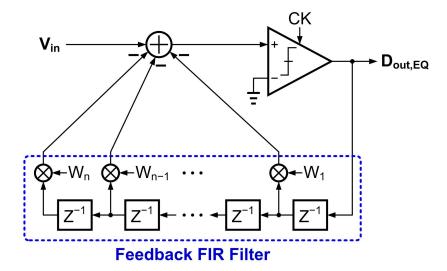

| 2.31       | Block diagram of a receiver decision feedback equalizer with direct feedback taps                                                                                                                                                                                                                                   | 51       |

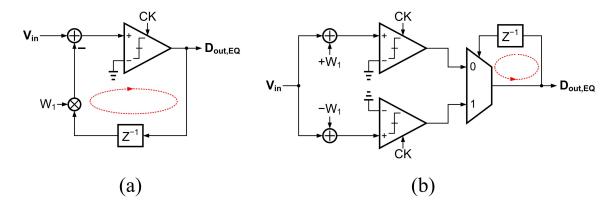

| 2.32       | Simplified block diagram of a 1-tap DFE using (a) direct feedback implementation, and (b) loop-unrolled technique to relax critical delay path                                                                                                                                                                      | 52       |

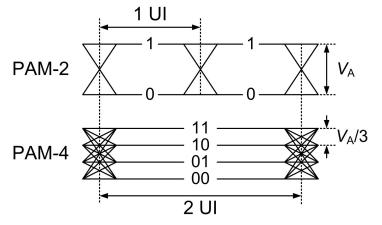

| 2.33       | Common pulse amplitude modulation schemes in serial links: simple PAM-2 (1 bit/symbol) and PAM-4 (2 bits/symbol)                                                                                                                                                                                                    | 52       |

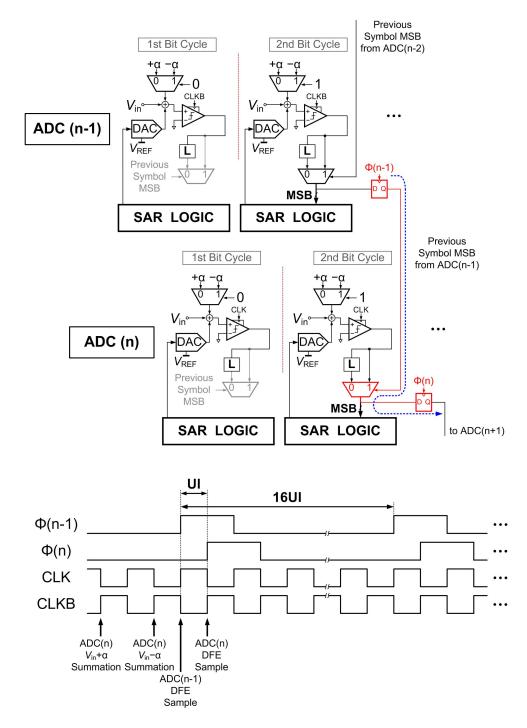

| 3.1<br>3.2 | A high-speed link with an ADC-based receiver                                                                                                                                                                                                                                                                        | 55<br>57 |

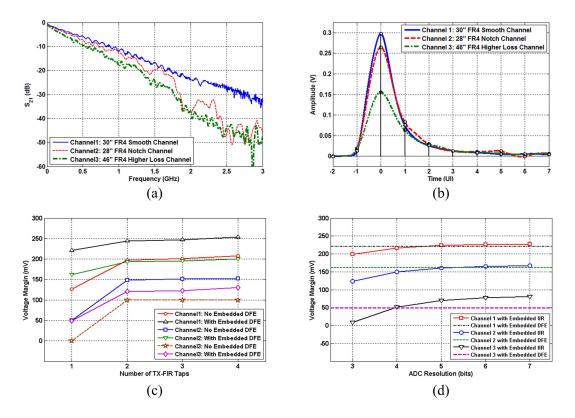

| 3.3        | (a) Magnitude and (b) 1.6Gb/s pulse responses of three FR4 channels. (c) Impact of including one tap of embedded DFE equalization for different levels of TX-FIR equalization, and (d) impact of ADC resolution with embedded DFE and embedded IIR equalization with no TX FIR equalization over three FR4 channels | 59       |

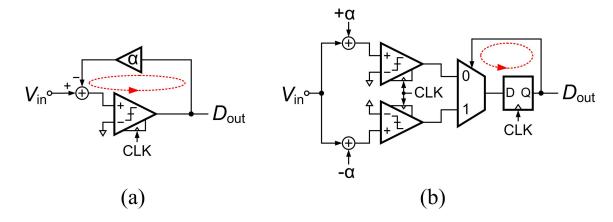

| 3.4        | DFE implementations: (a) direct-feedback, and (b) loop-unrolled                                                                                                                                                                                                                                                     | 61       |

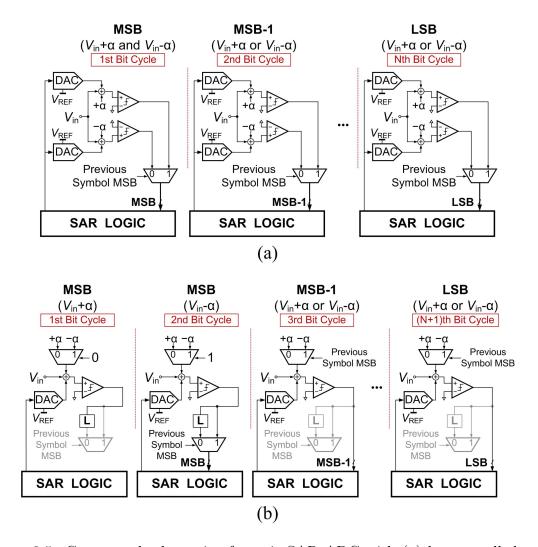

| 3.5        | Conceptual schematic of a unit SAR ADC with (a) loop-unrolled, and (b) proposed redundant cycle 1-tap embedded DFE                                                                                                                                                                                                  | 63       |

| 3.6        | Conceptual schematic of a unit SAR ADC (a) with redundant cycle 2-tap embedded DFE, and (b) with loop-unrolled 2-tap embedded DFE.                                                                                                                                                                                  | 65       |

| 3.7        | Critical delay path for the redundant cycle 1-tap embedded DFE. The instants when the summation and sampling in the 1-tap embedded DFE occur are shown.                                                                                                                                                             | 66       |

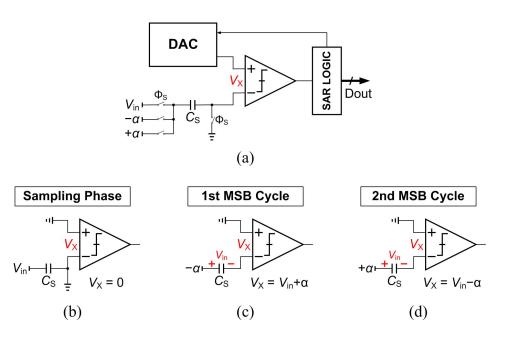

| 3.8        | SAR ADC with embedded 1-tap DFE: (a) simplified block diagram, operation during the (b) sampling phase, (c) first MSB evaluation, and (d) second MSB evaluation                                                                                                                                                     | 68       |

| 3.9  | Block diagram of the 16-way time-interleaved SAR ADC with embedded 1-tap DFE                                                                                                                                                                      | 69      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 3.10 | Unit SAR ADC schematic with redundant cycle embedded 1-tap DFE.                                                                                                                                                                                   | 69      |

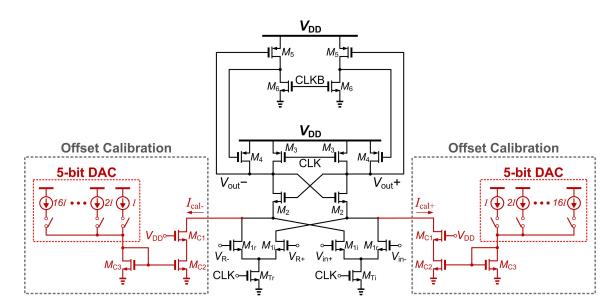

| 3.11 | Schematic of the 4-input comparator with offset calibration current DACs                                                                                                                                                                          | 71      |

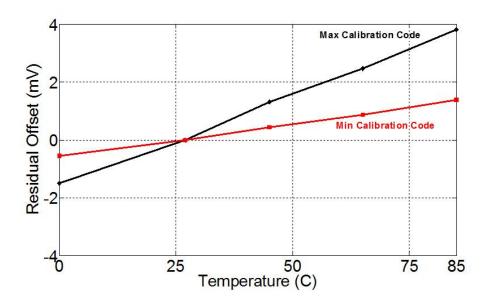

| 3.12 | Temperature dependency of residual unit ADC offset calibrated at $27^{\circ}C$ room temperature                                                                                                                                                   | 71      |

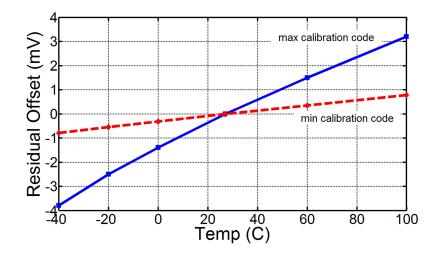

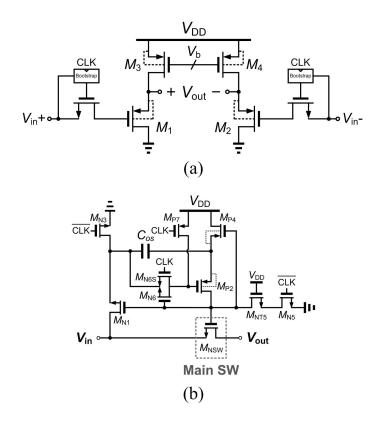

| 3.13 | Front-end T/H: (a) schematic, and (b) bootstrapped switch structure.                                                                                                                                                                              | 74      |

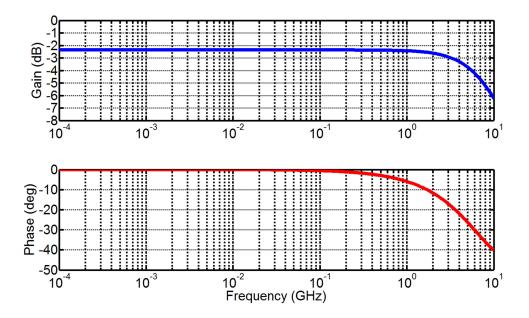

| 3.14 | Simulated front-end T/H buffer frequency response                                                                                                                                                                                                 | 75      |

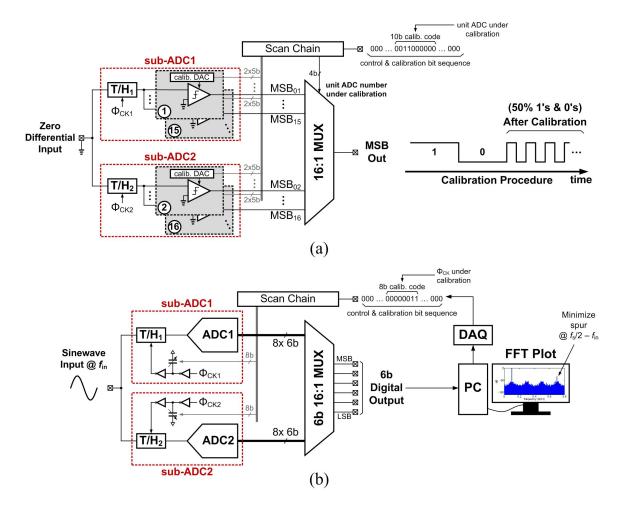

| 3.15 | Simplified diagrams of the foreground (a) offset calibration, and (b) clock skew calibration setups                                                                                                                                               | 76      |

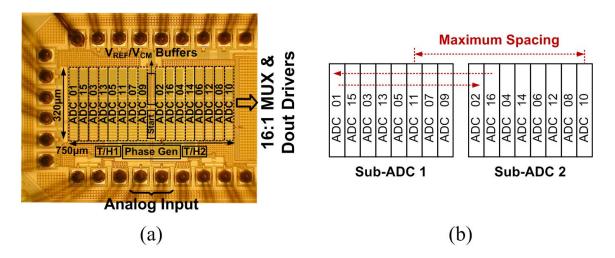

| 3.16 | Prototype ADC implemented in an LP 90nm CMOS process: (a) chip micrograph, and (b) optimized order of unit ADCs with respect to spacing between each two consecutive ADCs                                                                         | 78      |

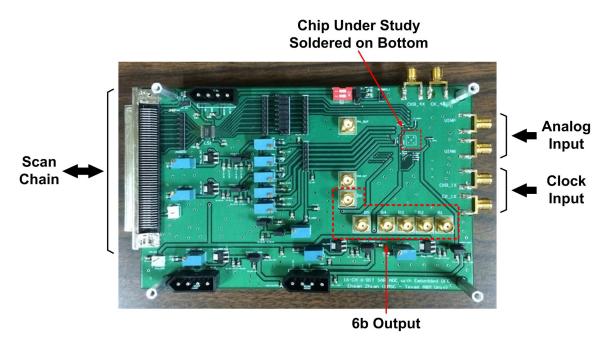

| 3.17 | Custom test board for the prototype 1.6GS/s ADC implemented in an LP 90nm CMOS process                                                                                                                                                            | 79      |

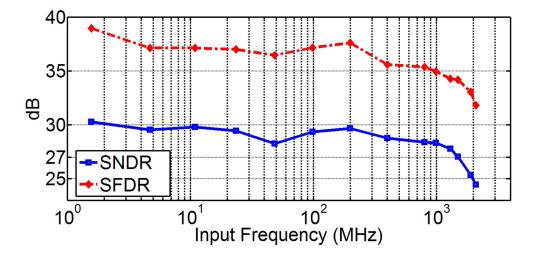

| 3.18 | ADC SNDR/SFDR vs. input frequency at $f_s = 1.6 \mathrm{GHz}.$                                                                                                                                                                                    | 80      |

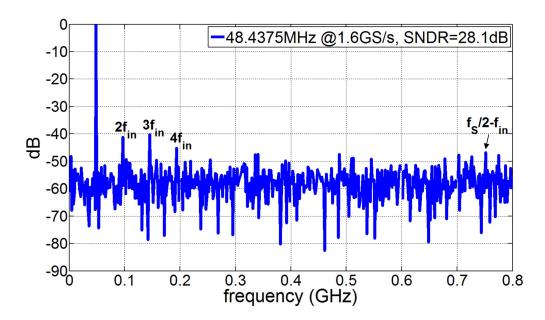

| 3.19 | The 1.6GS/s ADC normalized output spectrum for $f_{in}=48.437$ MHz.                                                                                                                                                                               | 81      |

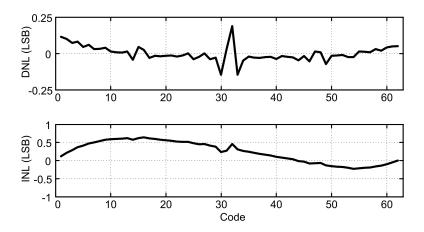

| 3.20 | DNL/INL plots with $f_{in}=2.7$ MHz at $f_s=1.6$ GHz                                                                                                                                                                                              | 82      |

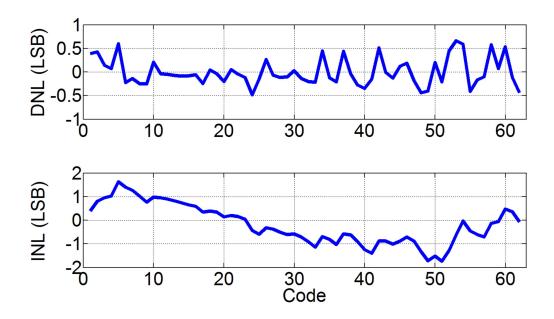

| 3.21 | Measured DFE tap coefficient range and resolution using a DC input voltage                                                                                                                                                                        | 82      |

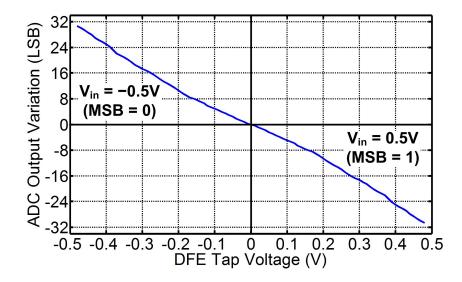

| 3.22 | $1.6 \text{Gb/s}$ ADC input generated by $2^{23}-1$ PRBS after a 2-tap FIR with 15dB de-emphasis, and measured digitized 6b ADC output (b) without, and (c) with 1-tap DFE enabled                                                                | 83      |

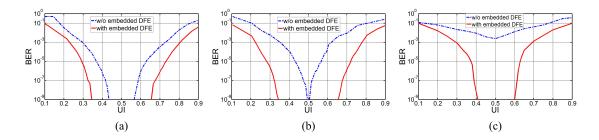

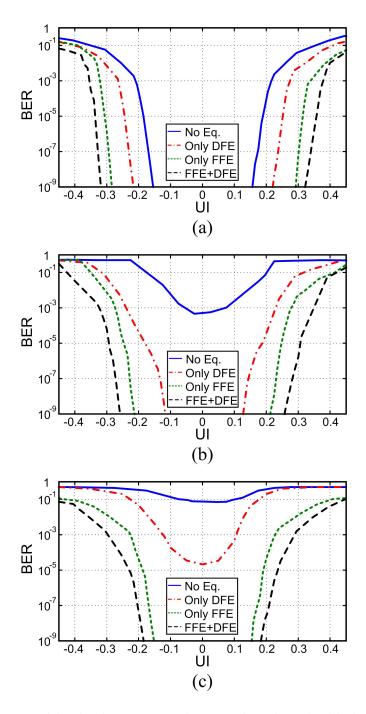

| 3.23 | Measured bathtub curves for the (a) 30-inch smooth, (b) 28-inch notch, and (c) 46-inch higher-loss FR4 channels shown in Fig. 3.3, with and without 1-tap embedded DFE for a $2^{10}-1$ PRBS input with $1V_{pp}$ TX swing and no TX equalization | 83      |

|      | 1, pp 111 5, mg ma no 111 oquanzanom                                                                                                                                                                                                              | $\odot$ |

| 3.24 | Measured bathtub curves for the (a) 30-inch smooth, and (b) 28-inch notch FR4 channels shown in Fig. 3.3, with and without 1-tap embedded DFE for a $2^{10} - 1$ PRBS input with $300mV_{pp}$ TX swing and no TX equalization                                                                                                                          | 83       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

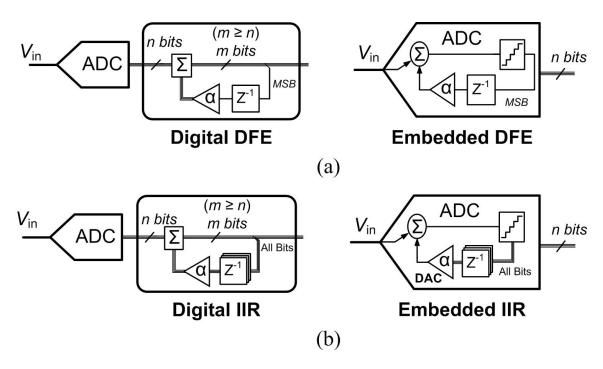

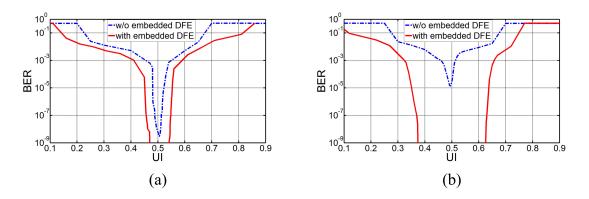

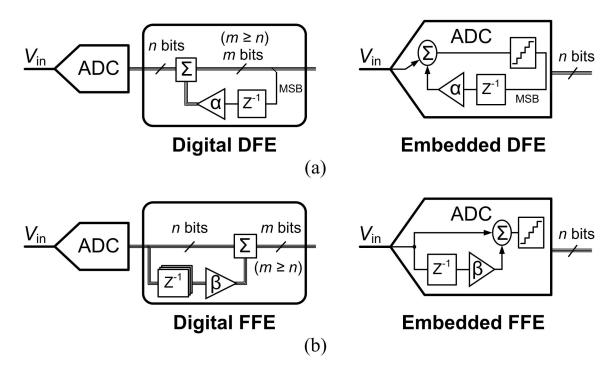

| 4.1  | Block diagrams of (a) digital versus embedded DFE, and (b) digital versus embedded FFE                                                                                                                                                                                                                                                                 | 90<br>91 |

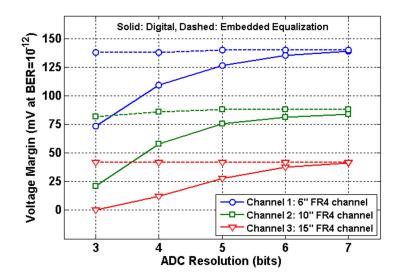

| 4.3  | Simulated voltage margin versus ADC resolution with both digital and embedded implementations of a 2-tap FFE + 1-tap DFE equalization structure for channels 1-3 in Fig. 4.2                                                                                                                                                                           | 92       |

| 4.4  | Impact of including embedded DFE and FFE equalization on (a) voltage margin and (b) timing margin for channels 1-3 in Fig. 4.2, with tap coefficients shown for the embedded equalization. (c) Impact of including embedded DFE and FFE equalization on voltage margin and timing margin in the presence of a front-end CTLE for channel 4 in Fig. 4.2 | 93       |

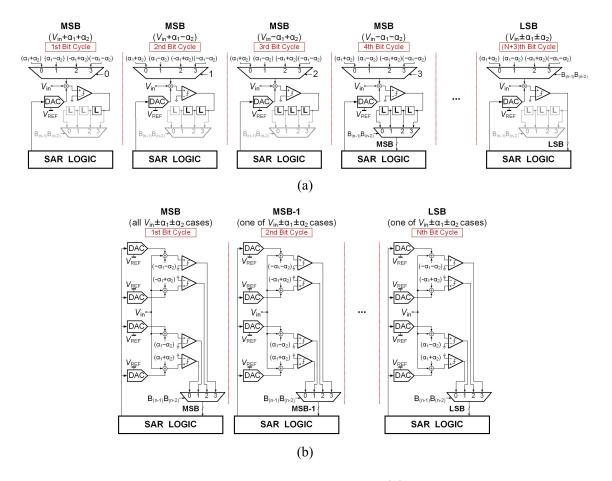

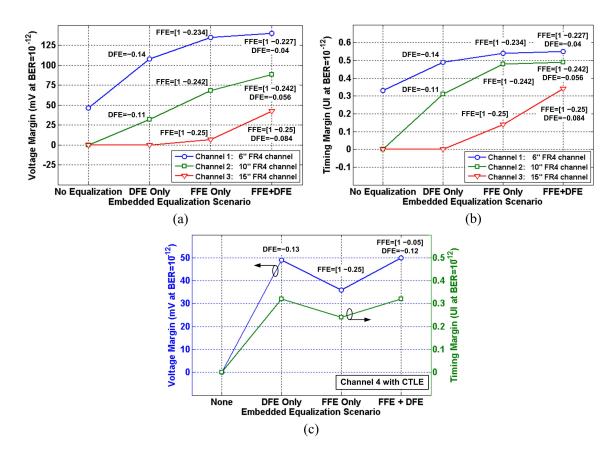

| 4.5  | Conceptual schematic of a unit SAR ADC with the proposed sampled 2-tap embedded FFE and redundant cycle 1-tap embedded DFE                                                                                                                                                                                                                             | 95       |

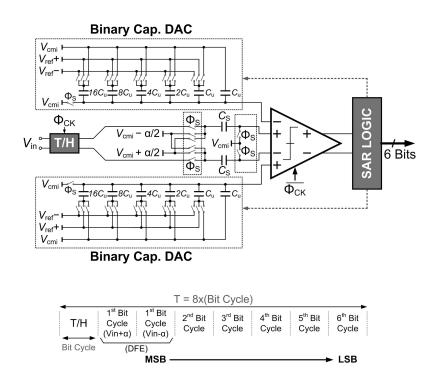

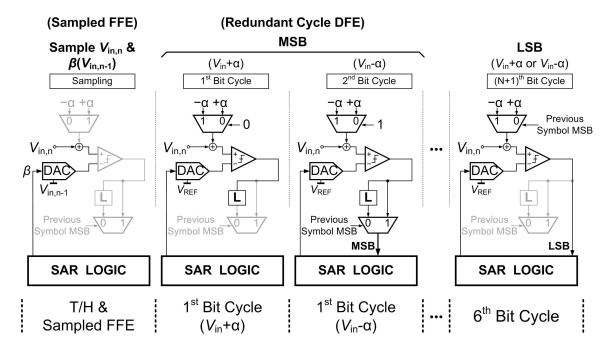

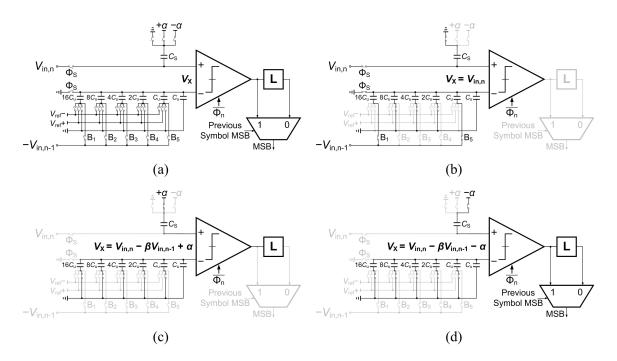

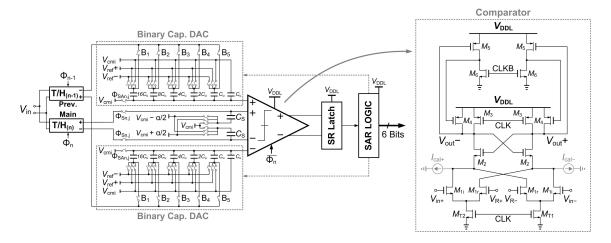

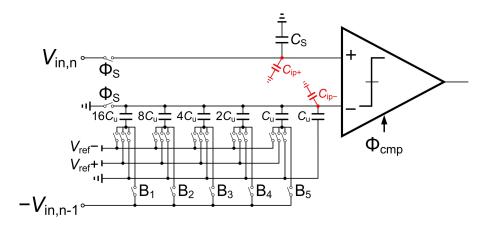

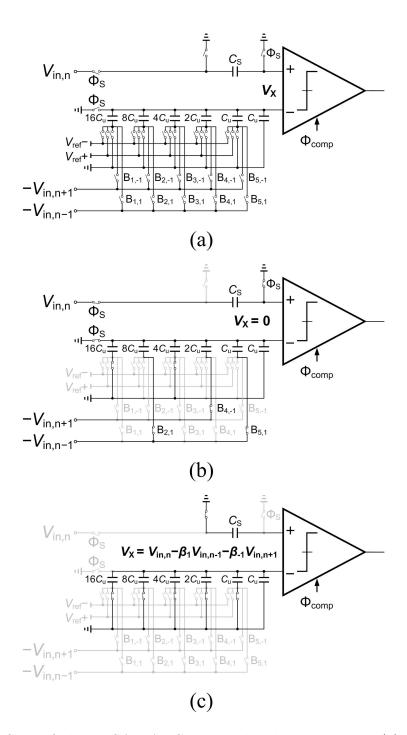

| 4.6  | Simplified unit SAR ADC with embedded 2-tap FFE and 1-tap DFE: (a) single-ended schematic, and operation during the (b) sampling phase, (c) first MSB evaluation, and (d) second MSB evaluation assuming $B_1B_2B_3B_4B_5 = 10001$ for the FFE                                                                                                         | 97       |

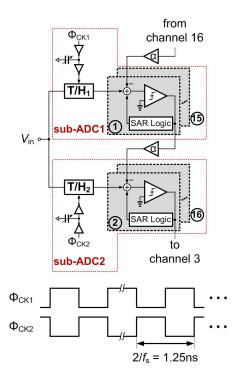

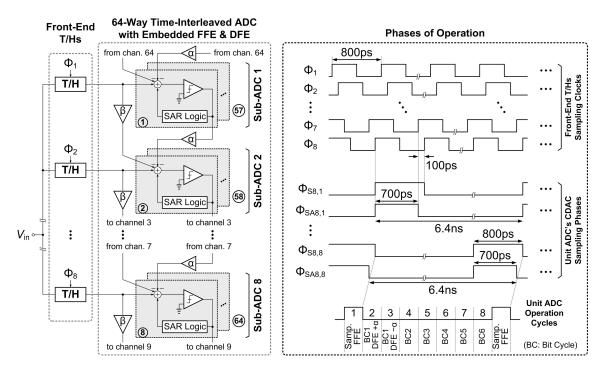

| 4.7  | Block diagram of the 64-way time-interleaved SAR ADC with embedded FFE and DFE                                                                                                                                                                                                                                                                         | 99       |

| 4.8  | Fully differential schematic of the unit ADC with sampled 2-tap embedded FFE and redundant cycle 1-tap embedded DFE                                                                                                                                                                                                                                    | 100      |

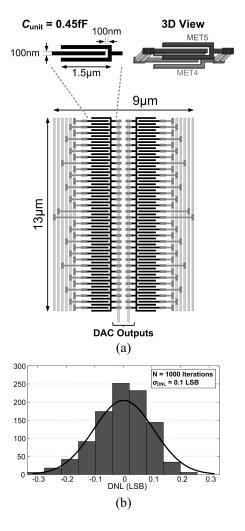

| 4.9  | (a) Custom layout of the capacitive DAC with $0.45fF$ MOM unit capacitors. (b) CDAC worst-case 01111 to 11111 transition DNL simulation results using 1000 Monte Carlo iterations                                                                                                                                                                      | 101      |

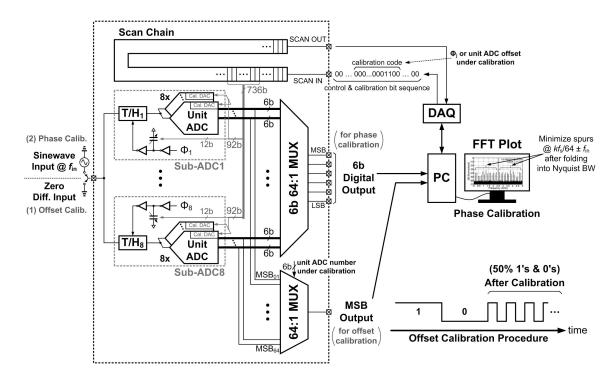

| 4.10 | Simplified diagram of the foreground offset and clock skew calibrations setup.                                                                                                                                                                                                                                                                         | 103      |

| 4.11 | Temperature dependency of residual unit ADC offset calibrated at $27^{\circ}C$ room temperature.                                                                                                                                                                                                                                                       | 104      |

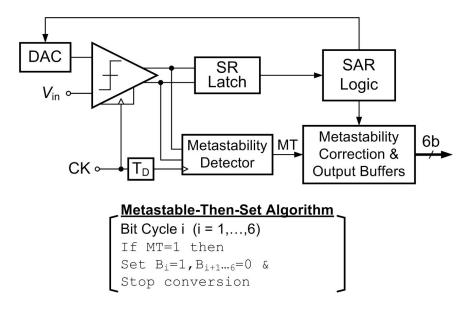

| 4.12 | Simplified metastability detection and correction block diagram and algorithm                                                                                                                                                                               | 105 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

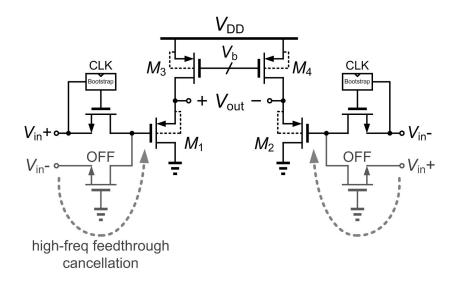

| 4.13 | Front-end T/H schematic with dummy OFF switches for high-frequency input feed-through cancellation                                                                                                                                                          | 106 |

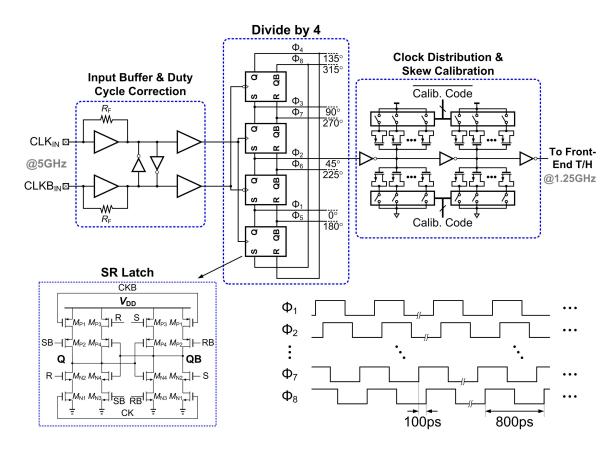

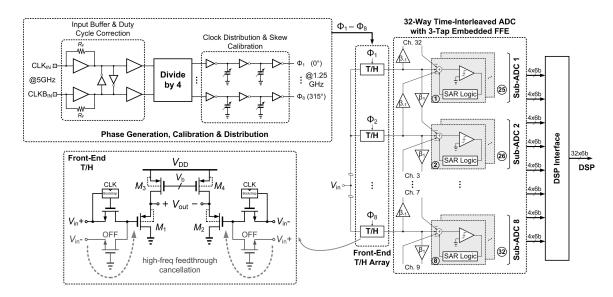

| 4.14 | Front-end T/Hs sampling clocks generation, distribution, and calibration network                                                                                                                                                                            | 107 |

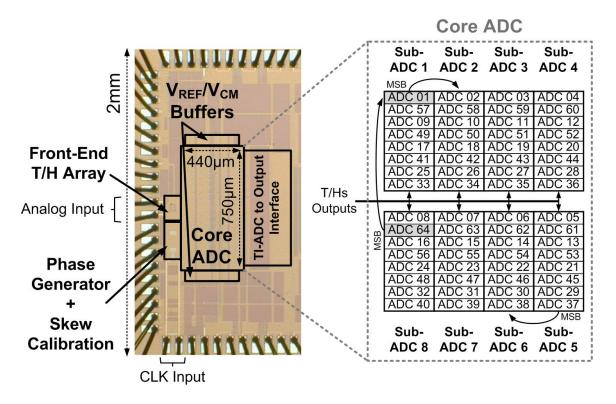

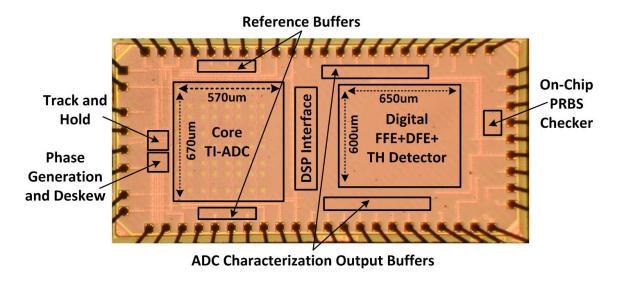

| 4.15 | Prototype ADC chip micrograph and core ADC floorplan                                                                                                                                                                                                        | 108 |

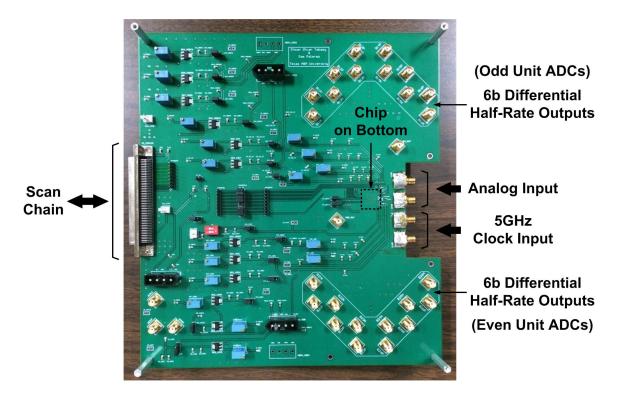

| 4.16 | Custom test board for the prototype 10GS/s ADC implemented in a GP 65nm CMOS process                                                                                                                                                                        | 109 |

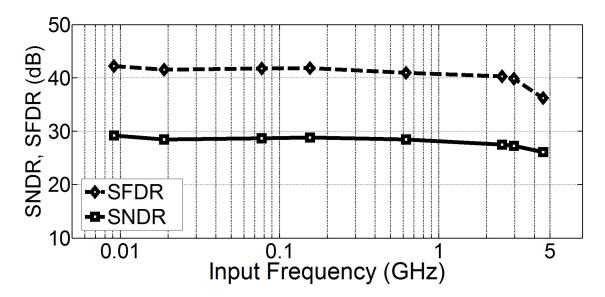

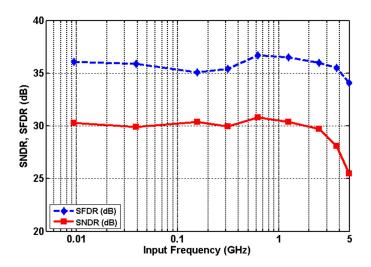

| 4.17 | ADC SNDR and SFDR vs. input frequency at $f_s=10~\mathrm{GHz}.$                                                                                                                                                                                             | 110 |

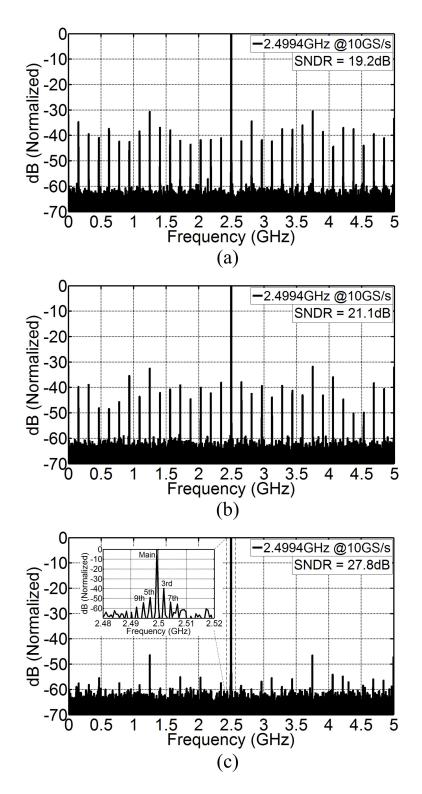

| 4.18 | 10-GS/s ADC normalized output spectrum for $f_{in} = 2.4994$ GHz using a 16k-point FFT: (a) before calibration, (b) after only offset calibration, and (c) after offset and clock skew calibration                                                          | 11  |

| 4.19 | DNL/INL plots with $f_{in}=9.746$ MHz at $f_s=10$ GHz                                                                                                                                                                                                       | 11: |

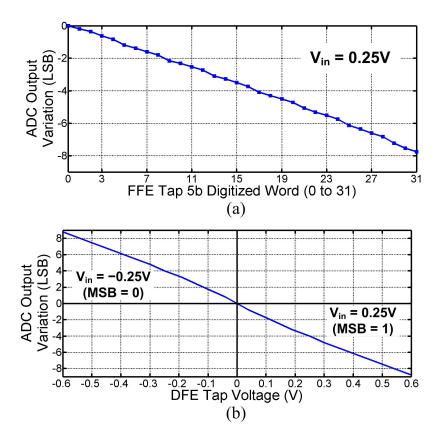

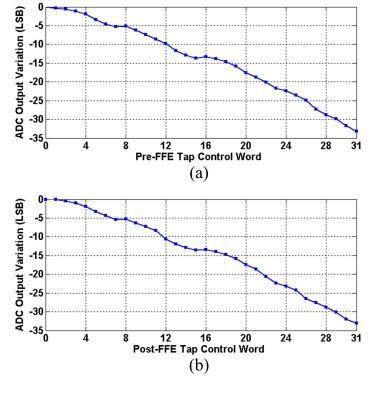

| 4.20 | Measured tap coefficient range and resolution using DC input voltages for embedded (a) FFE 2nd tap, and (b) 1-tap DFE                                                                                                                                       | 113 |

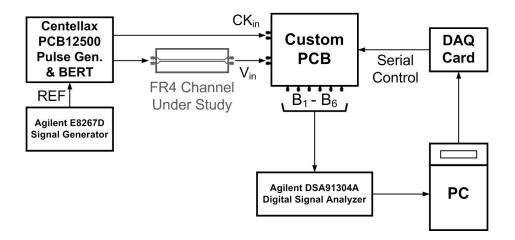

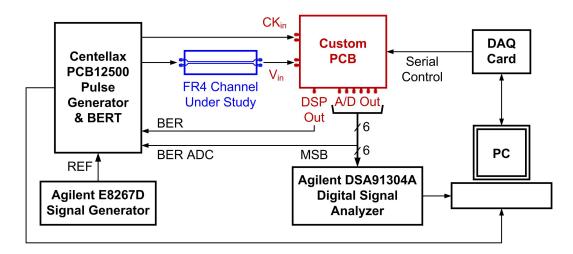

| 4.21 | Embedded equalization characterization test setup                                                                                                                                                                                                           | 114 |

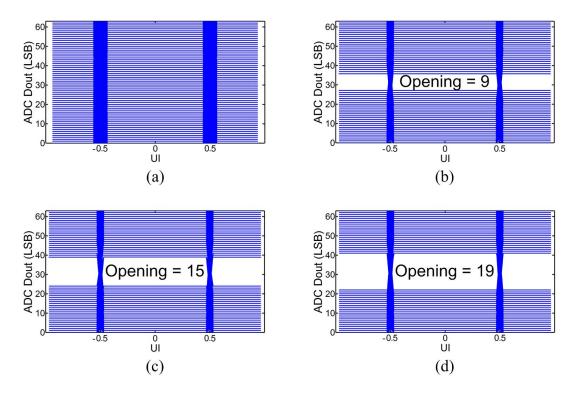

| 4.22 | Measured digitized 6b ADC output (a) without equalization, (b) with only 1-tap embedded DFE, (c) with only 2-tap embedded FFE, and (d) with both embedded FFE and DFE, for a 10-Gb/s $2^{10}-1$ PRBS input over a 10-inch FR4 channel                       | 11  |

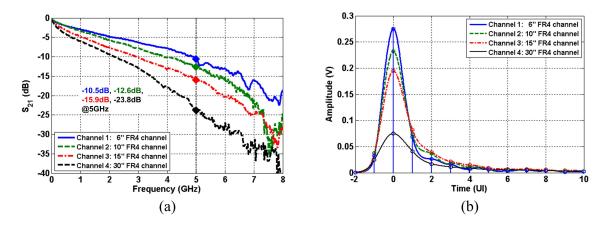

| 4.23 | Measured bathtub curves without and with embedded equalization for a $10\text{-Gb/s}\ 2^{10}-1$ PRBS input over (a) 6-inch FR4, (b) $10\text{-inch}\ FR4$ , and (c) $15\text{-inch}\ FR4$ channels, with channel frequency responses shown in Fig. $4.2(a)$ | 110 |

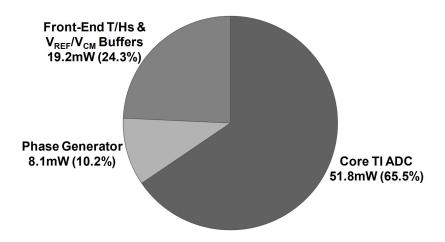

| 4.24 | 10 GS/s ADC power breakdown                                                                                                                                                                                                                                 | 11' |

| 4.25 | Simplified unit SAR ADC with limited ISI cancellation range for the embedded FFE equalization due to undesired attenuation at the comparator input for the equalization tap coefficients relative to the main cursor.                                       | 12  |

| 4.26 | Simplified unit SAR ADC with embedded 3-tap FFE: (a) single-ended schematic, and operation during the (b) sampling phase, and (c) first MSB evaluation assuming $B_{1,-1}B_{2,-1}B_{3,-1}B_{4,-1}B_{5,-1} = 00010$ for the pre-cursor tap, and $B_{1,1}B_{2,1}B_{3,1}B_{4,1}B_{5,1} = 01001$ for the post-cursor tap | 123 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.27 | Block diagram of the 32-way time-interleaved asynchronous SAR ADC with embedded 3-tap FFE                                                                                                                                                                                                                            | 124 |

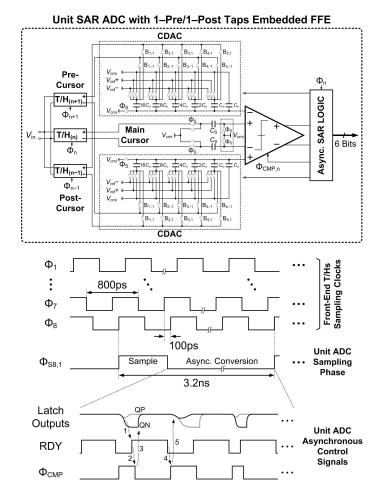

| 4.28 | Fully differential schematic of the unit asynchronous SAR ADC with sampled 3-tap embedded FFE                                                                                                                                                                                                                        | 126 |

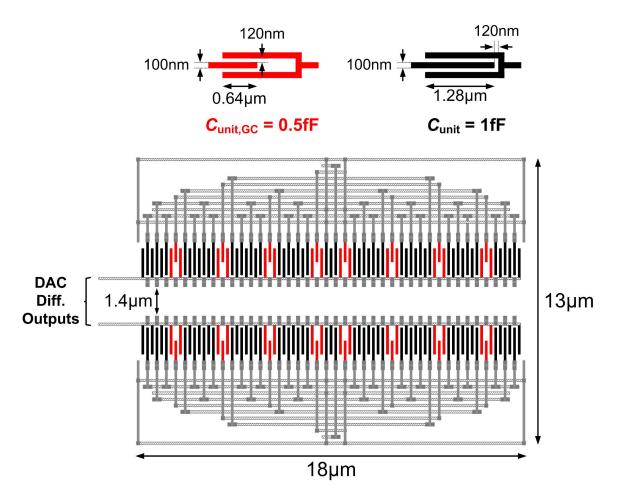

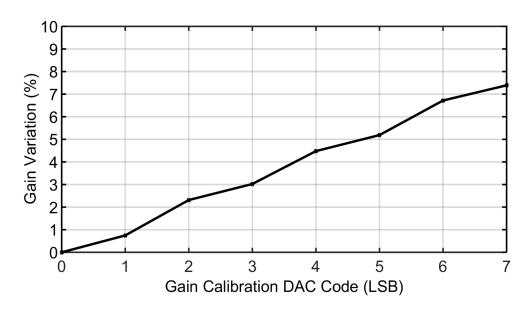

| 4.29 | Custom layout of the differential capacitive DAC with $1fF$ MOM unit capacitors and 4-bit embedded gain calibration                                                                                                                                                                                                  | 127 |

| 4.30 | Embedded gain calibration range and resolution for each capacitive DAC                                                                                                                                                                                                                                               | 128 |

| 4.31 | Prototype ADC chip micrograph                                                                                                                                                                                                                                                                                        | 128 |

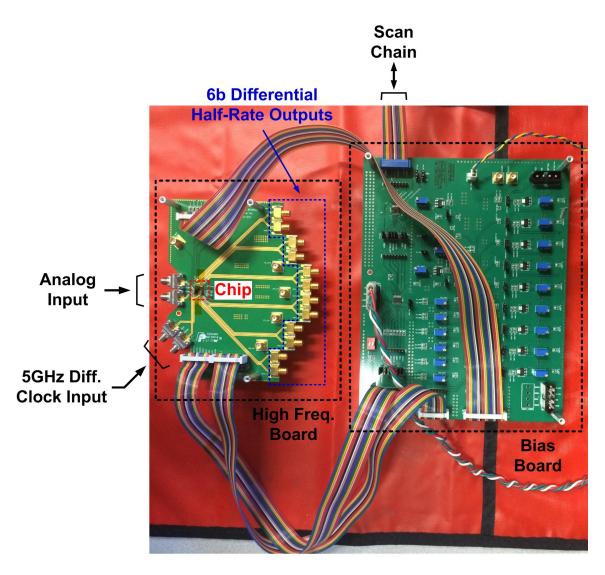

| 4.32 | Custom test boards for the prototype 10GS/s ADC implemented in a GP 65nm CMOS process. Two separate boards are designed: bias board and high-frequency board connected with ribbon cables for transferring the bias signals, supply voltages, and scan chain control bits                                            | 129 |

| 4.33 | ADC SNDR and SFDR vs. input frequency at $f_s=10$ GHz                                                                                                                                                                                                                                                                | 130 |

| 4.34 | Measured tap coefficient range and resolution using DC input voltages for embedded (a) FFE pre-cursor tap, and (b) FFE post-cursor tap                                                                                                                                                                               | 131 |

| 4.35 | Embedded equalization characterization test setup                                                                                                                                                                                                                                                                    | 132 |

| 4.36 | (a) FR4 channels under study, and (b) measured bathtub curves with embedded 3-tap FFE for a 10-Gb/s $2^{23}-1$ PRBS input over the three FR4 channels                                                                                                                                                                | 133 |

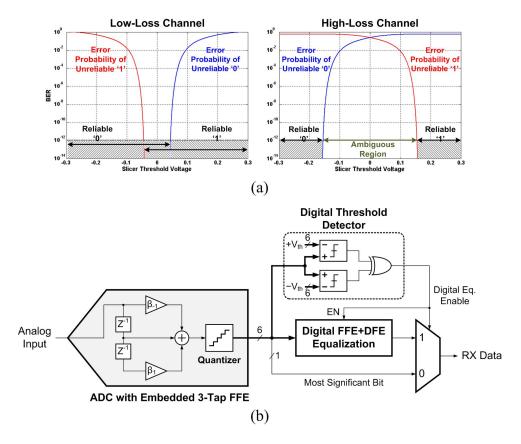

| 4.37 | (a) Receiver voltage margin BER bathtub curves with low- and high-<br>loss channels, and (b) simplified block diagram of the proposed hybrid<br>ADC-based receiver.                                                                                                                                                  | 135 |

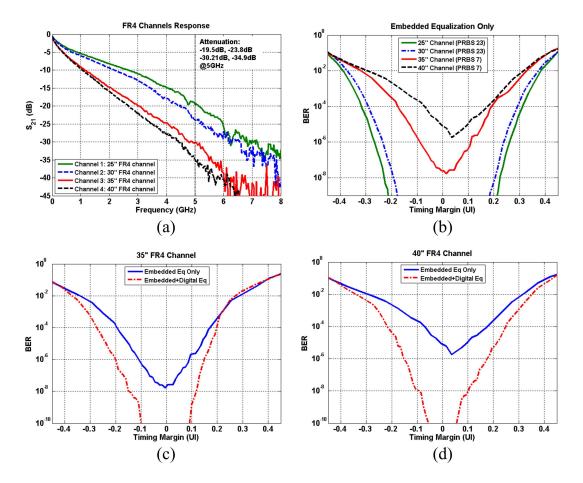

| 4.38 | (a) FR4 channels frequency response. (b) Received BER bathtub curves after the front-end ADC using only the embedded 3-tap FFE. Receiver BER bathtub curves with only embedded equalization and combined embedded plus digital equalization for (c) a 35" FR4 channel, and (d) a 40" FR4 channel | 137 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

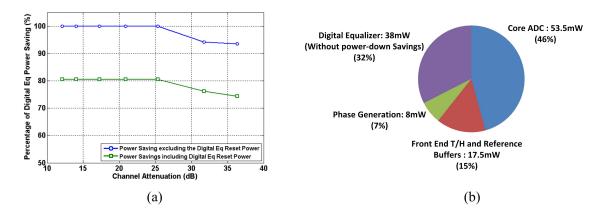

| 4.39 | (a) Hybrid ADC-based receiver digital equalizer power savings vs. channel attenuation (BER $< 10^{-10}$ ), and (b) receiver power breakdown                                                                                                                                                      | 138 |

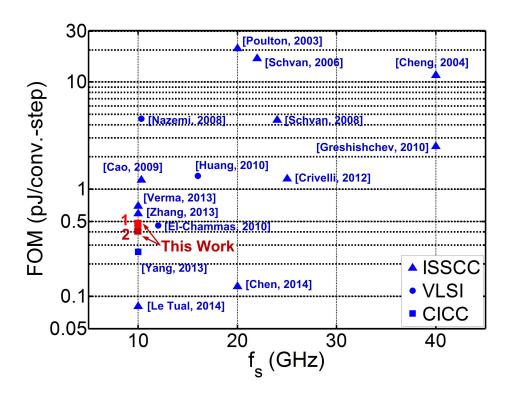

| 5.1  | ADC performance comparison against previous general purpose ADCs with 10+GS/s sampling rate                                                                                                                                                                                                      | 140 |

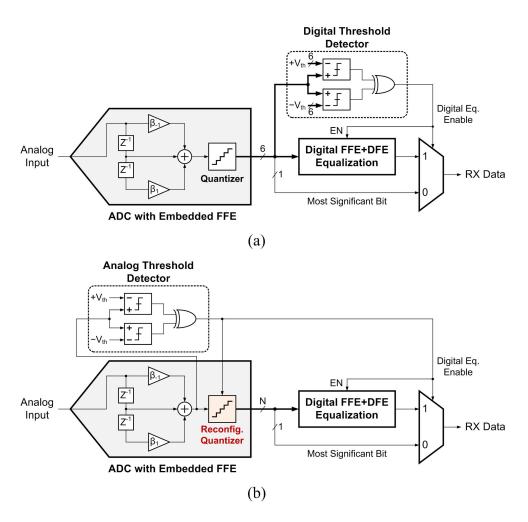

| 5.2  | Simplified block diagrams for (a) hybrid ADC-based RX with dynamically enabled digital equalizer, and (b) hybrid RX with dynamically enabled front-end ADC and digital equalizer                                                                                                                 | 145 |

# LIST OF TABLES

| ΓABLΙ | $\Xi$                                                     | I | Page |

|-------|-----------------------------------------------------------|---|------|

| 1.1   | Applications with $\geq$ 10Gb/s Data Rate                 |   | 3    |

| 3.1   | 16-Way 1.6GS/s 6-Bit ADC Performance Comparison           |   | 86   |

| 4.1   | 64-Way 10GS/s 6-Bit ADC Performance Comparison            |   | 119  |

| 4.2   | Proposed 10GS/s 6-Bit ADCs Performance Comparison         |   | 134  |

| 4.3   | Proposed 10Gb/s ADC-Based Receiver Performance Comparison |   | 139  |

#### 1. INTRODUCTION

With the advance of CMOS technology many applications are formed for wireline communications, and every year new applications are emerging, while standards supporting higher data transmission rates are being proposed for the existing applications. Most high-speed links serialize the parallel data for off-chip transmission due to the limited number of input/output (I/O) pads/pins and density constraints [1]. Examples of serial I/O links exist for interfacing processors to processors such as Intel QPI (6.4Gb/s) and AMD Hypertransport (6.4Gb/s), processors to peripherals such as PCIe (2.5, 5, 8Gb/s) and USB3 (4.8Gb/s), processors to memory such as RDRAM (1.6Gb/s) and XDR DRAM (7.2Gb/s), interfacing to storage units such as SATA (6Gb/s) and Fibre Channel (20Gb/s), and different networking standards such as Ethernet (1, 10Gb/s) for local area network (LAN), and SONET (2.5, 10, 40Gb/s) for wide area network (WAN).

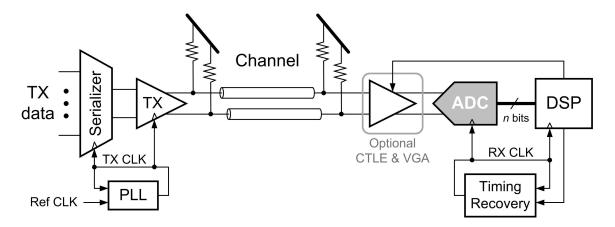

As the data rates of wireline communication links increases, channel impairments such as skin effect, dielectric loss, fiber dispersion, reflections and cross-talk become more pronounced. This warrants more interest in analog-to-digital converter (ADC)-based serial link receivers (Fig. 1.1), as they allow for more complex and flexible back-end digital signal processing (DSP) relative to binary or mixed-signal receivers [2–5]. Utilizing this back-end DSP allows for complex digital equalization and more bandwidth-efficient modulation schemes, while also displaying reduced process/voltage/temperature (PVT) sensitivity. Furthermore, these architectures offer straightforward design translation and can directly leverage the area and power scaling offered by new CMOS technology nodes.

One key issue with ADC-based receivers is the significant power consumption of

Figure 1.1: A high-speed electrical link system with an ADC-based receiver.

both the front-end ADC and the subsequent digital equalization and symbol detection at high data rates. Previous works, such as [5], [6], and [7], present techniques to reduce the front-end ADC power by using optimal positioning of threshold voltages, configurable resolution based on the channel characteristics, and mixed-mode pre-equalization. Embedding analog equalization in the ADC is another promising approach to both reduce ADC resolution and digital equalization complexity [8], allowing for improvements in overall receiver power consumption with low-overhead implementations of the common feed-forward equalizer (FFE) and decision-feedback equalizer (DFE) topologies used in wireline receivers [9–12].

This research targets the design of efficient ADC-based receivers with 10Gb/s data rate; however, the ideas proposed in this work can be extended to higher data rates, and they are compatible with (and may even benefit from) CMOS technology scaling. Some of the available current and future application standards with data rates around 10Gb/s and above are listed in Table 1.1.

Table 1.1: Applications with  $\geq$  10Gb/s Data Rate

| Technology                       | Application              | Data Rate (Gb/s) |

|----------------------------------|--------------------------|------------------|

| OC-192                           | Wide Area Network (WAN)  | 9.953            |

| OC-256                           | Wide Area Network (WAN)  | 13.271           |

| OC-768                           | Wide Area Network (WAN)  | 39.813           |

| OC-1536                          | Wide Area Network (WAN)  | 79.626           |

| OC-3072                          | Wide Area Network (WAN)  | 159.252          |

| 10 Gigabit Ethernet (10GBASE-X)  | Local Area Network (LAN) | 10               |

| Infiniband FDR-10 1x             | Local Area Network (LAN) | 10.31            |

| Infiniband FDR 1x                | Local Area Network (LAN) | 13.64            |

| Infiniband EDR 1x                | Local Area Network (LAN) | 25               |

| UPA                              | Computer Bus             | 15.36            |

| PCI Express (PCIe) 4.0 (x1 link) | Computer Bus             | 16               |

| Fibre Channel 16GFC              | Storage                  | 12               |

| Fibre Channel 16GFC              | Storage                  | 12               |

| Serial Attached SCSI (SAS) 3     | Storage                  | 12               |

| SATA Express 3.2                 | Storage                  | 16               |

| Serial Attached SCSI (SAS) 4     | Storage                  | 24               |

| USB 3.1                          | Peripheral               | 10               |

| Thunderbolt                      | Peripheral               | 10 x2            |

| Thunderbolt 2                    | Peripheral               | 20               |

### 1.1 Dissertation Organization

The challenges in the design of time-interleaved data converters are covered in Chapter 2. Main high-speed ADC architectures are briefly introduced and successive approximation register (SAR) topology, which is the architecture used in the rest of this work is explained in more details. Also, a brief discussion of high-speed links and receiver equalization techniques implemented in this work, namely feed-forward equalization (FFE) and decision feedback equalization (DFE), are given as a background to the rest of this dissertation.

The remainder of this work focuses on the analysis, design and implementation of different techniques to efficiently embed partial equalization inside the front-end high-speed ADC, and hence, improve the efficiency of the full ADC-based receiver.

Embedded multi-level DFE, which can be treated as embedded quantized infinite impulse response (IIR) equalization, has also been previously proposed for pipeline ADCs [13]. DFE is a very powerful equalization technique, as it can selectively reduce post-cursor ISI without amplifying noise or cross-talk. However, one important issue in any DFE implementation involves the critical feedback timing path from the decision comparator to the summation circuit that subtracts the post-cursor ISI. Loop unrolling can be employed to resolve this issue, where speculative comparison with a redundant comparator is used [14]. This approach, however, can incur significant hardware overhead [13]. Chapter 3 presents a time-interleaved (TI) SAR ADC architecture with a novel low-overhead 1-tap embedded DFE [15]. Statistical bit error rate (BER) simulation results are discussed, showing performance advantages with embedded DFE, and comparing it against embedded IIR equalization, for different FR4 channels. The novel embedded DFE technique, called redundant cycle DFE, which introduces an additional cycle in the time-interleaved SAR ADC in order to perform the DFE loop-unrolling with minimal hardware overhead, is proposed in this chapter. Experimental results of a 6-bit 1.6GS/s ADC prototype with the proposed embedded 1-tap DFE, fabricated in a low power (LP) 90nm CMOS technology, verifies the effectiveness of the embedded DFE.

Feed-forward equalizers are effective in canceling a large amount of inter-symbol interference (ISI) with a relatively small number of taps. A 2-tap version of this equalizer topology has been implemented in a time-interleaved (TI) flash ADC with additional CML input stages that follow the input track-and-holds (T/H) to realize the extra FFE tap [5]. While this approach is effective, significant linearity, speed, and power consumption trade-offs exist with this current-mode approach. FFEs have also been embedded in successive approximation register (SAR) ADCs [16], [17],

with charge-sharing in a capacitive digital-to-analog converter (CDAC) performing the signal scaling and summation of multiple input samples, followed by ADC conversion. However, a drawback of this single-CDAC approach is that the main cursor signal is attenuated such that the FFE tap sum is always fixed, similar to transmitter de-emphasis equalization [12]. Chapter 4 presents two 10GS/s 6-bit ADC solutions in 65nm CMOS that efficiently incorporate novel embedded equalization schemes. The first prototype is a 6-bit 10GS/s ADC with embedded 2-tap FFE and 1-tap DFE. The second prototype utilized in a full 10Gb/s receiver, includes a 3-tap embedded FFE, one pre-cursor and one post-cursor taps, with  $\sim 100\%$  main cursor amplitude range of operation for pre-cursor and post-cursor FFE tap coefficients. The statistical simulations of ADC-based receivers are carried out that quantify the performance advantages of these embedded equalization structures. The proposed embedded equalization techniques, which allow for flexibility in equalizer tap weighting at minimal hardware and power overhead, are analyzed in the same chapter, and experimental results from general purpose (GP) 65nm CMOS prototypes verify the effectiveness of the proposed embedded equalization structures.

Finally, in Chapter 5 the performances of the 10GS/s proposed ADCs are compared against the state-of-the-art general-purpose ADCs with similar resolution and data rates, and concluding remarks are drawn. At last, some recommendations are presented for curious researchers to follow up this work in the future.

#### 2. BACKGROUND ON HIGH-SPEED ADC-BASED RECEIVERS

This chapter explains briefly the details of two main building blocks in a wireline ADC-based receiver; namely, front-end baud-rate ADC and receiver equalization. First section discusses main building blocks and ADC architecture candidates in high-speed time-interleaved (TI) ADCs. Second section provides an introduction to high-speed link receivers. The main target for this chapter is to prepare the reader for the remainder of this dissertation.

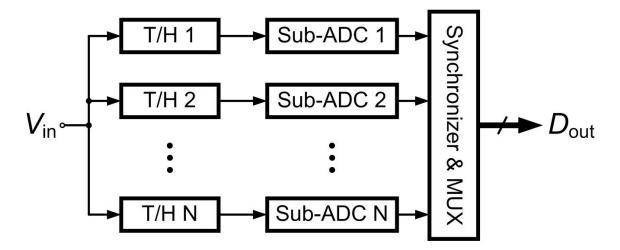

Fig. 2.1 shows the block diagram of a generic time-interleaved ADC with N parallel sub-ADCs, where each sub-ADC has a front-end track-and-hold (T/H). In this system, the sample rate of the full ADC is N times the sample rate of each sub-ADC [18]. This enables sampling rates higher than what is limited by the technology. In practice, however, non-idealities arising from differences among the interleaved channels can degrade the full ADC performance compared to the sub-ADCs.

Jitter is another important source of performance degradation in high-speed ADCs, which has nothing to do with the time-interleaving and can affect the performance of any converter, since it is an inevitable result of noise in electronic circuits. As it will be discussed later in this chapter, jitter impacts the ADC output signal-to-noise ratio, especially at high input frequencies, which is a problem in most Nyquist-rate time-interleaved ADCs targeting very high sampling rates.

#### 2.1 Time-Interleaving Challenges

The time-interleaved ADC performance is sensitive to any mismatch among the parallel converter channels, namely, offset, gain, and phase mismatches. Any of these mismatches can cause harmonic distortion, which degrades the ADC performance, and should be calibrated to the desired resolution level. The following sections discuss

Figure 2.1: Simplified block diagram of an N-way time-interleaved ADC.

each mismatch in detail.

#### 2.1.1 Offset Mismatch

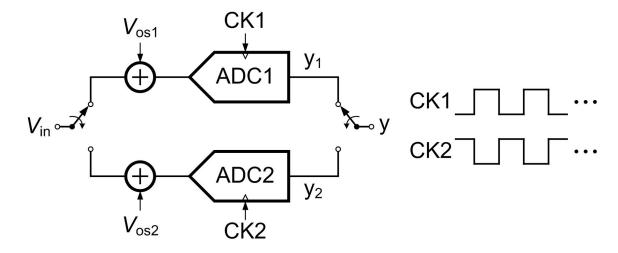

Offset mismatches among the parallel sub-ADCs introduce a periodic additive pattern to the output of the full ADC. For simplicity, we consider two sub-ADCs in the calculations here as shown in Fig. 2.2; however, the analysis can be extended to more number of parallel channels in general. Assuming a single-tone input,  $cos(\omega t + \phi)$ , the outputs of the two sub-ADCs only considering the offset voltages are [19], [20]

$$ADC1: y[n] = cos(\omega nT + \phi) + V_{os1} \qquad n = even,$$

(2.1)

$$ADC2: y[n] = cos(\omega nT + \phi) + V_{os2} \qquad n = odd,$$

(2.2)

where T is the sampling period of the overall ADC. The quantization noise is ignored for simplicity. Combining the two sub-ADC outputs, the overall ADC output can be expressed as

$$y[n] = cos(\omega nT + \phi) + V_{os} + (-1)^n \frac{\Delta V_{os}}{2},$$

(2.3)

Figure 2.2: Two-way time-interleaved ADC with offset mismatch.

where  $V_{os} = (V_{os1} + V_{os2})/2$  and  $\Delta V_{os} = V_{os1} - V_{os2}$ . Also,  $(-1)^n$  can be rearranged as  $(-1)^n = cos(\omega_S nT/2)$ , where  $\omega_S = 2\pi/T$  is the sampling frequency. Hence,

$$y[n] = \cos(\omega nT + \phi) + V_{os} + \frac{\Delta V_{os}}{2} \cos\left(\frac{\omega_S nT}{2}\right). \tag{2.4}$$

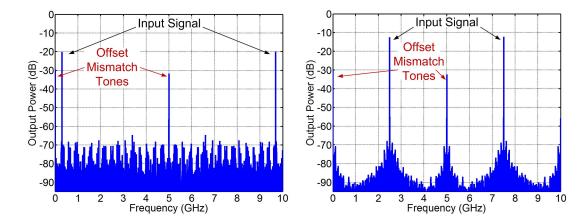

As shown by the second and third terms in Eq. 2.4, the offset mismatch results in two error terms for a 2-way time-interleaved ADC; a DC term and a single tone at half the sampling frequency in the overall ADC output. Another important observation is that these error terms are independent of the input amplitude and frequency. The two-way TI ADC is simulated in MATLAB assuming a 6-bit resolution for each sub-ADC. The simulated output spectrum only considering the impact of quantization noise and offset mismatch is shown in Fig. 2.3 for two cases with different input amplitudes and frequencies but similar offset errors. As expected the undesired tones due to offset mismatch are independent of the input amplitude and frequency.

A more general analysis shows that for an N-way time-interleaved ADC, the offset mismatch among the parallel channels results in distortion tones inside the ADC

Figure 2.3: Simulated output spectrum of a two-way time-interleaved ADC with offset mismatch for two different sets of input frequencies and amplitudes.

Nyquist bandwidth of the ADC output spectrum at frequencies  $(k/N)\omega_S$ , where k = 0, 1, 2, ..., N/2 [21].

The DC offset term can easily be removed. Regarding the other undesired spectral terms, only the matching of the offset voltage among all unit ADCs is critical. This means, the offset voltages in all unit ADCs do not need to be removed. One ADC can be picked and the offset in all other unit ADCs should be matched to the offset in the reference converter.

#### 2.1.2 Gain Mismatch

Gain mismatch among the time-interleaved unit ADCs can also degrade the overall ADC performance. Similar to the offset mismatch, if only two parallel unit ADCs with gains  $G_1$  and  $G_2$  and no other error are considered for simplicity as shown in Fig. 2.4, the unit ADCs outputs for a single-tone sinewave input are

$$ADC1: y[n] = G_1 cos(\omega nT + \phi) \qquad n = even,$$

(2.5)

Figure 2.4: Two-way time-interleaved ADC with gain mismatch.

$$ADC2: y[n] = G_2 cos(\omega nT + \phi) \qquad n = odd.$$

(2.6)

By combining the two equations, the overall ADC output is

$$y[n] = \left[G + (-1)^n \frac{\Delta G}{2}\right] \cos(\omega nT + \phi), \tag{2.7}$$

where  $G = (G_1 + G_2)/2$  and  $\Delta G = G_1 - G_2$ . By applying  $(-1)^n = \cos(\omega_S nT/2)$  in the previous equation, the ADC output terms can be rearranged as

$$y[n] = \left[G + \frac{\Delta G}{2}\cos\left(\frac{\omega_S nT}{2}\right)\right]\cos(\omega nT + \phi)$$

$$= G\cos(\omega nT + \phi) + \frac{\Delta G}{2}\cos\left(\frac{\omega_S nT}{2}\right)\cos(\omega nT + \phi).$$

(2.8)

By applying trigonometric identities while keeping only the terms inside the Nyquist band of the overall ADC, Eq. 2.8 is simplified to

$$y[n] = G\cos(\omega nT + \phi) + \frac{\Delta G}{2}\cos\left[\left(\omega - \frac{\omega_S}{2}\right)nT + \phi\right]. \tag{2.9}$$

Figure 2.5: Simulated output spectrum of a two-way time-interleaved ADC with gain mismatch for two different sets of input frequencies and amplitudes.

The second term in the above equation shows the undesired tone due to gain mismatch. This term depends on the input frequency but is independent of the input amplitude. The MATLAB behavioral model of a 6-bit time-interleaved ADC is used to show the output spectrum in the presence of gain mismatch for two cases with different input frequencies and amplitudes as shown in Fig. 2.5.

In the general case of N time-interleaved ADC structure with gain mismatch errors, the undesired distortion tones inside the Nyquist band appear at  $\pm \omega + (k/N)\omega_S$ , where k = 1, 2, ..., N/2 [21].

## 2.1.3 Phase Mismatch

Phase mismatch, also known as clock skew, is another challenging issue in the design of time-interleaved ADCs. If the analog input signal is sampled at exactly multiples of overall ADC sampling period  $T = 1/f_S$  in parallel unit ADCs, there is no phase mismatch. However, any deviation from the ideal sampling instants due to phase mismatch among the parallel unit ADCs results non-uniform sampling [22]. Let's consider the simplified two-way time-interleaved ADC again, this time with

Figure 2.6: Two-way time-interleaved ADC with phase mismatch.

only phase mismatch, as shown in Fig. 2.6. To model the phase mismatch, it is considered that ADC1 sampling instant is the reference, and ADC2 sampling instants are deviated from the ideal multiples of T by dt. The outputs of the two sub-ADCs can be expressed as

$$ADC1: y[n] = cos(\omega nT + \phi) \qquad n = even,$$

(2.10)

$$ADC2: \ y[n] = cos(\omega(nT+dt)+\phi) \quad \ n = odd, \eqno(2.11)$$

where the quantization error is ignored for simplicity. Combining the unit ADC outputs, the overall ADC output is

$$y[n] = \cos\left[\omega\left(nT + \frac{dt}{2} - (-1)^n \frac{dt}{2}\right) + \phi\right]. \tag{2.12}$$

Using  $(-1)^n = \cos(\omega_S nT/2)$  and the trigonometric identity  $\cos(A-B) = \cos(A)$

cos(B) + sin(A)sin(B), Eq. 2.12 can be simplified as

$$y[n] = \cos\left[\omega\left(nT + \frac{dt}{2}\right) + \phi\right] \cos\left(\frac{\omega dt}{2}\right) + \sin\left[\omega\left(nT + \frac{dt}{2}\right) + \phi\right] \cos\left(\frac{\omega_S nT}{2}\right) \sin\left(\frac{\omega dt}{2}\right). \tag{2.13}$$

Using the trigonometric identity  $sin(A)cos(\omega_S nT/2) = sin[A - (\omega_S nT/2)]$ , the previous expression can be modified as

$$y[n] = \cos\left(\frac{\omega dt}{2}\right) \cos\left[\omega\left(nT + \frac{dt}{2}\right) + \phi\right] + \sin\left(\frac{\omega dt}{2}\right) \sin\left[\omega\left(nT + \frac{dt}{2}\right) - \frac{\omega_S nT}{2} + \phi\right], \tag{2.14}$$

which after rearrangement can be expressed as

$$y[n] = \cos\left(\frac{\omega dt}{2}\right) \cos\left[\omega\left(nT + \frac{dt}{2}\right) + \phi\right] + \sin\left(\frac{\omega dt}{2}\right) \sin\left[\left(\omega - \frac{\omega_S}{2}\right)nT + \omega\frac{dt}{2} + \phi\right].$$

(2.15)

The first term represents the desired input with small amplitude modulation due to phase mismatch. The second term, however, represents the undesired tone at  $(\omega - \omega_S/2)$  frequency due to phase mismatch. Interestingly, the unwanted tone is exactly at the same frequency that the tone due to gain mismatch would appear but with 90° phase shift. Also, note that the phase mismatch error depends on both input frequency and amplitude. Assuming that the sampling instant deviation dt is much smaller than the sampling period T,  $cos(\omega dt/2) \approx 1$  and  $sin(\omega dt/2) \approx \omega dt/2$ . Hence, Eq. 2.15 can be simplified to a more intuitive form as

$$y[n] \approx \cos\left[\omega\left(nT + \frac{dt}{2}\right) + \phi\right] + \left(\frac{\omega dt}{2}\right)\sin\left[\left(\omega - \frac{\omega_S}{2}\right)nT + \omega\frac{dt}{2} + \phi\right].$$

(2.16)

Figure 2.7: Simulated output spectrum of a two-way time-interleaved ADC with phase mismatch for two different sets of input frequencies and amplitudes.

The output spectrum of a 6-bit 10GS/s two-way time-interleaved ADC in the presence of phase mismatch for two cases with different input frequencies and amplitudes is shown in Fig. 2.7, which verifies the previous analysis.

### 2.1.4 Phase Random Jitter

Another important challenge in high-speed data converters is the impact of random jitter in front-end sampling clock before quantization, which introduces aperture uncertainty at the sampling instants. At high input frequencies the effect of jitter exacerbates, which can limit the achievable SNR of a high data rate ADC in return. Hence, the maximum jitter specifications at maximum input frequency should be clearly calculated in order to derive the design requirements of the clock generator.

It can be proven that the A/D converter's SNR in the presence of sampling clock jitter for a generic input is calculated as [23]

$$SNR = 10\log_{10}\left(\frac{R_x(0)}{-R_x''(0) \cdot R_{tj}(0)}\right) dB, \qquad (2.17)$$

where  $R_x$  and  $R_{tj}$  are the autocorrelations of input and timing jitter, respectively.

This equation can be simplified for two common cases: a sinusoidal input, and a random signal input, which is more applicable to this research.

For the case of a sinusoidal input, assuming  $x(t) = A\sin(\omega t)$ , the input autocorrelation function is

$$R_x(t) = \frac{A^2}{2}\cos(\omega t). \tag{2.18}$$

By substituting this in 2.17, the well-known equation for SNR as a function of aperture jitter on the sampling instant of a sinusoidal signal can be achieved

$$SNR = 20\log_{10}\left(\frac{1}{\omega\sigma_{tj}}\right) dB. \tag{2.19}$$

## 2.1.4.2 Random Signal Input with Rectangular Spectrum

For the case of a random signal input with rectangular power spectrum,  $S_x(f) = rect(f/2f_B)$ , where  $f_B$  is the signal bandwidth, the input autocorrelation function can be derived as

$$R_x(t) = 2f_B \cdot \frac{\sin(\omega_B t)}{\omega_B t} \,. \tag{2.20}$$

By substituting this in 2.17, the SNR as a function of aperture jitter on the sampling instant of a random signal can be achieved

$$SNR = 20 \log_{10} \left( \frac{\sqrt{3}}{\omega_B \sigma_{tj}} \right) dB.$$

(2.21)

Comparing 2.19 and 2.21, it shows that the sampling time jitter is about 1.7 times relaxed for applications with random-type signals with rectangular power spectrum compared to applications with sinusoidal inputs and similar maximum input frequen-

cies. This is specifically important in high data rate ADC-based wireline receivers, similar to this research, that one of the main design challenges is to meet the jitter requirements at full Nyquist bandwidth.

### 2.2 High-Speed Track-And-Holds

Most analog to digital converters have a front-end sampler. In high-speed timeinterleaved structures, a front-end sampler can relax the timing accuracy requirements in the following stages.

Basically, a track-and-hold  $(T/H)^1$  consists of a switch and a load capacitor as shown in Fig. 2.8(a). However, in practice this structure can be used only for low-to-medium speed and/or low-resolution applications. The main issue with this simple structure is the kick-back from output to input. Besides, achieving a high input bandwidth becomes challenging for large load capacitance, especially in new CMOS technologies where the on-resistance of  $SW_1$  can be as large as hundreds of Ohms, and it changes as a function of input signal. This can result in non-linearity issues. Therefore, usually a closed-loop or open-loop active T/H topology is used to isolate input/output terminals and achieve higher linearity, as shown in Fig. 2.8(b) and (c).

In closed-loop T/H configuration, shown in Fig. 2.8(c), the sampling switch  $SW_1$  is located inside the feedback loop. So, this switch experiences a voltage swing much smaller than input and output swings; hence, the nonlinearity of sampling switch is reduced in contrast to open-loop topologies. The main limitation of closed-loop T/H circuits is speed considerations [24]. In tracking mode, circuit operates as a two-

<sup>&</sup>lt;sup>1</sup>Also sometimes referred as sample-and-hold (S/H) in the literature. However, in practice usually this structure tracks the input voltage during one operation phase and holds it during the next phase. Hence, track-and-hold seems a more suitable term and is used throughout this dissertation. Although beyond the scope of this research, there are other circuits that actually perform as a sample-and-hold.

Figure 2.8: (a) Simple T/H, b) practical open-loop T/H, and (c) a conventional implementation of closed-loop T/H.

stage opamp with  $C_H$  as a Miller capacitance. Another drawback of this structure is signal path from  $V_{in}$  to  $V_{out}$  through input capacitance of  $A_1$  opamp. This path introduces hold-mode high-frequency feed-through that affects the overall linearity. In summary, this structure is suitable for high-accuracy applications, however, low-to-medium speeds [25].

In contrast to closed-loop structures, an open-loop topology, as shown in Fig. 2.8(b), can potentially achieve the highest possible speed in a given technology. Besides, by using a good buffer the kickback problem and input-to-output feed-through issues related to simple structure of Fig. 2.8(a) can be alleviated.

Consider the basic T/H circuit shown in Fig. 2.8(a). In order to achieve a signal-to-noise ratio (SNR) >40dB (= 6.35 effective number of bits) using this simple circuit, the maximum input-referred noise and the minimum load capacitance (for  $V_{in,pp} = 1V$ ) can be calculated as

$$SNR = \frac{v_{in,pp}^2/8}{v_{nrms,in}^2} = \frac{v_{in,pp}^2/8}{kT/C_L} > 40 \, dB \,,$$

(2.22)

which results in  $v_{nrms,in} < 3.5 mV_{rms}$ , and  $C_L > 0.33 fF$ . It can be concluded that the T/H stage performance is not limited by the sampling noise for the target applications

of this research. For BW > 5GHz and  $C_L = 200fF$ , maximum switch on-resistance can be found

$$BW = \frac{1}{2\pi R_{on}C_L} > 5 GHz \quad \Rightarrow \quad R_{on} < 159 \,\Omega.$$

(2.23)

While this value for switch on-resistance may seem trivial, it should be noted that as shown later for large input swings and low supply voltages this constraint proves to become stringent and even impossible for a simple NMOS or PMOS switch. Based on these results, it is obvious that the linearity of the T/H with the mentioned required specifications is very important.

In this section, different blocks in a high-speed open-loop T/H are analyzed briefly. The simplest CMOS buffer can be realized by a source-follower (SF) stage. Since most today technologies are N-well processes, our discussions are focused on using the PMOS source-follower buffer in order to remove the non-desirable MOS body effects by connecting the transistor body terminal to its source.

Fig. 2.9 shows two basic implementations of a single-ended source-follower based buffer with approximately unity gain. At first look, an ideal current source with high output impedance, for example a cascode current source, may seem a better implementation for having a larger output impedance and more constant current. However, it is not the optimum choice for this particular application. The linearity of source-follower buffer depends on the linearity of  $M_1$  transconductance  $g_{m1}$ , which can be approximated by the following equation using a square-law MOS device behavior.

$$g_m \approx \frac{2I_D}{(V_{GS} - V_{th})} \,. \tag{2.24}$$

Figure 2.9: Source-follower buffer using (a) an ideal current source, and (b) a simple PMOS current source.

Since these buffers are working in open-loop configuration, the input transistor sees large voltage swing, and hence  $V_{GS}$  can change, while  $I_D$  is almost constant for a cascode current source. This results in a variable  $g_m$  depending on the input voltage, and hence output voltage distortion [26], [27]. However, for the simple buffer in Fig. 2.9(b), as  $V_{GS}$  varies,  $I_D$  changes in the same direction which results in a more constant input transconductance; therefore better linearity. Besides, Fig. 2.9(b) usually has a larger output voltage swing compared to Fig. 2.9(a).

Based on the previous discussion, the basic pseudo-differential open-loop T/H structure is shown in Fig. 2.10. The main advantages of this structure are its simplicity, and large output swing compared to higher stacked buffers. Note that the dummy NMOS transistors in series with input NMOS switches, where the source terminal is shorted to the drain, are for clock feed-through and charge-injection cancellations.

Figure 2.10: Pseudo-differential source follower based T/H stage using simple NMOS switches.

## 2.2.2.1 Switch Design

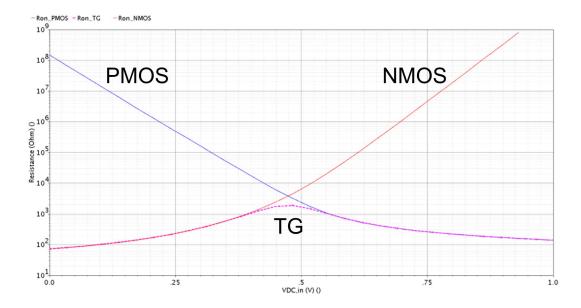

As mentioned before, for high input voltage swing and/or low supply voltage, achieving a linear switch may be challenging. Fig. 2.11 shows three basic switch topologies: single NMOS, single PMOS, and transmission gate (TG), also known as CMOS switch. The on-resistance  $R_{on}$  of each topology as a function of input voltage is shown in Fig. 2.12. As expected, NMOS switch works better at switching of small input voltages, while PMOS switch is suitable for large input voltage switching. The range of  $R_{on}$  variation is approximately  $100\Omega - 100M\Omega$ . The on-resistance of a TG switch on the other hand is always equal to the parallel combination of the two NMOS and PMOS switches, which is less than a few kilo Ohms for the whole input voltage range. Therefore, this topology is extensively used in high-speed applications.

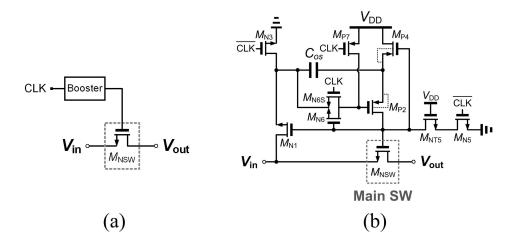

In the past two decades, many other modified switch topologies have been proposed. Most of them can be categorized into two basic families: (1) Clock-boosting switch, and (2) bootstrapped switch. A common approach for achieving improved linearity switch is by boosting the clock amplitude, as shown in Fig. 2.13(a) [28,29]. This technique is generally known as "clock boosting". This technique is fast and usually implemented by boosting the nominal clock amplitude through a charge-

Figure 2.11: Simple switch architectures: (a) Single NMOS or PMOS switch, and (b) complementary MOS switch also known as transmission gate.

pump stage. However, it introduces some reliability issues, since for small input voltages close to zero, gate-source voltage of NMOS switch  $M_{NSW}$  can become larger than  $V_{DD}$ , which in return can cause breakdown of the switch transistor.

Another common switch modification is bootstrapped technique shown in Fig. 2.13(b) for a well-known implementation [30]. In this structure, when the clock signal CLK is low, rail-to-rail supply voltage is placed over  $C_{os}$  capacitor. When CLK goes high,  $C_{os}$  is placed between the gate and source terminals of the main switch transistor  $M_{NSW}$ . This way, ideally the gate-source voltage of  $M_{NSW}$  is always equal to the supply voltage  $V_{DD}$  independent of the input voltage, which results in a small and constant  $R_{on}$  for the whole range of operation. Therefore, it performs very linearly. However, the main tradeoff is the large area required for  $C_{os}$ .

In this section, many buffer topologies suitable for high-speed applications are reviewed. All these architectures are originated from the simple source-follower stage. The simplest source-follower (SF) buffer, as discussed earlier, is shown in Fig. 2.9(b).

Figure 2.12: On-resistance of NMOS, PMOS and transmission-gate switches versus input voltage amplitude (Wn =  $10\mu m$ , Wp =  $20\mu m$ , with minimum length L = 100nm, and  $V_{DD}=1V$  in 90nm CMOS technology).

This structure has a large output swing. The main issue is that the output impedance is approximately  $1/g_{m1}$  in this topology. This means that a very large current is required to achieve bandwidth in giga-Hertz range, especially for driving a large load capacitance. Therefore, in the following sections some modifications of this basic structure is analyzed.

The bandwidth of a SF-based buffer is dependent on the time constant of the dominant pole at its output node as  $BW \approx 1/(2\pi R_{out}C_L)$ , where  $R_{out} \approx 1/g_{m1}$ . Hence, for achieving a large bandwidth output resistance and/or output capacitance should be decreased. In a conventional SF-based buffer with a fixed load capacitance, this can be accomplished only by increasing the current consumption. Recently, negative impedance converter (NIC) topologies have been used to cancel part of the load capacitance using a negative capacitance, and therefore increase the bandwidth and/or power efficiency [31,32]. A basic NIC structure is shown in Fig. 2.14(a) used

Figure 2.13: Modified switch topologies: (a) Clock-boosting switch, and (b) bootstrapped switch.

at the output node of a SF-based buffer [32]. The output impedance of NIC circuit can be calculated as

$$Z_{out,NIC} = -\frac{1}{sC_C} \cdot \frac{g_{m7,8} + s(C_{gs7,8} + 2C_C)}{g_{m7,8}}, \ s = j\omega \ll 2\pi f_T$$

(2.25)

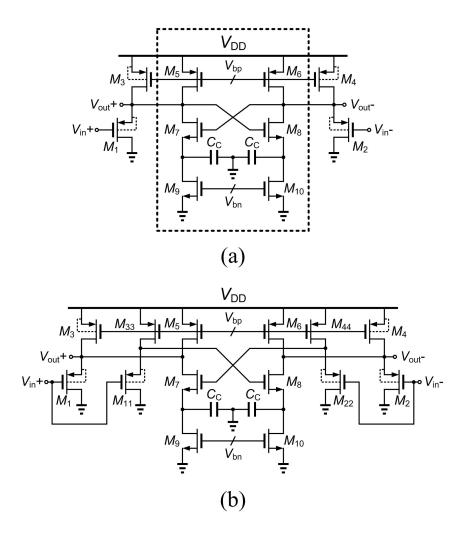

Although Fig. 2.14(a) topology has been used previously in many different applications, it introduces some reliability issues due to the positive feedback loop. Therefore, oscillation may occur due to process/temperature variations. A more robust design for negative-impedance implementation in a fully-differential structure is shown in Fig. 2.14(b) [33]. In this new structure, a replica source-follower stage is used in order to remove the undesirable feedback from differential outputs to each other. In other words, the capacitance cancellation is performed using feed-forward paths. Although the NIC-based structures work pretty well at low frequencies, unfortunately their performance improvement fades away at high frequencies.

As mentioned earlier, for a single-pole buffer  $BW \approx 1/(2\pi R_{out}C_L)$ . This means

Figure 2.14: Pseudo-differential source-follower based buffer using negative capacitance (a) in a positive feedback configuration, and (b) in a feed-forward configuration.

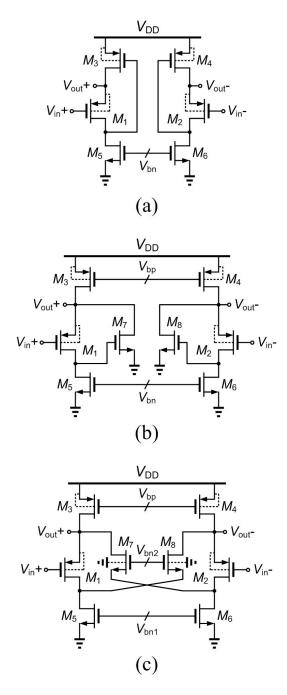

the buffer bandwidth can be increased either by decreasing the load capacitance, as performed in the NIC structures, or by decreasing the output resistance. Flipped-voltage follower (FVF) technique delivers a smaller output resistance by the order of  $g_m r_o$  compared to a conventional source-follower stage [34], [35]. The differential version of conventional FVF-based buffer is shown in Fig. 2.15(a). The topology of

Fig. 2.15(a), however, has a very limited input voltage swing range, as shown below

$$V_{DD} - |V_{GS3}| - |V_{th1}| < V_{in} < |V_{th1}| + |V_{th3}| - |V_{GS1}|.$$

(2.26)

A modified version of this structure called folded FVF is shown in Fig. 2.15(b). In this circuit the input swing range has increased to

$$V_{GS7} - |V_{th1}| < V_{in} < V_{DD} - |V_{OV3}| - |V_{GS1}|. (2.27)$$