# PATTERNING ORGANIC ELECTRONICS BASED ON NANOIMPRINT LITHOGRAPHY

A Dissertation

by

# YI-CHEN LO

## Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

| Chair of Committee, | Xing Cheng             |

|---------------------|------------------------|

| Committee Members,  | Rusty Harris           |

|                     | Edgar Sanchez-Sinencio |

|                     | Jaime Grunlan          |

| Head of Department, | Chanan Singh           |

May 2014

Major Subject: Electrical and Computer Engineering

Copyright 2014 Yi-Chen Lo

#### ABSTRACT

The objective of this work is to investigate a high-resolution patterning method based on nanoimprint lithography (NIL) for the fabrication of organic electronics. First, a high-resolution, nondestructive method was developed to pattern organic semiconductors. In this approach, a sacrificial template made of amorphous fluorinated polymer (Teflon-AF) was first patterned by NIL. Poly(3-hexylthiophene) (P3HT), a organic semiconductor, was then spin-coated on the Teflon-AF template. Removing the sacrificial template by a fluorinated solvent achieved high-resolution P3HT patterns. P3HT lines and squares of various sizes (0.35 micron to tens of microns) were obtained by this method. This process of removing the sacrificial template is fully compatible with organic semiconductors. This technique was then used to fabricate passive-matrix organic light-emitting diode (PMOLED) arrays for flat-panel display applications.

Fabrication of a self-aligned bottom gate electrode for organic metal semiconductor field effect transistor (OMESFET) was also developed. This self-aligned gate allows the transistor to have a potential to operate in the high frequency. Owing to the lack of an insulating layer, OMESFET can also work in a relatively low voltage range compared to other organic field effect transistors with an insulating layer. This work also demonstrates its capability of patterning alternating self-aligned metals at the nanoscale.

This research also developed a low-cost and time-saving technique to create nanostructures by transferring nanoscale polymeric sidewalls into a substrate. This polymer sidewall transfer lithographic technique can be used for generating nanostructures without advanced electron-beam lithography. Potential applications include the fabrication of nanoimprint molds with high-resolution patterns for applications in nanofluidics and nanophotonics. The polymeric sidewall is a vertically spreading layer deposited by spin-coating a polymer solution on a vertical template. Varying processing parameters such as the solution concentration or the spin-coating speed, changes the sidewall dimension, which, after pattern transfer, also changes the structure dimension on the substrate. High-resolution trenches of about 15 nm have been achieved after transferring straight-line sidewalls into the substrate. Other than straight-line sidewall patterns, this method also fabricated ring-shaped patterns including circles, squares, and concentric squares.

Finally, a new structure of organic solar cells (OSCs) was investigated for increasing the solar power conversion efficiency. Although the experimental result did not meet the theoretical expectation, reasonable modifications of the device structure will be tested to achieve the goal in the future.

#### ACKNOWLEDGEMENTS

First, I want to thank my parent and my family for supporting me parts of my financial expenses to pursue the PhD degree. I also want to thank my wife for her encouragement and love. Their great supports help me concentrate on my research works and complete the PhD degree.

Second, I would like to thank my advisor, Prof. Cheng for his guidance and support throughout the course of this research. I also would like to thank my committee members, Prof. Grunlan, Prof. Harris, and Prof. Sanchez, for their helpful suggestions during my research study.

Third, I would like to thank all my colleagues at Texas A&M University for all the project discussions. These helpful discussions helped me to overcome many experimental difficulties.

Finally, thanks also go to my friends, the department staff, the AggieFab staff, and all the people I know for giving me a wonderful time during my study at Texas A&M University.

iv

# NOMENCLATURE

| AFM                            | Atomic force microscope            |

|--------------------------------|------------------------------------|

| Al                             | Aluminum                           |

| Al <sub>2</sub> O <sub>3</sub> | Aluminum oxide                     |

| Ar                             | Argon                              |

| Au                             | Gold                               |

| BHJ                            | Bulk heterojunction                |

| Cr                             | Chromium                           |

| CVD                            | Chemical vapor deposition          |

| DCB                            | 1,2-Dichlorobenzene                |

| DPI                            | Dots per inch                      |

| DSSCs                          | Dye-sensitized solar cells         |

| DUV                            | Deep ultraviolet lithography       |

| EUV                            | Extreme ultraviolet lithography    |

| FDTS                           | Perfluorodecyltrichlorosiliane     |

| g <sub>m</sub>                 | Transconductance                   |

| HCL                            | Hydrochloric acid                  |

| HFEs                           | Hydrofluoroethers                  |

| HfO <sub>2</sub>               | Hafnium oxide                      |

| HMDS                           | Hexamethyldisilazane               |

| НОМО                           | Highest occupied molecular orbital |

| ICP                            | Inductively coupled plasma                                    |

|--------------------------------|---------------------------------------------------------------|

| ITO                            | Indium tin oxide                                              |

| $N_2$                          | Nitrogen                                                      |

| NIL                            | Nanoimprint lithography                                       |

| OFESC                          | Organic field effect solar cell                               |

| OFETs                          | Organic field effect transistors                              |

| OLEDs                          | Organic light emitting diodes                                 |

| OMISFET                        | Organic metal insulator semiconductor field effect transistor |

| OMESFET                        | Organic metal semiconductor field effect transistor           |

| OSCs                           | Organic solar cells                                           |

| РСВМ                           | [6,6]-Phenyl- C61 butyric acid methyl ester                   |

| PECVD                          | Plasma enhanced chemical vapor deposition                     |

| PEDOT:PSS                      | poly(3,4-ethylenedioxythiophene) poly(styrenesulfonate)       |

| PMOLED                         | Passive matric organic light emitting diode                   |

| РЗНТ                           | poly(3-hexylthiophene)                                        |

| RIE                            | Reactive ion etching                                          |

| SAM                            | Self-assembled monolayer                                      |

| SEM                            | Scanning electron microscope                                  |

| SFIL                           | Step and flash imprint lithography                            |

| $SF_6$                         | Sulfur hexafluoride                                           |

| Si <sub>3</sub> N <sub>4</sub> | Silicon nitride                                               |

| SiO <sub>2</sub>               | Silicon dioxide                                               |

Glass transition temperature

$T_{g}$

# TABLE OF CONTENTS

| Pa                                                                                                                                                                                                                                                                                                                                                  | ige                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| ABSTRACT                                                                                                                                                                                                                                                                                                                                            | ii                                        |

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                    | .iv                                       |

| NOMENCLATURE                                                                                                                                                                                                                                                                                                                                        | v                                         |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                   | /iii                                      |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                     | X                                         |

| CHAPTER I INTRODUCTION AND LITERATURE REVIEW                                                                                                                                                                                                                                                                                                        | 1                                         |

| <ul> <li>1.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                 | 2<br>4<br>6<br>6<br>6<br>8<br>8<br>8<br>9 |

| CHAPTER II HIGH-RESOLUTION NON-DESTRUCTIVE PATTERNING OF ISOLATED ORGANIC SEMICONDUCTORS FOR DEVICE APPLICATIONS                                                                                                                                                                                                                                    | 13                                        |

| <ul> <li>2.1 Introduction</li> <li>2.2 Experimental method</li> <li>2.3 Results and discussion</li> <li>2.3.1 Patterning polymer sacrificial template</li> <li>2.3.2 Patterning isolated organic semiconductor structures</li> <li>2.3.3 Patterning OLED arrays</li> <li>2.3.4 Advantages and future development</li> <li>2.4 Conclusion</li> </ul> | 14<br>16<br>16<br>19<br>23<br>25          |

| CHAPTER III FABRICATING ORGANIC METAL-SEMICONDUCTOR FIELD<br>EFFECT TRANSISTOR (OMESFET) OF SELF-ALIGNED BOTTOM GATE                                                                                                                                                                                                                                | 29                                        |

| 3.1 Introduction                                         |    |

|----------------------------------------------------------|----|

| 3.2 Experimental method                                  |    |

| 3.3 Results and discussion                               |    |

| 3.3.1 OMESFET of self-aligned gate electrode             | 35 |

| 3.3.2 Self-aligned metal in nanoscale                    | 41 |

| 3.4 Conclusion and future work                           | 42 |

|                                                          |    |

| CHAPTER IV HIGH-RESOLUTION PATTERNING BY POLYMERIC       |    |

| SIDEWALL TRANSFERRED LITHOGRAPHY                         | 45 |

|                                                          |    |

| 4.1 Introduction                                         | 45 |

| 4.2 Experimental method                                  |    |

| 4.3 Results and discussion                               |    |

| 4.3.1 Sidewall fabrication and pattern transfer          | 48 |

| 4.3.2 Change of trench dimension                         |    |

| 4.3.3 Ring-shaped sidewall contours                      | 56 |

| 4.4 Conclusion                                           | 57 |

|                                                          |    |

| CHAPTER V FIELD EFFECT SOLAR CELLS                       |    |

| 5.1 Introduction                                         | 50 |

| 5.1 Introduction                                         |    |

| 5.3 Discussion and measurement results                   |    |

|                                                          |    |

| 5.4 Conclusion and future work                           | 0/ |

| CHAPTER VI CONCLUSIONS AND FUTURE WORKS                  | 68 |

|                                                          | 00 |

| REFERENCES                                               |    |

|                                                          |    |

| APPENDIX A P3HT/PCBM BILAYER ORGANIC SOLAR CELL          | 83 |

|                                                          |    |

| APPENDIX B ENCAPSULATION FOR ORGANIC TRANSISTORS         | 88 |

| APPENDIX C REDUCTION OF CONTACT RESISTANCE IN P3HT BASED |    |

| ORGANIC FIELD EFFECT TRANSISTORS                         | 02 |

|                                                          |    |

# LIST OF FIGURES

| Figure 1. 1. | Fundamental principles of thermal nanoimprint lithography and UV nanoimprint lithography.                                                                                                                                                                                                                                                                                                                                                                                                       | .3 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1. 2. | The sub-10 nm patterns fabricated by NIL. The figure on the left is the nanoimprint mold of 10 nm protrusions in dimension and the one on the right is the imprinted patterns on the imprint resist[8]                                                                                                                                                                                                                                                                                          | .3 |

| Figure 1. 3. | The process of fabricating an imprinting mold                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .5 |

| Figure 1. 4. | The photolithography patterning method for organic semiconducting materials and the organic semiconducting material patterned by photolithography[15]                                                                                                                                                                                                                                                                                                                                           | .7 |

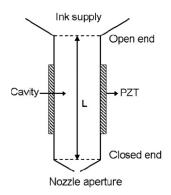

| Figure 1. 5. | The piezoelectric ink-jet printing nozzle with piezoelectric tubular actuator attached on the side in order to eject a fixed volume of solutions[18]                                                                                                                                                                                                                                                                                                                                            | .8 |

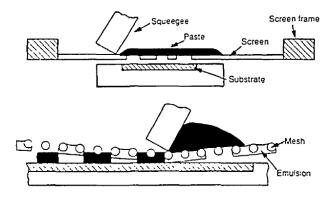

| Figure 1. 6. | The schematic diagram of the screen printing principle[20].                                                                                                                                                                                                                                                                                                                                                                                                                                     | .9 |

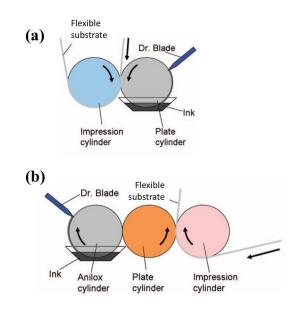

| Figure 1. 7. | Schematic diagram of (a) gravure printing and (b) flexo printing[21]                                                                                                                                                                                                                                                                                                                                                                                                                            | 10 |

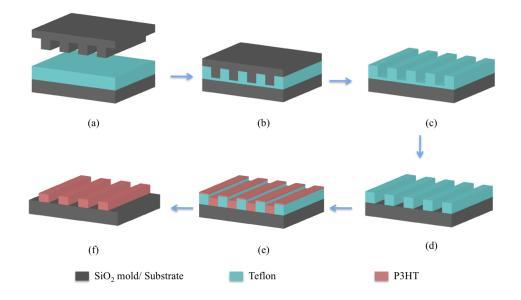

| Figure 2. 1. | Schematics of nondestructive patterning of isolated P3HT by<br>nanoimprint. (a) Spin-coat the Teflon-AF solution to form a thin<br>Teflon-AF film. (b) Thermally imprint the Teflon-AF film by a<br>nanoimprint mold. (c) After releasing the mold, patterns are generated<br>in the Teflon-AF film. (d) Remove the residual layer by oxygen RIE.<br>(e) Spin-coat P3HT on the Teflon-AF sacrificial template. (f) Dissolve<br>the Teflon-AF template in FC-40 solvent to obtain P3HT patterns. | 16 |

| Figure 2. 2. | Contact angles of water droplet on different Teflon-AF surface<br>conditions. (a) Pristine Teflon-AF after spin-coating. (b) Teflon-AF<br>after oxygen RIE. (c) RIE-treated Teflon-AF after 1 minute annealing<br>at 160°C. (d) RIE-treated Teflon-AF after 1 minute annealing at 240°C.<br>(e) Water contact angle variation after 1 minute annealing at different<br>temperatures.                                                                                                            | 18 |

| Figure 2. 3. | Images of isolated P3HT grating patterns achieved by nanoimprint and sacrificial template. (a) and (b) show the optical image and the fluorescent image of 50 $\mu$ m P3HT gratings, respectively. (c) and (d) show the optical image and the fluorescent image of 5 $\mu$ m P3HT                                                                                                                                                                                                               |    |

|              | gratings, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                       | .20 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2. 4. | Images of P3HT square patterns achieved by nanoimprint and sacrificial template. (a) and (b) show the optical microscope image and the fluorescent microscope image of 1 $\mu$ m P3HT squares, respectively. (c) and (d) show the optical microscope image and the fluorescent microscope image of 0.5 $\mu$ m P3HT squares, respectively.                                                                                                                   | .21 |

| Figure 2. 5. | Scanning electron microscopy (SEM) monographs of 350 nm P3HT grating patterns. (a) Teflon-AF and the P3HT patterns before removing the Teflon-AF template. (b) Cross-sectional view of 350 nm P3HT patterns after dissolving the Teflon-AF template.                                                                                                                                                                                                         | .22 |

| Figure 2. 6. | Schematics of the fabrication process for the passive-matrix organic<br>light-emitting diode (PMOLED) array. (a) Pattern ITO on a glass<br>substrate. (b) Spin-coat Teflon-AF on the substrate. (c) Thermally<br>imprint Teflon-AF with a nanoimprint mold. (d) Remove the residual<br>layer by oxygen RIE. (e) Deposit a stack of PEDOT:PSS, P3HT and Al.<br>(f) Dissolve the Teflon-AF template to liftoff the PEDOT:PSS/P3HT/Al<br>stack on the template. | .24 |

| Figure 2. 7. | PMOLED array patterned by nanoimprint and sacrificial template.<br>(a) The vertical stripes are 50 µm ITO patterns and the horizontal stripes are stacks of PEDOT:PSS/P3HT/Al. The intersections of the vertical and the horizontal patterns are OLED pixels. (b) Optical image of the electrically biased PMOLED array.                                                                                                                                     | .25 |

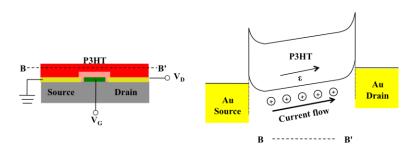

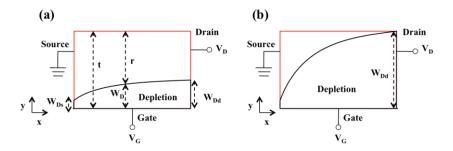

| Figure 3. 1. | Schematic diagrams of OMESFET in both top gate configuration and<br>bottom gate configuration. The overlap area between the gate and the<br>source/drain in the bottom gate structure is smaller than that in top gate<br>structure.                                                                                                                                                                                                                         | .31 |

| Figure 3. 2. | The fabrication process of OMESFETs with a self-aligned gate electrode.<br>(a) Spin-coat an imprinting resist (PMMA or Teflon) on the Au/Cr<br>surface. (b) Thermally imprint the resist. (c) Remove the imprinting<br>mold. (d) Use RIE to remove the residue layer of the resist. (e) Over etch<br>the Au/Cr. (f) Deposit Al/Cr as the gate electrode. (g) Dissolve the resist<br>to liftoff the Al/Cr (h) Spin-coat P3HT.                                 | .32 |

| Figure 3. 3. | The detail of forming the depletion region. (a) The depletion region<br>expands and turns of the conducting channel when increasing the<br>reverse gate bias. (b) The energy band diagrams perpendicular to the<br>gate electrode show the cause of the depletion region in P3HT and the<br>expansion of the depletion region. (c) The energy band diagrams along                                                                                            |     |

|              | the source and drain electrodes show the condition at equilibrium and at the reverse gate bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

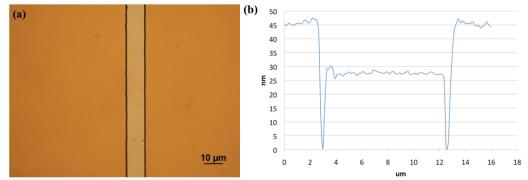

| Figure 3. 4. | (a) The optical microscope image of the OMESFTs electrodes. The Au sorce/drain electrodes are separated by the Al gate electrode. (b) The AFM image of the device cross-section                                                                                                                                                                                                                                                                                                                                                                                                                    |

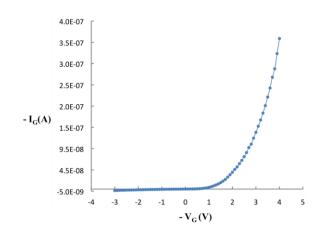

| Figure 3. 5. | Rectifying response of the MESFET measuring from the Al electrode37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

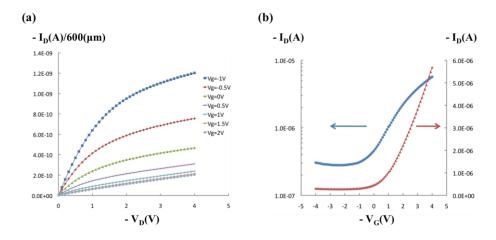

| Figure 3. 6. | Electric responses of the P3HT based OMESFETs of 10 µm channel<br>length and 600 µm channel width. (a) Width normalized I-V response.<br>(b) Transfer characteristics                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 3. 7. | The electric field in the P3HT film drives the current flowing from the source electrode to the drain electrode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 3. 8. | The P3HT channel diagram in (a) the linear region and (b) the saturation region40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

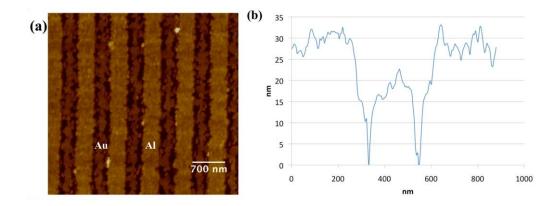

| Figure 3. 9. | Alternating Au and Al metal lines in nanoscale. (a) AFM image.<br>(b) Cross-section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

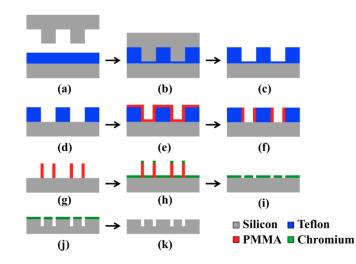

| Figure 4. 1. | Schematics of the experimental processing. (a) Spin-coat the Teflon-AF solution to form a thin film. (b) Thermally imprint the film with a grating mold. (c) The pattern of the mold is transferred into the Teflon-AF film. (d) Remove the Teflon-AF residue layer by oxygen RIE. (e) Spin-coat the PMMA solution on Teflon-AF. (f) Remove the PMMA residue layer by oxygen RIE. (g) Dissolve Teflon-AF by FC-72 solvent. (h) Deposit a thin Cr layer. (i) Remove the PMMA sidewalls and liftoff the Cr on the PMMA. (j) Use Cr as a mask and etch the silicon substrate. (k) Remove the Cr layer |

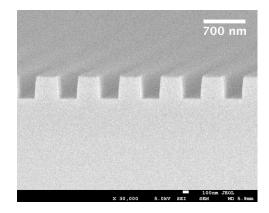

| Figure 4. 2. | The nanoimprint mold of 700 nm periodic grating with 300 nm trenches, 400 nm protrusions and 350 nm depth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

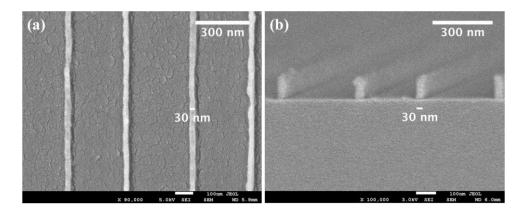

| Figure 4. 3. | <ul><li>PMMA sidewalls after completely removing the Teflon-AF template.</li><li>(a) Top view of PMMA sidewalls. (b) The profile of PMMA sidewalls51</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                     |

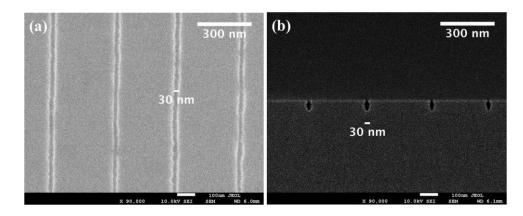

| Figure 4. 4. | (a) The top-view of the trench patterns after transferring sidewalls into the substrate. (b) The cross-section of the trench patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

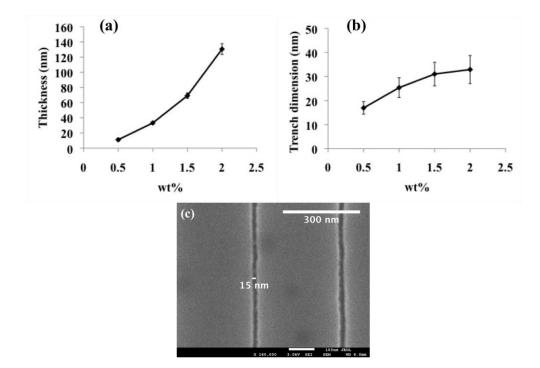

| Figure 4. 5. | (a) PMMA residue thicknesses in the Teflon-AF template with respect to PMMA solution concentrations. (b) Trench dimensions with respect to PMMA solution concentrations. (c) Trenches of about 15 nm were                                                                                                                                                                                                                                                                                                                                                                                          |

|              | achieved by processing the 0.5 wt% PMMA solution at 3000 rpm                                                                                                                                                                                                                                                                                                                                                                  | .54 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

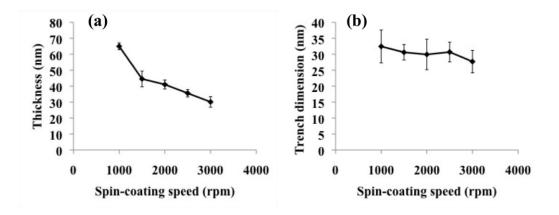

| Figure 4. 6. | (a) PMMA residue thicknesses in the Teflon-AF template with respect to spin-coating speeds. (b) Trench dimensions with respect to spin-coating speeds.                                                                                                                                                                                                                                                                        | .55 |

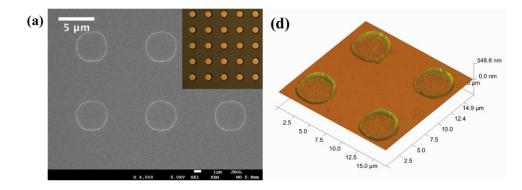

| Figure 4. 7. | SEM images of PMMA sidewall contours: (a) circles, (b) squares, and (c) concentric squares. The inset images are their corresponding molds for creating the sidewalls. Three-dimensional AMF images of the sidewall contours: (d) circles, (e) squares, and (f) concentric squares                                                                                                                                            | .56 |

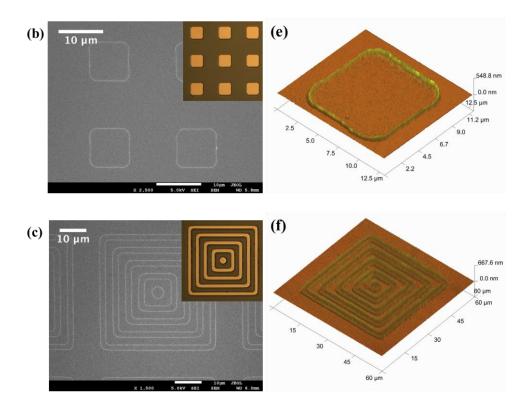

| Figure 5. 1. | The process of fabricating a field effect solar cell. (a) Deposit $Si_3N_4$ on<br>thermally grown $SiO_2$ . (b) Pattern Au grating as the anode electrode.<br>(c) Deposit Teflon-AF as a patterning template. (d) Expose Au electrode<br>by patterning the Teflon-AF layer. (e) Deposit PEDOT:PSS as the hole<br>transport layer and mixture of P3HT and PCBM as the active layer.<br>(f) Deposit ITO as a cathode electrode. | .61 |

| Figure 5. 2. | The 100 nm Au grating of a 50% duty cycle patterned on the $Si_3N_4$ serving as the organic solar cell anode                                                                                                                                                                                                                                                                                                                  | .62 |

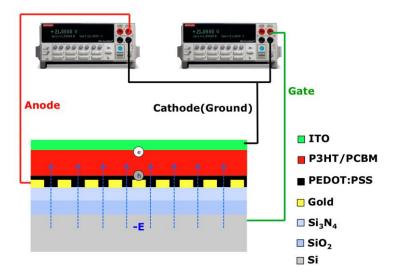

| Figure 5. 3. | The experimental setup for testing the organic field effect organic solar cell (OFESC) and the OFESC device structure.                                                                                                                                                                                                                                                                                                        | .64 |

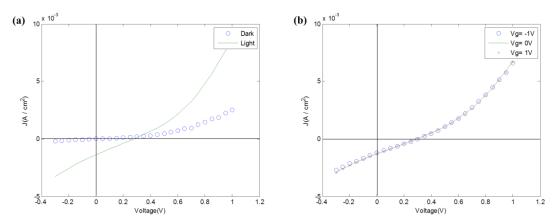

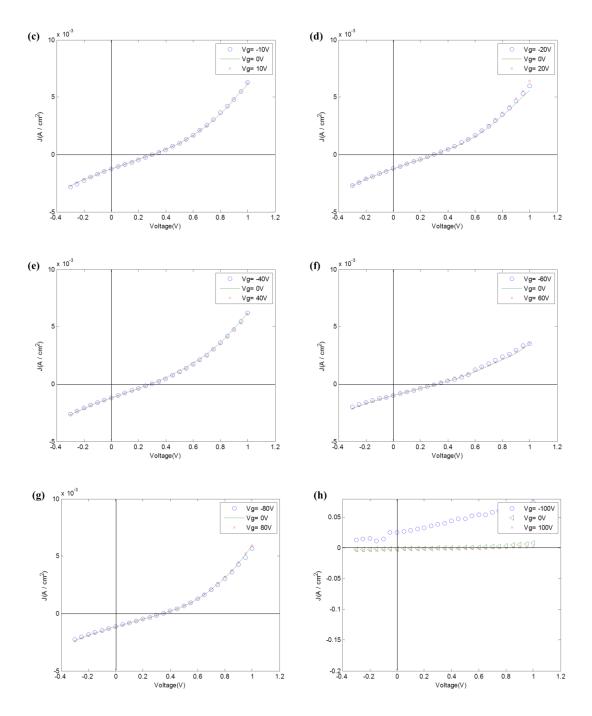

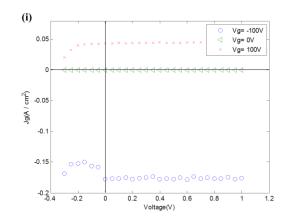

| Figure 5. 4. | <ul> <li>(a) The electric responses of the OFESC in both dark and light environments. (b) – (g) Electric responses of the OFESC in various gate biasing conditions without large gate leakage currents. (h) The electric responses of the OFESC at a large gate biases of ±100 V.</li> <li>(i) Large gate leakage currents occur measuring from the gate terminal at ±100 V gate bias.</li> </ul>                             | .65 |

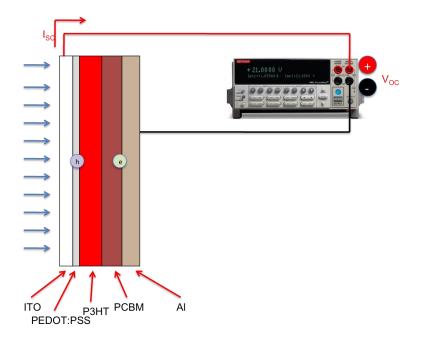

| Figure A. 1. | The device structure of the P3HT/PCBM organic bilayer solar cell and the experimental setup for the solar cell measurement.                                                                                                                                                                                                                                                                                                   | .84 |

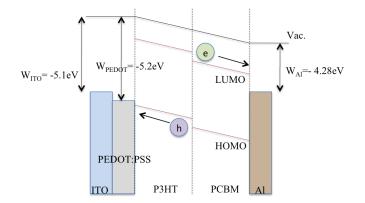

| Figure A. 2. | The energy diagram of the P3HT/ PCBM bilayer solar cell                                                                                                                                                                                                                                                                                                                                                                       | .85 |

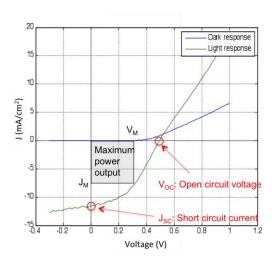

| Figure A. 3. | The electric output of the organic solar cell. The blue line is the output<br>in the dark environment and the green line is the output in the light<br>environment. The maximum power output of the solar cell is the<br>maximum rectangular area within the region of the green line and X-Y<br>coordinates.                                                                                                                 | .86 |

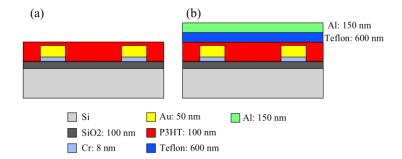

| Figure B. 1. | The device structures of the P3HT based OFETs. (a) without encapsulation. (b) with encapsulation.                                                                                                                                                                                                                                                                                                                             | .88 |

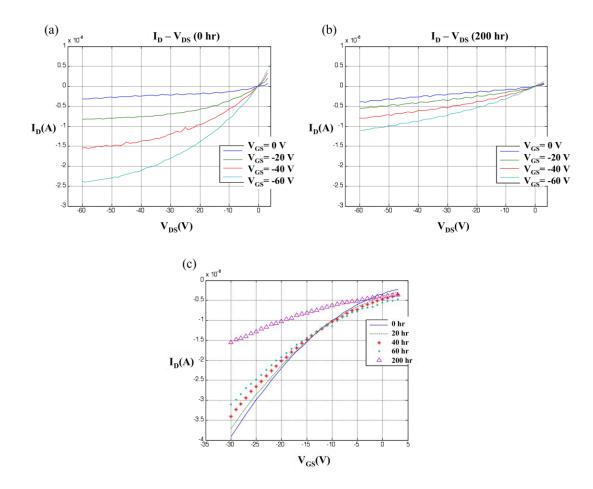

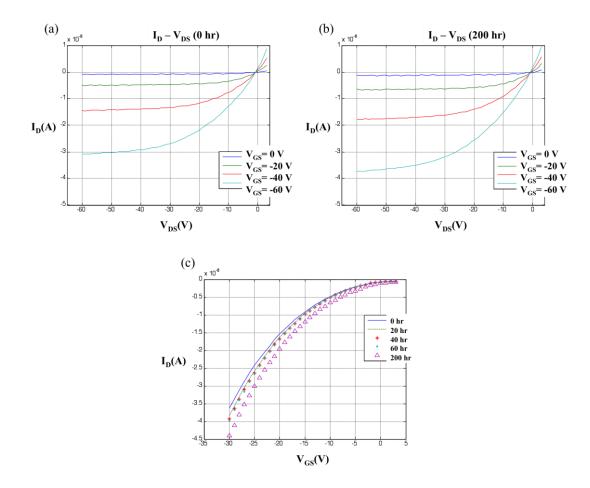

| Figure B. 2. | <ul> <li>Device measurements of the P3HT OFETs without encapsulation.</li> <li>(a) The I<sub>D</sub>-V<sub>DS</sub> curve measured as the device was just fabricated.</li> <li>(b) The I<sub>D</sub>-V<sub>DS</sub> curve after exposing the device 200 hours to the air.</li> <li>(c) Transfer characteristic measured at different time.</li> </ul> | .89 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure B. 3. | Device measurements of the encapsulated P3HT OFETs. (a) The $I_D$ - $V_{DS}$ curve measured as the device was just fabricated. (b) The $I_D$ - $V_{DS}$ curve after exposing the device 200 hours to the air. (c) Transfer characteristic measured at different time.                                                                                 | .90 |

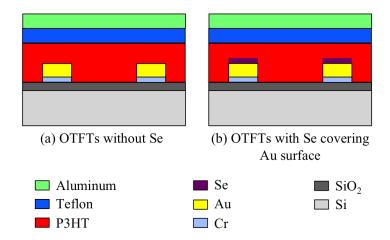

| Figure C. 1. | The encapsulated OFETs (a) without Se coating and (b) with Se coating on the Au electrode surface.                                                                                                                                                                                                                                                    | .93 |

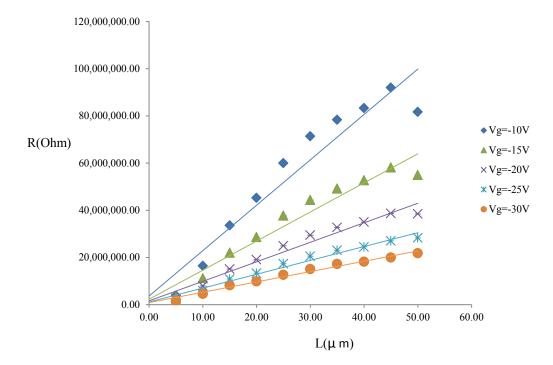

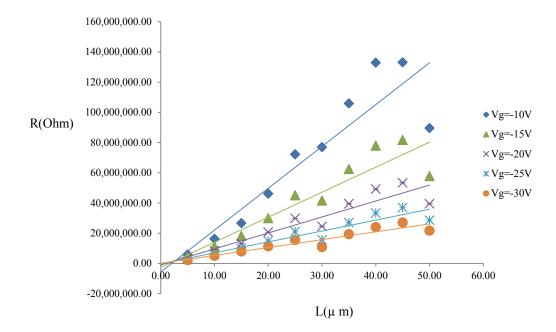

| Figure C. 2. | Data group that can extract the contact resistance.                                                                                                                                                                                                                                                                                                   | .95 |

| Figure C. 3. | Data group that cannot extract the contact resistance.                                                                                                                                                                                                                                                                                                | .96 |

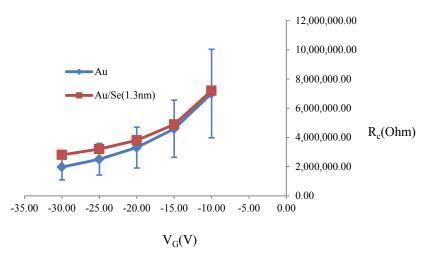

| Figure C. 4. | Contact resistances of both the Au contact and the Au/Se contact in different gate voltages.                                                                                                                                                                                                                                                          | .97 |

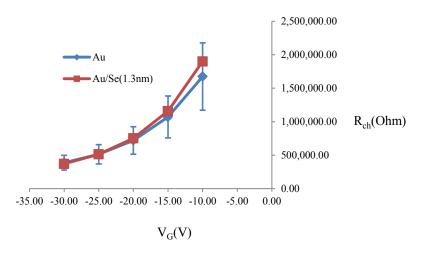

| Figure C. 5. | Channel resistances of both the Au case and the Au/Se case in different gate voltages.                                                                                                                                                                                                                                                                | .97 |

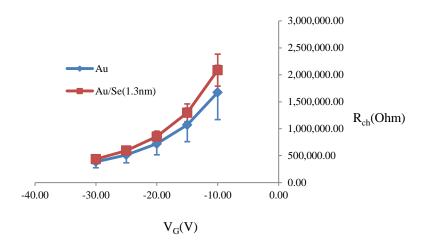

| Figure C. 6. | Channel resistances of both the Au case and the Au/Se case in different gate voltages. In this case, all the 8 groups of Au/Se case were used                                                                                                                                                                                                         | .98 |

#### CHAPTER I

#### INTRODUCTION AND LITERATURE REVIEW

#### **1.1 Introduction**

Since the organic semiconductor was first reported in 1948[1], successful demonstrations of electronics made of organic semiconductors have attracted more and more research interests due to several advantages: low-cost fabrication, ease of processing, and the capability of building flexible electronics. Organic semiconductors are conjugated molecules that include conjugated small molecules and conjugated polymers depending on their molecular size. These conjugated molecules contain alternating single bond and double bonds. This bonding arrangement results in delocalization of electrons in organic molecules, providing them very attractive electrical and optical properties[2, 3]. With these novel properties, organic semiconductors can be used for many electronic applications including organic light-emitting diodes (OLEDs)[4, 5], organic solar cells (OSCs)[6], and organic field-effect transistors (OFETs)[7].

In recent years, the continuous improvement of organic electronics has enabled the realization of their practical application, which requires them to be integrated into circuits. Therefore, patterning organic electronics becomes an important topic in device applications. Currently, there are many technologies used for patterning polymer materials, such as photolithography, ink-jet printing, screen printing, flexo printing, gravure printing, laser writing, electron-beam lithography, and nanoimprint lithography (NIL). Among these techniques, laser writing and electron-beam lithography cannot be used for patterning organic semiconductors because their high energy damages the material. NIL is the most suitable technique for electronics application due to its highresolution and high-throughput capability. Other patterning techniques either lack of high-resolution capability or have low fabrication throughput. Since this work is primarily based on NIL, in this literature review, only NIL will be introduced in more detail while other patterning methods will be briefly discussed.

#### **1.2 Nanoimprint lithography (NIL)**

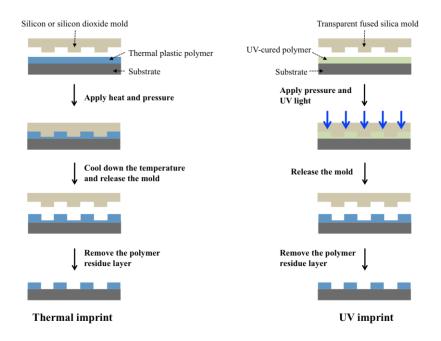

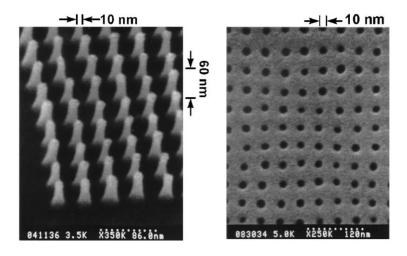

NIL is an emerging technique toward high-resolution and high-throughput patterning. It is a mechanical molding lithography, so the working principle of NIL is fundamentally different from the conventional photolithography. The principle of this technique is to transfer patterns from the imprinting mold to the resist coated on a substrate. Figure 1.1 schematically illustrates the process of NIL. This technique has already demonstrated a capability of fabricating high-resolution patterns. As illustrated in Figure 1.2, patterns of about 10 nm can be obtained by NIL[8]. There are mainly two types of nanoimprint approaches, thermal imprint and UV imprint. Because of their different principles, their mold and imprint resist are different and will be discussed in the following sections.

Figure 1. 1. Fundamental principles of thermal nanoimprint lithography and UV nanoimprint lithography.

Figure 1. 2. The sub-10 nm patterns fabricated by NIL. The figure on the left is the nanoimprint mold of 10 nm protrusions in dimension and the one on the right is the imprinted patterns on the imprint resist[8].

### **1.2.1 Nanoimprint mold**

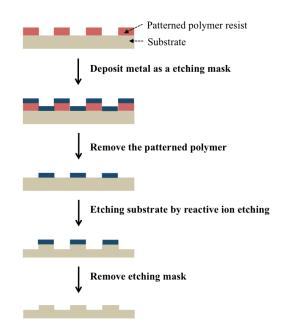

In thermal NIL, the selection of mold material is based on the considerations of material hardness, thermal expansion coefficient, and compatibility with traditional nanofabrication processing. The material hardness strongly affects the durability of the nanoimprint mold. The thermal expansion coefficient plays a critical role in the thermal NIL because a thermal mismatch between the mold and the substrate causes pattern distortions during the processing and affects the pattern fidelity. Therefore, using the same material for both the mold and the substrate forms a good pair for a highly precise NIL[9]. Currently, fabricating silicon and silicon dioxide molds can be easily achieved with semiconductor manufacturing technology. As shown in Figure 1.3, the required processes of building structures on Si and SiO<sub>2</sub> are patterning polymer resist on the substrate, depositing metal as an etching mask, and etching the substrate using reactive ion etching (RIE) technique. Concluding all of the discussions mentioned above, Si and SiO<sub>2</sub> are the most suitable material for the imprint mold[9]. The fabrication of a UVimprint mold is the same as that of a thermal imprint mold. The only requirement is to use a transparent substrate for UV light to pass through. Fused silica, therefore, is usually the most used material for UV-imprint.

Figure 1. 3. The process of fabricating an imprinting mold.

High density of nanostructrues on the surface of the mold increases its surface area, resulting in a large contact interface between the mold and the imprinted resist compared to that between the substrate and the imprinted resist. Such large contact interface causes a strong adhesion of the imprinted resist to the mold and becomes difficult to separate the mold and the imprinted resist after molding the resist. This phenomenon leads to large defected patterns. In this regard, the surface of the mold is usually treated to reduce the adhesion. The most used method is to coat the mold surface with a self-assembled monolayer (SAM) of a fluorosilane, such as tridecafluoro-1,1,2,2tetrahydrooctyltrichlorosilane (CF<sub>3</sub>-(CF<sub>2</sub>)<sub>5</sub>(CH<sub>2</sub>)<sub>2</sub>SiCl<sub>3</sub>). This method can be processed by either a solution-phase or a vapor-phase coating[10, 11]. This coating has a low surface energy which reduces the adhesion of the resist to the mold and it has been proven to be repeatedly used for thousands of UV nanoimprints[9].

#### **1.2.2 Nanoimprint resist**

Polymers used as the imprinting resist need to meet two requirements during the imprinting processing: low young's modulus and low viscosity. In thermal imprint, these requirements can be simultaneously achieved by heating the polymer above their glass transition temperature ( $T_g$ ). Empirically, the imprint temperature is chosen about 70°C–90°C above the  $T_g$  in order to have a good imprint result[9, 12]. Poly(methyl methacrylate) (PMMA) is the most commonly used imprint resist due to its low volume change under large temperature and pressure variations[13]. In the case of UV-imprint, the imprint resist is originally a liquid phase precursor that can be cured by UV-light exposure. This liquid phase resist has automatically satisfied two requirements of NIL, low young's modulus and low viscosity, without exposure to high temperature and high pressure that could limit the throughput of NIL processing[9]. A derivative technique, step and flash imprint lithography (SFIL), was then developed based on UV-imprint, allowing this technique potentially be used for integrated circuit manufacturing[14].

## 1.3 Other patterning methods for organic semiconductors

## **1.3.1** Photolithography

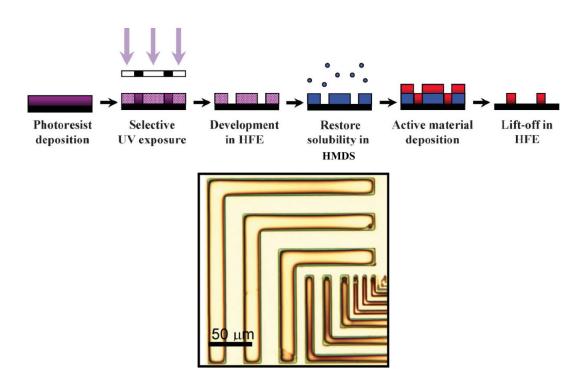

Photolithography is a widely used technique for patterning electronics in current semiconductor manufacturing. It is an optical lithography that utilizes a light source to resolve patterns pre-designed on a photo-mask. Recently, it has been adapted to pattern organic semiconducting molecules by employing a special fluorinated photoresist that can be processed in fluorinated solvents which, for example hydrofluoroethers (HFEs), have been proven to be inert to organic semiconducting molecules[15]. The fabrication processing is the same as traditional photolithography. Figure 1.4 shows an example of the processing method and a patterned result of an organic semiconducting material. Due to the limitation of light wavelength, the reported minimum dimension by using UV-lithography is  $0.4 \mu m$ [16].

Figure 1. 4. The photolithography patterning method for organic semiconducting materials and the organic semiconducting material patterned by photolithography[15].

## **1.3.2 Ink-jet printing**

Processing organic semiconductors in solution phase enables them to be patterned by ink-jet printing[17]. Like the conventional ink-jet printer, this approach directly prints patterns by continuously ejecting droplets from a piezoelectric nozzle to a desired location. The technique of ejecting a fixed volume of droplets attributes to a change of pressure generated by a piezoelectric tubular actuator attached to the nozzle. Figure 1.5 shows a general structure of the piezoelectric ink-jet printing nozzle. Printable devices, such as OLEDs, OFETs and OSCs, have been demonstrated based on this technique. Currently, this approach can provide patterns with dimensions greater than 20  $\mu$ m[17].

Figure 1. 5. The piezoelectric ink-jet printing nozzle with piezoelectric tubular actuator attached on the side in order to eject a fixed volume of solutions[18].

### 1.3.3 Screen printing

Screen printing is a printing technique that is commonly used in printing images on soft substrates such as clothes and papers. This technique was then adapted for electronic applications because of its high throughput. The principle of the method is illustrated in Figure 1.6. The screen stencil is held above the substrate with a paste applied on top of it. The squeegee presses the paste across the screen stencil, pushing the paste though the screen stencil and depositing the paste on the substrate. The patterning resolution of this technique is able to reach 10  $\mu$ m[19].

Figure 1. 6. The schematic diagram of the screen printing principle[20].

## **1.3.4 Gravure printing and flexo printing**

Both gravure printing and flexo printing are roll-to-roll printing techniques potentially offering low cost and high throughput manufacturing. The difference between these two methods is that gravure printing uses a concave cylinder while flexo printing uses a convex cylinder. Figure 1.7 shows a schematic diagram of gravure printing and flexo printing. In gravure printing, the concave cylinder is immersed in the ink that covers the entire concave structures. A doctor blade scrapes the ink on the cylinder surface, leaving the grooves full of ink, which is then transferred to the flexible substrate with a pressure induced by an impression cylinder. In flexo printing, an anilox cylinder is immersed in the ink like the gravure printing. The doctor blade does not directly contact with the anilox cylinder instead it keeps a small gap between the blade and the cylinder. The plate cylinder with convex structures is coated with ink by contacting with the anilox cylinder. Then, the ink can be transferred to the flexible substrate with a pressure induced by the impression cylinder[21].

Figure 1. 7. Schematic diagram of (a) gravure printing and (b) flexo printing[21].

The resolution of the printed patterns directly depends on the dimension of the structure fabricated on the cylinders. Currently, gravure printing provides a pattern resolution of 9  $\mu$ m[22] and flexo printing offers a resolution of 50  $\mu$ m[23].

### **1.4 Proposed method for patterning organic electronics**

In this work, several patterning and fabrication methods for organic electronics are proposed. All these techniques are primarily based on NIL due to its potential advantages of high-resolution and high-throughput. Patterning organic semiconductors and metal electrodes is the main investigation of those proposed techniques because both organic semiconductors and metal electrodes are major parts of organic electronics. These patterning methods along with experimental details, novelties, and results will be discussed respectively in different chapters.

In Chapter II, the technique for high-resolution and non-destructive patterning of isolated organic semiconductors for device applications is described in detail. Submicron isolated organic semiconductor patterns are successfully achieved, with a potential to further reduce the pattern resolution into deep sub-micron region. The technique has the capability of achieving the highest organic semiconductor patterning resolution, thus providing a practical route towards the fabrication of organic integrated circuits based on high-performance nanoscale organic electronic devices.

For organic electronics to enter commercial applications, the device and circuit performance must be further enhanced. Current OFET device structure is not optimized for this purpose, resulting in organic circuits with low performance. In Chapter III, a technique to fabricate self-aligned organic MESFET device is presented. This technique eliminates parasitic capacitance and resistance in organic transistors, thus has the potential to achieve low operational power and high-frequency applications for organic circuits.

During the course of this research, a new technique is devised to fabricate sub-20 nm structures without advanced lithographic techniques. The technique is called polymer sidewall transfer lithography, and its process and capabilities are described in Chapter IV

in detail. This technique opens a facile route towards the fabrication of nanostructures with simple lab equipment. Potential applications include the fabrication of nanoimprint molds, nanofluidic devices and nanostructures for photonic applications.

At the end of this work, a novel organic electronic device, entitled organic fieldeffect solar cells, is fabricated by NIL. The device principles, fabrication schemes and preliminary results are discussed in Chapter V.

#### CHAPTER II

# HIGH-RESOLUTION NON-DESTRUCTIVE PATTERNING OF ISOLATED ORGANIC SEMICONDUCTORS FOR DEVICE APPLICATIONS<sup>\*</sup>

#### **2.1 Introduction**

Today, electronic devices made of organic semiconductors have exhibited many potential advantages over traditional electronics, including low-cost fabrication, flexible devices, and large-area integration. With these advantages, many researches have been investigated to explore more practical applications for these novel electronics. In order to have advanced applications, organic electronics such as OFETs and OLEDs, need to be patterned into isolated units, such that organic integrated circuits[24-26] and OLED displays[27] can be implemented. For integrated circuit applications, isolating electronics reduces device crosstalk within circuits. For display applications, red, green, and blue organic light-emitting pixels integrated into the display need to be separated and operated individually in order to generate images. To achieve organic semiconductor patterning, many advanced techniques were developed such as photolithography[15], ink-jet printing[28], screen printing[29], and nanoimprint lithography (NIL)[30]. Among them, NIL is the most suitable technique to patterning organic semiconductors due to its capability of patterning nanoscale structure, high throughput, and low-cost fabrication[8]. However, the residual layer after conventional nanoimprint connects all

<sup>&</sup>lt;sup>\*</sup>Reprinted with permission from "High-resolution nondestructive patterning of isolated organic semiconductors" by Yi-Chen Lo, Dawen Li, Zhenzhong Sun, Shoieb Shaik, and Xing Cheng, 2012. *Journal of Vacuum Science & Technology B*, 30, 06FB04, Copyright 2012 by American Vacuum Society.

Journal of Vacuum Science & Technology B, 30, 06FB04, Copyright 2012 by American Vacuum Society. DOI 10.1116/1.4757956

units and becomes a major issue in achieving isolated organic semiconductor structures. The conventional method to eliminate the residual layer is to use oxygen reactive ion etching (RIE)[30], but the highly reactive oxygen plasma can damage organic semiconductors, resulting in severe device degradation.

A nondestructive patterning method for organic semiconductors by employing a fluorinated sacrificial template that can be wet processed by fluorinated solvents was reported before[15]. Its process contains a sequence of photolithography patterning, deposition of organic semiconductor, and liftoff processing. The photolithography step is to pattern a fluorinated polymer template. After depositing the organic semiconductor on the patterned template, the liftoff process used to dissolve the template by a fluorinated solvent forms isolated organic semiconductor structures on the substrate. The fluorinated solvents are inert to non-fluorinated materials, including most of the organic semiconducting materials. In order to pattern even higher resolution patterns, I propose to combine NIL and the fluorinated template processing for the purpose of nondestructively patterning sub-micron isolated organic semiconductor structures.

#### 2.2 Experimental method

In this experiment, Teflon-AF 1600 purchased from Dupont was used as the nanoimprint resist and the template material. FC-40, a perfluorinated solvent purchased from Sigma Aldrich, was selected to dissolve Teflon-AF[31]. The organic semiconductor to be patterned is poly(3-hexylthiophene) (P3HT, from Rieke Metals). P3HT was selected in this experiment because it is a widely used conjugated polymer in

various applications, including OFETs and organic solar cells (OSCs). The solvent to dissolve the P3HT polymer was 1,2-dichlorobenzene (DCB) purchased from Sigma Aldrich. A Teflon-AF solution of 2 wt% was made by dissolving Teflon-AF in FC-40. The solution was heated to 40°C for at least 24 hours to completely dissolve Teflon-AF. A P3HT solution was obtained by dissolving P3HT in DCB (15 mg/ml) and the P3HT solution was also heated to 40°C and stirred for 24 hours. Nanoimprint molds of various dimensions were made of thermally grown silicon dioxide and coated with perfluorodecyltrichlorosiliane (FDTS) in order to easily separate the mold from the resist after imprinting. To coat FDTS on the mold, a small amount of FDTS was mixed with heptane and the mold was immersed into the solution for 10 minutes. After coating FDTS, the mold surface became highly hydrophobic.

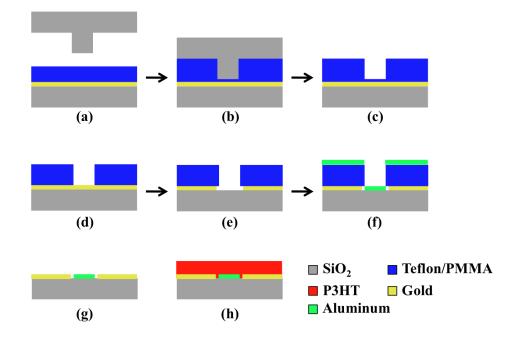

The patterning technique is schematically illustrated in Figure 2.1. The steps from (a) to (f) are explained as following: (a) The 2 wt% Teflon-AF solution was spin-coated on the silicon dioxide substrate at 800 rpm, forming a 210 nm–230 nm thick Teflon-AF film serving as the nanoimprint resist; (b) The mold thermally imprinted the Teflon-AF film at 230°C and 900 psi; (c) The mold pattern was transferred into the resist after releasing the mold. The patterned resist served as a sacrificial template to pattern organic semiconductors; (d) Oxygen RIE was used to anisotropically etch the Teflon-AF template in order to eliminate the residual layer; (e) The organic semiconductor P3HT was spin-coated on the Teflon-AF sacrificial template; and (f) After removing the Teflon-AF template by the FC-40 solvent, isolated P3HT structures were formed on the substrate.

Figure 2. 1. Schematics of nondestructive patterning of isolated P3HT by nanoimprint. (a) Spin-coat the Teflon-AF solution to form a thin Teflon-AF film. (b) Thermally imprint the Teflon-AF film by a nanoimprint mold. (c) After releasing the mold, patterns are generated in the Teflon-AF film. (d) Remove the residual layer by oxygen RIE. (e) Spin-coat P3HT on the Teflon-AF sacrificial template. (f) Dissolve the Teflon-AF template in FC-40 solvent to obtain P3HT patterns.

## 2.3 Results and discussion

## **2.3.1 Patterning polymer sacrificial template**

To nondestructively pattern P3HT, a fluorinated sacrificial template that can be processed by fluorinated solvents is needed[15, 32]. The main reason to use fluorinated material as the sacrificial template is that the wet process with fluorinated solvents is fully compatible with organic semiconductors. Fluorinated solvents are classified as orthogonal to both polar and non-polar solvents; in other words, fluorinated solvents are inert to organic materials that can be processed in polar and non-polar solvents[32].

Teflon-AF 1600 has a glass transition temperature of 160°C. Experiments show that the imprinting temperature needs to be at least 220°C to completely transfer patterns from the mold to Teflon-AF 1600. Therefore, the imprinting temperature was set to be 230°C to mold the Teflon-AF layer. For the imprinting pressure, the range of 300 psi to 900 psi successfully transfers patterns above 220°C. Higher pressures out of this range have a risk to break the mold and lower pressures cannot fully transfer patterns.

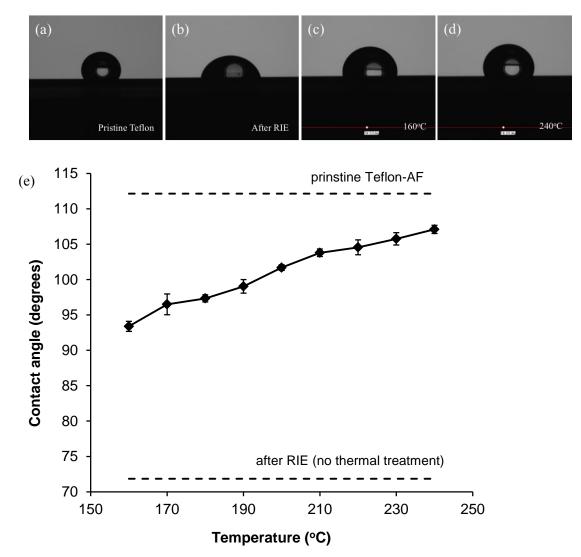

Although the surface of Teflon-AF is highly hydrophobic, oxygen RIE removal of the residual layer after nanoimprint increases its surface energy and renders the surface hydrophilic property. In general, a hydrophobic template surface is desired in the process of spin-coating the P3HT solution in order to aggregate P3HT mostly in the template cavities and repel the P3HT solution from the template surface. Fortunately, the hydrophobic surface of Teflon-AF after oxygen RIE can be restored by thermal treatment above its glass transition temperature (160°C). Figure 2.2 illustrates contact angles of water droplet on the Teflon-AF surface before and after RIE treatment. The flat pristine Teflon-AF had a contact angle of around 112° (Figure 2.2(a)). After oxygen RIE treatment, the surface turned from hydrophobic to hydrophilic, and the contact angle was generally below 90° (Figure 2.2(b)). After thermal treatment at 160°C on a hotplate for 1 minute, the contact angle increased to 93.4°. Figure 2.2(e) shows a continuous increase in the contact angles of water droplet on the Teflon-AF surface as the annealing temperature increases. After 240°C annealing for 1 minute, the contact angle was restored to 107.1°, which is close to that of the pristine Teflon-AF surface. In this work,

the annealing temperature of 170°C was used to ensure hydrophobic Teflon-AF surface while maintaining pattern fidelity.

Figure 2. 2. Contact angles of water droplet on different Teflon-AF surface conditions. (a) Pristine Teflon-AF after spin-coating. (b) Teflon-AF after oxygen RIE. (c) RIE-treated Teflon-AF after 1 minute annealing at 160°C. (d) RIE-treated Teflon-AF after 1 minute annealing at 240°C. (e) Water contact angle variation after 1 minute annealing at different temperatures.

#### 2.3.2 Patterning isolated organic semiconductor structures

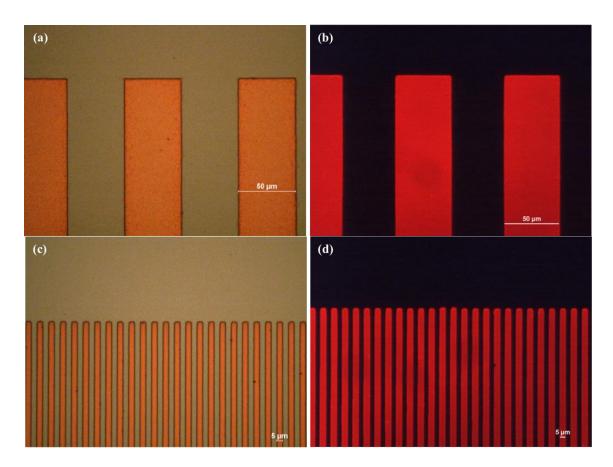

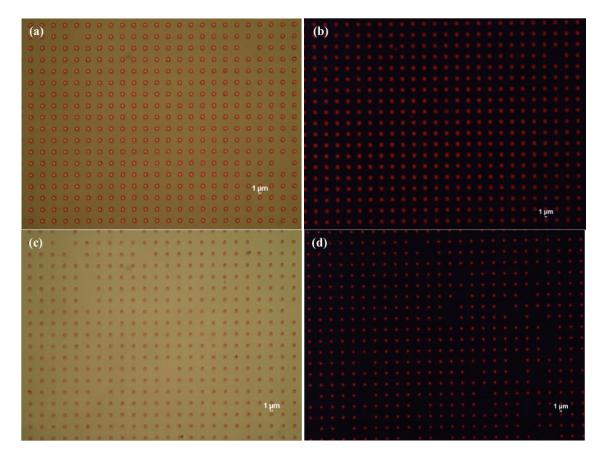

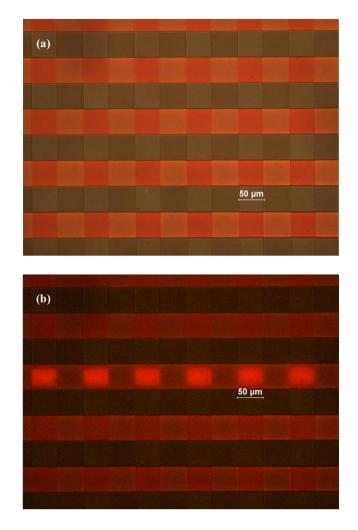

Organic semiconductor structures ranging from tens of microns to sub-micron can be easily achieved by the technique described in Figure 2.1. The patterning results of P3HT structures are shown in Figure 2.3. Figure 2.3 (a) and (b) show the optical microscope image and the fluorescent microscope image of 50  $\mu$ m P3HT lines, respectively. Figure 2.3 (c) and (d) show 5  $\mu$ m P3HT gratings in optical and fluorescent microscope images, respectively. In the fluorescent images, the dark background clearly indicates that P3HT patterns are completely isolated. All P3HT gratings exhibit smooth line edges. Since nanoimprint lithography has the potential to produce high-resolution patterns, sub-micron P3HT structures are also obtained by the same approach. Figure 2.4 shows P3HT square patterns in the dimension of 1  $\mu$ m and 0.5  $\mu$ m. Figure 2.4 (a) and (c) are optical microscope images and Figure 2.4 (b) and (d) are fluorescent microscope images.

Figure 2. 3. Images of isolated P3HT grating patterns achieved by nanoimprint and sacrificial template. (a) and (b) show the optical image and the fluorescent image of 50  $\mu$ m P3HT gratings, respectively. (c) and (d) show the optical image and the fluorescent image of 5  $\mu$ m P3HT gratings, respectively.

In Figure 2.4, some defects, especially in the 0.5 µm patterns, were observed after patterning. This issue was caused by the poor adhesion between the P3HT pattern and the substrate. After spin-coating the P3HT solution on the Teflon-AF template, it was found that a small amount of P3HT can still stay on the Teflon-AF surface despite the surface hydrophobicity after thermal treatment. Therefore, to efficiently dissolve the Teflon-AF template and liftoff P3HT on the template, an ultrasonic bath was used. Poor adhesion between the P3HT squares and the substrate resulted in a few missing

structures during the ultrasonic agitation. Comparing Figure 2.4 (a) and (c), smaller structures with smaller contact area to the substrate yield more defects.

Figure 2. 4. Images of P3HT square patterns achieved by nanoimprint and sacrificial template. (a) and (b) show the optical microscope image and the fluorescent microscope image of 1  $\mu$ m P3HT squares, respectively. (c) and (d) show the optical microscope image and the fluorescent microscope image of 0.5  $\mu$ m P3HT squares, respectively.

The 350 nm P3HT grating patterns are also obtained as shown in Figure 2.5. Figure 2.5 (a) shows both the P3HT pattern and the Teflon-AF template. Two peeled-off Teflon-AF lines clearly show that P3HT filled in the trenches of the Teflon-AF template. Figure 2.5 (b) is the cross-sectional view of the P3HT grating after removing the TeflonAF Template. The sub-micron isolated P3HT lines are well defined. It also shows that the edges of the P3HT lines are taller than the middle of the P3HT lines. This is caused by the drying process of the P3HT solution in the trenches of the Teflon-AF template.

Figure 2. 5. Scanning electron microscopy (SEM) monographs of 350 nm P3HT grating patterns. (a) Teflon-AF and the P3HT patterns before removing the Teflon-AF template. (b) Cross-sectional view of 350 nm P3HT patterns after dissolving the Teflon-AF template.

## 2.3.3 Patterning OLED arrays

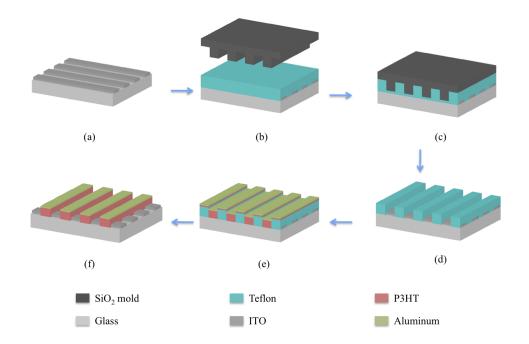

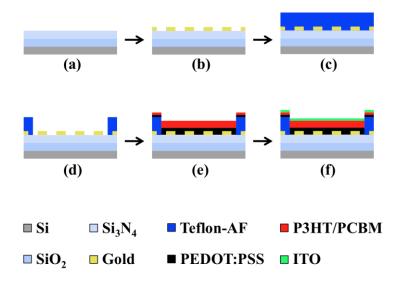

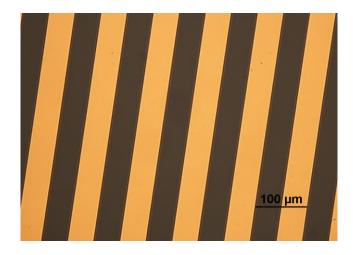

The proposed patterning technique can be used to not only pattern isolated organic semiconductor structures, but also fabricate organic electronic device arrays. Based on the method developed in this work, a passive-matrix organic light-emitting diode (PMOLED) array was demonstrated. Figure 2.6 shows the processing steps. First, indium tin oxide (ITO) stripes of 50 µm were patterned on a glass substrate by photolithography (Figure 2.6(a)). To pattern the ITO, S1805 photoresist purchased from Rohm and Haas was spin-coated (4000 rpm) on the 40 nm thick ITO layer deposited on the glass substrate. After UV exposure (20 mJ/cm<sup>2</sup>) with a photo-mask of 50 µm stripe patterns, the sample was developed in the MF-319 developer to reveal photoresist stripes on the ITO layer. The photoresist stripes served as the mask in the processing of the ITO etching. The ITO was wet etched in the 37% hydrochloric acid (HCl). Finally, the patterned photoresist stripes, after etching the ITO, were removed by acetone. By this mean, ITO stripes can be achieved. Then 2 wt% Teflon-AF solution was spin-coated on top of the ITO stripes to form a 230 nm thick Teflon-AF film (Figure 2.6(b)). After thermally imprinting the Teflon-AF film at 230°C and 900 psi with a grating mold of 400 nm in depth and 100 µm wide, 50% duty cycle (Figure 2.6(c)), the mold was released and oxygen RIE was used to remove the residual layer (Figure 2.6(d)). A very thin poly(3,4-ethylenedioxythiophene) poly(styrenesulfonate) (PEDOT:PSS) layer was spin-coated as the hole transport layer and a 100 nm thick P3HT film was spin-coated as the light emitting layer. After that, a 100 nm thick aluminum (Al) layer was thermally evaporated on top of the P3HT layer (Figure 2.6(e)). Finally, dissolving the Teflon-AF

template and lifting off the PEDOT:PSS/P3HT/Al stack completed the device fabrication. Figure 2.7(a) shows the PMOLED pattern imaged from the backside of the glass. The vertical white stripes are ITO patterns and the horizontal stripes are stacks of PEDOT:PSS/P3HT/Al. The intersections of the vertical and the horizontal lines are individual OLED pixels. Each pixel is addressable by applying a turn-on voltage to its corresponding row and column electrodes. Figure 2.7(b) shows an array of electrically biased OLED pixels. Each pixel is a 50 µm square. Since the pitch is 100 µm and the duty cycle is 50%, this method easily demonstrated a PMOLED display of 254 dots per inch (DPI) resolution.

Figure 2. 6. Schematics of the fabrication process for the passive-matrix organic lightemitting diode (PMOLED) array. (a) Pattern ITO on a glass substrate. (b) Spin-coat Teflon-AF on the substrate. (c) Thermally imprint Teflon-AF with a nanoimprint mold. (d) Remove the residual layer by oxygen RIE. (e) Deposit a stack of PEDOT:PSS, P3HT and Al. (f) Dissolve the Teflon-AF template to liftoff the PEDOT:PSS/P3HT/Al stack on the template.

Figure 2. 7. PMOLED array patterned by nanoimprint and sacrificial template. (a) The vertical stripes are 50  $\mu$ m ITO patterns and the horizontal stripes are stacks of PEDOT:PSS/P3HT/Al. The intersections of the vertical and the horizontal patterns are OLED pixels. (b) Optical image of the electrically biased PMOLED array.

## 2.3.4 Advantages and future development

By using the fluorinated template patterned by nanoimprint as the intermediate step, I have successfully achieved non-destructive patterning of organic semiconductor structures. Patterning isolated organic semiconductor structures with nanoimprint has several advantages over other printing or photolithography-based techniques. First, nanoimprint technique has high-resolution capability and this characteristic easily enables high-resolution organic semiconductor structures. Although the smallest structure we demonstrated here is 350 nm, there is no fundamental limitation on smaller patterns. Potentially sub-100 nm structures can be attained. Second, nanoimprint ensures well-defined patterns with very low line edge roughness. The pattern size, shape and line edge roughness are determined by mold patterns, which can be precisely controlled with mature microelectronic processing of thermally grown SiO<sub>2</sub>. In printing-based techniques, the spreading of organic semiconductor ink can smear the pattern shape and change the pattern size. Third, nanoimprint has extended its application to roll-to-roll processing to achieve a fast and low-cost patterning[33], and 3-D nanoimprint to realize self-aligned lithography that overcomes the difficulty of layer-to-layer alignment in fabricating electronic devices[34, 35]. The proposed technique has no limitation to be adapted to both roll-to-roll processing and 3-D nanoimprint. Fourth, the technique presented here can be applied to all organic semiconductors, including organic small molecules. It is expected that thermally evaporating small molecules and lifting off in fluorinated solvents can achieve isolated structures of small molecules. Finally, the overall process is still simple and low cost, and it can be easily extended to fabricate integrated organic electronics in large scale.

It is also noticed that the presented technique needs further tailoring and optimization. First, poor adhesion between P3HT and the substrate resulted in the missing of a few structures after lifting off in the dultrasonic bath. This can be addressed by using coupling agents, such as amine silanes[36], to improve the adhesion between

organic semiconductors and the silicon or silicon oxide surfaces. Second, the tall edges in P3HT patterns may become an issue in some device fabrications. This issue can be easily addressed by pressing the patterned structures with a flat mold to smooth out the tall edges.

High-resolution patterning of isolated organic semiconductor structures is expected to have many applications in organic electronics. It can be used to directly pattern OLED arrays for flat-panel display and solid-state lighting applications. The submicron and deep sub-micron organic semiconductor patterns can also be used to fabricate high performance OFETs with high cut-off frequencies. Also, the isolated patterns enable the possibility of fabricating organic integrated circuits because devices are isolated from each other to prevent cross interference.

## **2.4 Conclusion**

The proposed method combining NIL and fluorinated template processing has successfully demonstrated the capability of patterning isolated P3HT structures from 0.35µm to tens of microns. Inherited from traditional NIL, this technique is capable of generating high-resolution structures. Additionally, this technique achieves nondestructive patterning of organic semiconductors because oxygen RIE is not directly applied to the P3HT thin film and the FC-40 solvent is compatible with organic semiconductors. The patterning technique demonstrated here is not limited to P3HT. It is applicable to all organic semiconductors, both solution-processed and vapor-deposited materials. Moreover, the technique can be extended to directly fabricate organic

electronic device arrays. In the case of PMOLED fabrication, this technique provides a proof-of-concept demonstration. Although P3HT is not the optimized material for OLED application, other materials suitable for OLEDs can be used in the future for flat-panel display and solid-state lighting applications.

#### CHAPTER III

## FABRICATING ORGANIC METAL-SEMICONDUCTOR FIELD EFFECT TRANSISTOR (OMESFET) OF SELF-ALIGNED BOTTOM GATE

#### **3.1 Introduction**

Organic electronics have become a potential research topic due to their attractive advantage of low-cost fabrication, and the possibility of making flexible electronic devices. Today, continuous evolutions of organic semiconductors and modifications of the device structure have gradually improved the device performance[37, 38]. Even though the device performance has been greatly improved in the past few years, organic field effect transistors (OFETs) still need a lot of effort to be used in practical applications due to its high operational voltage and low operational frequency.

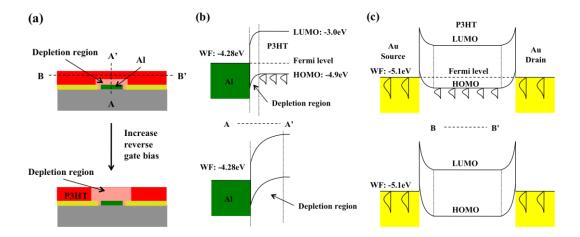

Organic field effect transistors are mainly classified as organic metal-insulatorsemiconductor field effect transistors (OMISFETs) and organic metal-semiconductor field effect transistors (OMESFETs) according to the device structure[39]. The structure of OMISFETs contains an insulating layer between the gate electrode and the semiconducting material. The insulating layer is an important part that influences the operational voltage and the device performance. To build flexible electronics, the insulating layer also needs to be flexible and usually dielectric polymers are preferred[40]. Typically, polymer insulators have low breakdown potentials and low dielectric constants. To prevent the device breakdown, the transistor needs to use a thick polymeric insulating layer, which requires a large gate voltage to induce field effect charges in the transistor channel. This is the main reason that OMISFETs usually need a large operational voltage. Moreover, the interface between the insulating layer and the organic semiconductor also influences the device performance[41-43]. In MESFETs structure, the gate electrode directly contacts with the organic semiconductor and forms a depletion region in the semiconducting bulk[44, 45]. Such depletion region due to the lack of electric carriers is a nonconductive layer. In the forward bias or without bias at the gate electrode, only a thin depletion layer is formed and the semiconducting bulk mainly occupies the channel region of the transistor. This condition is considered as turn-on status because the channel is able to conduct current through the semiconducting bulk. In the condition of reverse bias, the depletion layer expands and eventually occupies the entire organic semiconductor, turning off the conducting channel[46]. This on/off mechanism only requires a relatively low voltage compare to OMISFETs. Therefore, OMESFETs is actually a potential device to be used for low voltage circuit applications[47, 48].

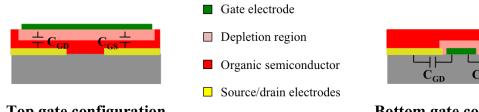

OMESFETs in current literature are built as top gate and bottom source/drain configuration with organic semiconductors sandwiched between the gate and the source/drain because of its simple fabrication process. However, the top gate configuration is difficult to restrict the gate electrode to the channel region and therefore the gate has a large overlap area with source and drain. Such large overlap causes a large parasitic capacitor between electrodes and greatly lowers the device cut-off frequency[49]. Therefore, a bottom gate, bottom source/drain configuration becomes a better device structure for high-speed circuit applications because the overlap area can be reduced. Figure 3.1 shows schematic diagrams of OMESFET in both top gate configuration and bottom gate configuration. The minimized electrode overlap in the bottom gate structure can reduce the capacitance and provides the device a higher cut-off frequency. However, when the device dimension is greatly shrunk, it becomes more and more difficult to pattern the bottom gate by an optical alignment system. In this research, I propose a method to fabricate a self-aligned gate electrode for OMESFET by employing nanoimprint lithography (NIL). This approach does not require a highly accurate alignment system and is able to align the gate electrode easily in the channel region without contacting with source/drain electrodes.

Top gate configuration

**Bottom gate configuration**