# ENERGY HARVESTING FOR SELF-POWERED WIRELESS SENSORS

A Dissertation

by

## JASON LEE WARDLAW

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

December 2011

Major Subject: Electrical Engineering

## ENERGY HARVESTING FOR SELF-POWERED WIRELESS SENSORS

### A Dissertation

by

## JASON LEE WARDLAW

### Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

| Chair of Committee, | Aydın İlker Karşılayan |

|---------------------|------------------------|

| Committee Members,  | José Silva-Martínez    |

|                     | Hamid Toliyat          |

|                     | Ibrahim Karaman        |

| Head of Department, | Costas Georghiades     |

December 2011

Major Subject: Electrical Engineering

#### ABSTRACT

#### Energy Harvesting for Self-Powered Wireless Sensors. (December 2011)

Jason Lee Wardlaw, B.S., Texas A&M University

Chair of Advisory Committee: Aydın İlker Karşılayan

A wireless sensor system is proposed for a targeted deployment in civil infrastructures (namely bridges) to help mitigate the growing problem of deterioration of civil infrastructures. The sensor motes are self-powered via a novel magnetic shape memory alloy (MSMA) energy harvesting material and a low-frequency, low-power rectifier multiplier (RM). Experimental characterizations of the MSMA device and the RM are presented. A study on practical implementation of a strain gage sensor and its application in the proposed sensor system are undertaken and a low-power successive approximation register analog-to-digital converter (SAR ADC) is presented. The SAR ADC was fabricated and laboratory characterizations show the proposed low-voltage topology is a viable candidate for deployment in the proposed sensor system. Additionally, a wireless transmitter is proposed to transmit the SAR ADC output using on-off keying (OOK) modulation with an impulse radio ultra-wideband (IR-UWB) transmitter (TX). The RM and SAR ADC were fabricated in ON  $0.5\mu$ m CMOS process.

An alternative transmitter architecture is also presented for use in the 3-10GHz UWB band. Unlike the IR-UWB TX described for the proposed wireless sensor system, the presented transmitter is designed to transfer large amounts of information with little concern for power consumption. This second method of data transmission divides the 3-10GHz spectrum into 528MHz sub-bands and "hops" between these sub-bands during data transmission. The data is sent over these multiple channels for short distances ( $\approx$ 3-10m) at data rates over a few hundred million bits per second

(Mbps). An UWB TX is presented for implementation in mode-I (3.1-4.6GHz) UWB which utilizes multi-band orthogonal frequency division multiplexing (MB-OFDM) to encode the information. The TX was designed and fabricated using UMC  $0.13\mu$ m CMOS technology. Measurement results and theoretical system level budgeting are presented for the proposed UWB TX.

To Dorothy, Neuman, Martha, N.J., and Kelly.

#### ACKNOWLEDGMENTS

First I would like to thank my advisor and mentor Dr. Aydın Ilker Karşılayan. I was fortunate enough to meet Dr. Karşılayan during my undergraduate studies and then was even further blessed with being able to continue to work with him during my graduate studies. His guidance, understanding and humor have helped me through many challenging times. His approach to circuit design, as well as life, has allowed me to make adaptations to myself to be a better engineer and a better person.

I would next like to thank Dr. Silva-Martínez for being a great professor and a great individual to learn from. His dedication to his craft as well as his expert knowledge have helped influence me in more ways than I can verbalize. The approach he takes to analysis, design, explanation, and inspiration is one which has allowed me to better understand very complicated tasks with ease.

Dr. Toliyat is a great mentor and advisor. I appreciate the times he has sat with me and discussed life unflinchingly. I thank him for his advice and his willingness to teach me what he could. His comments have meant a great deal to me.

Dr. Karaman has been a great voice during my work over the past few years. I feel fortunate enough that he not only agreed to be on my committee, but also allowed me to work with him and his research group on this project. The collaboration would not have been as successful without him.

A great many thanks go to the head of the Analog and Mixed Signal Center at Texas A&M University for his guidance, friendship, advice, and willingness to share. Thank you to Dr. Edgar Sánchez-Sinencio for all you have done for me.

Thank you to all of my friends at Texas A&M and in the AMSC (present and past). Those which deserve special recognition are: Dr. Tim Fischer, Dr. Burak Kelleci, Félix Fernández-Rodríguez, Dr. Marvin Onabajo, Alfredo Peréz-Carrillo, Mandar Kulkarni, John Mincey, Marcos López-Rivera, Dr. Hesam Aslanzadeh, Dr. Mohamed El-Nozahi, Dr. Mohammed Mobarak, Dr. Faramarz Bahmani, Richard Kamprath, Esq., David Báez-Villegas, Johnny Lee, Praveena Kode, Dr. Jianhong Xiao, Raghavendra Kulkarni, Dr. Miguel Rojas-Gonzalez, Dr. Cho-Ying "Stephen" Lu, Shan Huang, Mohan Geddada, Dr. Nicolas Frank, Dr. Burak Başaran, Erik Pankratz, Chang-Joon "C.J." Park and those which I cannot remember at the moment.

The influence of many individuals in the Department of Electrical and Computer Engineering have also had a great impact on my ability to complete this program. Whether they know this or not, the following individuals are thanked graciously: Dr. Scott Miller, Dr. Garng M. Huang, Dr. Costas Georghiades, Dr. Bogumila Styblinski, Ms. Tammy Carda, Ms. Jeannie Marshall, Dr. Deepa Kundur, Dr. Takis Zourntos, and Dr. Shankar Bhattacharyya, among others.

I have been fortunate enough to have great mentors and friends at Texas A&M University. Additionally, I have, in one way or another, had great interactions, advice, thoughts, conversations, and lessons from many individuals. These include, but are not limited to: Jeff Koelling (Micron Technology Corp.), Harish Venkata (Micron Technology Corp.), Myung-Hoe Bae (Micron Technology Corp.), Kirk Ashby (Zoran), Ron Spencer (Zoran), Jaber Khoja (Zoran), Phil Hisayasu (Zoran), Jan-Michael Stevenson (Zoran), Mike Womac (Zoran), Chi-Wang "Jerry" Shum (Zoran), Ryan Lobo (Zoran), Barbara Ureste (Zoran), Lorne Olson, Ken Clayton, Kim Beumer, Will Ezell (Linear Technology Corp.), Jim Douglass (Linear Technology Corp.), Ping Zhou (Linear Technology Corp.), and Roger Kidson (Linear Technology Corp.). I learned something from each of you that has made me a better engineer, a better person, and a better colleague.

Lastly, and certainly not least, I would like to thank my wife for her unconditional love and support. Without her I would have lost my motivation long ago and would not have been able to complete this.

# TABLE OF CONTENTS

# CHAPTER

| Ι   | RESEARCH MOTIVATION                                                                                                                                                                                                                                                                                                                                                     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | A. Introduction       1         1. Structural Health Monitoring       2         2. Methods of SHM       4         3. Vibration Based SHM       4         B. Proposed Solution       6         C. Dissertation Organization       7                                                                                                                                      |

| II  | MAGNETIC SHAPE MEMORY ALLOY                                                                                                                                                                                                                                                                                                                                             |

|     | A. MSMA       10         B. Electromagnetism in the MSMA       15         1. Coil       16         2. Calculations       23         C. NiMnCoIn Measurements       27                                                                                                                                                                                                   |

| III | DC POWER GENERATION                                                                                                                                                                                                                                                                                                                                                     |

|     | A. Background32B. Energy Harvesting33C. Previous Work351. Rectifier Multiplier37D. CMOS Rectifiers391. Standard and Schottky Diode Rectifiers392. MOS Diode Rectifiers413. Efficiency Enhancement Techniques41E. Proposed Self-powered Rectifier451. Motivation452. Basic Architecture46F. Design Considerations541. Start-up542. Comparator Design573. Switch Sizing61 |

|     | 4. Capacitor Selection615. Ability to Power Other Circuits64                                                                                                                                                                                                                                                                                                            |

|     | <ul> <li>G. Measurement Results and Discussion</li></ul>                                                                                                                                                                                                                                                                                                                                      | 65<br>65<br>68<br>73<br>76                                                                                                                                             |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IV  | SENSOR AND MODULATION CHOICE                                                                                                                                                                                                                                                                                                                                                                  | 77                                                                                                                                                                     |

|     | A. Strain Gage Analysis                                                                                                                                                                                                                                                                                                                                                                       | 77<br>82<br>85<br>86<br>86<br>87<br>87                                                                                                                                 |

| V   | IMPULSE ULTRA WIDEBAND TRANSMITTER                                                                                                                                                                                                                                                                                                                                                            | 90                                                                                                                                                                     |

|     | <ul> <li>A. Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                            | 90<br>98<br>99<br>102                                                                                                                                                  |

| VI  | LOW-VOLTAGE LOW-POWER SUCCESSIVE APPROX-<br>IMATION ADC                                                                                                                                                                                                                                                                                                                                       | 103                                                                                                                                                                    |

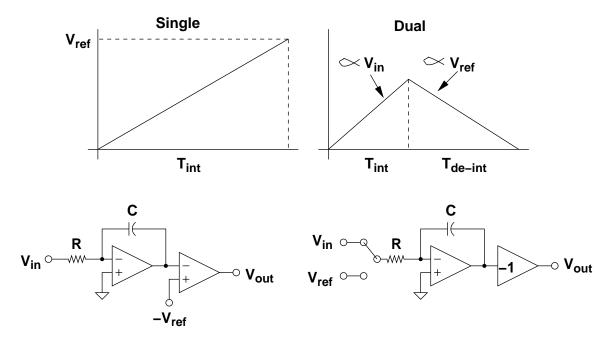

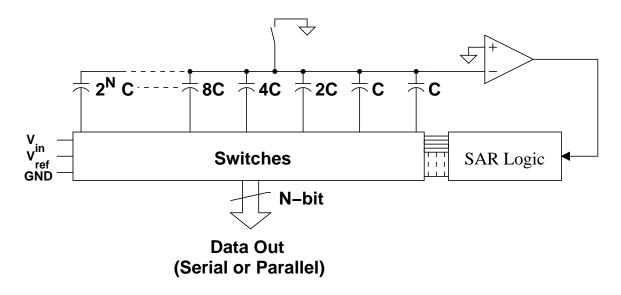

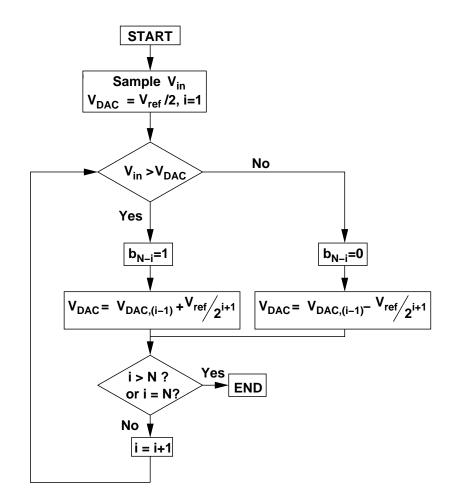

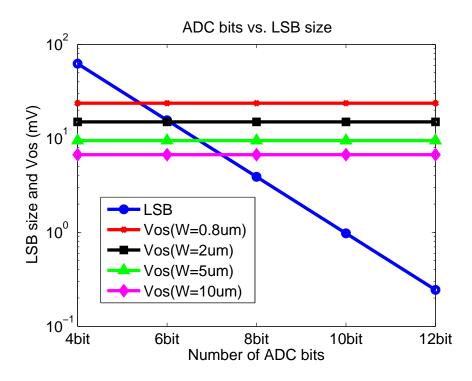

|     | <ul> <li>A. Introduction</li> <li>B. Low-Power ADCs</li> <li>1. Integrating ADC</li> <li>2. Successive Approximation Register ADC (SAR ADC)</li> <li>C. SAR ADC Design</li> <li>1. Number of Bits</li> <li>2. Comparator</li> <li>3. SAR Logic</li> <li>4. Clock Generation</li> <li>5. DAC</li> <li>D. Simulation Results</li> <li>E. Measurement Results</li> <li>F. Conclusions</li> </ul> | <ol> <li>103</li> <li>104</li> <li>106</li> <li>109</li> <li>111</li> <li>115</li> <li>118</li> <li>121</li> <li>122</li> <li>123</li> <li>125</li> <li>132</li> </ol> |

| VII | MULTI-BAND OFDM ULTRA WIDEBAND TRANSMITTER                                                                                                                                                                                                                                                                                                                                                    | 133                                                                                                                                                                    |

| A. Introduction                     | 133 |

|-------------------------------------|-----|

| B. UWB                              | 134 |

| C. UWB TX Design                    | 137 |

| 1. System                           | 137 |

| 2. Filter $\ldots$                  | 141 |

| 3. Mixer $\ldots$                   | 142 |

| 4. Power Detector $\ldots$          | 145 |

| D. Measurement Results              | 150 |

| E. Conclusion                       | 151 |

| VIII CONCLUSIONS AND FUTURE WORK    | 154 |

| A. Future Work/Research Suggestions | 155 |

| REFERENCES                          | 156 |

| VITA                                | 170 |

## LIST OF TABLES

| TABLE |                                                                                      | Page |

|-------|--------------------------------------------------------------------------------------|------|

| Ι     | Comparison of different power sources for sensor networks, (mod-<br>ified from [23]) | 11   |

| II    | Performance comparison with recently reported rectifiers                             | 75   |

| III   | MB-OFDM sub-carrier allocation.                                                      | 137  |

## LIST OF FIGURES

| FIGURE | Ξ                                                                                                                                                                                                                                                                        | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1      | Generalized SHM sensor architecture                                                                                                                                                                                                                                      | 7    |

| 2      | Different methods of flux change in NiMnGa and NiMnCoIn MS-<br>MAs upon mechanical loading/unloading in the presence of a bias<br>magnetic field.                                                                                                                        | 13   |

| 3      | Side cross-sectional view of the pick-up coil used with the MSMA material.                                                                                                                                                                                               | 17   |

| 4      | Equivalent electrical model of MSMA harvested voltage and coil resistance $R_{coil}$ with rectifier input resistance $R_L$                                                                                                                                               | 20   |

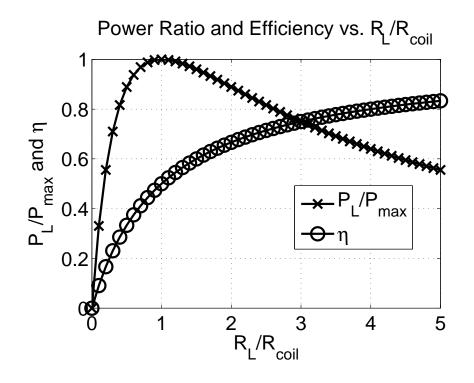

| 5      | Plots of (2.13), $\eta$ , and (2.14), $P_L/P_{max}$ , versus ratio of load resistance $R_L$ and coil resistance $R_{coil}$ to determine optimum value of RM input resistance and coil resistance to obtain a high efficiency and a reasonable power delivered to the RM. | 21   |

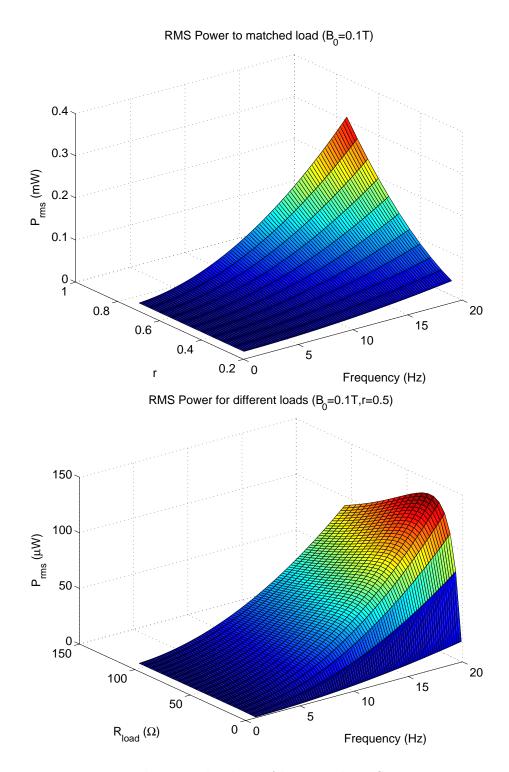

| 6      | Theoretical values of harvested RMS power                                                                                                                                                                                                                                | 24   |

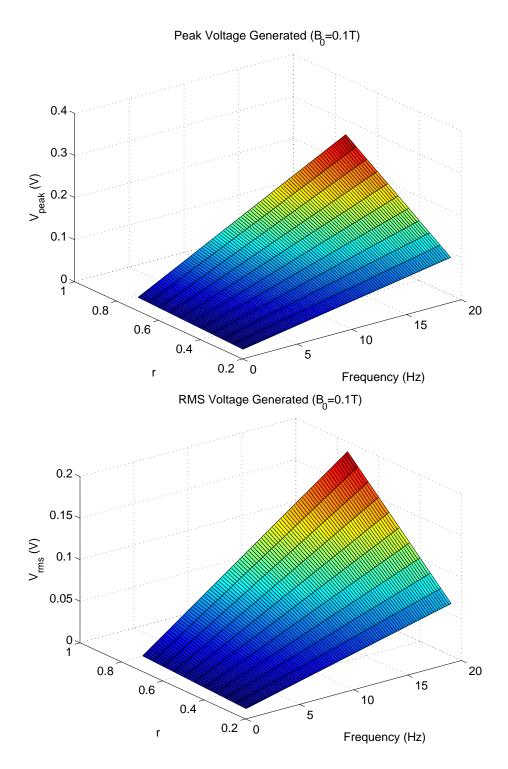

| 7      | Theoretical values of harvested peak and RMS voltages                                                                                                                                                                                                                    | 26   |

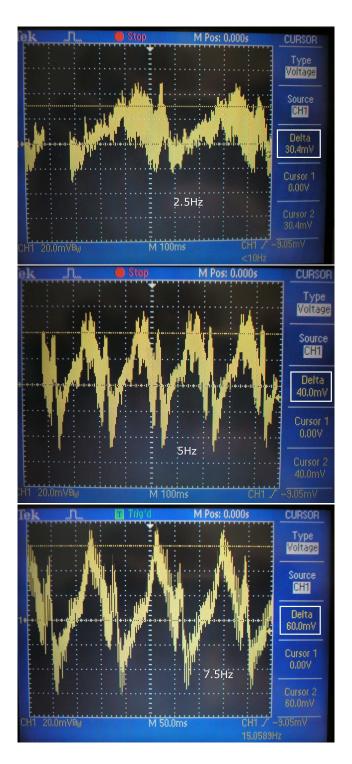

| 8      | Measured MSMA output voltage of the energy harvesting sample<br>at three different frequencies of sinusoidal mechanical excitation:<br>2.5, 5, and 7.5Hz                                                                                                                 | 28   |

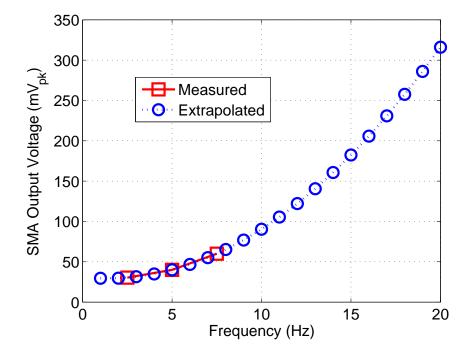

| 9      | Extrapolated MSMA output voltage vs. frequency.                                                                                                                                                                                                                          | 29   |

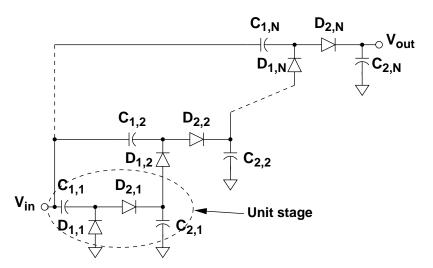

| 10     | Greinacher/Cockroft-Walton N-stage inductorless transformer                                                                                                                                                                                                              | 35   |

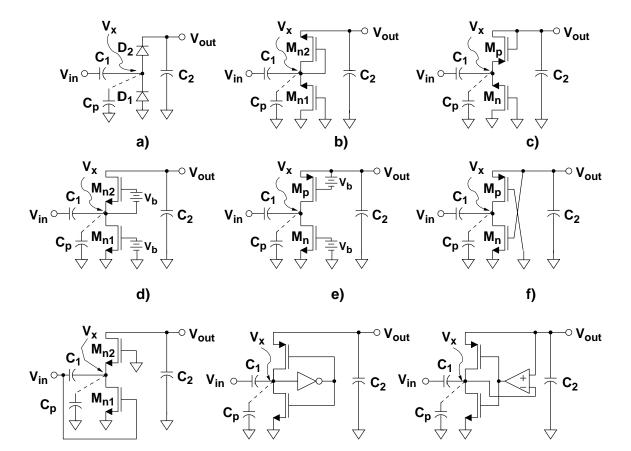

| 11     | Different rectifier architectures with: a) diodes, b) NMOS, c)<br>CMOS, d) EVC, e) IVC, f) SVC, g) bootstrapped, h) inverter-<br>based, i) comparator-based                                                                                                              | 40   |

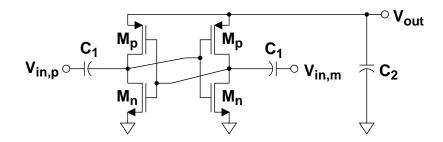

| 12     | Self-driven rectifier (Four Transistor Cell/Differential Drive Rec-<br>tifier/Negative Voltage Converter).                                                                                                                                                               | 43   |

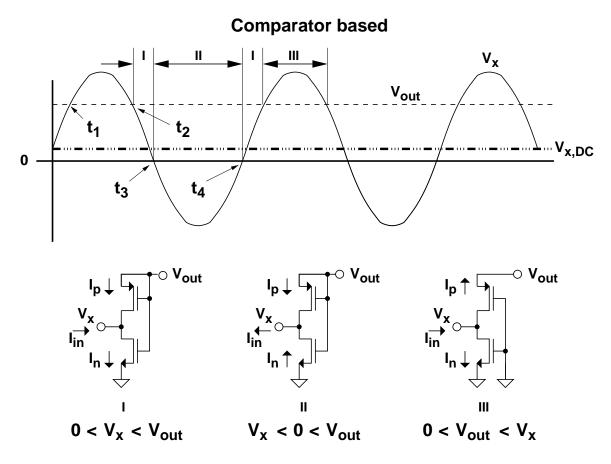

| 13 | Principle of operation of an ideal comparator based rectifier                                                                                                                                                                                                                                                                                                        | 47 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 14 | Proposed SPR with comparator (top) and detailed view of the clock doubler (bottom).                                                                                                                                                                                                                                                                                  | 49 |

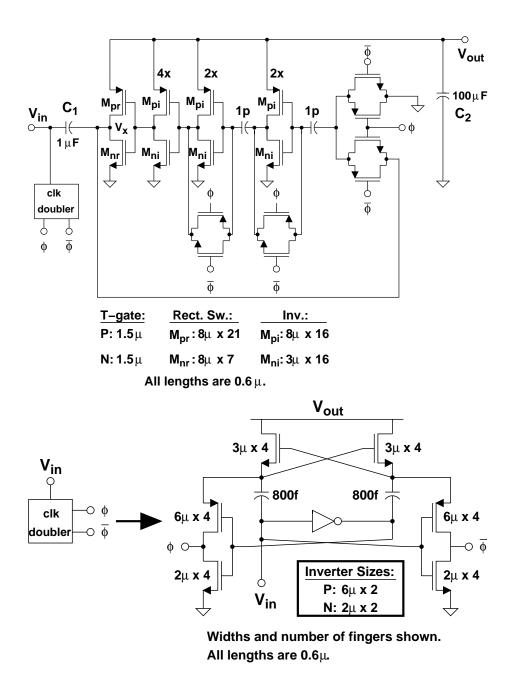

| 15 | Current waveforms for the proposed SPR                                                                                                                                                                                                                                                                                                                               | 53 |

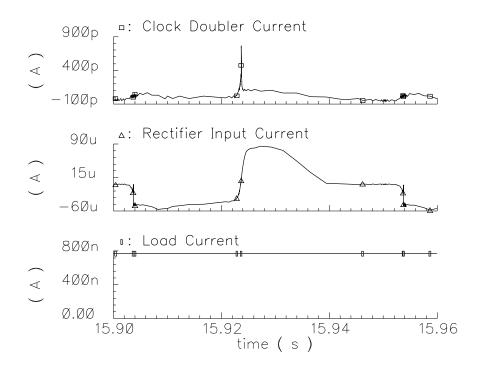

| 16 | Simulated SPR DC output voltage (top) and power conversion efficiency (bottom) for load resistances of $100k\Omega$ and $1M\Omega$ with a 20Hz input frequency.                                                                                                                                                                                                      | 55 |

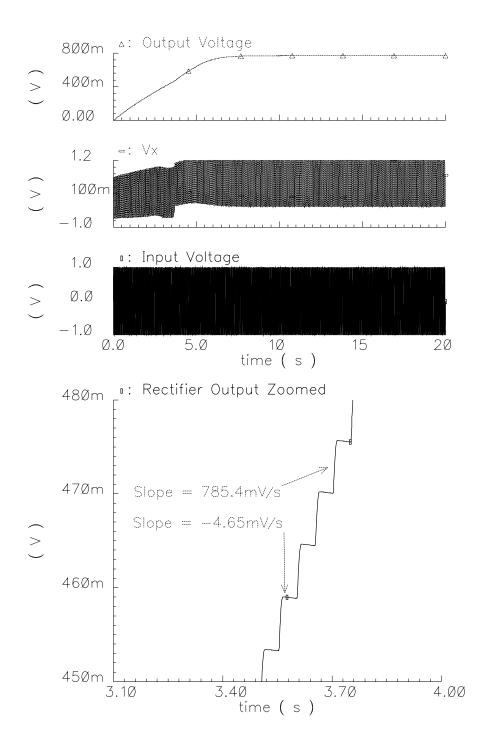

| 17 | Simulated rectifier voltage waveforms (top) and zoomed in view of<br>the rectifier output voltage during start up showing the charging<br>and discharging of the output capacitor (bottom)                                                                                                                                                                           | 58 |

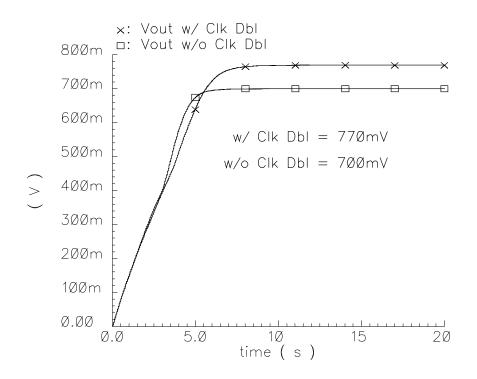

| 18 | Simulated DC output voltages of proposed SPR with clock doubling circuitry in the comparator to drive the transmission gates and without clock doubling circuitry where inverters are used to drive the transmission gates. The input signal was a 20Hz sinusoid with a 1V amplitude. The load was a 1M $\Omega$ resistor while $C_1 = 1\mu$ F and $C_2 = 100\mu$ F. | 60 |

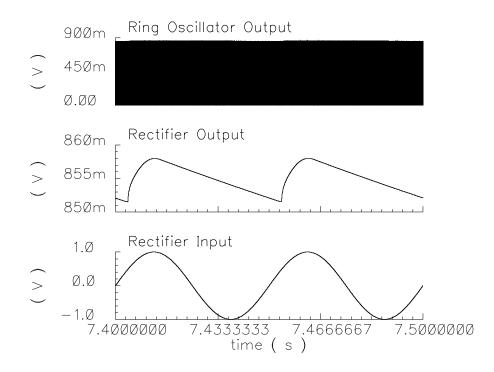

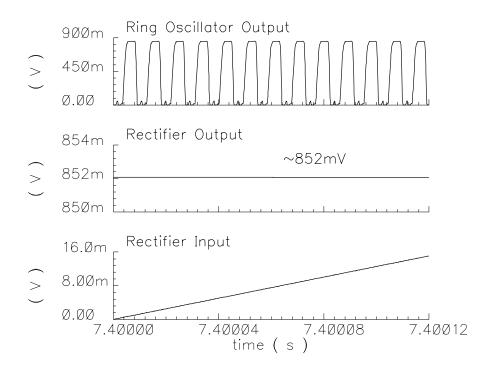

| 19 | Simulated 5-stage ring oscillator start-up powered by single stage<br>proposed SPR with $1V_{pk}$ , 20Hz input signal with $C_1 = 1\mu$ F and<br>$C_2 = 100\mu$ F. Oscillation frequency is approximately 6.3kHz                                                                                                                                                     | 63 |

| 20 | Zoomed view of Fig. 19                                                                                                                                                                                                                                                                                                                                               | 64 |

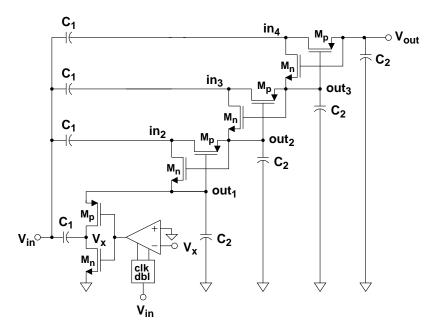

| 21 | 4-stage rectifier with proposed SPR and three cascaded SVC structures.                                                                                                                                                                                                                                                                                               | 65 |

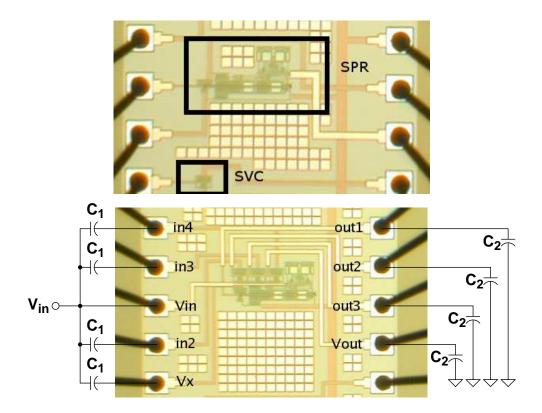

| 22 | ON $0.5\mu m$ CMOS SVC and SPR (top) and 4-stage rectifier with SPR and three cascaded SVC stages (bottom)                                                                                                                                                                                                                                                           | 66 |

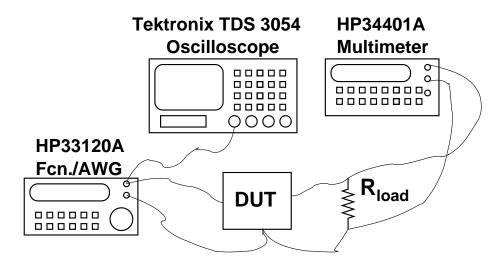

| 23 | Test-bench for rectifier measurements                                                                                                                                                                                                                                                                                                                                | 66 |

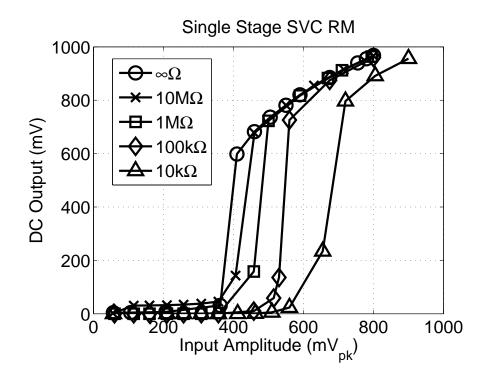

| 24 | Measured single stage SVC DC output voltage                                                                                                                                                                                                                                                                                                                          | 68 |

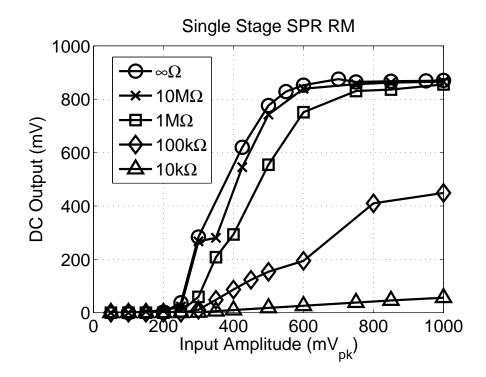

| 25 | Measured single stage SPR DC output voltage                                                                                                                                                                                                                                                                                                                          | 69 |

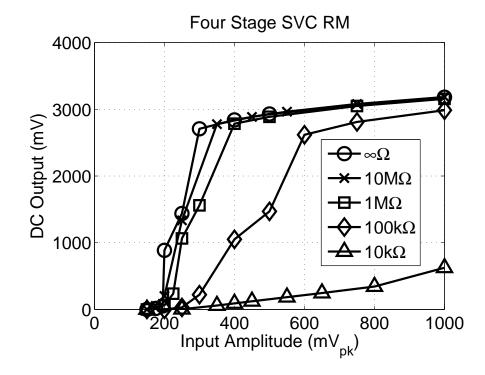

| 26 | Measured 4-stage RM SVC DC output voltage                                                                                                                                                                                                                                                                                                                            | 69 |

## FIGURE

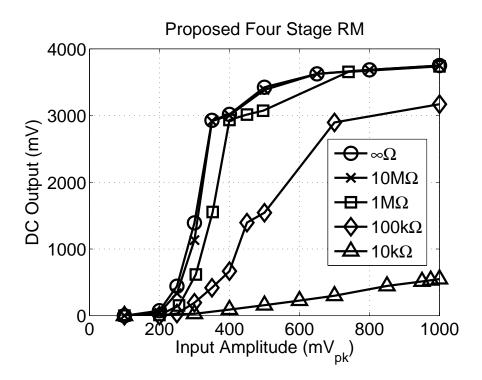

| 27 | Measured 4-stage RM utilizing the proposed SPR DC output voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

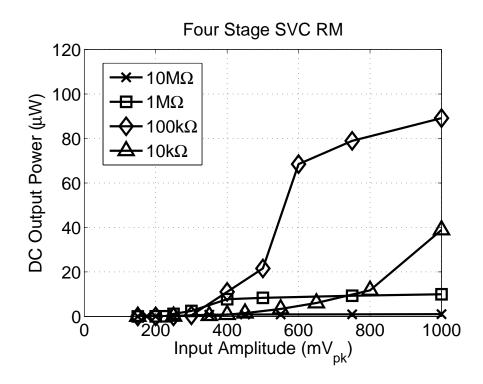

| 28 | Measured 4-stage SVC DC output power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70 |

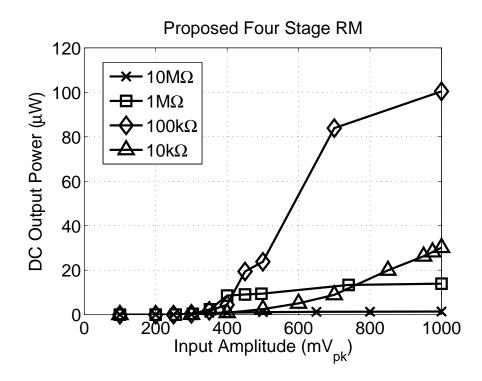

| 29 | Measured 4-stage RM utilizing the proposed SPR DC output power.                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71 |

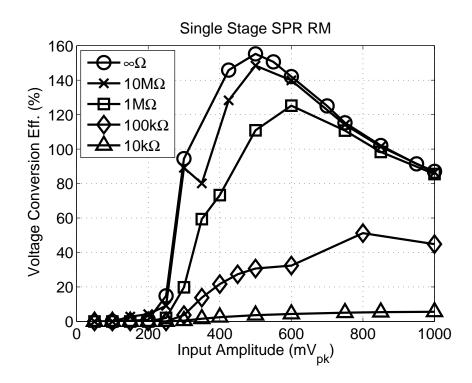

| 30 | Measured single stage SPR VCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 71 |

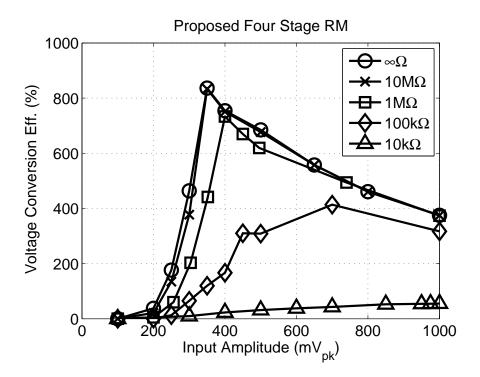

| 31 | Measured 4-stage RM utilizing the proposed SPR VCE                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72 |

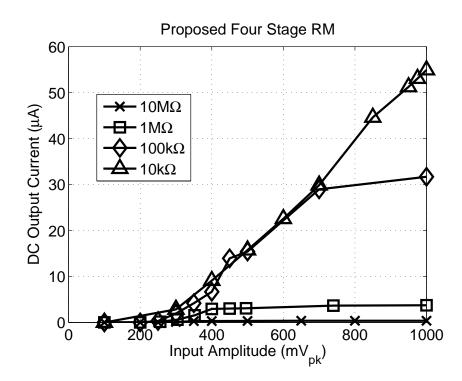

| 32 | Measured 4-stage RM utilizing the proposed SPR DC output current.                                                                                                                                                                                                                                                                                                                                                                                                                                              | 72 |

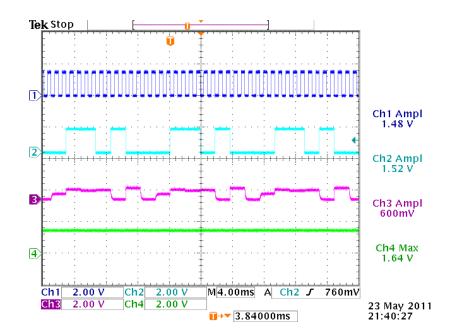

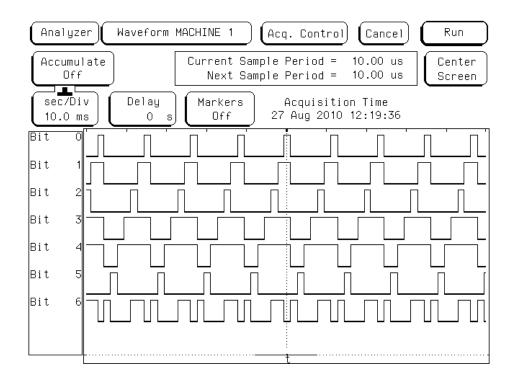

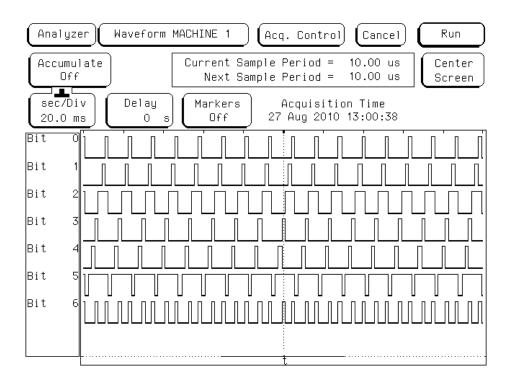

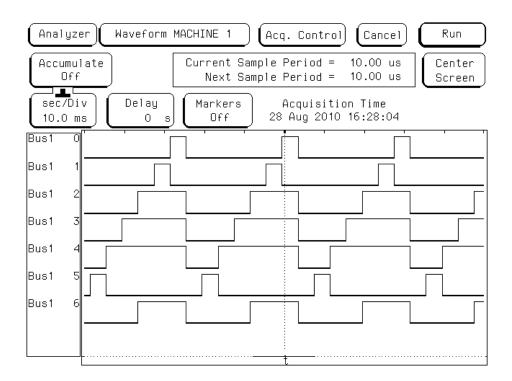

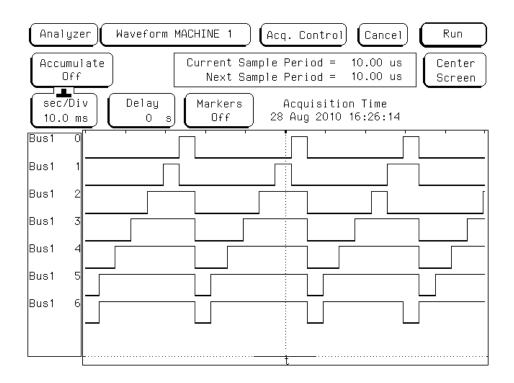

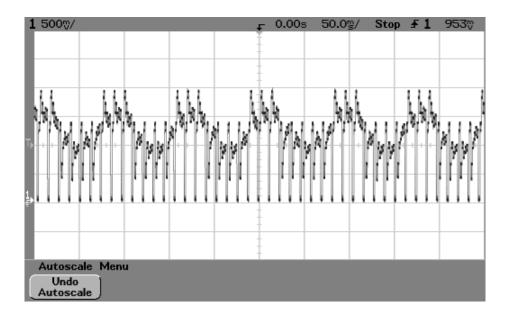

| 33 | Measurement results of the proposed 4-stage rectifier powering<br>a low-voltage, low-power 6 bit successive approximation register<br>analog-to-digital converter (SAR ADC). The input to the 4-stage<br>rectifier was a 20Hz sinusoid with a 1.2V amplitude. From top to<br>bottom, the measurement shows the output of the on-chip SAR<br>ADC clock generator, the serial output of the 6 bit SAR ADC,<br>the output of the DAC used in the SAR ADC, and the DC voltage<br>produced by the 4-stage rectifier | 74 |

| 34 | Generalized SHM sensor architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 78 |

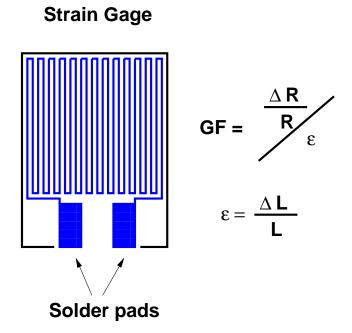

| 35 | Typical strain gage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 79 |

| 36 | Differential to single-ended converter/lowpass filter                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 80 |

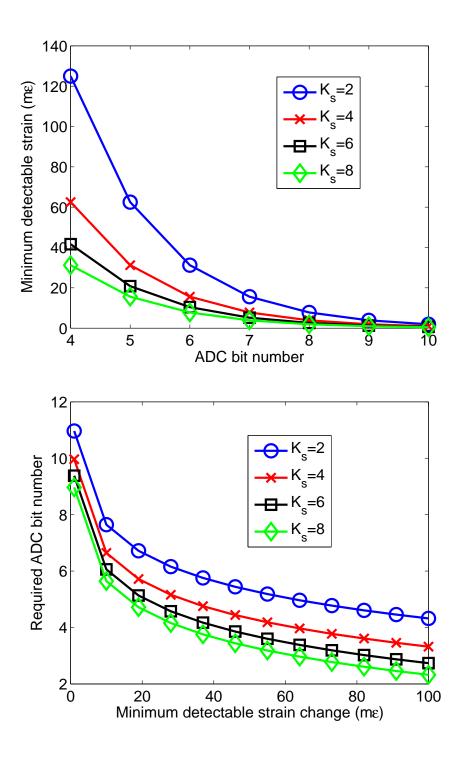

| 37 | ADC resolution and minimum detectable strain change for dif-<br>ferent gage factors: ADC bits as variable (upper); minimum de-<br>tectable strain change as variable (lower).                                                                                                                                                                                                                                                                                                                                  | 83 |

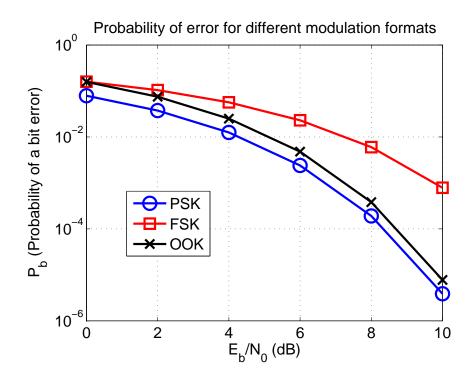

| 38 | Probability of bit error for three different modulation formats                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88 |

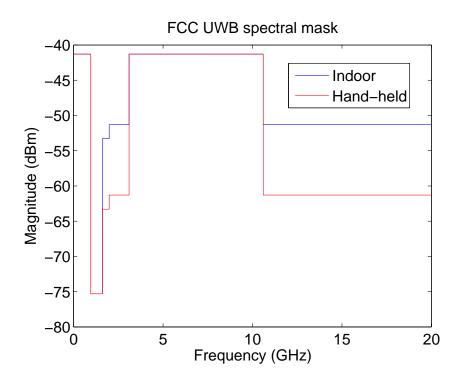

| 39 | FCC UWB spectral mask for indoor and outdoor transmissions                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 91 |

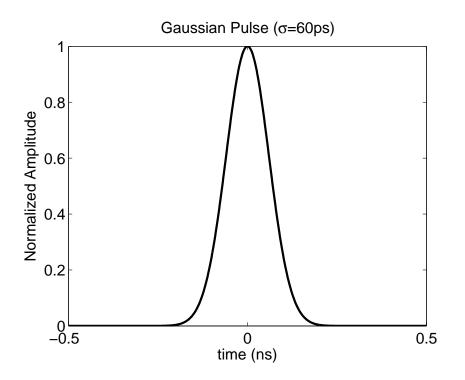

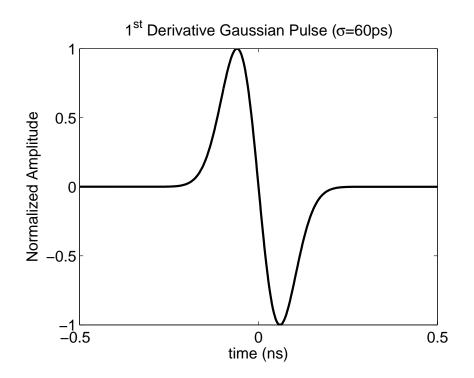

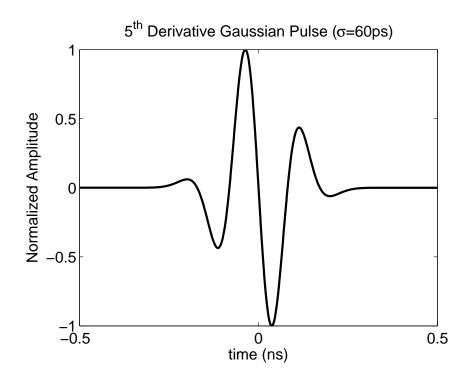

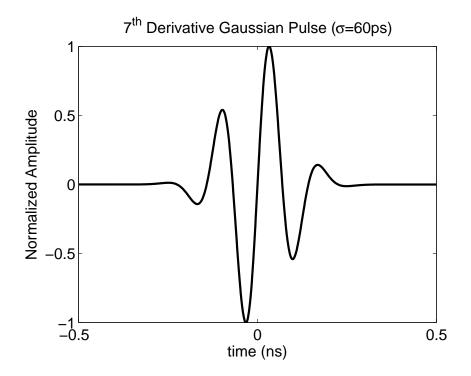

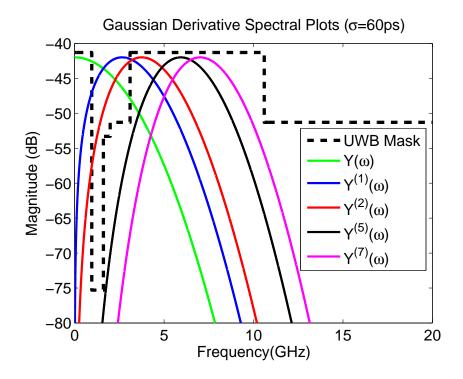

| 40 | Normalized response of the Gaussian pulse $\sigma = 60$ ps                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 92 |

| 41 | Normalized response of the Gaussian pulse $1^{st}$ derivative $\sigma=60 \mathrm{ps.}$ .                                                                                                                                                                                                                                                                                                                                                                                                                       | 93 |

| 42 | Normalized response of the Gaussian pulse $2^{nd}$ derivative $\sigma=60 \mathrm{ps.}$ .                                                                                                                                                                                                                                                                                                                                                                                                                       | 93 |

| 43 | Normalized response of the Gaussian pulse $5^{th}$ derivative $\sigma = 60$ ps.                                                                                                                                                                                                                                                                                                                                                                                                                                | 94 |

| 44 | Normalized response of the Gaussian pulse $7^{th}$ derivative $\sigma=60 {\rm ps.}$ .                                                                  | 94  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 45 | Normalized spectra of the Gaussian pulse and its $1^{st}$ , $2^{nd}$ , $5^{th}$ and $7^{th}$ derivatives and the UWB spectral mask provided by the FCC | 97  |

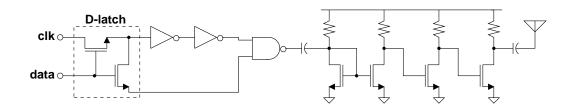

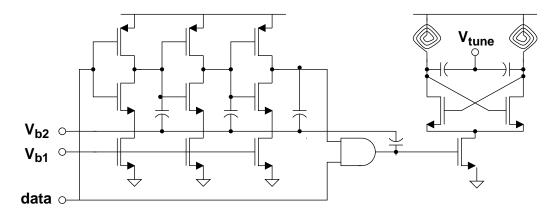

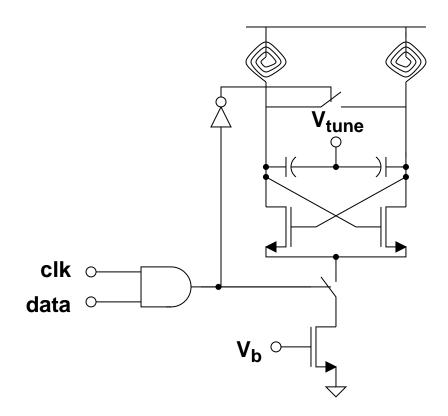

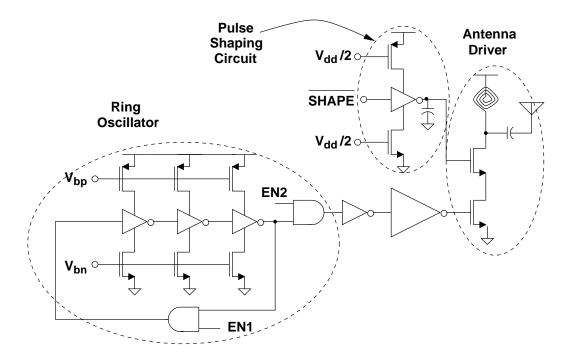

| 46 | Impulse radio UWB TX from [86]                                                                                                                         | 99  |

| 47 | Impulse radio UWB TX from [87]                                                                                                                         | 100 |

| 48 | Impulse radio UWB TX from [88]                                                                                                                         | 101 |

| 49 | Impulse radio UWB TX from [46]                                                                                                                         | 102 |

| 50 | Principle of single and dual-slope IADCs.                                                                                                              | 106 |

| 51 | Top-level view of a SAR ADC.                                                                                                                           | 107 |

| 52 | Binary Search Algorithm.                                                                                                                               | 109 |

| 53 | ADC LSB size and NMOS transistor input referred offset voltage<br>for $0.5\mu$ m CMOS and minimum length device                                        | 111 |

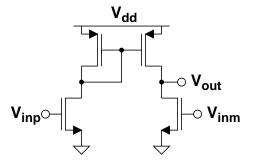

| 54 | Low-voltage Low-power Inverter Based Comparator.                                                                                                       | 114 |

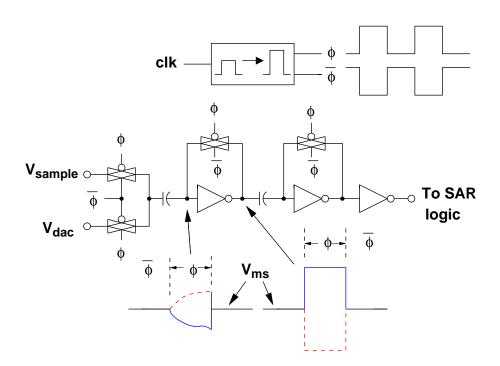

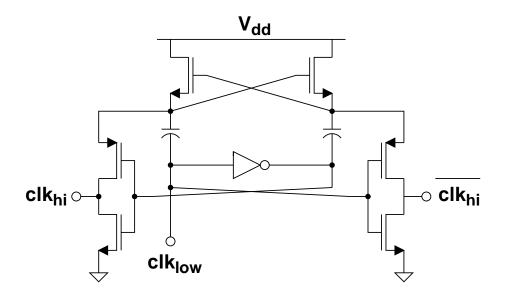

| 55 | Clock Voltage Doubler                                                                                                                                  | 116 |

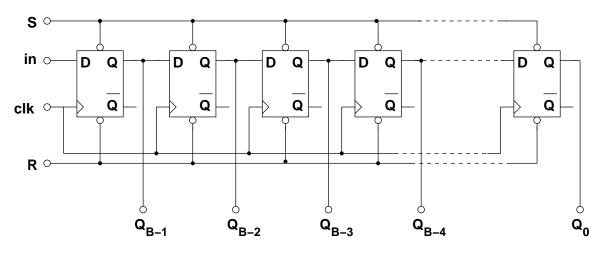

| 56 | Shift register.                                                                                                                                        | 117 |

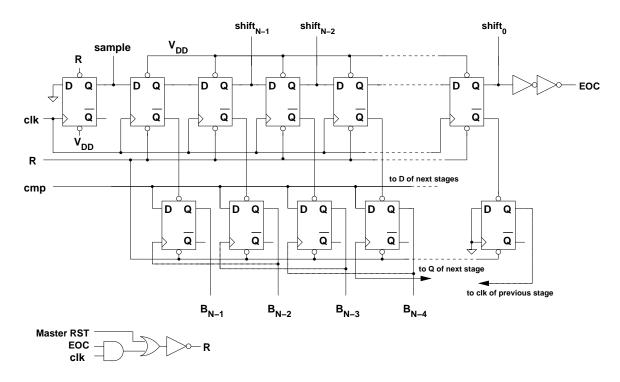

| 57 | SAR logic used to implement the binary search algorithm                                                                                                | 118 |

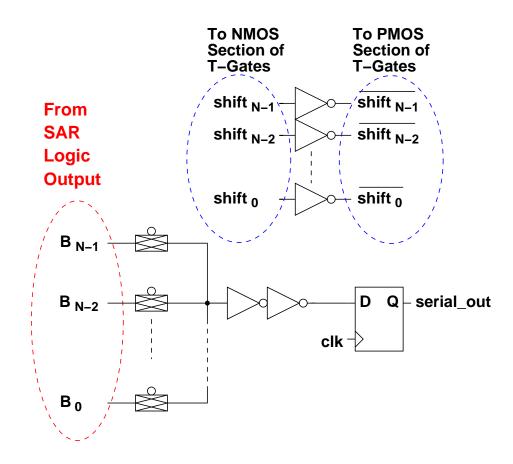

| 58 | Multiplexer used to implement the parallel to serial conversion                                                                                        | 119 |

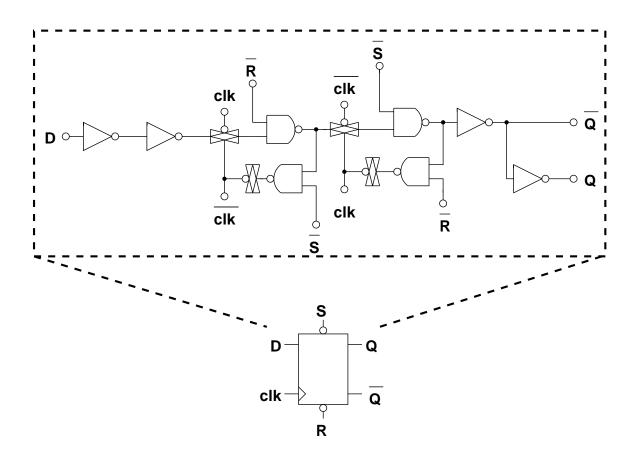

| 59 | Pass Transistor Logic D-Flip Flop based on NAND gates                                                                                                  | 120 |

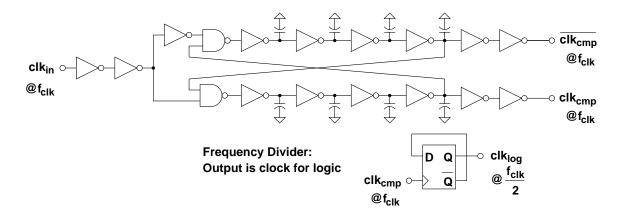

| 60 | Non-overlapping Clock Generator and Frequency Divider                                                                                                  | 121 |

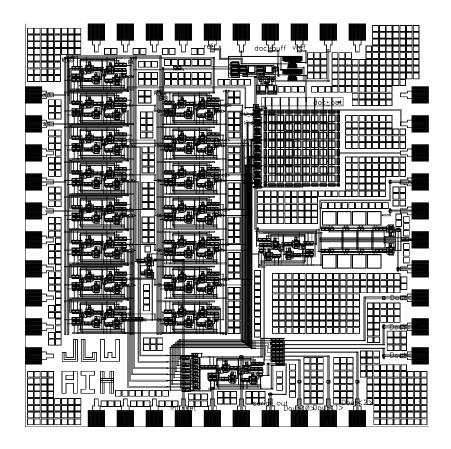

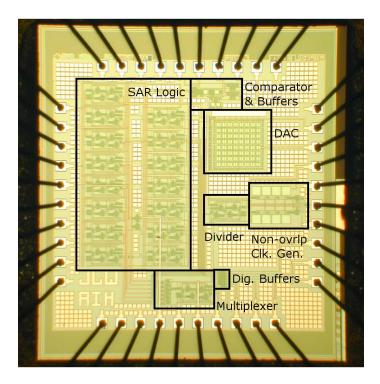

| 61 | Layout of the 6-bit SAR ADC.                                                                                                                           | 123 |

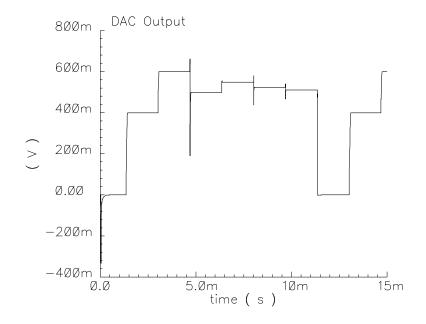

| 62 | DAC output for a 513mV sampled value                                                                                                                   | 124 |

| 63 | ADC output and master clock signal                                                                                                                     | 124 |

| 64 | Chip micrograph of ON $0.5\mu$ m CMOS SAR ADC                                                                                                          | 125 |

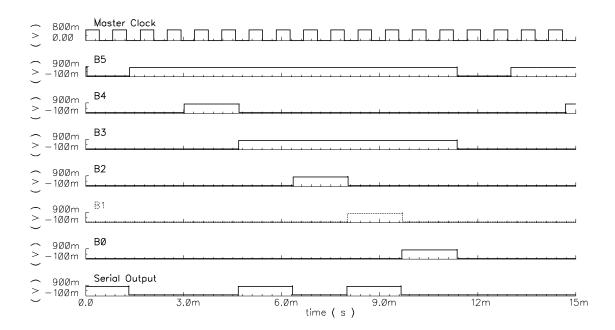

| 65 | Measured SAR ADC outputs for $V_{dd} = 0.9V$ and $V_{in} = 513mV$                        | 126 |

|----|------------------------------------------------------------------------------------------|-----|

| 66 | SAR ADC output bits for $V_{ref} = 0.3V_{DC}$ , $V_{dd} = 0.9V$ , $f_{clk} = 1.2kHz$ .   | 126 |

| 67 | SAR ADC output bits for $V_{ref} = 0.5V_{DC}$ , $V_{dd} = 0.9V$ , $f_{clk} = 1.2kHz$ .   | 127 |

| 68 | SAR ADC output bits for $V_{ref} = 0.8V_{DC}$ , $V_{dd} = 1.8V$ , $f_{clk} = 1.2kHz$ .   | 128 |

| 69 | SAR ADC output bits for $V_{ref} = 1.72 V_{DC}$ , $V_{dd} = 1.8V$ , $f_{clk} = 1.2kHz$ . | 129 |

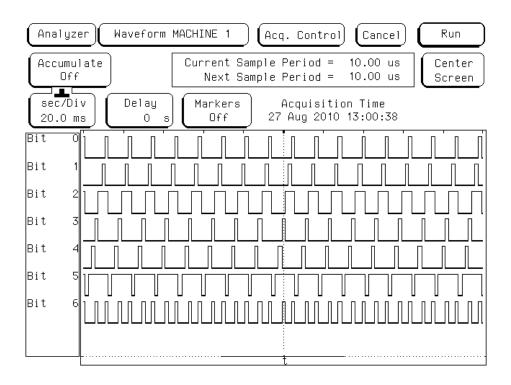

| 70 | Oscilloscope plot of the DAC output with a sine wave input                               | 129 |

| 71 | Zoomed view of oscilloscope plot of the DAC output with a sine wave input.               | 130 |

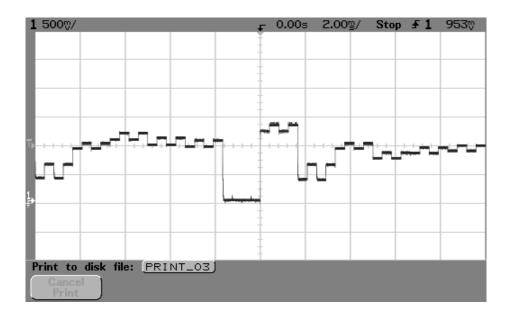

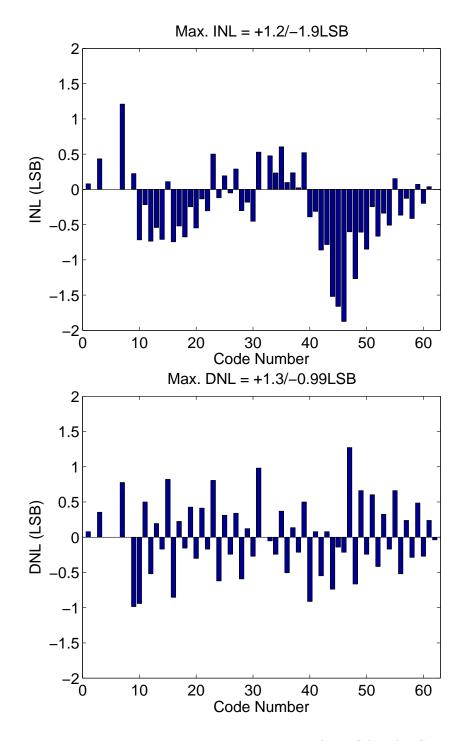

| 72 | Measured INL and DNL of the SAR ADC                                                      | 131 |

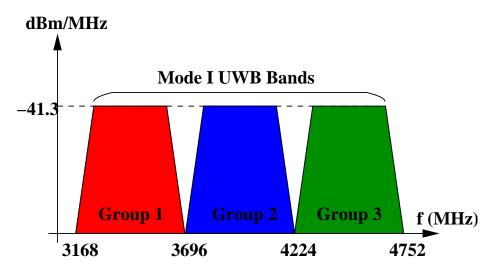

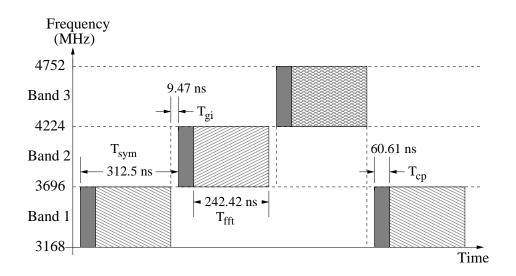

| 73 | MB-OFDM UWB spectrum                                                                     | 135 |

| 74 | UWB band-hopping scheme                                                                  | 136 |

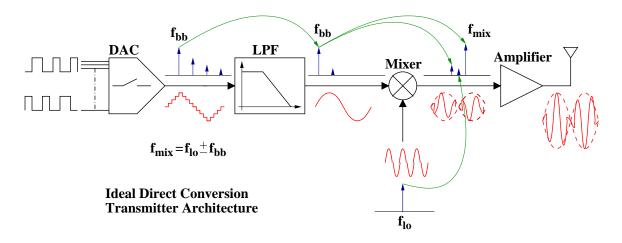

| 75 | Ideal Direct Conversion TX with frequency and time domain signals.                       | 139 |

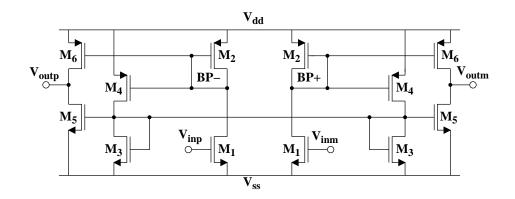

| 76 | UWB LPF biquad schematic.                                                                | 141 |

| 77 | UWB LPF schematic.                                                                       | 142 |

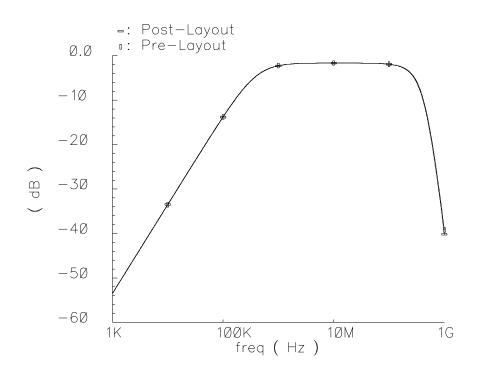

| 78 | UWB LPF pre and post-layout AC simulation results                                        | 143 |

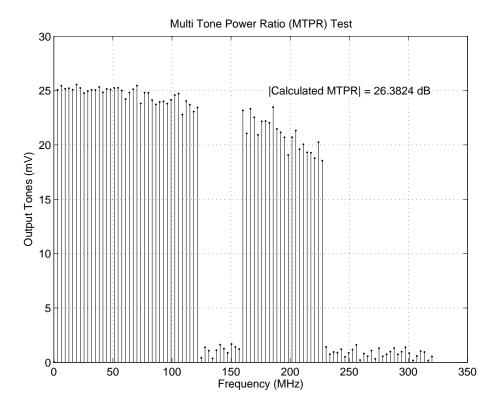

| 79 | UWB LPF post-layout MTPR results                                                         | 144 |

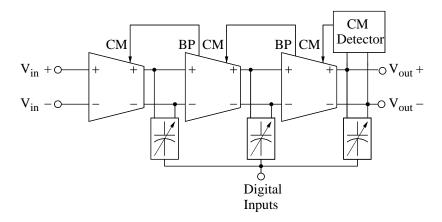

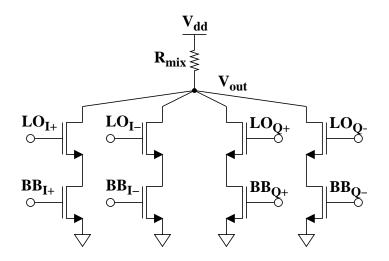

| 80 | UWB up-conversion mixer schematic                                                        | 144 |

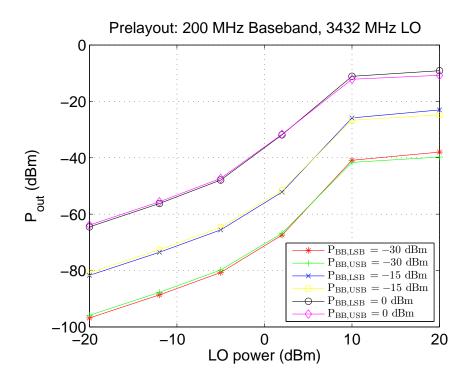

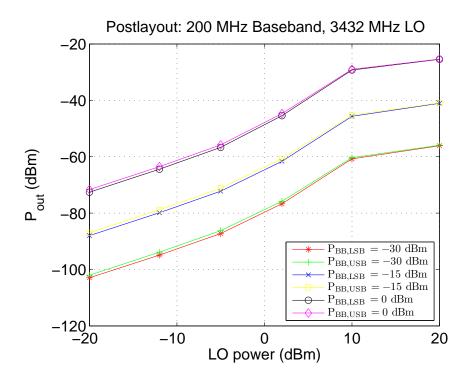

| 81 | UWB mixer pre-layout sims. 200MHz baseband and 3432MHz LO. $$ .                          | 145 |

| 82 | UWB mixer post-layout sims. 200MHz baseband and 3432MHz LO                               | 146 |

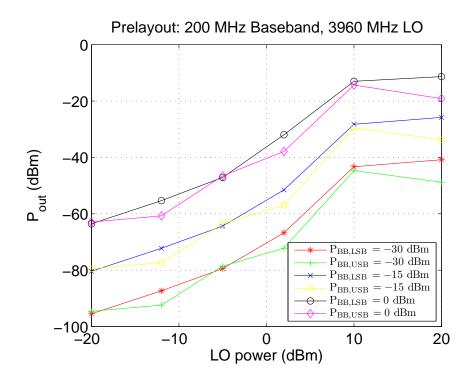

| 83 | UWB mixer pre-layout sims. 200MHz baseband and 3960MHz LO. $$ .                          | 146 |

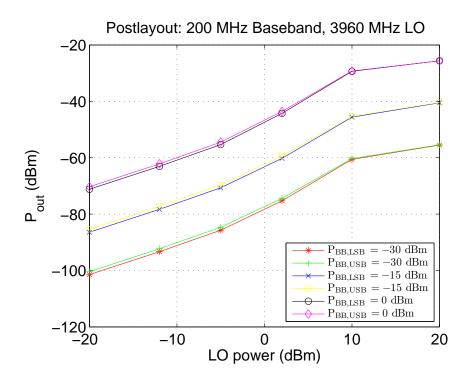

| 84 | UWB mixer post-layout sims. 200MHz baseband and 3960MHz LO                               | 147 |

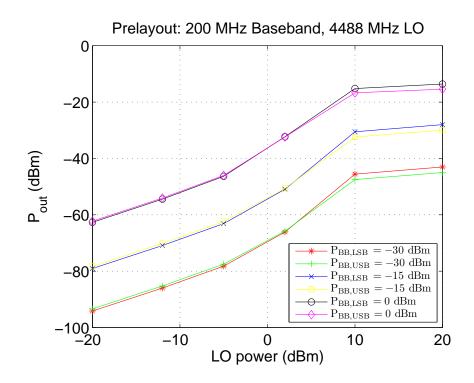

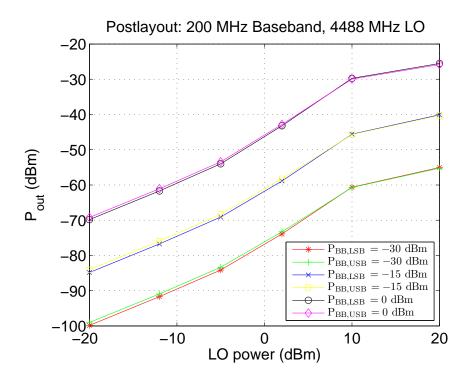

| 85 | UWB mixer pre-layout sims. 200MHz baseband and 4488MHz LO. $$ .                          | 147 |

# FIGURE

| 86 | UWB mixer post-layout sims. 200MHz baseband and 4488MHz LO                                                 | 148 |

|----|------------------------------------------------------------------------------------------------------------|-----|

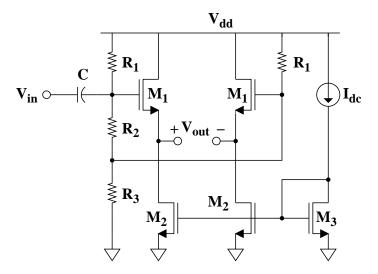

| 87 | UWB power detector schematic.                                                                              | 149 |

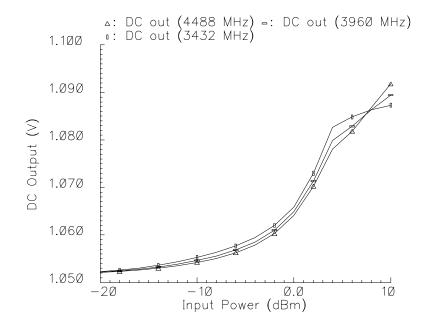

| 88 | UWB power detector post-layout DC output                                                                   | 149 |

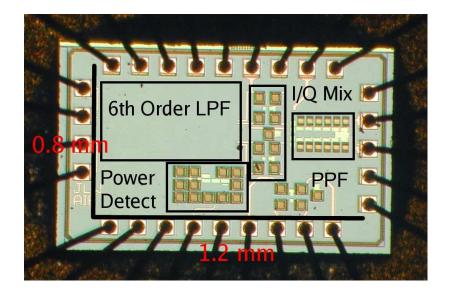

| 89 | UWB TX chip micrograph                                                                                     | 150 |

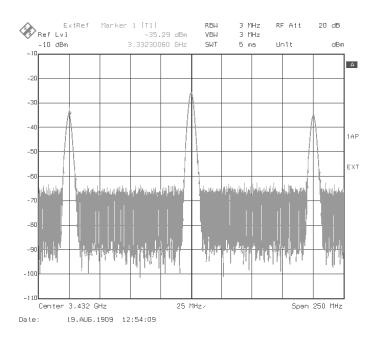

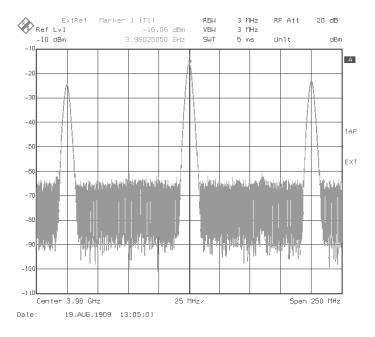

| 90 | Measured I channel mixer output 3432MHz LO 100MHz BB. $\ .\ .$ .                                           | 151 |

| 91 | Measured I channel mixer output 4488MHz LO 100MHz BB. $\ .\ .$ .                                           | 152 |

| 92 | Measured I channel mixer output 3960MHz LO 100MHz BB. $\ . \ . \ .$                                        | 152 |

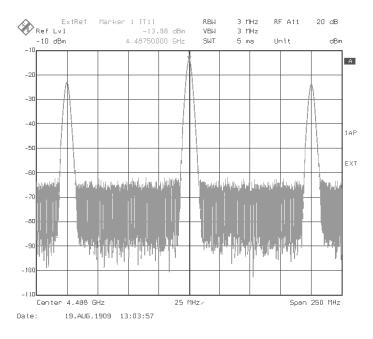

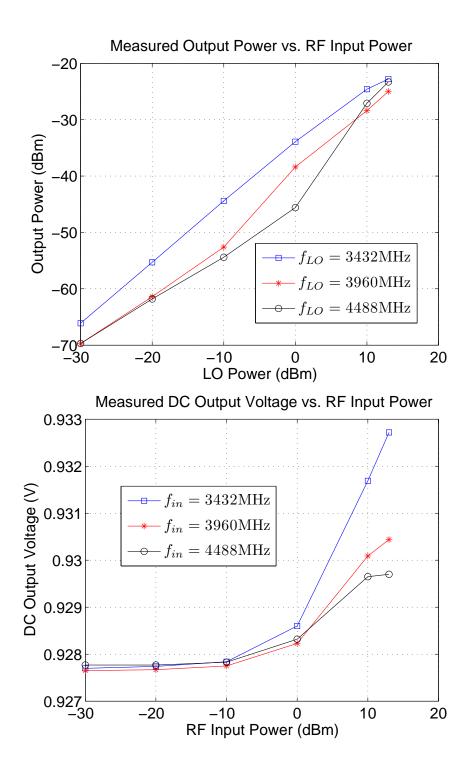

| 93 | a) Measured I channel mixer output power as a function of LO amplitude; b) Measured power detector output. | 153 |

#### CHAPTER I

#### RESEARCH MOTIVATION

Concrete gained popularity over marble with the Romans for two reasons: 1) it was easier to mold into desired shapes; and 2) it was less costly than other hard materials. The concrete which the Romans used had a comparable compressive strength to the concrete which is used today. The main difference between the concrete used by the Romans and the concrete used today is the reinforced steel, or rebar, in modern concrete. The rebar is a steel rod which is textured to provide better anchoring to the concrete. It is used within modern concrete structures to provide a greater tensile strength than the concrete used by the Romans. One of the main applications of concrete, at least in the U.S., is the construction of roads, highways, and bridges.

#### A. Introduction

With concrete being such a widely used material in the world it is necessary to insure a robust performance to day-to-day use. However, concrete is usually exposed to elements, changes in the Earth (e.g., earthquakes, mudslides, etc.), and a host of other events which compromise the integrity of concrete structures. Even with the introduction of rebar to improve the tensile strength of concrete, there is only so much damage and abuse a structure can take before it must either be repaired or replaced. One cause of deficient concrete is cracking due to the introduction of water into porous regions which then expand and corrode the concrete's internal structure. Over a period of years this corrosion may lead to larger cracks, holes, or even the eventual collapse of a structure. To avoid accidents, injuries, and deaths it is necessary

The journal model is IEEE Journal of Solid-State Circuits.

to identify and mitigate any issues which may occur with concrete structures.

#### 1. Structural Health Monitoring

In the U.S. alone there are more than 55,000 interstate bridges in use today, of which approximately 25% are deemed as structurally deficient [1]. It is estimated that it will cost more than \$9 billion USD and more than 20 years to fix all deficient bridges while costing even more to maintain the bridges on this list. These reports do not go into full detail on the status of other infrastructures in the U.S. (buildings, roads, etc.). Often times these deficiencies are not a major threat to individuals and their daily routine. Even though the threats are not apparent on a daily basis, the potential to cause damage and injury is there. For example, in late 2007 a portion of I-35 in Minnesota collapsed killing 13 people and injuring 145. According to the National Transportation Safety Board (NTSB), the crash was attributed to an inherent design flaw in the structure and a larger load than the bridge had been designed for [2]. While design flaws are not something that are intended, they do occur. Had a fault detection system been in place during the bridge's operation, perhaps the danger could have been predicted and avoided.

To help mitigate the threats posed by civil infrastructures to people it is necessary to implement methods of determining the state of these civil infrastructures. The term used to describe the analysis and determination of the state of a civil infrastructure is dubbed Structural Health Monitoring (SHM). One of the first implemented, as well as one of the most common methods, of SHM in use today is visual inspection. Road crews drive, walk, climb, etc., along roads and bridges, buildings and other structures, to see if there are any major deficiencies. These inspectors are trained on what types of things to look for (cracks, rigidness, etc.) as well as locations of the most common failures (corners, girder connections, bolts, etc.). One of the drawbacks to this method is by the time there is visual confirmation of concrete damage it is often beyond repair or the damage has progressed to a stage which cannot be detected through visual methods alone [3]. According to [4], visual inspection has significant shortcomings which affect the ability to properly determine the reliability and accuracy of visual inspection techniques. This is attributed to personal feelings and comfort levels of the evaluators. An example of one factor is an individual's comfort level with heights and their inability to perform an in-depth analysis due to fear.

Although visual inspection should still remain as a method of monitoring civil infrastructures, it is necessary to implement a system based on sensors. To this end, the sensors would provide an unbiased record of the structure. As such, more focus needs to be turned to a system based on mechanical and/or electronic systems to determine if there are structural deficiencies. These SHM systems can typically be classified into two main categories: destructive and non-destructive. Destructive damage evaluation (DDE) is performed when a building, road, bridge, etc., must be torn apart to determine the integrity of the material and to make a determination about any issues which are present. Non-destructive damage evaluation (NDE) is usually performed by studying different properties of the bridge without modifying the structure in any way. Some of the parameters which are evaluated are strain or stress at different points on or within the structure, frequency and modes of vibration, impedance changes and others [3].

An issue with many of the forms of NDE is they either require regular human interaction with the system or they require cables to be distributed throughout the infrastructure to provide power, send and receive information, etc. Ideally, human interaction should be minimized with the system due to inconvenient and/or dangerous sensor placement making it difficult for an individual to access. For typical SHM systems where cables are used to transmit the data to a central data processing point, it is necessary to have the cables placed appropriately during initial construction of the structure. If the cables become exposed to the elements there is a potential these cables may become damaged. Additionally, if any issues occur where there is a break or a crack in the concrete structure around the cables, a great deal of stress may be placed on the cables causing them to break and require replacement. For systems which are battery powered, the batteries may only last a few days, months, or years before requiring replacement. This is not only an inconvenient task, but it is also one which could prove costly in the event many sensors are used in a given location.

#### 2. Methods of SHM

Since visual inspection in itself is not the most efficient method to determine deficiencies in a structure, SHM has taken on many forms. In [5–10] the authors describe the fact that when a vehicle passes over a bridge or roadway, there is a vibration in the bridge at a specific frequency which is related to the speed of the vehicle, the relative ratio of the masses of the vehicle and the bridge span, as well as the length of the bridge section, among other things. In [11] the authors devise a system which looks at the electrical impedance change of a section of concrete when cracks appear. In [12] Eddy currents are detected through a coil placed along a section of road and impedances are measured and shown to change when a damage is near. Additionally, the impedance difference will be greater the closer one gets to the damage, thus allowing one to determine where the damage is located. In [13] the authors use a method of visual inspection using cameras to determine where faults may be located.

#### 3. Vibration Based SHM

Regardless of how well any system is secured, how much mass a system contains, the ambient/core/operating temperature of a system, etc., everything vibrates. Whether

it is from moving parts within the system, a passer-by driving or walking near the system, or from the rotation of the Earth, everything vibrates. While this is an issue in many cases, for the purpose of powering a sensor network for SHM this is a benefit. Over the past 20 years there has been extensive research in using the vibrational properties of bridges and other structures to determine faults in the system [5–10] and [14–20]. When dealing with vibrations and determining what information should be extracted, there are typically two things that one can look at: frequency of vibration and modal shapes (i.e., the amplitudes and general waveform shapes of the oscillations). Both of these characteristics for a bridge are characteristic of the type of bridge, length of the bridge, length of the bridge span, and other factors. Therefore, these properties must be determined soon after the bridge is completed in order to track any changes. One method of doing this is to measure the driving frequency of the bridge. The driving frequency is determined by using a vehicle with a well-known mass and driving the vehicle over a span of the bridge in question. The data of the bridge vibration is then gathered and the frequencies of vibration of the bridge are then computed using an FFT. The relationship between the speed of a vehicle and its driving frequency is

$$\omega_d = \frac{\pi v}{L} \text{ rad/s} \tag{1.1}$$

where v is the vehicles velocity in meters per second and L is the span of the bridge section. For vehicle speeds of 5, 10 and 15 m/s (11.18, 22.36 and 33.54 mph) the driving frequencies are 0.1, 0.2 and 0.4Hz, respectively. This is typically well below the bridges natural frequency (typically 2-20Hz) and therefore oscillation is avoided. Since most of these vibrations are at low frequencies, the detection of the oscillations should be done with devices having a fairly low input impedance at these frequencies (e.g., inductive and not capacitive as in the case of piezo based measurement equipment) to facilitate measurements and circuit design.

It has been shown in [7] that the bridge natural frequency changes when there is a damaged section of the bridge. Therefore, it can be concluded that proper detection of this frequency can allow for determination of the state of the bridges health. Once this is done, the information must then be sent back to a data collection center for processing. One method to do this would be running cables throughout the structure, but this may lead to problems as the cables themselves could easily become damaged and would require replacement. To this end, the information should be transmitted wirelessly and the sensors would then be powered from a different source. One method of obtaining power for use in circuits is the use of a battery. However, for SHM, batteryless devices are a better approach as they inherently require less maintenance. Therefore, efforts have been made to scavenge energy from the bridge vibration to power the sensor system [21].

#### B. Proposed Solution

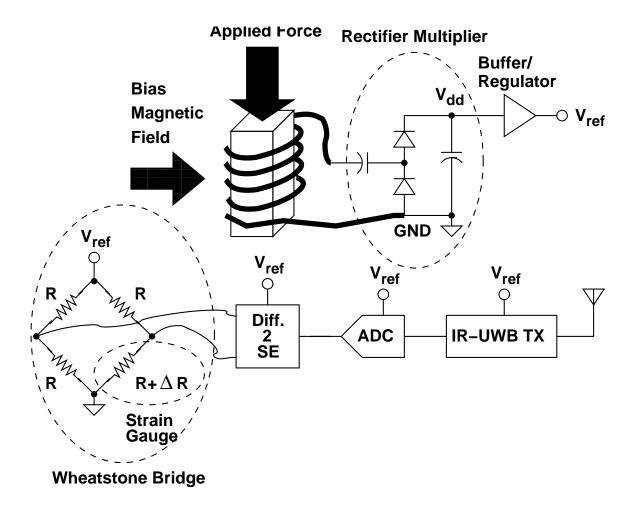

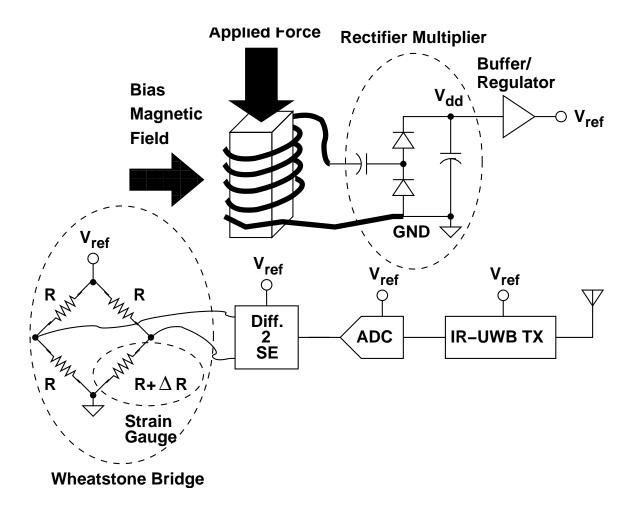

In this work a self-powered wireless sensor system is proposed with an intended application for NDE SHM of civil infrastructures with a targeted application of bridges, although the system could be applied to any concrete structure. The proposed system is comprised of a a vibrational energy harvesting component, power conditioning circuitry, a sensor, a low-power circuit to convert the sensor information into an electrically digital signal, and a low-power transmitter to send the data to a central data processing location. The proposed system contains no external battery which provides the benefit of fewer human interactions and therefore a lower cost. A general diagram of the proposed system is shown in Fig. 1.

Fig. 1.: Generalized SHM sensor architecture.

### C. Dissertation Organization

The dissertation is organized as follows: chapter 2 discusses a Magnetic Shape Memory Alloy (MSMA) material which is intended to serve as the energy harvesting mechanism; chapter 3 discusses some methods of DC power extraction from the MSMA material using low-power and efficiency-enhanced AC-DC converters (rectifiers); chapter 4 provides a discussion on data modulation choices for the sensor information as well as information on the proposed sensor for the wireless sensor system; chapter 5 provides information about the implementation of a wireless transmitter; and chapter 6 is focused on the design, simulation, and measurement of a low-power ADC. In addition to the proposed low-power wireless sensor system, chapter 7 gives the background, design and chip measurement of a mode-I multi-band OFDM ultra-wideband transmitter (MB-OFDM UWB TX). Finally, chapter 8 provides some conclusions and future work.

#### CHAPTER II

#### MAGNETIC SHAPE MEMORY ALLOY

A shape memory alloy (SMA) is an alloy which 'remembers' its original shape and will return to this state after deformation. The ability of the SMA to return to its original shape implies the strain applied to the material is in the material's elastic region meaning Hooke's Law (2.1),

$$\sigma = \epsilon E \tag{2.1}$$

where the tensile stress ( $\sigma$ ) is equal to the strain ( $\epsilon$ ) times a constant (E =Young's Modulus), still holds. The elastic ability of SMAs have recently made them a viable solution in sensing, actuation, power generation and magnetic refrigeration applications. One of the driving forces behind using these materials for these applications is their structural robustness compared to more brittle devices, namely piezoelectrics. SMAs are typically compounds of CuZnAlNi, NiTi, NiMnX (where X can be Ga or CoIn) or CuAlNi, to name a few. For sensing and power generation applications, systems will typically directly adapt mechanical changes into an electrical signal (as in the case of piezoelectrics). However, this is usually done with a very low conversion efficiency as mechanical changes are typically fairly low frequency (< 1kHz) and the components used to perform the mechanical-to-electrical conversion (MEC) are better suited for higher frequency applications (> 10kHz).

In [22] a method of improving the efficiency of the MEC is proposed where first the magnetic flux change of the material induced by a mechanical change is subsequently converted into an electrical signal. It is shown in this paper that the potential harvestable electrical energy from low frequency vibrations is significant enough to power a sensor and its associated wireless circuitry (>  $100\mu$ W). The SMA used in [22] is slightly different in nature than those which are typically studied as it converts mechanical changes into magnetic flux changes putting it in a class of SMA devices which are known as magnetic shape memory alloys (MSMAs). These MSMA devices are very well-suited for applications where a force will be applied regularly and in a system which will experience regular vibrations. Table I provides a list of different theoretically attainable powers and/or energies from different energy harvesting methods [23]. As is seen from the table, vibrational energy harvesting has the potential to obtain enough energy to power an array of electronic and sensing devices.

### A. MSMA

As mentioned previously, to help improve the efficiency of the MEC at lower frequencies, MSMA devices show a greater promise than other materials which are currently employed (namely piezoelectric devices). One of the main reasons why is because piezoelectric materials tend to have an electrical impedance which is capacitive. As such, if the load of the piezoelectric device is not a relatively high impedance at the frequency of excitation then the efficiency of the conversion is limited. Additionally, the piezoelectric device must be excited at a high enough frequency to help lower the effective source impedance and produce a usable output level. Some recently reported results show that practical power levels may be obtained by using piezoelectric devices, but these results still rely on fairly high frequencies and/or the addition of batteries to power the harvesting circuitry [24, 25]. For piezoelectric systems, the mechanical system then becomes the limiting factor as most mechanical systems do not work well and/or are incapable of operating at as high of a frequency as the corresponding electrical circuitry. Although civil structures such as bridges

### Table I.

|                                |                      |                  |                          | Add.    | Volt. Reg. | Easily   |

|--------------------------------|----------------------|------------------|--------------------------|---------|------------|----------|

| Power Source                   | $\frac{\mu W}{cm^3}$ | $\frac{J}{cm^3}$ | $\frac{\mu W}{cm^3}$ yr. | Storage |            | Obtained |

|                                |                      |                  |                          | Req.'d  |            |          |

| Prim. Batt.                    | -                    | 2880             | 90                       | No      | No         | Yes      |

| Sec. Batt.                     | _                    | 1080             | 34                       | -       | No         | Yes      |

| Micro-Fuel Cell                | -                    | 3500             | 110                      | Maybe   | Maybe      | No       |

| Heat Engine                    | -                    | 3346             | 106                      | Yes     | Yes        | No       |

| Radioactive( <sup>63</sup> Ni) | 0.52                 | 1640             | 0.52                     | Yes     | Yes        | No       |

| Solar (out)                    | $15k^*$              | -                | -                        | Usually | Maybe      | Yes      |

| Solar (in)                     | 10*                  | -                | -                        | Usually | Maybe      | Yes      |

| Temp.                          | 40**                 | -                | -                        | Usually | Maybe      | Soon     |

| Human                          | 330                  | -                | -                        | Yes     | Yes        | No       |

| Air Flow                       | 380***               | -                | -                        | Yes     | Yes        | No       |

| Vibration                      | 200                  | -                | -                        | Yes     | Yes        | Yes*     |

Comparison of different power sources for sensor networks, (modified from [23]).

and buildings have modes of oscillation which occur at higher frequencies, the low frequency vibrations are typically ones with larger amplitudes and therefore larger forces on the power conversion device which then result in larger harvestable output powers. However, the factors which are a severe bottleneck with piezoelectric devices in these systems are an advantage for systems which utilize MSMAs. With MSMA devices, the MEC is performed by sensing a magnetic flux change within the material and then converting the magnetic flux change into an electrical signal via a pick-up coil. The methods in which this magnetic change occurs is typically through martensitic variant reorientation or martensite phase transformation of the MSMA device [22, 26, 27].

Previous work on energy harvesting using MSMAs has been performed utilizing NiMnGa MSMA single crystalline samples [22]. MSMAs can convert mechanical work, such as from mechanical vibrations, first into a magnetic induction change in the material in the presence of a constant bias magnetic field, which can then be converted into electrical energy through pick-up coils. There are two major mechanicallyinduced microstructural changes that manifest themselves as large magnetization changes in MSMAs. The first one is the stress/strain-induced rotation of martensite variants (the microstructural change) within the material [22, 28, 29]. Magnetic domains are strongly coupled with martensite variants in the material exhibiting this mechanism such that martensite variant rotation leads to magnetic domain rotation, and thus magnetic flux change. NiMnGa MSMAs utilize this mechanism to harvest energy from mechanical vibrations or otherwise waste mechanical work [22]. The level of current which can be generated in the pick-up coils, and thus the amount of power which may be delivered to a load, depends on the magnetic induction change upon martensite variant rotation, which is measured to be on the order of 0.15 to 0.2 Tesla in near stoichiometric  $Ni_2MnGa$  MSMAs [22, 29]. We have recently demonstrated in these materials that the power output levels on the order of a Watt are within reach, upon the conversion of relatively large amplitude mechanical vibrations under 200Hz frequency [22].

The second mechanism of mechanically-induced microstructural and magnetic changes in MSMAs is the stress-induced martensitic phase transformation from a ferromagnetic to a para/antiferro-magnetic phase [26, 27], which is fully reversible upon unloading the stress. This mechanism can cause a large magnetic flux change

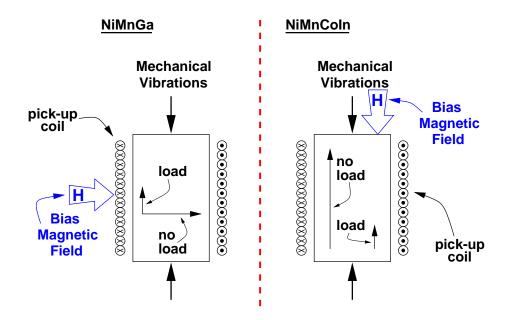

Fig. 2.: Different methods of flux change in NiMnGa and NiMnCoIn MSMAs upon mechanical loading/unloading in the presence of a bias magnetic field.

in the presence of a bias field due to large differences in the saturation magnetizations of the transforming phases. Typical MSMAs exhibiting this large change are NiMnCo(In,Sn,Sb) alloys. They are also called meta-magnetic SMAs because of the simultaneous magnetic and structural phase transitions [27, 30–36]. As compared to the magnetic induction change associated with the mechanically-induced martensite variant rotation, the magnetic induction change during the stress-induced martensitic transformation in these materials can be multiple times higher, depending on the bias field levels [27]. Thus, using meta-magnetic SMAs as energy harvesting materials is more beneficial in terms of power output levels for a given vibrational loading. In addition, the magnetization rotations and the nature of the flux change in these two mechanisms are notably different, as shown in Fig. 2 for a NiMnGa and a NiMnCoIn MSMAs. In NiMnGa, the magnetization direction usually changes from horizontal to vertical in the figure upon loading and vice versa upon unloading (depending on the single crystal orientation), but this configuration is the best one per [22, 28]. In meta-magnetic SMAs such as NiMnCoIn alloys, the magnetic flux can be aligned perpendicular to the pick-up coil at all times and the magnetization can change from almost zero to maximum (i.e., saturation magnetization) upon loading/unloading. This implies in NiMnCoIn that the maximum flux change can be sensed by the coil and then generate the maximum output voltage. Moreover, since magnetic domains are strongly coupled with microstructure in NiMnGa, it is necessary to use very expensive single crystals. However, in meta-magnetic SMAs, because saturation magnetization levels of the transforming phases dictate the magnetic induction change upon structural phase transformation, relatively inexpensive polycrystals can be used. In the present study, we, thus, implement a NiMnCoIn meta-magnetic SMA as a potential energy harvesting material to convert the mechanical vibrations into a usable electrical signal.

In both MSMA MEC systems, the equivalent source impedance is better suited for low frequency applications as it may typically be modeled by a series combination of a resistor and inductor as opposed to a series resistor and capacitor as is the case in piezoelectric devices. The values of these components are dependent on geometry and choice of material used to extract the electrical signal but may be practically limited to less than 200 $\Omega$  and 20*nH*. While compared to values associated with integrated circuits these values are large, the implementation produces a fairly small physical device (approximately the size of a sugar cube [ $\approx 1 \text{cm}^3$ ]).

#### B. Electromagnetism in the MSMA

Assuming the applied strain/stress/force/etc., is sinusoidal in nature, it is safe to say the magnetic field will have an equation represented by

$$B = B_0 r \sin\left(\omega t\right). \tag{2.2}$$

The value of  $B_0$  is half the reversible magnetic flux density change, r is the volume fraction of the material undergoing reorientation and is defined as  $\epsilon/\epsilon_{max}$ ,  $\epsilon$  is the applied strain range,  $\epsilon_{max}$  is the maximum reorientation strain, and  $\omega = 2\pi f$  where fis the frequency of excitation of the material. The values of  $\epsilon$  and  $\epsilon_{max}$  are important values as they determine many of the characteristics of the alloy and define a range of energy which may be harvested.

Since the mechanical changes induce a magnetic flux change within the material, a coil is needed to capture the electric field change (as described by Faraday's law of electromagnetic induction). More discussion on the design of the coil, as well as the coil's electrical parameters, will be provided in the following section. The induced voltage may be determined from Faraday's equation

$$V = N \frac{\mathrm{d}\phi}{\mathrm{d}t} = N A \frac{\mathrm{d}B}{\mathrm{d}t}.$$

(2.3)

In (2.3) the value of N is the number turns of the coil,  $\phi$  is the magnetic flux within the material, A is the cross sectional area of the magnetic field and B is the induced magnetic field within the material.

Solving for the derivative and the maximum of (2.2) and then substitution of the

simplified form of (2.2) into (2.3) results in

$$\frac{\mathrm{d}B}{\mathrm{d}t} = \frac{\mathrm{d}B_0 r \sin(\omega t)}{\mathrm{d}t}$$

$$= \omega B_0 r \cos(\omega t)$$

$$\frac{\mathrm{d}B}{\mathrm{d}t}\Big|_{\mathrm{max}} = \omega B_0 r$$

$$V_{rms} = \frac{NA\omega B_0 r}{\sqrt{2}}.$$

(2.4)

The value shown in (2.4) is the maximum obtainable RMS voltage from the MSMA device. While there are many non-idealities which may be considered, this result provides an intuitive prediction which relates many known and/or quantifiable parameters to the available output voltage. If the value of the peak induced voltage is desired then the value in (2.4) should be multiplied by  $\sqrt{2}$  to obtain the wanted result.

#### 1. Coil

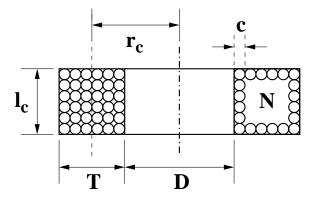

To determine the available power from the flux change of the MSMA material it is necessary to first relate the mechanical parameters to electrical parameters for further optimization. Assuming the coil appears as in fig. 3, we must begin with the standard equation for the resistance of a material.

$$R = \rho \frac{L}{A} \tag{2.5}$$

In (2.5), R is the resistance of the coil material used (copper (Cu) in this case),  $\rho$  is the resistivity of the coil material in  $\Omega$ ·m L is the length of the material in m and A is the cross-sectional area in  $m^2$ . In a practical situation, and for numerous

turns of the coil, it may be difficult to know the exact number of turns obtained

Fig. 3.: Side cross-sectional view of the pick-up coil used with the MSMA material.

by the pickup coil. However, the number of turns may be estimated from readily available physical parameters which can be measured and/or selected when choosing the wire. Figure 3 shows the physical parameters of the coil which may be measured or selected. The parameters are:  $l_c$ , the vertical height of the coil; c, the diameter of the copper wire;  $r_c$ , the distance from the center of the coil to the center of the winding; D, the inner diameter of the coil (this is where the MSMA material fits); T, the thickness of the winding; and N, the number of turns. Since, for large N, actually counting the number of turns may be difficult and tedious, it may be better to determine an approximate value for these based on measured parameters  $(l_c, c \text{ and } c)$ T). From (2.5), we know that  $\rho$  is a physical parameter of copper and is equal to  $1/6 \times 10^{-7} \Omega$ ·m. Another way to represent this is by representing this same information as a conductivity ( $\sigma$ ) instead of with the wire's resistivity (conductivity is the inverse of resistivity). The value of A in (2.5) may be determined by assuming the copper wire is uniform in diameter and it is a perfect circle giving  $A = \pi c^2/4$ . Finally, the length of the wire used to wrap around the coil may be estimated by taking a few assumptions: 1) the wire does not extend far from the material itself (i.e., T is small); 2) the coil is wrapped in such a way that there is almost no space between the coil and the MSMA device (i.e., the width of the MSMA is approximately equal to D, the inner diameter of the coil). Knowing this, we may say that the length of the wire, L in (2.5), is equal to  $\pi ND$ . Now, the resistance may be written as

$$R_{coil} = \frac{\pi ND}{\sigma \pi \frac{c^2}{4}} = \frac{4ND}{\sigma c^2}.$$

(2.6)

At this point, the majority of the parameters in (2.6) may be measured and/or selected during the initial design of the coil. However, knowing the actual value of Nmay be challenging for values greater than a few hundred. Therefore, if we assume that there is no space between the coil turns and that they are all aligned in perfect rows and columns, it is possible to estimate the number of turns. The number of rows may may be estimated by  $l_c/c$  and the number of columns may be estimated by T/c. Another way to view this is to assume the Cu wire is a square with side length of c. The overall rectangular area of one side of the cross-section of the coil is given by the product of the length and the width,  $l_c$  and T. The number of turns may be determined by dividing the overall cross-section area,  $l_cT$ , by the cross-sectional area of the wire,  $c^2$ . The total number of turns is then estimated as

$$N \approx \frac{l_c T}{c^2}.$$

(2.7)

Substituting (2.7) into (2.6) provides us with our desired result as

$$R_{coil} \approx \frac{4l_c TD}{\sigma c^4}.$$

(2.8)

Although the frequencies of excitation in mechanical systems are relatively low (when compared to radio frequency (RF) integrated circuits (ICs)), the inductance of the coil may still play an issue in the amount of power which can be extracted from the MEC. Therefore, it is necessary to determine this value based on known physical quantities of the pick-up coil. In [37] and [38] physical parameters of inductors are used to estimate inductance. The author in these papers takes into great account the different parameters and how they relate to each other and how they will change based on physical dimensions. From these papers it is therefore reasonable to say that the coil inductance is approximately

$$L_{coil} = \frac{\mu \pi N^2 r_c^2}{l_c + 0.9 r_c}, \text{ for } l_c > \frac{2}{3} r_c$$

(2.9)

where  $\mu$  is the permeability of the coil material; N,  $l_c$  and  $r_c$  are the same as previously described. By substituting in our previous approximation for N and taking into account  $r_c = T/2 + D/2$  results in

$$L_{coil} = \frac{\mu \pi \left[ l_c T \left( D + T \right) \right]^2}{4c^4 \left[ l_c + 0.45 \left( D + T \right) \right]}.$$

(2.10)

Depending on the volume of the MSMA, the inner dimensions and height of the coil are fixed since the MSMA must fit in the center of the coil and, to maintain as uniform a magnetic field as possible, the coil should not be taller than the MSMA sample [37,38]. Since the equivalent impedance of the coil determines, in conjunction with the equivalent input impedance of the rectifier, the amount of power which may be transferred from the energy harvester to the AC-DC converter the pick-up coil design is crucial.

Assuming the magnetic flux change may be sensed by the coil without any loss, and the time varying magnetic field within the MSMA is  $B = B_0 r \sin(\omega t)$  the output voltage of the coil with no load may be expressed as [22]

$$\hat{V}_{coil} = NA_c \frac{\mathrm{d}B}{\mathrm{d}t} \approx \frac{\pi^2 l_c T D^2 B_0 r f}{2c^2}.$$

(2.11)

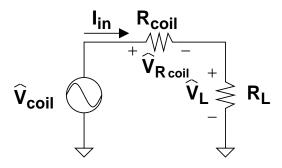

With the approximated output voltage from the coil known, and assuming the rectifier stage has an input resistance of  $R_L$ , it is possible to predict the amount of power delivered to and voltage across  $R_L$  as well as determine the overall efficiency

Fig. 4.: Equivalent electrical model of MSMA harvested voltage and coil resistance  $R_{coil}$  with rectifier input resistance  $R_L$ .

$\eta$  of the electrical power delivery. Although the efficiency of converting the mechanical vibration into a change in magnetization and thus a voltage is important, this efficiency will be assumed ideal (i.e., 1) and the only efficiency in question will be the conversion of the power delivered from the coil to the input of the rectifier. The resistance of the coil was found in (2.8) and therefore, using voltage division on the equivalent model shown in Fig. 4, the peak load voltage  $\hat{V}_L$  may be given as

$$\hat{V}_{L} = \hat{V}_{coil} \frac{R_{L}/R_{coil}}{1 + R_{L}/R_{coil}}.$$

(2.12)

In energy harvesting systems, the amount of energy scavenged is typically low and therefore any losses within the system impose limitations on the overall system performance. Therefore, it is necessary to achieve a high power conversion efficiency  $\eta$  so as to not waste the harvested energy while obtaining the required amount of energy for the system. In addition to  $\eta$ , it is also beneficial to study the power delivered  $P_{load}$  to the load  $R_{load}$  and how this power level effects the peak AC voltage (V<sub>pk</sub>) across  $R_L$ . For maximum power transfer the value of  $R_L$  should be set to  $R_{coil}$  which is defined by the maximum power transfer theorem. Calling  $P_{max}$  the power delivered to  $R_L$  when it is equivalent to  $R_{coil}$ , the ratio of  $P_{load}/P_{max}$  may now be taken into account for the analysis. Therefore, the electrical efficiency  $\eta$  may be defined as the power delivered to the load  $R_L$  divided by the power put into the system. This power,  $P_{in}$ , is equal to the power dissipated on  $R_{coil}$  plus the power delivered to  $R_L$ .

$$\eta = \frac{P_{load}}{P_{in}} = \frac{\hat{V}_L I_{in}}{\hat{V}_L I_{in} + \hat{V}_{R_{coil}} I_{in}} = \frac{R_L / R_{coil}}{1 + R_L / R_{coil}}$$

(2.13)

$$\frac{P_{load}}{P_{max}} = \frac{4R_L/R_{coil}}{\left(1 + R_L/R_{coil}\right)^2} \tag{2.14}$$

One important observation about  $\eta$  is that it is equal to the ratio  $\hat{V}_L/\hat{V}_{coil}$ . This means the larger the efficiency, the larger the peak voltage which appears across  $R_L$ . This is an important observation and will be revisited later when discussing the AC-DC conversion.

Fig. 5.: Plots of (2.13),  $\eta$ , and (2.14),  $P_L/P_{max}$ , versus ratio of load resistance  $R_L$ and coil resistance  $R_{coil}$  to determine optimum value of RM input resistance and coil resistance to obtain a high efficiency and a reasonable power delivered to the RM.

Since the proposed system does not contain any external batteries and is intended to operate solely on the harvested energy from the MSMA, a method of converting the AC signal from the coil into a DC level is necessary. The value of  $R_L$  is a model for the input resistance of a passive rectifier-multiplier (RM) architecture. A single stage RM implemented with diodes and capacitors is shown in Fig. 1 as the stage to which the coil connects. As will be discussed in the following section, obtaining the largest voltage as efficiently as possible while simultaneously producing adequate power for the remaining circuitry is critical. Therefore, rather than being concerned with maximum power, the overall efficiency may be a more critical parameter. To gain an insight,  $\eta$  and the ratio  $P_{load}/P_{max}$  are plotted in Fig. 5 as a function of  $R_L/R_{coil}$ . It can be shown that these two functions intersect when  $R_L/R_{coil} = 3$  which leads to  $\eta = 0.75$  and  $P_{load}/P_{max} = 0.75$ . Conversely, if the system were designed for maximum power, i.e.,  $R_L/R_{coil} = 1$ , leads to  $\eta = 0.5$  and  $P_{load}/P_{max} = 1$ .