# EVALUATION OF CACHE INCLUSION POLICIES IN CACHE MANAGEMENT

## A Thesis

by

## LUNA BACKES DRAULT

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE

Chair of Committee, Daniel Jiménez

Committee Members, Paul Gratz

Dilma Da Silva

Head of Department, Dilma Da Silva

August 2017

Major Subject: Computer Engineering

Copyright 2017 Luna Backes Drault

#### ABSTRACT

Processor speed has been increasing at a higher rate than the speed of memories over the last years. Caches were designed to mitigate this gap and, ever since, several cache management techniques have been designed to further improve performance.

Most techniques have been designed and evaluated on non-inclusive caches even though many modern processors implement either inclusive or exclusive policies. Exclusive caches benefit from a larger effective capacity, so they might become more popular when the number of cores per last-level cache increases.

This thesis aims to demonstrate that the best cache management techniques for exclusive caches do not necessarily have to be the same as for non-inclusive or inclusive caches. To assess this statement we evaluated several cache management techniques with different inclusion policies, number of cores and cache sizes.

We found that the configurations for inclusive and non-inclusive policies usually performed similarly, but for exclusive caches the best configurations were indeed different. Prefetchers impacted performance more than replacement policies, and determined which configurations were the best ones. Also, exclusive caches showed a higher speedup on multi-core.

The least recently used (LRU) replacement policy is among the best policies for any prefetcher combination in exclusive caches but is the one used as a baseline in most cache replacement policy research. Therefore, we conclude that the results in this thesis motivate further research on prefetchers and replacement policies targeted to exclusive caches.

# DEDICATION

To Alex, for his love, patience and unconditional support.

#### ACKNOWLEDGMENTS

First of all, I want to thank my advisor, Daniel Jiménez, for giving me the chance of joining his lab and believing in me to be his first master's student. I appreciate the support and freedom he gave me to explore a topic I was very interested in. I also want to thank the committee members Paul V. Gratz and Dilma Da Silva for being available on their busy schedules and asking me good questions and giving feedback on this work.

I also want to thank many people that helped me directly and indirectly such as labmates, friends and family. Elvira, who I met a few years ago in Italy and I ended up in her group across the world. It was nice having a known and friendly face in the university. She made me feel welcomed and helped me during this two years, we will miss you in the lab. Sangam for her understanding and help during stressful days. And to all my other labmates for their feedback and talks, Ivan, Elba and Samira.

I also thank my previous advisor, Filippo Mantovani, for still giving me advice despite the distance and time difference. Including musical advice to help me write the last part of this thesis.

To my parents, Maria Teresa and Paulo, for supporting my decision to move in to a different country and being able to visit and attend the defense of this thesis, together with Alejandro and Emilia. I really appreciated their support and the delicious food they brought. And to all the rest of my family that are scattered around the world but still care about and support me. My 24 cousins: Ceci, Laura, Maria Emilia, July, Josefina, Tomy, Martin, Guada, Fran, Majo, Juan, Edu, Luciana, Nacho, Santy, Sebi, Juampy, Lucas, Agustín, Betty, Katia, Yaundé, Kayawe, Kitwe, and their wives/husbands and children; for cheering me up from the distance and

caring about me. My 16 aunts and uncles: *Mary, Lucy*, Titi, Cecilia, Miguel, Monica, Eduardo, Alicia, Emilio, José Maria, Rosi, Tito, Marcela, Ghi, Julius and Denise; for their love. My grandmother Lilia, for always sharing her knowledge and wisdom from her 101 years. My grandfathers and my vó Erica, that live in my memory. Most of them are far away but I remember them every day.

To many friends in different stages of my life, such as Alba, Laura, Ainoa, Francesc, Aleix, Khaoula, Rio, Jing, Dani, Lis, Jane, Mathi and Andrea. To follow Alba's latest success in SoundSix slightly delayed the progress of this thesis but surely made it more special.

Most special thanks to Alex, for surviving through two of my degrees and agreed to the third one. This would not have been possible without his love, support, cheers and confidence in me. The third time's the charm.

#### CONTRIBUTORS AND FUNDING SOURCES

#### Contributors

This work was supported by a thesis committee consisting of Professor Daniel A. Jiménez and Professor Dilma Da Silva of the Department of Computer Science and Engineering and Professor Paul V. Gratz of the Department of Electrical and Computer Engineering.

The traces and the simulator were provided by Jinchun Kim of the Department of Electrical and Computer Engineering. He also contributed on this thesis by upgrading the simulator and adding more features to experiment.

All other work conducted for the thesis was completed by the student independently.

# **Funding Sources**

This research was supported in part by a grant from the National Science Foundation, NSF CCF-1216604/1332598.

Portions of this research were conducted with the advanced computing resources provided by Texas A&M High Performance Research Computing.

## NOMENCLATURE

BRRIP bimodal RRIP

CPU central processing unit

CSV comma separated value

DAAMPM DRAM-aware access map pattern matching

DRAM dynamic RAM

DRRIP dynamic RRIP

EAF evicted address filter

eDRAM embedded DRAM

FP frequency priority

GIPPR genetic insertion and promotion for pseudo-LRU

replacement

HP hit promotion

IPC instructions per cycle

IPV insertion and promotion vector

KPC kill the program counter

KPC-P KPC prefetching algorithm

KPC-R KPC replacement algorithm

LLC last-level cache

LRU least recently used

MDPP minimal disturbance placement and promotion

MLP memory-level parallelism

MPKI misses per kiloinstruction

MRU most recently used

MSHR miss status holding registers

OS operating system

PC program counter

PLRU pseudo least recently used

RAM random-access memory

RRIP re-reference interval prediction

RRPV re-reference prediction value

SDBP sampling-based dead block prediction

SHiP signature-based hit predictor

SMP symmetric multiprocessor

SPEC standard performance evaluation corporation

SRAM static RAM

SRRIP static RRIP

SSH secure shell

TLB translation lookaside buffer

# TABLE OF CONTENTS

|                                                                                                                                                                                                        | Page                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| ABSTRACT                                                                                                                                                                                               | . ii                       |

| DEDICATION                                                                                                                                                                                             | . iii                      |

| ACKNOWLEDGMENTS                                                                                                                                                                                        | . iv                       |

| CONTRIBUTORS AND FUNDING SOURCES                                                                                                                                                                       | . vi                       |

| NOMENCLATURE                                                                                                                                                                                           | . vii                      |

| TABLE OF CONTENTS                                                                                                                                                                                      | . X                        |

| LIST OF FIGURES                                                                                                                                                                                        | . xiv                      |

| LIST OF TABLES                                                                                                                                                                                         | . xvi                      |

| 1. INTRODUCTION                                                                                                                                                                                        | . 1                        |

| 1.1 My Project          1.1.1 Objectives          1.1.2 Contributions          1.2 Document Structure                                                                                                  | . 2<br>. 3                 |

| 2. BACKGROUND                                                                                                                                                                                          | . 4                        |

| 2.1       Memory Hierarchy          2.1.1       Miss Types          2.1.2       Load Flow          2.1.3       Write Policies          2.1.4       Cache Coherence          2.1.4.1       MSI Protocol | . 8<br>. 9<br>. 11<br>. 12 |

| 2.1.4.2 MSI-Like Protocols                                                                                                                                                                             | . 15<br>. 16<br>. 17       |

| 2.2.3 Non-Inclusive                                                                                                                                                                                    |                            |

|    | 2.3            | Replac  | cement Policies                         | 23 |  |  |

|----|----------------|---------|-----------------------------------------|----|--|--|

|    |                | 2.3.1   | LRU                                     | 25 |  |  |

|    | 2.4            | Prefete | chers                                   | 26 |  |  |

|    |                | 2.4.1   | Next-Line                               | 28 |  |  |

|    |                | 2.4.2   | Instruction Pointer-Based Stride        | 28 |  |  |

|    |                | 2.4.3   | Best-Offset                             | 29 |  |  |

|    |                | 2.4.4   | DRAM-Aware Access Map Pattern Matching  | 30 |  |  |

|    |                | 2.4.5   | KPC                                     | 31 |  |  |

| 3. | REL            | LATED   | WORK                                    | 33 |  |  |

|    | 3.1            | Re-Re   | ference Interval Prediction             | 33 |  |  |

|    | 3.2            | Sampl   | ing Dead Block Prediction               | 35 |  |  |

|    | 3.3            |         | cure-Based Hit Predictor                | 37 |  |  |

|    | 3.4            |         | nal Disturbance Placement and Promotion | 37 |  |  |

|    | 3.5            |         | ed Address Filter                       | 39 |  |  |

|    | 3.6            |         | otron Learning for Reuse Prediction     | 40 |  |  |

|    | 3.7            |         | eye                                     | 41 |  |  |

|    | 3.8            |         | s and Insertion                         | 42 |  |  |

|    | 3.9            |         | chy-Awareness and Bypass                | 43 |  |  |

| 4. | ME             | ГНОДС   | DLOGY                                   | 47 |  |  |

|    | 11             | D       | : 1 Ct                                  | 17 |  |  |

|    | 4.1            |         | imental Setup                           | 47 |  |  |

|    |                | 4.1.1   | Host Machine                            | 47 |  |  |

|    |                | 4.1.2   | Benchmarks                              | 47 |  |  |

|    | 4.0            | 4.1.3   | Simulator                               | 50 |  |  |

|    | 4.2            |         |                                         | 52 |  |  |

|    |                | 4.2.1   | Configurations                          | 52 |  |  |

|    |                | 4.2.2   | Performance Measurement                 | 53 |  |  |

| 5. | IMPLEMENTATION |         |                                         |    |  |  |

|    | 5.1            | Chamj   | pSim Code                               | 55 |  |  |

|    |                | 5.1.1   | Cache Operation                         | 55 |  |  |

|    |                | 5.1.2   | Non-Inclusive Implementation            | 56 |  |  |

|    |                | 5.1.3   | Statistics                              | 58 |  |  |

|    | 5.2            | Modify  | ying ChampSim                           | 58 |  |  |

|    |                | 5.2.1   | Inclusive Implementation                | 58 |  |  |

|    |                | 5.2.2   | Exclusive Implementation                | 62 |  |  |

|    | 5.3            | Scripts | S                                       | 65 |  |  |

|    |                | 5.3.1   | Execute                                 | 65 |  |  |

|    |                |         | Plots                                   | 67 |  |  |

| 6. | RES        | ULTS                            | 9 |

|----|------------|---------------------------------|---|

|    | 6.1        | Single-Core Results             |   |

|    |            | 6.1.1 Inclusion Results         |   |

|    |            | 6.1.2 Prefetcher Impact         |   |

|    | <i>c</i> o | 6.1.3 Replacement Policy Impact |   |

|    | 6.2        | Multi-Core Results              |   |

|    |            | 6.2.1 Inclusion Results         |   |

|    |            | 6.2.2 Prefetcher Impact         |   |

|    | c o        | 6.2.3 Replacement Policy Impact |   |

|    | 6.3        | Size Sensitivity                |   |

|    |            | 6.3.1 Inclusion Results         |   |

|    |            | 6.3.2 Prefetcher Impact         |   |

|    | C 1        | 6.3.3 Replacement Policy Impact |   |

|    | 6.4        | Discussion                      | J |

| 7. | SUM        | MARY                            | 1 |

|    | 7.1        | Conclusions                     | 1 |

|    | 7.2        | Future Work                     |   |

| RE | EFER.      | ENCES                           | 5 |

| ΑF | PEN        | DIX A. SINGLE-CORE RESULTS      | 3 |

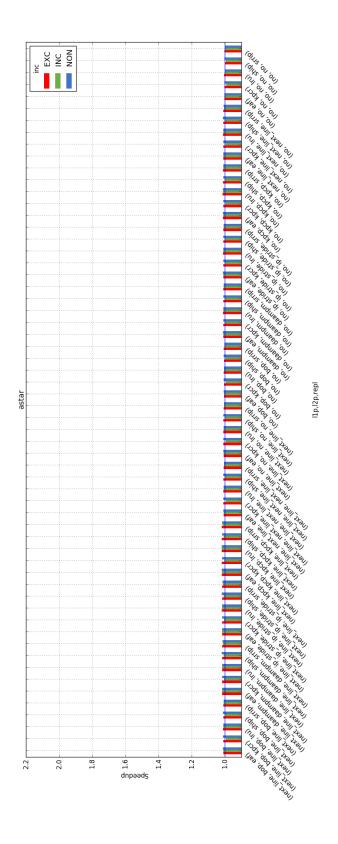

|    | A.1        | Astar                           | 4 |

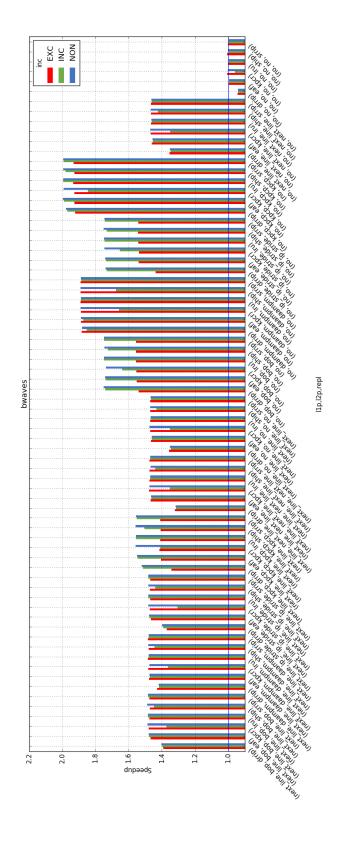

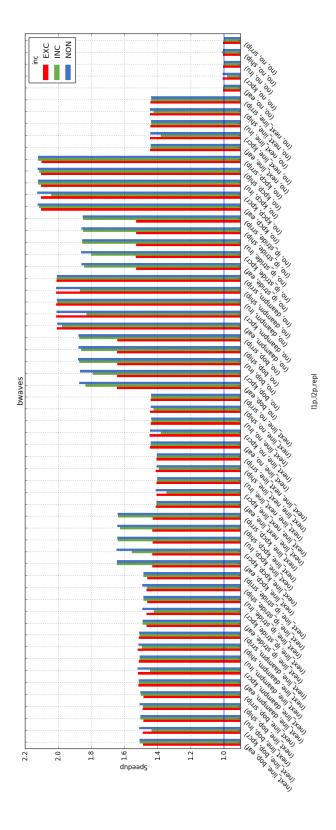

|    | A.2        | Bwaves                          | 5 |

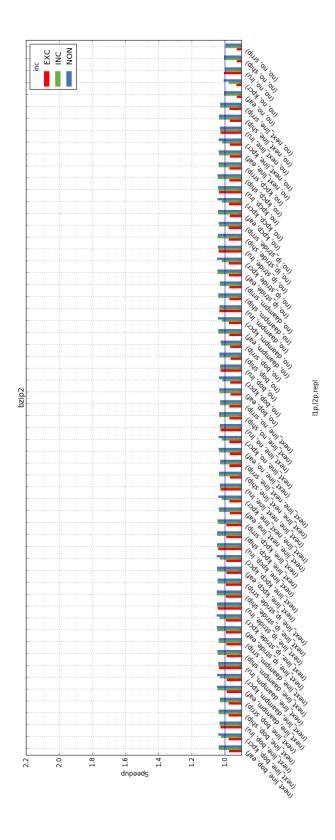

|    | A.3        | Bzip2                           | 6 |

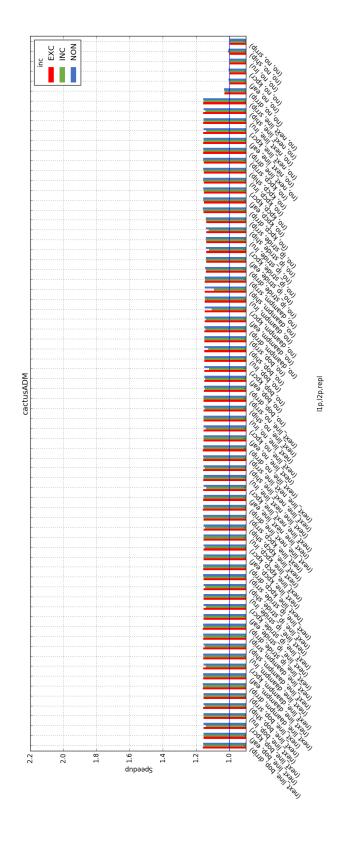

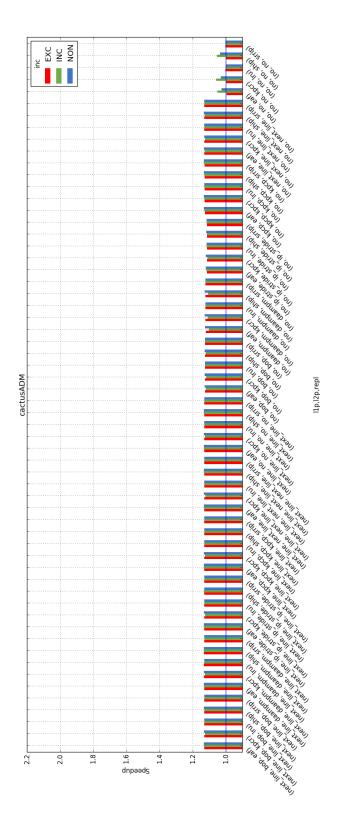

|    | A.4        | CactusADM                       |   |

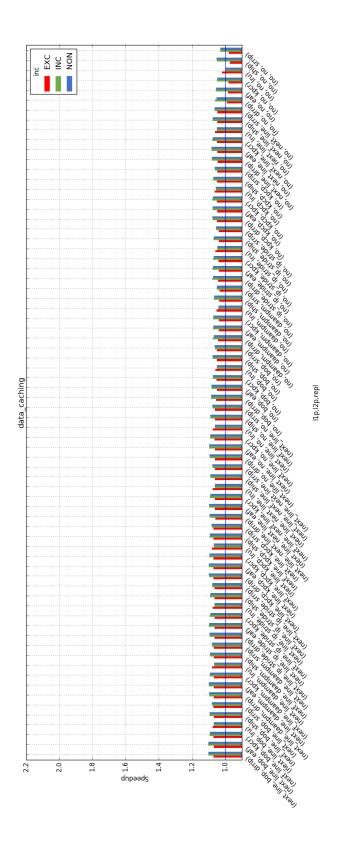

|    | A.5        | Data Caching                    | 8 |

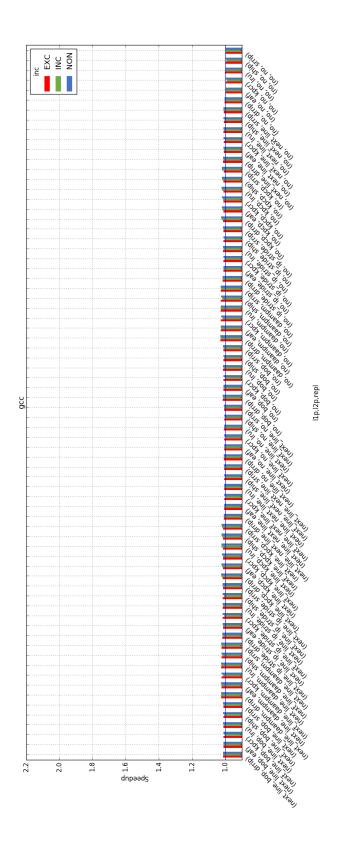

|    | A.6        | Gcc                             | 9 |

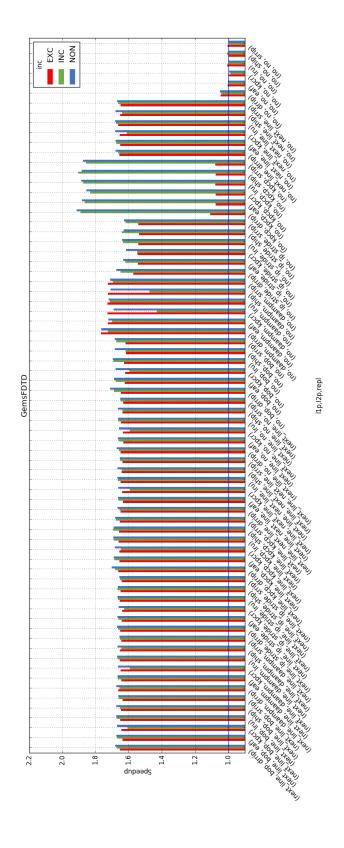

|    | A.7        | GemsFDTD                        | 0 |

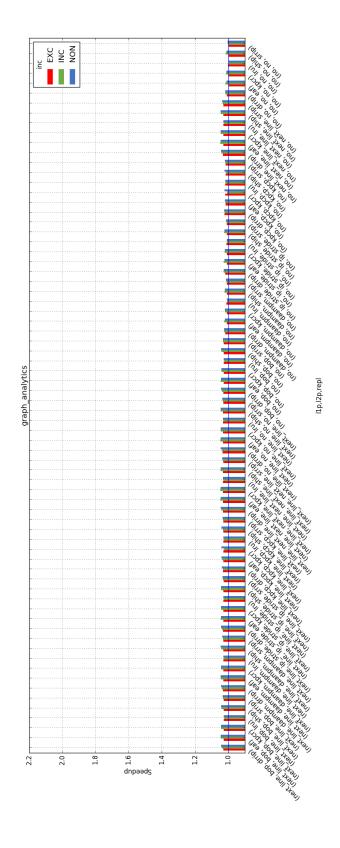

|    | A.8        | Graph Analytics                 | 1 |

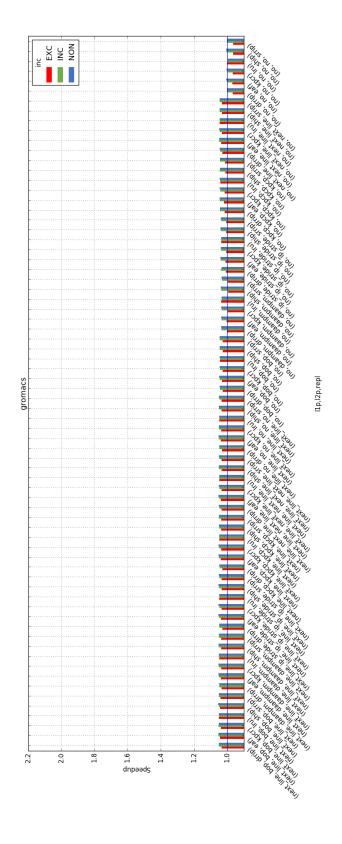

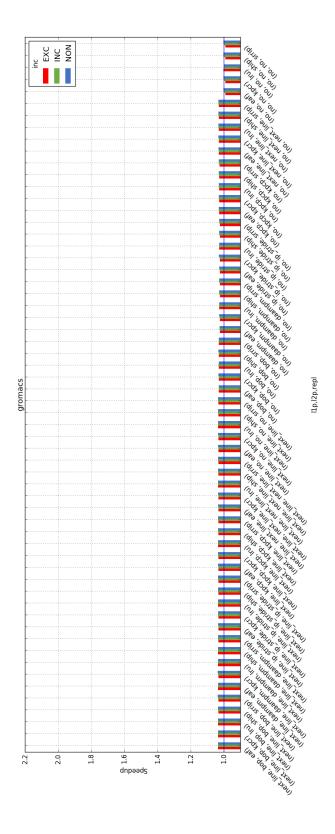

|    | A.9        | Gromacs                         |   |

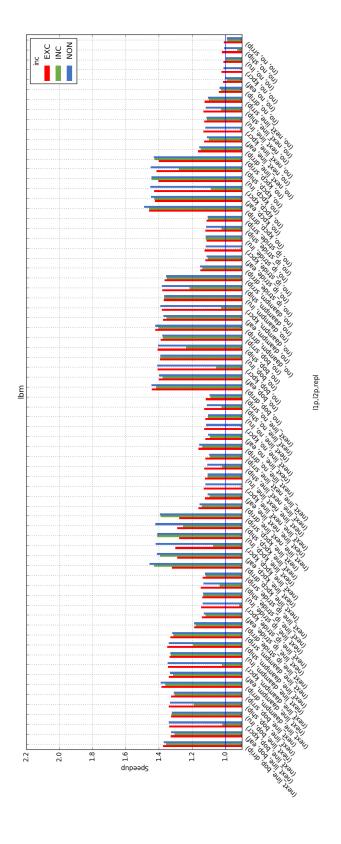

|    | A.10       | Lbm                             | 3 |

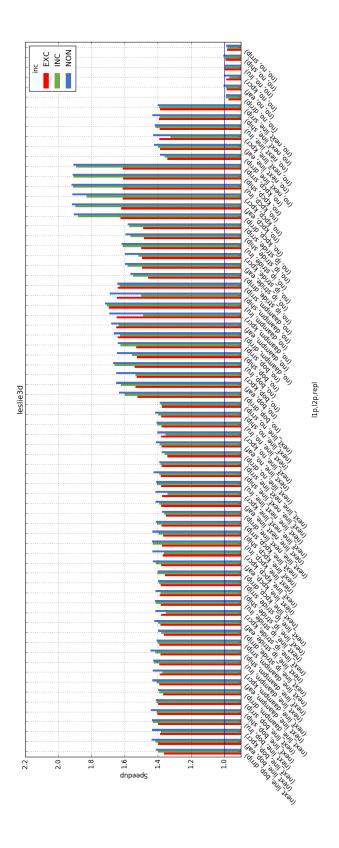

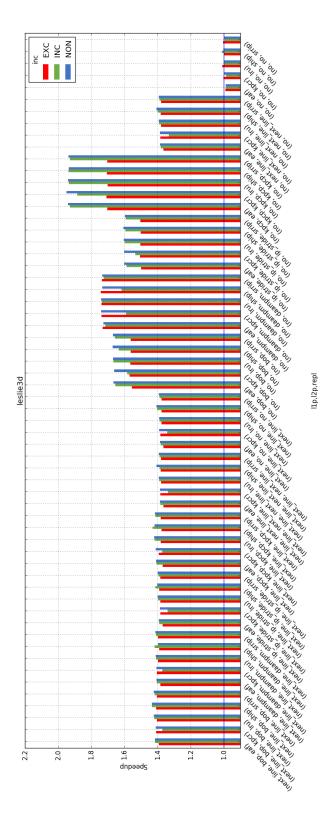

|    | A.11       | Leslie3d                        | 4 |

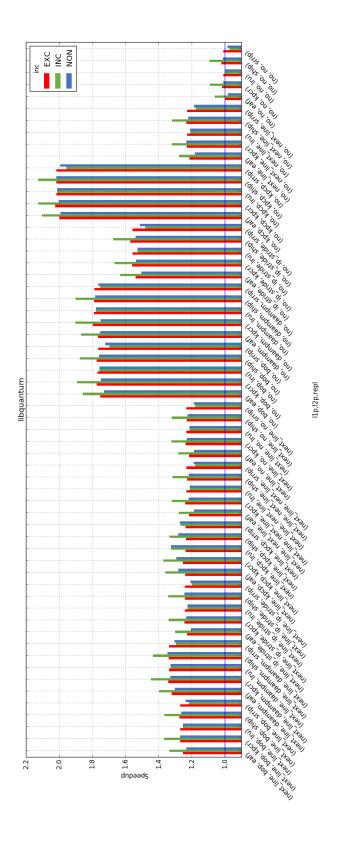

|    |            | Libquantum                      | 5 |

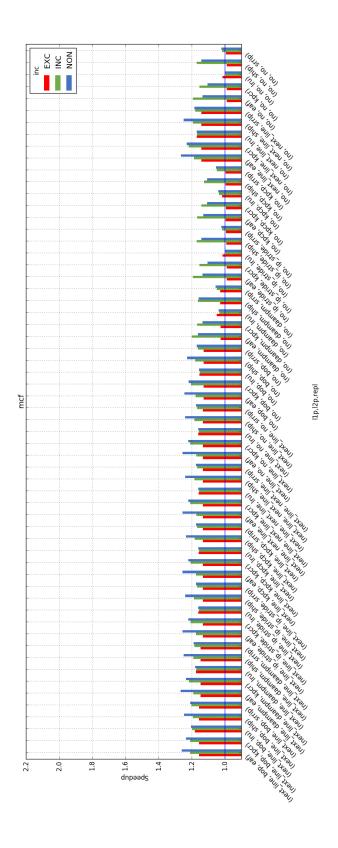

|    |            | Mcf                             | 6 |

|    | A.14       |                                 | 7 |

|    | A.15       | Mlpack Cf                       |   |

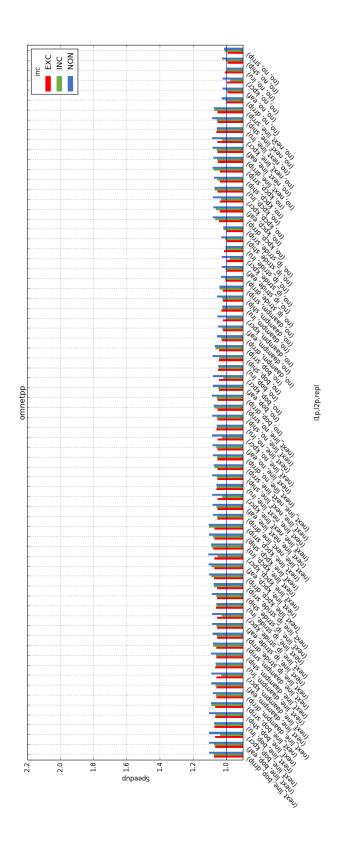

|    |            | Omnetpp                         |   |

|    |            | Sat Solver                      | _ |

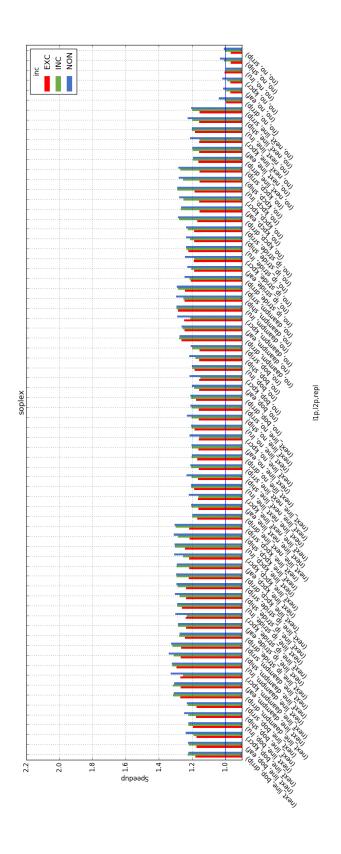

|    |            | Soplex                          |   |

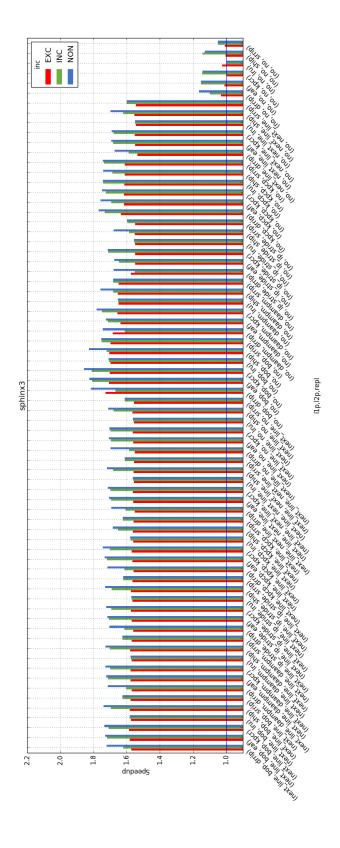

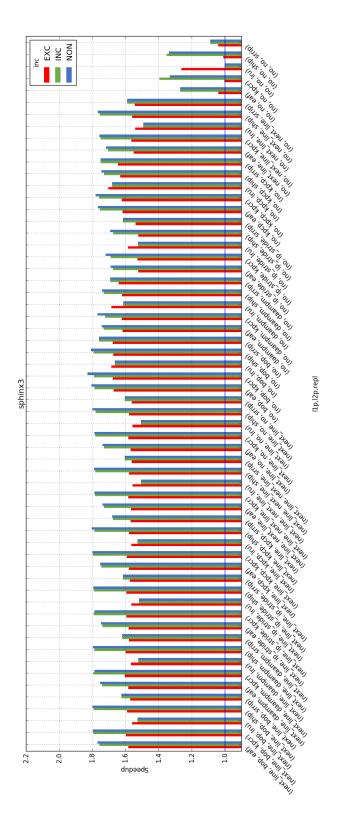

|    |            | Sphinx3                         |   |

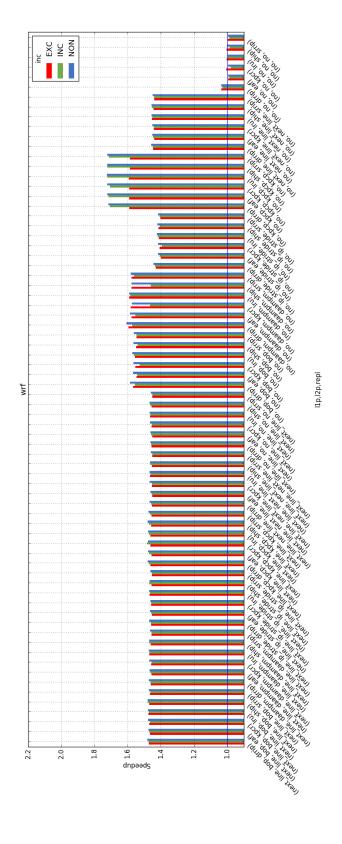

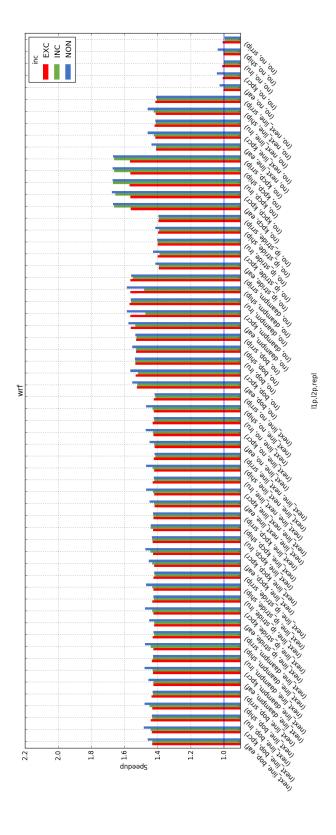

| A.20  | Wrf                                             |

|-------|-------------------------------------------------|

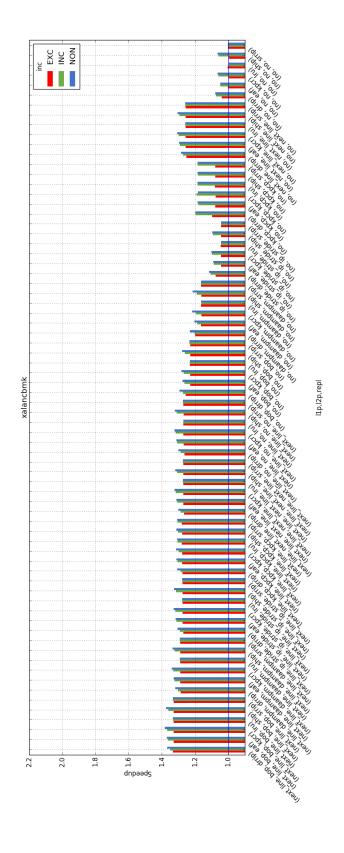

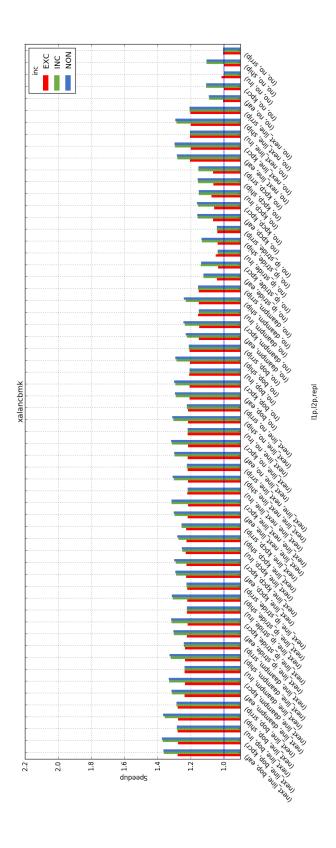

| A.21  | Xalancbmk                                       |

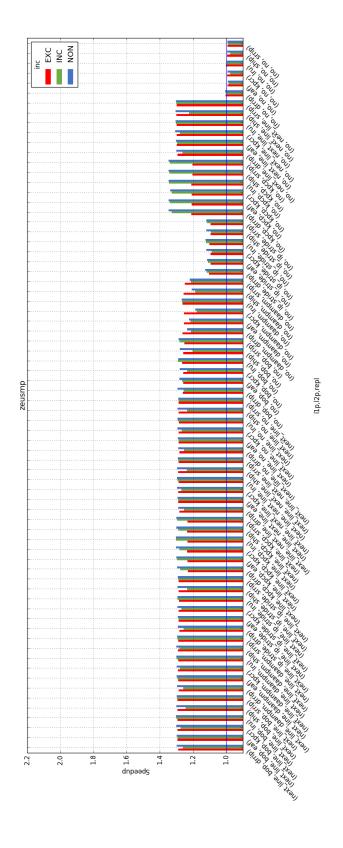

| A.22  | Zeusmp                                          |

| APPEN | DIX B. MULTI-CORE RESULTS                       |

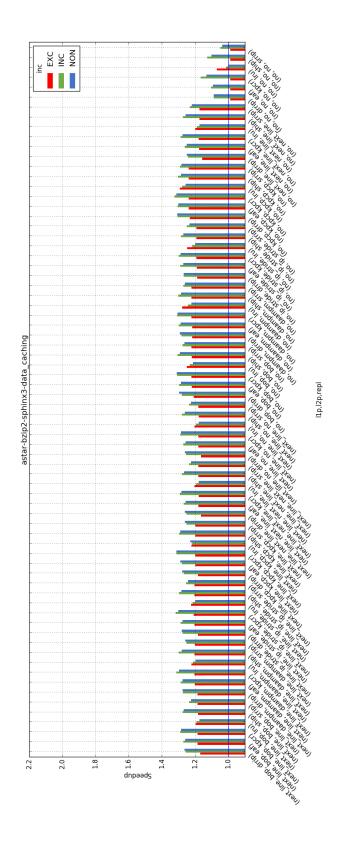

| B.1   | Astar-Bzip2-Sphinx3-Data_Caching                |

| B.2   | Astar-Bzip2-Sphinx3-Data_Caching                |

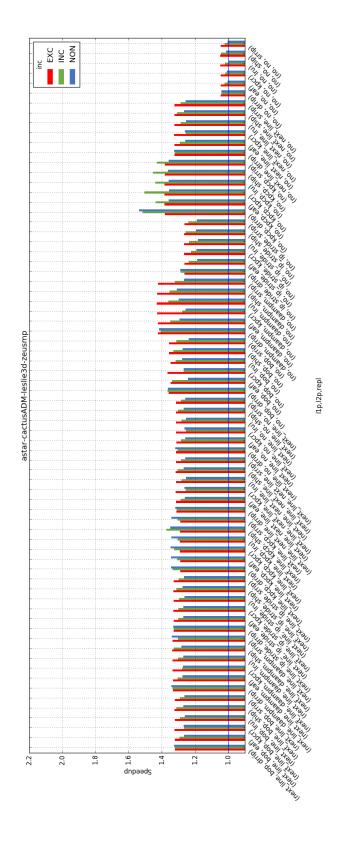

| B.3   | Astar-Leslie3d-Soplex-Zeusmp                    |

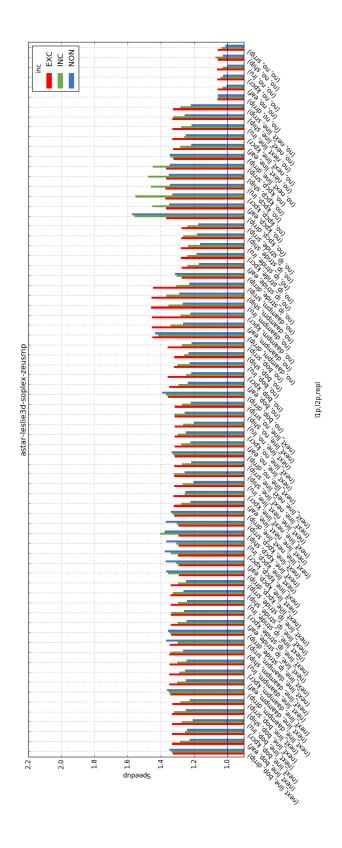

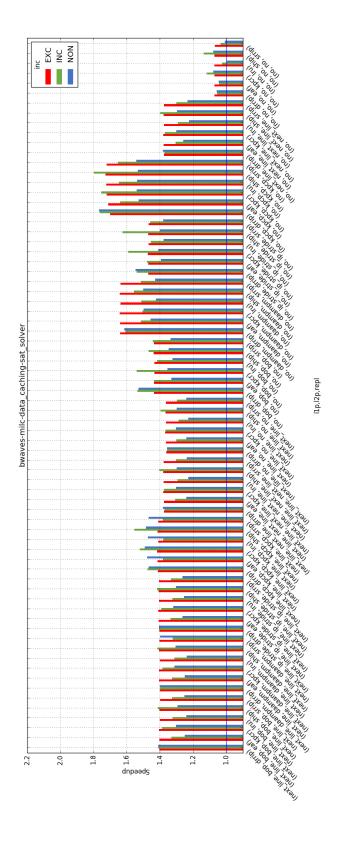

| B.4   | Bwaves-Milc-Data_Caching-Sat_Solver             |

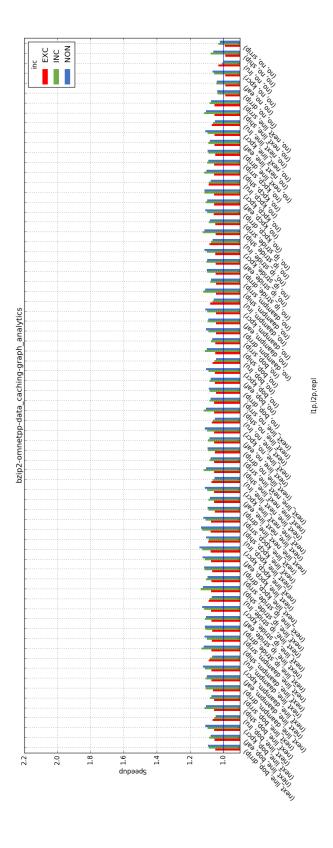

| B.5   | Bzip2-Omnetpp-Data_Caching-Graph_Analytics      |

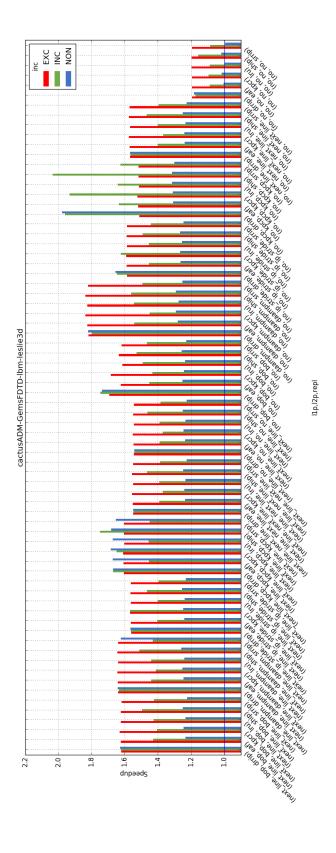

| B.6   | CactusADM-GemsFDTD-Lbm-Leslie3d                 |

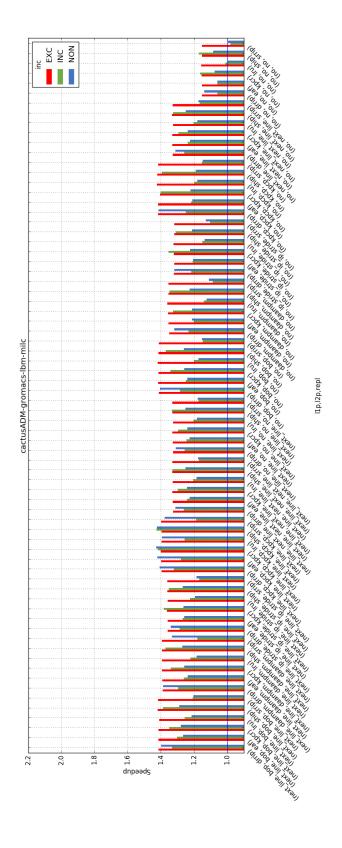

| B.7   | CactusADM-Gromacs-Lbm-Milc                      |

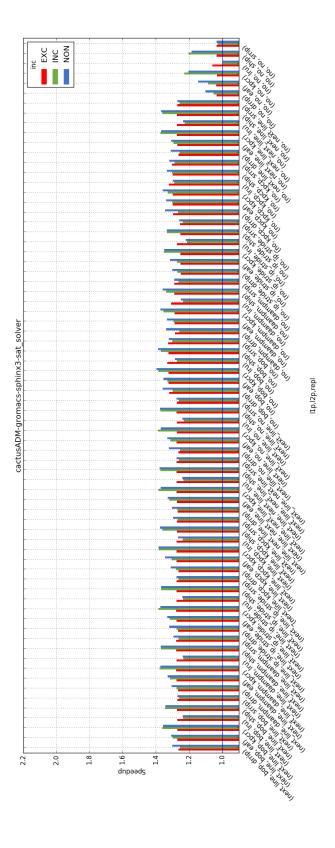

| B.8   | CactusADM-Gromacs-Sphinx3-Sat Solver            |

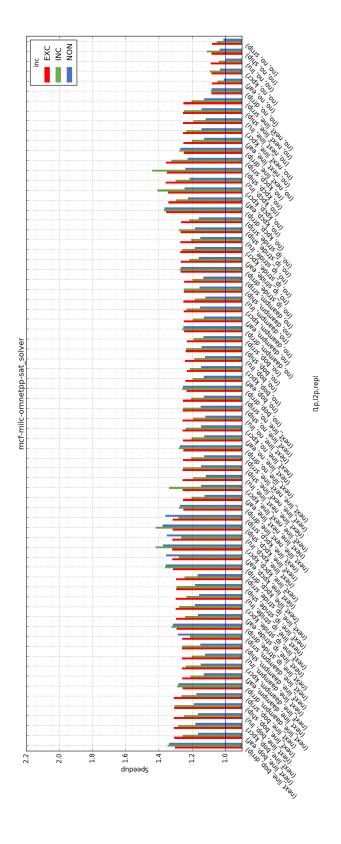

| B.9   | Mcf-Milc-Omnetpp-Sat_Solver                     |

| APPEN | DIX C. SINGLE-CORE SIZE SENSITIVITY RESULTS 126 |

| C.1   | Astar                                           |

| C.2   | Bwaves                                          |

| C.3   | Bzip2                                           |

| C.4   | CactusADM                                       |

| C.5   | Data_Caching                                    |

| C.6   | Gcc                                             |

| C.7   | GemsFTD                                         |

| C.8   | Graph_Analytics                                 |

| C.9   | Gromacs                                         |

| C.10  | Lbm                                             |

| C.11  | Leslie3d                                        |

| C.12  | Libquantum                                      |

| C.13  | Mcf                                             |

| C.14  | Milc                                            |

| C.15  | Mlpack_Cf                                       |

| C.16  | Omnetpp                                         |

| C.17  | Sat Solver                                      |

| C.18  | Soplex                                          |

|       | Sphinx3                                         |

|       | Wrf                                             |

|       | Xalancbmk                                       |

|       | Zeusmp                                          |

# LIST OF FIGURES

| FIGUR | FIGURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | Diagram of the memory hierarchy in a modern processor. The higher the capacity of the cache, the higher the latency to access a block in that cache. In a multi-core, there are replications of the "core" part inside the "SoC" part                                                                                                                                                                                                                                                                      | 7    |

| 2.2   | Cache coherence problem example                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13   |

| 2.3   | Memory hierarchy in a multi-core processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13   |

| 2.4   | Simplified state transition diagram of the MSI cache coherence protocol                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 15 |

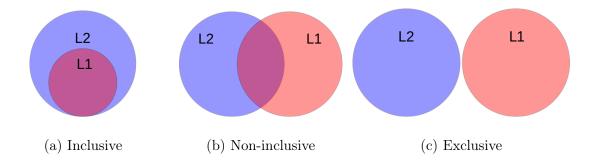

| 2.5   | Diagram to show where the data is in an a) inclusive, b) non-inclusive, and c) exclusive cache. The intersection is data duplication                                                                                                                                                                                                                                                                                                                                                                       | 17   |

| 5.1   | Main functions on ChampSim to operate the cache                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55   |

| 5.2   | Inclusive cache high-level code on top of the non-inclusive implementation                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61   |

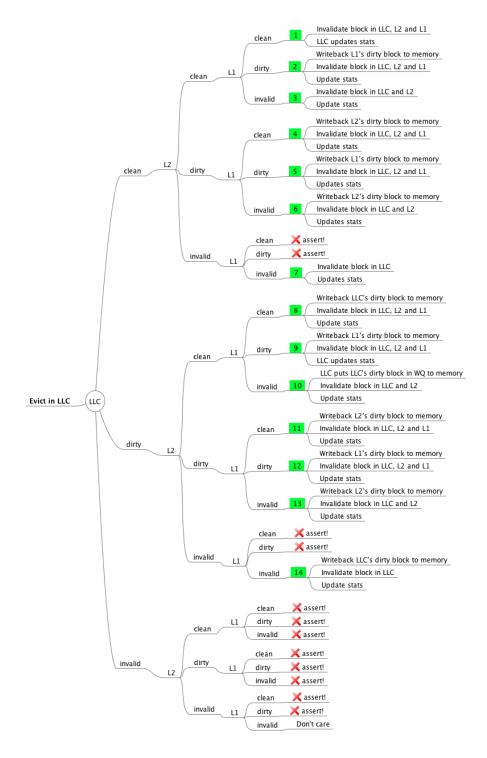

| 5.3   | Diagram with all the possible cases on an LLC miss in an inclusive cache on a single core simulation                                                                                                                                                                                                                                                                                                                                                                                                       | 63   |

| 5.4   | Exclusive cache high-level code on top of the non-inclusive implementation                                                                                                                                                                                                                                                                                                                                                                                                                                 | 66   |

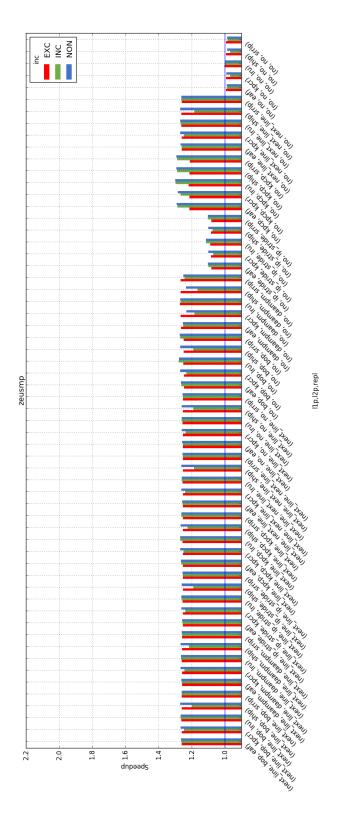

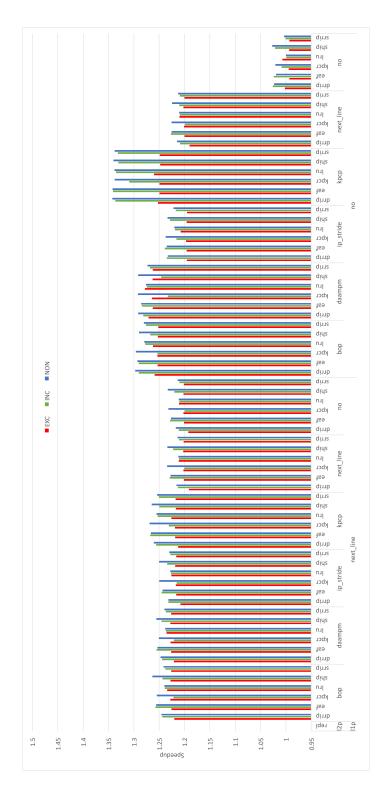

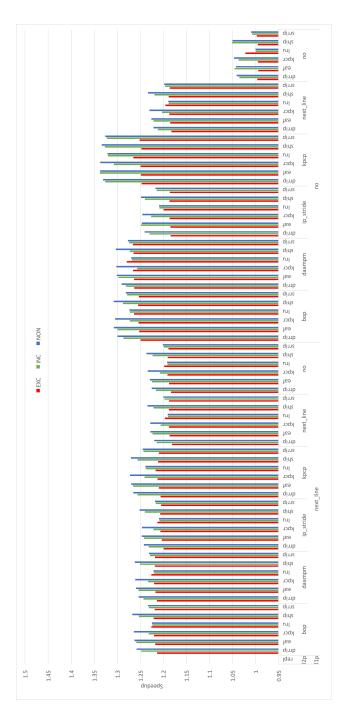

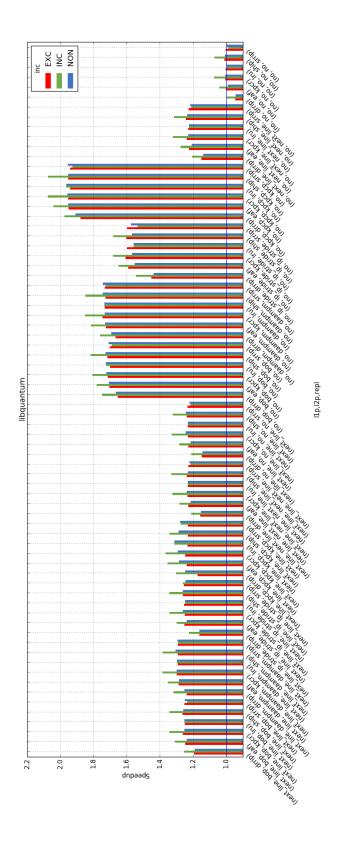

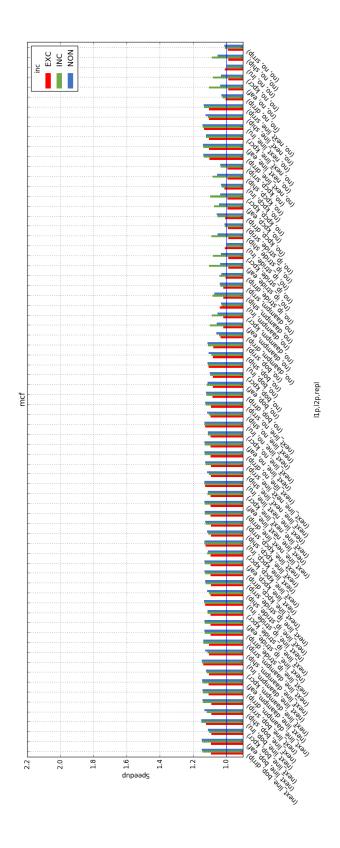

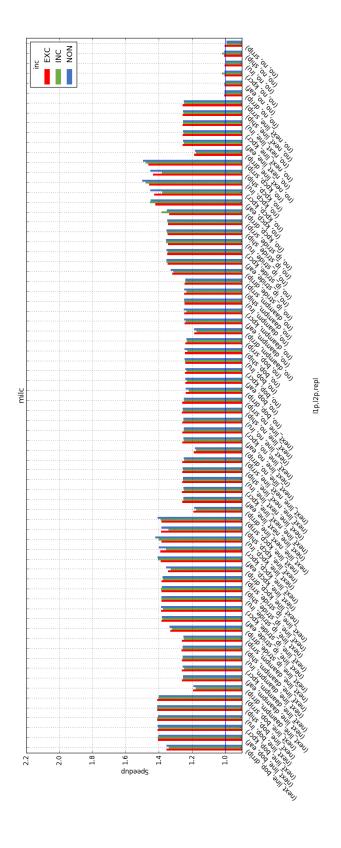

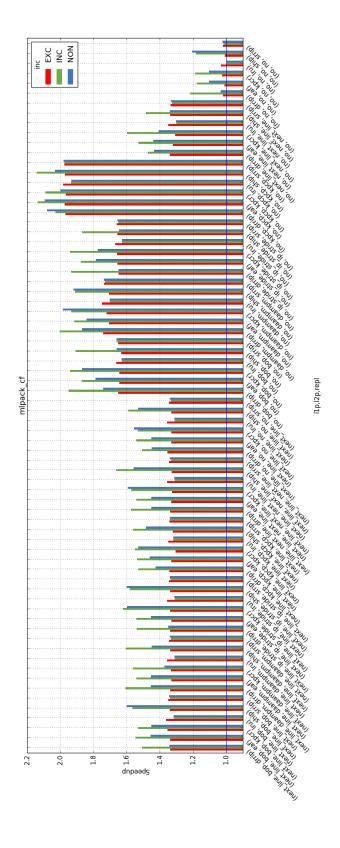

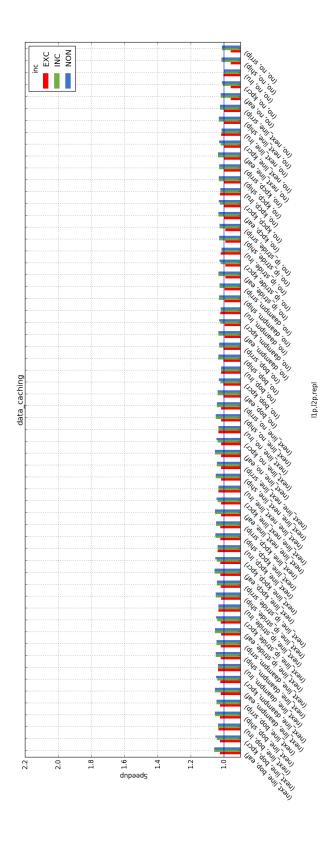

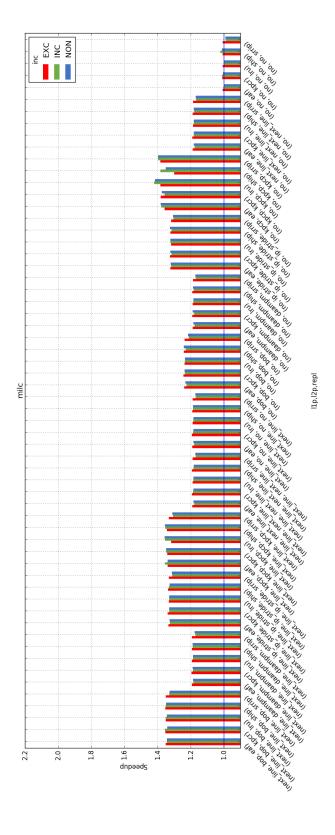

| 6.1   | Geomean speedups to compare different configurations of L1 and L2 prefetchers, replacement policies and cache inclusions. The configurations compared are: L1 prefetcher, L2 prefetcher, replacement policy and cache inclusion. The Y-axis shows the speedup over the baseline configuration: no prefetchers, LRU replacement policy and a non-inclusive cache. The X-axis shows the different cache configurations, in order of: L1 prefetcher (l1p), L2 prefetcher (l2p) and replacement policy (repl). | 70   |

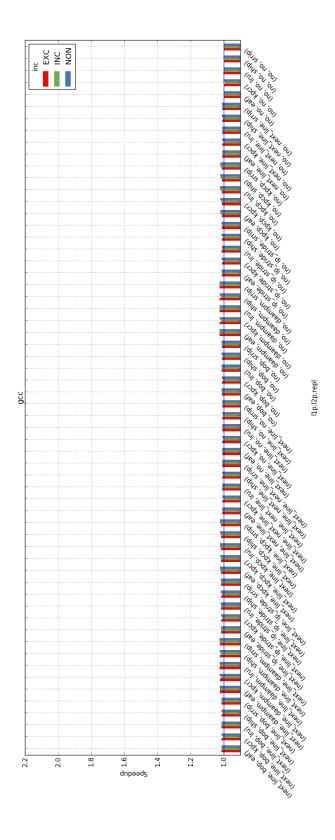

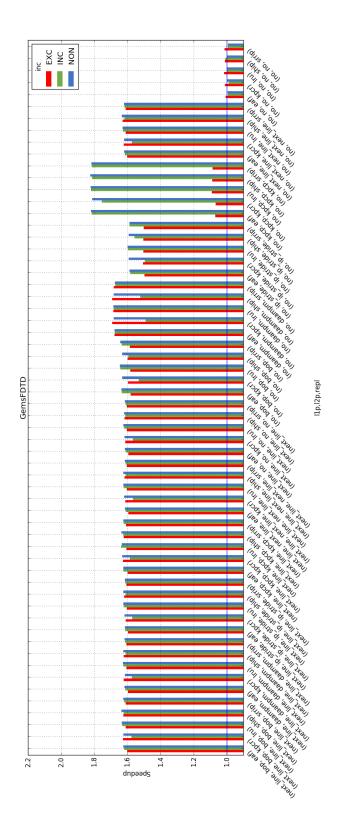

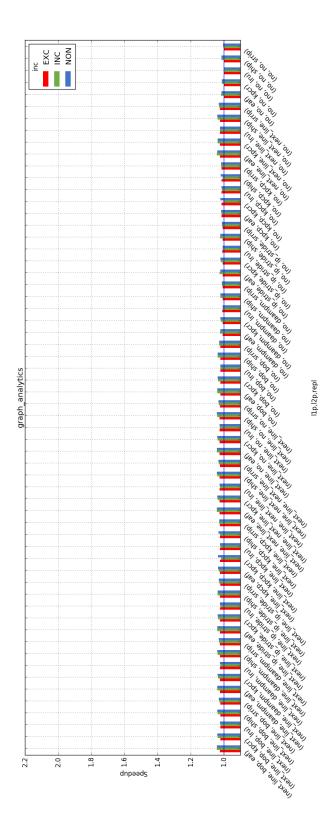

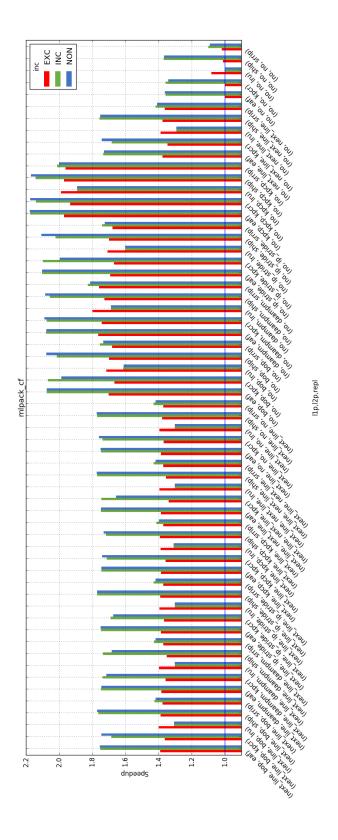

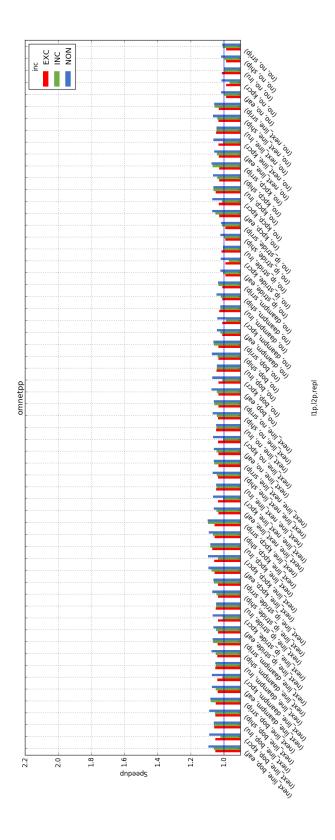

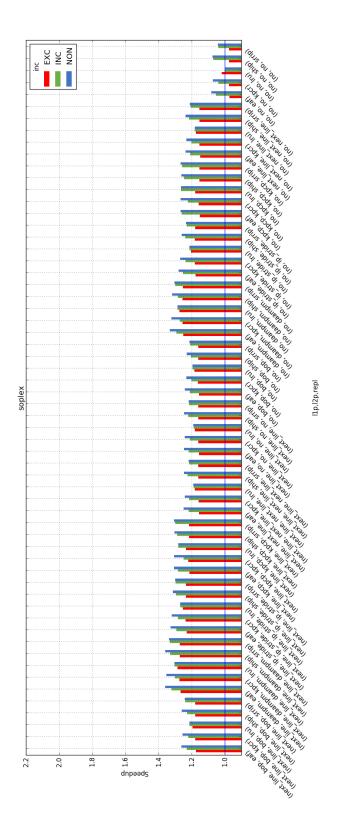

| 6.2 | Geomean speedups to compare different configurations of L1 and L2 prefetchers, replacement policies and cache inclusions. The configurations compared are: L1 prefetcher, L2 prefetcher, replacement policy and cache inclusion. The Y-axis shows the speedup over the baseline configuration: no prefetchers, LRU replacement policy and a non-inclusive cache. The X-axis shows the different cache configurations, in order of: L1 prefetcher (l1p), L2 prefetcher (l2p) and replacement policy (repl)                                                                                                                  | 73 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

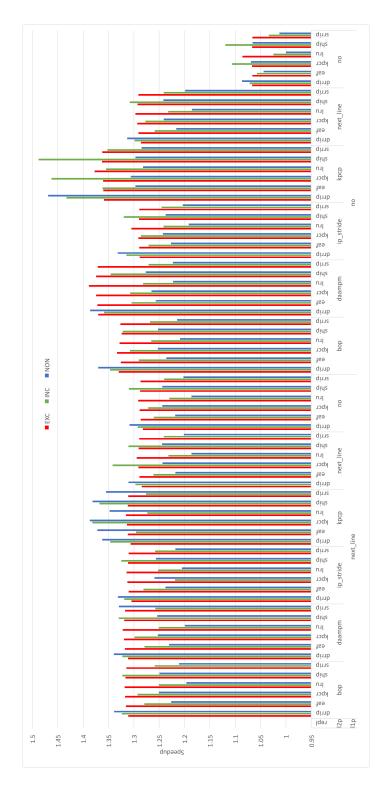

| 6.3 | Geomean speedups to compare size sensitivity with different configurations of L1 and L2 prefetchers, replacement policies and cache inclusions on a large cache configuration. The size of each cache level is: 64KB L1, 512KB L2 and 2MB LLC. The configurations compared are: L1 prefetcher, L2 prefetcher, replacement policy and cache inclusion. The Y-axis shows speedup over the baseline configuration: no prefetchers, LRU replacement policy and a non-inclusive cache. The X-axis shows the different cache configurations, in order of: L1 prefetcher (l1p), L2 prefetcher (l2p) and replacement policy (repl) | 77 |

# LIST OF TABLES

| TABLE                                                              |      |  |

|--------------------------------------------------------------------|------|--|

| 2.1 Inclusion policy properties                                    | . 23 |  |

| 3.1 State-of-the-art replacement policies and the inclusion policy | . 34 |  |

| 3.2 L2 cache block classification in the CHAR algorithm            | . 46 |  |

| 4.1 SPEC CPU2006 memory intensive benchmarks                       | . 49 |  |

| 4.2 CloudSuite benchmarks                                          | . 49 |  |

| 4.3 Multiprogrammed workloads mixes for simulating 4 cores         | . 49 |  |

| 4.4 Simulator configuration                                        | . 50 |  |

| 5.1 Model of an non-inclusive two-level cache                      | . 57 |  |

| 5.2 Model of an inclusive two-level cache                          | . 59 |  |

| 5.3 Model of an exclusive two-level cache                          | . 64 |  |

#### 1. INTRODUCTION

The size of transistors has kept decreasing thanks to technology improvements and therefore increasing the number of transistors per chip as stated by Moore's Law [1, 2]. This led to add more complexity to the compute core in the chip to improve performance (e.g. out-of-order execution) and include multiple levels of cache memory to reduce the gap with memory latency by exploiting data locality.

Due to power density constraints, computer architects changed the way of designing chips over a decade ago: increasing the number of cores per chip instead of building more complex single-core chips [3]. The last-level cache (LLC), i.e., the level closer to memory and further away from cores, is typically shared among all cores in the chip. When shared, it stores blocks from all cores and is typically sized at about 1-2 megabytes (MB) per core. Increasing the number of cores requires a larger cache to maintain high core performance.

There are several ways to manage how data is allocated in the multiple levels of cache depending on whether a higher level (closer to memory) includes data resident in lower levels (closer to cores). In *inclusive* caches, a data block present in a cache, must also be present in all of its corresponding higher levels. To accomplish this, every cache miss will allocate the data block read from memory in all cache levels, including the LLC. At the same time, when a data block is evicted from a cache, the block is invalidated in all of its corresponding lower levels. The result of this policy is a lower effective cache capacity due to the data replication across cache levels, and the potential performance and energy impact of inclusiveness-induced invalidations.

Non-inclusive caches attempt to reduce the limitations of inclusive accesses by not enforcing inclusivity in higher cache levels. When a data block is accessed,

it is still allocated in all cache levels. However, an eviction on a cache does not trigger invalidation in lower levels. There is still data replication, but there are not inclusiveness-induced invalidations affecting performance and energy.

Exclusive caches go one step further by enforcing that a data block present in a cache cannot be also present in a corresponding higher-level cache. To enforce this, on a cache miss the block is sent to the lower levels and not allocated in the exclusive cache. On a LLC hit, the block would be sent to the lower level and invalidated in the exclusive cache. Only data evicted from lower levels is present in the exclusive cache, a design known as victim cache [4]. The result is that there is no data replication and, as a consequence, there cannot be inclusiveness-induced invalidations.

# 1.1 My Project

In this thesis we evaluate different prefetchers and replacement policies for the three cache inclusion types: inclusive, non-inclusive and exclusive. We use singlethreaded applications for single- and multi-core (multiprogrammed workloads).

We use the ChampSim simulator, used in the 2nd Cache Replacement Championship [5], to model the different cache configurations. The benchmarks will be several traces from SPEC CPU2006 [6], CloudSuite [7] and one machine learning workload trace from mlpack [8].

## 1.1.1 Objectives

The main objectives of this project are:

- Quantify the correlation between cache replacement, prefetching and cache inclusion policies.

- Prove the need of having a different cache management technique depending on the cache inclusion type.

#### 1.1.2 Contributions

The contributions of this project to fulfill the aforementioned objectives are:

- A comprehensive evaluation of multiple cache configurations including multiple replacement policies and prefetchers for all three inclusion policies: inclusive, non-inclusive and exclusive caches.

- A discussion on the results targeting to understand the gaps in the design of cache replacement policies to improve performance and reduce energy consumption in the presence of a given inclusion policy.

#### 1.2 Document Structure

Chapter 2 introduces the basics on cache hierarchy that are necessary to understand on the following chapters. Chapter 3 explains the state of the art on cache replacement policies. Chapter 5 explains the implementation details of this project and discusses the challenges that came up. Chapter 4 describes the methodology used in the project. This includes the tools and the evaluation methodology. Finally, we conclude showing and discussing the results, the lessons learned and the conclusions of this work. At the end, we propose different lines of future work.

#### 2. BACKGROUND

The improvement rate of processor speed has been higher than that of memory speed for a few decades, the so called *memory wall* [9]. It is necessary to develop techniques to mitigate this performance gap. One solution was introducing several levels of memory, also known as the *memory hierarchy*, to bring data closer to the processor. There has been extensive research on improving memory management. Specifically for the cache hierarchy, the memory between the processor and main memory, the two most important topics have been prefetching and cache replacement policies.

Prefetching aims to bring data to a cache level closer to the processor before the data is requested. This reduces the latency on accessing the block if the prefetcher was accurate (brought the data that was to be requested) and timely (the time the data arrived to the cache made the accesses hit). However, prefetching can also pollute the cache with blocks that are evicted before being used if it brings data that will not be used or it is brought too late or too early, thus interfering with actual useful data.

Replacement policies improve the management of cache contents to evict first the blocks that are not likely to be used again to make space to the newly requested blocks. They can also hurt performance if the block removed was still in use and is requested shortly after.

Cache blocks that contain the data can be in either of the cache levels. The inclusion policy decides in how many levels and where to keep each block. For example, if we put the same block in all cache levels, the effective space of the cache hierarchy would be reduced but it could be faster to access assuming the block would

still be in the next cache level.

In the following sections of this chapter, we introduce basic concepts of the memory hierarchy and techniques to improve its use.

# 2.1 Memory Hierarchy

Computer programs usually have memory access patterns that exhibit spatial or temporal locality. Spatial locality refers to a memory access to a location most likely will result in recurrent accesses to nearby memory locations. For example, when accessing in order all elements in an array, where all the array elements are stored consecutively in memory. Temporal locality refers to a memory access that will likely result in another reference to the same memory location again in the near future. For example, when in an array operation we need to read and then write on an array several times.

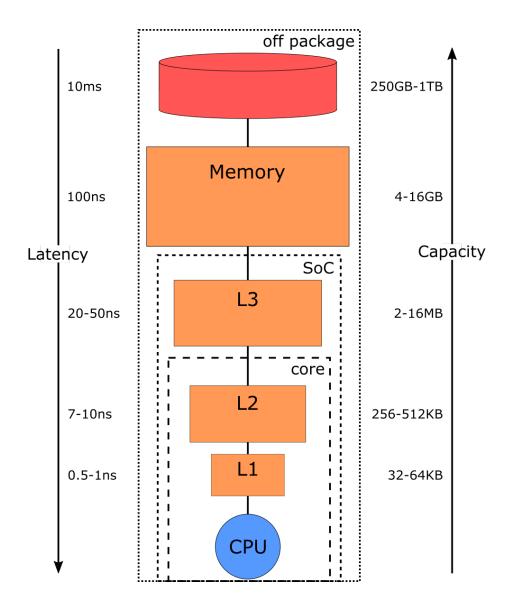

Figure 2.1 shows an example of a memory hierarchy in a modern system. To reduce the latency of bringing data from main memory to the processor, architects exploited the spatial and temporal locality of programs with faster and smaller memories between the processor and the main memory. These small memories are called caches. Typically there are two, three or four levels of cache, each one of a different size and access latency. The closest level to the processor is typically called "L1", for level 1, the next "L2", and so on. We will call the closest level to the processor the *lowest* and the last one before the main memory the *highest*, i.e. the lower level of L2 is L1. Typically, the L1 is divided in two: L1 data (L1D) and L1 instructions (L1I).

The core also contains a few registers where all data in use is stored to compute the current fragment of code (inside of CPU in Figure 2.1). This is a very small and expensive memory, and it is the fastest one. As a rule of thumb, the closer to the processor, the smaller the cache capacity and latency. The latency of each element on the memory hierarchy depends on different properties: its technology, its capacity and its distance to the core. The different latencies at the different cache levels have to do with their implementation in terms of logic and technology. Accessing larger data arrays require larger latency because of more complex circuitry, such as large decoders/encoders, that involve longer gate nets. At the same time, bit cells in on-chip caches are implemented with 6 transistors (6T SRAM) for faster access although at higher power, while off-chip memory is implemented with 1 capacitor bit cells (DRAM [10]) that loses its charge and must be refreshed periodically for higher density (less area per bit) and lower power consumption at the expense of latency and refresh cost. Also, on-chip caches typically run at higher frequency. Some on-chip caches are implemented with embedded DRAM (eDRAM) which provide higher density and low power at the expense of latency. This eDRAM technology is applicable to LLCs because their latency would be prohibited for caches closer to the core.

The basic unit for cache storage is the cache block. A cache block contains a certain number of data bytes. Each cache level is organized in cache sets. A cache set may contain from one block to all blocks of the cache. The data is placed in the cache in a position that depends on its address. To identify which block of the set we want, a tag is used as a unique identifier. Cache memories can be mapped in different ways: direct mapped, set associative and fully associative. A direct mapped cache places a block in a given position indexed by some bits of its address. Several blocks can be mapped to the same position. In this mapping, each set contains one single cache block. The fully associative cache places the blocks in any of the positions available. In this case, one set contains all blocks. The set associative cache is a compromise between those two: each set contains are a small number of

Figure 2.1: Diagram of the memory hierarchy in a modern processor. The higher the capacity of the cache, the higher the latency to access a block in that cache. In a multi-core, there are replications of the "core" part inside the "SoC" part.

ways (typically 2, 4, 8 or 16), each block being placed in the set that is chosen by its address, and at any ways within the set.

A cache hit happens when a block is requested and it is currently stored in one of the levels. A cache miss is when the block is not there on reference. On a cache miss, to improve performance, a cache in a modern processor typically has special registers called miss status holding registers (MSHR) where it stores information about the block that missed while its requests to the next cache levels and memory is resolved. A cache with MSHR is called a non-blocking cache. Keeping that information in multiple MSHRs allows to have multiple cache misses being resolved in memory and more load/store instructions in flight. This is called memory-level parallelism (MLP), and allows overlapping latencies from multiple accesses and the core to progress computation on instructions that are independent from those misses.

# 2.1.1 Miss Types

There are four different types of misses depending on the reasons that cause them: compulsory, capacity, conflict and coherence. Compulsory misses are the ones that are a miss because the execution of the program has just started and the caches are empty. These misses are also called cold misses. Capacity misses occur because of the limited cache size. These misses completely disappear with a sufficiently large cache. Conflict misses occur because of the data mapping in the cache. In a direct mapped cache, each block is mapped to a particular cache position. When placing a block in the cache, the block in that position is evicted. A definition by Hill, "conflict misses are misses that would not occur if the cache were fully associative with LRU replacement". Coherency misses occur when private caches invalidate other copies of their blocks in the cache hierarchy and subsequent accesses to those invalidated copies miss.

There are several techniques to reduce these four miss types. Compulsory misses can be reduced by a prefetcher that predicts which blocks are going to be used and brings them to the cache before they are requested. However, prefetchers can pollute the cache with data that is not going to be used if the predictions are wrong. Compulsory misses can also be reduced by increasing block size. A larger cache reduces capacity misses. A larger cache fits more blocks, but then latency may be higher. Conflict misses happen because of the mapping, so with a higher associativity it is less likely that a block that will be needed is going to be evicted. However, the higher the associativity, the higher the energy, the slower and more complex the cache. Coherency misses can be reduced by using a different coherence protocol, for example one that updates the block at other caches instead of invalidating the block.

# 2.1.2 Load Flow

At the start of a program all cache levels are empty. Below there is an order on what happens when the first load instruction executes in a 2-level inclusive cache. From the cycle the load operation is selected to access the L1 cache:

### 1. In parallel:

- Decode the index of the L1 cache set with virtual bits

- Search the translation of virtual to physical in the translation lookaside buffer (TLB)

- 2. There is a TLB miss, because that memory page was not accessed before

- 3. The page walker searches the page

- 4. If there is a page fault, the operating system (OS) causes an exception to bring the page from disk to memory and stores the translation in the page table and in the TLB

- 5. The instruction is re-executed

- 6. On the second access to the TLB, the physical address is found, and all tags in the set are compared to that address, and if a block matches, it checks if the block is valid

- 7. It is an L1 miss because the block was not accessed before and the prefetcher is not trained yet

- 8. Find the victim block where the data will be stored in the L1 whenever it arrives from memory (depends on the replacement policy) and update the state of the replacement policy and prefetcher (if necessary)

- 9. The information about the instruction is stored in an MSHR of the L1 (assuming there is one empty, otherwise we have to wait until one becomes free)

- 10. Decode the index of the L2 cache set

- 11. Check all the tags in the set and whether the block is valid

- 12. It is an L2 miss

- 13. Find the victim block where the data will be stored in the L1 whenever it arrives from memory (depends on the replacement policy)

- 14. The information about the instruction is stored in an available MSHR of the L2

- 15. Request to the memory controller to load the line that contains the required data

- 16. The memory controller reads the line and sends the block back to the requester L2

- 17. The cache controller receives the block and matches the address to the information in the L2 MSHR

- 18. Evict victim block and write it to memory if it was dirty

- 19. The block is stored in the L2 and sent to the L1 (and repeats the steps for block replacement as in the L2)

- 20. The data requested by the load operation is sent to the central processing unit (CPU)

If the 2-level cache was non-inclusive, it would have been the same list and order. The difference is in the exclusive cache: in the step 19, the block would not have been allocated in the L2, only in the L1.

#### 2.1.3 Write Policies

The cache hierarchy keeps data in some or all of their levels while the data is in use. Modified data must be written back to memory at some point. There are two main moments that a block can be written to memory: immediately or before invalidation. These two write policies are called write-through and write-back respectively.

A write-through cache writes the block to main memory immediately after writing it to the cache data array. This is a simple implementation that does not require any work at invalidation, but it requires to send the block to memory on every write. In this case, cache blocks and main memory contain the latest and updated data. This simplifies coherence (see subsection 2.1.4) but increases data movement.

A write-back cache only writes the block to main memory when it is evicted from the cache. Meanwhile, the data in main memory is a stale copy. A write-back cache is more complex as it requires one bit (dirty bit) to identify whether the block has been modified -so called dirty block. If the block is modified, it needs to be written to memory on eviction. If the block has not been modified -so called clean block, it can be simply invalidated with no further action.

In both write policies, it is not defined what to do on a write miss. There are two possibilities: either allocate the block "write allocate" or not, "write-no-allocate". Write allocate loads the block that missed to the cache and then writes it. Write-no-allocate writes the data directly to main memory bypassing the cache.

Any combination of write policies and write miss policies are possible. However, there are two that are generally more efficient: write-back with write allocate and write-through with write-no-allocate.

#### 2.1.4 Cache Coherence

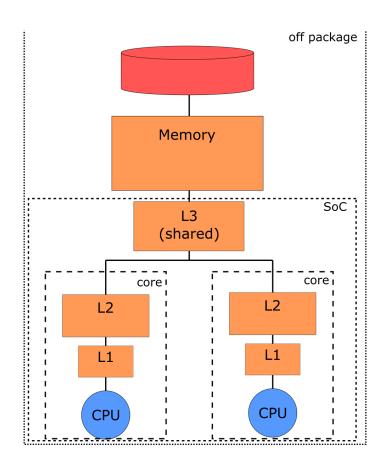

Modern microprocessors have multiple cores. Each core has at least one private cache and there generally is a cache that is shared among all cores. Figure 2.3 shows an example of a typical three-level cache hierarchy with two cores where the L3 is shared among all cores, and L1 and L2 are private for each core. The same block of data can be present in several private caches for multithreaded applications, where different threads share data. For example, in a program with two threads, each running in a different core, we can have the situation shown in Figure 2.2. If there is no coherence, the last load miss will come from memory with a stale value because the correct value is in thread 1's private cache.

The two main techniques to solve this problem are invalidation and update. On invalidation, only one copy of the block is allowed to exist at a time, whenever another core requests that block, the previous is invalidated. On update, each write to a block is also written to all other present copies of that block.

Multi-core processors implement these techniques atomically through a cache

```

Thread 1: load A (miss)

Thread 2: load A (miss)

Thread 1: write A (hit)

Thread 2 L1: load B (miss) --> invalidate A

Thread 2: load A (miss)

```

Figure 2.2: Cache coherence problem example.

Figure 2.3: Memory hierarchy in a multi-core processor.

coherence protocol. Each cache block has a coherence state to represent information such as which and how many cores have the block and if the block has been modified. The simpler state information would be for a single-core write-through cache, where the only two states are: valid and invalid. In that example, all blocks are invalid first and are marked as valid at a fill. On a write, the block is still valid and the main memory is updated. Another simple state information would be for a single-core write-back cache, with four states: valid, invalid, modified (dirty) and clean.

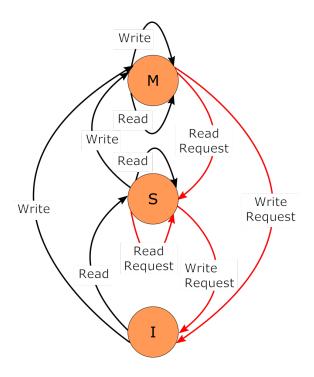

# 2.1.4.1 MSI Protocol

A simple cache coherence protocol is the MSI protocol. This protocol implements the invalidation technique and is used in write-back caches. There are three different states in this protocol: "M", "S" and "I". The "M" state stands for *modified* and is equivalent to a dirty block. This state can only be held by one of the copies across multiple private caches. The "S" stands for *shared*, this means that the block is valid and clean. One or more copies of the block across multiple private caches can be in this state. The "I" stands for *invalid*.

Cache coherence protocols are usually represented with a state transition diagram that shows when and what triggers a transition from one state to another. Figure 2.4 shows the state transition diagram for the MSI protocol. The black arrows show the actions (read/write) initiated by the core. The red arrows represent the requests initiated by caches. There are two main transitions that cause several messages. First, a block in the shared state that is going to be written by one of the cores generates an invalidate message to invalidate all copies in other caches. Second, when a core wants to read a block that is in modified state in another core's private cache, the modified block value is written to memory and transferred to the reading core and both copies are set to shared state. This implies snoop or directory operations in

Figure 2.4: Simplified state transition diagram of the MSI cache coherence protocol.

the on-chip network to find the modified copy and transfer the modified block value to the reading core.

# 2.1.4.2 MSI-Like Protocols

There have been multiple efforts to improve on the MSI protocol, mainly to reduce coherence traffic. One of the issues in the MSI protocol is that every time that there is only one copy of a block in the shared state and that the core wants to modify it, it has to send unnecessary invalidation messages to the bus. The MESI protocol improves on this case. The new state "E" stands for exclusive and means that there is exactly one copy of the block at a time and it is clean. When a block is filled for a read the first time, it transitions from invalid to exclusive. Then, when the core wants to write the block transitions to modified without the need to send

invalidations to other because it is known that it is the only copy in the system. This protocol significantly reduces coherence traffic when a block is private, i.e., accessed by a single core.

Another issue in the MSI protocol is that every time that there is a read request from a core of a block in the modified state in another core, the modified block must be written to memory. The MOSI protocol adds the *owned* state, "O". A block arrives to this state when a modified block receives a read request from another core. The cache that had the modified block, so called the "owner", is the responsible to respond and send the block to all read requests to that block and, later, to send the value to memory before invalidation. The cores that receive that block keep the block in shared state. This avoids writing the block to memory until the latest possible moment.

The MOESI protocol puts together all the states used in the previous protocols. This protocol improves performance by delaying the writes to main memory as much as possible and by reducing unnecessary coherence messages when a block is only referenced by a single core.

#### 2.2 Inclusion Policies

A cache level is related to the previous or the next level (if any of those exist) depending on which data blocks each level contains. A particular cache level can contain exactly all, exactly none or some of the data blocks of the lower level.

An *inclusive* cache contains all data blocks of the lower level. An *exclusive* cache does not contain any of the data blocks of the lower level. A *non-inclusive* cache can contain some blocks from the lower level but not necessarily all or none. Figure 2.5 shows a diagram of each of the inclusion policies.

Each cache level can use a different inclusion policy. For example, the L3 can

Figure 2.5: Diagram to show where the data is in an a) inclusive, b) non-inclusive, and c) exclusive cache. The intersection is data duplication.

be exclusive of L2 while the L2 is inclusive of L1. All these inclusion policies have their benefits and drawbacks, mostly related to latency, data replication and data movement.

#### 2.2.1 Inclusive

An inclusive cache level contains all data blocks from lower levels plus some other blocks. Figure 2.5a shows a diagram of which data is in which cache, where the intersection is data duplication. That is, a data block is replicated in both cache levels.

In a 2-level cache hierarchy, the data block will be placed in both cache levels on an L2 miss. If the block is evicted from the L1 and, later, a request comes (L1 miss), the data may still be in the L2, thus avoiding accessing main memory. On an L1 eviction, only write backs of dirty blocks are required. If the block is clean, there is no need to copy it back to the L2 because it is already there as per the inclusion policy. A potential problem is on an L2 eviction: to preserve inclusivity, if the block was present in L1, it must be evicted too.

In a multi-core system, this inclusion policy simplifies the coherence protocol im-

plementation. A cache wanting to invalidate copies of a block in other caches just has to notify the LLC because it has the information of all blocks in all lower caches. With this, there is no need for coherence message broadcasts, thus reducing complexity and energy consumption. Also, coherence information (state and caches having a copy) can be encoded with the cache block so the information is available when accessing it, thus cutting latency of potentially having to access separate structures, such as a directory.

Given that an inclusive LLC knows which lower caches have a block that is going to be evicted, invalidation messages can be directed to those caches without the need of broadcasting the message.

One disadvantage is the effective cache size due to data duplication. The effective size of the cache hierarchy is the size of the LLC. For example, in a 2-level cache hierarchy, the effective size is the one from L2 because it contains all contents from L1. The L1 cache only keeps data closer but does not contribute with additional capacity.

Another disadvantage is back invalidations. An eviction from the LLC can generate an invalidation in an L1. If it was present in the L1, the block may be in use. This can be a problem if the replacement policy is not aware of the usage of a block in the lower caches. Jaleel et al. claim that the limited performance of an inclusive cache comes from back invalidations because the LLC replacement policy is not aware of the core presence of blocks and their recency [11].

A related problem is that an inclusive cache has less flexibility to improve cache management due to the impossibility of bypassing the LLC to maintain inclusivity.

$$E = c_n (2.1)$$

Equation 2.1 shows the calculation of the effective cache capacity in a cache hierarchy with inclusive LLC, where E is the overall system effective cache capacity and n is the number of cache levels, thus  $c_n$  being the capacity of the LLC.

#### 2.2.2 Exclusive

An exclusive cache does not include any replicated block from lower levels. Figure 2.5c shows a diagram of the data blocks of each cache level in an exclusive cache. In this case, there is no overlap and the intersection of the two sets is empty, so there is no data replication. This inclusion policy increases the total amount of data blocks that can fit in the whole cache hierarchy.

The exclusive inclusion policy is similar to a victim cache [4]. In a three-level cache hierarchy, the LLC would be the victim cache of a two-level cache. Victim caches contain the evicted blocks from the lower levels aiming to reduce conflict misses. This was originally introduced as a fully associative small cache to reduce conflict misses from direct-mapped caches.

However, it incurs higher complexity. In the example of two cache levels (L1 and L2), when a block that is in L1 (and not in L2) is evicted, it will be allocated in L2. When the block is accessed again, it will be invalidated in L2 and allocated in L1. This generates more work to do on an L2 hit. Also, it makes impossible to use the recency of a block to choose which block to replace when the L2 cache is full, as it only contains data that was evicted from L1 and not accessed again since that eviction.

Jouppi and Wilton identified the benefits of exclusive caching and evaluated them [12]. They found that the extra space of not duplicating the data in the two levels of cache and a higher associativity in the LLC was indeed beneficial. Ten years later, Zheng et al. evaluated the performance of exclusive cache hierarchies with respect to inclusive caches [13]. They found that exclusive caching is beneficial for most of the benchmarks they tried (SPEC 2000), but especially for smaller lower-level caches. They suggest that exclusive caches are more suitable for server applications and embedded systems.

The main benefits when using exclusive caches are:

- Less conflict misses by behaving like a higher associativity cache, as two memory references that are mapped to the same set can reside one in each level instead of only one.

- Higher hit rate thanks to a higher effective space by avoiding the blocks duplication in different levels. This is especially relevant in caches with more than 3 levels of cache or with large lower level caches.

- Avoids premature evictions from the lower levels of cache by not requiring back invalidations, like in an inclusive cache policy.

The main drawbacks and limitations of an exclusive cache are:

- Less design flexibility because the block size of the exclusive cache has to be the same as the other cache levels.

- More control complexity and power consumption due to the higher data movement of blocks from one level to the other.

- More complex cache coherence protocols and more area required in symmetric multiprocessor (SMP). This is only important for multithreaded programs, which is not the case of this thesis work.

Equation 2.2 shows the effective capacity of an exclusive cache, being E the effective capacity, n the number of cache levels, and c the capacity of a cache level.

The higher effective capacity is one of the most attractive features of an exclusive cache. For this same reason, exclusive caches have been investigated in other fields, such as in storage to reduce the impact of the high usage of cache RAM in disk arrays [14].

$$E = \sum_{i=1}^{n} c_i , \qquad (2.2)$$

## 2.2.3 Non-Inclusive

A non-inclusive cache level may or may not contain blocks from lower levels. Figure 2.5b shows a diagram of one possible case in a non-inclusive cache, where just some blocks from L1 are also in L2. The data is replicated when there is a miss in a cache level, and the block is allocated in that cache level and all higher ones. For example, in an L1 miss where the block is in none of the caches, the block will be allocated in L2 and L1. The difference with an inclusive cache is that the inclusivity is not enforced. That means, when a block is evicted from a higher level, it does not generate back invalidations to the lower levels. This simplifies the implementation of this type of caches.

The main advantages that can be gained by forcing non-inclusion are a higher effective cache and lower conflict misses. The effective cache size is higher compared to an inclusive cache. In the best case scenario, the effective cache size is the sum of all caches, like in the exclusive case (see Equation 2.2). That is the case when all cache blocks present in the L1 have been replaced in the L2. However, the worst-case scenario is when none of the L1 blocks have been evicted from the L2, equivalent to an inclusive cache (see Equation 2.1). The cache hierarchy usage in a case with non-inclusive cache changes depending on the application and replacement policy.

Conflict misses will be reduced in the intermediate or last-level cache. The blocks that are referenced frequently stay in L1, therefore L2 has space for other blocks.

One disadvantage of non-inclusive caches is coherence. A non-inclusive LLC that needs to evict a block will have to ask all the lower level caches if they have the block, because that information is not present in the LLC, unless a separate directory is implemented and then it must access the directory and pay its extra latency. If the block is present in any lower-level caches, it needs to be invalidated or updated. However, there has been work to separate the cache coherence structures (i.e. directory) from the data blocks of the cache. Zhao et al. proposed a non-inclusive cache with an inclusive directory to keep the positive features of both inclusive and non-inclusive policies [15].

# 2.2.4 Summary of Inclusions

Table 2.1 shows a summary of all the inclusion policies explained previously in this section.

Modern processors use different types of inclusion policies in each level of cache. The most common is to either use an inclusive or an exclusive policy in the LLC and an inclusive or non-inclusive in the lower levels. Below there are a few examples of real processors with the information on the inclusion policy they use. None of the ones covered here has a non-inclusive LLC.

For example, AMD processors generally use an exclusive last-level cache and Intel, an inclusive one. The AMD Athlon (from the Thurderbird architecture) had an exclusive L2 (LLC), while its rival at the time, the Pentium 4 (from Willamette) [16] had inclusive L2 (LLC). Currently, the latest AMD Zen architecture has a (mostly) exclusive L3. Current Intel processors like Sandy Bridge, Ivy Bridge and Skylake have an inclusive L3 and a non-inclusive L2 [17]. The Intel Knights Landing has an

|             | Inclusive              | Non-inclusive     | Exclusive         |

|-------------|------------------------|-------------------|-------------------|

| Data        | $\uparrow$             | <b>†</b>          | None              |

| replication |                        |                   |                   |

| Benefits    | Simple coherence,      | Simple to         | Highest effective |

|             | no copy back necessary | implement         | capacity          |

| Drawback    | Wastes cache space,    | Data replication  | More complex on   |

|             | back invalidations     | on a miss,        | an LLC hit        |

|             |                        | complex coherence |                   |

| Replacement | Core-aware problem     | Simple            | Heuristic problem |

| policies    |                        |                   | (no recency,      |

|             |                        |                   | frequency info)   |

Table 2.1: Inclusion policy properties.

L2 (LLC) that is inclusive of the L1D and non-inclusive of L1I [18].

The ARM Cortex-A9 can have an (optional) L2 cache(LLC). The core has support to be attached to exclusive L2 caches as long as that is properly configured both in the core and L2 controller sides [19].

The processors in the IBM POWER series had mostly L3 (LLC) exclusive caches. The POWER5 has an L3 exclusive and an L2 inclusive of both L1D and L1I [20]. The POWER6 has an L3 exclusive cache and the POWER7 has an L3 mostly exclusive cache [21]. The IBM zEC12 has an inclusive L3 (on die) and an inclusive L4 (off-die, on-package) [22].

## 2.3 Replacement Policies

To reduce the gap of memory and processor performance, computer architects designed caches to bring in-use data nearer the processor. One of the important design decisions in a cache is the replacement policies. Caching and replacement

policies have been researched in different fields such as systems [23, 24, 25, 26, 27] and databases. In this thesis we only consider caches in the memory system.

Cache replacement policies are algorithms to improve cache management. They are used when the cache is full and a new block has to be allocated: the algorithm chooses which block to evict from the cache to place the new one.

The best algorithm would be to evict a block that is no longer going to be used in the future. This is only possible with knowledge of the future. Belady proposed an optimal cache replacement algorithm assuming knowledge on the future [28]. As a processor does not have such knowledge, there has been plenty of work in cache replacement algorithms.

A naive algorithm would be to choose a block at random and replace it. This is easy to implement but not generally effective, as it evicts a block that me be in use. There has been plenty of work to improve this algorithm trying to evict the least useful data. One way to improve cache management would be to decide based on how recently the block has been accessed, like least recently used (LRU). Another way is using machine learning to learn from the past accesses and make a prediction of which blocks will likely be accessed again.

Cache blocks can be accessed in many different patterns. A technique that has been used to adapt cache management to different patterns depending on the application is set dueling [29]. Set dueling uses different replacement policies on a few cache sets and compares their performance. The best replacement policy across the compared sets is used for the rest of the cache.

A replacement policy can maintain information on the blocks to later decide which block to evict. There are two main cache operations that trigger actions in a replacement policy: the placement (or insertion) of a new block into the cache, and the promotion (or update) of an existing cache block. On placement, the replacement policy can statically or dynamically decide the initial value of the information to keep with the inserted block. If the cache if full, the placement also triggers the replacement algorithm to choose which cache block to evict. A cache hit typically triggers a promotion of the accessed block. Usually, the replacement policy will mark the block to be more protected of eviction than it was before. The replacement policy can also implement a bypass policy. This means that the cache block that was going to be placed in the cache might be predicted not to be used before its eviction. In that case, the block is considered dead and it is not placed in the cache, but forwarded to the next level.

## 2.3.1 LRU

The least recently used (LRU) is a simple and intuitive replacement policy that is often used as a baseline to compare other policies. This replacement policy evicts the cache block that has not been used for the longest time. This policy has been implemented to exploit temporal locality, given that a block that has been used recently is likely to be reused soon. However, that is not always the case. Some applications do not have such high temporal locality, for example, a large data set that does not fit in the cache and it is accessed many times from the first to the last element. In that case, by the time the first element is accessed again, it would have been evicted from the cache as it was the least recently used block.

The LRU policy keeps the information per block on the order that the blocks of a set had been accessed. For example, in an 8-way set associative cache, the blocks will be ordered from zero to seven, being zero the most recently used position and seven the least. The placement of a block in the cache is set to position zero because is the block that has just been accessed. On a cache hit, for example, to a block in position four, the block is also set to position zero. All other blocks' positions are

recalculated. On a fill that triggers the replacement of a block, the victim block will be the one in the LRU position, position 7 in this example.

This replacement policy requires to store a considerable amount of bits per block and to recalculate the position and update it for each cache block in a set. This is very costly. For this reason, an approximation of this replacement policy has been proposed: the Pseudo-LRU (PLRU). PLRU is commonly implemented as a tree making the number of bits to store and modify to be small. PLRU is beneficial compared to LRU for large cache associativities. There are many other heuristics around the access recency or frequency such as most recently used, not recently used, least frequently used, not frequently used.

#### 2.4 Prefetchers

Cache misses are a common reason for CPU stalls in computers. Prefetching, in conjunction with other techniques, such as replacement policies, is one effort to to reduce these stalls by predicting misses and issuing a memory request before the actual access occurs. Prefetching is a technique used to hide memory latency by bringing data that will potentially be needed by the processor to a closer level of the memory hierarchy. Prefetching can be done either for instructions or for data. Also, it can be implemented in hardware, software or a combination of both. There is, however, the risk of polluting the cache when the prefetched data is not used due its eviction before use or wrong prediction.

There are several prefetching approaches proposed in the literature contained in two categories: hardware and software. Software prefetching consists in adding instructions to the program to fetch data ahead of its use. They do not speculate on data but add instruction overhead. Contrarily, hardware schemes do not require programmer or compiler intervention and incur no instruction overhead. However, they may mispredict the next data to be accessed causing cache pollution and additional traffic and power consumption.

Hardware prefetching can be classified in two categories: spatial and temporal. Spatial schemes use accesses to the current blocks as the basis for prefetch decisions. Temporal schemes use lookahead decoding of the instruction stream to decide what and when to prefetch [30]. Due to the greater complexity of the data access pattern compared to instructions, data prefetching techniques are more diverse and thoroughly researched than instruction prefetching techniques.

There are three main types of hardware prefetching: address correlated, spatially correlated and execution based. Address correlated prefetching relies on identifying address correlations of previous misses. These prefetchers predict that a sequence of accesses happening close in time are likely to be accessed together in the future. These prefetchers work well to exploit the patterns of algorithms that traverse data structures such as linked lists.

The spatially correlated prefetching exploits the regularity and repetition in data layout. Data structures and objects have a fixed layout in memory and is frequently aligned to cache lines. The same layout patterns are often similar for other objects in memory. The regularity of the layouts and the reusability of the patterns makes this prefetching technique effective also to reduce cold misses. One common special case is the sequential and stride prefetching. Stride prefetchers exploit the spatial locality by prefetching, for example, the next contiguous block. These prefetchers can be tuned to work for a different stride (e.g. instead the next block, the fourth next block) and to identify multiple strides.

The execution-based prefetching executes the program's memory accesses ahead of the actual execution so data is brought closer ahead of time. Execution-based prefetching seek to access earlier the exact addresses that are going to be accessed

later. It does not speculate to decide which addresses to prefetch. Prefetches are known to be useful because the program had already executed or will execute them in the future. This is achieved by using spare resources to execute future instructions or by adding extra hardware to the memory hierarchy to monitor which of the evicted addresses might be needed.

In the rest of this section, the prefetchers used in our experiments are described.

## 2.4.1 Next-Line

The code is stored sequentially in memory and many instructions are accessed consecutively. This prefetcher exploits these two characteristics and simply brings the cache line that is stored after the one that has been accessed. Next-line is a prefetching technique for bringing the next consecutive cache block [31]. This prefetcher works specially well for instructions, but also for applications with high spatial locality.

This prefetching technique has been extended to a variable number of cache lines to be prefetched. In terms of instructions, it can be adapted to recognize and prefetch entire basic blocks.

#### 2.4.2 Instruction Pointer-Based Stride

Stride prefetchers aim to remove compulsory and capacity misses. These prefetchers predict that, when an access to a memory address is missed, another memory access to an address that is the same plus an offset will be likely accessed and missed in the future. Stride prefetchers generate a cache allocation of the predicted block. If the block is prefetched and accessed (hits), it is a useful prefetch. Therefore, stride prefetchers are not only configured to prefetch on miss but also to prefetch on hit.

This pattern is usually regular within the multiple execution of the same static instruction. For this reason, stride prefetchers are typically implementated to track information per instruction pointer (PC). The tracked information includes the next address to be prefetched and the identified stride [32]. They also typically include a degree and distance. The degree is how many prefetchers an access by the instruction at the corresponding PC triggers, and distance is how far ahead it starts prefetching, i.e., a distance of one would prefetch address + stride, while a prefetch distance of N would prefetcher  $address + (N \times stride)$ .

## 2.4.3 Best-Offset

Offset prefetching is a generalization of the next-line prefetcher, where an offset can be specified. In next-line, the offset would be one. But bringing the immediate next line is not always the best case for all applications. The access patterns can be different and, therefore, dynamically adjusting the best offset improves the usefulness of the prefetcher. Another problem is timeliness. Prefetching a block late may still improve performance but in a smaller scale. Bringing a block with a higher offset may guarantee that the prefetch arrives on time.

Michaud proposed the Best-Offset Hardware Prefetching [33] (BOP) to solve these two problems. He implemented a learning algorithm that tries different offsets and uses the best. BOP has a table to store the base address of the recent prefetched requests that BOP tried (recent requests table or RR) plus an offset list and a score table. During the learning phase, BOP tests an offset and updates the score for some L2 read accesses depending whether it was a hit or a miss in the recent requests table. Whenever all offsets in the list have been tested, they start again until a certain number of iterations of this process. The offset with the highest score is the one chosen.

# 2.4.4 DRAM-Aware Access Map Pattern Matching

Dynamic RAM (DRAM) is a type of memory cheaper than the one used for caches, so it is typically used for a larger capacity. The main application of DRAM is the computer's main memory, which is the memory that is between storage and the cache hierarchy. The DRAM is divided in multiple banks, which can be accessed in parallel. Each bank is composed of many rows. Whenever a row has to be read or written, the row has to be activated and brought to a row buffer. The read or write operations are done to the row buffer. The latest DDR devices limit the number of activations during a time window. Optimizing the use of the row buffer will improve performance if the limit is not enough.

One problem of prefetching techniques in DRAM is that when two cores are prefetching different blocks, if those accesses go to the same DRAM bank, they will be activating and deactivating the row buffer, resulting in ping-pong effect that prevents any of the cores being able to enjoy row buffer locality. This is in contrast to the case where one of the cores sends the prefetches alone and all those prefetchers accessing the same row get row buffer hits. If those prefetches are interleaved with prefetchers from other core to the same bank but different rows, those row buffer hits will become row buffer misses given the interference between the different core's prefetchers.

Ishii et al [34] proposed a prefetching technique to exploit locality in DRAM called DRAM-aware access map pattern matching (DAAMPM). Before the time the prefetch is going to be used, they suggest to wait and reorder the prefetch requests to optimize row activation. The prefetches are reordered in a way that all blocks that need to access the same row are done together. To implement this, they maintain a memory access map data structure that tracks memory locations accessed in the

recent past.

Another problem they identify is that many replacement policies are not aware about which blocks in the cache are allocated by prefetches or by demands. Most replacement policies promote a block on a hit to protect it from being evicted. However, a prefetched block should not be considered as a hit the first time it is accessed in that context, otherwise we would be promoting all blocks that have been only used once and might be dead. A solution would be to add a prefetch bit per cache line that is set to one when the prefetched block is filled to the cache. Whenever there is a hit to that block, the replacement policy will not promote the block but will set the prefetch bit to zero. However, adding an additional bit to all cache blocks in the last level cache would be very costly. For this, the authors also propose a prefetch-aware cache line promotion [34] (PACP). The idea is that the core issuing a demand access after a prefetch includes a bit to specify that the accessed block should not be promoted, as it has only been accessed once after the prefetch.

#### 2.4.5 KPC

There has been extensive research in cache management, in both cache replacement policies and prefetchers. The efforts, however, have mainly been made separately. There has been little work on studying their interaction and their effect in each of the cache levels [34, 35, 36]. Those studies show that the benefit of replacement policies can be small or negative when combined with a prefetcher.