# PRINCIPLED APPROACHES TO LAST-LEVEL CACHE MANAGEMENT

A Dissertation

by

# ELVIRA TERAN

# Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

| Chair of Committee, | Daniel A. Jiménez |

|---------------------|-------------------|

| Committee Members,  | Nancy M. Amato    |

|                     | Eun Jung Kim      |

|                     | Paul Gratz        |

| Head of Department, | Dilma Da Silva    |

August 2017

Major Subject: Computer Science

Copyright 2017 Elvira Teran

#### ABSTRACT

Memory is a critical component of all computing systems. It represents a fundamental performance and energy bottleneck. Ideally, memory aspects such as energy cost, performance, and the cost of implementing management techniques would scale together with the size of all different computing systems; unfortunately this is not the case. With the upcoming trends in applications, new memory technologies, etc., scaling becomes a bigger a problem, aggravating the performance bottleneck that memory represents. n A memory hierarchy was proposed to alleviate the problem. Each level in the hierarchy tends to have a decreasing cost per bit, an increased capacity, and a higher access time compared to its previous level. Preferably all data will be stored in the fastest level of memory, unfortunately, faster memory technologies tend to be associated with a higher manufacturing cost, which often limits their capacity. The design challenge is, to determine which is the frequently used data, and store it in the faster levels of memory.

A cache is a small, fast, on-chip chunk of memory. Any data stored in main memory can be stored in the cache. For many programs, a typical behavior is to access data that has been accessed previously. Taking advantage of this behavior, a copy of frequently accessed data is kept in the cache, in order to provide a faster access time next time is requested. Due to capacity constrains, it is likely that all of the frequently reused data can not fit in the cache, because of this, cache management policies decide which data is to be kept in the cache, and which in other levels of the memory hierarchy. Under an efficient cache management policy, a encouraging amount of memory requests will be serviced from a fast on-chip cache.

The disparity in access latency between the last-level cache and main memory motivates the search for efficient cache management policies. There is a great amount of recently proposed work that strives to utilize cache capacity in the most favorable to performance way possible. Related work focus on optimizing the performance of caches focusing on different possible solutions, *e.g.* reduce miss rate, consume less power, reducing storage overhead, reduce access latency, etc.

Our work focus on improving the performance of last-level caches by designing policies based on principles adapted from other areas of interest. In this dissertation, we focus on several aspects of cache management policies, we first introduce a space-efficient placement and promotion policy which goal is to minimize the updates to the replacement policy state on each cache access. We further introduce a mechanism that predicts whether a block in the cache will be reused, it feeds different features from a block to the predictor in order to increase the correlation of a previous access to a future access. We later introduce a technique that tweaks traditional cache indexing, providing fast accesses to a vast majority of requests in the presence of a slow access memory technology such as DRAM.

# DEDICATION

A mi madre, mi padre, mi hermana y mi hermano, que por los mil caminos que he tomado en esta vida, en todos me han seguido y apoyado.

#### ACKNOWLEDGMENTS

I would first like to express my deepest gratitude to my doctoral advisor Dr. Daniel A. Jiménez, not only for convincing me to pursue a graduate degree, but also guiding me through the process, until the very end. All of the work achieved during these years would have not been possible without your help, guidance, and indescribable amount of patience towards me. You believed in me in times when I did not believed in myself, and for that I will always be grateful.

I would like to thank my co-authors, Yingying Tian, Zhe Wang, Jinchun Kim, Dr. Paul Gratz, Chris Wilkerson and Zeshan Chishti, for all their help in the collaboration of several research projects and the knowledge they shared with me.

To my family, I have no words to thank you for all the support you provided me. To the friends I gained through these years at school, thank you for always backing me up when times got tough.

#### CONTRIBUTORS AND FUNDING SOURCES

# Contributors

This work was supported by a dissertation committee consisting of Professors Daniel A. Jiménez, Nancy M. Amato, Eun Jung Kim of the Department of Computer Science and Engineering and Professor Paul Gratz of the Department of Electrical and Computer Engineering.

Chapter 3 and 4 were a collaboration with Yingying Tian and Zhe Wang while they were students at Texas A&M University. Chapter 5 was a collaboration with Chris Wilkerson, Zeshan Chishti and Zhe Wang of Intel Labs.

All other work conducted for the dissertation was completed by the student independently.

# **Funding Sources**

This work was funded in part by National Science Foundation grants CCF-1216604/1332598 and CCF-1649242, as well as a gift from Intel Corporation.

# TABLE OF CONTENTS

| I                                                                                                                                                                                | Page             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| BSTRACT                                                                                                                                                                          | ii               |

| EDICATION                                                                                                                                                                        | iv               |

| CKNOWLEDGMENTS                                                                                                                                                                   | v                |

| ONTRIBUTORS AND FUNDING SOURCES                                                                                                                                                  | vi               |

| BLE OF CONTENTS                                                                                                                                                                  | vii              |

| ST OF FIGURES                                                                                                                                                                    | X                |

| ST OF TABLES                                                                                                                                                                     | xiii             |

| INTRODUCTION                                                                                                                                                                     | 1                |

| <ul> <li>1.1 Multi-level Cache Hierarchy</li> <li>1.2 Last-level Cache Management Policies</li> <li>1.3 Dissertation Statement</li> <li>1.4 Dissertation Organization</li> </ul> | 1<br>2<br>2<br>3 |

| RELATED WORK                                                                                                                                                                     | 4                |

| 2.1Placement and Promotion Decision2.1.1Dynamic Placement2.1.2Placement and Promotion Vectors                                                                                    | 4<br>4<br>4      |

| 2.2 Reuse Prediction       2.2.1 Re-reference Interval Prediction         2.2.2 Dead Block Prediction       2.2.2 Signature-Based Hit Prediction                                 | 5<br>5<br>5<br>6 |

| <ul> <li>2.2.5 Signature-Based Fitt Frediction</li></ul>                                                                                                                         | 7<br>7<br>7      |

| 2.4       DRAM Last-Level Caches         2.4.1       Tag Optimizations for DRAM LLCs                                                                                             | 7<br>8           |

| 2.4.2 Access Latency Optimization for Direct-Map DRAM Caches MINIMAL DISTURBANCE PLACEMENT AND PROMOTION                                                                         | 8<br>10          |

| ,    | 3.1 | Introdu | ction                                    | )  |

|------|-----|---------|------------------------------------------|----|

| ,    | 3.2 | Motiva  | tion                                     | ;  |

|      |     | 3.2.1   | Policy Based on Binary Trees             | ;  |

|      |     | 3.2.2   | PseudoLRU Disturbs Non-Promoted Blocks   | 5  |

| ,    | 3.3 | Design  |                                          | 1  |

|      |     | 3.3.1   | Minimal Disturbance Placement            | 1  |

|      |     | 3.3.2   | Minimal Disturbance Promotion            | ,  |

|      |     | 3.3.3   | Dynamic MDPP                             | )  |

| ,    | 3.4 | Evaluat | tion                                     | )  |

|      |     | 3.4.1   | Methodology                              | 2  |

|      |     | 3.4.2   | Overhead Analysis                        | 5  |

|      |     | 3.4.3   | Results for Static Policies              | 5  |

|      |     | 3.4.4   | Results for Dynamic Policies             |    |

|      |     | 3.4.5   | Analysis                                 | ;  |

| ,    | 3.5 | Summa   | 1ry                                      | ŀ  |

|      |     |         |                                          |    |

| 4.   | PER | CEPTRO  | ON LEARNING FOR REUSE PREDICTION    35   | )  |

| 4    | 4.1 | Introdu | ction                                    | 5  |

|      |     |         | Better Accuracy with Perceptron Learning |    |

| 4    | 4.2 |         | 40                                       |    |

|      |     | 4.2.1   | Perceptron Learning for Reuse Prediction |    |

|      |     | 4.2.2   | Predictor Organization                   |    |

|      |     | 4.2.3   | Replacement and Bypass Optimization      |    |

| 4    | 4.3 |         | tion                                     | 1  |

|      |     | 4.3.1   | Methodology                              | 1  |

|      |     | 4.3.2   | Overhead Analysis                        | )  |

|      |     | 4.3.3   | Features and Parameters                  | ł  |

|      |     | 4.3.4   | Results for Multi-Core                   | 5  |

|      |     | 4.3.5   | Results for Single-Core                  | 1  |

|      |     | 4.3.6   | Alternative Metrics                      | ;; |

|      |     | 4.3.7   | Analysis                                 |    |

| 4    | 4.4 | Summa   | ury                                      | ;  |

|      |     |         |                                          |    |

| 5. ] | LOW | /-COST  | ASSOCIATIVITY FOR DRAM CACHES            | ŀ  |

|      | 5.1 | Introdu | ction                                    | 1  |

|      | 5.2 |         | tion                                     |    |

|      | 5.4 | 5.2.1   | Importance of Associativity   68         |    |

|      | 5.3 |         |                                          |    |

|      |     | 5.3.1   | Just-In-Time Associativity               |    |

|      |     | 5.3.2   | JITA Cache Organization                  |    |

|      |     | 5.3.3   | Accessing the JITA Cache                 |    |

|      |     | 5.5.5   | Accessing the JTTA Cache                 | r  |

|    | 5.4  | Evalua  | tion      |       |     |     |    |     |   |     |   |     |     |   | • |       |   | • |   |   | • | • | • |   | 79 |

|----|------|---------|-----------|-------|-----|-----|----|-----|---|-----|---|-----|-----|---|---|-------|---|---|---|---|---|---|---|---|----|

|    |      | 5.4.1   | Methodo   | ology | •   |     |    | •   |   |     |   |     |     |   | • | <br>• |   | • |   |   |   |   | • |   | 80 |

|    |      | 5.4.2   | Results   |       |     |     |    | •   |   |     |   |     |     |   | • | <br>• |   | • |   |   |   |   | • |   | 81 |

|    |      | 5.4.3   | Analysis  |       |     |     |    | ••• |   |     |   |     |     |   | • | <br>• | • | • |   |   |   | • | • |   | 83 |

|    | 5.5  | Summa   | ary       |       |     |     | •  | •   |   |     | • | •   | •   |   | • | <br>• | • | • | • |   |   | • | • | • | 86 |

| 6. | SUM  | IMARY   | AND CO    | DNCI  | LUS | SIO | NS |     | • |     |   | •   |     |   | • |       | • | • |   |   |   | • | • | • | 87 |

|    | 6.1  | Contril | outions . | •••   |     |     |    | •   |   | • • | • | • • | • • | • | • | <br>• | • | • | • | • | • | • | • | • | 87 |

| RE | FERE | ENCES   |           |       |     |     |    | •   |   |     |   |     |     |   |   |       |   | • |   |   |   |   |   | • | 89 |

# LIST OF FIGURES

| FIGURI | Ē                                                                                                                                                                                                                            | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.1    | Average change in position caused by a promotion for the non-promoted blocks                                                                                                                                                 | 11   |

| 3.2    | The nodes in an example PseudoLRU tree arranged in ascending order of node number showing the labels guiding replacement policy                                                                                              | 14   |

| 3.3    | Regions of Protection in the PseudoLRU Tree                                                                                                                                                                                  | 19   |

| 3.4    | Average change in recency stack position for LRU, PseudoLRU, and MDPP Cache                                                                                                                                                  | 20   |

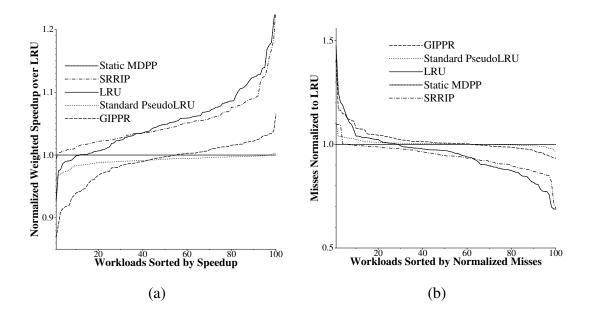

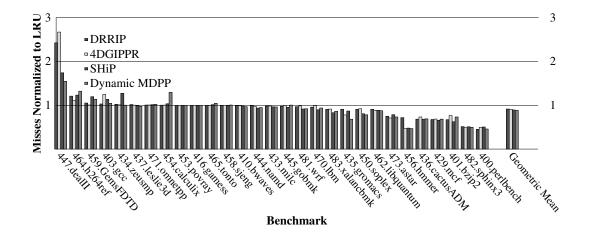

| 3.5    | (a) Normalized Weighted Speedup over LRU for Static Policies on 8-core Workloads, and (b) Misses Normalized to LRU for Static Policies                                                                                       | 27   |

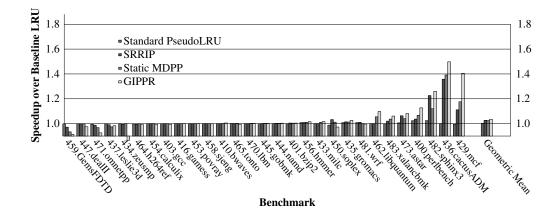

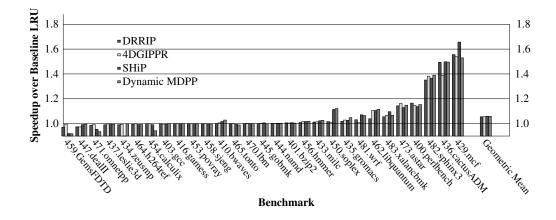

| 3.6    | Speedup over LRU for Static Policies on Single-Threaded Workloads                                                                                                                                                            | 28   |

| 3.7    | Misses Normalized to LRU                                                                                                                                                                                                     | 28   |

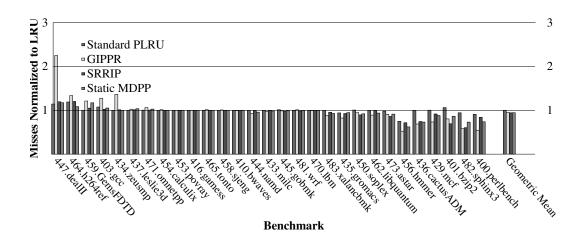

| 3.8    | (a) Normalized Weighted Speedup over LRU for Dynamic Policies on 8-<br>core Workloads, and (b) Misses Normalized to LRU for Static Policies                                                                                  | 30   |

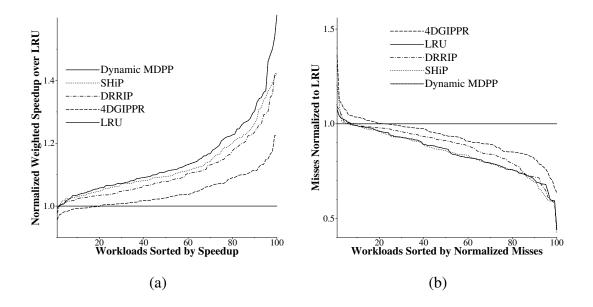

| 3.9    | Speedup over LRU for Dynamic Policies on Single-Threaded Workloads .                                                                                                                                                         | 31   |

| 3.10   | Misses for the Dynamic Policies Normalized to LRU                                                                                                                                                                            | 32   |

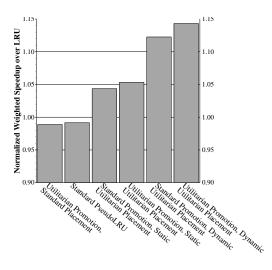

| 3.11   | Contributions of minimal disturbance promotion and static/dynamic mini-<br>mal disturbance placement                                                                                                                         | 33   |

| 4.1    | Violin plots for false positive (darker) and coverage (lighter) rates. Per-<br>ceptron learning is significantly more robust, with higher coverage, fewer<br>false positives, and less variance in accuracy across workloads | 36   |

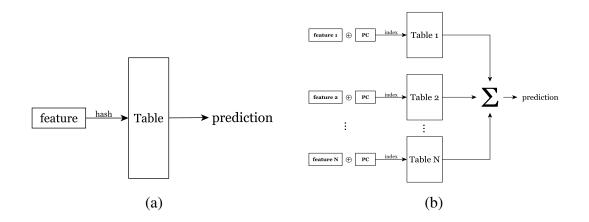

| 4.2    | (a) Previous PC-based Reuse Predictors and (b) Perceptron-based Reuse Predictor                                                                                                                                              | 38   |

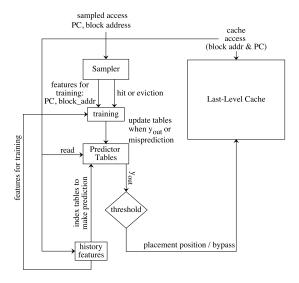

| 4.3    | Datapath from extracting features from an access, to making a prediction and acting on it                                                                                                                                    | 41   |

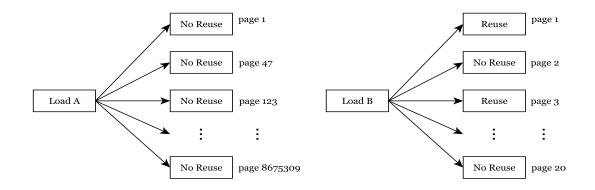

| 4.4  | Two different kinds of correlation. The PC of one load (left) always corre-<br>lates with no reuse on thousands of pages, while another load (right) has no<br>correlation through the PC but does have correlation through page number.                                                                                      | 42 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

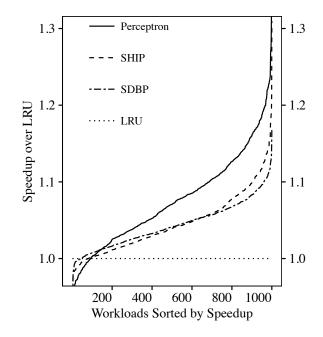

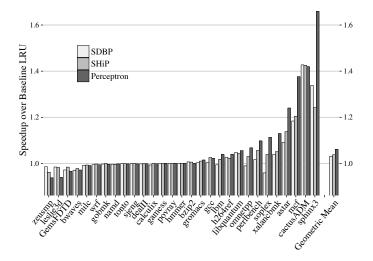

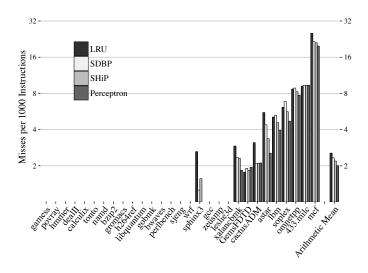

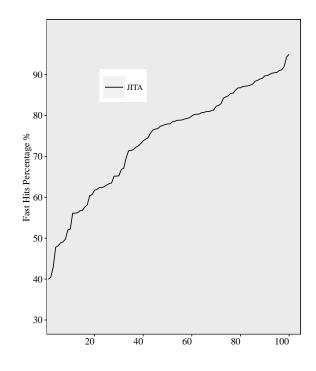

| 4.5  | Normalized Weighted Speedup over LRU for 8-Core Multi-Programmed<br>Workloads                                                                                                                                                                                                                                                 | 55 |

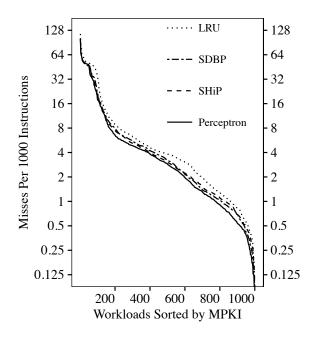

| 4.6  | Misses per 1000 Instructions for 8-Core Multi-Programmed Workloads                                                                                                                                                                                                                                                            | 57 |

| 4.7  | Speedup over LRU for Single-Thread Workloads.                                                                                                                                                                                                                                                                                 | 60 |

| 4.8  | Misses per 1000 Instructions for Single-Thread Workloads                                                                                                                                                                                                                                                                      | 61 |

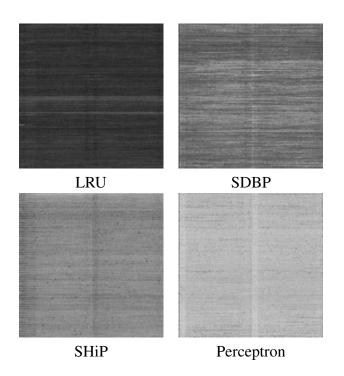

| 4.9  | Heat map of cache efficiency in cache sets for the various techniques on<br>a typical multi-programmed workload. Darker signifies poor efficiency<br>while lighter means better efficiency.                                                                                                                                   | 62 |

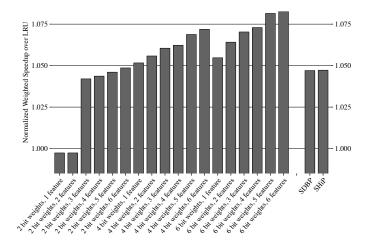

| 4.10 | Cumulative impact of increasing numbers of features and weight widths                                                                                                                                                                                                                                                         | 62 |

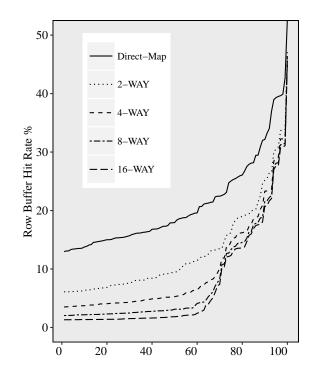

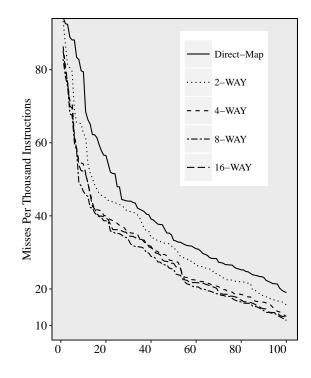

| 5.1  | Row-buffer hit rates for one hundred randomly chosen eight-core mixes.<br>The mixes on the x-axis are sorted in increasing order of row-buffer hit rate                                                                                                                                                                       | 68 |

| 5.2  | Misses per thousand instructions for one hundred randomly chosen eight-<br>core mixes. The mixes on the x-axis are sorted in increasing order of MPKI                                                                                                                                                                         | 69 |

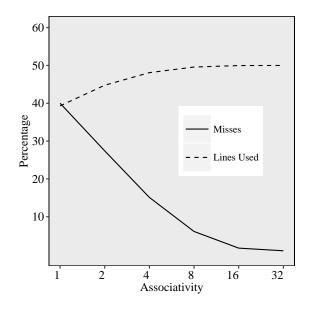

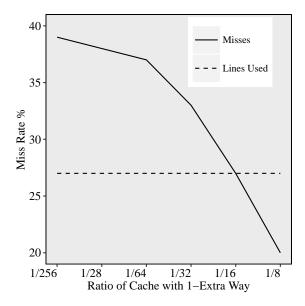

| 5.3  | Percentage of accesses that miss in the cache, as well as the percentage of total lines in the cache that were used for a 64MB cache running a workload that repeatedly scans a 32MB working set.                                                                                                                             | 70 |

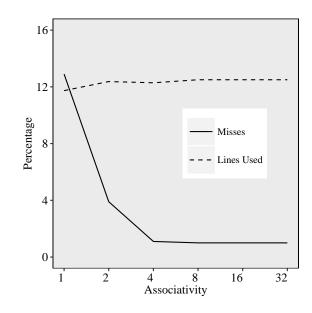

| 5.4  | Percentage of accesses that miss in the cache, as well as the percentage of total lines in the cache that were used for a 256MB cache running a workload that repeatedly scans a 32MB working set.                                                                                                                            | 71 |

| 5.5  | Percentage of the cache where we need associativity.                                                                                                                                                                                                                                                                          | 72 |

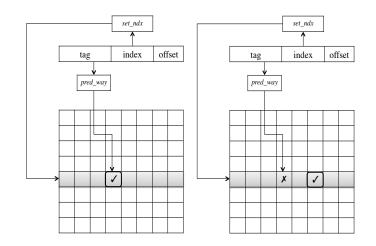

| 5.6  | On the left, we illustrate a fast hit, the requested data is in fact is in the pre-<br>dicted way. To right of the figure we can observe a slow hit, the requested<br>data is no located on its corresponding static position, but does reside and<br>in the cache and is accessed paying a somewhat more costly access time. | 75 |

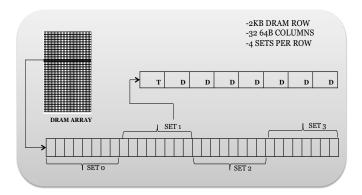

| 5.7  | 2KB DRAM row containing four cache sets, for each set, we allocate its corresponding tags in a 64B block, followed by seven 64B blocks filled with data                                                                                                                                                                       | 75 |

| 5.8  | JITA's insertion policy.                                                                                                                                                                                                                                                                                                      | 78 |

|      |                                                                                                                                                                                                                                                                                                                               |    |

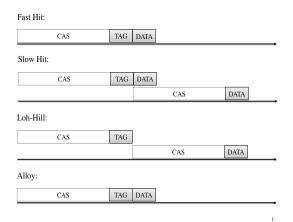

| 5.9  | Different access latencies for each policy.                                                                              | 79 |

|------|--------------------------------------------------------------------------------------------------------------------------|----|

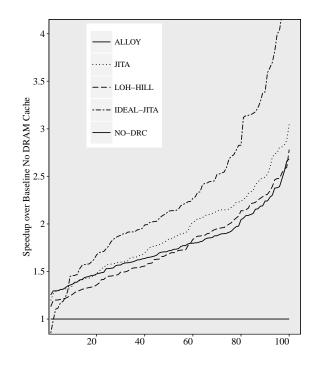

| 5.10 | Normalized Weighted Speedup over baseline no DRAM cache for 8-Core<br>MultiProgrammed Workloads                          | 81 |

| 5.11 | Misses per 1000 Instructions for 8-Core Multi-Programmed Workloads                                                       | 84 |

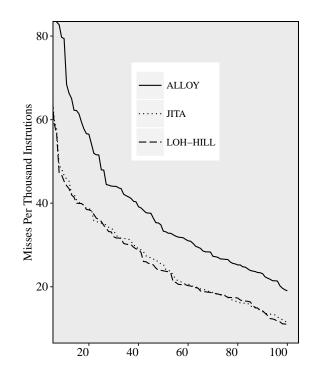

| 5.12 | Fast hits percentage for each of the 100 eight core mixes. Percentages are sorted in an increasingly order on the x-axis | 85 |

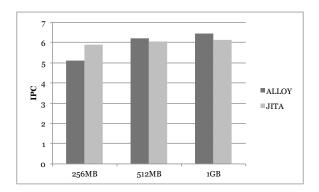

| 5.13 | Average IPC for 100 eight-core mixes for different cache sizes                                                           | 85 |

# LIST OF TABLES

TABLE

| 3.1 | Minimal Disturbance promotion for 16-way associativity                                                                                     | 15 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Overhead required by the various techniques                                                                                                | 23 |

| 4.1 | Overhead required by the various techniques is approximately the same in our experiments. See text for details of sampler entry overheads. | 50 |

Page

#### 1. INTRODUCTION

To this day, memory latency continues to be a critical performance bottleneck. For years, processor speeds continued to constantly increase, while memory speeds failed to keep up. In order to alleviate the cost of memory latency, computer architects proposed the idea of a multi-level memory hierarchy, where each level design is chosen by comparing the trade-offs between speed, capacity, manufacturing costs, and others.

#### 1.1 Multi-level Cache Hierarchy

Starting from the memory hierarchy level that is physically the closest to the core, the trend appears to be, to sacrifice capacity for better access latency compared to the next level in the hierarchy. On-chip memory is referred to as caches. A cache can be define as a small fast memory, which goal is, to store only data that is frequently accessed.

The most significant gap in memory speeds between two consecutive levels in the memory hierarchy appears in between the last level cache (LLC) located on-chip and main memory located off-chip. For many years, the rule of thumb was, where this scenario consisted of an SRAM LLC, and DRAM technology for main memory, however, with emerging Non-Volatile Memory (NVM) technologies, architects have proposed adding an on-chip DRAM LLC to the hierarchy, as a cost effective way to replace DRAM as main memory. Each of the different technologies ingrain in different challenges, SRAM is the most access-latency efficient technology, unfortunately it's manufacturing cost, and density makes it unfeasible to satisfy these days huge capacity requirements. DRAM has been the one solution for capacity problems for years, but DRAM access-latency is higher than desired. New trends in technology appeal to be a manufacturing cost-efficient solution for main memory, but the savings come with the price of paying an even higher access latency than that of DRAM. Due to the attractive potential benefits that can be

obtained from LLCs, many researches in the field have proposed a wide variety of policies to obtain optimize the performance of LLCs, all with the solely purpose of managing cache content in most favorable to performance way possible [1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27]. Despite the amount of efforts in the research, today there is still room to bridge the performance of the state-of-the-art policy and that of an unfeasible optimal technique. The very best performance of a cache will happen when every single memory request can be served from an on-chip cache, and accessing the slow main memory is avoided at all cost. However, in order for this to happen, data would have to be fetch to the cache before the core requests it, and in order to make this possible, knowledge of the future is required, making this approach unfeasible. The goal of architects is to design better management policies such that their performance come as close as possible to the performance of an optimal policy.

#### **1.2 Last-level Cache Management Policies**

The effectiveness of the management policy translates directly into an overall better system performance. Because of the limited capacity of the LLC, and the constant growth of memory requests from current applications, very often, it becomes not possible to fit the application's working set in the LLC. Policies must make the decision to evict some of the residing data in the LLC, in order to make room for the new requested data. There are several other management decisions policies cover, in these dissertation, we present several policies that focus on tackling different challenges that are present in LLCs.

#### **1.3 Dissertation Statement**

The performance and efficiency of last-level caches can be improved by applying principles of machine learning and other areas of research to intelligent last-level cache management policies.

#### **1.4 Dissertation Organization**

In this dissertation we present three novel management policies that are designed to overcome some difficulties that are present in current memory systems, as well as preparing for the challenges that upcoming memory technologies represent. Our proposed work is characterized by the idea of following principles found in machine learning and other areas of interest. We demonstrate that by adapting this principles to cache management, we are able boost performance, save storage overhead, and further reduce access latency.

For the following chapters, in order to put our work into perspective, we will first introduce some of the most relevant related work. Following, each of the proposed mechanism will be introduced, first stating the background and motivation that lead up to this work. Each technique will then be introduced in detail, followed by articulating the methodology and results we obtained. In Chapter 3, our Minimal Disturbance Placement and Promotion policy is introduced, following the same intuition as that of the minimal disturbance principle found in neural networks, we were able to optimize the compelling storage overhead saving tree-based PseudoLRU technique, yielding the same performance as the state-of-the-art technique, while requiring a fraction of the storage overhead. Chapter 4 proposes an accurate reuse predictor policy, it is able to highly accurately predict whether a block in the LLC will be reused again before it is evicted. The predictor is inspired by neural networks, and trained following the perceptron learning rule. It provides the predictor with an extra kick of accuracy and a reduces the training period for application with changing behavior phases. Chapter 5 is used to describe a policy that provides affordable access-latency in the presence of a set-associative DRAM cache, with essentially the high hit-rate associativity delivers. Finally, Chapter 6 gives a conclusion of the work done and presented in this dissertation.

#### 2. RELATED WORK

Our work builds on the contributions of many other researchers to the field. To place our work in the context of other research, we now review some of the most recent related work.

#### 2.1 Placement and Promotion Decision

Each reference block has a last reference during the execution of an application, for several of the blocks the first reference might be the last reference. The placement and promotion of a block should be accordingly to their reuse.

## 2.1.1 Dynamic Placement

The Least Recently Used (LRU) policy places blocks into the Most Recently Used (MRU) position. Qureshi *et al.* observe that changing the placement position to LRU sometimes results in an improvement as blocks that are no re-referenced after being brought to the cache, are quickly eliminated avoiding these blocks to pollute the cache [28]. The authors of this work propose dynamic insertion policy (DIP) that determines at run-time whether LRU or MRU placement works best for a particular workload. Jaleel *et al.* propose a thread-aware version of DIP, TADIP [13] that improves over DIP as well as previous thread-aware cache management policies. Khan and Jiménez propose decision tree analysis for choosing from a wider range of placement positions [14].

#### 2.1.2 Placement and Promotion Vectors

Genetic Insertion and Promotion for PseudoLRU Replacement (GIPPR) uses genetic algorithms to find *insertion and placement vectors* (IPVs) for tree-based PseudoLRU [22]. The vectors assign the placement position for new blocks as well as the position to which a block in a given original position should be promoted. A single vector does not generalize well to different workloads, so in this work the authors propose to supply the policy with four vectors from which the best performing one is chosen at run-time using set-dueling. GIPPR begins with a blank slate on which the trace-driven genetic algorithm writes a novel placement and promotion drawn from an enormous search space. GIPPR work attempts to find the most favorable positions for blocks to be placed and promoted to.

## 2.2 Reuse Prediction

Much recent work on last-level cache replacement has focused on predicting whether and when a block will be re-referenced.

# 2.2.1 Re-reference Interval Prediction

Re-reference Interval Prediction (RRIP) categorizes blocks as near-immediate re-reference interval, intermediate re-reference intervals, and distant re-reference interval [12], associating these positions with cache blocks in a way roughly analogous to the positions in other replacement policies. Static RRIP (SRRIP) always places into the same position (*e.g.* distant re-reference interval) while Dynamic RRIP (DRRIP) uses set-dueling [29] to adapt the placement position to the particular workload. RRIP is a simple policy, requiring little overhead (2 or 3 bits per block) and no complex prediction structures, while resulting in significant improvement in performance. The intuition behind this policy is to allow incoming blocks to the cache to remain just the enough amount of time to be re-referenced again and promoted to a more favorable position, or in the opposite case, to be evicted quickly and allow the allocation of other blocks.

#### 2.2.2 Dead Block Prediction

Dead block predictors predict whether a block will be used again before it is evicted. There are numerous dead block predictors applied to a variety of applications in the literature [30, 31, 32, 33, 34, 35, 6, 16]. In some of our work, we take inspiration from the Sampling Dead Block Prediction (SDBP) of Khan *et al.* [16]. In this work, a *sampler* keeps partial tags of sampled sets. Three tables of two-bit saturating counters are accessed using a technique similar to a skewed branch predictor [36]. For each hit in the sampled set, the program counter (PC) of the relevant memory instruction is hashed into the three tables and the corresponding counters are decremented. For each eviction from a sampled set, the counters corresponding to the PC of the last instruction to access the victim block are incremented. For any access to the LLC, the predictor may be consulted by hashing the PC of the memory access instruction into the three tables and taking the sum of the indexed counters. When the sum exceeds some threshold, the accessed block is predicted to be dead. Tags in sampled sets are managed with true LRU and a reduced associativity, but the LLC may be managed by any policy. The paper applies dead block prediction to replacement and bypass, but in this work we use the predictor for determining placement position and bypass.

#### 2.2.3 Signature-Based Hit Prediction

Wu *et al.* [37] approach re-reference prediction from the opposite perspective of dead block prediction: rather than predict whether a block is dead, their signature-based hit predictor (SHiP) predicts the likelihood that a block will be hit again. This technique uses a table of 3-bit saturating counters indexed by a signature of the block, *e.g.* the memory instruction PC that caused the initial fill of the block. When a block with a given signature is hit, the counter associated with that signature is incremented. When a block with a given signature is evicted, the counter is decremented. The hit predictor is used to determine placement position for RRIP. When the counter corresponding to the signature of an incoming block exceeds some threshold, the block is predicted to have a "distant rereference interval," otherwise it is predicted to have an "intermediate re-reference interval." That work proposes an efficient sampling-based predictor where a small subset of cache

sets keep metadata such as signatures, and the predictor generalizes to the whole cache.

# 2.3 Machine Learning for Cache Management

#### 2.3.1 Perceptrons in Microarchitecture

Perceptron learning was proposed for predicting conditional branches [38]. In this work, a perceptron weights vector is selected by a hash of the branch address and its dot product with an input vector of branch history outcomes. If the product is at least 0, the branch is predicted as taken, otherwise it is predicted not taken. The weights are updated with the perceptron update rule: if the prediction is incorrect, or the dot product does not exceed some threshold magnitude, then the weights are incremented or decremented based on their correlation to the corresponding history bits.

Subsequent work on predicting branches with perceptron-like algorithms improved the latency of the operation by using history bits to generate indices into weights tables rather than as input to the dot product computation [39, 40, 41]. In some of our work we take this approach as well, using input features to index weights tables and updating the weights with perceptron learning.

#### 2.4 DRAM Last-Level Caches

With the increasing demands for memory capacity, on-chip stacked DRAM caches have been proposed, as the new last level cache that comes right before main memory, in order to improve the hierarchy performance [42, 43, 44, 45]. DRAM technology represent challenges that are often not an issue with SRAM, some proposed optimizations include: reducing the overhead of supporting tags, improving hit rate, and optimizing access latency, etc.

#### 2.4.1 Tag Optimizations for DRAM LLCs

Because of the large magnitude of DRAM caches, storing each corresponding tag from each of the cache blocks.

The Loh-Hill cache [47] was proposed to co-locate the tags and data in the same DRAM cache row. The request will read the tag first, then determine in which column the data resides and access it all with a row buffer hit access timing. Although the Loh-Hill cache reduces access latency compared to a naive scheme that places the tag and the data into different rows, accessing the tag still adds significant access latency to the critical path. The DRAM cache data may be accessed only after obtaining the tag and finding out the location of the data. Huang and Nagarajan[26] propose prefetching tags into a small on-chip SRAM tag cache. Requests with spatial locality are able to read tags from the fast on-chip tag cache. However, incorrectly prefetched tags to the tag cache incur in a significant bandwidth overhead. The Buffered Way Predictor (BWP) technique [48] has been proposed to predict the way number of the cache set where the data being requested is located. The data can be fetched from the DRAM cache according to the predicted way number, avoiding having to read in all tag from the set first. However, the key drawback of BWP is that it requires 6% of the SRAM cache capacity to store the way number of the DRAM cache data.

## 2.4.2 Access Latency Optimization for Direct-Map DRAM Caches

Qureshi and Loh[46] propose the Alloy Cache, a direct-mapped DRAM cache design. This work explores the trade-off between access latency and miss rate for DRAM caches. The Alloy cache proposed to prioritize access latency over miss rate for a DRAM cache. The technique co-locates tags and data in the same DRAM cache block so the tag and data can be streamed out in two back-to-back data bursts. It incorporates a Memory Access Predictor (MAP) to predict whether a request will hit in the DRAM cache or not. The prediction is used to guide whether to do a parallel or sequential access between the DRAM cache and main memory. The Alloy Cache sacrifices DRAM cache hit rate for a lower access latency, however, for workloads that significantly benefit from a set-associative cache design, the Alloy cache might degrade their performance.

#### 3. MINIMAL DISTURBANCE PLACEMENT AND PROMOTION \*

In this chapter, we introduce our work Minimal Disturbance Placement and Promotion (MDPP), a space-efficient replacement algorithm. MDPP builds upon a tree-based PseudoLRU technique, and guides the placement and promotion decisions following the *minimal disturbance* principle. MDPP is presented in a static and dynamic version. Static MDPP can match the state-of-the-art policies' performance, while dynamic MDPP outperforms previously proposed work.

# 3.1 Introduction

With the disparity between cache latency and memory latency, a replacement policy that reduces misses can significantly improve performance. Many replacement policies order blocks into distinct positions, choosing to replace the block in a least favorable position when there is a miss to a set. Positions are manipulated by the placement and promotion policies. The placement policy decides what the initial position of a block should be, while the promotion policy decides what the new position of a re-referenced block should be. To accommodate a block in a new position, often other blocks must change their positions. These changes can disturb non-referenced blocks, causing them to move closer to the least favorable position by an amount that may be out of proportion to their merit. Previous work focuses on what happens to the just-referenced block without regard to the the effect on the other, non-referenced blocks.

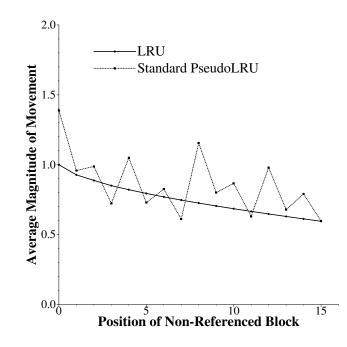

Figure 3.1 shows the average change in position of non-referenced blocks for two common replacement policies: least-recently-used (LRU) replacement policy as well as tree-based PseudoLRU over a set of 100 multi-core workloads described in Section 3.4.

<sup>\*2016</sup> IEEE. Reprinted, with permission, from E. Teran, Y.Tian, Z. Wang and D. Jiménez, "Minimal disturbance placement and promotion", April 2016

An evicted block travels one position beyond the maximum value, *i.e.* it moves out of the set. The LRU policy is relatively well-behaved, moving non-referenced blocks no more than one position and often less than one position when a block is promoted or placed. Tree-based PseudoLRU, a widely-used space efficient policy, moves blocks' positions much further than LRU, and the movement varies wildly with the non-referenced block's original position.

Figure 3.1: Average change in position caused by a promotion for the non-promoted blocks

In this work, we develop a replacement policy that reserves promotion privileges to blocks with an actual risk of being evicted, we found that promoting blocks that hold higher positions in the recency stack introduce unnecessary changes to all blocks' ordering, something we would like to avoid. Widrow and Lehr introduced the *minimal disturbance principle* applied to neural network learning that says: "Adapt to reduce the output error for the current training pattern, with minimal disturbance to responses already learned". Guided by this principle, we present a technique that only promotes referenced blocks when unprotected, meaning they are at risk of being evicted, it does not promote blocks protected from eviction, doing this we attempt to introduce the minimal disturbance to blocks in the set.

We apply this approach to tree-based PseudoLRU. The results are a simple static policy that significantly outperforms true LRU with less complexity, and a dynamic policy that outperforms the state-of-the-art on multi-core workloads. The dynamic MDPP Cache achieves a normalized weighted speedup of 11.0% on multi-core workloads over LRU while SHiP [37] achieves an 9.1% speedup.

This chapter describes the following contributions:

- We show that tree-based PseudoLRU is a disturbing policy. That is, it causes changes to the positions of non-referenced blocks that are out of proportion to those blocks' likelihood to be referenced again.

- 2. We introduce a static minimal disturbance placement and promotion policy for PseudoLRU. We describe the policy and show that it outperforms other static policies for single-threaded workloads and is competitive with other static policies for multi-core workloads. Because it builds on the space-efficient PseudoLRU policy, the MDPP has lower space overhead than previous recent work on replacement.

- 3. We introduce a minimal disturbance dynamic placement and promotion policy that adapts the placement policy to changing program behavior using dead block prediction resulting in dynamic MDPP. We show that this policy matches the performance of the state-of-the-art replacement policy single-threaded workloads with a

speedup of 5.9% over LRU, and exceeds the state-of-the-art performance for multicore workloads with a normalized weighted speedup of 11.0% over LRU.

## 3.2 Motivation

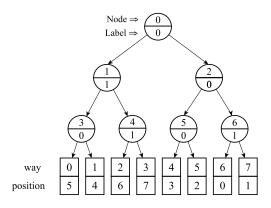

# 3.2.1 Policy Based on Binary Trees

PseudoLRU policies are based on providing an effect similar to the least-recently-used (LRU) policy, but with a more efficient representation. LRU orders blocks in a recency stack from most-recently-used (MRU) to least-recently-used, placing new blocks into the MRU position and evicting blocks from the LRU position. As blocks are reused, they are moved to the MRU position with all blocks previously ahead of the reused block shifted down the recency stack. At any point in the algorithm, each block has a distinct position in the recency stack. For an *n*-way set-associative cache, the positions are numbered 0 (MRU) through n - 1 (LRU).

The tree-based PseudoLRU replacement policy uses a binary tree to prioritize cache blocks [49]. The leaves of the tree are the indices of blocks (*i.e.* ways) in a set. The internal nodes are labeled with bits: 0 or 1. The internal nodes are represented as an array of bits with an implicit tree structure. There are n - 1 internal nodes in a binary tree with n leaves. Thus, tree-based PseudoLRU is space efficient since it requires only n - 1 bits per set compared with  $n \log_2 n$  bits per set for LRU.

#### PseudoLRU Replacement

On replacement, the victim block is chosen by tracing a path from the root of the tree to a leaf block. At each internal node, if the label is one, then the next node on the path is the right child of the current node; otherwise, it is the left child.

# **PseudoLRU Placement and Promotion**

When a block is placed or re-referenced, it is promoted. The bits along the path from the root to the associated leaf are modified such that the replacement algorithm would

Figure 3.2: The nodes in an example PseudoLRU tree arranged in ascending order of node number showing the labels guiding replacement policy

choose to go in the opposite direction from the leaf. That is, for all the nodes along a path from root to leaf, if the leaf is in the left subtree of the current node, then the bit in that node is changed to 1, otherwise the bit is changed to 0. Thus, among all blocks in the set, the promoted block receives the most protection from being evicted.

# Protection

We can formalize the notion of protection in a PseudoLRU tree: a leaf is *protected* at tree level l if the l<sup>th</sup> node on a path from root to leaf is labeled 0 when the leaf is in the right subtree of that node, or labeled 1 when the leaf is in the left subtree of that node; otherwise, the leaf is *unprotected*. A promoted block is protected at all levels, while the block chosen as the victim is unprotected at all levels. We also define the *protected subtree* of a node to be the right subtree if the node is labeled 0, or the left subtree if the node is labeled 1.

# **PseudoLRU Ordering**

The leaves of the PseudoLRU tree may be ordered from 0 to n - 1 in much the same way as the positions in the LRU recency stack [22]. The most protected leaf occupies position 0, *i.e.* the "PseudoMRU" block. The most unprotected leaf occupies position

| <b>Old Position</b> | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|---------------------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| New Position        | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 | 1 | 2  | 3  | 0  | 1  | 0  | 0  |

Table 3.1: Minimal Disturbance promotion for 16-way associativity.

n - 1, *i.e.* it is the PseudoLRU block. The other blocks occupy positions in between. For example, the sibling of the PseudoMRU block occupies position 1, and the first cousins of the PseudoMRU block are in positions 2 and 3. Let us think of the position of a leaf as a binary integer whose least significant bit is associated with the leaf. At each level of the tree, the relevant bit in the position is 1 if the leaf is unprotected at that level, or 0 if it is protected at that level.

One way to see the ordering is by considering a simple transformation on the binary tree: for each internal node labeled with 0, swap the left and right subtrees and change the label to 1. This procedure produces a canonical form in which the leaf nodes are ordered from left to right in ascending recency position: the rightmost leaf is the PseudoLRU way and the leftmost leaf is the PseudoMRU way. For example, Figure 3.2 shows an example 8-way associative PseudoLRU tree representing internal nodes numbers 0 through 6 labeled with randomly chosen binary values. After the transformation, nodes 0, 2, 3, and 5 would have their left and right subtrees swapped, placing the leaves into ascending order of position.

Promoting a block has the effect of moving other blocks into less fortunate positions, sometimes dramatically so. For instance, promoting a block such that the bit in the root node is toggled may move the previous PseudoLRU block down by n/2 positions.

Only one block at a time is in the PseudoLRU position, but the position of each block is roughly proportional to its vulnerability to being moved to the PseudoLRU position in the near future.

#### 3.2.2 PseudoLRU Disturbs Non-Promoted Blocks

Let us consider the placement/promotion algorithm for tree-based PseudoLRU. At each level in the tree, the algorithm alters a bit to protect the referenced block without regard for the disturbance caused to other blocks. We consider the disturbance to a block to be the number of positions it is moved as a result of an placement or promotion to another block. Disturbance typically can be defined as the act of interfering with the arrangement, order, or harmony of, in this case the promotion of referenced blocks alters the order of non-referenced blocks in the set , that can lead to consequences such as making non-referenced blocks become vulnerable to eviction.

PseudoLRU is a disturbing policy because it changes in the positions of the nonreferenced blocks out of proportion to the analogous changes in standard LRU. Figure 3.1 shows the average magnitude of the change in position (the *y*-axis) for non-referenced blocks when a block at a given position (the *x*-axis) is placed or promoted for LRU and PseudoLRU. The average is for a 16-way set-associative 16MB cache taken over the 100 8-core workloads described in Section 3.4. For LRU, the maximum change in the position of a non-referenced block is 1 when the formerly MRU block is not referenced, and goes down to 0.6 for the LRU block. For tree-based PseudoLRU, the non-referenced blocks' positions are changed much more. The formerly PseudoMRU block travels on average two positions away, the block in position 12 moves 1.39 positions away, and at most block positions the distance traveled is significantly higher than the corresponding position in true LRU.

Thus, tree-based PseudoLRU is more disturbing to blocks' positions than true LRU, so the blocks' PseudoLRU recency positions are inaccurate reflections of their true recency positions in true LRU. That is, blocks that might have locality may needlessly be moved too close to LRU, exposing them to the risk of eviction. To the extent that imitating true LRU is a worthy goal, PseudoLRU somewhat fails. This is not really surprising as we expect to give up some performance when gaining a more space-efficient policy. However, what is surprising is that *this level of disturbance is totally unnecessary*, and removing it results in a replacement policy superior to LRU.

#### 3.3 Design

We present a different placement and promotion policy for tree-based PseudoLRU: place and promote blocks to positions that cause the minimal amount of disturbance among all blocks. The positions of blocks in the tree can be directly manipulated with simple algorithms [22], but we must still choose what the new positions should be to minimize disturbance.

#### 3.3.1 Minimal Disturbance Placement

When an incoming block is placed, we must balance the potential disturbance caused to existing blocks with the potential risk of eviction to the placed block if it is left completely unprotected from eviction. What is the choice of placement position to achieve minimal disturbance?

From this, we decide that the logical choice of placement is the one that affords the most protection to the incoming block while still allowing for a majority of the existing blocks to remain in the same position, while disturbing a minority of blocks .

Based on this premise, for an *n*-way set-associative cache, a MDPP Cache would place incoming blocks in position 3n/4. Since the previous position of a newly evicted block was n - 1, placing the block into position 3n/4 insures that the labels of the root node and the second-level nodes remain the same so there are no wide swings in the positions of the 3/4 of blocks closest to PseudoMRU. Changing bits any closer to the root risks affecting the positions of a majority of other blocks. The newly placed block remains unprotected at the root level and second level, but fully protected beyond that so it has a good opportunity to be referenced and thus promoted.

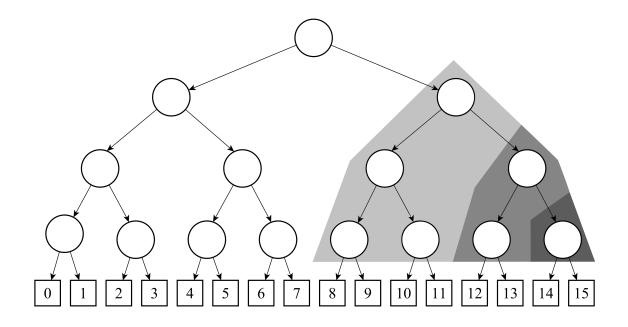

#### 3.3.2 Minimal Disturbance Promotion

Table 3.1 gives the old and new positions for promotions for 16-way associativity. Let us recursively subdivide the PseudoLRU tree into  $1 + \log_2 n$  regions of greater and lesser protection, starting with the protected subtree of the root, then the protected subtree of the unprotected subtree of the root, and so on, ending with singleton subtrees at positions n-2and n-1. Figure 3.3 illustrates these regions of protection. When a block *B* is promoted, a minimal number of bits in the tree are changed such that the first block in the smallest unprotected region that contains *B* is moved to the MRU position. As a result, *B* is moved along with the first block to a position relatively close to MRU. This strategy gives due protection to the promoted block while minimizing movements among the other blocks. Thus, for n = 16, *i.e.* 16-way associativity, the blocks in positions 0 through 7 remain in the same positions because they are already in the protected subtree. Position 8 moves to position 0, position 9 moves to position 1, and so forth as in Table 3.1.

Note that implementing our modified promotion and placement policies incurs virtually no extra energy or area penalty; the replacement status vector is updated using the same sort of logic as tree-based PseudoLRU, but with a different set of state transitions. Indeed, dynamic energy is reduced because for a great many accesses no update needs to be made to the status vector.

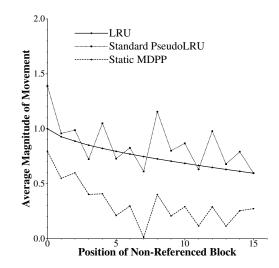

#### **Effect of Minimal Disturbance on Block Positions**

Figure 3.4 shows the effect of minimal disturbance placement and promotion on the average change of non-referenced blocks. The magnitude of changes in position is far less than the average for PseudoLRU or even true LRU. The block in position 0 moves the most, an average of 0.79 positions. Movements of subsequent blocks steadily decrease until block 8, which moves an average of 0.40 positions. The block in the PseudoLRU

Figure 3.3: Regions of Protection in the PseudoLRU Tree

position moves an average of 0.27 positions. We can quantify the "total disturbance" of a placement and promotion policy as the area under the curve in Figure 3.4. Integrating the curves for the three replacement policies, we see that the total disturbance caused by LRU is 12.1, by PseudoLRU is 13.8, and by minimal disturbance PseudoLRU is 5.2.

Quantifying disturbance for RRIP is problematic for two reasons: 1) block positions are not distinct, as in LRU and PLRU; and 2) promotion of a block in RRIP is decoupled from changes in other block positions; blocks are only moved away from MRU on evictions so RRIP is not directly comparable with policies where promotions necessarily disturb some non-promoted blocks.

# **Disturbance to the Evicted Block**

Figure 3.4 assumes that the disturbance of moving from one position to the next is constant. However, evicting a block, *i.e.* moving it from LRU to a position out of the cache, incurs far more disturbance to a block than simply moving it to another position. Thus, for

Figure 3.4: Average change in recency stack position for LRU, PseudoLRU, and MDPP Cache

example, an absurd policy of inserting only into the LRU position and never promoting any blocks would have a very high miss rate but relatively cause minimal disturbance. A more nuanced formulation of the disturbance metric would assign a larger distance to evicting a block than to simply changing its position. This distance would take into account latency to satisfy a cache miss as well as the probability that the block will be referenced again. There is no general way to know that probability *a priori* but, as we will see in Section 3.3.3 we can estimate it dynamically with dead block prediction.

# 3.3.3 Dynamic MDPP

The minimal disturbance MDPP Cache policy as presented so far is a *static* policy. That is, the policy remains the same regardless of the run-time features of the workload. However, a great deal of recent work has focused on *dynamic* policies that change in response to workload characteristics. Thus, we extend the minimal disturbance idea to a dynamic policy. In particular, we allow the placement position to be adapted through dead block prediction.

Some recent dynamic policies adapt the placement position using techniques such as prediction [37] and set-dueling [28, 12]. Other policies implement selective *bypass*, *i.e.* when an incoming block is predicted to not be used before it is evicted, it is not placed in the cache but rather bypassed to the core [16, 19]. Both of these ideas are compatible with the minimal disturbance idea of causing as little disturbance as possible. Clearly, selective bypass works along provoking minimal disturbance: a block that will not be re-referenced will only pollute the cache and confuse the replacement policy. Such a block cannot be disturbed by bypass because it is already a dead block. Adapting the placement position can also achieve the minimal disturbance for PseudoLRU caches as long as the placement position is beyond the halfway point in the PseudoLRU recency stack so as not to make wide swings in block positions.

We use the sampling-based dead block prediction algorithm (SDBP) [16] to drive block placement and bypass. A dead block predictor predicts whether a block that has been placed or referenced will be referenced again before it is evicted. The SDBP paper uses the program counter (PC) of a memory instruction to index a skewed predictor that provides a number between 0 and 9. If that number exceeds a threshold, the referenced block is predicted to be dead. If the block is referenced again, the corresponding counters in the prediction tables are decremented. If the block is evicted before being referenced again, the counters are incremented. The predictor learns from a *sampler*, a small set of partial tags held separately from the cache and managed with the LRU policy. In the original paper, each cache block has a prediction bit associated with it to drive the replacement policy. Our technique does not need this extra bit since the PseudoLRU block is always evicted. The technique only consults the predictor when a block is placed.

We modify the MDPP Cache policy to incorporate dynamism for a 16-way set-associative cache as follows: on a cache miss, the PC of the offending memory instruction is used to

consult the dead block predictor. The predictor returns a confidence value c between 0 and 9. If c = 0, the block is placed in position 8, which is the closest placement to PseudoMRU that does not disturb the 8 blocks in the protected subtree of the root. If 0 < c < 6 then the block is placed in position 14. This choice of placement position swaps the previous PseudoLRU block with the next-to-PseudoLRU block, having no effect on the positions of any other block in the set. If  $c \ge 6$  then the block is bypassed, and the replacement state for the set remains unchanged. The cutoff for bypass of 6 or greater was determined empirically.

# 3.4 Evaluation

## 3.4.1 Methodology

We model performance with two simulators: one for single-threaded workloads and one for eight-core multi-programmed workloads. Both simulators use the following memory hierarchy parameters: L1 data cache: 32KB 8-way associative, L2 unified cache: 256KB 8-way, 16-way, DRAM latency: 200 cycles. The single-thread simulator uses a 4MB L3 cache while the multi-core simulator uses a 16MB L3 cache. The single-thread simulator is a modified version of CMP\$im [50]. The version we used was provided with the JILP Cache Replacement Championship [51]. It models an out-of-order 4-wide 8-stage pipeline with a 128-entry instruction window. This infrastructure enables collecting instructions-per-cycle (IPC) figures as well as misses per kilo-instruction and dead block predictor accuracy. For multi-core workloads, we found that CMP\$im was quite slow and was unable to complete correctly beyond six cores. Thus, we adapted an in-house simulator to interoperate with CMP\$im's cache replacement code to model eight core workloads.

## Workloads

We use the 29 SPEC CPU 2006 benchmarks. Each benchmark is compiled for the 64bit X86 instruction set. The programs are compiled with the GCC 4.1.0 compilers for C,

| Technique          | Overhead for 4MB cache                        | Overhead for 16MB cache                       |

|--------------------|-----------------------------------------------|-----------------------------------------------|

| LRU                | 4 bits $\times 2^{16}$ blocks = 32KB          | 4 bits $\times 2^{18}$ blocks = 128KB         |

| PseudoLRU          | 15 bits $\times 2^{12}$ sets = 7.5KB          | 15 bits $\times 2^{14}$ sets = 30KB           |

| Static MDPP Cache  | same as PseudoLRU: 7.5KB                      | same as PseudoLRU: 30KB                       |

| SRRIP/DRRIP        | 2 bits $\times$ 2 <sup>16</sup> blocks = 16KB | 2 bits $\times$ 2 <sup>18</sup> blocks = 64KB |

| SHiP               | 16KB for RRIP +                               | 64KB for RRIP +                               |

| SHIP               | 11KB predictor = $27$ KB                      | 11KB predictor = 75KB                         |

| Dynamic MDPP Cache | 7.5KB + 11KB predictor = 18.5KB               | 30KB + 11KB predictor = $41KB$                |

Table 3.2: Overhead required by the various techniques

C++, and FORTRAN. We use SimPoint [52] to identify up to 6 segments (i.e. *simpoints*) of one billion instructions each characteristic of the different program phases for each workload.

# **Single-Threaded Workloads**

For single-threaded workloads, the results reported per benchmark are the weighted average of the results for the individual simpoints. The weights are generated by the Sim-Point tool and represent the portion of all executed instructions for which a given simpoint is responsible. Each program is run with the first ref input provided by the runspec command. For each run, the simpoint is used to warm microarchitectural structures for 500 million instructions, then measures and reports results for the subsequent one billion instructions.

## **Multi-Core Workloads**

For eight-core multi-programmed workloads, we generated 100 workloads consisting of mixes from the SPEC CPU 2006 simpoints described above. Each workload is a mix of eight simpoints chosen uniformly randomly without replacement. For each workload the simulator warms microarchitectural structures until 500 million total instructions have been executed, then measures results until at least one benchmark reaches one billion instructions. Thus, all 8 cores are active during the entire measurement period.

# **Replacement Policies**

We compare our proposed technique against several related techniques: static and dynamic versions of re-reference interval prediction (SRRIP/DRRIP)[12], signature-based hit predictor for RRIP (SHiP)[37], and static and dynamic versions of genetic placement and promotion for tree-based PseudoLRU replacement (GIPPR/DGIPPR) [22]. For both simulators, we directly use code provided by the respective authors either through the World Wide Web or through personal communication. Our dynamic policy uses SDBP [16]. For that predictor, we used the code that is available from the cache replacement championship website[51].

The SHiP authors also graciously provided code for their hit predictor in a form that was readily adaptable to the RRIP code. We modified this code to implement the samplingbased policy described in their paper and use the program counter (PC) as the signature for the hit predictor. Thus, what we hereafter refer to as SHiP in this paper is called SHiP-PC-S in that paper's nomenclature[37]. This modification allows us to control the overhead consumed by SHiP's structures. Thus, we may allocate the same amount of storage to both SHiP and SDBP for a fair comparison of the dynamic policies. To be clear, we implement sampling-based SHiP using the PC as the signature and deciding the placement position for a baseline RRIP policy with a maximum re-reference prediction value of three.

The results we present in this paper compare our technique against SRRIP, DRRIP, SHiP, and GIPPR. In preparing this work, we also compared our technique against SDBPbased replacement and bypass [16] and protecting distance based policy [19]. We find that SHiP is superior in performance to these other policies, so we choose not to present those results and are content to compare with SHiP. We compare with SRRIP as an excellent static policy. We compare with DRRIP as a relatively simple dynamic policy with good performance. We compare with GIPPR/DGIPPR as the most closely related previous work.

#### 3.4.2 Overhead Analysis

## **Overhead for Predictors**

Both SHiP and SDBP require extra state for their prediction structures. SHiP uses a 14-bit signature derived as a hash of the PC indexing a table of 16,384 three-bit saturating counters. It also keeps 14-bit signatures for each block in the sampled sets. SDBP keeps three tables of 8,192 2-bit saturating counters each indexed by a different 13-bit hash of the PC. It also keeps a *sampler*, an array of cache metadata kept separately from the main cache. Each block in the sampler includes a 15-bit partial tag, a valid bit, a prediction bit, a 4-bit LRU stack position and a 15-bit signature. The associativity of the sampler is 12. To keep the same amount of state for each predictor, we use 192 sampled sets for SHiP and 96 sampled sets for SDBP. Both predictors consume approximately 11KB.

#### **Overhead for Techniques**

Each replacement policy we study require some overhead. Table 3.2 summarizes the overhead of the various polices. Note that DRRIP and DGIPPR require a few extra bits for set dueling counters. We ignore this tiny extra storage overhead. The multi-core MDPP Cache saves area over SHiP due to the fact that it requires only one bit of replacement state per block rather than two. This savings translates to a fraction of a percent of the bits allocated to the cache so we do not wish to overstate this advantage. Nevertheless, we note that the replacement state saved is typically implemented using larger 8T register file cells rather than 6T SRAM cells, and the savings in terms of cells per core of the dynamic MDPP Cache over SHiP is approximately 8KB, which is roughly equivalent to the size of a moderate dual-ported branch direction predictor or branch target buffer.

## **Impact of Storage Overhead**

In the main results, we model SHiP and the dynamic MDPP Cache with the same storage overhead for the predictors, including tables of counters and set sampling overhead. However, SHiP consumes 32 extra bits per set for storing the 16 2-bit re-reference interval prediction values, while the MDPP Cache requires only an additional 15 bits per set to store the PseudoLRU tree.

In another area study (not illustrated for space reasons), we performed three iso-area comparisons of SHiP with dynamic MDPP Cache to study the impact of this additional storage overhead. In the first experiment, we modeled SHiP with a smaller 2.5KB predictor, thus reducing the total overhead of SHiP to roughly the same as the dynamic MDPP Cache for the single-core 4MB cache configuration. This change had negligible impact on SHiP's performance. In the second experiment, we modified SHiP to use one bit for RRIP states rather than two bits, so that SHiP and the dynamic MDPP Cache would have equivalent storage requirements for the larger 16MB cache. This change resulted in a reduction of SHiP's speedup from 9.1% to 6.9%. In the third experiment, we allowed the 16MB dynamic MDPP Cache to expand the number of sampled sets such that SHiP and the MDPP Cache consume the same number of bits overall, including the per-set bits in the hardware budget. This allows the MDPP Cache to use 966 sampled sets instead of 96, resulting in an increase in the speedup to 11.5% from 11.0%. Thus, while the size of the SHiP predictor does not seem to have a large impact on performance, the size of the per-block state, which is the majority of the cache management metadata storage in the multi-core cache, has a significant impact on performance. Moreover, replacing SHiP with the dynamic MDPP Cache and keeping total area constant results in an 11.5% speedup.

## **3.4.3** Results for Static Policies

This section gives results for static policies. These policies do not adapt to changing workload characteristics, but are relatively simple to implement and verify. For instance, the static MDPP Cache policy could be plugged in easily to an existing PseudoLRUreplaced cache by simply modifying the algorithm or lookup table that implements placement and promotion.

Figure 3.5: (a) Normalized Weighted Speedup over LRU for Static Policies on 8-core Workloads, and (b) Misses Normalized to LRU for Static Policies

## **Multi-Core Workloads**

Figure 3.5 shows weighted speedup normalized to LRU for SRRIP, static MDPP Cache, and standard PseudoLRU with a 16MB last-level cache (see Section 4.3.1 for our definition of speedup). The figure shows the speedups for each workload in ascending sorted order to yield S-curves. Standard PseudoLRU performs somewhat worse than LRU, giving a geometric mean speedup of 0.99. SRRIP gives a 5.2% improvement over LRU. Static MDPP Cache gives a 2.8% improvement over LRU. The best speedup of the static MDPP Cache over SRRIP is 10%, while the best speedup of SRRIP over the static MDPP Cache is 16%. SRRIP performs better, but at a cost of 56% more storage overhead. GIPPR with a single vector (not shown) performs quite poorly, so much so that it is impractical to

Figure 3.6: Speedup over LRU for Static Policies on Single-Threaded Workloads

Figure 3.7: Misses Normalized to LRU

illustrate the performance graphically. Its average speedup over LRU is 0.87, *i.e.* it delivers a 13% slowdown. We have probed deeply into the GIPPR algorithm with the author of the original work to try to determine why it performs so poorly on multi-core workloads. GIPPR was designed by a genetic algorithm using single-threaded workloads. We conclude that its parameters work well in that context, but are not suitable for multi-core workloads. Single-core workloads are characterized by a few distinct patterns of behavior

that can be captured by a handful of GIPPR vectors, but multi-core workloads combine characteristics resulting in a wide range of behaviors that cannot be distilled down to a small number of vectors.

## Misses

Figure 3.5(b) illustrates misses for the static policies on multi-core workloads. The graph shows misses normalized to LRU in descending order, *i.e.* best-to-worst from left-to-right, to yield S-curves. GIPPR delivers the fewest misses for approximately 20% of the workloads, but is worse than LRU for a majority of workloads, giving on average 5.7% more misses than LRU. SRRIP and static MDPP Cache perform closely, with SR-RIP giving 94.5% of the misses of LRU and MDPP minimal disturbance PseudoLRU giving 94.8% of LRU. minimal Disturbance PseudoLRU performs significantly worse than LRU for about 20% of the workloads. Several of those workloads are quite sensitive to misses, explaining SRRIP's significant performance advantage over minimal disturbance PseudoLRU. Standard PseudoLRU performs similarly to LRU.

#### Single Threaded Workloads

Figure 3.6 gives the speedup over LRU for several static techniques on single-threaded workloads with a 4MB last-level cache. The benchmarks on the *y*-axis are sorted based on their performance on the DRRIP policy. We use the same ordering in Section 3.4.4 for the bar chart there. Most of the benchmarks are not helped or significantly hurt by most of the polices. The aggregate speedup attributable to the polices are mostly due to the memory intensive benchmarks listed to the right of 401.bzip2. However, some benchmarks such as 459.GemsFDTD and 471.omnetpp experience some slowdown from non-LRU policies.

Standard PseudoLRU gives no speedup or slowdown over LRU on average. SRRIP gives a geometric mean 2.6% speedup over LRU. GIPPR with a single vector optimized for the SPEC CPU 2006 benchmarks gives a speedup of 3.5%. minimal Disturbance

Figure 3.8: (a) Normalized Weighted Speedup over LRU for Dynamic Policies on 8-core Workloads, and (b) Misses Normalized to LRU for Static Policies

PseudoLRU gives a speedup of 2.5%. Thus, the static MDPP Cache gives comparable performance to SRRIP. While GIPPR is slightly better than the static MDPP Cache on single-threaded workloads, we shall see that GIPPR performs poorly on multi-core workloads.

## Misses

Figure 3.7 illustrates misses normalized to LRU for the single-threaded workloads. The benchmarks on the *y*-axis are sorted in descending order of misses for DRRIP normalized to LRU. Although GIPPR gives the best speedup, it only gives a geometric mean 95% of the misses of LRU. This counterintuitive result is largely due to the contribution of 447.dealII, for which GIPPR more than doubles the misses of LRU, but whose change in performance is smaller than the changes for benchmarks such as 436.cactusADM and 429.mcf. The geometric mean of normalized misses for standard PseudoLRU is approximately the same as LRU. SRRIP and static MDPP Cache both give an arithmetic

Figure 3.9: Speedup over LRU for Dynamic Policies on Single-Threaded Workloads

mean 94% of the misses of LRU.

## 3.4.4 **Results for Dynamic Policies**

This section gives results for dynamic policies. These policies adapt to different workload characteristics using set-dueling and/or prediction. Dynamic policies deliver the best performance in the literature. In particular, SHiP represents the current state-of-the-art cache management policy.

# **Multi-Core Workloads**

Figure 3.8(a) shows the normalized weighted speedup for the various dynamic techniques. The speedups for the 100 workloads are shown as S-curves, sorted in ascending order. DRRIP yields an 8.4% speedup. The state-of-the-art SHiP policy gives a 9.1% speedup. The dynamic MDPP Cache achieves an 11.0% speedup. The best speedup of the dynamic MDPP Cache over SHiP is 25%, while the best speedup of SHiP over the dynamic MDPP Cache is 18%. Thus, the MDPP Cache improves performance over previous techniques without increasing complexity.

## Misses

Figure 3.8(b) shows the misses normalized to LRU for the various dynamic tech-

niques sorted in descending order, *i.e.* best-to-worst from left-to-right, to yield S-curves. 4DGIPPR is by far the worst, giving an average 4.2% more misses than LRU. SHiP and dynamic MDPP Cache are evenly matched, both delivering 85% of the misses of LRU. The advantage of MDPP Cache over SHiP on speedup is likely due to the effects of memory-level parallelism and other second-order effects in the workloads. DRRIP gives 87% of the misses of LRU. All of the policies except for 4DGIPPR give fewer misses than LRU for 85% – 90% of the workloads.

## **Single-Threaded Workloads**

Figure 3.9 illustrates the speedup over LRU of the various dynamic techniques. The benchmarks on the *y*-axis are sorted based on their speedup over LRU for the DRRIP policy. DRRIP achieves a speedup of 5.4% over LRU. Dynamic MDPP Cache yields a 5.9% speedup. 4DGIPPR, the 4-vector dynamic version of GIPPR, gives a 5.6% speedup. SHiP gives a 5.9% speedup. Thus, dynamic MDPP Cache matches the performance of the state-of-the-art policy SHiP and exceeds the performance of 4DGIPPR whose 4 vectors are specially designed to work well with these specific single-threaded workloads.

Figure 3.10: Misses for the Dynamic Policies Normalized to LRU

Figure 3.11: Contributions of minimal disturbance promotion and static/dynamic minimal disturbance placement

# Misses

Figure 3.10 gives the normalized misses for the dynamic policies. The benchmarks on the *y*-axis are sorted in descending order of their misses on DRRIP normalized to LRU. DRRIP and 4DGIPPR both give geometric mean normalized misses of 91% of LRU. SHiP delivers a geometric mean normalized misses of 89% of LRU. Dynamic minimal disturbance PseudoLRU yields 88% of the misses of LRU. Curiously, all of the dynamic policies seem to give more misses than the static policies on 447.dealII, although this fact does not have a large impact on performance because 447.dealII is not as memory-bound as some of the other benchmarks.

#### 3.4.5 Analysis